# A 15.3-dBm, 18.3% PAE F-Band Power Amplifier in 130-nm InP HBT With Modulation Measurements

Vinay Iyer<sup>®</sup>, Graduate Student Member, IEEE, Jay Sheth<sup>®</sup>, Member, IEEE, Linsheng Zhang<sup>®</sup>, Graduate Student Member, IEEE, Robert M. Weikle<sup>®</sup>, Fellow, IEEE, and Steven M. Bowers<sup>®</sup>, Senior Member, IEEE

Abstract—A scalable platform for modulation measurements at millimeter- and submillimeter-wave frequencies is presented and demonstrated at 121 GHz. The system is used to characterize a 130-nm InP stacked power amplifier (PA) at saturated power levels, without using digital predistortion (DPD). A peak data rate of 10 Gb/s is achieved at a peak power level of 14.1 dBm (max power added efficiency (PAE) point) and is the highest recorded data rate on stand-alone PAs at frequencies greater than 100 GHz at peak power levels greater than 10 dBm. The PA exhibits a peak gain of 11.7 dB and a 3-dB bandwidth (BW) of 45 GHz, measured from 90 to 135 GHz. The peak measured PAE and saturated output power ( $P_{\rm sat}$ ) at 112.5 GHz are 18.3% and 15.3 dBm, respectively.

Index Terms—Heterojunction bipolar transistor (HBT), millimeter-wave-integrated circuit (MMIC), modulation measurements, power amplifiers (PAs).

## I. Introduction

OWER amplifiers (PAs) are crucial building blocks in a variety of applications and influence system efficiency and performance metrics. F- and D-band PAs specifically have use in short-range applications, such as inter-chip communications, and in millimeter-wave front-haul and back-haul for communication systems [1]. The stacked PA topology is an attractive candidate to simultaneously optimize gain, output power, and power added efficiency (PAE) in scaled technologies [2], [3]. Advances in silicon and III-V technologies have also enabled the realization of complete transmitter chains capable of high data rates at moderate to high effective isotropic radiated power (EIRP). There have been previous demonstrations of complete transmitters at D-band, but these systems used custom integrated circuits to perform modulation [4], [5], [6], [7], [8]. There is value in being able to characterize the performance of individual circuit blocks using commercial equipment as millimeter-wave systems proliferate.

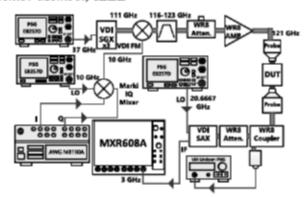

This work presents a custom-built modulation chain using commercial equipment, as shown in Fig. 1, that is used to

Manuscript received 9 September 2022; revised 1 November 2022; accepted 29 November 2022. Date of publication 2 January 2023; date of current version 10 May 2023. This work was supported in part by the NSF (SpectrumX—an NSF Spectrum Innovation Center) under Grant AST-2132700 and in part by the National Ground Intelligence Center (NGIC) under Contract W50NH921C0013. (Corresponding author: Vinay Iyer.)

Vinay Iyer, Jay Sheth, Linsheng Zhang, and Steven M. Bowers are with the Department of Electrical and Computer Engineering, University of Virginia, Charlottesville, VA 22903 USA (e-mail: vvi4hc@virginia.edu).

Robert M. Weikle is with the Department of Electrical and Computer Engineering and the Department of Physics, University of Virginia, Charlottesville, VA 22903 USA.

Color versions of one or more figures in this letter are available at https://doi.org/10.1109/LMWT.2022.3227755.

Digital Object Identifier 10.1109/LMWT.2022.3227755

Fig. 1. 121-GHz modulation measurement setup depicting the flow of various signals and components. Waveguide connections are colored blue.

characterize the behavior of stand-alone circuit blocks, such as PA at 121 GHz, across a range of power levels. Next, the design and characterization of an example wideband stacked PA in a 130-nm InP process are detailed. The stacked PA [9] has a peak |S21| of 11.7 dB, a peak PAE of 18.3%, a 3-dB bandwidth (BW) from 90 to 135 GHz, and a gain greater than 8.8 dB from 90 to 140 GHz. The PA has at least 10 dB of gain from 95 to 130 GHz. The PA stages and interstage network are designed so as to have a load line match close to 50  $\Omega$ . The amplifier is capable of data rates of 500 mega symbols per second (MSPS) 16 quadrature amplitude modulation (OAM) with an rms error vector magnitude (EVM) of 5.8% and an average PAE of 5.2% at an average output power level of 8.2 dBm, and 5-giga symbols per second (GSPS) QPSK with an rms EVM of 14.3% at an average output power of 7.8 dBm with a peak-to-average power ratio (PAPR) of 6.3 dB. Using a low-frequency arbitrary waveform generator (AWG), this chain is also capable of being extended to higher frequencies and higher modulation BWs, such as 64 QAM, at higher P<sub>sat</sub> than the Tx module used in [10].

#### II. MODULATION CHAIN

This demonstration was designed at a center frequency of 121 GHz. On the transmitter side, a Keysight E8257D signal generator is used to produce an local oscillator (LO) for a WR8 Virginia Diode Inc. (VDI) Signal Extender (SGX) at 37 GHz. The SGX (×3) multiplies the signal up to the WR8 band. A Keysight M8190A AWG is used to generate baseband in-phase/quadrature-phase (I/Q) data, which is then used to drive a Marki I/Q mixer (MMIQ 0520HS). The LO input to the I/Q mixer is powered by an E8257D at 10 GHz. The signal multiplied up by the WR8 extender is mixed with the RF output of the Marki I/Q mixer using a VDI Fundamental Mixer. The output of the mixer is connected to a VDI bandpass

2771-957X © 2023 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See https://www.ieee.org/publications/rights/index.html for more information.

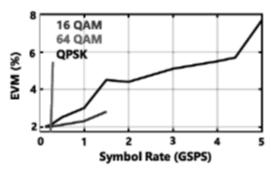

Fig. 2. EVM performance of the chain without the DUT across modulation formats. The measured EVM at 5-GHz QPSK is 7.7%.

mesh filter that passes the 121-GHz modulated signal. The image at 101 GHz is rejected by more than 50 dB. The modulated signal at 121 GHz passes through a waveguide attenuator and is then amplified using a VDI WR8 amplifier to ensure the PA device under test (DUT) can be saturated to peak output power. The P1dB of the VDI amplifier is 13 dBm. The combination of the attenuator and VDI amplifier enables measurements for the DUT at various back-off power levels. On the receiver side, the signal from the probe is sent to a waveguide 10-dB directional coupler. The coupled output is connected to a PM5 power meter. The IF output of the SAX (centered at 3 GHz) is connected to a Keysight MXR608A 6-GHz scope. The scope runs the Vector Signal Analyzer (VSA) software and is used to analyze the waveform and look at the rms EVM numbers. The 10-MHz reference clock on all Keysight equipment is connected together, with the oscilloscope clock output acting as the master. The chain is characterized without the probes and DUT to understand the effects on the measurements of the DUT's EVM performance. As shown in Fig. 2, this wideband chain is capable of up- and down-converting a low-power 1500-MSPS 16-QAM signal with an EVM of 2.8%, a 300-MSPS 64-QAM signal with an EVM of 5.5%, and a 5-GSPS QPSK signal with an EVM of 7.7%. An adaptive equalization generated by the Keysight VSA is applied to this chain (without the PA).

### III. PA DESIGN

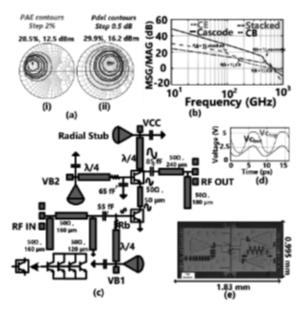

The single stage large signal power gain at frequencies greater than 100 GHz is typically low, and amplifiers usually have multiple stages [11]. The stacked amplifier topology [12], [13], [14], [15] is an excellent design choice for increasing output power and gain while ensuring all devices stay within their safe operating area (SOA) limit. This PA was fabricated in the Teledyne 130-nm InP heterojunction bipolar transistor (HBT) process  $(f_t/f_{max})$  in excess of 500 GHz/1 THz [16], [17]. The BVCE<sub>O</sub> is 3.5 V. The technology has three metal layers and metal-insulator-metal (MIM) capacitors. Fig. 3(b) compares the maximum stable gain (MSG; the MSG that can be achieved by a potentially unstable device) for the cascode, common emitter (CE), common base (CB), and stacked topologies for a unit transistor with an emitter length of 6  $\mu$ m. In the stacked PA, a CE stage drives a CB stage, with an interstage matching network in between, so the voltage across the two stages swings in phase. The capacitance at the base of the CB stage is designed in conjunction with the interstage transmission line to ensure optimal phasing, as shown in Fig. 3(d).

Fig. 3(a) compares the simulated load pull contour between class A CE [Fig. 3(a)-(i)] and the stacked PA [Fig. 3(a)-(ii)]

Fig. 3. (a) Loadpull contours for class A (i) CE and (ii) stacked PA. Each stage in the CE and stacked PA was comprised of four transistors, each 6-μm long. (b) MSG comparison for the CE, CB, and stacked topology. (c) Schematic of the stacked PA. (d) Collector voltage waveform at the two nodes. (e) Die photograph of the stacked PA.

at 125 GHz at various levels of compression. Fig. 3(c) shows the architecture of the design. Radial stubs are used in this design for broadband bias insensitivity. The transistors in the CB stage are laid out with the bases in proximity so as to minimize stray inductance and prevent instability. The series capacitors are EM simulated in isolation before insertion into the matching networks. Each stage in the CE and stacked PA consists of four transistors, with an emitter length of 6  $\mu$ m each. The optimum load impedance for the CE amplifier is  $10 + j15 \Omega$  for peak efficiency. Matching this impedance to 50  $\Omega$  requires high-Q components and is difficult to design with broad BW. The optimum load impedance for the stacked PA design is  $60 + j40 \Omega$ , making a broadband match easier to implement. The simulated output network passive efficiency exceeds 80% for the WR8 band. The simulated interstage and output matching network losses are 0.9 and 0.7 dB at 125 GHz. A 65-fF capacitor was used at the base of the cascode stage, and a 150- $\Omega$  resistor (Rb) was used to both thermally ballast and electrically stabilize the PA, as shown in Fig. 3(c).

## IV. MEASUREMENTS AND RESULTS

## A. CW Measurements

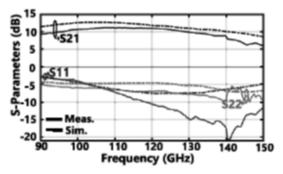

A die photograph is shown in Fig. 3(e). The small signal S parameters were measured across two bands, WR8 and WR5, using VDI Vector Network Analyzer (VNA) Extenders (VNAx) interfaced to a Keysight PXA VNA. The small signal S-parameters (simulated and measured) are shown in Fig. 4(c). The peak measured gain is 11.7 dB at 112.5 GHz and exceeds 10 dB from 95 to 130 GHz.

Large signal measurements were performed from 90 to 140 GHz. A Keysight signal generator connected to a VDI WR8 tripler (WR8.0X3) followed by a VDI amplifier is used to drive the input of the PA. The output power is measured using a VDI PM5 power meter. The PA saturates at 8.5-dBm available input power. Fig. 5(a) plots the measured and simulated peak PAE (%), and output power at peak PAE (dBm) across frequency. The measured peak PAE is 18.3%, and the peak output power is 15.3 dBm, at 112.5 GHz.

Fig. 4. Simulated and measured S-parameters of the PA showing a 3-dB gain BW of 45 GHz.

Fig. 5. Large signal. (a) Measured and simulated output power at maximum PAE (%), and maximum PAE (%). (b) Measured and simulated gain (dB), output power (dBm), and PAE (%) at 112.5 GHz—with a peak PAE and output power at peak PAE, of 18.3% and 15.3 dBm.

Fig. 5(b) plots the simulated and measured gain (dB), output power (dBm), and PAE (%) at 112.5 GHz against available input power, showing 7 dB of gain at peak PAE.

## B. Modulation Measurements

Modulation measurements are performed at 121 GHz using the setup in Fig. 1. The complete signal chain, without the DUT, is equalized across power levels using the VSA software, and input power numbers are noted. The stimulus generated is then applied to the chain with the PA. The PA performance is measured up to 5-GSPS QPSK, limited by the equipmentspecifically the sampling speed of the AWG. The PA output power and modulation performance are simultaneously measured to arrive at PAE numbers. Demonstrative results are plotted in Fig. 6(a) and (b) for 500 MSPS 16 QAM and 5-GSPS QPSK, respectively. The trends across average output power level are plotted in Fig. 6(c). The EVM is 14.3% for 5-GSPS QPSK (PAPR of 6.3 dB), operating at an average power of 7.8 dBm—the output power at maximum PAE at 120 GHz is 14.2 dBm. Table I compares the performance of the PA with prior stand-alone PAs operating at frequencies greater than 100 GHz. The PA achieves a maximum data rate at state-of-the-art levels while at a higher power level.

Fig. 6. Constellations for (a) 500 MSPS 16 QAM and (b) 5-GSPS QPSK.

(c) Performance across average output power (dBm), depicting 14% EVM for 5-GSPS QPSK.

TABLE I

TABLE OF COMPARISON FOR STAND-ALONE PAS/FRONT

ENDS AT GREATER THAN 100 GHZ

| Ref.                 | This Work         |         | [10]                            | [18]             | [4] / [19]         |        |

|----------------------|-------------------|---------|---------------------------------|------------------|--------------------|--------|

| Pout 1dB<br>BW (GHz) | 97.5-122.5        |         | 107-135**                       | 147-153.5**      | 125-145**          |        |

| Technology           | 130nm InP         |         | 130nm SiGe                      | 45nm<br>CMOS SOI | 250nm InP<br>+CMOS |        |

| PA Topology          | 1 stg.<br>stacked |         | 8 way slotline<br>comb. Doherty | Tx FE.           | 4 way<br>combined  |        |

| Psat (dBm)           | 15.3              |         | 22.7                            | 1.9              | 17                 |        |

| Peak PAE (%)         | 18.3              |         | 18.7                            | 11**             | 20                 |        |

| @ (GHz)              | 112.5             |         | 110                             | 149.9            |                    |        |

| Peak S21 (dB)        | 11.7              |         | 21.8                            | 22.5**           | 20                 |        |

| Mod. Freq.           | 121 GHz           |         | 131.5 GHz                       | 150.7 GHz        | 135 GHz            |        |

| Mod. Format          | 16 QAM            | QPSK    | 16 QAM                          | 64 QAM           | 64QAM              | 16QAM  |

| Data rate<br>(Gb/s)  | 2                 | 10      | 8                               | 10.56            | 6                  | 4      |

| EVM                  | 5.8%              | 14.3%   | 11.6%                           | 9.5%             | 12%**              | 12%**  |

| PAE <sub>sog</sub>   | 5.2%<br>8.2 dRm   | 7.8 dBm | 7.9%<br>13.7 dBm                | 0.1 dBm          | 11 dRm             | 11 dRm |

| Pouterg              | 8.2 dBm           | 7.8 dBm | 13.7 dBm                        | U.1 dBm          | 11 dBm             | 11 dBm |

<sup>\*\*</sup>Estimated from plots

## V. CONCLUSION

This work presents a scalable modulation chain built using commercial equipment at 121 GHz and its demonstration using a 130-nm InP HBT PA. The PA has a 3-dB small signal gain BW from 90 to 135 GHz with a peak gain of 11.7 dB, a peak PAE of 18.3%, and a peak power of 15.3 dBm at 112.5 GHz. To the best of author's knowledge, these results demonstrate the highest data rate for stand-alone PAs operating at frequencies greater than 100 GHz, at peak output power greater than 10 dBm using commercially available equipment.

#### ACKNOWLEDGMENT

The authors would like to thank Dr. Jeffrey Hesler and Virginia Diodes for help on measurements, and Dr. Herbert Zirath, Chalmers University, Gothenburg, Sweden, and Dr. Travis Blalock, University of Virginia, Charlottesville, VA, USA, for technical discussions.

#### REFERENCES

- Radio Frequency Channel/Block Arrangements for Fixed Service Systems Operating in the Bands 130–134 GHz, 141–148.5 GHz, 151.5–164 GHz and 167–174.8 GHz, Int. Telecommun. Union, Geneva, Switzerland, 2009.

- [2] Z. Liu, T. Sharma, and K. Sengupta, "80–110-GHz broadband linear PA with 33% peak PAE and comparison of stacked common base and common emitter PA in InP," *IEEE Microw. Wireless Compon. Lett.*, vol. 31, no. 6, pp. 756–759, Jun. 2021.

- [3] K. Eriksson, I. Darwazeh, and H. Zirath, "InP DHBT distributed amplifiers with up to 235-GHz bandwidth," *IEEE Trans. Microw. Theory Techn.*, vol. 63, no. 4, pp. 1334–1341, Apr. 2015.

- [4] A. A. Farid, A. S. H. Ahmed, and M. J. W. Rodwell, "A 27.5dBm EIRP D-band transmitter module on a ceramic interposer," in *Proc. IEEE Radio Freq. Integr. Circuits Symp. (RFIC)*, Jun. 2021, pp. 43–46.

- [5] A. Singh et al., "A D-band radio-on-glass module for spectrally-efficient and low-cost wireless backhaul," in *Proc. IEEE Radio Freq. Integr. Circuits Symp. (RFIC)*, Aug. 2020, pp. 99–102.

- [6] S. Carpenter et al., "A D-band 48-Gbit/s 64-QAM/QPSK direct-conversion I/Q transceiver chipset," IEEE Trans. Microw. Theory Techn., vol. 64, no. 4, pp. 1285–1296, Apr. 2016.

- [7] A. Simsek, A. S. H. Ahmed, A. A. Farid, U. Soylu, and M. J. W. Rodwell, "A 140GHz two-channel CMOS transmitter using low-cost packaging technologies," in *Proc. IEEE Wireless Commun.* Netw. Conf. Workshops (WCNCW), Apr. 2020, pp. 1–3.

- [8] M. Ito, T. Okawa, and T. Marumoto, "D-band transceiver utilizing 70-nm GaAs-mHEMT technology for FDD system," in Proc. IEEE BiCMOS Compound Semiconductor Integr. Circuits Technol. Symp. (BCICTS), Nov. 2019, pp. 1–4.

- [9] V. Iyer, J. Sheth, L. Zhang, R. M. Weikle, and S. Bowers, "A 90–125 GHz stacked PA in 130 nm InP HBT with 18.3 % peak PAE at 15.3 dBm output power," in *Proc. United States Nat. Com*mittee URSI Nat. Radio Sci. Meeting (USNC-URSI NRSM), Jan. 2022, pp. 224–225.

- [10] X. Li et al., "A 110-to-130GHz SiGe BiCMOS Doherty power amplifier with slotline-based power-combining technique achieving >22dBm saturated output power and >10% power back-off efficiency," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2022, pp. 316–318.

- [11] H. Wang, P. M. Asbeck, and C. Fager, "Millimeter-wave power amplifier integrated circuits for high dynamic range signals," *IEEE J. Microw.*, vol. 1, no. 1, pp. 299–316, Jan. 2021.

- [12] Z.-M. Tsai, M.-F. Lei, and H. Wang, "An HBT four-cell monolithic stacked power amplifier," in *IEEE MTT-S Int. Microw. Symp. Dig.*, Jun. 2007, pp. 151–154.

- [13] T. J. Farmer, A. Darwish, B. Huebschman, E. Viveiros, H. A. Hung, and M. E. Zaghloul, "Class—A stacked SiGe HBT power amplifier at millimeter-wave," in *Proc. Int. Semiconductor Device Res. Symp.* (ISDRS), Dec. 2011, pp. 1–2.

- [14] A. Chakrabarti and H. Krishnaswamy, "High-power high-efficiency class-E-like stacked mmWave PAs in SOI and bulk CMOS: Theory and implementation," *IEEE Trans. Microw. Theory Techn.*, vol. 62, no. 8, pp. 1686–1704, Aug. 2014.

- [15] M. F. Lei, Z. M. Tsai, K. Y. Lin, and H. Wang, "Design and analysis of stacked power amplifier in series-input and series-output configuration," *IEEE Trans. Microw. Theory Techn.*, vol. 55, no. 12, pp. 2802–2812, Dec. 2007.

- [16] M. Urteaga et al., "A 130 nm InP HBT integrated circuit technology for THz electronics," in IEDM Tech. Dig., Dec. 2016, p. 29.

- [17] M. Bao, V. Vassilev, D. Gustafsson, and H. Zirath, "G-band power amplifiers in 130 nm InP technology," in *Proc. 15th Eur. Microw. Integr. Circuits Conf. (EuMIC)*, Jan. 2021, pp. 5–8.

- [18] A. Hamani et al., "A 84.48-Gb/s 64-QAM CMOS D-band channel-bonding Tx front-end with integrated multi-LO frequency generation," IEEE Solid-State Circuits Lett., vol. 3, pp. 346–349, 2020.

- [19] A. S. H. Ahmed, M. Seo, A. A. Farid, M. Urteaga, J. F. Buckwalter, and M. J. W. Rodwell, "A 140GHz power amplifier with 20.5dBm output power and 20.8% PAE in 250-nm InP HBT technology," in *IEEE MTT-S Int. Microw. Symp. Dig.*, Aug. 2020, pp. 492–495.