Article

# MOCVD-grown β-Ga<sub>2</sub>O<sub>3</sub> as a Gate Dielectric on AlGaN/GaN-Based Heterojunction Field Effect Transistor

Samiul Hasan <sup>1,\*</sup>, Mohi Uddin Jewel <sup>1</sup>, Scott R. Crittenden <sup>2</sup>, Dongkyu Lee <sup>3</sup>, Vitaliy Avrutin <sup>4</sup>, Ümit Özgür <sup>4</sup>, Hadis Morkoç <sup>4</sup> and Iftikhar Ahmad <sup>1,\*</sup>

- Department of Electrical Engineering, University of South Carolina, Columbia, SC 29208, USA

- Department of Physics and Astronomy, University of South Carolina, Columbia, SC 29208, USA

- Department of Mechanical Engineering, University of South Carolina, Columbia, SC 29208, USA

- Department of Electrical and Computer Engineering, Virginia Commonwealth University, Richmond, VA 23284, USA

- \* Correspondence: shasan@email.sc.edu (S.H.); ahmad@cec.sc.edu (I.A.)

**Abstract:** We report the electrical properties of Al<sub>0.3</sub>Ga<sub>0.7</sub>N/GaN heterojunction field effect transistor (HFET) structures with a Ga<sub>2</sub>O<sub>3</sub> passivation layer grown by metal-organic chemical vapor deposition (MOCVD). In this study, three different thicknesses of β-Ga<sub>2</sub>O<sub>3</sub> dielectric layers were grown on  $Al_{0.3}Ga_{0.7}N/GaN$  structures leading to metal-oxide-semiconductor-HFET or MOSHFET structures. X-ray diffraction (XRD) showed the  $(\overline{2}01)$  orientation peaks of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> in the device structure. The van der Pauw and Hall measurements yield the electron density of  $\sim 4 \times 10^{18}$  cm<sup>-3</sup> and mobility of  $\sim$ 770 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup> in the 2-dimensional electron gas (2DEG) channel at room temperature. Capacitance voltage (C-V) measurement for the on-state 2DEG density for the MOSHFET structure was found to be of the order of  $\sim 1.5 \times 10^{13}$  cm<sup>-2</sup>. The thickness of the Ga<sub>2</sub>O<sub>3</sub> layer was inversely related to the threshold voltage and the on-state capacitance. The interface charge density between the oxide and  $Al_{0.3}Ga_{0.7}N$  barrier layer was found to be of the order of  $\sim 10^{12}$  cm<sup>2</sup>eV<sup>-1</sup>. A significant reduction in leakage current from  $\sim 10^{-4} \text{ A/cm}^2$  for HFET to  $\sim 10^{-6} \text{ A/cm}^2$  for MOSHFET was observed well beyond pinch-off in the off-stage at -20 V applied gate voltage. The annealing at 900 °C of the MOSHFET structures revealed that the Ga<sub>2</sub>O<sub>3</sub> layer was thermally stable at high temperatures resulting in insignificant threshold voltage shifts for annealed samples with respect to as-deposited (unannealed) structures. Our results show that the MOCVD-gown Ga<sub>2</sub>O<sub>3</sub> dielectric layers can be a strong candidate for stable high-power devices.

Keywords: GaN; MOSHFET; Ga2O3; MOCVD; gate dielectric

Citation: Hasan, S.; Jewel, M.U.; Crittenden, S.R.; Lee, D.; Avrutin, V.; Özgür, Ü.; Morkoç, H.; Ahmad, I. MOCVD-grown  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> as a Gate Dielectric on AlGaN/GaN-Based Heterojunction Field Effect Transistor. Crystals 2023, 13, 231. https://doi.org/ 10.3390/cryst13020231

Academic Editors: Peng Chen and Zhizhong Chen

Received: 6 January 2023 Revised: 21 January 2023 Accepted: 23 January 2023 Published: 28 January 2023

Copyright: © 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

## 1. Introduction

GaN-based heterojunction field effect transistors (HFETs) have excellent properties such as high critical breakdown field, high current, and superior thermal/chemical stability, which are coveted for high power, both RF and high-frequency switching applications under harsh environments [1–4]. The high-frequency performance of HFETs is limited by a series of effects associated with charge leakage, trapping/de-trapping, and conduction characteristics at different locations of the devices [5]. One of the most significant performance-limiting phenomena is the injection of electrons from the gate electrode to the surface region of the semiconductor on the drain side of the gate electrode, which results in reliability issues as well as limitations on the input drive in power applications [6,7]. For high drain and gate bias, the magnitude of the electric field under the gate region can cause tunneling/leakage of electrons from the gate metal to the semiconductor. Thus, the tunneling/gate leakage effect becomes critical for radio frequency (RF) applications because the electric field oscillates with the total terminal (dc+RF) voltage [8]. During the high voltage portion of the RF cycle, a pulse of electrons will tunnel from the gate by acquiring sufficient energy and can cause gate breakdown [9,10]. The electron transport

Crystals **2023**, 13, 231 2 of 12

on the surface is sluggish due to high effective mass, and dispersion is introduced due to the charging/discharging time constant [11]. The electrons escaping from the gate metal gather on the surface, creating a "virtual gate" effect that functions as an effective increase in gate length on the drain side can result in leakage current [7]. As a result, the conducting channel depletes of free electrons, and the device dc current and RF power decreases [7]. To overcome this problem, a dielectric material, often an oxide layer, is introduced between the metal gate and the semiconductor, creating metal-oxide-semiconductor-HFET (MOSHET) for high-frequency applications. Thus, the gate tunneling is reduced or eliminated with improved surface charge modulation by an insulating oxide layer under the gate [7,12].

The incorporation of the oxide layer improves the GaN-based HFET performance by minimizing the gate leakage current, maximizing the output power (as the input can be driven harder), improving the breakdown voltage, etc [13]. The interface between the semiconductor and oxide layer, however, plays an important role in transistor performance [14]. Chemically and thermally stable oxides with low density of interface states between the insulator (oxide) and semiconductor are required [15]. Several groups have reported the use of different dielectrics, such as aluminum oxide (Al $_2$ O $_3$ ) [16], hafnium dioxide (HfO $_2$ ) [17], zirconium dioxide (ZrO $_2$ ) [18], silicon dioxide (SiO $_2$ ) [19], silicon nitride (Si $_3$ N $_4$ ), and hexagonal boron nitride (h-BN) [20], fabricated by several deposition methods, including atomic layer deposition (ALD) [14], pulsed laser deposition (PLD) [21], and plasma enhanced chemical vapor deposition (PECVD) [21]. SiO $_2$ /hBN has also been reported to be used as a substrate material for field effect transistors [22].

$Ga_2O_3$  is a promising material with potential dielectric applications for high-power devices because of its wide bandgap (4.4–5.3 eV) and high breakdown voltage (8 MVcm<sup>-1</sup>) [23,24]. It has a moderate dielectric constant (k = 10.6), which is higher than those of traditional dielectrics such as  $SiO_2$  (k = 3.9), and  $Si_3N_4$  (k = 7.4) [16]. This dielectric-constant value allows gate scaling and a smaller voltage for the same charge. The feasibility of using  $Ga_2O_3$  as a gate dielectric was demonstrated by employing ALD with compounds such as trimethylgallium, and triethylgallium as a Ga precursor and ozone or oxygen ( $O_2$ ) plasma as an oxygen precursor [23,25,26]. The  $Ga_2O_3$  layers grown by ALD for MOSHFETs are amorphous and prone to change their properties, especially threshold voltage, with annealing due to crystallization [27]. The use of crystalline metal–organic chemical vapor deposition (MOCVD) grown β- $Ga_2O_3$  as a gate dielectric has so far not been reported. A comprehensive study of the electrical properties is necessary to determine the feasibility of MOCVD  $Ga_2O_3$  as a gate dielectric.

In this work, we study the electrical properties of  $Al_{0.3}Ga_{0.7}N/GaN$  HFET with MOCVD-grown  $\beta$ - $Ga_2O_3$  as a passivation/dielectric layer.  $\beta$ - $Ga_2O_3$  layers of three different thicknesses of 10 nm, 20 nm, and 30 nm were grown on top of  $Al_{0.3}Ga_{0.7}N/GaN$  creating MOSHFET structures. Furthermore, the variations in electrical properties, particularly the shift in threshold voltage, are studied for annealed and as-deposited MOSHFET structures with MOCVD-grown  $\beta$ - $Ga_2O_3$ .

## 2. Experimental Methods

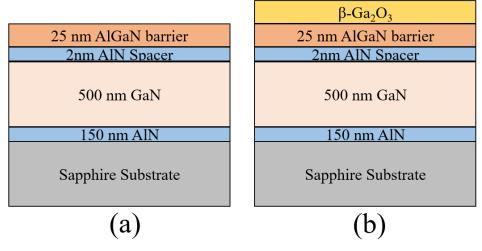

The epilayers used for devices studied in this paper were deposited in a vertical cold wall metal–organic chemical vapor deposition (MOCVD) system using nitrogen ( $N_2$ ) as a carrier gas on a 2-inch diameter c-axis sapphire substrate with  $0.2^\circ$  offcut. Trimethylaluminum (TMAl), triethylgallium (TEG), ammonia (NH<sub>3</sub>), and ultra-high purity oxygen were used as aluminum (Al), gallium (Ga),  $N_2$ , and oxygen ( $O_2$ ) precursors, respectively. First, a thin 150 nm aluminum nitride (AlN) buffer layer was grown on the sapphire substrate using the process described in [28,29]. Then, on top of the AlN layer, a 500 nm thick gallium nitride (GaN) channel layer with a V/III ratio of 8000 at a temperature of 960 °C, a 2 nm AlN spacer, and a 25 nm thick barrier aluminum gallium nitride ( $Al_{0.3}Ga_{0.7}N$ ) layers with V/III ratio of 5000 at a temperature of 1020 °C were grown at 100 Torr chamber pressure, creating heterojunction field effect transistor (HFET) structure [30–32]. The van der Pauw and Hall effect measurements show that the GaN layers used for our device structures

Crystals 2023, 13, 231 3 of 12

were highly resistive. Figure 1 shows the schematic of the FET epilayer structures used in this paper where, Figure 1a exhibits the schematic of the HFET structure. For this study, the  $\beta\text{-}Ga_2O_3$  layers were grown on top of the HFET structure using the MOCVD process at 700 °C, 50 Torr chamber pressure, and a VI/III ratio of ~900. The details of the  $Ga_2O_3$  growth can be found elsewhere [33]. This creates a MOSHFET structure with the dielectric layer thickness varying from 10 nm to 30 nm, as shown in Figure 1b. The MOSHFET structure with 30 nm oxide thickness was annealed to gauge its electrical and thermal stability. Annealing was performed at 900 °C for 30 min in a 50/50  $O_2/N_2$  (nitrogen was used as carrier gas) environment to avoid desorption from the  $Ga_2O_3$  layer.

Figure 1. The epilayer structure of the (a)  $Al_{0.3}Ga_{0.7}N/GaN$  HFET, (b)  $Ga_2O_3$  MOSHFET.

We characterized the structural quality and electrical properties of all the device structures obtained in this work. A Rigaku Miniflex II Desktop X-ray diffractometer with Cu-K $\alpha$ 1 x-ray source ( $\lambda$  = 1.5406 Å) operated at 30 mA current and 15 kV voltage was used to evaluate the structural properties of the epilayers. The capacitance–voltage (C-V) measurements were performed using a mercury probe controller model 802B connected with a HP 4284A Precision LCR Meter capable of measuring the impedance as a function of frequency. Gate leakage current was measured in the same mercury probe set up with Keysight B2910 Precision Source/Measure Units (SMU). The gate diameter of the mercury probe was 797  $\mu$ m with 0.1 pF stray capacitance. The van der Pauw/Hall effect measurements were performed on the samples using the MMR Technologies Inc. H-50 controller and MPS-50 programmable power supply with indium contacts.

#### 3. Results and Discussions

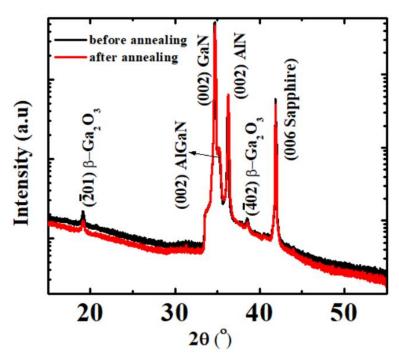

Figure 2 shows the X-ray diffraction (XRD)  $2\theta$  scan of the MOSHFET structure (before and after annealing). The peaks at  $18.8^{\circ}$  and  $38.2^{\circ}$  are related to the ( $\overline{2}01$ ) and ( $\overline{4}02$ )  $Ga_2O_3$  of the  $\beta$  phase [34]. The peak at  $34.5^{\circ}$  and the adjacent higher angle shoulder are consistent with the (002) and (002) reflection from the GaN channel and AlGaN barrier layers, respectively [35]. Note that the GaN channel layer was grown on  $0.15~\mu m$  AlN. The peak at  $36.1^{\circ}$  is due to the (002) AlN reflection. The peaks at  $20.4^{\circ}$  and  $41.6^{\circ}$  correspond to the (003) and (006) sapphire reflections [34]. The most common method of oxide dielectric deposition is ALD, which is mostly used for depositing amorphous materials [36]. The problem with amorphous layers is that, during the rapid thermal annealing (RTA) step required to form ohmic contacts to MOSHFETs, there occurs a phase transformation from amorphous to crystalline structure [27]. This transformation results in the formation of a microcrystalline structure with multiple grain boundaries, which creates leakage paths, rendering it unsuitable for device applications [27]. The process used for the MOCVD oxide deposition favors the growth of single-crystal  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> dielectric layers, as confirmed by the XRD data. Therefore, it is expected that, as Ga<sub>2</sub>O<sub>3</sub> is already in the crystalline

Crystals **2023**, 13, 231 4 of 12

form, the thermal treatment will have a minimal impact on its electrical properties, as we demonstrate by the annealing experiments in the later description.

Figure 2. XRD  $2\theta$  scan of the MOSHFET structure (before and after annealing) confirming the presence of the peaks consistent with crystalline  $Ga_2O_3$  ( $\beta$  phase), GaN, AlGaN, AlN, and sapphire substrate.

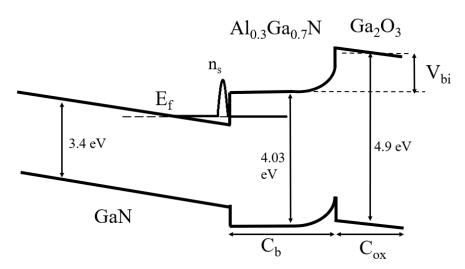

The origin of the highly conductive quantum confined two-dimensional electron gas (2DEG) at the AlGaN/GaN interface is due to the lack of inversion symmetry along the [0001] axis of GaN coupled with AlN being relatively more electronegative [2]. The difference between spontaneous and piezoelectric polarization and band offset at the interface introduces a fixed polarization-induced sheet of carrier charges, indicated by the shift of Fermi level in the conduction band. Schrödinger and Poisson's equation-based charge distribution and band diagram can be calculated using different available tools [37]. However, a simpler approach using the Langer and Heinrich rule helps to estimate different parameters and understand the band structure at the heterojunction interfaces [38,39]. Figure 3 shows the schematical band diagram for the Ga<sub>2</sub>O<sub>3</sub> MOSHFET. The bandgaps for GaN, Al<sub>0.3</sub>Ga<sub>0.7</sub>N, and Ga<sub>2</sub>O<sub>3</sub> are 3.4 eV, 4.03 eV (using Vegard's law), and 4.9 eV ( $\beta$  phase), respectively [40]. The position of the Fermi level in GaN near the channel-barrier interface is in the conduction band; where n<sub>s</sub> is the sheet carrier density, C<sub>b</sub> is the Al<sub>0.3</sub>Ga<sub>0.7</sub>N barrier layer capacitance, C<sub>ox</sub> is the Ga<sub>2</sub>O<sub>3</sub> layer capacitance. We can express the total gate capacitance (C<sub>G</sub>) using the series capacitance formula as below:

$$\frac{1}{C_G} = \frac{1}{C_b} + \frac{1}{C_{ox}} \tag{1}$$

Crystals **2023**, 13, 231 5 of 12

**Figure 3.** The representative band diagram of GaN/AlGaN MOSHFET with Ga<sub>2</sub>O<sub>3</sub> as a gate dielectric.

The capacitance–voltage (C-V) measurements of the MOSHFET structure were performed using a mercury probe gate contact to extract pertinent electrical parameters of the device structures, such as threshold voltage ( $V_{th}$ ), zero gate voltage capacitance, and 2DEG electron density. The total gate capacitance is given by Equation (1), i.e., the addition of the oxide dielectric layer capacitance in series with the barrier layer capacitance. The benefit of an oxide dielectric is to increase the gate breakdown voltage and/or reduce the gate leakage current by suppressing the surface states, sometimes superseded by the impact of different device electrical parameters such as threshold voltage and gate leakage current. The threshold voltage of the MOSHFET structure is given by the Equation [41]:

$$V_{th,MOSHFET} = V_{th,HFET} \left( 1 + \frac{d_i \varepsilon_{s,b}}{\varepsilon_i d_{s,b}} \right)$$

(2)

where  $V_{th,MOSHFET}$  and  $V_{th,HFET}$  are the threshold voltage of the MOSHFET and HFET (that without the oxide layer- otherwise identical), respectively.  $d_i$ ,  $d_{s,b}$ ,  $\varepsilon_i$  and  $\varepsilon_{s,b}$  are the thicknesses and dielectric constants of the insulator/oxide (indexed by i) and semiconductor barrier (indexed by s,b) layers, respectively. From equation (2), it is clear that if  $d_i$  increases,  $V_{th,MOSHFET}$  increases, whereas  $V_{th,MOSHFET}$  decreases with the increase in  $\varepsilon_i$ . Thus, a higher dielectric constant and lower dielectric thickness are desirable for minimum threshold voltage shifts.

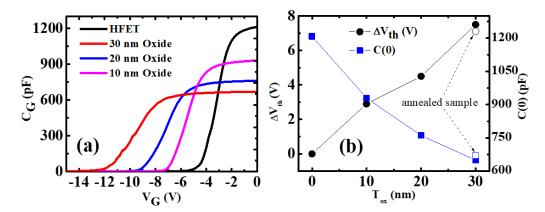

Figure 4 shows the capacitance voltage characteteristics, threshold voltage and zero capacitance dispersion of our samples. Figure 4a shows the C-V data for HFET and MOSH-FET structures with oxide thicknesses of 10 nm, 20 nm, and 30 nm. The addition of oxide on the HFET barrier adds capacitance in series with the existing barrier layer capacitance, which would lower the overall gate capacitance. The relative dielectric constants for the AlGaN barrier layer (9.2) and that for the  $Ga_2O_3$  (10.6) are very close [42], and the AlGaN barrier layers is undoped. Due to these reasons, we did not observe any change in the C-V curve shape near the zero-gate voltage position when increasing the negative gate voltage before depleting the channel. From equation (2), we observe that as the thickness of the oxide layer increases, the  $V_{th}$  should increase. The C-V measurements on the MOSHFET structure with MOCVD-grown Ga<sub>2</sub>O<sub>3</sub> gate dielectric confirm the increase in the V<sub>th</sub> value. As the thickness of the  $Ga_2O_3$  layer increased, the  $V_{th}$  exhibited a negative shift. Thus, with the increase in dielectric layer thickness, a higher voltage is required to deplete the 2DEG. During the C-V measurement, when 2DEG starts to deplete, the capacitance decreases drastically, ultimately leading to pinching off of the channel. By further increasing the gate voltage beyond pinch-off, the depletion layer extends to the GaN channel. Figure 4b summarizes the above discussion.

Crystals **2023**, 13, 231 6 of 12

**Figure 4.** C-V characteristics at 1MHz frequency of (a) HFET and  $Ga_2O_3$ -based MOSHFETs with different oxide thicknesses, (b) Threshold voltage and zero gate-voltage capacitance dispersion for HFET and  $Ga_2O_3$  MOSHFETs.

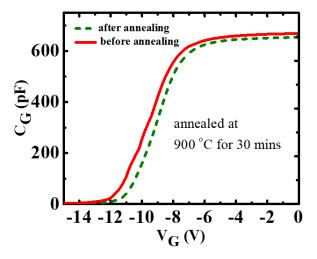

Figure 5 compares the C-V data for annealed and as-deposited MOSHFETs with a 30 nm thick  $\beta\text{-}Ga_2O_3$  as a gate oxide layer. The 30-min annealing at 900 °C was performed in the MOCVD reactor, used for the  $Ga_2O_3$  growth, as described in the experimental method section. As shown in Figure 2, the pre and post-annealed XRD was similar. As can be concluded from the C-V data, the annealing experiment did not result in any discernable change in the  $V_{th}$  and zero capacitance values, demonstrating the excellent thermal stability of the crystalline  $\beta\text{-}Ga_2O_3$ . The change in threshold voltage (open circle) and capacitance (open square) for the annealed MOSHFET structure are also shown in Figure 4b.

**Figure 5.** *C-V* data of at 1MHz frequency Ga<sub>2</sub>O<sub>3</sub>-based MOSHFET with 30 nm oxide thickness annealed (dashed line) and unannealed (continuous line).

The carrier density  $N_d$  was calculated using the Hall effect data and found to be on the order of  $10^{18}$  cm<sup>-3</sup>, the exact values of the carrier density can be found in Table 1. The built-in voltage  $V_{bi}$  (as shown in the band diagram: Figure 2) can be measured from  $1/C^2$  intercept with the x-axis and expressed by equation (3) [43]:

$$V_{bi} = \frac{qN_d x_d^2}{2\epsilon_s} + \frac{qN_d x_d}{\epsilon_{ox}} t_{ox} + \frac{Q_{ox}}{\epsilon_{ox}} t_{ox}$$

(3)

Crystals **2023**, 13, 231 7 of 12

|          | V <sub>th</sub> (V) | μ<br>(cm <sup>2</sup> V <sup>-</sup> s <sup>-1</sup> )<br>(Hall) | R <sub>sh</sub><br>(Ωcm <sup>-</sup><br>(Hall) | N <sub>d</sub> <sup>2</sup> ) (cm <sup>-3</sup> ) (Hall) | n <sub>s</sub><br>(cm <sup>-2</sup> )<br>(C-V) | n <sub>s</sub><br>(cm <sup>-2</sup> )<br>(Hall) | Q <sub>ox</sub><br>(Ccm <sup>-2</sup> )<br>(C-V) | D <sub>it</sub><br>(cm <sup>-2</sup> eV <sup>-1</sup> )<br>(C-V) | Leakage<br>Current at<br>-20 V<br>(A/cm <sup>-2</sup> ) |

|----------|---------------------|------------------------------------------------------------------|------------------------------------------------|----------------------------------------------------------|------------------------------------------------|-------------------------------------------------|--------------------------------------------------|------------------------------------------------------------------|---------------------------------------------------------|

| HFET     | <b>-</b> 5          | 750                                                              | 537                                            | $6.8 \times 10^{18}$                                     | $1.25 \times 10^{13}$                          | $1.55 \times 10^{13}$                           | None                                             | None                                                             | $1.66 \times 10^{-4}$                                   |

| 10 nm    | -7.9                | 772                                                              | 630                                            | $5.0 \times 10^{18}$                                     | $1.28 \times 10^{13}$                          | $1.4 \times 10^{13}$                            | $-6.68 \times 10^{12}$                           | $7.47 \times 10^{12}$                                            | $1.3 \times 10^{-6}$                                    |

| 20 nm    | -9.5                | 770                                                              | 650                                            | $4.2 \times 10^{18}$                                     | $1.24\times10^{13}$                            | $1.42 \times 10^{13}$                           | $-1.64 \times 10^{13}$                           | $7.57 \times 10^{12}$                                            | $1.12 \times 10^{-6}$                                   |

| 30 nm    | -12.5               | 776                                                              | 685                                            | $4.4\times10^{18}$                                       | $1.4\times10^{13}$                             | $1.4 \times 10^{13}$                            | $-2 \times 10^{13}$                              | $4.98 \times 10^{12}$                                            | $9.54 \times 10^{-7}$                                   |

| annealed | d –12.1             | 760                                                              | 680                                            | $4.5 \times 10^{18}$                                     | $1.4 \times 10^{13}$                           | $1.4 \times 10^{13}$                            | $-3.06 \times 10^{12}$                           | $3 \times 10^{12}$                                               | $8.33 \times 10^{-7}$                                   |

**Table 1.** The summary of the key electrical parameters measured/calculated from C-V and Hall measurements.

Here,  $t_{ox}$  and  $\epsilon_{ox}$  are the thickness and permittivity of the oxide layer,  $N_d$  is the carrier concentration,  $x_d$  and  $\epsilon_s$  are the depletion width and permittivity of the AlGaN barrier layer. If we set  $t_{ox}=0$ , then the 2nd and 3rd term of Equation (3) becomes zero, and the equation represents the built-in voltage for conventional HFET structure. Using Equation (1) and the parallel plate capacitance formula for each series capacitor component, we can calculate the value of  $x_d$  at zero gate voltage. Inserting the determined value of  $x_d$ , and previously calculated/measured  $N_d$ ,  $t_{ox}$ , and known  $\epsilon_{ox}$ ,  $\epsilon_s$  into Equation (3), we can obtain the oxide charge  $Q_{ox}$ . The calculated values of  $Q_{ox}$  for all the samples is shown in Table 1. We observe a trend in the value of  $Q_{ox}$ ; as the oxide thickness increases, the value of  $Q_{ox}$ , become more negative which increases  $V_{th}$  shift supporting Equation (2). There may be impact of stress on the charge, but we did not isolate that in our calculation. Due to low thickness, we did not observe any signature peak of the dielectric  $Ga_2O_3$  or barrier AlGaN layer in Raman measurement (Figure S2 in Supplementary Section).

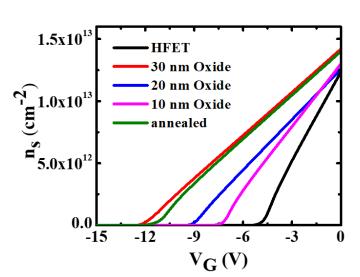

Figure 6 shows the 2DEG carrier density ( $n_s$ ) versus the gate voltage ( $V_G$ ) for 10, 20, and 30 nm gate oxide thicknesses calculated using the following equation:

$$qn_s = (V_G - V_{th})C_G \tag{4}$$

Figure 6. 2DEG carrier density in FETs vs. applied gate voltage for different gate oxide thicknesses.

In all three cases, the zero-gate voltage value of sheet carrier density is very close in the range of (1.25–1.5)  $\times$   $10^{13}$  cm $^{-2}$ , a slightly higher value of  $n_s$  could be due to sample-to-sample variations. The sheet carrier concentrations measured using van der Pauw/Hall effect method are also in the range of (1–1.5)  $\times$   $10^{13}$  cm $^{-2}$ , which validates our calculations using the value from the C-V measurement by employing equation (4). The sheet carrier

Crystals 2023, 13, 231 8 of 12

concentration does not change with oxide layer thickness or annealing of the oxide layer. In previous studies for the ALD-grown amorphous oxide dielectrics-based MOSHFETs, it has been demonstrated that the annealing of the oxide layers drastically shifts  $V_{th}$ . As we can see in Figure 5, annealing of the crystalline  $Ga_2O_3$  based MOSHFET, there is no noticeable change in the threshold voltage in contrast to the case for previously reported ALD-grown oxides [44]. To further validate the MOCVD oxide material property we can use Equation (1), to calculate the experimental dielectric constant for  $\beta$ -Ga $_2O_3$ . The values of the gate capacitance,  $C_G$ , before and after annealing are  $1.64 \times 10^{-7}$  F/cm $^{-2}$  and  $1.67 \times 10^{-7}$  F/cm $^{-2}$  (for 1 MHz frequency measurement).  $C_b$  is the barrier capacitance of the MOSHFET, and the value is  $3.3 \times 10^{-7}$  F/cm $^{-2}$ . Based on  $C_{ox} = \frac{\epsilon_r \epsilon_0}{t_{ox}}$ , we get  $\epsilon_r = 10.9$  (using  $C_G = 1.67 \times 10^{-7}$  F/cm $^{-2}$ ), whereas the reference value is 10.6. Thus, it can be inferred that the MOCVD-grown oxide has a dielectric property that is very close to the previously reported literature value [42].

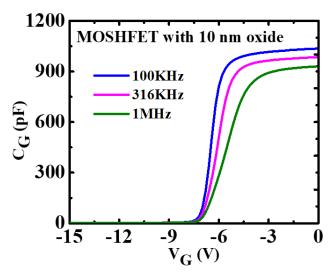

The interface trapped charge or interface traps stem(s) from dangling bonds at the semiconductor–insulator interface. The frequency-dependent High–Low method is commonly used to determine interface charge density ( $D_{it}$ ). Figure 7 shows the frequency-dependent CV measurement used to calculate the interface charge densities for MOSHFET with 10 nm oxide thickness (the frequency-dependent C-V measurements of MOSHFET with 20 nm, 30 nm oxide thickness along with the annealed sample are shown in the Supplementary Section Figure S1).

**Figure 7.** Frequency-dependent C-V characteristic of a MOSHFET with 10 nm thick gate oxide at frequencies of 100 kHz, 316 kHz, and 1 MHz.

The High–Low frequency CV method compares a low-frequency C-V curve with one that is free of interface traps. The latter is usually referred to as a high-frequency C-V measurement, where interface traps with relatively long-time constants cannot respond, leading to decreased measured capacitance. At low frequencies, the interface traps can respond, if not deep, thus resulting in higher capacitance; 100 kHz and 1 MHz frequencies are the typical values can be used for CV-based calculations of the density of interface states ( $D_{it}$ ) of Nitride systems [45]. Consequently, from the difference between high- and low-frequency CV measurements, the  $D_{it}$  can be obtained based on Equation (5) at a specific applied gate voltage [46]:

$$D_{it}(V_G) = \frac{C_{ox}}{q} \left( \frac{C_{LF}}{C_{ox} - C_{LF}} - \frac{C_{HF}}{C_{ox} - C_{HF}} \right)$$

(5)

where  $C_{ox}$  is the capacitance of the oxide dielectric layer calculated using the parallel plate capacitor formula, q is the unit elementary charge,  $C_{LF}$  is the MOSHFET low-frequency

Crystals **2023**, 13, 231 9 of 12

capacitance value and  $C_{HF}$  is the MOSHFET high-frequency capacitance value. The total trap densities for all the samples are tabulated in Table 1. For all samples, the calculated interface trap densities are in the range (3–7.57)  $\times$  10<sup>12</sup> cm<sup>-2</sup>eV<sup>-1</sup>; these values are close to the typically calculated values of MOSHFETs (typical values are in the order of  $\sim$ 10<sup>11</sup> cm<sup>-2</sup>eV<sup>-1</sup>–10<sup>13</sup> cm<sup>-2</sup>eV<sup>-1</sup>) [27]. The  $D_{it}$  value is expected to be lower for the processed devices due to the mesa isolation [47]. Our data revealed no specific correlation between the oxide thickness and interface trap densities. Ideally, this is the case, but the total number of bulk defects in the oxide under the gate would depend on the thickness, more data are needed to find any correlation. It is observed that the annealed sample showed a slightly smaller trap density, which can correlate to the higher  $n_s$ , the origin of which is not yet explored.

To further investigate the  $\beta\text{-}Ga_2O_3$  viability as a gate dielectric leakage current measurements were performed for all the samples. Figure 8 shows the gate leakage current in the HFET and different thicknesses  $\beta\text{-}Ga_2O_3$  MOSHFET structure. There is a significant reduction in leakage current for the MOSHFET structure compared to the HFET structure in the off-stage. The leakage current at -20 V for HFET is  $\sim\!10^{-4}$  A/cm², and it reduces to  $\sim\!10^{-6}$  A/cm² for MOSHFET. This remarkable improvement in the gate leakage current shows that  $\beta\text{-}Ga_2O_3$  can be used as an effective dielectric layer for GaN/AlGaN MOSHFETs. Table 1 summarizes the key electrical parameters of the GaN/AlGaN-based HFET and GaN/AlGaN/ $\beta\text{-}Ga_2O_3$ -based MOSHFET determined in this work.

**Figure 8.** Gate leakage current characteristics for HFET and for different gate oxide thicknesses MOSHFET.

# 4. Conclusions

We have demonstrated MOCVD-grown single-crystal  $Ga_2O_3$  thin films as a gate dielectric on AlGaN/GaN HFETs. We have found that an increase in the thickness of the dielectric layer has an impact on threshold voltage  $V_{th}$ , shifting it to more negative values and reducing the zero capacitance as additional  $C_{ox}$  is added in series. The sheet carrier densities for HFET and MOSHFETs were determined to be ~ $10^{13}$  cm $^{-2}$ , well within the typical range- of  $10^{12}$  cm $^{-2}$ – $10^{13}$  cm $^{-2}$  for AlGaN/GaN-based devices. The leakage current was reduced by approximately 2 order from ~ $10^{-4}$  A/cm $^2$  for HFET to ~ $10^{-6}$  A/cm $^2$  for MOSHFET at -20 V. Moreover, the addition of the oxide layer did not change the sheet carrier concentration but had an impact on the calculated value of oxide charge  $Q_{ox}$ . The calculated  $Q_{ox}$  value was found to be negative and mainly responsible for depleting the 2DEG. As the thickness of the  $Ga_2O_3$  layer increases, the  $Q_{ox}$  becomes more negative, following a trend similar to the change in  $V_{th}$  with increasing gate oxide thickness. The

Crystals **2023**, 13, 231 10 of 12

charge density in the oxide–AlGaN barrier interface was found to be of the order of  $\sim 10^{12}~\rm cm^2 eV^{-1}$ . The thermal stability, as confirmed by the annealing experiment, suggests that the MOCVD-grown single-crystal Ga<sub>2</sub>O<sub>3</sub> layer could be more suitable for the gate dielectric application compared to the ALD-grown oxide due to threshold voltage stability. The moderate interface trap density and good thermal stability indicate that MOCVD-grown  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> is an excellent candidate for gate dielectric as well as a passivation layer for III-Nitride-based high-power RF MOSHFET devices.

**Supplementary Materials:** The following supporting information can be downloaded at: https://www.mdpi.com/article/10.3390/cryst13020231/s1. Figure S1. Frequency-dependent CV measurements of MOSHFET with (a) 20 nm thick gate oxide (b) 30 nm thick gate oxide, and (c) annealed 30 nm thick gate oxide. Figure S2. (a) Raman spectra of HFET and MOSHFET (30 nm oxide), (b) Raman spectra of Ga<sub>2</sub>O<sub>3</sub> on sapphire to identify the Ga<sub>2</sub>O<sub>3</sub> signature peak positions.

**Author Contributions:** S.H. Conceptualization of this study, Experimentation, Data curation, Methodology, Writing—original draft, M.U.J.: Revision, Experimentation, S.R.C.: Revision, Experimentation, Editing, D.L.: Revision, Experimentation, Editing, V.A.: Revision, Editing, Ü.Ö.: Revision, Editing, H.M.: Revision, Editing, I.A.: Conceptualization of this study, Visualization, Editing, Revision, Principal Investigator of this study. All authors have read and agreed to the published version of the manuscript.

Funding: This research was funded by National Science Foundation (NSF), grant number 2124624.

**Data Availability Statement:** The data generated during and/or analyzed during the current study are available from the corresponding authors on reasonable request.

**Acknowledgments:** This research was supported by National Science Foundation (NSF) award No. 2124624 managed by Dominique M. Dagenais.

Conflicts of Interest: The authors declare that they have no conflict of interest.

## References

- 1. Morkoç, H. Handbook of Nitride Semiconductors and Devices, Materials Properties, Physics and Growth; Wiley-VCH: Weinhem, Germany, 2009; ISBN 9783527408375.

- 2. Mohammad, S.N.; Salvador, A.A.; Morkoc, H. Emerging gallium nitride-based devices. *Proc. IEEE.* 1995, 83, 1306–1355. [CrossRef]

- 3. Morkoc, H. *Nitride Semiconductors and Devices*; Springer: Berlin/Heidelberg, Germany; New York, NY, USA, 1999; ISBN 3-540-64038.

- 4. Zeng, F.; An, J.X.; Zhou, G.; Li, W.; Wang, H.; Duan, T.; Jiang, L.; Yu, H. A Comprehensive Review of Recent Progress on GaN High Electron Mobility Transistors: Devices, Fabrication and Reliability. *Electronics* **2018**, *7*, 377. [CrossRef]

- 5. Islam, N.; Mohamed, M.F.P.; Khan, M.F.A.J.; Falina, S.; Kawarada, H.; Syamsul, M. Reliability, Applications and Challenges of GaN HEMT Technology for Modern Power Devices: A Review. *Crystals* **2022**, *12*, 1581. [CrossRef]

- 6. Kim, H.; Lee, J.; Liu, D.; Lu, W. Gate Current Leakage and Breakdown Mechanism in Unpassivated AlGaNGaN High Electron Mobility Transistors by Post-Gate Annealing. *Appl. Phys. Lett.* **2005**, *86*, 143505. [CrossRef]

- Leach, J.H.; Morkoç, H. Status of Reliability of GaN-Based Heterojunction Field Effect Transistors. Proc. IEEE 2010, 98, 1127–1139.

[CrossRef]

- 8. Rao, G.P.; Singh, R.; Lenka, T.R. Performance Analysis of AlGaN/GaN HEMT for RF and Microwave Nanoelectronics Applications. In *HEMT Technology and Applications*; Springer Nature: Singapore, 2023; pp. 139–153. [CrossRef]

- 9. Trew, R.J. Wide bandgap semiconductor transistors for microwave power amplifiers. IEEE Microw. Mag. 2000, 1, 46–54. [CrossRef]

- 10. Brar, B.; Boutros, K.; DeWarnes, R.E.; Tilak, V.; Shealy, R.; Eastman, L. Impact ionization in high performance AlGaN/GaN HEMTs. In Proceedings of the IEEE Lester Eastman Conference on High Performance Devices, Newark, DE, USA, 8 August 2002; pp. 487–491.

- 11. Trew, R.J.; Green, D.S.; Shealy, J.B. AlGaN/GaN HFET reliability. IEEE Microw. Mag. 2009, 10, 116-127. [CrossRef]

- 12. Zhou, H.; Lou, X.; Sutherlin, K.; Summers, J.; Kim, S.B.; Chabak, K.D.; Gordon, R.G.; Ye, P.D. DC and RF Performance of AlGaN/GaN/SiC MOSHEMTs with Deep Sub-Micron T-Gates and Atomic Layer Epitaxy MgCaO as Gate Dielectric. *IEEE Electron Device Lett.* **2017**, *38*, 1409–1412. [CrossRef]

- 13. Liu, C.; Chor, E.F.; Tan, L.S. Investigations of HfO<sub>2</sub>/AlGaN/GaN metal-oxide-semiconductor high electron mobility transistors. *Appl. Phys. Lett.* **2006**, *88*, 173504. [CrossRef]

- 14. Asubar, J.T.; Yatabe, Z.; Gregusova, D.; Hashizume, T. Controlling surface/interface states in GaN-based transistors: Surface model, insulated gate, and surface passivation. *J. Appl. Physics.* **2021**, *129*, 121102. [CrossRef]

- 15. Ramanan, N.; Lee, B.; Misra, V. Accurate characterization and understanding of interface trap density trends between atomic layer deposited dielectrics and AlGaN/GaN with bonding constraint theory. *Appl. Phys. Lett.* **2015**, *106*, 243503. [CrossRef]

Crystals **2023**, 13, 231 11 of 12

16. Gusev, E.P.; Copel, M.; Cartier, E.; Baumvol, I.J.; Krug, C.; Gribelyuk, M.A. High-resolution depth profiling in ultrathin Al<sub>2</sub>O<sub>3</sub> films on Si. *Appl. Phys. Letters.* **2000**, *76*, 176–178. [CrossRef]

- 17. Lee, B.H.; Kang, L.; Nieh, R.; Qi, W.J.; Lee, J.C. Thermal stability and electrical characteristics of ultrathin hafnium oxide gate dielectric reoxidized with rapid thermal annealing. *Appl. Phys. Letters.* **2000**, *76*, 1926–1928. [CrossRef]

- 18. Copel, M.; Gribelyuk, M.; Gusev, E. Structure and stability of ultrathin zirconium oxide layers on Si (001). *Appl. Phys. Letters.* **2000**, *76*, 436–438. [CrossRef]

- 19. Husna, F.; Lachab, M.; Sultana, M.; Adivarahan, V.; Fareed, Q.; Khan, A. High-Temperature Performance of AlGaN/GaN MOSHEMT with SiO<sub>2</sub> Gate Insulator Fabricated on Si (111) Substrate. *IEEE Trans. Electron Devices* **2012**, *59*, 2424–2429. [CrossRef]

- 20. Illarionov, Y.Y.; Rzepa, G.; Waltl, M.; Knobloch, T.; Grill, A.; Marco, M.; Furchi, M.M.; Mueller, T.; Grasser, T. The role of charge trapping in MoS<sub>2</sub>/SiO<sub>2</sub> and MoS<sub>2</sub>/hBN field-effect transistors. *2d Mater.* **2016**, *3*, 035004. [CrossRef]

- 21. Balakrishnan, G.; Babu, R.V.; Shin, K.S.; Song, J.I. Growth of highly oriented  $\gamma$ -and  $\alpha$ -Al<sub>2</sub>O<sub>3</sub> thin films by pulsed laser deposition. *Opt. Laser Technol.* **2014**, *56*, 317–321. [CrossRef]

- 22. Khan, M.F.; Rehman, S.; Akhtar, I.; Aftab, S.; Ajmal, H.M.S.; Khan, W.; Kim, D.-k.; Eom, J. High mobility ReSe<sub>2</sub> field effect transistors: Schottky-barrier-height-dependent photoresponsivity and broadband light detection with Co decoration. 2d Mater. 2019, 7, 015010. [CrossRef]

- 23. Passlack, M.; Schubert, E.F.; Hobson, W.S.; Hong, M.; Moriya, N.; Chu, S.N.; Konstadinidis, K.; Mannaerts, J.P.; Schnoes, M.L.; Zydzik, G.J. Ga<sub>2</sub>O<sub>3</sub> films for electronic and optoelectronic applications. *J. Appl. Phys.* **1995**, 77, 686–693. [CrossRef]

- 24. Green, A.J.; Speck, J.; Xing, G.; Moens, P.; Allerstam, F.; Gumaelius, K.; Neyer, T.; Arias-Purdue, A.; Mehrotra, V.; Kuramata, A.; et al. β-Gallium Oxide Power Electronics. *APL Mater* **2022**, *10*, 029201. [CrossRef]

- 25. Choi, D.W.; Chung, K.B.; Park, J.S. Low temperature Ga<sub>2</sub>O<sub>3</sub> atomic layer deposition using gallium tri-isopropoxide and water. *Thin Solid Films* **2013**, 546, 31–34. [CrossRef]

- 26. Donmez, I.; Ozgit-Akgun, C.; Biyikli, N. Low temperature deposition of Ga<sub>2</sub>O<sub>3</sub> thin films using trimethylgallium and oxygen plasma. *J. Vac. Sci. Technol. A Vac. Surf. Films* **2013**, *31*, 01A110. [CrossRef]

- 27. Hashizume, T.; Nishiguchi, K.; Kaneki, S.; Kuzmik, J.; Yatabe, Z. State of the Art on Gate Insulation and Surface Passivation for GaN-Based Power HEMTs. *Mater. Sci. Semicond. Process.* **2018**, *78*, 85–95. [CrossRef]

- 28. Hasan, S.; Mamun, A.; Hussain, K.; Gaevski, M.; Ahmad, I.; Khan, A. Growth Evolution of High-Quality MOCVD Aluminum Nitride Using Nitrogen as Carrier Gas on the Sapphire Substrate. *J. Mater. Res.* **2021**, *36*, 4360–4369. [CrossRef]

- 29. Hasan, S.; Mamun, A.; Hussain, K.; Patel, D.; Gaevski, M.; Ahmad, I.; Khan, A. Investigation of MOCVD Grown Crack-Free 4 Mm Thick Aluminum Nitride Using Nitrogen as a Carrier Gas. MRS Adv. 2021, 6, 456–460. [CrossRef]

- 30. Shrestha, N.; Shrestha, N.M.; Wang, Y.Y.; Li, Y.; Chang, E.Y. Effect of AlN Spacer Layer on AlGaN/GaN HEMTs. In Proceedings of the 16th International Workshop on Computational Electronics, Nara, Japan, 4–7 June 2013; ISBN 978-3-901578-26-7.

- 31. Hubáček, T.; Hospodková, A.; Kuldová, K.; Zíková, M.S.; Pangrác, J.; Čížek, J.; Liedke, M.O.; Butterilng, M.; Wagner, A.; Hubík, P.; et al. Improvement of Luminescence Properties of N-GaN Using TEGa Precursor. *J. Cryst. Growth* **2020**, *531*, 125383. [CrossRef]

- 32. Roy, P.; Jawanpuria, S.; Vismita; Prasad, S.; Islam, A. Characterization of AlGaN and GaN Based HEMT with AlN Interfacial Spacer. In Proceedings of the IEEE 2015 5th International Conference on Communication Systems and Network Technologies, CSNT, Gwalior, India, 4–6 April 2015; pp. 786–788.

- 33. Jewel, M.U.; Hasan, S.; Crittenden, S.; Avrutin, V.; Özgür, Ü.; Morkoç, H.; Ahmad, I. Growth of Thick Phase-Pure β-Ga2O3 on a c-Plane Sapphire Substrate Using MOCVD. *SPIE Conf. Proceeding*, 2023; *submitted*.

- 34. Ghose, S.; Rahman, S.; Hong, L.; Rojas-Ramirez, J.S.; Jin, H.; Park, K.; Klie, R.; Droopad, R. Growth and Characterization of β-Ga<sub>2</sub>O<sub>3</sub> Thin Films by Molecular Beam Epitaxy for Deep-UV Photodetectors. *J. Appl. Phys.* **2017**, *122*, 095302. [CrossRef]

- 35. Moram, M.A.; Vickers, M.E. X-ray diffraction of III-nitrides. Rep. Prog. Phys. 2009, 72, 036502. [CrossRef]

- 36. George, S.M. Atomic Layer Deposition: An Overview. Chem. Rev. 2010, 110, 111–131. [CrossRef]

- 37. Grundmann, M. BandEng. 2005. Available online: http://my.ece.ucsb.edu/mgrundmann/ (accessed on 6 January 2023).

- 38. Langer, J.M.; Heinrich, H. Deep-level impurities: A possible guide to prediction of band-edge discontinuities in semiconductor heterojunctions. *Phys. Rev. Letters.* **1985**, *55*, 1414. [CrossRef]

- 39. Jena, D. Polarization Induced Electron Populations in III–V Nitride Semiconductors Transport, Growth, and Device Applications. Ph.D. Thesis, University of California Santa Barbara, Santa Barbara, CA, USA, 2003.

- 40. Langer, J.M.; Delerue, C.; Lannoo, M.; Heinrich, H. Transition-metal impurities in semiconductors and heterojunction band lineups. *Phys. Rev. B* **1988**, *38*, 7723. [CrossRef] [PubMed]

- 41. Rai, S.; Adivarahan, V.; Tipirneni, N.; Koudymov, A.; Yang, J.; Simin, G.; Khan, M.A. Low threshold-14 W/mm ZrO<sub>2</sub>/AlGaN/GaN metal-oxide-semiconductor heterostructure field effect transistors. *Jpn. J. Appl. Phys.* **2006**, 45, 4985. [CrossRef]

- 42. Shih, H.Y.; Chu, F.C.; Das, A.; Lee, C.Y.; Chen, M.J.; Lin, R.M. Atomic Layer Deposition of Gallium Oxide Films as Gate Dielectrics in AlGaN/GaN Metal–Oxide–Semiconductor High-Electron-Mobility Transistors. *Nanoscale Res. Lett.* **2016**, *11*, 235. [CrossRef]

- 43. Sze, S.; Li, Y.; Ng, K. Physics of Semiconductor Devices; John and Wiley and Sons: Hoboken, NJ, USA, 2021.

- 44. Mollah, S.; Hussain, K.; Mamun, A.; Alam, M.D.; Chandrashekhar, M.V.; Simin, G.; Khan, A. Threshold voltage control with high-temperature gate-oxide annealing in ultrawide bandgap AlGaN-channel MOSHFETs. *Appl. Phys. Express* **2022**, *15*, 104001. [CrossRef]

Crystals **2023**, 13, 231

45. Osvald, J. Interface traps contribution to capacitance of Al2O3/(GaN) AlGaN/GaN heterostructures at low frequencies. *Phys. E Low-Dimens. Syst. Nanostructures* **2017**, *93*, 238–242. [CrossRef]

- 46. Schroder, D.K. Frontmatter. In Semiconductor Material and Device Characterization; John and Wiley and Sons: Hoboken, NJ, USA, 2005.

- 47. Remesh, N.; Kumar, S.; Guiney, I.; Humphreys, C.J.; Raghavan, S.; Muralidharan, R.; Nath, D.N. A Novel Technique to Investigate the Role of Traps in the Off-State Performance of AlGaN/GaN High Electron Mobility Transistor on Si Using Substrate Bias. *Phys. Status Solidi* **2020**, 217, 1900794. [CrossRef]

**Disclaimer/Publisher's Note:** The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content.