# Imperfection-enabled memristive switching in van der Waals materials

Received: 29 July 2022

Accepted: 25 May 2023

Published online: 17 July 2023

Check for updates

Mengjiao Li<sup>1,2,4</sup>, Hefei Liu<sup>1,4</sup>, Ruoyu Zhao<sup>1,4</sup>, Feng-Shou Yang<sup>2</sup>, Mingrui Chen<sup>1</sup>, Ye Zhuo<sup>1</sup>, Chongwu Zhou<sup>1</sup>✉, Han Wang<sup>1</sup>✉, Yen-Fu Lin<sup>1,2,3</sup>✉ & J. Joshua Yang<sup>1</sup>✉

Memristive devices can offer dynamic behaviour, analogue programmability, and scaling and integration capabilities. As a result, they are of potential use in the development of information processing and storage devices for both conventional and unconventional computing paradigms. Their memristive switching processes originate mainly from the modulation of the number and position of structural defects or compositional impurities—what are commonly referred to as imperfections. While the underlying mechanisms and potential applications of memristors based on traditional bulk materials have been extensively studied, memristors based on van der Waals materials have only been considered more recently. Here we examine imperfection-enabled memristive switching in van der Waals materials. We explore how imperfections— together with the inherent physicochemical properties of the van der Waals materials—create different switching mechanisms, and thus provide a range of opportunities to engineer switching behaviour in memristive devices. We also discuss the challenges involved in terms of material selection, mechanism investigation and switching uniformity control, and consider the potential of van der Waals memristors in system-level implementations of efficient computing technologies.

Internet of Things and artificial intelligence technologies, which rely on large data streams and data-centric computing, require efficient data processing and storage components. Memristive devices can offer non-volatile storage capabilities, multiple storage states and compatibility with silicon technology, and have the potential to overcome the limitation of conventional von Neumann computing architectures and act as building blocks for the next generation of computing technologies<sup>1–3</sup>. Typically, the devices are based on electrical-bias-induced switching between a high-resistance state (HRS) and a low-resistance state (LRS)—known as a SET and RESET process<sup>4</sup>. The resistive switching originates from the generation, annihilation and/or rearrangement of material imperfections at the atomic scale. The presence of even a tiny

number of imperfections can substantially change the electronic/ionic interactions, ion distribution or migration kinetics, giving rise to rich switching characteristics in memristive materials.

Comprehensive investigations of traditional oxide materials (including titanium-, tantalum-, hafnium- and silicon-based devices) have revealed several types of memristive switching mechanism and demonstrated a variety of potential applications<sup>5–7</sup>. For higher integration density and energy efficiency, researchers keep shrinking the minimal dimensions of memristors. However, this scaling creates challenges in terms of achieving reliable resistive switching. At thicknesses below 3 nm, local non-uniformity and random defects severely impact the switching invariability<sup>8</sup>. For instance, because the device resistance

<sup>1</sup>Electrical and Computer Engineering Department, University of Southern California, Los Angeles, CA, USA. <sup>2</sup>Department of Physics, National Chung Hsing University, Taichung, Taiwan. <sup>3</sup>Department of Material Science and Engineering, Institutes of Nanoscience, i-Center for Advanced Science and Technology (i-CAST), National Chung Hsing University, Taichung, Taiwan. <sup>4</sup>These authors contributed equally: Mengjiao Li, Hefei Liu, Ruoyu Zhao.

✉e-mail: [chongwu@usc.edu](mailto:chongwu@usc.edu); [wang679@usc.edu](mailto:wang679@usc.edu); [yenfulin@nchu.edu.tw](mailto:yenfulin@nchu.edu.tw); [jjoshuay@usc.edu](mailto:jjoshuay@usc.edu)

depends strongly on the dielectric thickness, even a tiny fluctuation results in a substantial device-to-device variation, which becomes a severe problem for most applications, which involve millions to billions of such devices. Moreover, it has been shown theoretically and experimentally that a thinner dielectric layer lowers the forming threshold of conductive pathways (also called conduction channels or filaments), leading to multiple conduction channels and working currents elevated to hundreds of microamperes or milliamperes, which would reduce energy efficiency<sup>9,10</sup>. The possibility of channel overgrowth will be further aggravated if the thickness decreases to a nanoscale or subnanoscale, as the effect of defects will be amplified and the enlarged switching region seriously threatens the switching reliability<sup>11</sup>. Thus, innovation of switching media is necessary to further improve memristive performance.

As an alternative, layer-structured van der Waals (vdW) materials with a lower electron density of states enable low-current resistive switching below nanoampere levels<sup>12-15</sup>. A high-quality vdW crystal offers atomic-level local uniformity in both morphology and dimension. Such a uniform switching medium is expected to reduce variations between different devices and switching cycles. Their all-surface geometry makes vdW systems an excellent platform for introducing and characterizing various defects. Defects and ionic activities can be effectively controlled in atomically thin vdW layers via electric, magnetic, thermal or optical fields<sup>16,17</sup>, and novel properties emerge in polymorphic phase structures of transition metal chalcogenides (TMCs)<sup>18</sup>. These unique features of vdW materials provide a greater freedom for creating precisely engineered memristive devices.

Recent work on vdW memristive devices has shown the importance of understanding the interplay between the intrinsic physico-chemical properties of the materials and the imperfections in the system. For example, a single vacancy defect in a vdW monolayer represents the smallest switching dimension in terms of thickness and area<sup>19</sup>. The electrostatic gating effect enables vacancies to multidirectionally migrate in planar devices to tune the Schottky barrier heights and conductivity<sup>16,20</sup>. The migration process can be driven by existing grain boundaries that provide faster paths for ion motion<sup>15,21</sup>. The layered structure and layer-number-dependent structural symmetry of TMCs render metal-ion intercalation accessible and manipulable, and can be used to control phase distribution and regulate local resistance<sup>22</sup>. Compared with traditional oxide materials, some oxidized vdW materials can retain their pristine crystal structures and are more robust against high temperature<sup>23,24</sup>. Recent work has already highlighted how various imperfections contribute to the switching processes in vdW memristors. However, a more comprehensive understanding of the imperfection-enabled switching mechanisms and characteristics is fundamental to realizing the full potential of vdW memristive devices.

In this Review, we examine work on vdW memristors that provides insight into how different imperfections in vdW systems enable memristive behaviours. We consider three imperfection-enabled memristive mechanisms and characteristics, which can be used for applications in data storage, neuromorphic computing and radiofrequency devices. We also discuss the key challenges that need to be addressed to develop high-performance memristive devices and propose more precise imperfection engineering strategies for developing high-density and energy-efficient computing systems.

## Imperfections in vdW memristive materials

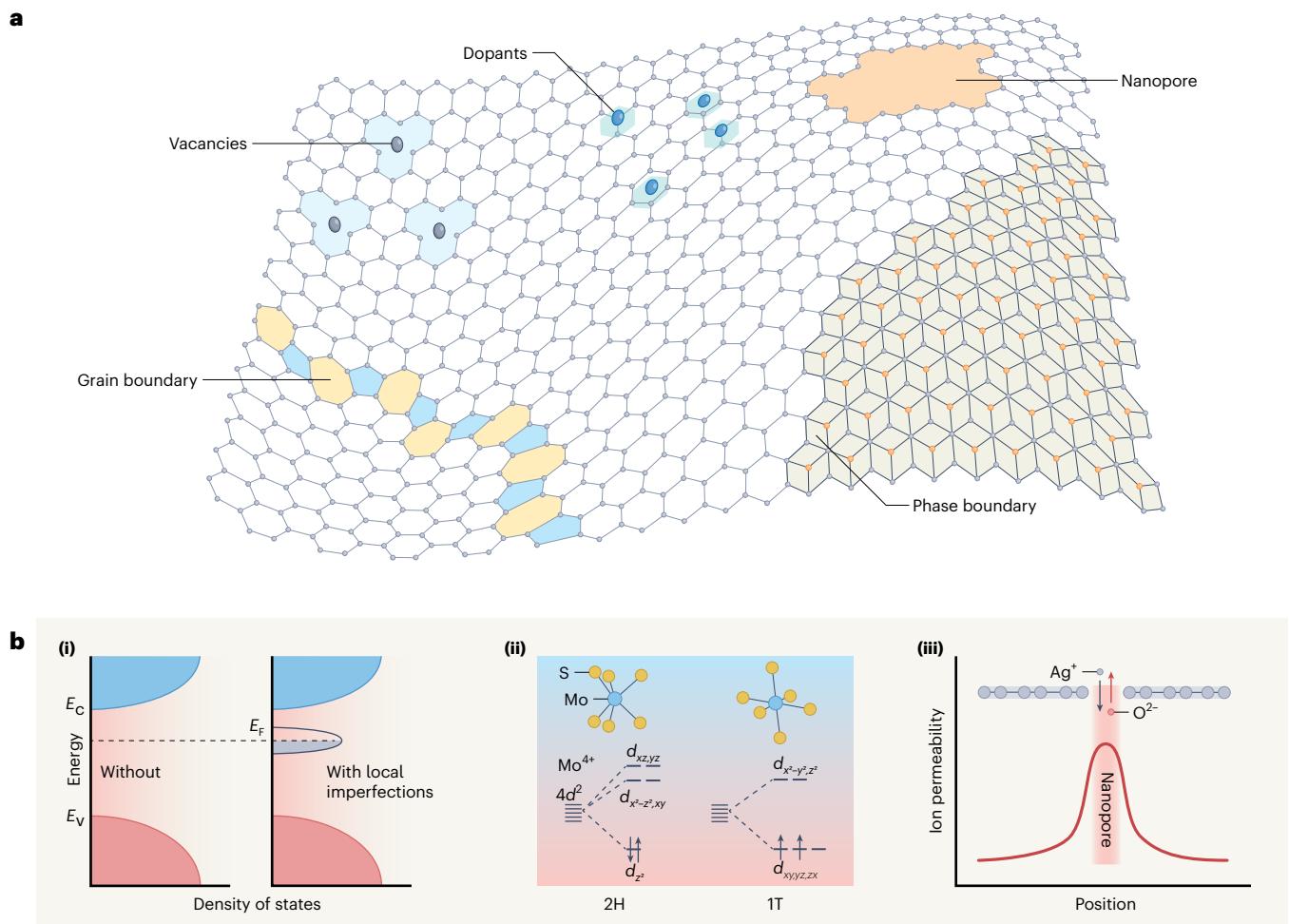

'Imperfections' in this review refers to various defects, disorders or impurities in vdW materials, which are traditionally viewed as undesirable factors but play critical roles in memristive devices (Fig. 1a). As summarized in Supplementary Table 1, imperfections can be generated during crystal preparation or post-treatment. The defect type, density, size and distribution are primarily determined by the specific preparation technique (for example, chemical vapour transportation,

chemical vapour deposition (CVD), mechanical or liquid exfoliation, and hydrothermal methods) and conditions (for example, temperature gradient, precursor concentration, substrate orientation, vapour flow rate, and exfoliating force)<sup>25</sup>. Vacancies are the most common defects in vdW materials, including single, double and multiple vacancies, depending on the number of atoms missing from the lattice sites<sup>26</sup>. Vacancy defects can serve as active sites in favour of the occupation and removal of metal atoms to change the resistance. In addition, they can migrate driven by electric field and induce structural or valence alteration to the host layer<sup>21</sup>. Grain boundaries, a group of dislocation cores stitching two grains, arise from the coalescence of neighbouring crystal domains<sup>27,28</sup>. A diversity of morphologies can be formed depending on the misorientation angles<sup>29</sup>. Grain boundaries can accommodate numerous mobile particles and introduce notable fluctuations in electronic states<sup>29,30</sup>, as shown in Fig. 1b(i). For example, a metallic wire-like grain boundary in graphene induces a local doping effect on the Fermi level. Edge atoms in grain boundaries bond weakly to the interior ones and can be easily mobilized. These properties make grain boundaries an active factor in regulating the electrical transport of vdW materials.

Imperfections such as structural-distortion-induced phase boundaries and oxidization-induced dopants can be intentionally created by post-treatment<sup>31-33</sup>. The entropy difference between different phases of two-dimensional (2D) vdW systems is smaller than that of three-dimensional (3D) bulk systems, leading to a lower phase transformation barrier<sup>34</sup>. This makes polymorphic phase transition in vdW materials more accessible to enable resistive switching. For example, lithium intercalation can produce new phases by modifying the electronic states and inducing structural distortion (Fig. 1b(ii))<sup>35,36</sup>. 'Dopants' refers to the exotic atoms incorporated into the crystal lattice that modify the charge carrier type and density of the host materials, and can modulate the switching dynamics by either directly participating in the resistive switching or introducing other types of defect, such as vacancies. As a typical doping approach, the oxidization of vdW materials induced by surface plasma or thermal annealing can effectively enhance their memristive properties, as mobile oxygen anions can play a more active role in the resistive switching process<sup>12,37</sup>. Recent studies reported that resistive-switching-inactive TMCs that feature a low defect density—for example,  $\text{ReS}_2$ —can be doped by Mo irradiation using molecular beam epitaxy, during which lattice disorders and sulfur vacancies can be introduced<sup>38</sup>. Moreover, other mild doping strategies such as CVD-based alloying doping, surface charge transfer doping or chemical treatment doping may also be applicable to vdW materials<sup>39,40</sup>.

Cracks and wrinkles are also imperfections in vdW materials. They are usually created over the course of device fabrication and regarded as undesirable factors for device yield in large-scale fabrication. For vdW memristors built in the pristine region, cracks and wrinkles outside the switching area have little impact on the switching behaviour because the working currents in these devices are driven locally and usually out of plane<sup>41</sup>. On the other hand, wrinkles within the switching area potentially offer a platform to investigate the strain effect on memristive dynamics. Furthermore, if we intentionally introduce some missing parts in vdW materials, for example, creating nanopores by ion bombardment or cracking gaps by strain engineering, then we can control the spatial distribution of ion permeability to better manipulate the conductive channel<sup>42,43</sup>.

## Imperfection-enabled memristive mechanisms

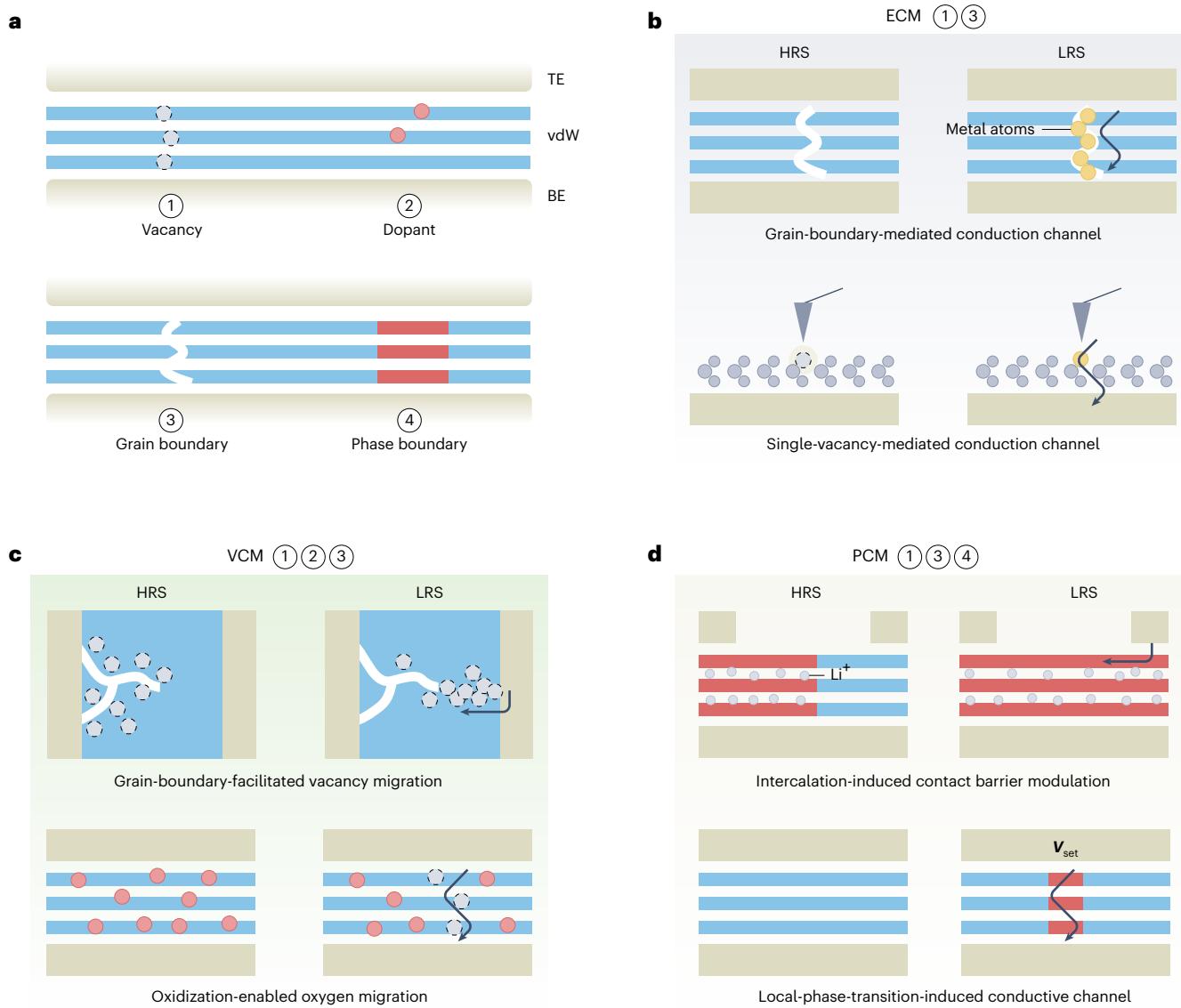

Recently reported vdW memristive devices can be categorized into three groups according to the microscopic switching physics: electrochemical metallization (ECM), valence-change mechanism (VCM) and phase-change mechanism (PCM). The three switching mechanisms rely on either the manipulation of conduction channels or the modulation of contact barrier heights and each of them involves a set of imperfections, as summarized in Fig. 2. This section will introduce the dominant

**Fig. 1 | Various imperfections in vdW materials.** **a**, Structural schematics of various imperfections generated during material preparation or post-treatment processes, including vacancies, dopants, grain boundaries, phase boundaries and nanopores in vdW materials. **b**, Typical imperfection-enabled properties of vdW memristive materials. (i) The introduction of finite electronic states near the Fermi level by material imperfections, such as metal atoms occupying chalcogen vacancies and grain boundaries, leading to local metallic behaviour<sup>19,26,30</sup>. (ii) The electronic states of Mo 4d orbitals of 2H and 1T MoS<sub>2</sub>. The 2H semiconductive phase in the trigonal-prismatic unit originates from the three-group splitting of Mo 4d orbitals and completely occupied  $4d_{z^2}$ . The 1T metallic phase in the octahedral unit results from the two-group splitting and partially occupied  $4d_{xy, yz, zx}$ . (iii) The ion permeability of a defective vdW film<sup>94</sup>. The pristine part without nanopores shows a low ion permeability but the region with nanopores has a high ion permeability.

electronic states of Mo 4d orbitals of 2H and 1T MoS<sub>2</sub>. The 2H semiconductive phase in the trigonal-prismatic unit originates from the three-group splitting of Mo 4d orbitals and completely occupied  $4d_{z^2}$ . The 1T metallic phase in the octahedral unit results from the two-group splitting and partially occupied  $4d_{xy, yz, zx}$ . (iii) The ion permeability of a defective vdW film<sup>94</sup>. The pristine part without nanopores shows a low ion permeability but the region with nanopores has a high ion permeability.

or assistant role of imperfections and analyse the microscopic picture of a specific switching process.

### Electrochemical metallization

ECM-based memristors are basically electrochemical cells with electrochemically active metal electrodes. Their switching process features the formation and rupture of metallic conductive channels that bridge two electrodes, which determines the resistive states of the device stack. Metal atoms from the active electrode need to overcome a series of energy barriers during ionization, migration and reduction to realize resistive switching. Vacancies and grain boundaries in switching media serve as active host sites for metal atoms to form metallic conductive bridges<sup>12,44,45</sup>.

Most ECM switching processes are contributed by both vacancies and grain boundaries (except in single crystals)<sup>12,13,19,44–51</sup>. In switching media, vacancies serve as active host centres for metal atoms to form metallic conductive bridges<sup>12,44,45</sup>. Grain boundaries are fast paths for metal ion migration and provide preferred forming locations for conduction channels<sup>13,52,53</sup>. Moreover, grain boundaries also have a low activation energy for the generation and transport of vacancy defects<sup>21</sup>. These factors work synergistically to promote the modulation

of conductive channels in the ECM switching process. Generally, the larger the grain size, the lower the operation current, as there are fewer grain boundaries to help form conductive channels<sup>52</sup>. So far, memristive switching facilitated by grain boundaries has been demonstrated in few-layer vdW materials (for example, TMCs and hexagonal boron nitride (h-BN)) sandwiched by active electrodes (for example, Ag, Ti, Cu)<sup>12,13,52,53</sup>. The channel formation at grain boundaries can be confirmed by microscopic morphology and elemental distribution variation (Fig. 2b).

When the thickness of the switching medium decreases to a monolayer, even filling a single metal atom in or removing it from a vacancy can markedly change the resistance of vdW materials. This type of memristive device is called an atomristor (Fig. 2b), and shows great potential for overcoming the thickness bottleneck of bulk-oxide memristors<sup>44,46</sup>. ECM switching atomristors were first demonstrated in a vertical metal/monolayer MoS<sub>2</sub>/metal device and then in a broad group of monolayer vdW materials (for example, disulfide, diselenide and h-BN)<sup>44,47</sup>.

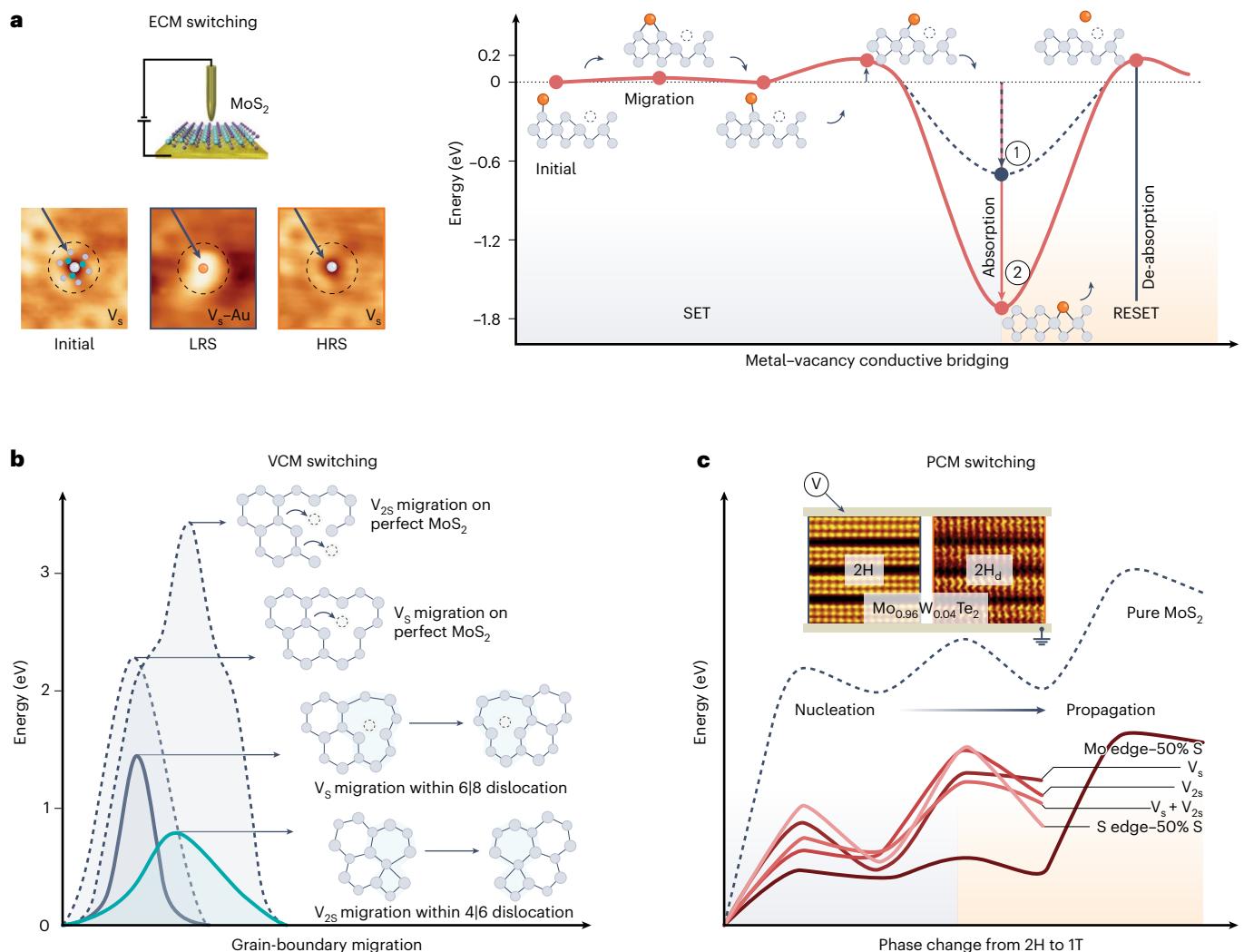

The role of native vacancies in ECM switching of a MoS<sub>2</sub> single-defect atomristor is visualized via *in situ* scanning tunnelling microscopy<sup>19</sup>. As shown in Fig. 3a, a gold probe and a MoS<sub>2</sub> monolayer

**Fig. 2 | Imperfection-enabled switching mechanisms in vdW memristors.**

**a.** A schematic of a typical vertical vdW memristor with various imperfections. The numbers indicate different types of imperfection. In the case of lateral devices, the metal electrodes should be arranged at the left and right ends of the switching medium. TE and BE represent the top and bottom electrodes, respectively. **b–d.** Illustrations of the HRS and LRS of three resistive switching mechanisms. Each of them is contributed by a specific set of imperfections. The numbers indicate the related imperfection types. **b.** In ECM switching, vacancies and grain boundaries facilitate the formation of the conduction channel. The yellow circles represent

metal atoms from the electrodes. **c.** In VCM switching, the intrinsic vacancies (for example, chalcogen vacancies) or introduced vacancies (for example, oxygen vacancies) dominate the switching process by forming conductive channels or modulating the contact barrier height. The presence of grain boundaries favours vacancy migration. **d.** In PCM switching, chemical intercalation or external electric field can induce reversible phase transition between two crystalline phases with different conducting properties<sup>22,72</sup>. The involved phases include 1T metallic phases, 2H semiconducting phases and their distorted structures (for example,  $T_d$ ,  $T'$  and  $2H_d$  phases).

on top of a gold thin film form a  $\text{Au}/\text{MoS}_2/\text{Au}$  memristor. A gold atom occupying a single-sulfur vacancy serves as the conductive bridge. The ECM switching process involves dissociation of the gold ion/atom, moving on the surface of a defect-free region, occupying a vacancy site (SET) and departing from the vacancy site (RESET). However, there are two possible pathways for the switching process depending on whether a redox process of the gold atom occurs. In the first pathway, the gold atom undergoes ionization and reduction at the two electrodes, akin to the case of conventional oxide-based electrochemical memristors. The second pathway does not involve the redox process. An individual gold atom can detach itself from the electrode since gold has a relatively low atomization enthalpy<sup>47</sup>. The free gold atom is rather unstable. It would diffuse along the defect-free region and be captured by a vacancy site since the gold atom absorption is

energetically more favourable at a vacancy site (route 1) than in the defect-free region (route 2). The rupture of the metal bridge needs to overcome the departing barrier energy to reset the sulfur vacancy, which defines the threshold voltage of the RESET operation. As a result, devices with different electrode materials and vacancy types possess different switching thresholds and characteristics<sup>54</sup>. For instance, a low binding energy between metal atoms/ions and vacancies results in a low switching voltage (for example,  $\text{Ag}/\text{MoTe}_2$ ); a high binding energy typically leads to a high switching stability (for example,  $\text{Ag}/\text{h-BN}$ ). Moreover, the absorption process and the kinetic profile are closely related to defect density and distribution<sup>21</sup>. Beyond the single-defect case in monolayer media, the physical processes of ECM switching in multilayer media are more complicated, especially if grain boundaries or dopants are involved.

**Fig. 3 | Imperfection-related kinetics of the resistive switching processes.** **a**, Right: typical energy paths and corresponding structural schematics of metal atom diffusion in ECM switching<sup>19,47</sup>. The absorption process of the metal atom at a sulfur vacancy site releases energy and increases local conductance, corresponding to the SET operation. The desorption process consumes energy and results in a conductance decrease, corresponding to the RESET operation. Left: the *in situ* scanning tunnelling microscopy images, revealing the evolution of a defective MoS<sub>2</sub> monolayer during the switching process—an unoccupied sulfur vacancy (Initial), a vacancy filled by a Au atom (LRS) and a reset vacancy (HRS). **b**, The energy paths and corresponding structural schematics for vacancy migration in VCM switching<sup>21,59</sup>. The migration of a V<sub>s</sub> or a V<sub>2S</sub> faces a lower energy barrier on a MoS<sub>2</sub> surface with dislocations (6|8 and 4|6 dislocations) than on a pristine region, revealing the role of grain boundaries in promoting

vacancy migration. **c**, The calculated energy paths of phase transition in PCM switching<sup>72,74</sup>. It involves the 1T phase nucleation and propagation on a base of 2H MoS<sub>2</sub> with different statuses: perfect region, V<sub>s</sub>, V<sub>2S</sub>, two separated V<sub>s</sub> (V<sub>s</sub> + V<sub>s</sub>), sulfur edge with 50% sulfur coverage (S edge-50% S) and molybdenum edge with 50% sulfur coverage (Mo edge-50% S). Compared with the perfect region, defective areas have lower energy barriers for phase transition. Inset: high-magnification annular dark-field scanning transmission electron microscopy images of the 2H phase and the distorted transient 2H<sub>d</sub> phase of a MoTe<sub>2</sub>-based (Mo<sub>0.96</sub>W<sub>0.04</sub>Te<sub>2</sub>) memristor driven by electric field. The x axis in **a**–**c** represents the reaction coordinate of the corresponding switching processes. Panels adapted with permission from: **a**, ref. 19, Springer Nature Limited; **b**, the curve for V<sub>s</sub> migration within 6|8 dislocation, ref. 21, Springer Nature Limited; **b**, other curves, ref. 59, John Wiley and Sons; **c**, ref. 72, Springer Nature Limited.

### Valence-change mechanism

The migration and redistribution of the anions (or equivalently charged vacancies), typically driven by electric field and/or thermal effect, can lead to conductance change in vdW media sandwiched by inert electrodes. This type of switching mechanism, VCM, is mainly based on the modulation of either filamentary conductive channels or contact barrier heights. The commonly involved imperfections in VCM are vacancies and grain boundaries<sup>15,16,20,24,37,43,55–57</sup>. Mobile vacancies either naturally exist in vdW materials—for example, chalcogen vacancies in TMCs—or can be introduced via extra treatments—for example, oxygen vacancies in oxidized TMCs (Fig. 2c).

The characteristics of VCM switching are primarily determined by ion-migration energy barriers<sup>58</sup>. In TMCs, the intrinsic chalcogen

species, such as sulfur, selenium or tellurium anions, possess lower migration barriers than transition metal cations. Therefore, they are more mobile and dominant in VCM switching<sup>16,24</sup>. Grain boundaries can further reduce the migration barrier of vacancies and facilitate VCM switching. This phenomenon was experimentally confirmed in monolayer TMCs. Researchers revealed that the reconstruction of grain boundaries in a MoS<sub>2</sub> monolayer promotes the migration of neighbouring point defects<sup>21,59</sup>. Compared with the defect-free region, the migration energy barrier is lowered by about 40% for a single-sulfur vacancy (V<sub>s</sub>) within the 6|8 dislocation core and reduced by 80% for a double-sulfur vacancy (V<sub>2S</sub>) within a 4|6 dislocation core (Fig. 3b).

Grain-boundary-mediated VCM switching was first demonstrated in a lateral monolayer MoS<sub>2</sub> memristor<sup>16</sup>. Atomic force microscopy and

electrostatic force microscopy captured the reversible migration of grain boundaries in the switching process. The external electric field drives the lateral motion of sulfur vacancies to modify the Schottky barrier heights at the metal–semiconductor interfaces and switch the device between high- (vacancy depletion) and low- (vacancy accumulation) resistance states (Fig. 2c). Subsequent studies revealed that diverse grain-boundary topologies enhance the degree of freedom in shaping the switching polarity, volatility, linearity and additional gate tunability<sup>20</sup>. Although a couple of desirable characteristics are gained in grain-boundary-mediated memristors, two major engineering issues need to be addressed. First, the strong dependence of switching features on grain-boundary topologies gives rise to severe device-to-device variation. Second, the grain size, typically ranging from micrometres to tens of nanometres, limits the density of grain boundaries and the minimal size of the device, imposing a ceiling on their scalability. Both issues might be partially resolved by improving the synthesis homogeneity of vdW films or intentionally creating grain boundaries via electron-beam or laser irradiation<sup>15</sup>.

Compared with intrinsic chalcogen and metal ions, oxygen ions possess an even lower migration barrier and a higher mobility<sup>12,24,60</sup>. Thus, the oxidized vdW materials have been studied as the switching media for realizing an ultrathin switching layer, lower energy consumption and reduced switching variation (Supplementary Fig. 1 and Supplementary Table 2)<sup>12,24,37,55,61,62</sup>. Oxygen element can be introduced into vdW materials by several gentle oxidization processes, such as thermal oxidization, oxygen plasma and ultraviolet ozone treatment<sup>63,64</sup>. For air-sensitive materials, natural oxidization under ambient conditions is adequate<sup>65,66</sup>. The substitutional oxygen ions can be redistributed by electric field, thermal gradient or chemical potential difference, leading to two types of VCM switching dominated by interface contact barriers and nanoconductive channels, respectively. The switching type is related to the specific oxidization method and oxidative topologies. In a mild low-temperature thermal oxidization, the thickness of the oxide layer is generally limited to less than 3 nm. The relevant switching characteristics are mainly determined by the metal/oxide interface because the thin oxide layer (the reservoir of oxygen ions) enables oxygen vacancy ( $V_O^{2+}$ ) migration and metal valence change<sup>37,61</sup>. A region abundant in oxygen ions possesses a higher metal valence, leading to a higher interface contact barrier and lower conductance, and vice versa. In contrast to the interface effect, if oxidization occurs in a moist environment, many oxygen ions can deeply penetrate the vdW host and substitute the chalcogen ions of TMCs<sup>24</sup>. This creates more in-depth oxygen vacancies and allows them to form conductive bridges between the top and bottom electrodes. The motion of  $V_O^{2+}$  during the SET and RESET processes was visualized in a thermally oxidized  $MoS_{2-x}O_x$  memristor, primarily involving thermophoresis and thermal dissolution (Fig. 2c)<sup>24</sup>. Additionally, using graphene to replace metal electrodes can provide a thermally and chemically stable interface to protect the conductive channel and avoid ion penetration into metal electrodes, which can reduce device failure caused by channel overgrowth<sup>11,12</sup>.

### Phase-change mechanism

TMCs have various crystalline phases with distinct electrical conduction properties<sup>67</sup>. A typical example of PCM switching is based on the reversible phase transition between metallic 1T, semiconductive 2H or their distorted structures of TMCs to modulate interface contact barriers or local conduction channels. Unlike the conventional phase-change memory devices that undergo a phase transition between amorphous and crystalline states, the phases involved in vdW-based PCM switching are all crystalline states with slight differences in atom dispositions<sup>68</sup>. Thus, the switching between the semiconductive and metallic phases of TMCs involves a lower energy barrier. The low phase transition barrier promises low-energy-consumption memristors; on the other hand, it may compromise the retention of memory states.

The phases of TMCs feature different electron arrangements in the  $d$  orbital of the transition metal atoms, and a slight variation of charge density can change their relative stability. The structural change of TMCs could be achieved by the electrostatic gating effect or interface charge injection<sup>69</sup>. Among the most investigated TMCs ( $MX_2$ ,  $M = Mo$ ,  $W$ ;  $X = S$ ,  $Se$ ,  $Te$ ), tellurides (for example,  $MoTe_2$ ) are expected to possess the lowest polymorphic energy difference<sup>67</sup>. For example, a moderate electric voltage (usually below 1 V) can switch the resistance of a  $MoTe_2$  memristor by forming a  $2H_d$  conduction channel in the  $2H$  semiconductive region (Fig. 2d). The conduction channel in TMCs can be vertically formed in a tiny region, indicating the scalability potential of PCM devices; however, it also implies switching variation if the randomness of the nanofilament formation cannot be well controlled. Compared with conventional phase-change materials such as  $Ge_2Sb_2Te_5$ , the phase transition between crystalline phases also endows TMCs with a fast switching speed (5 ns)<sup>70,71</sup>. Further studies uncovered that alloying engineering can be used to tune the PCM switching process. Taking  $Mo_{1-x}W_xTe_2$  memristors as an example, the incorporation of  $W$  can facilitate the SET process since the  $2H$  to  $1T'$  transition of  $WTe_2$  is more thermodynamically favourable at room temperature than is that of  $MoTe_2$ <sup>67,72</sup>.

Chemical intercalation is commonly used to achieve PCM switching owing to the layered feature of TMCs<sup>73</sup>. It results in the phase transition through transferring charges from the intercalants to the transition metal atoms and changing the electronic structure of the TMC. Thus, the motion of intercalated ions driven by electric field leads to the motion of phase boundaries in TMCs. Controlling lateral ion motion through chemical intercalation can modulate the charge transport barrier at the contact interface of  $MoS_2$  and metal electrodes. A forward voltage drives  $Li^+$  to move toward the right-hand metal electrode in Fig. 2d, leading to motion of the  $1T/2H$  phase boundary in the same direction, thereby realizing an ohmic contact; a reverse voltage removes the  $Li^+$  from this electrode region, resulting in opposite motion of the phase boundary and an elevated Schottky contact barrier. The intralayer migration barrier determines the mobility of the alkali metal ions for either drift or spontaneous diffusion. Thus, there is a trade-off between the required operating voltage and the retention of PCM devices. In addition, similarly to the planar vacancy migration, by controlling the migration direction of intercalants, researchers realized multidirectional resistance modulation in PCM devices. This property can be used to implement the multiple interactions between artificial synapses<sup>22</sup>.

The switching process of PCM is also influenced by vacancies, grain boundaries or dopants in the switching region<sup>74</sup>. These defects can affect the nucleation and propagation of phase transition. For example, sulfur vacancies favour the resistive switching from HRS to LRS because the presence of one sulfur vacancy can reduce the energy barrier of the nucleation step from  $2H$  to  $1T$  phase transition by 60% when compared with a defect-free region (Fig. 3c)<sup>74</sup>. Introduced dopants, such as Re or Tc atoms in  $MoS_2$  flakes, provide extra charges for filling incomplete orbitals and stabilizing the metastable phases, which benefits the stability of the PCM switching<sup>18</sup>.

It is worth noting that some of the above-mentioned material imperfections can serve as charge traps by providing localized states. These localized states may impact the carrier transport in the dielectric materials and hence the electrical properties of devices. Some studies claim that charge trapping/detrapping events can lead to resistive switching in vdW devices<sup>75</sup>. However, other possible switching mechanisms, such as ECM or VCM, cannot be excluded. The exact impact of the charge trapping/detrapping event on the memristive switching process is still controversial and requires more solid evidence.

### Electronic applications of vdW memristors

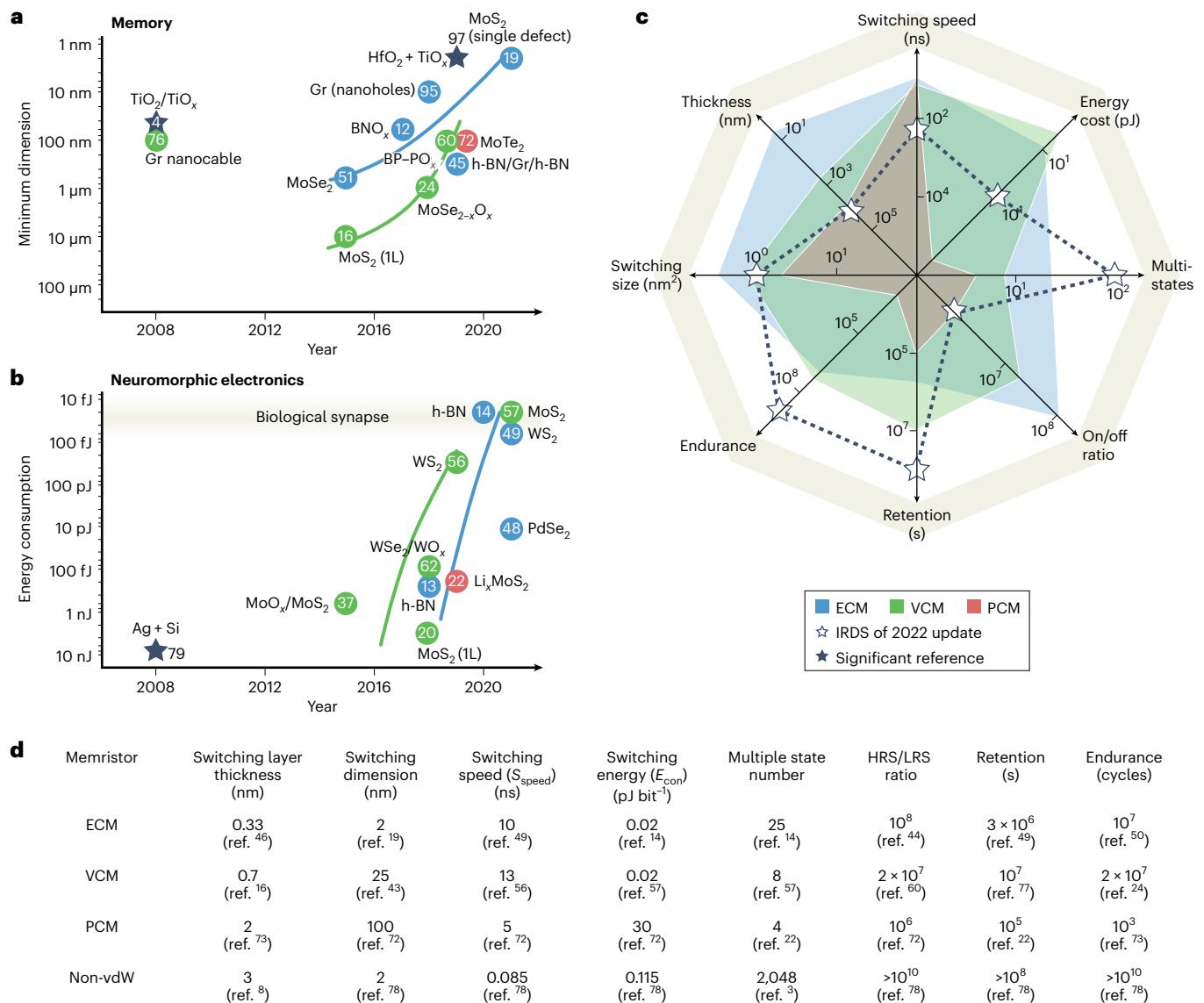

Different types of memristive switching show advantages in different aspects of performance metrics (Fig. 4c,d and Supplementary Table 3). They provide a palette of device designs for various applications

**Fig. 4 | The development and benchmarks of vdW memristors for various applications.** **a,b**, Minimum dimension and energy consumption are selected as the representative metrics for memory (**a**) and neuromorphic electronics (**b**), respectively. Circles and guiding lines of different colours correspond to different switching mechanisms. Filled stars indicate some examples based on non-vdW materials for each application. The numbers in the symbols are the respective reference numbers. The top yellow region in **b** highlights the energy

cost per spike in biological synapses (10–100 fJ). **Gr**, graphene; **BP-PO<sub>x</sub>**, black phosphorus–phosphorous oxide; **1L**, monolayer. **c**, Radar graphs of the critical benchmarks for three types of switching mechanism. Open stars indicate the performance requirements set by ref. 103. Different coloured regions represent different switching mechanisms. **d**, The values corresponding to the graphs in **c**. Several representative non-vdW resistive switching devices are also included for comparison.

(Fig. 4 and Supplementary Fig. 2). In this section, the state-of-the-art vdW memristive devices for data storage, neuromorphic electronics and radiofrequency switches are summarized.

### Memory

One of the most effective strategies for realizing memory cells with ultrahigh density and capacity is to reduce the device size. The enhancement of integration density for traditional transistor-based memory has been approaching an end. As an alternative, vdW-based memristors enable resistive switching in subnanometre-thick media without compromising the switching window or reliability (Supplementary Fig. 1a).

From the perspective of device miniaturization, Fig. 4a maps the development of vdW memristive devices in terms of time and feature dimension. Although resistive switching in a graphene nanoscale system was observed as early as 2008, the actual switching mechanism

was proved to be the breakdown of oxide substrates instead of the proposed nanogap between graphene flakes<sup>76</sup>. Solution-processed memristors based on VCM switching attracted attention due to their low-temperature fabrication<sup>37,55,77</sup>. Oxidized vdW materials were then employed in VCM switching devices to obtain exceptional thermal robustness and durability (Fig. 5a and Supplementary Fig. 1c)<sup>12,24</sup>. The feature sizes of the devices mentioned above are all at a tens-of-micrometres level, possibly due to the difficulty of fabrication. Subsequent studies on PCM switching demonstrated local phase transformation within several crystal cells, showing its potential in further size downscaling<sup>71,72</sup>.

Over the past five years, imperfection-engineered ECM switching has gained more research attention since the conductive channels can be repeatedly manipulated within a sub-10-nm<sup>2</sup> area<sup>13,45–48,52,53</sup>. For example, the permeation of metal atoms into an oxidized h-BN

bilayer can enhance the local electric field, leading to a promoted ion hopping process and a lowered switching threshold<sup>12</sup>. Since 2017, Lanza et al. have engineered various defects in CVD-grown h-BN films for realizing rich ECM switching properties, ultralow switching energy and improved device yield<sup>13,14,41,52</sup>. Further feature size shrinkage was achieved by manipulating a single point defect in monolayer TMCs with a 2 nm footprint<sup>19</sup>.

Important metrics of vdW memristors are summarized in Fig. 4d. In terms of scalability and energy consumption, vdW memristors show potential to outperform non-vdW memristors. Nevertheless, the endurance and retention of vdW memristors remain inferior to the state-of-the-art metal-oxide memristors, which is understandable considering that the research on vdW memristors is still at a rudimentary stage. On top of this, these important properties are not well characterized to the upper limit by the existing reports. Note that the retention of PCM memristors is particularly short because the metastable phase of TMCs is vulnerable to thermal noise and tends to spontaneously relax to the thermodynamic stable phase due to the low phase transition barrier.

### Neuromorphic electronics

Implementing deep learning algorithms in conventional von Neumann computers encounters a critical technology challenge due to the overwhelmingly frequent data transportation between the physically separated processing and memory modules, incurring severe energy and time inefficiency<sup>78</sup>. This motivates the hardware innovation represented by neuromorphic electronics. The main idea of neuromorphic computing is to build artificial neural networks that not only compute in memory but also physically mimic the synapses and neurons in biological nervous systems, which can implement biological learning rules to fulfil complex learning and cognitive tasks, reduce power consumption and accelerate the learning process<sup>79,80</sup>.

One crucial part of synapse emulation is to implement various modes of synaptic plasticities, such as short- and long-term plasticity, spike-timing-dependent plasticity and heterosynaptic plasticity. Short- and long-term plasticity have been demonstrated using MoS<sub>2</sub> or oxidized MoS<sub>2</sub> memristive devices on flexible substrates<sup>37,81</sup>. Spike-timing-dependent plasticity, which is a popular variant of the Hebbian learning rule, was achieved in a MoS<sub>2</sub> memristor via the formation and rupture of the metallic conductive pathway along the grain boundaries<sup>53</sup>. Heterosynaptic plasticity was then implemented in a single multigate MoS<sub>2</sub> memtransistor by tuning in-plane ion migration. The additional gate tunability enhances the modulation range of the switching threshold and zero-bias resistance, potentially enabling applications such as fault-tolerant neural networks (Fig. 5b)<sup>20</sup>. In terms of energy cost, most vdW synapses remain at a nanojoule to picojoule level, still far from the energy efficiency of their biological counterparts (Fig. 4b). Several recent studies revealed that this issue could be addressed by properly devising the switching operation protocols. For example, setting a low-level compliance current (CL) can achieve a 20 fJ switching by partially rupturing the conductive pathways in ECM switching devices<sup>14</sup>. However, the improved energy consumption obtained by this strategy necessitates a higher operational complexity (Fig. 5f).

An ideal artificial synapse is expected to meet many other merit requirements, including linear and symmetrical weight update, multiple well defined weight states, large dynamic range, low switching variation and high endurance. Supplementary Table 4 summarizes these metrics of reported synaptic devices based on vdW materials. The dynamic range and the endurance of these devices vary from case to case to a large degree, but they are overall outperformed by the state-of-the-art metal-oxide synaptic devices according to the data in the current literature. However, it is believed that these metrics may not have been pushed to their upper limit in the measurement design of previous reports. In particular, the nonlinearity of conductance change

is a common issue of ECM and VCM switching devices, because the physical process (ion drift or diffusion) that dominates the evolution of the conduction channels varies at different stages of switching<sup>82</sup>. Several approaches have been developed to improve the programming linearity of vdW memristors. Chen et al. employed low-level CL in operating few-layer h-BN ECM memristors to achieve 25 linearly increasing conductance states<sup>14</sup>.

More complicated functionalities such as information processing and recognition in human brains require dynamic interactions between numerous neurons, dendrites and synapses in neural networks. However, there have been a relatively limited number of studies on artificial neurons and even fewer on artificial dendrites<sup>83</sup>. The pioneering works on vdW-based artificial neurons focus on taking advantage of their volatile switching mechanisms<sup>84,85</sup>. For example, a 1T-TaS<sub>2</sub> memristor based on charge-density-wave phase transition realized tunable stochastic spiking characteristics, similar to the case of biological neurons. The stochasticity originates from the microscopic random reconfiguration of charge-density-wave domains (Fig. 5g).

### Radiofrequency switches

A radiofrequency switch is a crucial reconfigurable component of radiofrequency circuits, which play a core role in high-frequency communication and Internet of Things technologies. A high-performance radiofrequency switch is expected to have low on-state resistance ( $R_{on}$ ) and low off-state capacitance ( $C_{off}$ ) to afford low insertion loss, high isolation and high cutoff frequency  $f_c = 1/2\pi R_{on} C_{off}$ . Low power consumption and scalability also become more critical for 5G and 6G applications.

For complementary metal–oxide–semiconductor transistor (CMOS)-based radiofrequency switches, static energy dissipation is the knottiest problem, as they are volatile and require a constant non-zero hold bias. This inspires the development of emerging non-volatile devices. Early attempts to develop memristive non-volatile switches used planar switching media such as a solid-state electrolyte (for example, GeSe<sub>2</sub>) or an air nanogap (Supplementary Fig. 3)<sup>86</sup>. However, technical difficulties mainly related to silicon-based thermal budget barriers impede their industrial application. The emergence of vdW memristors provides a possible solution<sup>187</sup>. Taking an ECM switching-based h-BN atomristor as an example, its non-volatile nature results in zero static power dissipation, and the low  $R_{on}$  (Fig. 5c) guarantees a high cutoff frequency to cover the entire 5G spectrum (100 GHz)<sup>87</sup>. Given that  $C_{off}$  decreases proportionally with a smaller switching area, the area-independent  $R_{on}$  of vdW switches helps circumvent the trade-off between performance and device scalability. On the basis of this advantage, downscaled MoS<sub>2</sub> switches (0.04  $\mu\text{m}^2$ ) demonstrate the data transmission ability to satisfy 6G communication requirements<sup>88</sup>. However, the endurance of ECM atomristors is problematic due to the low structural robustness against the high operating current.

### Challenges facing vdW memristor applications

Despite the substantial research progress made in defect physics, switching mechanisms and device benchmarking of vdW memristors over the last decade, some key issues still prevent their practical commercialization. To fully exploit the advantages of vdW memristive materials, further research on imperfection engineering is needed for optimized device design and characterization, variation control and system-level integration.

Imperfection engineering of vdW memristors aims to customize the imperfection types, distributions or tunability in vdW materials to achieve desirable memristive characteristics. From the viewpoint of physics, the imperfection-mediated switching mechanisms of vdW memristors are similar to those of metal-oxide memristors, especially for ECM and VCM<sup>7</sup>. However, imperfections in vdW materials provide a larger engineering space for more precisely tuning switching behaviours. First, a vdW system possesses more imperfection

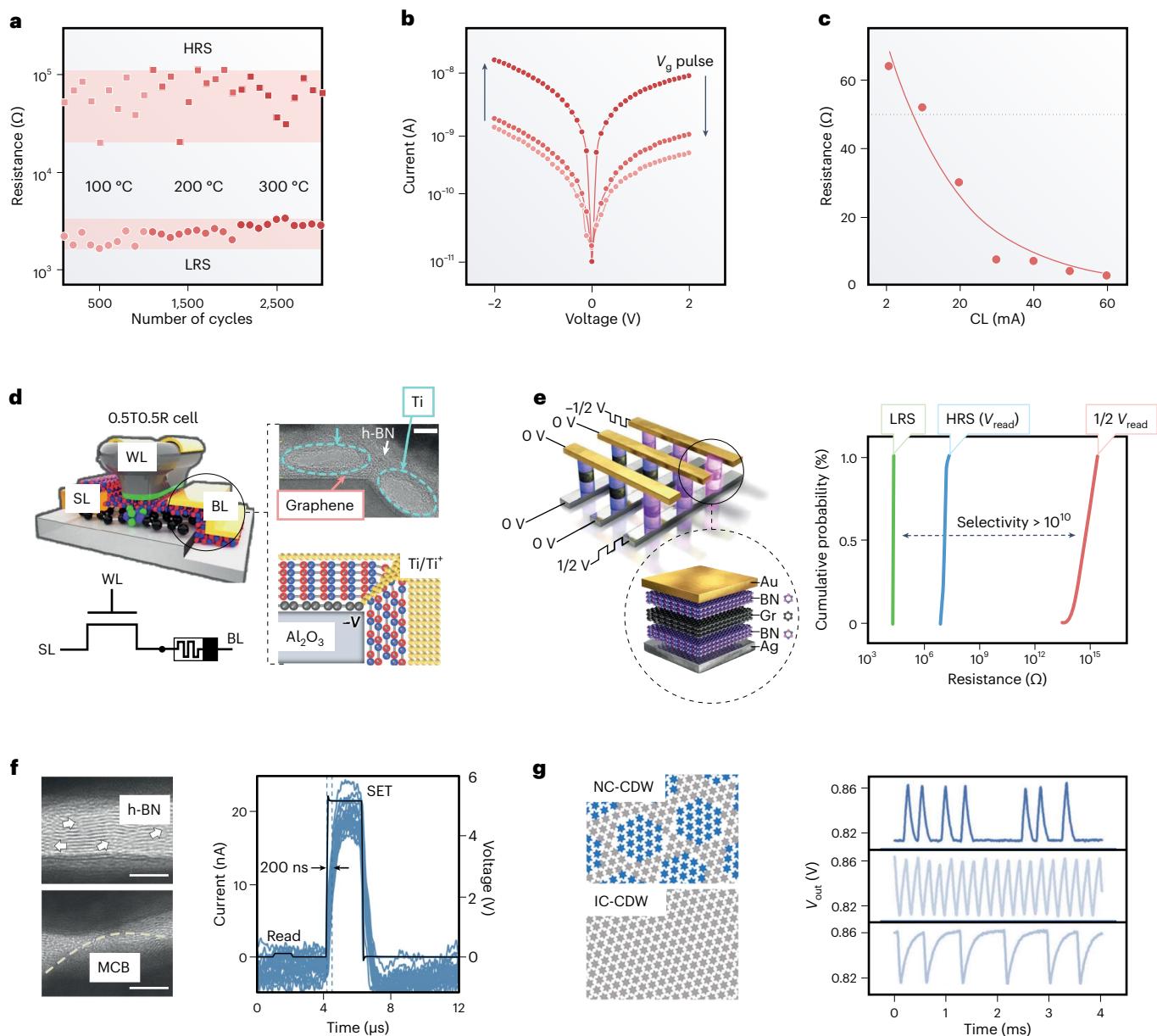

**Fig. 5 | Selected special characteristics of vdW memristors.** **a**, A  $\text{MoS}_{2-x}\text{O}_x$ /graphene memristor that can tolerate high operation temperatures. The switching between LRS and HRS remains robust as the temperature increases<sup>24</sup>. **b**, Gate voltage ( $V_g$ )-tunable current–voltage characteristics of a polycrystalline  $\text{MoS}_2$  memristor<sup>20</sup>. **c**, LRS resistance of a monolayer h-BN memristor as a function of CL<sup>87</sup>. The low resistance (below  $50 \Omega$ ) is critical for radiofrequency applications. **d**, Left: schematics of a vdW heterostructure 0.5T0.5R cell<sup>49</sup>. The key design features of this ultracompact 0.5T0.5R cell are the dielectric layer and edge contact shared by the transistor and the memristor. WL, word-line; SL, source-line; BL, bit-line. Right: cross-sectional TEM image of the h-BN memristor with a Ti conductive filament and simulated switching mechanism of the SET process. The scale bar in the TEM image is 5 nm. **e**, Left: schematics of a memristor array with self-selectivity and a zoomed-in single device structure (Au/h-BN/Gr/h-BN/Ag)<sup>45</sup>. Right: resistance variation of the selected cell at LRS, HRS and half-selected states. **f**, Left: cross-sectional TEM images of an Ag/h-BN/Au device after applying a current–voltage sweep with different values of CL. The

small conductive islands at  $CL = 10 \text{ nA}$  (top) and the well developed conductive filament at  $CL = 2 \text{ mA}$  (bottom) indicate the threshold switching behaviour of the h-BN device<sup>13</sup>. Both scale bars are 4 nm. The arrows in the top panel mark the local defect paths in h-BN switching medium. The dashed line in the bottom panel describes the developed metallic conductive bridge (MCB). Right: the  $I$ – $t$  curve (blue) of the Ag/h-BN/Ag memristor under a fast voltage pulse measurement (black curve) reveals the energy-efficient switching<sup>14</sup>. **g**, Schematics of the atomic structure of two different phases of 1T-Ta<sub>2</sub>, NC-CDW and IC-CDW represent the nearly commensurate and incommensurate charge-density-wave phases, respectively. Output voltage waveforms of a 1T-Ta<sub>2</sub> neuron show different oscillation behaviours at various bias conditions, including stochastic oscillation (top and bottom) and regular oscillation (middle). Panels adapted with permission from: **a**, ref. 24, Springer Nature Limited; **b**, ref. 20, Springer Nature Limited; **c**, ref. 87, Springer Nature Limited; **d**, ref. 49, IEEE; **e**, ref. 45 under a Creative Commons licence CC BY 4.0; **f**, Left: ref. 13, Springer Nature Limited; **f**, Right: ref. 14, Springer Nature Limited; **g**, ref. 85, American Chemical Society.

types. The diverse anion types that dominate the VCM switching in TMCs and phase boundaries between regions of semiconductor and metal states are unique imperfections in vdW memristors. Second, more controllability over the distribution of imperfections can be

realized in vdW systems. The well defined grain boundaries obtained via post-treatments can lower the ion-migration barrier and thus the energy consumption, and also reduce switching variation<sup>13,16</sup>. Similarly, if the vacancy density can be precisely controlled, a single-defect

memristor crossbar array with the smallest footprint can be expected for highly dense memory chips<sup>19</sup>. Moreover, a vdW system provides more tunability of switching features in lateral devices. For instance, the conductance of a vdW memtransistor can be tuned by a gate voltage, which is not effective for the traditional metal-oxide lateral memristors because they typically feature a large bandgap<sup>20</sup>. In addition, we can use intercalation ions to define the phase boundaries and the intercalation ion drift can be controlled via multiple electrode pairs in different directions, which enables the emulation of biological synaptic interactions<sup>22</sup>.

## Design and characterization

The uncovered memristive behaviours in many vdW materials are still far from being fully understood. The diversity of defects in vdW materials implies the coexistence of multiple switching mechanisms in a single system, for instance, the coexistence of ECM and VCM switching in oxidized MoS<sub>2</sub> (ref. 55). This incurs technical difficulties in precisely probing the dynamics of a specific type of imperfection and evaluating its contribution to the overall switching process. In addition, new physical phenomena and properties emerge with new materials, such as the charge-density-wave phase transition in 1T-TaS<sub>2</sub> (ref. 85). Expansion of the vdW family inevitably complicates the material selection for an optimized device design<sup>39,85</sup>. To overcome these problems, device modelling analysis and *in situ* characterizations should be combined to understand the underlying mechanisms and seek optimal device designs.

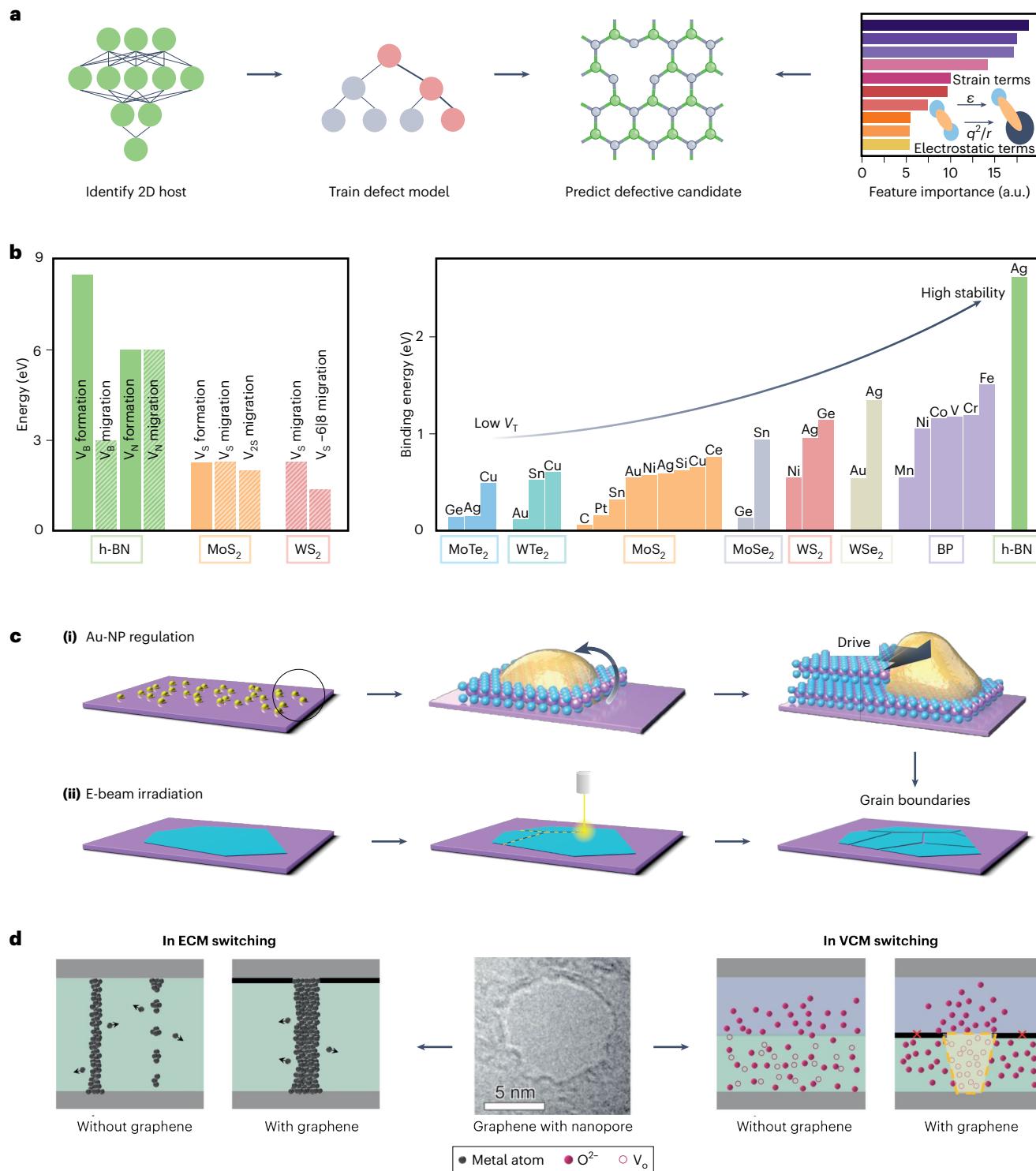

Advanced physical modelling via machine learning and first-principles calculation is proposed to efficiently predict the role of critical imperfections in shaping resistive characteristics. Taking ECM switching as an example, the optimization includes identifying promising switching media, training defective structure models by introducing metal atoms, and predicting ideal metal electrode candidates via evaluation of the binding energy barriers (Fig. 6a)<sup>54</sup>. Different barrier heights lead to different memristive switching behaviours in the corresponding ECM memristors, as the formation and motion of the defects are regulated by the energy profile (Fig. 6b)<sup>21,47</sup>. Regarding the host materials, h-BN provides higher energy barriers than the TMC group. For PCM switching, tellurides and their alloys serve as a thermodynamically more favourable platform for phase transition<sup>36,67</sup>.

As to mechanism exploration, *in situ* microscopic techniques have been employed to uncover the resistive switching process in an all-surface 2D switching system (Supplementary Table 1). Commonly used *in situ* techniques include conductive atomic force microscopy, transmission electron microscopy (TEM) and scanning transmission X-ray microscopy. They are mainly used to visualize critical physical processes, such as a single-defect evolution, grain boundary migration and localized phase transformation<sup>16,19,22,72</sup>. These observations provide crucial inputs for constructing the physical models of switching.

## Variation control

From the engineering perspective, the variability of the resistive switching process is one of the most critical issues impeding commercialization<sup>89</sup>. For ECM and VCM switching, an effective optimization method to reduce switching variation is to control the imperfection distribution by modifying the growth process or applying a post-treatment.

During material growth, imperfections such as grain boundaries and dopants can be predesigned to suppress switching variation. Efforts have been made to introduce prefabricated precursors or threading dislocations to control the channel formation/rupture in conventional oxides<sup>90</sup>. However, these methods still face non-uniformity problems for large-scale applications. In vdW systems, this issue can be further addressed since the grain-boundary distribution can be engineered via adjusting large-area CVD fabrication<sup>91</sup>. For example, predeposited metal nanoparticles (NPs) (such as Au NPs) can act as the growth nuclei of TMCs. The density of metal NPs defines the size of TMC domains (Fig. 6c(i))<sup>25</sup>. Therefore, the average distance between grain boundaries can be constrained below 5 nm by depositing high-density

metal NPs. The vdW switching layer with dense grain boundaries makes the scalable fabrication of memristive devices possible. Predepositing metal nanoclusters (for example, Ag or Cu) serving as seeding materials can provide another approach to predesign the conductive channels for reducing device variation of vdW memristors but still needs more experimental attempts<sup>92</sup>.

Post-treatment techniques such as surface plasma, electron-beam exposure or ion bombardment are used to introduce vacancies, grain boundaries or nanopores to confine the conductive channels and optimize switching uniformity. Electron-beam irradiation with nearly atomic-scale spatial resolution can create defective regions and precisely alter the grain-boundary morphology (Fig. 6c(ii))<sup>93</sup>. As a typical example, the properties of the formed conductive channels in PdSe<sub>2</sub> flakes were controlled by tuning the applied electron-beam dosage. The partially reset filaments along the created grain boundaries substantially improve the switching uniformity (sixfold) when compared with the totally reset ones<sup>48</sup>. Other researchers used ion bombardment to generate defective nanopores in vdW materials as a new way to regulate ion motion. Pristine graphene films are ion impermeable, but the precreated nanopores allow the ions to pass through<sup>42,94</sup>. By employing vdW films with nanoscale holes as ion sieves, researchers can define the size, distribution and density of the conductive channels (Fig. 6d)<sup>43,50,95</sup>. Furthermore, narrowing the nanopores can restrict the ion species allowed to pass, which can mitigate the high operation current and stuck-ON issues. Even though the proposed post-treatment solutions are theoretically effective for device downscaling, their high dependence on the precision of the equipment employed should be considered.

## Integration

The integration of vdW memristors is critical for more practical applications. It has two aspects: integrating vdW memristors with current technology and realizing their scaling potential for ultradense memory arrays.

CMOS components are necessary in the hardware implementation of computing systems based on vdW memristors. While vdW memristor arrays can naturally serve as neural networks, CMOS components are still the best choice for the peripheral circuits<sup>96,97</sup>. Fortunately, vdW memristors are CMOS technology compatible due to the low-temperature synthesis and transfer capability<sup>98</sup>. They can be post-fabricated on a silicon chip through layer-by-layer stacking. A vdW memristor fabricated elsewhere can even be directly embedded in a silicon chip by a precise transfer process. Beyond silicon CMOS technology, it is worth to note that attempts have also been made to demonstrate an all-vdW computing system: for example, by integrating h-BN memristors with WS<sub>2</sub> transistors<sup>49</sup>.

Though individual vdW memristors are reported to possess many advantages, system-level demonstrations of vdW memristor crossbars remain rare. This issue mainly originates from the relatively immature synthesis and fabrication techniques of large-area vdW materials. For example, cracks and wrinkles can easily emerge over the transfer process. Several large-scale transfer techniques or transfer-free fabrication methods, such as layer-resolved splitting or adhesive wafer bonding methods, have been developed to address this challenge<sup>99</sup>. Moreover, more area-efficient architectures and advanced integration technology are still needed to take full advantages of vdW memristors at a system level.

VdW memristors have two notable merits in 2D planar integration. From the point of view of the technology node, single-defect atomristors possibly have the smallest switching footprint thanks to the one-atom-thick switching layer. The theoretical device density can reach 160 Tbit in. <sup>-2</sup> at a 2 nm pitch, comparable to a TiO<sub>x</sub>/HfO<sub>2</sub> crossbar array of 2 nm feature size, although the practical realization is still facing technical difficulties<sup>19,100</sup>. Also, the unique properties of vdW materials enable more integration architectures. The traditional 1T1R

**Fig. 6 | Imperfection engineering to improve the performance of vdW memristors.** **a**, A workflow schematic of a deep learning method for predicting point-defect-enabled ECM switching in vdW materials. It involves identifying promising 2D host materials, training defective structure models and predicting ideal defect candidates. The rightmost panel shows various features in computing the defect formation energy. Top to bottom: mean number of  $p$  valence electrons, defect species chemical potential, electronegativity, mean number of  $p$  valence electrons<sup>a</sup>, energy of highest occupied molecular orbital, mean atomic weight<sup>a</sup>, number of valence electrons, mean atomic weight, chemical fingerprint, vdW radius. <sup>a</sup>The absolute value of a pristine or defective structure, and the others are the differences between the two systems<sup>54</sup>. **b**, Left: the calculated energy barriers of the defect formation and migration in various vdW materials. Right: calculated binding energies of various vacancies and metal atoms. In theory, a lower binding energy leads to smaller threshold voltages ( $V_T$ )

for resistive switching, while a higher binding energy results in higher switching stability. **c**, Engineering the grain boundaries in vdW materials via (i) modifying material preparation or (ii) a post-treatment process<sup>25,48</sup>. Predeposition of metal NPs is a typical method to control grain size. A common method to tailor grain-boundary topologies is electron-beam irradiation. **d**, Engineering the defective nanopores in 2D films to define the size and distribution of conductive filaments. The middle TEM image shows the morphology of a graphene film with an 8 nm nanopore. Left: in ECM memristors, a defective graphene film between the active electrode and switching medium leads to a better-defined filament than found in a device without a graphene film. Right: in VCM switching, defective graphene as an ion-blocking layer confines the overinjection of oxygen vacancies<sup>43,50,95</sup>. Panels adapted with permission from: **a**, ref. 54, American Chemical Society; **c**, ref. 42, Springer Nature Limited.

(one transistor and one resistor) design has been commonly used due to the anti-interference capability; however, the addition of the transistor compromises the scaling advantage of memristors. A 0.5TO.5R memory cell based on stackable vdW layers was recently proposed as a possible solution (Fig. 5d)<sup>49</sup>. It features a shared resistively switchable insulator (h-BN) and an edge contact (graphene) between the transistor and the memristor, achieving a more area-efficient memory unit. However, such a scenario can only reduce the cell area if the transistor and the memristor are assumed to be fabricated in the same plane, and show no clear advantage compared with the state-of-the-art 3D stacking 1T1R arrays<sup>3</sup>. Another strategy to achieve simplified system integration is to build memristive devices with self-selectivity. For example, in a vertical Ag/h-BN/graphene/h-BN/Au heterostructure, the graphene film with ion impermeability and h-BN films with defective vacancies enables the formation of a volatile Ag filament and a non-volatile boron filament in two h-BN regions, respectively. Such a design integrates both volatile and non-volatile kinetics in a single cell and leads to a 10<sup>10</sup> self-selectivity (Fig. 5e)<sup>45</sup>.

3D integration architectures of vdW systems exhibit several advantages over bulk materials due to their atomically thin bodies and low-temperature fabrication. Compared with traditional silicon technology with thermal budget incompatibility issues, low-temperature fabrication for vdW devices (below 400 °C) facilitates the back-end-of-line integration process. In addition, vertically stacked vdW crossbar cells are supposed to be promising in reducing the integration thickness when compared with a 3D oxide system<sup>101</sup>. However, the fabrication requires more lithography steps, probably compromising the low cost and high yield. To overcome this difficulty, the recently reported vertically constructed 3D oxide memristors, which use rolled switching media and metal pillow electrodes, can provide some inspiration to reduce the lithography need<sup>102</sup>.

## Outlook

The compositional or structural imperfections in vdW materials lead to rich memristive switching mechanisms and offer several opportunities to engineer and tune their switching properties. There are three key types of memristive mechanism, each of which is associated with a specific group of imperfections. Such switching mechanisms provide vdW memristive devices with unique characteristics, including ultrasmall switching dimensions, multidirectional tunability and high-temperature robustness, leading to various applications, including but not limited to memory devices, neuromorphic electronics and radiofrequency switches.

Research on vdW memristors is still at an early stage of development and the path to commercialization will involve addressing numerous challenges related to mechanism exploration, device design, variation control and system-level integration. To further improve material selection and processing, device fabrication, circuit integration and algorithm implementation of vdW memristive systems, more systematic research on imperfection engineering through device–circuit–algorithm co-design and co-optimization is required.

## References

1. Lanza, M. et al. Memristive technologies for data storage, computation, encryption, and radio-frequency communication. *Science* **376**, 1066 (2022).

2. Zhou, F. et al. Optoelectronic resistive random access memory for neuromorphic vision sensors. *Nat. Nanotechnol.* **14**, 776–782 (2019).

3. Rao, M. et al. Thousands of conductance levels in memristors integrated on CMOS. *Nature* **615**, 823–829 (2023).

4. Yang, J. J. et al. Memristive switching mechanism for metal/oxide/metal nanodevices. *Nat. Nanotechnol.* **3**, 429–433 (2008).

5. Li, C. et al. Direct observations of nanofilament evolution in switching processes in HfO<sub>2</sub>-based resistive random access memory by *in situ* TEM studies. *Adv. Mater.* **29**, 1602976 (2017).

6. Yuan, F. et al. Real-time observation of the electrode-size-dependent evolution dynamics of the conducting filaments in a SiO<sub>2</sub> layer. *ACS Nano* **11**, 4097–4104 (2017).

7. Yang, J. J., Strukov, D. B. & Stewart, D. R. Memristive devices for computing. *Nat. Nanotechnol.* **8**, 13–24 (2013).

8. Chen, Y.-S. et al. An ultrathin forming-free HfO<sub>x</sub> resistance memory with excellent electrical performance. *IEEE Electron Device Lett.* **31**, 1473–1475 (2010).

9. Panja, R., Roy, S., Jana, D. & Maikap, S. Impact of device size and thickness of Al<sub>2</sub>O<sub>3</sub> film on the Cu pillar and resistive switching characteristics for 3D cross-point memory application. *Nanoscale Res. Lett.* **9**, 692 (2014).

10. Chen, A. Area and thickness scaling of forming voltage of resistive switching memories. *IEEE Electron Device Lett.* **35**, 57–59 (2014).

11. Liu, S. et al. Eliminating negative-SET behavior by suppressing nanofilament overgrowth in cation-based memory. *Adv. Mater.* **28**, 10623–10629 (2016).

12. Zhao, H. et al. Atomically thin femtojoule memristive device. *Adv. Mater.* **29**, 1703232 (2017).

13. Shi, Y. et al. Electronic synapses made of layered two-dimensional materials. *Nat. Electron.* **1**, 458–465 (2018).

14. Chen, S. et al. Wafer-scale integration of two-dimensional materials in high-density memristive crossbar arrays for artificial neural networks. *Nat. Electron.* **3**, 638–645 (2020).

15. Wang, X. et al. Grain-boundary engineering of monolayer MoS<sub>2</sub> for energy-efficient lateral synaptic devices. *Adv. Mater.* **33**, 2102435 (2021).

16. Sangwan, V. K. et al. Gate-tunable memristive phenomena mediated by grain boundaries in single-layer MoS<sub>2</sub>. *Nat. Nanotechnol.* **10**, 403–406 (2015).

17. Liu, X. W. et al. Temperature-sensitive spatial distribution of defects in PdSe<sub>2</sub> flakes. *Phys. Rev. Mater.* **5**, L041001 (2021).

18. Lin, Y. C., Dumcenco, D. O., Huang, Y. S. & Suenaga, K. Atomic mechanism of the semiconducting-to-metallic phase transition in single-layered MoS<sub>2</sub>. *Nat. Nanotechnol.* **9**, 391–396 (2014).

19. Hus, S. M. et al. Observation of single-defect memristor in an MoS<sub>2</sub> atomic sheet. *Nat. Nanotechnol.* **16**, 58–62 (2021).

20. Sangwan, V. K. et al. Multi-terminal memtransistors from polycrystalline monolayer molybdenum disulfide. *Nature* **554**, 500–504 (2018).

21. Azizi, A. et al. Dislocation motion and grain boundary migration in two-dimensional tungsten disulphide. *Nat. Commun.* **5**, 4867 (2014).

22. Zhu, X., Li, D., Liang, X. & Lu, W. D. Ionic modulation and ionic coupling effects in MoS<sub>2</sub> devices for neuromorphic computing. *Nat. Mater.* **18**, 141–148 (2019).

23. Fang, Z. et al. Temperature instability of resistive switching on HfO<sub>x</sub>-based RRAM devices. *IEEE Electron Device Lett.* **31**, 476–478 (2010).

24. Wang, M. et al. Robust memristors based on layered two-dimensional materials. *Nat. Electron.* **1**, 130–136 (2018). **This study reported a robust vdW memristive device with a high operating temperature enabled by the oxidisation of MoS<sub>2</sub> flakes.**

25. He, Y. et al. Engineering grain boundaries at the 2D limit for the hydrogen evolution reaction. *Nat. Commun.* **11**, 57 (2020).

26. Zhou, W. et al. Intrinsic structural defects in monolayer molybdenum disulfide. *Nano Lett.* **13**, 2615–2622 (2013).

27. Zou, X. & Yakobson, B. Defects in Two-Dimensional Materials. In Avouris, P., Heinz, T. & Low, T. (Eds.), 2D Materials: Properties and Devices (pp. 359–378) (2017) Cambridge: Cambridge University Press

28. Ma, J., Alfè, D., Michaelides, A. & Wang, E. Stone–Wales defects in graphene and other planar sp<sup>2</sup>-bonded materials. *Phys. Rev. B* **80**, 033407 (2009).

29. van der Zande, A. M. et al. Grains and grain boundaries in highly crystalline monolayer molybdenum disulphide. *Nat. Mater.* **12**, 554–561 (2013).

30. Lahiri, J., Lin, Y., Bozkurt, P., Oleynik, I. I. & Batzill, M. An extended defect in graphene as a metallic wire. *Nat. Nanotechnol.* **5**, 326–329 (2010).

31. Li, Y., Yan, H., Xu, B., Zhen, L. & Xu, C. Y. Electrochemical intercalation in atomically thin van der Waals materials for structural phase transition and device applications. *Adv. Mater.* **33**, 2000581 (2021).

32. Su, C. et al. Engineering single-atom dynamics with electron irradiation. *Sci. Adv.* **5**, eaav2252 (2019).

33. Tosun, M. et al. Air-stable n-doping of WSe<sub>2</sub> by anion vacancy formation with mild plasma treatment. *ACS Nano* **10**, 6853–6860 (2016).

34. Li, J. The mechanics and physics of defect nucleation. *MRS Bull.* **32**, 151–159 (2011).

35. Li, W., Qian, X. & Li, J. Phase transitions in 2D materials. *Nat. Rev. Mater.* **6**, 829–846 (2021).

36. Duerloo, K.-A. & Reed, E. J. Structural phase transitions by design in monolayer alloys. *ACS Nano* **10**, 289–297 (2016).

37. Bessonov, A. A. et al. Layered memristive and memcapacitive switches for printable electronics. *Nat. Mater.* **14**, 199–204 (2015).

38. Pam, M. E. et al. Interface-modulated resistive switching in Mo-irradiated ReS<sub>2</sub> for neuromorphic computing. *Adv. Mater.* **34**, 2202722 (2022).

39. Gong, Y. et al. Spatially controlled doping of two-dimensional SnS<sub>2</sub> through intercalation for electronics. *Nat. Nanotechnol.* **13**, 294–299 (2018).

40. Li, M. et al. High mobilities in layered InSe transistors with indium-encapsulation-induced surface charge doping. *Adv. Mater.* **30**, 1803690 (2018).

41. Shen, Y. et al. Variability and yield in h-BN-based memristive circuits: the role of each type of defect. *Adv. Mater.* **33**, 2103656 (2021).

42. Garaj, S. et al. Graphene as a subnanometre trans-electrode membrane. *Nature* **467**, 190–193 (2010).

43. Lee, J., Du, C., Sun, K., Kioupakis, E. & Lu, W. D. Tuning ionic transport in memristive devices by graphene with engineered nanopores. *ACS Nano* **10**, 3571–3579 (2016).

44. Ge, R. et al. Atomristor: nonvolatile resistance switching in atomic sheets of transition metal dichalcogenides. *Nano Lett.* **18**, 434–441 (2018).

45. Sun, L. et al. Self-selective van der Waals heterostructures for large scale memory array. *Nat. Commun.* **10**, 3161 (2019).

46. Wu, X. et al. Thinnest nonvolatile memory based on monolayer h-BN. *Adv. Mater.* **31**, 1806790 (2019).

47. Ge, R. et al. A library of atomically thin 2D materials featuring the conductive-point resistive switching phenomenon. *Adv. Mater.* **33**, 2007792 (2020).

48. Li, Y. S. et al. Anomalous resistive switching in memristors based on two-dimensional palladium diselenide using heterophase grain boundaries. *Nat. Electron.* **4**, 348–356 (2021).

49. Zhang, D., Yeh, C.-H., Cao, W. & Banerjee, K. 0.5T0.5R—an ultracompact RRAM cell uniquely enabled by van der Waals heterostructures. *IEEE Trans. Electron Devices* **68**, 2033–2040 (2021).

50. Zhao, X. et al. Confining cation injection to enhance CBRAM performance by nanopore graphene layer. *Small* **13**, 1603948 (2017). **This work employed nanoporous graphene to regulate the morphology and spatial distribution of conductive channels in metal-oxide memristors.**

51. Yan, Y., Sun, B. & Ma, D. Resistive switching memory characteristics of single MoSe<sub>2</sub> nanorods. *Chem. Phys. Lett.* **638**, 103–107 (2015).

52. Pan, C. et al. Coexistence of grain-boundaries-assisted bipolar and threshold resistive switching in multilayer hexagonal boron nitride. *Adv. Funct. Mater.* **27**, 1604811 (2017).

53. Xu, R. et al. Vertical MoS<sub>2</sub> double-layer memristor with electrochemical metallization as an atomic-scale synapse with switching thresholds approaching 100 mV. *Nano Lett.* **19**, 2411–2417 (2019).

54. Frey, N. C., Akinwande, D., Jariwala, D. & Shenoy, V. B. Machine learning-enabled design of point defects in 2D materials for quantum and neuromorphic information processing. *ACS Nano* **14**, 13406–13417 (2020).

55. Son, D. et al. Colloidal synthesis of uniform-sized molybdenum disulfide nanosheets for wafer-scale flexible nonvolatile memory. *Adv. Mater.* **28**, 9326–9332 (2016).

56. Yan, X. et al. Vacancy-induced synaptic behavior in 2D WS<sub>2</sub> nanosheet-based memristor for low-power neuromorphic computing. *Small* **15**, 1901423 (2019).

57. Feng, X. et al. Self-selective multi-terminal memtransistor crossbar array for in-memory computing. *ACS Nano* **15**, 1764–1774 (2021).

58. Song, D.-X., Ma, W.-G. & Zhang, X. Correlated migration of ions in a 2D heterostructure anode: guaranteeing a low barrier for a high site occupancy. *J. Mater. Chem. A* **8**, 17463–17470 (2020).

59. Wang, L. et al. Artificial synapses based on multiterminal memtransistors for neuromorphic application. *Adv. Funct. Mater.* **29**, 1901106 (2019).

60. Wang, Y. et al. High on/off ratio black phosphorus based memristor with ultra-thin phosphorus oxide layer. *Appl. Phys. Lett.* **115**, 193503 (2019).

61. Liu, L. et al. Low-power memristive logic device enabled by controllable oxidation of 2D HfSe<sub>2</sub> for in-memory computing. *Adv. Sci.* **8**, 2005038 (2021).

62. Huh, W. et al. Synaptic barristor based on phase-engineered 2D heterostructures. *Adv. Mater.* **30**, 1801447 (2018).

63. Yamamoto, M. et al. Self-limiting layer-by-layer oxidation of atomically thin WSe<sub>2</sub>. *Nano Lett.* **15**, 2067–2073 (2015).

64. Liu, Y. et al. Thermal oxidation of WSe<sub>2</sub> nanosheets adhered on SiO<sub>2</sub>/Si substrates. *Nano Lett.* **15**, 4979–4984 (2015).

65. Yang, F. S. et al. Oxidation-boosted charge trapping in ultra-sensitive van der Waals materials for artificial synaptic features. *Nat. Commun.* **11**, 2972 (2020).

66. Mleczko, M. J. et al. HfSe<sub>2</sub> and ZrSe<sub>2</sub>: two-dimensional semiconductors with native high-kappa oxides. *Sci. Adv.* **3**, 1700481 (2017).

67. Duerloo, K. A., Li, Y. & Reed, E. J. Structural phase transitions in two-dimensional Mo- and W-dichalcogenide monolayers. *Nat. Commun.* **5**, 4214 (2014).

68. Yang, H., Kim, S. W., Chhowalla, M. & Lee, Y. H. Structural and quantum-state phase transitions in van der Waals layered materials. *Nat. Phys.* **13**, 931–937 (2017).

**This paper critically examined the phase transition physics in vdW materials and highlighted the perspective applications of vdW electronics.**

69. Wang, Y. et al. Structural phase transition in monolayer MoTe<sub>2</sub> driven by electrostatic doping. *Nature* **550**, 487–491 (2017).

70. Rao, F. et al. Reducing the stochasticity of crystal nucleation to enable subnanosecond memory writing. *Science* **358**, 1423–1427 (2017).

71. Zhang, F. et al. An ultra-fast multi-level MoTe<sub>2</sub>-based RRAM. In *2018 IEEE International Electron Devices Meeting (IEDM)* 22.7.1–22.7.4 (IEEE, 2019).

72. Zhang, F. et al. Electric-field induced structural transition in vertical MoTe<sub>2</sub> and Mo<sub>1-x</sub>WTe<sub>2</sub>-based resistive memories. *Nat. Mater.* **18**, 55–61 (2019).

73. Cheng, P., Sun, K. & Hu, Y. H. Memristive behavior and ideal memristor of 1T phase MoS<sub>2</sub> nanosheets. *Nano Lett.* **16**, 572–576 (2016).

74. Jin, Q., Liu, N., Chen, B. & Mei, D. Mechanisms of semiconducting 2H to metallic 1T phase transition in two-dimensional MoS<sub>2</sub> nanosheets. *J. Phys. Chem. C* **122**, 28215–28224 (2018).

75. Han, S. T. et al. Black phosphorus quantum dots with tunable memory properties and multilevel resistive switching characteristics. *Adv. Sci.* **4**, 1600435 (2017).

76. Yao, J. et al. Resistive switching in nanogap systems on SiO<sub>2</sub> substrates. *Small* **5**, 2910–2915 (2009).

77. Hong, S. K., Kim, J. E., Kim, S. O., Choi, S.-Y. & Cho, B. J. Flexible resistive switching memory device based on graphene oxide. *IEEE Electron Device Lett.* **31**, 1005–1007 (2010).

78. Wang, Z. et al. Resistive switching materials for information processing. *Nat. Rev. Mater.* **5**, 173–195 (2020).

79. Jo, S. H. et al. Nanoscale memristor device as synapse in neuromorphic systems. *Nano Lett.* **10**, 1297–1301 (2010).

80. Ma, C. et al. Intelligent infrared sensing enabled by tunable moiré quantum geometry. *Nature* **604**, 266–272 (2022).

81. Feng, X. et al. A fully printed flexible MoS<sub>2</sub> memristive artificial synapse with femtojoule switching energy. *Adv. Electron. Mater.* **5**, 1900740 (2019).

82. Li, Y., Long, S., Liu, Q., Lv, H. & Liu, M. Resistive switching performance improvement via modulating nanoscale conductive filament, involving the application of two-dimensional layered materials. *Small* **13**, 1604306 (2017).

83. Li, X. et al. Power-efficient neural network with artificial dendrites. *Nat. Nanotechnol.* **15**, 776–782 (2020).

84. Kalita, H. et al. Artificial neuron using vertical MoS<sub>2</sub>/graphene threshold switching memristors. *Sci. Rep.* **9**, 53 (2019).

85. Liu, H. et al. A tantalum disulfide charge-density-wave stochastic artificial neuron for emulating neural statistical properties. *Nano Lett.* **21**, 3465–3472 (2021).

86. Pi, S., Ghadiri-Sadrabadi, M., Bardin, J. C. & Xia, Q. F. Nanoscale memristive radiofrequency switches. *Nat. Commun.* **6**, 7519 (2015).

87. Kim, M. et al. Analogue switches made from boron nitride monolayers for application in 5G and terahertz communication systems. *Nat. Electron.* **3**, 479–485 (2020).

**This study reported the monolayer h-BN memristor and its application in radiofrequency switches.**

88. Kim, M. et al. Monolayer molybdenum disulfide switches for 6G communication systems. *Nat. Electron.* **5**, 367–373 (2022).

89. Lanza, M., Smets, Q., Huyghebaert, C. & Li, L.-J. Yield, variability, reliability, and stability of two-dimensional materials based solid-state electronic devices. *Nat. Commun.* **11**, 5689 (2020).

90. Choi, S. et al. SiGe epitaxial memory for neuromorphic computing with reproducible high performance based on engineered dislocations. *Nat. Mater.* **17**, 335–340 (2018).

**This work demonstrated SiGe epitaxial memristors with engineered grain boundary distribution and provided inspiration for variation control of vdW memristors.**

91. Chen, T. A. et al. Wafer-scale single-crystal hexagonal boron nitride monolayers on Cu(111). *Nature* **579**, 219–223 (2020).

92. Wang, Z. R. et al. Memristors with diffusive dynamics as synaptic emulators for neuromorphic computing. *Nat. Mater.* **16**, 101–108 (2017).

93. Sun, L., Banhart, F. & Warner, J. Two-dimensional materials under electron irradiation. *MRS Bull.* **40**, 29–37 (2015).

94. Rollings, R. C., Kuan, A. T. & Golovchenko, J. A. Ion selectivity of graphene nanopores. *Nat. Commun.* **7**, 11408 (2016).

95. Zhao, X. et al. Breaking the current-retention dilemma in cation-based resistive switching devices utilizing graphene with controlled defects. *Adv. Mater.* **30**, 1705193 (2018).

96. Ambrogio, S. et al. Equivalent-accuracy accelerated neural-network training using analogue memory. *Nature* **558**, 60–67 (2018).

97. Hinton, H. et al. A 200×256 image sensor heterogeneously integrating a 2D nanomaterial-based photo-FET array and CMOS time-to-digital converters. In *2022 IEEE International Solid-State Circuits Conference (ISSCC)* 12.2.1–12.2.3 (IEEE, 2022).

**This paper provided the fabrication contexts of vdW device and CMOS integrated circuits.**

98. Zhu, K. et al. Hybrid 2D/CMOS microchips for memristive applications. *Nature* **618**, 57–62 (2023).