# ModuloNET: Neural Networks Meet Modular Arithmetic for Efficient Hardware Masking

Anuj Dubey<sup>1</sup>, Afzal Ahmad<sup>2</sup>, Muhammad Adeel Pasha<sup>3</sup>, Rosario Cammarota<sup>4</sup> and Aydin Aysu<sup>1</sup>

North Carolina State University, Raleigh, US, {aanujdu,aaysu}@ncsu.edu

The Hong Kong University of Science and Technology, Hong Kong, afzal.ahmad@connect.ust.hk

Abstract. Intellectual Property (IP) thefts of trained machine learning (ML) models through side-channel attacks on inference engines are becoming a major threat. Indeed, several recent works have shown reverse engineering of the model internals using such attacks, but the research on building defenses is largely unexplored. There is a critical need to efficiently and securely transform those defenses from cryptography such as masking to ML frameworks. Existing works, however, revealed that a straightforward adaptation of such defenses either provides partial security or leads to high area overheads. To address those limitations, this work proposes a fundamentally new direction to construct neural networks that are inherently more compatible with masking. The key idea is to use modular arithmetic in neural networks and then efficiently realize masking, in either Boolean or arithmetic fashion, depending on the type of neural network layers. We demonstrate our approach on the edge-computing friendly binarized neural networks (BNN) and show how to modify the training and inference of such a network to work with modular arithmetic without sacrificing accuracy. We then design novel masking gadgets using Domain-Oriented Masking (DOM) to efficiently mask the unique operations of ML such as the activation function and the output layer classification, and we prove their security in the glitch-extended probing model. Finally, we implement fully masked neural networks on an FPGA, quantify that they can achieve a similar latency while reducing the FF and LUT costs over the state-of-the-art protected implementations by 34.2% and 42.6%, respectively, and demonstrate their first-order side-channel security with up to 1M traces.

**Keywords:** Neural networks · Side-channel attacks · Hardware Masking

# 1 Introduction

Illicit extraction of proprietary machine learning (ML) models has become a serious concern in the ever-growing ML industry. Model owners can host a trained ML model either on a cloud server or on an edge device and provide a publicly accessible interface for predictions. Since designing and training an ML model is an expensive process, the trained model has a monetary value associated with it. It has been reported that a single trained ML model can cost as much as \$10M [Mag20]. Therefore, the model owner typically charges the users to use the model or purchase the device with the trained model [Sec20]. In both cases, the ML model carries a business value and should be kept confidential from the users.

Recent advances in ML algorithms and the semiconductor industry have enabled efficient deployment of ML models with reasonably high accuracy on resource-constrained edge devices. Edge-based inference obviates constant communication with the cloud,

<sup>&</sup>lt;sup>3</sup> Lahore University of Management Sciences, Lahore, Pakistan, adeel.pasha@lums.edu.pk

<sup>4</sup> Intel Labs, San Diego, US rosario.cammarota@intel.com

thus improving the inference latency and ensuring data privacy [ZCL<sup>+</sup>19]. Indeed, the number of edge-based artificial intelligence (AI) chips is expected to be doubled by 2024 [Ins20]. Despite these advantages, it becomes harder to ensure the confidentiality of the deployed model on the edge because the device operates in an environment where physical side-channels attacks like power/electromagnetic (EM) become more applicable.

Physical side-channel attacks are effective and hard to mitigate, primarily because they are based on the device's intrinsic properties, like the data-dependent CMOS power consumption [KJJ99]. Such attacks have been extensively studied over the last two decades in the context of cryptographic implementations [KJJ99, CEvMS15, KGB<sup>+</sup>18]. Correspondingly, the research on mitigating such attacks has also matured significantly, starting from the empirically secure primitives [AG01, TKL04] earlier to the provably secure primitives at present [ISW03, NRR06, GMK16, GM18, GIB18]. We envision a similar trend for the side-channel research on ML accelerators. Several recent works already demonstrate successful power/EM side-channel attacks on software and hardware implementations of an ML model [BBJP19, YKO<sup>+</sup>20, WLL<sup>+</sup>18, YMY<sup>+</sup>20, MBC21, JYI<sup>+</sup>20, TSSL20]. There have also been a few proposals on building side-channel defenses against such attacks using the well-known hiding and masking techniques [DCA20b, DCA20a].

The differences between ML and cryptographic algorithms cause challenges when adapting side-channel defenses towards ML. A major problem is due to the integer arithmetic used in neural network computations vs. modular arithmetic in cryptography. Integer arithmetic impedes the direct application of arithmetic masking in the neural network computations due to the leakage of the sign bit [DCA20b]. Prior work investigated this problem and proposed hiding the sign bit leakage through differential circuit styles [DCA20b]. Another work addressed it by decomposing the computations at the bit-level and applying Boolean masking on each operation [DCA20a]. While hiding requires precise control of the back-end flow (and still has some disputed claims [ISU18]), gate-level Boolean masking does not have this drawback but incurs significant overheads.

Motivation and Novelty. Both prior works approach the problem by changing defenses to fit the ML algorithm. By contrast, we explore the alternative—changing the ML frameworks to ease the defense's implementation. Specifically, we reformulate the neural network inference with modular arithmetic (rather than integer arithmetic) and design the building blocks for ML to work with modular arithmetic while preserving the model's accuracy. We call this neural network ModuloNET. We then apply efficient masking styles for different parts of ModuloNET and develop masked components unique for ML topologies. The results show that our solution combines the best of both worlds: it is significantly more secure against first-order attacks than the defense with hiding [DCA20b] and considerably less costly than the only-Boolean masked solution [DCA20a].

**Contributions.** A summary of our contributions and key results are as follows.

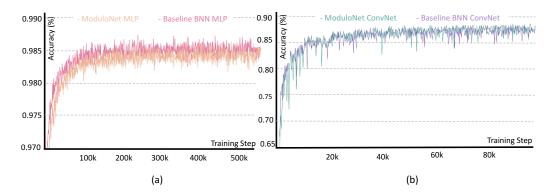

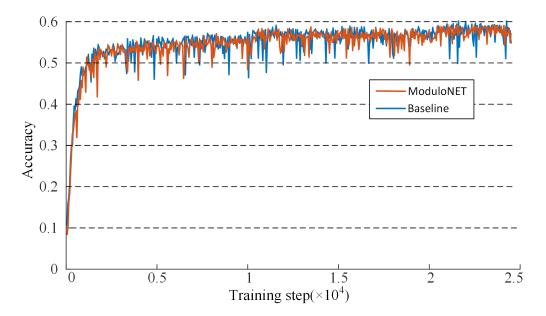

- We address the fundamental incompatibility of neural networks to cryptographic defenses by proposing an alternative way to construct inference that works on modular arithmetic with negligible accuracy loss: less than 0.5% for binarized multi-layer perceptron (MLP) on MNIST, and less than 1% for convolutional neural network (ConvNet) on CIFAR-10 and CIFAR-100 datasets. We identify the challenges of using modular arithmetic in activation, batch normalization (BN) and output layers, and propose a novel layer architecture to address them.

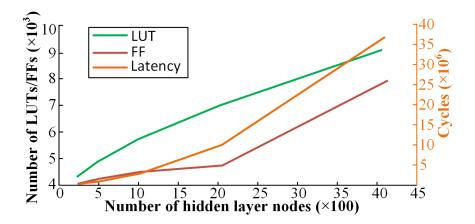

- We implement a parameterized fully-masked inference hardware in which the number of nodes within each layer can be tuned. We opportunistically apply suitable masking styles whenever they become efficient—arithmetic masking for fully connected layers and Boolean masking for activation layers, comparisons, and multiplexers. We

implement a novel and efficient masked thresholder design to securely evaluate the activation function. We also design a novel masked comparator to securely perform masked output layer computations. We implement secure Boolean-to-arithmetic and arithmetic-to-Boolean conversion circuits to switch between different masking styles. We also implement a binarized ConvNet design and show how to mask the (linear) convolution and (non-linear) maxpool operations. This demonstrates the scalability of our proposed techniques to more advanced architectures. The implementation results for the MLP design show that the proposed solution occupies 34.2% and 42.6% fewer LUTs and FFs while achieving virtually the same latency<sup>1</sup> compared to the Boolean-only masked solution [DCA20a].

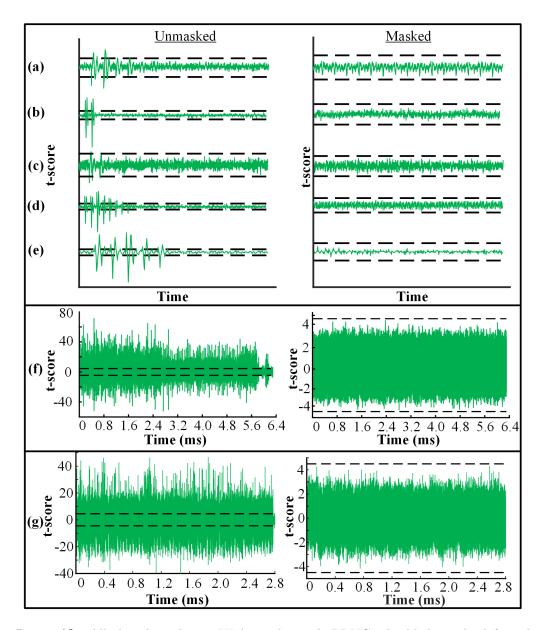

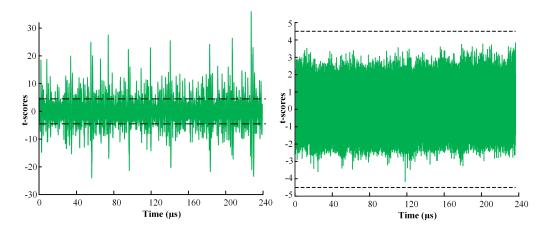

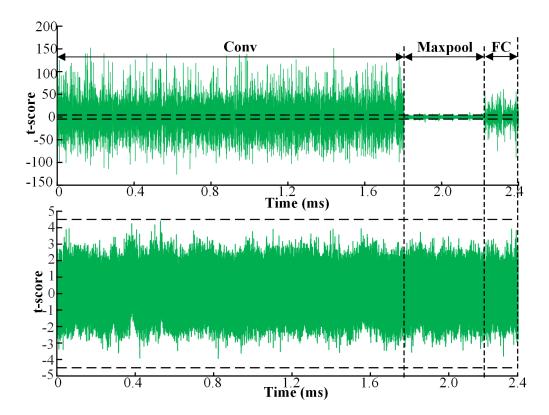

- We perform leakage evaluation tests of our neural network hardware implementation using the widely accepted TVLA methodology [GGJR11] on an FPGA with power measurements. We first evaluate the security of each masked primitive as a standalone unit and then evaluate the fully masked implementation using those primitives. We demonstrate a first-order security with 1M traces each in fixed and random datasets, both for the individual masked components as well as the fully composed design.

- We define the side-channel security for the ML-specific primitives using the glitch-extended probing model [RBN<sup>+</sup>15] in which the power and EM side-channel attacks become equivalent. We prove the security of the proposed masked gadgets for ML-specific operations like the activation function and output layer in this model.

**Organization.** Section 2 outlines our threat model. Section 3 presents relevant background information regarding our notation, hardware masking, and neural networks. Section 4 describes the proposed layer architecture and the software implementation of ModuloNET. Sections 5 and 6 discuss the hardware design of the baseline MLP and masked MLP. Section 7 discusses the design of the baseline and masked ConvNet designs. Section 8 presents the security proofs for the masked gadgets. Section 9 presents our proposed ML model accuracy, hardware implementation results, and leakage evaluation results. Section 10 discusses extensions and future applications of this work and Section 11 concludes the paper.

# 2 Threat Model

We follow the threat model adopted in prior side-channel works on ML model stealing [DCA20b, YKO<sup>+</sup>20]. Here, we summarize and highlight the key aspects. The neural network model is trained offline, and the trained model parameters are securely stored in the accelerator before deployment. The device is then deployed in an untrusted environment where it performs inferences. The attacker can obtain power/EM traces from the device while running inference, either via direct access or remotely [ZS18, SGMT18, WLL<sup>+</sup>18]. We assume a chosen-plaintext attack model where the attacker sends the inputs to the device for classification and can capture multiple traces corresponding to different inputs. The adversary then executes a power/EM-based side-channel attack with the captured traces [KJJ99, BCO04, CRR03]. Furthermore, we present our security proofs in Section 8 using glitch-extended probes first introduced by Reparaz et al. [RBN<sup>+</sup>15].

Following earlier works on model extraction [JSMA19, DCA20b, JCB<sup>+</sup>20], we assume that the hyperparameters of the model like the types/number of neural network layers are either public or obtained by another attack [PMG<sup>+</sup>17, YMY<sup>+</sup>20]. Thus, the adversary tries to extract the model *parameters*, not hyperparameters in our threat model. Also, the number of parameters is in billions while the number of hyperparameters is in hundreds

<sup>&</sup>lt;sup>1</sup>Refer to Table 2.

making parameters much more critical, hence lucrative in an ML IP. In fact, even if the adversary has access to the hyperparameters, it might still not be able to train the model without investing in the training data set, which is usually not free, or in the compute resources such as a GPU farm. Our work provides confidentiality for the parameters. Hence, the proposed defense's goal is to ensure that no information about parameters is leaked during any intermediate computation through a first-order power/EM-based side-channel attack. Therefore, the proposed masking scheme masks all intermediate computations and not just, say, the first and last layer. Although this may be another viable option (as in masking the first and last round of AES [SP06]) to reduce masking overheads, recent works have shown that deeper computations can be targeted with ever-evolving attacks [BBH+19].

We analyze binarized neural networks (BNNs) [CB16]. Following prior works on protecting ML hardware [DCA20b, DCA20a], our hardware implementation is constant-time/flow, making it immune to other side-channel attacks such as timing or the access-pattern based [HZS18]. Our design stores all the parameters of the model in the on-chip FPGA block RAMs. Therefore, the hardware implementation is also immune to any memory-based side-channel attacks. We exclude invasive attacks like voltage/EM fault-injection attacks in our threat model [BJH<sup>+</sup>21, TG20]. We also exclude template/profiled attacks for this work.

# 3 Background

In this section, we establish the notation that we utilize throughout the paper for ease of understanding. We also introduce the basics of neural networks, BNNs, and hardware masking. These fundamentals would serve as the groundwork for the reader in understanding our proposed methods in future sections.

#### 3.1 Notation

We denote vectors  $\mathbf{x}$  with lowercase bold, individual elements of the vectors with italicized subscripts  $x_i$ , matrices  $\mathbf{X}$  with uppercase, bold roman letters, and matrix elements  $x_{i,j}$  at position i, j, where i and j correspond to the row and column also with italicized subscripts. Every scalar x is non-binary unless explicitly stated as  $x \in GF(2)$ . We use bracketed subscript  $x_{[i]}$  to index the  $i^{th}$  bit of a scalar x, bar on the top  $\overline{x}$  to represent a bit-wise inverse, superscript  $x^i$  to refer to the  $i^{th}$  share of a masked variable x, calligraphic fonts  $\mathcal{O}$  to denote sets, and typewriter font F(.) to denote functions. We use braces in superscript  $w_{i,j}^{\{k\}}$  to index the variables in different layers of the neural network.

We denote a multiplexer function in hardware design sections as  $\mathtt{MUX}(.)$ , which is defined as follows.

$$\mathtt{MUX}(a,b;s) = \begin{cases} a, & s = 0 \\ b, & s = 1 \end{cases}$$

Modulo operation  $x \mod K$  is defined as  $x \mod K \triangleq x - K \left\lfloor \frac{x}{K} \right\rfloor \in [0,K)$ . We always use the letter K to denote the modulus. We define  $\mathtt{DOM}(.)$  (a type of masked AND gate) as  $\mathtt{DOM}(a^1,a^0,b^1,b^0,r) = (c^1,c^0)$  where  $\bigoplus_i c^i = a \cdot b$ ,  $\bigoplus_i a^i = a$ , and  $\bigoplus_i b^i = b$ .  $a^i,b^i,r \in GF(2) \forall i$  and r is a fresh and uniformly sampled bit. The  $\oplus$  and  $\cdot$  symbols represent the bitwise exclusive-OR and AND operations, respectively.

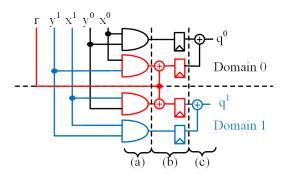

**Figure 1:** The design of a first-order pipelined DOM-indep multiplier [GMK16]. The components in black and blue belong to domains 0 and 1 respectively. The red colored components represent the cross-domain terms. (a), (b), and (c) refer to the *calculation*, resharing, and compression steps, respectively.

# 3.2 Hardware Masking for Side-Channel Security

Basics of Masking. Masking is a side-channel countermeasure that splits the secret variable into multiple, statistically independent shares and transforms the original function to work on these shares independently. In a d-th order masking scheme, the secret x is commonly split into d+1 shares  $x^0, x^1, \cdots x^d$  such that  $x=\bigoplus_i x^i, 0 \leq i < d+1$ , and  $\bigoplus$  is an addition in the field. The d shares  $x^0 \cdots x^{d-1}$  can be sampled uniformly and the  $(d+1)^{th}$  share can be created as  $x \oplus (\bigoplus_i x^i), 0 \leq i < d$ . This type of masking is typically called arithmetic masking for non-binary numbers. In GF(2), the additions become exclusive-OR and masking is commonly called Boolean masking. It is efficient to use arithmetic masking to mask arithmetic operations and Boolean masking to mask Boolean operations. Prior work on multiplicative masking of AES demonstrates the efficiency of such implementations [DRB18].

The most critical requirement for a masking scheme is to always keep the shares separated during computations. This is hard to achieve in practice due to glitches that can temporarily recombine the shares and leak the secret [MPO05]. Glitches can be reduced by inserting registers on data paths involving multiple shares [AGM<sup>+</sup>09]. Threshold Implementation (TI) is a theoretical solution to address the issue of glitches by enforcing the (non-completeness) property that none of the intermediate computations (a.k.a., component functions) involve manipulating all the shares of a secret simultaneously [NRR06]. A  $d^{th}$  order TI typically requires td+1 shares, where t and d are the algebraic degree of the function and the protection order, respectively. Some follow-up works tried to provide security in the presence of glitches using only d+1 shares [DRB<sup>+</sup>16, GMK16].

**Domain Oriented Masking.** Figure 1 shows a first-order secure DOM-indep multiplier, which assumes the inputs to be independent [GMK16]. The key idea behind DOM is to ensure that in a  $d^{th}$  order masked circuit that is split into d+1 independent circuits, each circuit only processes at most one share per secret variable. Each share index is associated with a so-called *domain*. A circuit that only receives one share per secret variable cannot leak the secret because every secret share is independent of the secret variable. A cross-domain term introduced due to a non-linear function can potentially leak the secret. Linear functions are affine, thus easy to mask without additional randomness. Figure 1 shows the three steps of a DOM-indep computation. The *calculation* step (a) computes all the partial products, the *resharing* step (b) integrates the cross-domain terms into the primary domains by remasking with a random bit r, and finally, the *compression* step (c) combines the terms into two output shares to prevent the otherwise unnecessary

increase in the number of domains. A register at the end of *resharing* step prevents any glitches to propagate to the *compression* step. We choose DOM instead of TI for this work because it provides security in presence of glitches using only uses d+1 shares and because of its widespread adoption in recent masking literature [FBR<sup>+</sup>21, ABP<sup>+</sup>18]. We discuss some more optimized alternatives in Section 10.

**Theoretical Attack Models.** The early research on hardware masking was missing a theoretical framework to model a side-channel adversary capabilities and the properties of the target platform. Thus, it was difficult to provide concrete security guarantees for a newly proposed masking scheme. Ishai *et al.* provided for the first time a theoretical framework to evaluate side-channel countermeasures, which is better known as the *t-probing model* [ISW03]. In this model, the adversary can observe the values of at most *t* wires in the masked circuit; the circuit is said to be secure if and only if the value on each of the t wires can be simulated using *only* randomness.

The t-probing model is a good starting point but it does not model the physical faults in hardware like glitches, transitions and coupling, which can potentially lead to side-channel leakages [MPO05]. Hence, the t-probing model was extended to the robust-probing model by Faust et al. [FGP+18], which also models physical faults in hardware. One of the key ideas in the robust-probing model was to use the so-called glitch-extended probes first introduced by Reparaz et al. [RBN+15]. These probes leak the value of not only the probed wire but all the wires in the fan-in until the last synchronisation point.

### 3.3 Neural Networks

Neural networks are a class of ML algorithms used for predictive modeling of data that have recently gained popularity due to their ease of use and effectiveness. They model an unknown function by analyzing a set of known data points (called the training dataset) and make predictions on new data (called the test dataset) using the modeled function.

A neural network consists of multiple neurons organized in layers working in a feed-forward fashion where one layer takes inputs from the previous layer, applies a series of operations, and feeds the outputs to the next layer. The fundamental unit of a neural network is called neuron. A network in which each neuron in a layer is connected to all the neurons in the next layer is often called a multi-layer perceptron (MLP). The layers in an MLP are intuitively termed as fully-connected (or dense) layers. Neurons multiply their inputs with layer weights and pass the sum to an activation function. Each incoming connection of a neuron has a weight value associated with it. The neuron performs a weighted summation of the inputs and computes the probability using a non-linear function like sigmoid, rectifier linear unit (ReLU), etc. Operations of all neurons within each layer can be condensed using matrix representation as

$$\mathbf{y} = \sigma(\mathbf{x} \cdot \mathbf{W} + \mathbf{b}),$$

where  $\mathbf{x}$ ,  $\mathbf{W}$ , and  $\mathbf{b}$  are input feature, layer weight and bias tensors, respectively. Feature vector,  $\mathbf{x} = \{x_m\}$ , for  $m \in \mathbb{N} \cap [1, M]$ , denotes the representations input to a layer, where M is the size of feature vector. Weight matrix,  $\mathbf{W} = \{w_{m,n}\}$ , and bias vector,  $\mathbf{b} = \{b_n\}$ , for  $n \in \mathbb{N} \cap [1, N]$ , represent the learned parameters of the layer, where N is the number of nodes in the layer. The connection weight matrix,  $\mathbf{W}$ , is calibrated during the training phase by feeding inputs and their corresponding labels, also known as ground truth data, to the network and using a method called backpropagation to iteratively revise the weights such that the network starts predicting the correct labels [Lin76]. Thus, the weights are crucial in deciding the model accuracy and hence the most lucrative target in an ML model extraction, which should be protected against side-channel attacks. Similar to weights, other parameters, like bias vectors,  $\mathbf{b}$ , and Batch-normalization (BN) [IS15] parameters

are also computed during training and stored offline for inference. BN is applied to the output of neurons of the layers of the neural network as a form of normalization of layer outputs.  $\mu$ ,  $\sigma$  are the mean and standard deviation of the neuron outputs and  $\gamma$ ,  $\beta$  are learnable parameters and are used to shift the mean and standard deviation, respectively. BN parameters are less critical compared to weights of a neural network but they may also be kept confidential.

Given the fact that the layers of neural networks are stacked together with the outputs of one layer being used as the inputs of the next layer, the distribution input to each layer may change with each successive layer, causing the learning algorithm to continuously chase a moving target. Batch-normalization (BN) is a form of standardization used to homogenize the distribution fed to each layer. BN significantly reduces the training time and stabilizes the training by normalizing inputs to each layer [IS15]. Given its wide ranging benefits from allowing training deeper networks to accelerated training, BN is one of the core fundamental operations utilized in neural networks.

Convolutional Neural Networks Fully-connected (FC) layers have several limitations that hamper the scalability and computational efficiency. First, the number of parameters keep increasing with the number of input features, which is a problem if the dataset has a lot of features (e.g., high-resolution images). Second, connecting all the previous layer neurons to the next layers neurons may lead to overfitting of data because every pixel acts as an input feature to every neuron of the next layer. Furthermore, fully-connected layers do not exploit spatial correlation between pixels of input images since each pixel is connected to every other pixel in the image with equal importance. A convolutional (conv) layer addresses these problems by processing smaller regions of the image called the receptive fields to compute the output features [FMI83, LHBB99]. It preserves the spatial relations between different parts of an input image and summarizes the features in a concise manner owing to the small receptive fields. It exploits the fact that each pixel and its neighborhood are semantically linked and meaningful. Furthermore, it also promotes translational invariance: the same object can appear anywhere within the image. The number of parameters in a conv layer does not increase with increasing input features, and unlike FC layers, only a subset of input features contribute to an output feature.

Every conv layer has a set of tensors called *kernels* that it uses to perform an inner product with the shifting receptive fields in the input image. The inner product operation is commonly called *convolution*. If we denote the input and output tensors of the convolution layer as  $\mathbf{X}$  and  $\mathbf{Y}$ , respectively, then the element at position (p,q,r) in  $\mathbf{Y}$  is computed as

$$Y_{p,q,r} = \sum_{i=1}^{n_h} \sum_{j=1}^{n_v} \sum_{k=1}^{n_i} X_{p+i,q+j,k} \times K_{i,j,k,r},$$

where  $n_h$ ,  $n_v$ , and  $n_i$  are the width, height, and depth of the kernel respectively. ConvNets are commonly seen in computer-vision applications. The kernels are learned through training and thus, should remain confidential.

Conv layers are usually followed by a pooling layer that aims to downsample the output retaining only important features. This helps to regularize the data and prevent positional dependence of the detection, i.e., the network detecting a certain feature only if it is present at a specific location. Two common ways to pool the data are either selecting the maximum (a.k.a, maxpool), or computing the average (a.k.a. avgpool). We choose to implement maxpool for our work because it is hardware-friendly for BNNs [UFG<sup>+</sup>17].

ConvNets gained popularity after AlexNet [KSH17], a deep ConvNet that demonstrated remarkable results on the ImageNet dataset, the largest computer-vision benchmark, at the ImageNet Large Scale Visual Recognition Challenge (ILSVRC) 2012 [RDS+15]. Since then, ConvNets are considered the de-facto set of algorithms for visual perception tasks

and are extensively utilized in a huge number of applications including self-driving vehicles, autonomous robots, and unmanned aerial vehicles (UAVs).

**Binarized Neural Networks.** The weights and activations in a typical neural network are 32/64-bit floating-point (FP) numbers with high storage and computational needs. Thus, such networks are not suitable for resource-constrained edge devices with low-power and storage requirements. To reduce the memory footprint and computation costs, quantized neural networks with low-precision parameters have been proposed [HCS<sup>+</sup>17].

BNNs [CB16] use binary weights and activations, and are a natural progression in extreme quantization to reduce the compute and memory footprints of deep neural networks (DNNs). They utilize bit-wise arithmetic operations such as XNOR-POPCOUNT (XP), which are extremely efficient compared to matrix multiply-accumulate operations in high-precision DNNs. XP on a BNN layer  $\boldsymbol{l} = [a_0, a_1, \cdots a_{N-1}]$  with binary features  $a_i$  is defined as

$$\mathtt{XP}(\boldsymbol{l}) = 2 \times \sum_{i=0}^{N-1} (w_i \overline{\oplus} a_i) - N,$$

where  $\times$  and  $\overline{\oplus}$  are multiplication and XNOR operations, respectively.

Prior works have demonstrated the computational efficiency of XNOR-POPCOUNT based arithmetic operations in DNNs. For instance, a GPU kernel exploiting the XNOR-POPCOUNT operations can achieve  $23\times$  faster matrix multiplication compared to a naive baseline implementation [CB16]. The designed kernel is  $3.4\times$  faster than cuBLAS and the MLP runs  $7\times$  faster using the XNOR-POPCOUNT kernel compared to the baseline. Big companies like Xilinx, Intel, and Apple are investing heavily in BNNs due to these advantages [UFG+17, KCS+20, Tec20]. Owing to their low memory footprint and lightweight nature of operations, BNNs are considered attractive for edge applications such as FPGA-accelerators [FZS+19], cryptographic neural network inference systems [LWYY20], and for designing low-bitwidth ConvNets [ZWN+16], among many other applications.

Despite their low-bitwidth operations, the accuracy obtained by BNNs is comparable to that obtained by full-precision neural networks. For instance, [ZWN<sup>+</sup>16] found the accuracy loss of a BNN-ConvNet with 1-bit weights and activations to be less than 0.5% compared to a full-precision ConvNet with seven convolutional layers and one dense layer, evaluated on the Google Street View House Number (SVHN) dataset. Similarly, [LZP17] achieved less than 5% accuracy loss on the ImageNet dataset [DDS<sup>+</sup>09], a challenging dataset notorious for its complexity in the computer vision community, using a ResNet-like network built entirely using binary convolution blocks, compared to a full precision network.

BNNs apply constraints on both weights and activations such that each element of these matrices is either +1 or -1, during both training and at run-time. This is achieved by applying a binarization function, either deterministic or stochastic, to both weights and activations before they are utilized in linear layer arithmetic. In this work, we utilize the deterministic binarization function, sgn(x), to facilitate our discussions due to its simplicity of implementation in hardware and comparable accuracy to its stochastic counterpart. Following equation describes the deterministic binarization function.

$$\operatorname{sgn}(\mathbf{x}) = \begin{cases} 1, & \text{if } x \ge 0\\ -1, & \text{otherwise} \end{cases}$$

(1)

While forward pass uses binarized weights and activations, the gradients computed during training are real-valued to allow Stochastic Gradient Descent (SGD) to calibrate the weights in small, iterative steps. Gradient Descent algorithm tries to find the minimum of the loss function using its gradient. The algorithm starts at an arbitrary point of the

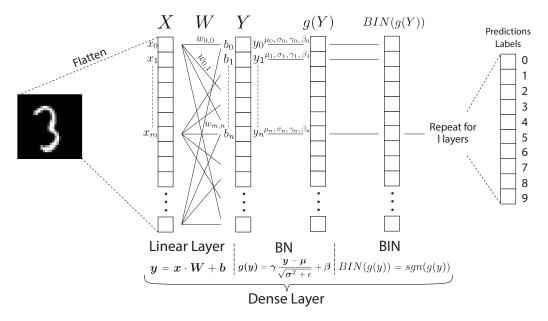

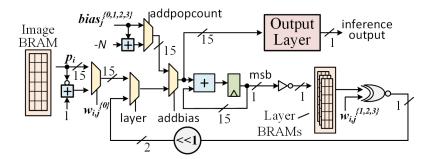

**Figure 2:** Baseline BNN-MLP dense layer architecture. Note that the last layer does not use the activation function to generate continuous score values.

objective function and computes its gradient with respect to each feature. The parameter value is updated in small steps according to the calculated gradient values at each step, leading to zero gradient. SGD is utilized to reduce the computations that baseline gradient descent needs for calculating the derivatives. The baseline gradient descent algorithm needs to compute the derivatives with respect to each feature for all data points. For large datasets, this is infeasible and makes the gradient descent algorithm too slow. Hence, SGD solves this problem by randomly picking only one data-point from the dataset to compute the gradients, therefore 'stochastic'. Although this significantly reduces the total number of computations to reach the minima, the path taken to reach this minima becomes more noisy due to the random data-points. But this does not matter as long as the algorithm does converge to the minima in lesser training time.

While the binarized activation function  $\operatorname{sgn}(x)$  is simple to implement, its gradient is zero for almost all values of x. Hence, the loss function gradient with respect to the activation function output will be zero, and the network will not learn. To counter this issue, Bengio  $\operatorname{et} \operatorname{al}$ . proposed a straight-through estimator for propagating gradients through the neurons [BLC13] as

$$g_x = g_q \mathbf{1}_{|x| \le 1},$$

where  $g_x = \frac{\partial L}{\partial x}$  denotes the gradient of loss function with respect to x. A straight-through estimator sets the input gradients equal to the output gradients, discounting the slope of the sgn(x) activation function altogether [CB16]. Simultaneously, it constrains the real-valued weights to [-1, +1] after each weight update during training since large magnitudes of weight values significantly worsen the performance. High-granularity input features are needed in the first layer in order for the network to be able to distinguish between them. Hence 8-bit input features are utilized for the first layer, while the rest of the layers use binarized features.

Baseline BNNs with deterministic activation function achieve 99.04% and 88.60% accuracy on MNIST and CIFAR-10, respectively. In comparison, [BIL<sup>+</sup>15] achieved 98.65% accuracy on the MNIST dataset using both binary weights and activations during

515

training. Using only binary weights and full precision activations, [CBD15] achieved an improvement of only 1.5% accuracy on CIFAR10 and reduction of 0.33% on MNIST. These examples demonstrate the comparable accuracy of BNNs despite their significantly lower memory and compute footprints compared to higher precision networks. Figure 2 shows the dense layer architecture of a baseline BNN-MLP. The architecture is similar to that of a generic MLP where a linear layer is followed by normalization followed by an activation function. However, BNN dense layers utilize binary  ${\bf x}$  and  ${\bf W}$  and an  ${\bf sgn}(.)$  activation function.

The Sign Bit Leakage Problem in Masked BNNs. Regular BNNs with integer additions leak via the sign bit in arithmetic masking because the output sharings are non-uniform [DCA20b]. The discussed vulnerability does not happen in modular arithmetic as there is no sign bit; the modulo operation wraps around the result if it is out of bounds. We propose a radically different approach at the algorithmic level that changes the arithmetic of neural networks from integer to modular and defines the inference operations with the new arithmetic from the ground up.

# 4 ModuloNET: Binary Networks with Modular Arithmetic

The sign-bit leakage problem has motivated us to explore neural network inference in modular arithmetic. Thus, we develop a neural network architecture in which all the integer additions are replaced with modular additions (mod K). To our best knowledge, this is the first paper that utilizes modular arithmetic directly during neural network inference<sup>2</sup>.

# 4.1 BNNs and Modular Arithmetic: Challenges

BNN inference has four major issues when layer arithmetic is moved to modular arithmetic.

- 1. Modulo operation entails loss of information and sudden changes in representations due to overflows.

- 2. Baseline binary activation function,  $\operatorname{sgn}(\cdot)$ , no longer stays feasible. For feature vector  $\mathbf{x}$  where  $\mathbf{x} = \{x_m\}$  for  $m \in \mathbb{N} \cap [1, M]$ , and M is the size of input vector, if  $x_m$  lies in a mod K, then

$$\operatorname{sgn}(x_{\mathbf{m}}) = \operatorname{sgn}(K) \ \forall \ m \in \mathbb{N} \cap [1, M] \tag{2}$$

Hence, activations of all layers are tied to a constant, sgn(K).

- 3. Application of BN becomes challenging. Modulo operation shifts the negative activations to the positive side (see Figure 3). Thus, BN cannot normalize the mean and standard deviation of the activations to a Gaussian distribution centered around zero anymore.

- 4. Modulo folding causes negative output scores of the last layer to wrap around. This results in wrong predictions to have high confidence scores (see Figure 3 (c)-(d)).

We analyze these issues and propose modifications to the baseline binary dense layer architecture that allow successfully operating with modular arithmetic in inference.

In supervised representation learning with regular arithmetic, the network automatically discovers its internal features during the training process. The operations of the neural

$<sup>^2</sup>$ Homomorphic encryption too uses modular arithmetic but does not directly apply such computations; instead it converts regular operations to homomorphic ones—Section 10 elaborates on the similarities and differences of our approach compared to the homomorphic encryption.

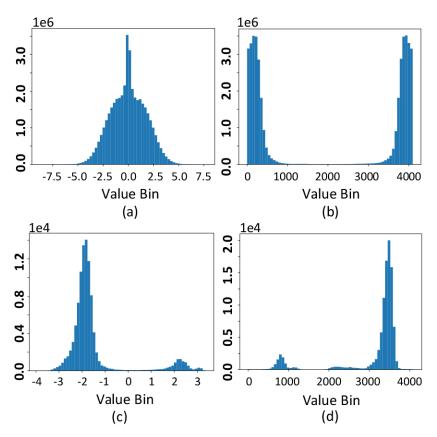

network are unconstrained in terms of representation range. However, constraining the inputs of the activation function in a feed-forward network to a modular domain during inference reduces the accuracy of the network since the modulo operation results in loss of information as highlighted in challenge 1. Figure 3 (a) shows the histogram distribution of output features,  $\mathbf{g}(\mathbf{y})$ , of the third layer of a baseline binarized MLP trained for MNIST. Figure 3 (b) shows the histogram distribution of output features of the same layer when the output of the dense layer is restricted to mod K where K=4096. Intuitively, reducing this representation space increases the information loss due to overflows and underflows of the feature representations with modular arithmetic.

Furthermore, in an unsigned finite domain K>0, the network loses the capacity to represent negative activations, which are fundamental to the functionality of BNNs, highlighted in challenge 2. Equation (2) illustrates that the usual activation function  $\operatorname{sgn}(.)$  cannot work with  $\operatorname{mod} K$  and requires modifications. Applying the constraint of modular arithmetic also reduces the effectiveness of BN (challenge 3) since modular arithmetic causes sudden changes in values for some activations, while leaving others completely unchanged, and BN operation does not accommodate these anomalies.

In the last layer, the negative scores output from the network wrap around because they underflow the representation range as identified in challenge 4 and illustrated in Figure 3 (c) and (d). This results in wrong predictions with high confidence because baseline neural networks use higher scores to represent high confidence predictions. Plot (c) shows the final layer output of a baseline BNN trained on MNIST. Value bins with high positive values represent correct classifications with high confidence, while those with high negative scores represent the wrong classifications with high confidence. Plot (d) shows the final layer output after applying mod 4096: high confidence wrong classifications are folded over and incorrectly classified by the network as correct with high confidence.

# 4.2 Proposed Layer Architecture

We propose modifications to the baseline dense layer architecture, whose output empirically follows the output of dense layers in baseline BNNs, however, for offline inference, the layer operations are constrained to modular arithmetic. To achieve this, BN can be fused into the preceding linear layer using a simple composition [YN17]. But to maintain binary XNOR-based multiplications between the feature vector  $\mathbf{x}$  and weight matrix  $\mathbf{W}$ , and integer additions of bias vector  $\mathbf{b}$ , the proposed architecture needs to ensure that the re-parametrization of learned parameters does not lead to non-binary weights and non-integer biases. Specifically, for the linear operation  $\mathbf{y} = \mathbf{x} \cdot \mathbf{W} + \mathbf{b}$ , the layer needs to ensure that  $\mathbf{W}$  and  $\mathbf{b}$  tensors maintain their data-types (i.e., binary and integer) during the re-parametrization to allow efficient hardware implementation and masking.

Baseline BNNs use integer biases in their linear layer but since we re-parametrize the layer to fuse the BN operation, the bias values are modified with the BN parameters. We use vanilla BN:  $\mathbf{g}(\mathbf{y}) = \gamma \frac{\mathbf{y} - \boldsymbol{\mu}}{\sqrt{\sigma^2 + \epsilon}} + \boldsymbol{\beta}$  in our experiments which generates floating point results during training.  $\boldsymbol{\mu}$ ,  $\boldsymbol{\sigma}$ ,  $\boldsymbol{\gamma}$ ,  $\boldsymbol{\beta}$ , are the mean, standard deviation, scale, and shift parameter vectors of the BN operation, respectively,  $\boldsymbol{\epsilon}$  is a small constant to prevent division by zero, and  $\mathbf{y}$  is the linear layer output vector. We can absorb these learned parameters offline to obtain a more concise and linear, multiply-accumulate based BN operation as  $\mathbf{g}(\mathbf{y}) = \boldsymbol{\psi}\mathbf{y} + \boldsymbol{\phi}$  where  $\boldsymbol{\psi} = \frac{\boldsymbol{\gamma}}{\sqrt{\sigma^2 + \epsilon}}$  and  $\boldsymbol{\phi} = \boldsymbol{\beta} - \boldsymbol{\psi}\boldsymbol{\mu}$  are the absorbed BN parameter vectors, computed offline after training. We propose a mod K-aware binary activation function based on the shape of the feature map distribution input to the function:

$$BIN(z) = -sgn\left(z - \frac{K}{2}\right) \tag{3}$$

This activation function shifts the activation decision boundary from z = 0 in vanilla

Figure 3: The histogram of feature maps before binarization for (a) third hidden layer, (c) output layer, for baseline MLP, and (b) third hidden layer, and (d) output layer, for ModuloNET MLP, using 64 bins. Activations are obtained using feed-forward run of the networks on the entire MNIST test split. Vertical axis shows the number of occurrences of activation values in the bin while horizontal axis shows the histogram bins.

BNNs to  $z = \frac{K}{2}$ , the center of the distribution in the mod K. The negative sign undoes the impact of modulo on the negative outputs of the  $\mathtt{BN}(\mathtt{Linear}(\cdot))$  composition, which causes all output feature values  $g(\mathbf{y}) < 0$  to fold, where K > 0. Empirically, our activation function allows the layer to 'undo' the modulo-introduced folding and generate an output activation distribution similar in shape to that obtained in baseline BNNs.

To fuse the BN into the preceding linear layer by composition, we note that the input to the activation function lies in mod K:  $g(\mathbf{y}) \mod K = (\psi \mathbf{y} + \phi) \mod K$ .

Our proposed activation function from Equation (3) can be re-formulated as

$$BIN(z) = \begin{cases} 1, & \text{if } z \leq \frac{K}{2} \\ -1, & \text{otherwise} \end{cases}$$

Consider the case when the output of this activation is +1, i.e.,  $BIN(g(y_n) \mod K) = +1$ ,

$$\Rightarrow (\psi_n y_n + \phi_n) \bmod K \le \frac{K}{2} \tag{4}$$

The network applies the following constraint on the value of K

$$K \ge 2 \max(|\psi_n y_n + \phi_n| : n \in \mathbb{N} \cap [1, N]), \tag{5}$$

and ensures that the modulo operation is lossless. It can effectively reconstruct the unmodulated input  $\psi_n y_n + \phi_n$  after batch-normalization that allows it to later undo the modulo folding. Thus, although modulo operation causes loss of information in general, original signal can be reconstructed with high probability if K is chosen to be large such that the operation does not cause values to scramble after folding. Formal proof is given as follows.

**Lemma 1.** n-th signal element,  $\psi_n y_n + \phi_n$ , can be reconstructed from  $(\psi_n y_n + \phi_n)$  mod  $K \forall n \in \mathbb{N} \cap [1, N]$  with high probability conditioned on occurrence

$$O_n \triangleq \left\{ \psi_n y_n + \phi_n \in \left[ -\frac{K}{2}, \frac{K}{2} \right] \right\} \tag{6}$$

*Proof.* Let  $z_n = (\psi_n y_n + \phi_n) \mod K$ . Also let

$$\tilde{z}_n = \left(z_n + \frac{K}{2}\right) \mod K - \frac{K}{2} \tag{7}$$

As probability  $Pr(O_n) \to 1$ , it can be seen from (7) that  $\tilde{z}_n \to \psi_n y_n + \phi_n$ , which corresponds to approximate regeneration of the original signal element. Furthermore, from Equation (6),  $Pr(O_n) = Pr(|\psi_n y_n + \phi_n| \le \frac{K}{2})$ . Considering the case of totally lossless modulo folding of the n-th signal element, i.e.,  $Pr(O_n) = 1$ , this is only possible if  $|\psi_n y_n + \phi_n| \le \frac{K}{2}$ .

Extending this to lossless regeneration of all N signal elements, that is

$$Pr(O_1) = 1, Pr(O_2) = 1, ..., Pr(O_N) = 1$$

(8)

We know that if  $Pr(O_i) = 1$  for i = n which produces  $\max(|\tilde{z}_n| : n \in \mathbb{N} \cap [1, N])$ , then in order for Equation (8) to be true, the following must hold

$$\max\left(|\psi_n y_n + \phi_n|: n \in \mathbb{N} \cap [1, N]\right) \leq \frac{K}{2}$$

This is the same result as Equation (5) which corresponds to lossless modulo folding of the signal. Hence, original signal elements,  $\psi_n y_n + \phi_n$ , can be unwrapped from the modulo-folded signal elements,  $z_n$ , using Equation (7), under the condition that K is selected using Equation (5).

Hence, under the constraint enforced by Equation (5) and for the case of BIN(g) = +1, we can rewrite Equation (4) as  $\psi_n y_n + \phi_n \ge 0$ . We modify the training process to apply the constraint  $Clip(\gamma)$  to be between 0 and  $+\infty$ . This enforces the  $\psi > 0$  constraint on Equation (4) and results in

$$y_n \ge -\frac{\phi_n}{\psi_n}$$

$$\sum_{i=1}^M x_i w_{i,n} + b_n \ge -\frac{\phi_n}{\psi_n}$$

$$\sum_{i=1}^M x_i w_{i,n} + b_n + \frac{\phi_n}{\psi_n} \ge 0$$

A similar analysis can be done for BIN(z) = -1 to show that when the activation output is -1, then,  $\sum_{i=1}^M x_i w_{i,n} + b_n + \frac{\phi_n}{\psi_n} < 0$ . Hence, for the case of BIN(z) = +1, the value  $\sum_{i=1}^M x_i w_{i,n} + b_n + \frac{\phi_n}{\psi_n} \geq 0$ , and less than 0 otherwise. In mod K, the activation function gets the composition BN(Linear(.)) as an input, given by  $\left(\mathbf{x} \cdot \mathbf{W} + \mathbf{b} + \frac{\phi}{\psi}\right) \mod K$ .

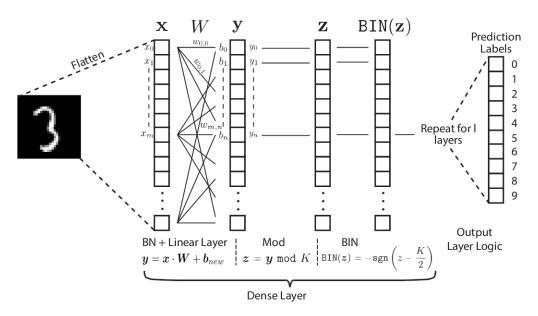

**Figure 4:** ModuloNET dense layer architecture for inference. The output of the last layer is processed using a more complex logic given by Algorithm 1.

Given both **b** and  $\phi$ ,  $\psi$  vectors are available offline after training, we re-parametrize bias vector as  $\mathbf{b}_{new} = \mathbf{round}(\mathbf{b} + \frac{\phi}{\psi})$ . This means that BN operation is absorbed into the preceding linear layer, using re-parametrization of the bias vector **b**. Round operation  $\mathbf{round}(\cdot)$  allows  $\mathbb{R} \to \mathbb{Z}$  mapping of biases, enabling integer addition of bias vector in hardware. Since **W** matrix does not change as a result of the re-parametrization, we can still use XNOR-multiplication in hardware. Layer architecture for inference with fused BN is shown in Figure 4.

# 4.3 A Note on Enforcement of Constraints

We applied two constraints when designing the modified dense layer architecture for ModuloNET, 1) Constraint on size as  $K \geq 2 \max(|\psi_n y_n + \phi_n| : n \in \mathbb{N} \cap [1, N])$ , and 2) Constraint on BN parameter  $\gamma$  during training,  $\text{Clip}(\gamma, 0, +\infty)$ . The empirical evaluation of these constraint's impact is as follows.

For the first constraint, note that choosing the modulus K becomes a challenge as the size is dependent on the components of the feature vector  $\mathbf{y}$ . Choosing an arbitrarily large K solves the issue but is sub-optimal given size K directly translates to the amount of randomness needed for hardware masking that we discuss in the Sections 6 and 7. However,  $\mathbf{y}$  is implicitly batch-normalized by the linear layer due to the re-parametrization of bias vector  $\mathbf{b}_{new}$  meaning smaller arbitrary K could be chosen, but the process of choosing K arbitrarily is not scalable for networks with large number of layers. For our network, we choose K based on the range of  $\mathbf{y}$  distribution of an infinite domain network,  $mod \infty$ , allowing us to find the smallest K values of each layer, leading to a more optimal design. This requires training the baseline BNN from scratch in infinite domain to extract the  $\mathbf{y}$  distributions. Future works could explore the possibility of making K a trainable parameter, removing the explicit dependency of the size on  $\mathbf{y}$ .

For the second constraint, representation learning handles  $\gamma$  well, as the rest of the BN parameters are unconstrained. Based on the fact that the accuracy results of our network with constrained  $\gamma$  are found to be similar to those without the constraint, we predict that the network negates the constraint on  $\psi$  using the freedom of calibration of the rest of the

#### Algorithm 1 Output Layer Functionality in ModuloNET

```

1: procedure CLASSIFY(\mathbf{z}, N, label)

input: z = z_0, z_1, z_2, ..., z_{N-1} N = num \ classes

output: predicted label

label \ local \leftarrow -1

label\_global \leftarrow -1

3:

local\_max \leftarrow -1

4:

global\_max \leftarrow -1

5:

for i = 0 \cdots N - 1 do

6:

if (z_i > local\_max) then

7:

if z_i < \frac{K}{2} then

8:

local\_max \leftarrow z_i

9:

label \ local \leftarrow i

10:

if (z_i > global\_max) then

11:

global\_max \leftarrow z_i

12:

label\_global \leftarrow i

13:

if local\_max \neq -1 then

14:

return\ label\_local

15:

16:

return label_global

17:

```

parameters such as those in  $\phi$ , allowing the network to perform just as well as without this constraint.

# 4.4 Tuning First and Last Layers

Baseline BNN uses non-binary feature map inputs because a higher granularity of input feature map data is crucial for the network to learn appropriate representations. It also normalizes the 8-bit unsigned input pixels to floating point values in the range [-1, +1]. However, our proposed architecture with modular arithmetic casts the 8-bit unsigned integers to a signed representation in the range [-128, 127]. Furthermore, it utilizes a larger K for the first layer since non-binary feature map inputs increase the size required to ensure lossless modulo folding.

Given the fact that the modulo operation makes the domain unsigned for K>0, the output of the final layer has to be processed differently than the conventional  $\max(\text{scores})$  approach to map the scores to the correct labels. Figure 3 (c) and (d) show that under the constraint  $K \geq 2 \max(|\psi_n y_n + \phi_n| : n \in \mathbb{N} \cap [1, N])$ , all activations that would be less than 0 in an infinite domain BNN reside between  $\frac{K}{2}$  and K in the  $\mod K$  domain due to folding. Hence, to recover the correct score output of the final layer, the network utilizes a more complex logic to find the score-to-output mapping. Our output layer algorithm to find the correct class, given the last layer node scores, is given in Algorithm 1. This algorithm finds the maximum score below the  $\frac{K}{2}$  threshold, called  $local\_max$ , and the global maximum score, called  $global\_max$ . Label corresponding to  $local\_max$  is returned if this max exists, otherwise, the global label is returned.

## 4.5 Choice of modulo K

As detailed in Section 4.2, ModuloNET dense layer architecture depends on careful selection of an additional hyper-parameter, the value of modulo K. The constraint on K dictated by Equation (5) is needed to ensure lossless folding of modulo since if K is chosen to be too small, modulo folding would cause values to scramble leading to loss of data. The value of K is dependent on the size of data input to the layers of the neural network. BNNs utilize binary values of activations and weights in all layer computations, with the exception of

**Figure 5:** Error rate of MLP-MNIST vs value of modulo K used in the network. Each point represents one test configuration using the specified K in all layers (Decimal exponents are shown only for highlighting the error trend in software implementation, actual hardware implementation only uses integer exponents).

the first layer. The exception comes from the fact that the learned weights need to encode high bit-width information in at least the first layer in order for the network to learn the fine-grained pixel information [CB16]. Hence, a larger K is required for the first layer. Since our goal is to design a hardware block which is reusable for all the layers of the neural network, we select the same K value for all layers. Furthermore, since K denotes the data representation bit-width, we select K to be an exponent of 2. Figure. 5 shows the variation of error rate of ModuloNET with values of K on the MNIST dataset. The error rate becomes roughly asymptotic around  $K = 2^{14}$ , while achieving the lowest error rate at  $K = 2^{15}$ . Hence, we utilize  $K = 2^{15}$  in our hardware design as 15-bits are required to achieve the minimum error rate. The results in Figure. 5 are intuitive: lower the mod K, higher the likelihood of modulo folding causing values to scramble; the folding no longer stays lossless.

## 4.6 Extension to ConvNets

ConvNet layers utilize similar operations as those in MLP, with the added maxpool operation in some of the layers. While maxpool appears between the convolutional (conv) layer and the BN operation, to facilitate the fusion of BN into the conv layer biases, BN operation should directly follow the conv layer. We note that  $\mathtt{maxpool}(\mathtt{BN}(.))$  composition is permutation-invariant. Hence, pooling operation commutes with BN under the constraint  $\gamma > 0$ . Note from Section. 4.2 that we apply this constraint anyways using  $\mathtt{Clip}(\gamma, 0, +\infty)$  for fusion of BN, and that it does not impact the network accuracy due to the freedom of calibration of the rest of the BN parameters. Hence, the network swaps the positions of BN and maxpool to allow BN to appear after conv. Sub-sampling using maxpool before applying BN is beneficial for faster training, however, the fusion of BN into the preceding conv layer keeps the inference complexity unaffected.

We also move the maxpool operation after the binarized activation function to maintain consistency with the layer structure used in our MLP. In our network, maxpool is applied to binary pooling windows, returning +1 if any element of the window is +1 and generating

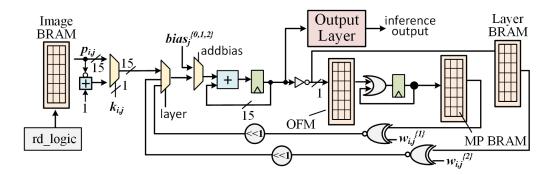

**Figure 6:** Hardware design of unmasked ModuloNET inference. The design accumulates the partial products in each cycle. It stores the inverted MSBs of the complete summation as the activations. For the output layer, it directly feeds the final summations to the output layer logic that computes the inferred label and its confidence score.

-1 if all components are -1. The re-parametrization of bias vector for fusion of BN is similar to that in the MLP, i.e.,  $\mathbf{b}_{new} = \mathtt{round}(\mathbf{b} + \frac{\phi}{2b})$ .

# 5 Baseline Hardware Design of ModuloNET

To obtain baseline hardware for our side-channel and overhead comparisons, we first design and implement an unmasked design of ModuloNET inference. It is an area-optimized, sequentialized hardware design for the MLP that performs one summation per cycle<sup>3</sup>. This allows the design to fit in our target FPGA and a direct comparison with earlier work [DCA20a]. The design has a throughput of 1 addition per cycle. For the following discussions, we denote the number of input pixels, hidden layer nodes, output layer nodes, and the modulus with L, M, N, and K, respectively. The design is parameterized for these values. The weights and activations are binary (i.e., -1 and +1 are represented as 0 and 1 respectively) and the bias value per node has a precision of  $log_2K$  bits.  $K = 2^{15} = 32768$  achieves the lowest error rate for our datasets. Thus, unless otherwise stated, all the weighted summations are performed in modulo 32768 and we omit the 'mod 32768' term.

## 5.1 Weighted Summations and XNOR-POPCOUNT

Figure 6 shows the hardware implementation of the weighted summations and XNOR-POPCOUNT. The image pixels and network parameters are loaded into a block RAM at the start of each inference. The hardware reads out the  $i^{th}$  input pixel  $p_i$  and the weight  $w_{i,j}^{\{0\}}$  that corresponds to the connection between the  $i^{th}$  input pixel and  $j^{th}$  hidden layer node (see Figure 4) from the respective block RAMs. It uses a multiplexer with binarized weight  $w_{i,j}^{\{0\}}$  as its select line, and the pixel  $p_i$  and its 2's complement  $(-p_i)$  as its data lines for the multiplication. It feeds the product to an accumulator. To perform the additions in  $mod\ K$ , we restrict the width of the accumulator data path to  $log_2K$  bits. The hardware feeds the sum of L partial products and  $bias_j^{\{0\}}$  to the activation function after L+1 cycles and saves the activation function outputs into layer BRAMs. For subsequent layer computations, the hardware reads the activation values  $a_i^{\{k\}}$  and weights  $w_{i,j}^{\{k\}}$  from the  $k^{th}$  layer and weight block RAMs and feeds them to the XNOR-POPCOUNT (XP) function defined in Section 3.3. XNOR is directly implemented on hardware using XNOR gates. To implement POPCOUNT, the hardware uses a left-shift operator to perform the

$<sup>^3</sup>$ One neuron computation with L input connections and a bias finishes in L+1 cycles.

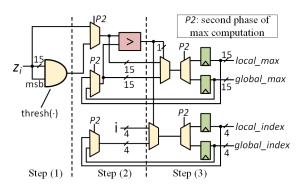

**Figure 7:** Hardware design of the unmasked output layer.  $z_i$  represents confidence score of the  $i^{th}$  node in the output layer.

multiplication by 2 and then adds -M along with  $bias_j^{\{k\}}$  in the last cycle of weighted summation for the  $j^{th}$  hidden layer node.

#### 5.2 Activation Function

The activation function in ModuloNET is given in Equation (3). To implement it on hardware, we reformulate the function  $-\operatorname{sgn}(x-\frac{K}{2})$ , where x represents the weighted sum, to a comparison of x with  $\frac{K}{2}$ . The hardware checks the MSB<sup>4</sup> of x to compare it with  $\frac{K}{2}$ . The final output is the inverse of MSB because of the negative sign in Equation (3).

# 5.3 Output Layer Max Function

Algorithm 1 presents the method to compute the final classification result and Figure 7 shows its hardware implementation. The hardware sequentially feeds each of the N confidence scores  $(z_i)$  to the output layer logic. The entire computation of the output layer happens in two phases corresponding to the  $local\_max$  and  $global\_max$  computations. First phase has three steps: (1) feed  $z_i$  to a comparator if it is below  $\frac{K}{2}$ , else feed a 0, (2) compare  $z_i$  with the value in  $local\_max$  register  $^5$ , and (3) update the  $local\_max$  register with  $z_i$  and the  $local\_index$  register with i if the comparator returns 1. Next, we sequentially describe the baseline hardware implementation of each step.

1. The hardware should return  $z_i$  if it is less than  $\frac{K}{2}$  (or equivalently if the MSB is equal to 0) and 0 if it is greater than  $\frac{K}{2}$  (or equivalently if the MSB is equal to 1). Thus, the function thresh(.) can be expressed as an AND of  $z_i$  and inverted MSB.

$$\mathtt{thresh}(z_i) = [z_{\lceil 14 \rceil}, z_{\lceil 13 \rceil}, \cdots, z_{\lceil 0 \rceil}] \odot [\overline{z_{\lceil 14 \rceil}}, \overline{z_{\lceil 14 \rceil}}, \cdots, \overline{z_{\lceil 14 \rceil}}],$$

where  $\odot$  is an element-wise AND operation. The design only requires  $log_2K - 1$  number of AND gates for this function because the MSB of the output is always 0.

- 2. The hardware feeds the thresholded confidence scores to a  $log_2K$ -bit comparator, which compares them with the stored value in  $local\_max$  register.

- 3. The design uses comparator output as a select for the multiplexer that either selects the value in  $local\_max$  or  $z_i$  to update the  $local\_max$  register. The  $local\_index$  register is also accordingly updated.

<sup>&</sup>lt;sup>4</sup>For any n-bit number, the MSB reveals if the number is greater or less than  $2^{n-1}$ ;  $K=2^n$ .

$<sup>^5</sup>$ Both  $local\_max$  and  $global\_max$  registers are initialized to zero at the start of the computation.

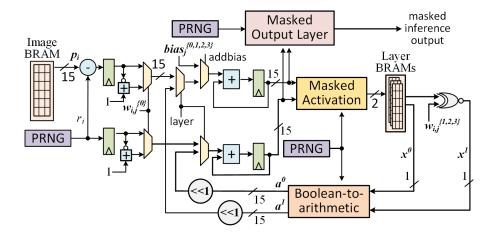

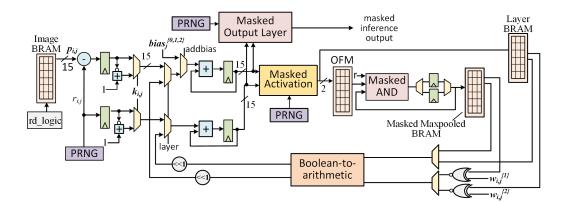

**Figure 8:** Hardware design of the fully masked ModuloNET inference showing various top-level masked components. The weights  $w_{i,j}^{\{k\}}$  and  $bias_j^{\{k\}}$  are read from the respective block RAMs. Figure is not to scale.

In the second phase, the hardware directly computes the max of N confidence scores  $z_i$  without thresholding. Thus, it directly executes the second and third steps to update the  $global\_max$  and  $global\_index$  registers. The hardware reuses the comparator for both phases by multiplexing the input of the comparator to either select  $thresh(z_i)$  or  $z_i$  based on the active phase of max computation handled by the control bit P2.

# 6 Fully Masked Hardware Design of ModuloNET

Figure 8 presents the overall hardware design of the first-order masked ModuloNET inference. The design follows the approach of the unmasked case where the hardware is sequentialized but it processes two shares in parallel. We suitably choose the masking style to be either Boolean or arithmetic based on the nature of operation to be masked for efficiency. We apply DOM with registered outputs for Boolean masking. Next, we describe the masking of all the major operations of the neural network.

# 6.1 Arithmetic Masking of Weighted Summations

Figure 8 shows the implementation of masked weighted summations using arithmetic masking because it is an arithmetic operation. The hardware reads  $p_i$  from the image BRAM, pads it to  $log_2K$ -bits, and splits it into two arithmetic shares  $p_i-r_i$  and  $r_i$ , where  $r_i$  is a  $log_2K$ -bit fresh random mask. Next, the hardware directly and independently computes the weighted summation on the two arithmetic shares. Finally, the hardware adds  $bias_j^{\{0\}}$  to one of the shares and sends both the shares to the masked activation function. The secret weights  $w_{i,j}^{\{k\}}$  remain hidden throughout the computation because the hardware combines it with randomized arithmetic shares before starting the computations.

Note that the secret in our model are the weights but we propose to mask the input pixels instead of masking the weights  $^6$ . Applying Boolean masking on the binary weights leads to more area overheads because the primary operation of weighted summation is arithmetic. In terms of security, since the adversary does not know the actual input  $(p_i - r_i)$

<sup>&</sup>lt;sup>6</sup>The process of randomizing the input is commonly known as *Blinding*—the inputs are unchanged but split into two shares. It preserves the functionality—still performs the same classification task.

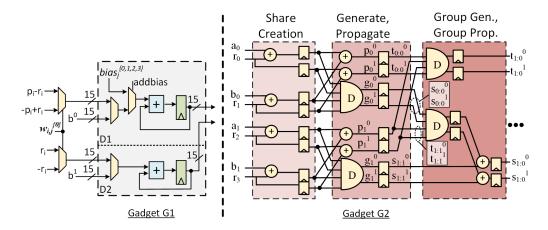

**Figure 9:** Hardware design of the masked activation function. A logarithmic carry chain propagates the carry using generate and propagate functions. AND gates are replaced with DOM-indep AND labeled as 'D'; we omit the masks in the figure to avoid clutter.

that gets multiplied by the secret  $(w_{i,j})$ , it cannot create a hypothesis on the intermediate computations for a first-order side-channel attack.

#### 6.2 Masked Activation Function

The activation function receives two arithmetic shares in the masked design and needs to compute if their sum is greater than or less than  $\frac{K}{2}$ , which depends on the MSB of the sum. Therefore, the hardware only needs to compute the MSB of the final summation in a masked fashion. A prior work solves this problem by implementing a masked LUT-based ripple carry chain to produce the two Boolean shares of the MSB [DCA20b]. However, such a design is good for applications where the security requirements are low; glitches can happen inside the LUTs and eventually reveal the secret [MPO05]. Prior literature suggests a number of alternatives such as Threshold Implementation [NRR06], DOM [GMK16], a synchronized variant of the Trichina's AND gate [DCA20a], etc., to perform masked operations with reduced glitches. We choose DOM for our design because it has low area and randomness requirements and provides a reasonable security against glitches<sup>7</sup>.

Figure 9 shows our proposed novel design of the masked activation function using DOM-indep AND gates for 8-bit operands<sup>8</sup>. We specifically use the DOM-indep multiplier instead of DOM-dep because we guarantee independent input sharings: the hardware creates fresh Boolean shares for the arithmetic share bits. The hardware needs to create Boolean shares of the input bits (of arithmetic shares) explicitly before feeding them into the masked AND gates because the logic to compute the carry is completely exposed in a gate-level masked design. The Share Creation block creates two Boolean shares for every bit of each arithmetic share.

Instead of adopting a linear ripple-carry design [DCA20b], we implement the carry chain of a Kogge-Stone adder [KS73] because it has a logarithmic latency. We only implement the data paths in the carry chain that are necessary to compute the MSB. We replace the AND gates in the logic with DOM-indep AND gates to mask the design; XORs being linear can directly process the two share domains independently. Level-0 of the tree produces the Boolean shares of carry-generate (g) and carry-propagate (p) terms. Following equations present the masked versions of g and p.

$$(g_i^1,g_i^0) = \mathtt{DOM}(a_{[i]}^1,a_{[i]}^0,b_{[i]}^1,b_{[i]}^0,r_a)$$

<sup>&</sup>lt;sup>7</sup>We discuss some alternative primitives in Section 10.

$<sup>^8\</sup>mathrm{We}$  show an illustration with 8-bits but the actual design has  $log_2K$ -bit operands.

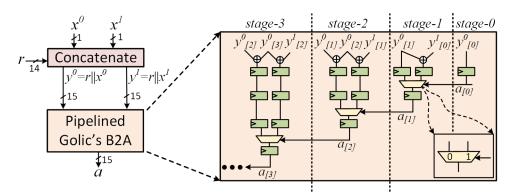

**Figure 10:** Design of our proposed circuit to process the binary Boolean shares  $(x^0, x^1)$  to produce a such that  $\bigoplus_i x^i = a + x^1$ . The circuit concatenates the Boolean shares with 14 random bits and feeds them to a pipelined version of Golic's Boolean to arithmetic circuit.

$$(p_i^1, p_i^0) = (a_{[i]}^1 \oplus b_{[i]}^1, a_{[i]}^0 \oplus b_{[i]}^0)$$

The subsequent levels process the group generate  $(s_{i:k}, s_{k-1:j})$  and group propagate  $(t_{i:k}, t_{k-1:j})$  terms to produce the group generate  $(s_{i:j})$  and group propagate  $(t_{i:j})$  for the next level. For any level l > 0, the relation between i and k can be generalized to  $i = k + 2^{l-1} - 1$ . For level-1, i = k and  $s_{i:i} = g_i$  and  $t_{i:i} = p_i$ . Following equations illustrate the masking of the group generate and group propagate terms.

$$(u^1, u^0) = \mathrm{DOM}(t^1_{i:k}, t^0_{i:k}, s^1_{k-1:j}, s^0_{k-1:j}, r_b)$$

$$(s^1_{i:j}, s^0_{i:j}) = (u^1 \oplus s^1_{i:k}, u^0 \oplus s^0_{i:k}), \ (t^1_{i:j}, t^0_{i:j}) = \mathrm{DOM}(t^1_{i:k}, t^0_{i:k}, t^1_{k-1:j}, t^0_{k-1:j}, r_c) \tag{9}$$

## 6.3 Boolean to Arithmetic Conversion

Prior literature shows that care should be taken while converting Boolean shares to arithmetic shares because the process of conversion might leak the original secret [Gou01]. Given the Boolean shares of a secret variable x as  $x^0$  and  $x^1$  such that  $\bigoplus_i x^i = x$ , the conversion aims to find an element a such that  $x^0 \oplus x^1 = a + x^1$ , where + is an addition mod K. We need to design a conversion circuit to convert the 1-bit Boolean shares of the activation to  $log_2K$ -bit arithmetic shares.

Figure 10 shows the proposed Boolean to arithmetic conversion circuit. Most prior works on share conversion in hardware assume the same field for inputs and outputs and try to reuse the existing randomness in the Boolean shares [Gol07, MTMM07a]. However, our design does not have  $log_2K$  bits in the Boolean shares. Thus, it first converts the 1-bit Boolean shares  $x^0$ ,  $x^1$  to  $log_2K$ -bit Boolean shares by concatenating each share with  $log_2K - 1$  fresh random bits. Next, it uses the circuit proposed by Golic to perform a secure Boolean to arithmetic share conversion [Gol07], with full pipelining to resist glitches. Following equations describe how each bit  $a_{[i]}$  of the arithmetic shares is produced by processing the bits of the Boolean shares  $y_{[i]}^j$ , where  $0 \le i \le 14$  and  $j \in (0,1)$ .

$$a_{[0]} = y_{[0]}^0 (10)$$

$$a_{[1]} = \mathtt{MUX}(y_{[1]}^0, y_{[1]}^0 \oplus y_{[0]}^1, a_{[0]}) \tag{11}$$

$$a_{[i]} = \texttt{MUX}(y_{[i-1]}^0 \oplus y_{[i]}^0, y_{[i]}^0 \oplus y_{[i-1]}^1, a_{[i-1]}) \tag{12}$$

The hardware feeds the produced arithmetic shares to the accumulator to process the next layer.

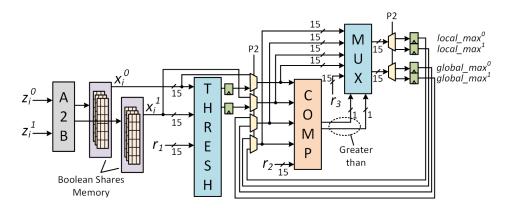

Figure 11: Hardware design of the fully masked output layer. Figure is not to scale.

# 6.4 Masked Output Layer

In the masked design, the output layer receives the arithmetic shares  $(z_i^0, z_i^1)$  of the confidence scores from the two adders and generates the Boolean shared inference result. Section 5.3 describes the three main operations in the output layer for the unmasked design viz. AND, comparison and multiplexer.

Since all the output layer operations like AND, comparison and multiplexing are bitwise manipulations, we apply Boolean masking to the complete output layer for efficiency. Therefore, the hardware first converts the arithmetic shares to Boolean shares and stores them in a Block RAM. Next, it performs all the operations of the baseline output layer described in Section 5.3 in a masked fashion. Figure 11 shows the hardware design of the fully masked output layer in terms of the four building blocks viz. arithmetic to Boolean converter (A2B), masked thresholder (THRESH), masked multiplexer (MUX) and masked comparator (COMP). We discuss the details of these components next.

The Design of Arithmetic to Boolean Share Converter. We again refer to the work by Golic to implement the arithmetic to Boolean share conversion [Gol07]. The work shows that the Boolean equations are symmetric for share conversion—Equations (10), (11), and (12) can be directly used to generate the arithmetic shares by simply swapping the Boolean share bits with the arithmetic share bits. Likewise, the hardware design of the arithmetic to Boolean converter is similar to the design of the *Pipelined Golic's B2A* block shown in Figure 10. However, the hardware feeds arithmetic shares  $(z_i^0, z_i^1)$  to this block as Figure 11 shows. The generated Boolean shares  $(x_i^0, x_i^1)$  are stored in two separate Block RAMs to be processed in the later steps of the max computation.

The Design of Masked Threshold. The hardware needs to securely threshold Boolean shares  $(x_i^0, x_i^1)$  based on whether  $x_i^0 \oplus x_i^1$  is greater or less than  $\frac{K}{2}$ . As mentioned in Section 5.3, this operation can be simplified to an AND operation of the confidence score with its inverted MSB. Similar to the masked activation function, we replace the regular AND gates with masked AND gates in the design that takes in  $x_i^0, x_i^1$ , the Boolean shares of the inverted MSB (i.e., one Boolean share inverted) and random mask  $r_1$ . Since the MSB of the output of THRESH is always zero, the hardware uses a random Boolean sharing of zero for it. Finally, the Boolean shared and thresholded confidence scores are sent to a masked comparator for the next step after registering the outputs.

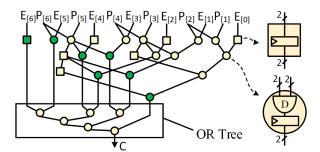

**Figure 12:** Hardware design of the masked comparator. The circles and squares on the right represent DOM-indep AND gate and a register. The green circles denote completed partial products of Equation 13 which are fed to the OR Tree for final evaluation of C.

The Design of Boolean Masked Comparator. We first describe a gate-level hardware design of comparator circuit and then explain its masking<sup>9</sup>. The Boolean function C(.) of an n-bit comparator is given in Equation (13).

$$\mathbf{C}(a,b) = \mathbf{E}_{[n-1]} | \mathbf{P}_{[n-1]} \cdot \mathbf{E}_{[n-2]} | \mathbf{P}_{[n-1]} \cdot \mathbf{P}_{[n-2]} \cdot \mathbf{E}_{[n-3]} | \cdots | \mathbf{P}_{[n-1]} \cdot \mathbf{P}_{[n-2]} \cdots \mathbf{P}_{[2]} \cdot \mathbf{P}_{[1]} \cdot \mathbf{E}_{[0]}, \tag{13}$$

where  $E_i = a_{[i]} \cdot b_{[i]}$  and  $P_i = a_{[i]} \overline{\oplus} b_{[i]} \ \forall i \in [0, n)$  represent the bit-wise comparison and equality check, respectively. The expression is amenable to a parallel-prefix computation.

Figure 12 shows the hardware design of a 7-bit comparator as an example. The hardware computes the final comparison in a parallel-prefix fashion by splitting the products with more terms (e.g.,  $P_6 \cdot P_5 \cdots P_0$ ) into multiple products with lesser terms ( $P_6 \cdot P_5$ ,  $P_4 \cdot P_3$ , and  $P_2 \cdot P_1$ ) and evaluating them in parallel. Subsequently, the hardware combines the partially computed products to fully compute all the product terms in Equation (13) and produce the final comparison result by 'ORing' them. We design its masked version by replacing the regular AND gates with DOM-indep multipliers having registered outputs.

We emphasize that the term 'comparison' in our work refers to comparing two variable numbers and returning whether one is greater than the other or not. Other works have also proposed designs for masked comparison, but in those works the term 'comparison' means an equality check [OSPG18]. Furthermore, the operation of thresholding is also a comparison and some works propose its masking [RRd+16], but thresholding compares a variable number to a fixed constant.

**The Design of Boolean Masked Multiplexer.** Finally, the hardware implements the logic to update the masked max and index registers based on the (Boolean) masked comparator result using a masked multiplexer. From Equation (14), a multiplexer consists of 2 AND and 1 OR operation; the OR can also be written in terms of AND.

$$\mathtt{MUX}(a,b,s) = \overline{\overline{(a \cdot s) \cdot \overline{(b \cdot \overline{s})}}} \tag{14}$$

where  $a, b, s \in GF(2)$  are the two data lines and the select line, respectively. To implement the masked version, we simply replace all the regular AND gates with masked AND gates. The masked index computations are performed accordingly.

<sup>&</sup>lt;sup>9</sup>The gate-level design is not needed for the baseline unmasked design, which uses the default implementation of a comparator by the synthesis tool for the target FPGA. However, masked design needs to define this in Boolean gates and use their secure versions.

Figure 13: Hardware design of the unprotected binarized ConvNet.

# 7 Hardware Design of ConvNet

We also implement a ConvNet hardware design to explore the masking of additional operations like convolution and maxpool and quantify the area overheads. Similar to the MLP design, we first implement a sequentialized unprotected ConvNet design and then implement its masked version. We choose a network architecture with 1 conv layer, 1 maxpool layer, 2 FC layers, and an output layer.

We have several reasons for choosing the smaller parameters compared to the original software implementation, which is listed in Section 9.1. First, our goal is to quantify the area overheads of masking; in an area-optimized design, any additional number of layers or node per layer will mostly increase the latency of the design, not the area because most of the design components are reused. Second, a lower latency design reduces the side-channel evaluation time. Third, the complete design will not fit the FPGA that we use. The software results show that our techniques are not limited by the ConvNet hyperparameters and can indeed provide a classification accuracy as good as the baseline. In this section, we demonstrate the techniques to mask the operations in a ConvNet that can be adopted and deployed in any ConvNet with a totally different set of hyperparameters. We discuss the impact of hyperparameters in Section 10.

Unprotected ConvNet Design. Figure 13 shows the hardware design of the unprotected ConvNet. Compared to the baseline MLP design, there are two important differences due to the two new convolution and maxpool operations. First, the ConvNet design requires special read logic for the image pixels and kernel elements: the controller assumes the linearly stored image pixels to be laid out as a 2D matrix, sequentially selects sub-matrices (called convolution windows) within the 2D matrix and generates addresses corresponding to the pixels in the sub-matrix. Second, the design requires logic to perform maxpool operation on the output of the convolutional layer: similar to the convolution operation, the controller needs to generate addresses for maxpool window elements and then select the maximum element in the window. In a BNN, maxpool is equivalent to OR operation and we also use this optimization in our design [UFG<sup>+</sup>17].

We reuse the weighted summation block of the MLP design to perform convolutions since convolution is also a weighted summation. Using the special read logic, the hardware reads out the pixels  $p_{i,j}$  from the Image BRAM (one pixel at a time / clock cycle) and kernel weights  $k_{i,j}$  from the kernal BRAM, multiplies them using the multiplexer and feeds the result to the accumulator. At the end of each convolution window, the hardware stores the inverted MSB of the weighted summation as the activated convolution result in output feature map (OFM) BRAM.

After finishing all the convolutions, the hardware initiates the maxpool operation. A

Figure 14: Hardware design of masked ConvNet.

special read logic reads out the elements of the OFM based on the maxpool window selected and feeds them to the maxpool logic. We implement maxpool as an OR accumulator: a register that is initialized to zero keeps storing the OR result of itself with a new input every cycle. The controller resets the register at the start of every maxpool window. Finally, the Maxpooled BRAM (MP BRAM) stores the results.

Since the network only has FC layers after maxpool, the flow is similar to MLP. The hardware processes the maxpooled results sequentially to compute the nodes of the first hidden layer. Finally the hardware computes the output layer confidence scores by processing the activations of the first hidden layer and produces the inference result.

Masked ConvNet Design. In addition to the MLP operations, the ConvNet design has two new operations: convolution and maxpool. The additional control circuits do not pose any security issues in the design because their operation is independent of the values of the secret parameters. However, the convolution and the maxpool operations' datapath need masking.