# Characterizing HfO<sub>2</sub>-based Ferroelectric Tunnel Junction in Cryogenic Temperature

Jae Hur, *Member, IEEE*, Chinsung Park, *Student Member, IEEE*, Gihun Choe, *Student Member, IEEE*, Prasanna Venkatesan Ravindran, *Student Member, IEEE*, Asif Islam Khan, *Member, IEEE* and Shimeng Yu, *Senior Member, IEEE*

Abstract—Since the discovery ferroelectric properties in doped HfO2, various types of memory devices have emerged based on this novel material. Especially, the ferroelectric tunnel junction (FTJ) has gained considerable attention for selector-less crossbar array. Although various studies have been done for the HfO2-based FTJs, there was no investigation of them at cryogenic temperature. While cryogenic memories are getting increasing attentions for diverse applications from high-performance computing to aerospace electronics, exploring the FTJ at cryogenic temperature is particularly interesting because it has been known for relatively poor retention characteristics and endurance at room temperature. For the first time, we characterize the HfO<sub>2</sub>based FTJ at cryogenic temperature down to 77 K. It was both endurance found that the retention and characteristics become greatly improved at 77 K. Furthermore, the read voltage was found to be critical for optimized performance in terms of on-current, off-current and their ratio at 77 K.

Index Terms—Ferroelectric tunnel junction (FTJ), Hf<sub>0.5</sub>Zr<sub>0.5</sub>O<sub>2</sub> (HZO), retention, endurance, reliability, cryogenic

# I. INTRODUCTION

FERROELECTRIC tunnel junction (FTJ) has recently obtained intensive interest due to the discovery of the doped HfO<sub>2</sub> as its ferroelectric layer [1]–[3]. Promising memory characteristics could be observed from many different groups for diverse memory applications [4]–[6]. The state-of-the-art HfO<sub>2</sub>-based FTJ demonstrated on/off ratio as high as ~30, while achieving extremely small power consumption down to ~1 fJ, could be obtained along with good retention (~10 years) and endurance (~10<sup>6</sup> cycles) [7]. To the best of our knowledge, however, the testing environments were limited to

Manuscript received xxxx xx, 2022; accepted xxxx xx, 2022. Date of publication xxxx xx, 2022; date of current version xxxx xx, 2022. This work was supported by ASCENT, one of six centers in JUMP, a Semiconductor Research Corporation (SRC) program sponsored by Defense Advanced Research Project Agency (DARPA). The review of this article was arranged by Editor xxxxx. (Corresponding author: Shimeng Yu.)

J. Hur, C. Park, G. Choe, P. V. Ravindran, A. I. Khan and S. Yu are with the School of Electrical and Computer Engineering, Georgia Institute of Technology, Atlanta, GA 30332, USA (e-mail: <a href="mailto:shimeng.yu@ece.gatech.edu">shimeng.yu@ece.gatech.edu</a>).

the room temperature (RT) or higher temperature in the previous HfO<sub>2</sub>-based FTJ studies. In the meantime, the low temperature-dependent study at cryogenic temperature is getting more significant attention as there lies a variety of applications including high performance cloud-computing, aerospace electronics, quantum computing, *etc.* [8]. Most recently, the FTJ using BaTiO<sub>3</sub> (BTO) layer was investigated under cryogenic temperature down to 10 K [9]. There was also a report with antiferroelectric tunnel junction with Hf<sub>0.5</sub>Zr<sub>0.5</sub>O<sub>2</sub> (HZO) layer whose current-voltage (I-V) characteristics were demonstrated at 230 K [10], but it is still insufficient to understand the full memory behavior and reliability performance of the HZO-based FTJ at even lower liquid-nitrogen temperature 77 K.

As HZO is compatible with CMOS and back-end-of-line (BEOL) processes [11], and highly scalable [12] unlike previous perovskite ferroelectrics, the HZO-based FTJs have greater potential to be used in the real applications. In this perspective, we took advantage of the HZO material as a ferroelectric layer in our FTJs and adopted the double-layer stack design with Al<sub>2</sub>O<sub>3</sub> interlayer [13]. Here, by using double-layer structure, the FTJ can have an intrinsic diode-like behavior [14] and more flexibility to the thickness optimization [15].

In this work, at cryogenic temperature of 77 K, the HZO-based double-layer FTJ structure is characterized in terms of on-current, off-current, on/off ratio (=on-current/off-current), and its memory reliabilities, *i.e.*, retention and cycling endurance. Although the reliability characteristics could be greatly improved at 77 K, the application of pre-pulses was needed at RT to let the FTJ have two stable states. It was also found that it is important to choose a right read voltage ( $V_{\rm read}$ ) to achieve better on/off ratio and reliability performances.

### II. FABRICATION PROCESS AND MEASUREMENT SET-UP

The fabricated FTJ structure has the multiple thin film stack of Al/TiN/Al<sub>2</sub>O<sub>3</sub>/HZO/TiN. Firstly, the p<sup>+</sup> Si wafer was RCA cleaned, which was followed by deposition of bottom 12nm-thick TiN electrode. Then, the 10nm HZO was deposited to be served as a ferroelectric layer. Next, the 2nm Al<sub>2</sub>O<sub>3</sub> and 12nm of top TiN electrode were deposited sequentially. All these layers were deposited using plasma-enhanced atomic layer deposition (PEALD) at 250 °C. Then, the sample was put into rapid thermal annealing (RTA) chamber and annealed at 450 °C for 30 secs. Lastly, 100nm-thick Al was deposited

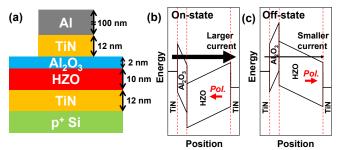

Fig. 1. (a) Schematic of the ferroelectric HZO-based capacitors fabricated, and energy band diagrams for FTJ at (b) on-state and (c) off-state.

as probing pad using e-beam evaporator. The Al and top TiN layers were patterned afterwards. Further details of the fabrication process can be found in [13].

The fabricated FTJ (approximately with the size of  $200\times200$   $\mu\text{m}^2$ ) was measured with Keithley 4200-SCS parameter analyzer. Write voltage ( $V_{\text{write}}$ ) of  $\pm 6$  V and pulse width ( $t_{\text{write}}$ ) of 50  $\mu\text{s}$  were used to program (to on-state) and erase (to off-state) the FTJ state. **Fig. 1(a)** shows the schematic of the fabricated FTJ structure and **Fig. 1(b),(c)** show the energy band diagrams to explain the operation mechanism. At on-state, the electrons tunnel through the  $Al_2O_3$  layer face only the  $Al_2O_3$  energy barrier due to the polarization heading towards the top electrode. On the other hand, at off-state, the electrons face both the  $Al_2O_3$  and HZO barriers as the polarization is induced towards the bottom electrode [3]. This leads to larger current at on-state compared to that at the off-state.

### III. FTJ PERFORMANCE AT ROOM TEMPERATURE

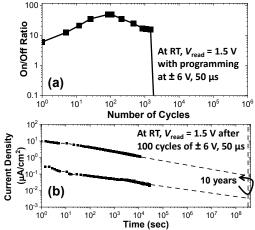

Fig. 2(a) shows the cycling endurance of the FTJ at read voltage ( $V_{\rm read}$ ) of 1.5 V at RT. Here, the program condition of  $V_{\rm write}$ =±6 V (+6 V/-6 V for on/off-state respectively applied to bottom TiN electrode) and  $t_{\rm write}$ =50 µs is stronger compared to [13], leading to faster hard breakdown at approximately  $2\times10^3$  cycles. However, the increasing and decreasing trend of the on/off ratio follow the similar trend where it increases up to approximately 100 cycles and starts to decrease after that. Fig. 2(b) shows the retention characteristics of the on-state and off-state current densities of the FTJ. Although the memory

**Fig. 2.** Reliability characteristics of the fabricated FTJ at RT: (a) Cycling endurance of on/off ratio and (b) retention drift of the on-state and off-state current densities.

window is sustained after 10 years with extrapolated lines, the absolute values of the current densities keep decreasing in both states, which will end up with reading false data. The analogous trend can be observed in the several previous literatures [5], [16] due to the imprint effect.

### IV. FTJ PERFORMANCE AT CRYOGENIC TEMPERATURE

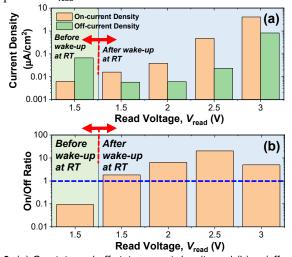

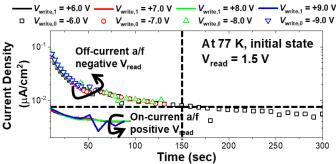

At cryogenic temperature of 77 K, the current densities of on-state and off-state were measured in the FTJ. It was found that the FTJ should go through wake-up cycles at RT before putting the sample into the cryogenic environment to achieve expected cryogenic memory performance. The left panel of Fig. 3(a) displays the comparison between the two states at  $V_{\rm read}$  of 1.5 V without the wake-up cycles at RT. Here, an abnormal behavior is observed where the FTJ current after positive write pulse is smaller than that after negative write pulse. This is due to the small number of defects in the ferroelectric layer in the beginning [3], which leads to inefficient trap-assisted-tunneling effect. Moreover, the probability becomes smaller at cryogenic temperature compared to the case at RT [10]. Nevertheless, this does not fully explain the opposite trend of on/off-state current. This may be due to the switching current induced from the small  $V_{\text{read}}$ . In other words, the positive polarity of read voltage is slightly flipping the ferroelectric domains over time after negative write voltage, leading to higher current. Indeed, it was found that after > 100 s of hold time, the read current after positive and negative write pulses became almost the same (Fig. 4). In addition, it needs to be noted that the offcurrent is smaller before the wake-up due to the not fullywoken-up ferroelectric domains in the FTJ [13]. After 100 wake-up cycles of  $V_{\text{write}}=\pm 6 \text{ V}$  and  $t_{\text{write}}=50 \text{ }\mu\text{s}$  at RT, in which the on/off ratio showed its maximum in Fig. 2(a), the on-state current became larger than the off-state current as shown in the right panel of Fig. 3(a). Moreover, it was also found that the on/off ratio becomes greatly dependent on the  $V_{\text{read}}$ .

**Fig. 3(b)** shows the highest on/off ratio >20 at  $V_{\rm read}$  of 2.5 V right after the wake-up cycles. Due to the higher off-state current at higher  $V_{\rm read}$  of 3 V, the on/off ratio decreased compared to  $V_{\rm read}$  of 2.5 V.

Fig. 3. (a) On-state and off-state current density and (b) on/off ratio of the fabricated FTJ at cryogenic temperature of 77 K.

**Fig. 4.** Retention characteristics of on/off current at 77 K before wake-up process.  $V_{\text{read}}$ =1.5 V and  $t_{\text{write}}$ =50  $\mu$ s.

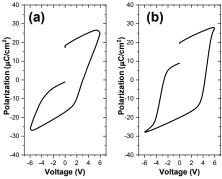

**Fig. 5.** P-V curves at (a) RT before RT-wake-up process and (b) 77 K after RT-wake-up process.

**Fig. 5** shows the polarization-voltage (P-V) characteristics of the FTJ at RT before wake-up and at 77 K after wake-up process. It should be noted that the hysteresis curve does not meet at 0 V possibly because of the depolarization field from Al<sub>2</sub>O<sub>3</sub> interlayer. The increased polarization values could be found with the increased defects for tunneling path.

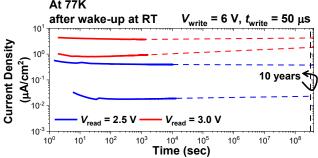

The retention behaviors of the FTJ at  $V_{\text{read}} = 2.5 \text{ V}$  and 3 V are demonstrated in Fig. 6. Compared to the retention drift of the FTJ at RT (Fig. 2(b)) the current densities of the on- and off-states are substantially more stable. At  $V_{\text{read}}$  of 2.5 V, the on/off ratio is expected to reach 10 years of retention without severe retention degradation due to the suppressed imprint effect at cryogenic environment. However, at  $V_{\text{read}}$  of 3.0 V, the off-state current is slightly increased as time goes on, which is because of the relatively high value of  $V_{\text{read}}=3.0 \text{ V}$ that induces the negatively polarized dipoles to the opposite direction. To minimize the retention degradation at 77 K, we chose the  $V_{\text{read}}$  values  $\leq 2.5$  V for characterizing cycling endurance of the FTJ at 77 K. Nevertheless, the coercive voltage of the FTJ extracted from I-V loop (not shown) are larger than 3 V (-3.5 V and 4.7 V), thus the  $V_{\text{read}} < 3.5 \text{ V}$  is still practicable. In Fig. 7, the FTJ did not experience the hard

Fig. 6. Retention drift of the on-state and off-state current densities at 77 K with  $V_{\rm read}$  of 2.5 V and 3.0 V.

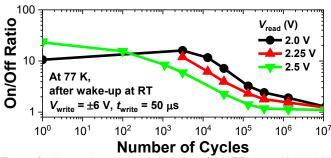

**Fig. 7.** Cycling endurance characteristics of the FTJ at 77 K with  $V_{\text{read}}$  of 2.0 V, 2.25 V and 2.5 V.

breakdown phenomenon at 77 K due to the suppressed stress-induced-leakage-current (SILC) effect [8]. Nevertheless, the on/off ratio keeps decreasing with increasing number of pulse cycles as both the on- and off-state current increase with the increasing trap densities in Al<sub>2</sub>O<sub>3</sub> and HZO films. Although the on/off ratio was higher with  $V_{\rm read}$ =2.5 V compared with  $V_{\rm read}$ =2.0 V, the trend was reversed after >10<sup>3</sup> cycles. The on/off ratio of  $V_{\rm read}$ =2.25 V was right in between the two after > 10<sup>3</sup> cycles. Therefore, the reading pulse condition must be carefully optimized in FTJ at cryogenic environments in terms of both retention and endurance characteristics.

### V. CONCLUSION

The memory performance of ferroelectric HfO<sub>2</sub>-based FTJ was investigated in cryogenic temperature for the first time. It was found that the reliability characteristics, i.e., both the retention and endurance performance, greatly improved at 77 K compared to RT environment. Here, pre-wake-up pulse cycles at RT were required to fully facilitate the FTJ memory performance before putting it to cryogenic temperature. Finally, optimization of reading condition was essential to maximize the on/off ratio and improved reliability same characteristics at the time. Although fabricated/measured FTJ had double-layer structure, it is expected that the other type of HfO<sub>2</sub>-based FTJ would perform analogous memory characteristic in cryogenic environment.

### Acknowledgements

This work was performed in part at the Georgia Tech Institute for Electronics and Nanotechnology, a member of the National Nanotechnology Coordinated Infrastructure (NNCI), which is supported by the National Science Foundation (Grant ECCS-2025462). P.V.R. was supported by the Georgia Tech Quantum Alliance (GTQA). The authors would like to thank Hang Chen for his technical help on the device fabrication.

## REFERENCES

- [1] M. Kobayashi, Y. Tagawa, F. Mo, T. Saraya, and T. Hiramoto, "Ferroelectric HfO<sub>2</sub> Tunnel Junction Memory with High TER and Multi-Level Operation Featuring Metal Replacement Process," *IEEE Journal of the Electron Devices Society*, vol. 7, no. 1, pp. 134–139, 2019, doi: 10.1109/JEDS.2018.2885932.

- [2] B. Max, M. Hoffmann, H. Mulaosmanovic, S. Slesazeck, and T. Mikolajick, "Hafnia-Based Double-Layer

Ferroelectric Tunnel Junctions as Artificial Synapses for Neuromorphic Computing," *ACS Appl. Electron. Mater.*, vol. 2, no. 12, pp. 4023–4033, Dec. 2020, doi: 10.1021/acsaelm.0c00832.

- [3] B. Max, M. Hoffmann, S. Slesazeck, and T. Mikolajick, "Direct Correlation of Ferroelectric Properties and Memory Characteristics in Ferroelectric Tunnel Junctions," *IEEE Journal of the Electron Devices Society*, vol. 7, pp. 1175–1181, 2019, doi: 10.1109/JEDS.2019.2932138.

- [4] T.-Y. Wu, H.-H Huang, Y.-H Chu, C.-C Chang, M.-H. Wu, C.-H. Hsu, C.-T. Wu, M.-C. Wu, W.-W. Wu, T.-S. Chang, H.-Y. Lee, S.-S. Sheu, W.-C. Lo, and T.-H. Hou, "Sub-nA Low-Current HZO Ferroelectric Tunnel Junction for High-Performance and Accurate Deep Learning Acceleration," in 2019 IEEE International Electron Devices Meeting (IEDM), Dec. 2019, p. 6.3.1-6.3.4. doi: 10.1109/IEDM19573.2019.8993565.

- [5] A. Sünbül, T. Ali, K. Mertens, R. Revello, D. Lehninger, F. Müller, M. Lederer, K. Kühnel, M. Rudolph, S. Oehler, R. Hoffmann, K. Zimmermann, K. Biedermann, P. Scharamm, M. Czernohorsky, K. Seidel, T. Kämpfe, and L. M. Eng, "Optimizing Ferroelectric and Interface Layers in HZO-Based FTJs for Neuromorphic Applications," *IEEE Transactions on Electron Devices*, vol. 69, no. 2, pp. 808–815, Feb. 2022, doi: 10.1109/TED.2021.3131971.

- [6] R. Berdan, T. Marukame, S. Kabuyanagi, K. Ota, M. Saitoh, S. Fujii, J. Deguchi, and Y. Nishi, "In-memory Reinforcement Learning with Moderately-Stochastic Conductance Switching of Ferroelectric Tunnel Junctions," in 2019 Symposium on VLSI Technology, Jun. 2019, pp. T22–T23. doi: 10.23919/VLSIT.2019.8776500.

- [7] Y.-S. Kuo, S.-Y. Lee, C.-C. Lee, S.-W. Li, and T.-S. Chao, "CMOS-Compatible Fabrication of Low-Power Ferroelectric Tunnel Junction for Neural Network Applications," *IEEE Transactions on Electron Devices*, vol. 68, no. 2, pp. 879-884, Feb. 2021, doi: 10.1109/TED.2020.3045955

- [8] J. Hur, Y.-C. Luo, Z. Wang, S. Lombardo, A. I. Khan, and S. Yu, "Characterizing Ferroelectric Properties of Hf<sub>0.5</sub>Zr<sub>0.5</sub>O<sub>2</sub> From Deep-Cryogenic Temperature (4 K) to 400 K," *IEEE Journal on Exploratory Solid-State Computational Devices and Circuits*, vol. 7, no. 2, pp. 168–174, Dec. 2021, doi: 10.1109/JXCDC.2021.3130783.

- [9] L. Chen, J. Zhou, X. Zhang, K. Ding, J. Ding, Z. Sun, and X. Wang, "Low-Temperature Tunneling Electroresistance in Ferromagnetic Metal/Ferroelectric/Semiconductor Tunnel Junctions," ACS Appl. Mater. Interfaces, vol. 13, no. 19, pp. 23282–23288, May 2021, doi: 10.1021/acsami.1c05366.

- [10] K.-Y. Hsiang, C.-Y. Liao, J.-H. Liu, J.-F. Wang, S.-H. Chiang, S.-H. Chang, F.-C. Hsieh, H. Liang, C.-Y. Lin, Z.-F. Lou, T.-H. Hou, C.W. Liu, and M. H. Lee, "Bilayer-Based Antiferroelectric HfZrO<sub>2</sub> Tunneling Junction with High Tunneling Electroresistance and Multilevel Nonvolatile Memory," *IEEE Electron Device Letters*, vol. 42, no. 10, pp. 1464–1467, Oct. 2021, doi: 10.1109/LED.2021.3107940.

- [11] W. Chakraborty, B. Grisafe, H. Ye, I. Lightcap, K. Ni, and S. Datta, "BEOL Compatible Dual-Gate Ultra Thin-Body W-Doped Indium-Oxide Transistor with I<sub>on</sub> = 370μA/μm, SS = 73mV/dec and Ion/Ioff Ratio > 4×10<sup>9</sup>," in 2020 IEEE Symposium on VLSI Technology, Jun. 2020, pp. 1–2. doi: 10.1109/VLSITechnology18217.2020.9265064.

- [12] J. Müller, E. Yurchuk, T. Schlösser, J. Paul, R. Hoffmann, S. Müller, R. Hoffmann, S. Müller, D. Martin, S. Slesazeck, P. Polakowski, J. Sundqvist, M. Czernohorsky, K. Seidel, P. Kücher, R. Boschke, M. Trentzsh, K. Gebauer, U. Schröder, and T. Mikolajick, "Ferroelectricity in HfO<sub>2</sub> enables nonvolatile data storage in 28 nm HKMG," in 2012 Symposium on VLSI Technology (VLSIT), Jun. 2012, pp. 25–26. doi: 10.1109/VLSIT.2012.6242443.

- [13] J. Hur, Y.-C. Luo, P. Wang, N. Tasneem, A. I. Khan, and S. Yu, "Ferroelectric Tunnel Junction Optimization by Plasma-Enhanced Atomic Layer Deposition," in 2020 IEEE Silicon Nanoelectronics Workshop (SNW), Jun. 2020, pp. 11–12. doi: 10.1109/SNW50361.2020.9131649.

- [14] S. Fujii, Y. Kamimuta, T. Ino, Y. Nakasaki, R. Takaishi, and M. Saitoh, "First demonstration and performance improvement of ferroelectric HfO<sub>2</sub>-based resistive switch with low operation current and intrinsic diode property," in *2016 IEEE Symposium on VLSI Technology*, Jun. 2016, pp. 1–2. doi: 10.1109/VLSIT.2016.7573413.

- [15] E. Covi, H. Mulaosmanovic, B. Max, S. Slesazeck, and T. Mikolajick, "Ferroelectric-based synapses and neurons for neuromorphic computing," *Neuromorph. Comput. Eng.*, vol. 2, no. 1, p. 012002, Feb. 2022, doi: 10.1088/2634-4386/ac4918.

- [16] A. Shekhawat, G. Walters, N. Yang, J. Guo, T. Nishida, and S. Moghaddam, "Data retention and low voltage operation of Al<sub>2</sub>O<sub>3</sub>/Hf<sub>0.5</sub>Zr<sub>0.5</sub>O<sub>2</sub> based ferroelectric tunnel junctions," *Nanotechnology*, vol. 31, no. 39, p. 39LT01, Jul. 2020, doi: 10.1088/1361-6528/ab9cf7.