# Comparing the thermal performance and endurance of resistive and PIN silicon microheaters for phase-change photonic applications

JOHN R. ERICKSON<sup>1</sup>, NICHOLAS A. NOBILE<sup>1</sup>, DANIEL VAZ<sup>1</sup>, GOURI VINOD<sup>1</sup>,

CARLOS A. RÍOS OCAMPO<sup>2,3</sup>, YIFEI ZHANG<sup>4</sup>, JUEJUN HU<sup>4</sup>, STEVEN A.

VITALE<sup>5</sup>, FENG XIONG<sup>1</sup>, NATHAN YOUNGBLOOD<sup>1,\*</sup>

<sup>1</sup>*Univ. of Pittsburgh, Dept. of Electrical & Computer Engineering, Pittsburgh, PA 15261, USA*

<sup>2</sup>*Univ. of Maryland, Dept. of Materials Science & Engineering, College Park, MD, USA*

<sup>3</sup>*Univ. of Maryland, Institute for Research in Electronics & Applied Physics, College Park, MD, USA*

<sup>4</sup>*MIT, Dept. of Materials Science & Engineering, Cambridge, MA, USA*

<sup>5</sup>*Advanced Materials and Microsystems Group, MIT Lincoln Laboratory, Lexington, MA*

*\*nathan.youngblood@pitt.edu*

**Keywords** Silicon Photonics, Phase Change Devices, Nonvolatile Materials

**Abstract:** Optical phase-change materials have enabled nonvolatile programmability in integrated photonic circuits by leveraging a reversible phase transition between amorphous and crystalline states. To control these materials in a scalable manner on-chip, heating the waveguide itself via electrical currents is an attractive option which has been recently explored using various approaches. Here, we compare the heating efficiency, fabrication variability, and endurance of two promising heater designs which can be easily integrated into silicon waveguides—a resistive microheater using n-doped silicon and one using a silicon p-type/intrinsic/n-type (PIN) junction. Raman thermometry is used to characterize the heating efficiencies of these microheaters, showing that both devices can achieve similar peak temperatures but revealing damage in the PIN devices. Subsequent endurance testing and characterization of both device types provide further insights into the reliability and potential damage mechanisms that can arise in electrically programmable phase-change photonic devices.

## 1. Introduction

The ability to reversibly control the phase and amplitude of light in both a nonvolatile and highly compact form-factor has been a key motivation behind current research into optical phase-change materials (PCMs) [1]. However, achieving this reversible control using a scalable integrated approach (i.e., electronic integration) has been more challenging for the optical community than it has for the electronics community. This can be attributed to the significant difference in area and volume between electronic PCM memristors (typically sub-50 nm in x-, y-, and z-dimensions) and photonic PCM devices (typically  $>1 \mu\text{m}$  in-plane, while  $\leq 50 \text{ nm}$  out-of-plane) which rules out directly applying current to the PCM itself. To reversibly switch these materials, high melting temperatures ( $\sim 900 \text{ K}$ ) and fast quenching rates ( $\sim 0.1$  to  $1 \text{ K/ns}$  in the case of  $\text{Ge}_2\text{Sb}_2\text{Te}_5$ ) are required which demands careful thermal engineering [2]. Additionally, the heat source used to switch the PCM should be optically transparent to prevent high insertion loss.

To address this challenge, several approaches have been demonstrated to enable scalable electrical control over optical PCMs for photonic circuits using waveguide-integrated resistive microheaters. This includes the use of transparent conductors [3]–[7], metallic heaters [8]–[10], graphene [11], [12], doped-silicon waveguides [13], [14], and silicon p-type/intrinsic/n-type (PIN) junctions [15]. For monolithic integration with silicon photonic platforms, microheaters based on single-doped silicon [13], [14], [16] and silicon PIN junctions [15], [17] are the most attractive choices as they can be fabricated using the same foundry-compatible processes commonly used to fabricate active silicon photonics devices (e.g., p-type/n-type (PN) modulators [18] and doped-silicon thermo-optic phase shifters [19]). While both designs can be easily incorporated into the standard silicon photonics process flow, these two approaches have their relative strengths and weaknesses. Using microheaters comprised of forward-biased silicon PIN junctions (here on referred to as “PIN microheaters”) has the potential to have very low insertion loss as the waveguide can be patterned in the intrinsic region of the junction. However, the heating response of these devices can be quite sensitive to device dimensions and doping levels as we have observed in simulations [17] and show experimentally in this work. On the other hand, single-doped silicon microheaters (here on referred to as “doped microheaters”) have simpler design considerations, which can be arbitrarily large, at the cost of higher applied voltages. A direct comparison between these two designs is challenging, since the reported devices from previous works have been processed separately under different process flows and doping conditions.

Here, we compare both doped and PIN microheater designs for switching PCMs which have been fabricated on the same chip together under the same conditions. This work investigates the steady-state heating response of PIN and doped microheaters using Raman thermometry and compares different PIN device geometries to further understand critical design parameters for these embedded heaters. Damage at the metal contacts was observed in the PIN devices after steady-state measurements (but not the doped devices), prompting us to explore the conditions under which this damage occurs. Endurance tests performed on doped and PIN microheaters revealed that for the same electrical power dissipation, doped microheaters exhibited less thermally-induced aging than PIN microheaters. Our results highlight the need for further research to improve the efficiency and lifetime of these microheaters for phase-change photonics applications.

## 2. Methods

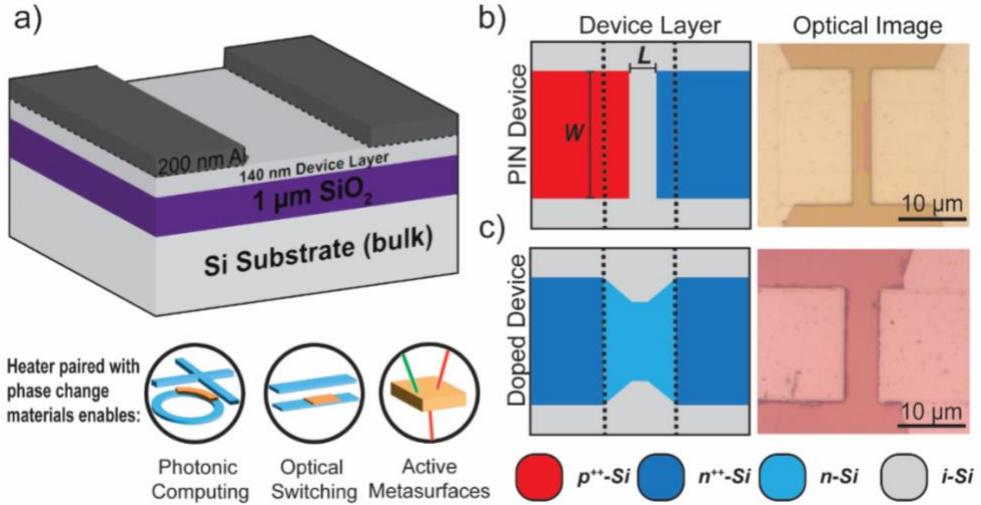

PIN microheaters of differing intrinsic region lengths and widths were fabricated in a 90 nm CMOS line at the MIT Lincoln Laboratory [13], along with an array of n-doped microheaters with a constant geometry and varying levels of internal doping. All devices were fabricated on silicon-on-insulator wafers with a device layer of  $\sim$ 140 nm Si on 1  $\mu$ m of SiO<sub>2</sub>. While waveguides were not patterned on these devices, the thin silicon device layer has similar dimensions to partially etched silicon contacts in a typical rib waveguide process. To make electrical contact to the silicon, 200 nm Al metal contacts were deposited on top of a thin Ti/TiN adhesion/barrier layer. Finally, a thin 10 nm passivating layer of SiO<sub>2</sub> was uniformly deposited on the chip which is needed to provide electrical isolation for a PCM layer deposited on top of the microheater.

**Fig. 1.** Schematic views of the microheaters studied (10 nm passivating SiO<sub>2</sub> layer is omitted for clarity). All devices share the same layer structure (a), as shown above. Schematics of both the (b) PIN and (c) doped device layers are shown, with specific doping areas color coded as denoted. For the PIN device, specific *W* and *L* dimensions are denoted. Contact edges are represented by the dotted lines. The top down views of both devices are paired with optical images of pristine devices. The doped regions for the PIN device are visible in the optical image.

## 2.1 Device Details

We fabricated 12 unique PIN microheater geometries based on the design demonstrated by Zheng et al. [15] which have four different device widths (*W*= 5, 10, 15, and 20 μm), and three different lengths (*L* = 0.9, 1.2, and 1.5 μm) as indicated in Fig. 1. To keep the contact resistance of the PIN devices consistent between different geometries, the distance between the edge of the metal contacts and the edge of the doped regions was kept constant at 0.8 μm, so that the total distance between contacts was always equal to *L* + 1.6 μm. Additionally, the distance between each metal contact edge and the doped region edge was kept constant at 5 μm so that edge-to-edge, the contact was always *W* + 10 μm. The doped microheaters based on the design by Ríos et al. [13] had a fixed geometry with 5 μm between contacts and a tapered, lightly n-doped channel, as shown in Fig. 1. This channel tapers to a 10×0.5 μm<sup>2</sup> area which localizes the Joule heating to the PCM/waveguide region in the center. The metal contacts for the doped microheaters are separated by 16 μm from edge-to-edge. Due to their high uniformity and reliability, only two devices of each doping level are measured to characterize their thermal performance, see Supporting Information (SI) Fig. S1 and S2 for more details.

For the PIN microheaters, both the p<sup>++</sup> and n<sup>++</sup> regions of the device were heavily doped ( $\sim 10^{20}$  cm<sup>-3</sup>) to minimize contact resistance as well as maximize current through the device [17]. The intrinsic region was unaltered, and as such is henceforth referred to as *undoped*. For the doped microheaters, the two n<sup>++</sup> regions used for ohmic contact were similarly heavily doped ( $\sim 10^{20}$  cm<sup>-3</sup>), while the interior n-regions were lightly doped at two different levels. Devices 1 and 2 were doped with  $n = 3 \times 10^{18}$  cm<sup>-3</sup>, while devices 3 and 4 were doped with  $n = 8 \times 10^{17}$  cm<sup>-3</sup>. Sheet resistances of each device measured can be found in section 2 of the SI.

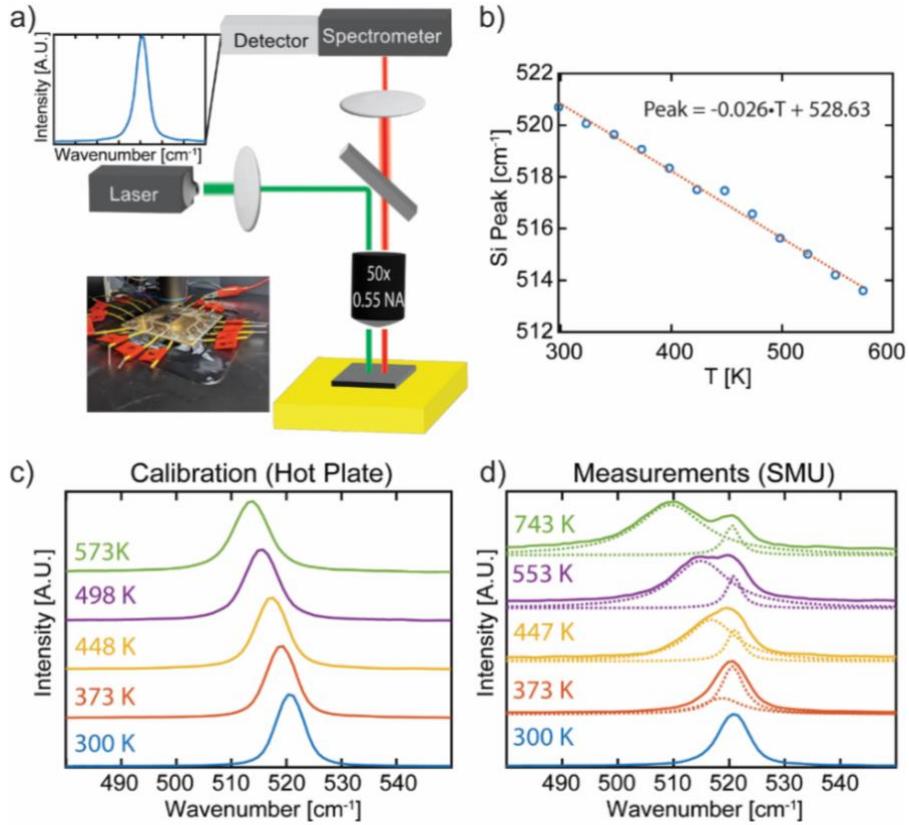

## 2.2 Raman Thermometry

Raman thermometry has emerged as a way to measure material specific temperatures inside of samples by tracking the shift of Raman peaks as a function of temperature [16], [20]–[26]. To acquire Raman spectra of our microheaters, a Horiba XploRA PLUS Raman microscope with 473 nm excitation laser and long working distance 50 $\times$ , 0.55 NA objective was used, resulting in a diffraction limited spot size of 1.18  $\mu\text{m}$ . During measurements, we set the 473 nm laser to a power of 250  $\mu\text{W}$  to ensure minimal excess heat was imparted into the devices through optical absorption. In order to convert the measured Raman spectra to the device temperature, we first calibrated the Si peak position versus sample temperature using a custom sample holder with built-in hotplate. More details regarding Raman spectra acquisition can be found in section 3 of the SI. The resulting calibration curve is shown in Fig. 2b and matches well with other results in the literature [20], [21], [24]. After calibration, the fabricated chip was wire bonded to a custom printed circuit board (PCB) to simplify electrical connectivity as shown in the inset in Fig. 2a. Devices were powered during the measurements using a Keithley 2450 Source Measure Unit (SMU) with up to 4 V for the PIN devices and up to 10 V for the doped devices. The resulting current-voltage (IV) characteristic of each device shown in Fig. 3a-b.

During temperature measurements, each applied DC voltage was maintained for 5 min to ensure both electrical and mechanical stability. Line scans were then performed to recenter and refocus the beam to account for any thermal drift present. Raman spectra were then obtained and fit using a similar peak-fitting and averaging method used for the calibration data, discussed in section 3 of the SI. However, at higher temperatures splitting of the Si peak occurred, as can be seen in Fig. 2d. This splitting is attributed to the higher temperature of the thin Si device layer (i.e., the Si layer in which the microheater is fabricated) relative to the bulk Si substrate beneath the  $\text{SiO}_2$ , causing the Si peaks from the different temperatures of these two layers to split [16]. These peaks were fitted using a double Lorentz curve, and device temperature was then calculated using the redshift of the proper Si peak using the calibration curve (Fig. 2b). This effect was not present in the generation of the calibration curve (Fig. 2c), since both the thin film Si and the underlying Si substrate were at the same temperature, resulting in one single Lorentz peak for the Si temperature.

**Fig. 2.** (a) Schematic of a Raman Microscopy process, inset shows an image of the wire bonded test sample. (b) Calculated calibration curve of Si peak location against a known temperature using a hotplate. (c) Example of the Si Raman peak shifting at known temperatures, generated by the in-situ hot plate. (d) Demonstrating the peak splitting observed at higher temperatures for the devices while powered. This peak splitting does not occur during generation of the calibration curve, due to the consistent heat provided by the hot plate used.

### 3. Results

#### 3.1 Temperature vs. Applied Power

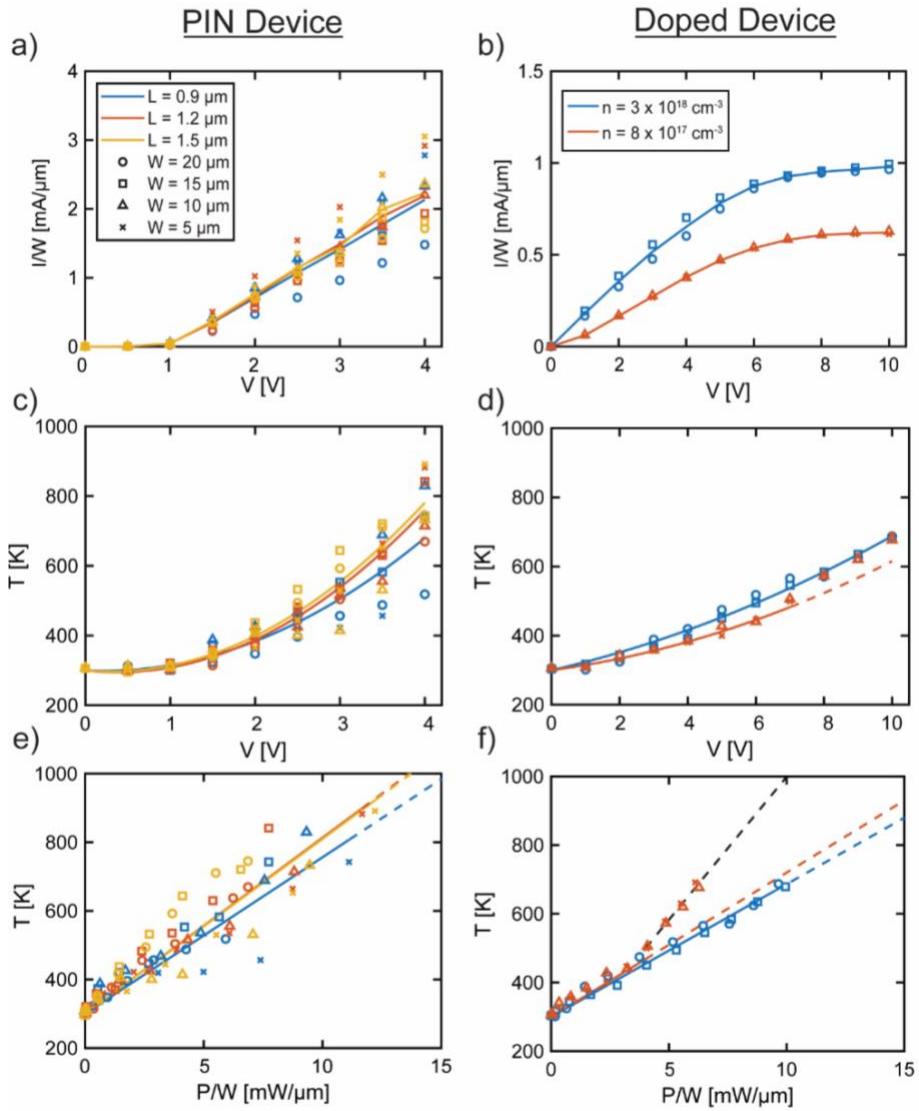

The IV curves during Raman measurements for all devices are shown in Fig. 3a (PIN) and Fig. 3b (single doped). The measured current for each device is normalized by device width ( $W$ ) to better facilitate comparison between the different device geometries. Fig. 3c-d shows the corresponding device temperature as a function of applied voltage and Fig. 3e-f shows the temperature as a function of applied power with temperature obtained using Raman thermometry. The PIN microheaters were grouped by device channel length ( $L$ ), while the doped microheaters were grouped by the concentration of the lightly n-doped region between the contacts. Heating in these devices should be linearly proportional to applied power (quadratic with respect to applied voltage in Fig. 3c-d) due to Joule heating. Note, we expect the temperature-power dependence in the PIN devices to be slightly non-linear due to additional heating from carrier recombination at the P-I and I-N interfaces [17]. For each group of devices in Fig. 3e-f (3 groups of 4 PIN devices and 2 groups of 2 doped devices), we fit a linear trend

(quadratic for Fig. 3c-d) to compare the relative heating efficiency of the devices. While we expected that channel length would be the dominant parameter to influence current and heating in the PIN devices, we observed significant variability in both the IV and thermal heating efficiency. This appears to indicate that the PIN devices showed greater sensitivity to our fabrication process than specific device geometry.

The doped microheaters reveal nonlinear IV behaviors at higher applied voltages as can be seen in Fig. 3b. At lower applied voltages, like those available on-chip (<5 V), the IV behavior is linear as expected, resulting in the higher doped device reaching higher currents (and therefore, higher applied power) at a given voltage [13], [16]. However, as the voltage approaches the highest applied voltage (10 V), the current behaviors significantly deviated from the linear trend. In addition, the device temperatures converge as shown in Fig. 3d. Further insight on the device IV behaviors is given through various calculations performed on the measured data (see Fig. S3). We hypothesize that this is due to velocity saturation effects in silicon where the linear relationship between carrier velocities and electric field breaks down at high electric fields [27], [28]. Velocity saturation has been widely accepted to be driven by carrier scattering with optical phonons [29]–[32], where once an electron’s kinetic energy exceeds the optical phonon energy, it scatters with the lattice and generates an optical phonon, causing its velocity to drop. This puts an effective cap on the carrier velocities seen in semiconductors, leading to the observed current saturation observed at high fields [29]–[32]. To confirm this, we measured the IV curves for different channel lengths and doping levels. Normalizing the voltage by channel length gives us a saturation field of  $\sim 1 \times 10^4$  V/cm which is consistent with literature [27], [30] (see Fig. S4). In our devices, this effect would imply that there is a nonlinear increase in phonon production above a certain applied voltage (E-field), resulting in increased heating rates.

Interestingly, we observe that the devices with a lower doping level ( $8 \times 10^{17}$  cm<sup>-3</sup>) reach higher temperatures than the devices with higher doping ( $3 \times 10^{18}$  cm<sup>-3</sup>) for the same applied power above a certain threshold (see black dashed line in Fig. 3f). This indicates that the devices with lower doping become more efficient heaters above this threshold which happens to occur at the onset of velocity saturation (around  $\sim 7$  V). One possible explanation for this effect is a higher phonon generation rate per carrier for the devices with lower doping levels. If we consider the systems below the saturation region, we know that mobility decreases with increasing doping ( $\mu_n$  is  $\sim 2 \times$  lower at room temperature for the higher doped devices [33]). Since the lower doped devices have higher mobilities and below velocity saturation  $v_{drift} = -\mu_n E$  is a valid assumption, we can thus conclude under these assumptions that the average carrier kinetic energy in the lower doped device is higher ( $E = \frac{m^* v_{drift}^2}{2}$ ). We further hypothesize that as the E-field continues to increase with increasing voltage, the kinetic energy of the carriers in both devices also increase, but the lower doped devices would then be able to reach the optical phonon scattering regime at lower fields.

**Fig. 3.** IV performance of the (a) PIN devices, and (b) doped devices. The solid lines are average IV performance, one for each length of the PIN devices, and one for each doping of the doped devices. Data points shown on both are for specific devices. (c) and (d) Results of the Raman Thermometry measurements showing the calculated device temperature vs. applied voltage for (c) PIN devices and (d) doped devices. The thermal fits assume a second order polynomial ( $T = T_0 + aV + bV^2$ ) to account for both Joule heating and temperature-dependent device resistance. For the  $n = 8 \times 10^{17} \text{ cm}^{-3}$  devices in (d), continuation of the expected quadratic fit is given by the dashed orange line, showing the deviation from this behavior above 7 V. Results of the Raman Thermometry measurements shown vs normalized applied power for (e) PIN devices and (f) doped devices. Linear trend lines are fit for the data for each device (both the 1.2 and 1.5  $\mu$ m long devices in (e) had similar trendlines, resulting in overlapping lines). For the  $n = 8 \times 10^{17} \text{ cm}^{-3}$  devices in (f), the deviation from expected Joule heating above 7 V is indicated by the dashed black line as a guide to the eye, with the expected linear trend continuing using the dashed orange line.

As can be seen in Fig. 3f, there is significant overlap in the device heating performance as a function of the applied power below the saturation region. However, once the lower doped device reaches velocity saturation conditions ( $4 \text{ mW}/\mu\text{m}$  at 7 V), the amount of heat generated greatly increases. As the E-field continues to increase beyond this point, our hypothesis implies the electrons in the channel generate optical phonons at a higher rate, increasing the amount of heat generated. The trend from pre-saturation conditions is continued using the dotted orange line to highlight this abrupt increase in heat generation in Fig. 3d and 3f.

Overall, the PIN microheaters can reach higher temperatures at much lower applied voltages and total power, as shown by Fig. 3c-d. However, when the results are normalized by device width the doped microheaters have a similar power efficiency, as shown in Fig. 3e-f. Additionally, the doped devices show a much larger degree of consistency between devices of the same doping level. Compared to the large variance in both thermal performance and IV response for the PIN devices (shown in Fig. 4a and Fig. 1c, respectively), it appears that the doped microheaters are much less sensitive to fabrication imperfections and could lead to improved reliability and yield. The higher doped devices behave extremely consistently with each other, as do the lower doped (see SI Fig. S1 and S2). These device pairs only differ through their n-channel doping level as discussed above.

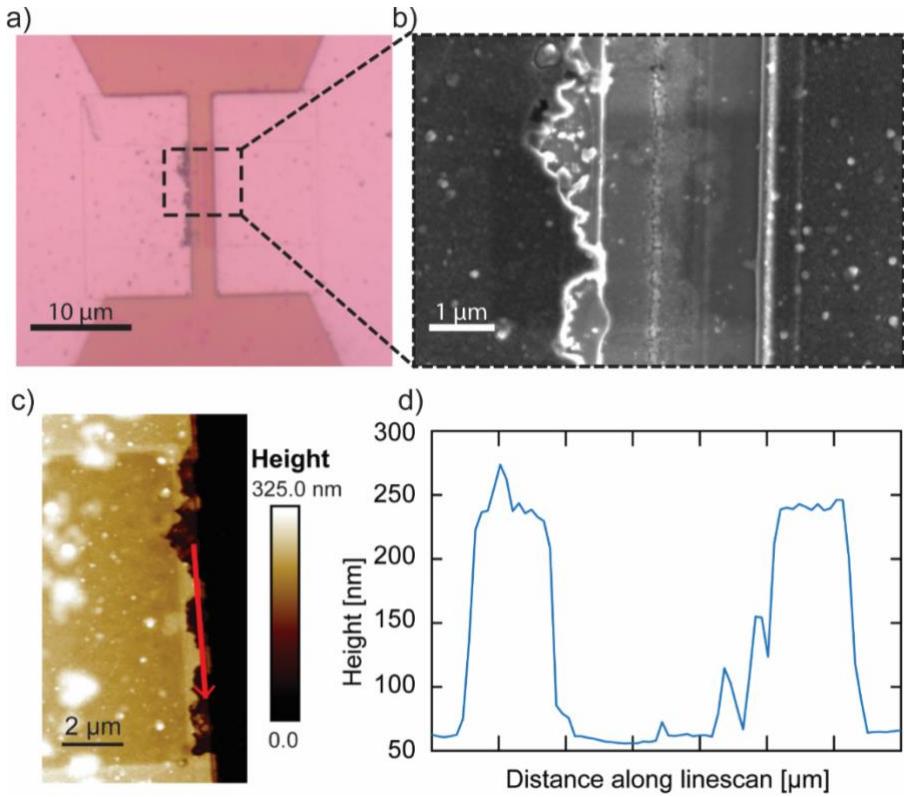

### 3.2 Endurance Testing

After performing Raman thermometry, we observed that holding the device at high temperatures and current densities for several minutes cause significant damage to the  $\text{p}^{++}$  terminal of the forward-biased PIN devices. This was consistently observed across the majority of the PIN devices tested as depicted in Fig. 4a. However, this damage was not observed in the doped devices. One possible explanation for this could be due to a larger separation of the metal contacts from the center region of highest temperature in the case of the doped devices. For the PIN devices, we attributed the cause of this damage to the relatively low melting temperature of the metal contacts (Al) which are exposed to high temperatures over several minutes. To test this hypothesis and further understand the full impact of this damage on the device performance as well as the extent of the damage, we performed further characterization and testing. The damaged devices were imaged using scanning electron (SEM) and atomic force microscopy (AFM). AFM topographic scans revealed that damaged regions of the electrode indeed matched the  $\sim 200 \text{ nm}$  thickness of the deposited Al layer (Fig. 4c-d). SEM images of the device (shown in Fig. 4b) also appear to show removal of the Al layer while the Ti/TiN adhesion and barrier layers remain undamaged after steady-state testing.

**Fig. 4.** Example of damage observed during Raman process. (a) shows a device after being powered. Devices were then characterized by (b) Scanning electron microscope image showing the contact disappearance. In addition, brighter spots in the midst of the channel likely indicate that the 10 nm  $\text{SiO}_2$  passivation layer has suffered ablation, allowing the underlying thin-film Si layer to shine brighter. The slightly darker area denotes carbon contamination from a previous, higher magnification scan. (c) Atomic force microscope image of the device, the red line depicts the path of a line scan. The results of which (d) show the resulting step size is  $\sim 200$  nm, implying the contact edge has completely delaminated and disappeared.

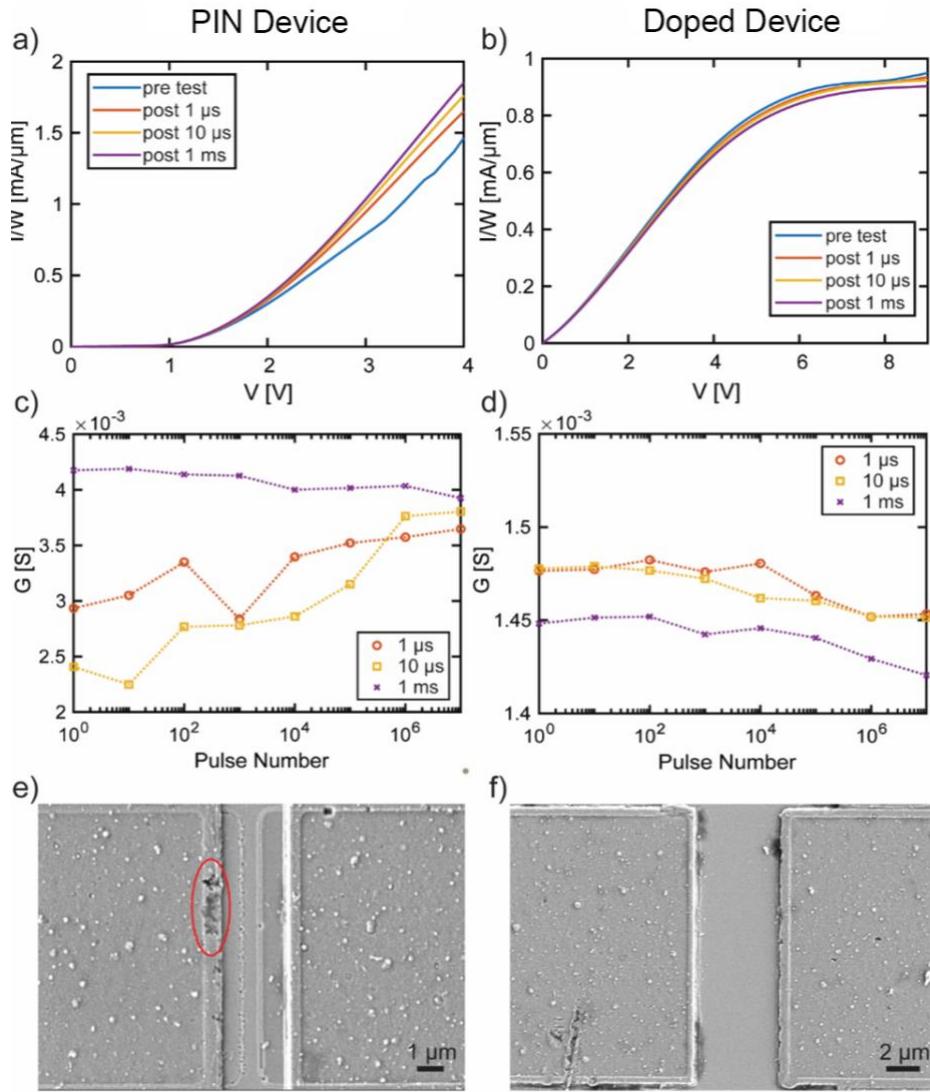

While steady-state operation can provide insights into device aging, these microheaters are intended to operate under pulsed conditions to reversibly switch optical PCMs. To investigate the potential effects that pulsed operation may cause on device performance and to observe which pulse conditions may cause similar electrode damage, endurance testing was carried out on new devices from both types of microheaters. For both the PIN and doped microheaters, a width of  $W = 10 \mu\text{m}$  was chosen ( $L = 0.9 \mu\text{m}$  for the PIN device,  $n = 3 \times 10^{18} \text{ cm}^{-3}$  for the doped device). During testing, up to 10 million pulses were applied to a test device, with varying pulse widths of 1  $\mu\text{s}$ , 10  $\mu\text{s}$  and 1 ms. To reproduce the conditions causing the damage during the Raman measurements, we applied 4 V pulses to the PIN devices. To also ensure the same applied power was used for both PIN and n-doped devices, we calculated an applied power of 7.4 mW/ $\mu\text{m}$  for the PIN microheater, when normalized by device width. The same applied power corresponds to a pulse amplitude of 8 V for the doped devices, which was then used during testing. A pulse duty cycle of 50% was used for each test.

**Fig. 5.** Results of endurance testing of the devices. IV sweeps of the (a) PIN and (b) n-doped device taken after each set of pulse widths. (c) and (d) Device conductivity was measured after every decade of cycling. SEM images of the (e) PIN and (f) doped devices post testing showing the onset of damage in the PIN microheater (highlighted area), and the lack thereof in the doped device.

At the end of the 10 million pulse test for each pulse width, an IV sweep was performed (Fig. 5a-b) and the device was inspected under an optical microscope. In addition, after each decade a short 400 ns long read pulse was applied to characterize the electrical performance of the stressed device (Fig. 5c-d). Visible damage was not observed on the PIN device until after the 1 ms pulse width cycle, shown in Fig. 5e. No damage was observed in the doped device after endurance testing (Fig. 5f) which agreed with our observations from Raman thermometry experiments. Although the damage did in fact occur in the PIN device as shown in Fig. 5e, the electrical performance of the device as measured by IV was not significantly affected after cycling beyond a moderate increase in forward bias current.

## 4. Discussion

While the initial goal of this work was to compare different intrinsic region lengths of PIN diodes, it became abundantly clear that a more important parameter was device width,  $W$ . With this in mind, temperature versus power results were then normalized by device width, as the smaller (low  $W$ ) devices all consistently outperform the larger (high  $W$ ) devices due to the smaller amount of volume being heated. In addition, appears that the smaller  $L$  devices heat much less efficiently than the wider devices, as evidenced by the lower slope of the trend line in Fig. 4a. This under performance is likely due to the lower volume of material being heated, as well as the closer proximity of the contacts which act as heat sinks. In this steady state measurement, both of those factors result in lower total temperatures, although their performance in pulsed applications are projected to be better in terms of heating speed than their wider companions [17].

As can be seen through the spread of points in Fig. 4a, there is still a large spread among the different PIN devices (likely due to the high requirements for consistent fabrication of these devices). In comparison, the doped microheater devices heat more consistently than the PIN devices, with a similar efficiency depending on the interior region doping level. However, it is worth emphasizing that PIN heaters still offer a higher potential for efficient heating at lower voltages, as evidenced by Fig. 3, which is ideal for typical on-chip voltages (i.e.,  $<5$  V).

We have also demonstrated unexpected behaviors of the doped heaters in the current saturation range of operation exhibited at higher voltages (Fig. 3f). We hypothesize the increased emission rate of optical phonons in devices operating at current saturation led to a second, more efficient heating regime in these devices. Lower doped devices are able to reach this regime at lower powers, therefore outperforming higher doped devices (Fig. 3f). However, for applications that are limited to on-chip voltages ( $<5$  V) we find that higher doped devices reach higher temperatures at lower voltages (Fig. 3d).

When comparing PIN microheaters with doped resistive microheaters, it is important to note some relative advantages and disadvantages of both designs. First, while not explored here, we do expect the maximum intrinsic channel length to be limited to sub-10  $\mu\text{m}$  to operate at reasonable applied voltages. This makes doped microheaters more appropriate for scaling to larger area devices such as reconfigurable metalens pixel arrays. Secondly, to prevent electromigration, RF pulses can be used to heat doped microheaters which is an impossibility for microheaters based on PIN diodes. Finally, it seems that fabricating consistent embedded PIN devices is more challenging than doped devices, both in regard to mitigating the large degree of randomness observed in the IV performance of our devices and further optimizing device endurance. However, the potential for operating at low applied voltages ( $<5$  V) with low optical insertion loss warrants further improvements and optimizations. In terms of optical performances, PIN and doped microheaters can offer comparable optical attenuation properties, ( $\sim 0.02\text{--}0.4$  dB/ $\mu\text{m}$  for devices of intrinsic region lengths 0.9–1.5  $\mu\text{m}$  [17] compared to 0.03 dB/ $\mu\text{m}$  for doping levels like those found in [13]). The PIN devices tested here compared promisingly with single doped devices for the dimensions tested. The final results of the comparison are summarized below in Table 1. With more improvements in both device structure and fabrication methods, PIN heaters should have a bright future.

**Table 1** – Comparison of PIN and Doped Devices

|                                     | <b>PIN Devices</b>      | <b>Doped Devices</b>                     |

|-------------------------------------|-------------------------|------------------------------------------|

| <b>Max Temp. (&lt;10 mW/μm)</b>     | 829.7 K (9.32 mW/μm)    | 687.4 K (9.65 mW/μm)                     |

| <b>Max Temp. (4 V)</b>              | 891.269 K               | 419.4 K                                  |

| <b>Power efficiency<sup>a</sup></b> | 45.6–51.3 K·μm/mW       | 38.7–42.02 (83.28 <sup>b</sup> ) K·μm/mW |

| <b>Endurance</b>                    | Medium                  | High                                     |

| <b>Sensitivity to fabrication</b>   | High                    | Low                                      |

| <b>Footprint</b>                    | 12.5–62 μm <sup>2</sup> | 25–100 μm <sup>2</sup>                   |

| <b>Optical Losses</b>               | 0.02–0.4 dB/μm [17]     | 0.03 dB/μm [13]                          |

<sup>a</sup>Values from fitted P-T trends.

<sup>b</sup>Value from observed increase in lower doped samples post velocity saturation.

## 5. Conclusion

This work has studied the heating response of two different types of embedded doped Si heaters, PIN and single doped devices. Specifically, the geometric effect of the intrinsic region length, and device width for PIN diodes was investigated. The PIN diodes were found to have a larger spread in device operation than expected, and as such are less consistent than the single doped microheaters, as fabricated. Both these devices were held at high DC power, and their steady state temperatures measured through Raman Thermometry methods, and it was found that both types of devices can reach significantly high temperatures under similar applied power densities. We also revealed unexpected heating performances at higher applied powers, showing lower doping can result in more efficient heating in single doped devices. During measurements damage was observed on the positive contacts of each PIN device, notably not at all on the single doped devices, and the impact of this damage on electrical performance was investigated through endurance testing. The endurance testing revealed that while damage does begin to occur at high enough ON time (10 million 1-ms-long pulses) the damage did not affect device operation. From this investigation, it was concluded that both devices have high potentials for large scale embedded heaters for photonic devices, but PIN devices of this nature might require a higher investment in device design and fabrication processes, while single doped microheater devices offer more reliable operation at the cost of requiring higher operating voltages.

## Funding

Office of Naval Research (N000141410765); National Science Foundation (2028624, 2003325, 2105972, 1901864, 2210168/2210169)

## Disclosures

The authors declare no conflicts of interest.

## Data Availability

Data underlying the results presented in this paper are not publicly available at this time but may be obtained from the authors upon reasonable request.

## Supplemental Document

See Supplement 1 for supporting content.

## References

- [1] M. Wuttig, H. Bhaskaran, and T. Taubner, “Phase-change materials for non-volatile photonic applications,” *Nat. Photonics*, vol. 11, no. 8, pp. 465–476, 2017, doi: 10.1038/nphoton.2017.126.

- [2] Y. Zhang, C. Ríos, M. Y. Shalaginov, M. Li, A. Majumdar, T. Gu, and J. Hu, “Myths and truths about optical phase change materials: A perspective,” *Appl. Phys. Lett.*, vol. 118, no. 21, p. 210501, May 2021, doi: 10.1063/5.0054114.

- [3] H. Taghinejad, S. Abdollahramezani, A. A. Eftekhar, T. Fan, A. H. Hosseinnia, O. Hemmatyar, A. Eshaghian Dorche, A. Gallmon, and A. Adibi, “ITO-based microheaters for reversible multi-stage switching of phase-change materials: towards miniaturized beyond-binary reconfigurable integrated photonics,” *Opt. Express*, vol. 29, no. 13, p. 20449, 2021, doi: 10.1364/oe.424676.

- [4] K. Kato, M. Kuwahara, H. Kawashima, T. Tsuruoka, and H. Tsuda, “Current-driven phase-change optical gate switch using indium-tin-oxide heater,” *Appl. Phys. Express*, vol. 10, no. 7, 2017, doi: 10.7567/APEX.10.072201.

- [5] N. Youngblood, C. Talagrand, B. F. Porter, C. G. Galante, S. Kneepkens, G. Triggs, S. Ghazi Sarwat, D. Yarmolich, R. S. Bonilla, P. Hosseini, R. A. Taylor, and H. Bhaskaran, “Reconfigurable Low-Emissivity Optical Coating Using Ultrathin Phase Change Materials,” *ACS Photonics*, vol. 9, no. 1, pp. 90–100, 2022, doi: 10.1021/acspophotonics.1c01128.

- [6] F. Xiong, A. D. Liao, D. Estrada, and E. Pop, “Low-power switching of phase-change materials with carbon nanotube electrodes,” *Science (80-. ).*, vol. 332, no. 6029, pp. 568–570, 2011, doi: 10.1126/science.1201938.

- [7] Z. Fang, J. Zheng, A. Saxena, J. Whitehead, Y. Chen, and A. Majumdar, “Non-Volatile Reconfigurable Integrated Photonics Enabled by Broadband Low-Loss Phase Change Material,” *Adv. Opt. Mater.*, vol. 9, no. 9, 2021, doi: 10.1002/adom.202002049.

- [8] J. Meng, N. Peserico, X. Ma, Y. Zhang, C.-C. Popescu, M. Kang, M. Miscuglio, K. Richardson, J. Hu, and V. J. Sorger, “Electrical Programmable Low-loss high cyclable Nonvolatile Photonic Random-Access Memory,” *arXiv:2203.13337*, 2022,

[Online]. Available: <https://arxiv.org/abs/2203.13337v4>

- [9] Y. Zhang, C. Fowler, J. Liang, B. Azhar, M. Y. Shalaginov, S. Deckoff-Jones, S. An, J. B. Chou, C. M. Roberts, V. Liberman, M. Kang, C. Ríos, K. A. Richardson, C. Rivero-Baleine, T. Gu, H. Zhang, and J. Hu, “Electrically reconfigurable non-volatile metasurface using low-loss optical phase-change material,” *Nat. Nanotechnol.*, vol. 16, no. 6, pp. 661–666, 2021, doi: 10.1038/s41565-021-00881-9.

- [10] S. Abdollahramezani, O. Hemmatyar, M. Taghinejad, H. Taghinejad, A. Krasnok, A. A. Eftekhar, C. Teichrib, S. Deshmukh, M. A. El-Sayed, E. Pop, M. Wuttig, A. Alù, W. Cai, and A. Adibi, “Electrically driven reprogrammable phase-change metasurface reaching 80% efficiency,” *Nat. Commun.*, vol. 13, no. 1, pp. 1–11, 2022, doi: 10.1038/s41467-022-29374-6.

- [11] C. Ríos, Y. Zhang, M. Y. Shalaginov, S. Deckoff-Jones, H. Wang, S. An, H. Zhang, M. Kang, K. A. Richardson, C. Roberts, J. B. Chou, V. Liberman, S. A. Vitale, J. Kong, T. Gu, and J. Hu, “Multi-Level Electro-Thermal Switching of Optical Phase-Change Materials Using Graphene,” *Adv. Photonics Res.*, vol. 2, no. 1, p. 2000034, Jan. 2021, doi: 10.1002/adpr.202000034.

- [12] Z. Fang, R. Chen, J. Zheng, A. I. Khan, K. M. Neilson, S. J. Geiger, D. M. Callahan, M. G. Moebius, A. Saxena, M. E. Chen, C. Ríos, J. Hu, E. Pop, and A. Majumdar, “Ultra-low-energy programmable non-volatile silicon photonics based on phase-change materials with graphene heaters,” *Nat. Nanotechnol.*, vol. 17, no. 8, pp. 842–848, 2022, doi: 10.1038/s41565-022-01153-w.

- [13] C. Ríos, Q. Du, Y. Zhang, C. C. Popescu, M. Y. Shalaginov, P. Miller, C. Roberts, M. Kang, K. A. Richardson, T. Gu, S. A. Vitale, and J. Hu, “Ultra-compact nonvolatile phase shifter based on electrically reprogrammable transparent phase change materials,” *PhotoniX*, vol. 3, no. 1, 2022, doi: 10.1186/s43074-022-00070-4.

- [14] H. Zhang, L. Zhou, L. Lu, J. Xu, N. Wang, H. Hu, B. M. A. A. Rahman, Z. Zhou, and J. Chen, “Miniature Multilevel Optical Memristive Switch Using Phase Change Material,” *ACS Photonics*, vol. 6, no. 9, pp. 2205–2212, Sep. 2019, doi: 10.1021/acsphotonics.9b00819.

- [15] J. Zheng, Z. Fang, C. Wu, S. Zhu, P. Xu, J. K. Doylend, S. Deshmukh, E. Pop, S. Dunham, M. Li, and A. Majumdar, “Nonvolatile Electrically Reconfigurable Integrated Photonic Switch Enabled by a Silicon PIN Diode Heater,” *Adv. Mater.*, vol. 32, no. 31, pp. 1–8, 2020, doi: 10.1002/adma.202001218.

- [16] S. A. Vitale, P. Miller, P. Robinson, C. Roberts, V. Liberman, Q. Du, Y. Zhang, C.-C. Popescu, M. Y. Shalaginov, M. Kang, K. A. Richardson, T. Gu, C. Ríos, and J. Hu, “Phase Transformation and Switching Behavior of Magnetron Plasma Sputtered Ge 2 Sb 2 Se 4 Te ,” *Adv. Photonics Res.*, vol. 3, no. 10, p. 2200202, 2022, doi: 10.1002/adpr.202200202.

- [17] J. R. Erickson, V. Shah, Q. Wan, N. Youngblood, and F. Xiong, “Designing fast and efficient electrically driven phase change photonics using foundry compatible waveguide-integrated microheaters,” *Opt. Express*, vol. 30, no. 8, pp. 13673–13689, 2022.

- [18] G. T. Reed, G. Z. Mashanovich, F. Y. Gardes, M. Nedeljkovic, Y. Hu, D. J. Thomson, K. Li, P. R. Wilson, S. W. Chen, and S. S. Hsu, “Recent breakthroughs in carrier depletion based silicon optical modulators,” *Nanophotonics*, vol. 3, no. 4–5, pp. 229–

245, 2014, doi: 10.1515/nanoph-2013-0016.

[19] D. Patel, V. Veerasubramanian, S. Ghosh, W. Shi, A. Samani, Q. Zhong, and D. V. Plant, “A  $4 \times 4$  fully non-blocking switch on SOI based on interferometric thermo-optic phase shifters,” *2014 IEEE Opt. Interconnects Conf. OI 2014*, vol. 5, pp. 104–105, 2014, doi: 10.1109/OIC.2014.6886101.

[20] R. Ostermeir, K. Brunner, G. Abstreiter, and W. Weber, “Temperature Distribution in Si-MOSFET’s Studied by Micro Raman Spectroscopy,” *IEEE Trans. Electron Devices*, vol. 39, no. 4, pp. 858–863, 1992, doi: 10.1109/16.127476.

[21] E. Yalon, Ö. B. Aslan, K. K. H. Smithe, C. J. McClellan, S. V. Suryavanshi, F. Xiong, A. Sood, C. M. Neumann, X. Xu, K. E. Goodson, T. F. Heinz, and E. Pop, “Temperature-Dependent Thermal Boundary Conductance of Monolayer MoS<sub>2</sub> by Raman Thermometry,” *ACS Appl. Mater. Interfaces*, vol. 9, no. 49, pp. 43013–43020, 2017, doi: 10.1021/acsami.7b11641.

[22] M. Kuball, J. M. Hayes, M. J. Uren, T. Martin, J. C. H. Birbeck, R. S. Balmer, and B. T. Hughes, “Measurement of temperature in active high-power AlGaN/GaN HFETs using Raman spectroscopy,” *IEEE Electron Device Lett.*, vol. 23, no. 1, pp. 7–9, 2002, doi: 10.1109/55.974795.

[23] S. Sandell, E. Chávez-Ángel, A. El Sachat, J. He, C. M. Sotomayor Torres, and J. Maire, “Thermoreflectance techniques and Raman thermometry for thermal property characterization of nanostructures,” *J. Appl. Phys.*, vol. 128, no. 13, 2020, doi: 10.1063/5.0020239.

[24] C. B. Saltonstall, J. Serrano, P. M. Norris, P. E. Hopkins, and T. E. Beechem, “Single element Raman thermometry,” *Rev. Sci. Instrum.*, vol. 84, no. 6, 2013, doi: 10.1063/1.4810850.

[25] T. Beechem, A. Christensen, S. Graham, and D. Green, “Micro-Raman thermometry in the presence of complex stresses in GaN devices,” *J. Appl. Phys.*, vol. 103, no. 12, 2008, doi: 10.1063/1.2940131.

[26] J. W. Pomeroy, M. Kuball, D. J. Wallis, A. M. Keir, K. P. Hilton, R. S. Balmer, M. J. Uren, T. Martin, and P. J. Heard, “Thermal mapping of defects in AlGaN/GaN heterostructure field-effect transistors using micro-Raman spectroscopy,” *Appl. Phys. Lett.*, vol. 87, no. 10, 2005, doi: 10.1063/1.2041823.

[27] E. J. Ryder, “Mobility of Holes and Electrons in High Electric Fields,” *Phys. Rev.*, vol. 90, no. 5, pp. 81–84, 1953.

[28] W. Shockley, “Hot electrons in Germanium and Ohm’s Law,” *Bell Syst. Tech. J.*, vol. 30, no. 4, pp. 990–1034, 1951.

[29] Z. Aksamija, S. Hahm, and U. Ravaioli, “Emission and Absorption of Phonons in Silicon,” *Phys. Status Solidi*, vol. 5, no. 1, pp. 90–93, 2008, doi: 10.1002/pssc.200776563.

[30] K. Natori, “New Solution to High-Field Transport in Semiconductors : II . Velocity Saturation and Ballistic Transmission New Solution to High-Field Transport in Semiconductors ;,” *Jpn. J. Appl. Phys.*, vol. 48, no. 3R, p. 034504, 2009, doi: 10.1143/JJAP.48.034504.

[31] E. Pop, R. Dutton, and K. Goodson, “Detailed Heat Generation Simulations via the

Monte Carlo Method," *Int. Conf. Simul. Semicond. Process. Devices*, pp. 121–124, 2003.

[32] K. H. Yeoh and D. S. Ong, "Steady-state and transient electron transport in silicon : From bulk to monolayer," *AIP Conf. Proc.*, vol. 1877, no. 1, p. 080003, 2017, doi: 10.1063/1.4999893.

[33] D. M. Caughey and R. E. Thomas, "Carrier Mobilities in Silicon Empirically Related to Doping and Field," *Proc. IEEE*, vol. 55, no. 12, pp. 2192–2193, 1967, doi: 10.1109/PROC.1967.6123.