# A 0.4-4 THz p-i-n Diode Frequency Multiplier in 90-nm SiGe BiCMOS

Sidharth Thomas<sup>®</sup>, Graduate Student Member, IEEE, Sam Razavian<sup>®</sup>, Student Member, IEEE, Wei Sun, Student Member, IEEE, Benyamin Fallahi Motlagh<sup>®</sup>, Student Member, IEEE, Anthony D. Kim<sup>®</sup>, Student Member, IEEE, Yu Wu, Student Member, IEEE, Benjamin S. Williams<sup>®</sup>, Senior Member, IEEE, and Aydin Babakhani<sup>®</sup>, Senior Member, IEEE

Abstract—This article introduces a silicon-based source that can radiate power from the lower end of the terahertz (THz) spectrum into the far-infrared region. The radiator consists of a millimeter-wave (mm-wave) oscillator that drives a PIN diode multiplier. The p-i-n diodes exhibit reverse recovery when driven strongly, and the diode switches a large amount of current in a short interval. This process is highly non-linear and generates a harmonic-rich waveform, which is utilized here for higher harmonic generation. An on-chip folded dipole antenna is used to radiate the generated THz signal. The harmonic radiation properties of the folded dipole are analyzed and presented here. Wireless harmonic injection locking is also demonstrated in this work in order to synchronize the chip to an external source. Designed in GlobalFoundries 90-nm SiGe BiCMOS process, the chip has an effective isotropic radiated power (EIRP) of 13 dBm and -14.2-dBm radiated power at 0.39 THz. The chip is characterized up to 0.8 THz using Virginia Diodes (VDI) mixers, and an EIRP of -3.8 dBm is measured at 0.78 THz. In order to measure the radiated tones at higher frequencies, Fourier-transform infrared (FTIR) spectroscopy is used with a room-temperature deuterated triglycine sulfate (DTGS) detector. Measurement results confirm the presence of tones extending from the THz region into the far-infrared region, with an SNR of 18.4, 14, 9.3, and 6.7 dB at 1.17, 2.21, 3.25, and 4.03 THz, respectively. This work is the first demonstration of a silicon source capable of generating detectable tones at far-infrared frequencies.

Index Terms—Far infrared, folded dipole, Fourier-transform infrared (FTIR), frequency multiplier, injection locking, millimeter wave (mm-wave), p-i-n diode, SiGe, terahertz (THz).

#### I. Introduction

THE terahertz (THz) band of the electromagnetic spectrum, from 0.3 to 3 THz, has been of increasing interest in recent years due to its unique position between RF and optical frequencies in the electromagnetic spectrum [1]. This band offers several attractive features from both ends of the spectrum. THz has a much smaller wavelength than RF and attenuates less than optical frequencies, making it an optimal candidate for high-resolution imaging and radar. Micro-Doppler radars at THz frequencies can enable high-precision

Manuscript received 2 February 2023; revised 17 May 2023 and 10 June 2023; accepted 19 June 2023. Date of publication 4 July 2023; date of current version 25 August 2023. This article was approved by Associate Editor Yuriy Greshishchev. (Corresponding author: Sidharth Thomas.)

The authors are with the Department of Electrical Engineering, University of California at Los Angeles, Los Angeles, CA 90095 USA (e-mail: sidhthomas@ucla.edu).

Color versions of one or more figures in this article are available at https://doi.org/10.1109/JSSC.2023.3289129.

Digital Object Identifier 10.1109/JSSC.2023.3289129

sub- $\mu$ m vibration sensing [2]. THz also finds applications in spectroscopy since several gases exhibit absorption windows within the THz band. Due to the vast amount of unallocated spectrum, THz can enable multi-Gb/s communication [3]. The far-infrared frequency range beyond 3 THz also offers several applications in astronomy and medicine [4].

However, the THz band has largely remained commercially untapped due to the challenges in the THz generation. The electronics and photonics community have attempted to bridge the THz gap [5]. However, these have only been successful to some extent, and there is significant interest in designing energy-efficient and economically viable THz sources.

Photonic approaches to THz generation are mainly limited by the lack of materials that have sufficiently small bandgaps, which can generate THz. Typical THz generation approaches involve techniques, such as difference frequency generation, photo-mixing, quantum cascade lasers, and photo-conductive antennas. These approaches have severe limitations that prevent commercial use. They are bulky, require cryogenic operating conditions, and are sometimes limited to slow pulsed operation [6], [7].

On the electronics front, silicon-based THz generation is of interest due to its digital circuit integration capabilities. Advanced CMOS nodes offer  $f_T/f_{\rm max}$  as high as 350/370 GHz [8]. Heterojunction bipolar transistors (HBTs) in commercial SiGe BiCMOS processes have achieved  $f_T/f_{\rm max}$  as high as 470/610 GHz [9]. HBTs also offer a higher breakdown voltage when compared to CMOS. Despite this, the highest frequency reported for a fundamental oscillator in silicon is 300 GHz [10]. This is due to the challenges in fundamental oscillator design at frequencies above  $f_{\rm max}/2$ . Harmonic generation approaches need to be used to generate power at higher frequencies.

Among existing literature, only a few silicon-based sources operate beyond 1 THz. In [11], a 1-THz radiator array is implemented using 91 oscillators having a fundamental frequency of 250 GHz. Active frequency multipliers have been presented in [12], [13], and [14] to generate power at 0.92, 1, and 1.4 THz, respectively. A harmonic oscillator is demonstrated in [15], with tones observed up to 2.45 THz. These tones were measured using a highly sensitive cryogenic bolometer detector. Compound semiconductor-based approaches have also been demonstrated [16], [17], [18]. However, these technologies do not offer the same extent of digital integration capabilities as silicon.

There is a need for silicon-based integrated solutions for THz generation. Existing works use the non-linearity in varactors and transistors to generate THz. These devices show weak non-linearity, which ultimately limits the generated harmonic power. Highly efficient harmonic generation was demonstrated in the 1960s at lower microwave frequencies using discrete step-recovery diodes (a category of p-i-n diodes). These devices are highly non-linear due to strong reverse recovery, and this was utilized for comb generation and high-efficiency harmonic generation [19], [20].

In our previous work [21], we report pulse generation using reverse recovery in silicon p-i-n diodes. A digital trigger at 15 GHz is used to excite a p-i-n diode into reverse recovery. During reverse recovery, p-i-n diodes generate a highly non-linear waveform rich in harmonics. Measurement results showed that strong tones were generated and could be measured up to 1.1 THz. This confirms the highly non-linear nature of the p-i-n diode since a 15-GHz signal could generate a tone at its 73rd harmonic at 1.1 THz. However, in [21], the digital trigger signal could not be increased beyond 15 GHz. Due to this low repetition rate, the generated power is low at high frequencies and cannot generate detectable tones beyond 1.1 THz.

This work builds on the p-i-n diode pulse generator from [21]. The goal here is to maximize the number of harmonics generated and study the possibility of signal generation beyond 1 THz. In this work, the p-i-n diode is driven using an on-chip millimeter-wave (mm-wave) oscillator at 130 GHz. The oscillator follows a standard Colpitt's topology [22], [23]. Because of the mm-wave trigger, the p-i-n diode can generate detectable tones at THz frequencies and even into the farinfrared region. A folded dipole antenna is used because of its impedance profile and harmonic radiation properties, which are explained in Section IV. This work also proposes wireless harmonic injection locking to lock the chip to an external source. Wireless locking consumes no dc power and does not limit the tuning range of the mm-wave LO. Using a Fourier-transform infrared (FTIR) spectrometer, broadband measurements are performed to measure the radiation up to 6 THz. This is the first demonstration of silicon-based generation above 2.5 THz. This work was presented in [24], and a detailed analysis is provided in this article.

The rest of this article is organized as follows. Section II explains the fundamentals of a p-i-n diode, reverse recovery mechanism and gives a general approach to frequency multiplier design. The circuit design details are explained in Section III. Section IV explains the antenna design and analysis and wireless harmonic injection locking. Measurement results are presented in Section V, and this article is concluded in Section VI.

## II. P-I-N DIODE

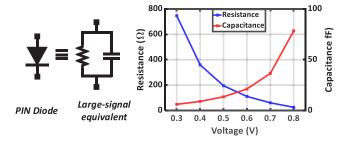

A p-i-n diode is a semiconductor diode with an undoped intrinsic region positioned between two heavily doped p+ and n+ semiconductor regions. Fig. 1(a) shows the doping profile of a p-i-n diode. The presence of the intrinsic region differentiates a p-i-n diode from a regular diode. Conventionally, these diodes are used in RF/microwave switches, attenuators,

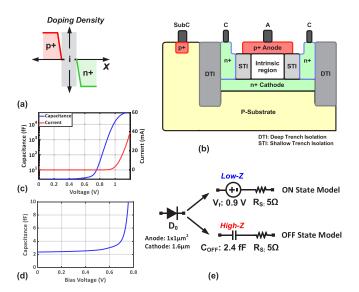

Fig. 1. (a) Doping profile of a p-i-n diode. (b) Illustration of a p-i-n diode in the GlobalFoundries 90-nm process. (c) Diode I-V and C-V curves. (d) Diode C-V curve (re-plotted to show depletion capacitance). (e) Small-signal model of the p-i-n diode during ON and OFF states.

limiters, photodetectors, and step-recovery diodes [25], [26]. The p-i-n diodes can easily be fabricated in standard silicon processes without any additional masks and are provided as standard cells in some process design kits (PDKs). Fig. 1(b) shows the structure of a p-i-n diode in GlobalFoundries 9HP PDK. It consists of a p+ anode, an intrinsic region, and an n+ cathode. The intrinsic region is realized using an n-layer in 9HP. A deep trench surrounds the diode for isolation. These diodes have low parasitic capacitance and a high breakdown voltage [27].

# A. Reverse Recovery in p-i-n Diodes

For the analysis presented in this article, we use the default p-i-n diode model from the GlobalFoundires 90-nm SiGe BiCMOS process (9HP—V1.2) PDK. Otherwise specified, the diode chosen has an anode area of  $1\times 1~\mu m$  and a cathode width of 1.6  $\mu m$ . The reasons for choosing this size are explained later in this section.

The I-V and the C-V behavior of the diode are plotted in Fig. 1(c) and (d), respectively. The C-V curve is obtained through small-signal Y-parameter simulations. The dominant capacitance is the diffusion capacitance when the diode is ON and the depletion capacitance when the diode is OFF. Due to the large diffusion capacitance, the diode behaves like a voltage source when ON and can sink a large current. When OFF, the diode behaves as a high-impedance capacitor (2.4 fF at 0-V bias). Based on this, a small-signal equivalent circuit for a p-i-n diode is given in Fig. 1(e) for both ON and OFF states. The diode contact resistance is also included in this model.

During a large-signal drive cycle, the p-i-n diode switches abruptly from the low-impedance ON stage to the high-impedance OFF stage. The abrupt switching is due to the reverse recovery and is the basis for multiplier design. A detailed analysis of a charge storage model for reverse recovery can be found in [28].

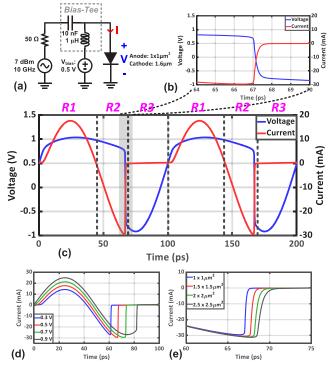

Fig. 2. (a) p-i-n diode driven by a 7-dBm RF source at 10 GHz. (b) and (c) Corresponding voltage and current waveforms simulated using SpectreRF. (d) Current waveform for different  $V_{\rm bias}$ 's. (e) Current waveform for different diode sizes (waveform is magnified to show the variation in slope).

The reverse recovery phenomenon can be understood by analyzing the circuit in Fig. 2(a). Here, the p-i-n diode is driven by an RF source at 10 GHz. A power level of 7 dBm is chosen such that there is sufficient power to drive the diode into reverse recovery under unmatched impedance conditions. The selection of the dc bias and diode size is explained later in this section. The corresponding voltage and diode current waveforms for the circuit in Fig. 2(a) under the above bias and drive conditions (simulated using SpectreRF) are plotted in Fig. 1(b) and (c). Three distinct regions of operation can be observed and are explained as follows.

During R1, the diode is in forward conduction mode. The p+ and n+ regions inject electrons and holes into the I-region. Due to the long minority carrier lifetime,  $\tau$  (>1 ns as per simulations), these carriers get stored in the I-region. The amount of stored charge  $Q_i$  for a diode current I is given by

$$I = \frac{dQ_i}{dt} + \frac{Q_i}{\tau}. (1)$$

Because of this carrier storage, a large diffusion capacitance is formed [Fig. 1(c)]. The voltage across the diode is clamped to the diode turn-on voltage  $V_f$ , which is about 0.9 V in this process.

During R2, the diode enters the reverse conduction mode, and the diode continues to conduct by depleting the stored carriers. The voltage across the diode still remains approximately equal to  $V_f$ .

Once all the carriers are depleted, the diode can no longer sustain current and undergoes reverse recovery. This is denoted in region R3. The current across the diode abruptly switches to zero (in <1 ps as per simulations), and the diode turns off. The time constant for the reverse current switching to zero,  $\tau_t$ , depends on the diode capacitance and junction resistance and is independent of the frequency of the source that drives the p-i-n diode. This enables realizing sharp switching using p-i-n diodes. Once all the carriers are depleted, the diode behaves like a small depletion capacitance [Fig. 1(d)]. To summarize, the p-i-n diode switches a large amount of current in a short interval due to reverse recovery.

## B. Bias and Diode Size Selection

The fast switching behavior makes p-i-n diodes a prime candidate for building frequency multipliers. The generated harmonic content is proportional to the rate of switching (di/dt). For multiplier design, we wish to maximize the amount of current that is being switched while minimizing the time taken for switching. The former can be maximized by choosing the dc bias of the diode such that it undergoes reverse recovery while carrying peak current. This is shown in Fig. 2(d), where  $V_{\text{bias}}$  is varied, while the diode size is fixed. In this example,  $V_{\text{bias}}$  of 0.5 V switches more current compared to other biases. Note that this bias can vary with the amount of input RF power.

The time taken for switching can be minimized by proper diode size selection. While larger diodes have less contact resistance, smaller diodes have less capacitance. It is shown in [21] that smaller diodes present sharper reverse recovery and time to switch. This is shown in Fig. 2(e), where  $V_{\rm bias}$  is fixed at 0.5 V, while the diode size is varied. It can be seen that the anode area of  $1\times 1~\mu{\rm m}$  presents the fastest switching, and this size is chosen for multiplier design in this work. While choosing the cathode area, we chose a large cathode width of 1.6  $\mu{\rm m}$ . This is because a larger cathode allows low-impedance contacts to the diode. Since the cathode is connected to an RF ground, its size does not contribute to parasitic capacitance.

# C. p-i-n Diode Multiplier Design

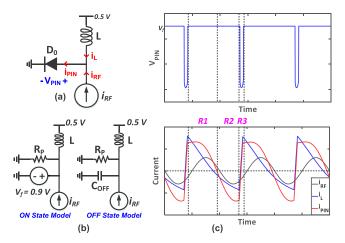

Based on the discussion above, we present an approach to multiplier design. A p-i-n diode driven by an ac current source is given in Fig. 3(a). The diode is replaced by its small-signal equivalent in Fig. 3(b). Here,  $R_P$  models the losses in the circuit.

The voltage and current waveforms for the ideal circuit in Fig. 3(b) are plotted in Fig. 3(c). In region R1, the current source provides a large-signal RF current to the p-i-n diode, which turns it on. The intrinsic region of the p-i-n diode gets filled with carriers during R1, and the voltage across the diode gets clamped to  $V_f$  ( $\approx$ 0.9 V). Since a dc voltage appears across the inductor, it conducts a ramp current during this interval, all of which sinks into the diode. In region R2, the current source has a negative current. The p-i-n diode can source this current due to the presence of stored carriers. The voltage across the diode remains clamped to  $V_f$ . However, reverse conduction depletes these carriers. The carriers eventually run out, and the diode turns off (region R3). Once OFF, the diode behaves like a capacitor,  $C_{\text{OFF}}$ . However,

Fig. 3. (a) p-i-n diode multiplier at  $f_0$ . (b) Equivalent circuit model of the p-i-n diode multiplier during ON and OFF states. (c) Voltages and currents in the idealized p-i-n diode multiplier.

KCL has to be satisfied, which forces the inductor to source the required current. The sudden change in inductor current creates a sharp negative voltage pulse at the diode. The height and width of this pulse depend on the quality factor of the LC tank. This voltage pulse causes a damped oscillation in the RLC circuit and charges  $C_{\rm OFF}$ . Once the diode is sufficiently charged, it starts conducting and enters forward conduction (region R1). This cycle is repeated.

The generated voltage pulse is rich in harmonics, and this circuit can behave like a comb generator when connected to a resistive load. When connected to a resonant load at a harmonic, this circuit can efficiently generate just that harmonic. It should be noted that the diode bias voltage sets the inductor current, which can be adjusted to change the onset of reverse recovery. Choosing a diode bias where the diode turns off while carrying peak reverse current will create the sharpest pulse. Based on this, the following design procedure is adopted.

- Appropriate selection of diode size and biasing as discussed above.

- Perform a conjugate match between the p-i-n diode and the RF source using the large-signal impedances at the fundamental frequency.

- 3) If a large number of output harmonics are desired (such as a frequency comb), connect the load to the p-i-n diode while avoiding additional matching networks.

- 4) If high power is required at a specific harmonic, connect a resonant load at that frequency to the p-i-n diode. The unwanted harmonics can be reactively terminated.

## III. CIRCUIT DESIGN

This section explains the circuit design techniques. We design the circuit with the goal of maximizing the number of harmonics generated in order to study the possibility of signal generation beyond 1 THz.

# A. mm-Wave Colpitts Oscillator

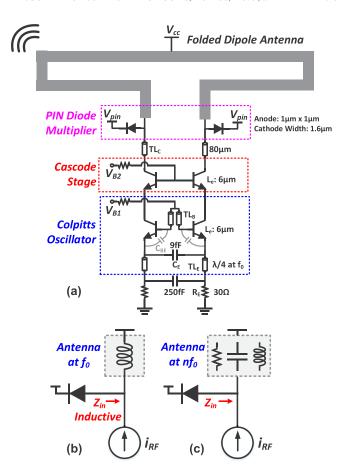

A differential Colpitts oscillator is used in this design to drive the p-i-n diode. Fig. 4(a) shows the schematic of the

Fig. 4. (a) Schematic of an mm-wave Colpitts oscillator driving a p-i-n diode multiplier and folded dipole antenna. (b) Equivalent circuit model of the oscillator-multiplier-antenna system at  $f_0$ . (c) Equivalent circuit model of the oscillator-multiplier-antenna system at higher harmonics.

Colpitts oscillator. The Colpitts tank formed by the capacitor  $C_E$ , the parasitic  $C_{\rm BE}$ , and the base transmission line (TL) TL<sub>B</sub> sets the resonance frequency to 130 GHz. TL<sub>B</sub> is shorted to a resistor, ensuring that the oscillator only starts up in the required odd mode. In the odd-mode conditions, the resistor appears on the virtual ground and does not load the tank. The emitter is connected to a TL, which is  $\lambda/4$  at the fundamental frequency  $f_0$ . This line creates a high impedance and does not load the oscillator core. Resistors  $R_E$  are used to set the bias. Alternatively, a single resistor of  $0.5R_E$  can also be used with a shunt capacitor to set the bias. An active current source bias is avoided since this would result in an upconversion of the flicker noise and can impact the phase noise performance of the oscillator.

Frequency tuning is achieved by changing the base voltage,  $V_{B1}$ , which varies the capacitance  $C_{\rm BE}$  and shifts the tank resonance. This frequency tuning method is advantageous at mm-wave frequencies compared to other techniques, such as varactor tuning, which is lossy and can degrade the quality factor of the resonance tank. However, changing the base voltage also changes the bias current. At a frequency away from the center frequency, the oscillator generates less power, and consequently, the generated harmonic power degrades. A cascode transistor driver stage connects the oscillator core to the p-i-n diode. This stage buffers the oscillation and

Fig. 5. Large-signal equivalent circuit and simulated large-signal input impedance for different voltage biases across the diode.

drives the p-i-n diode multiplier through  $TL_C$ , which performs impedance matching at the fundamental frequency. Under optimal bias conditions, when the transistors are biased at peak  $f_{\rm max}$ , the oscillator generates 5-dBm power and consumes 23 mA.

## B. p-i-n Diode Frequency Multiplier

The p-i-n diode is directly connected to a folded dipole antenna, as shown in Fig. 4(a). The diode size is chosen to have an anode area of  $1 \times 1 \mu m$  and a cathode width of 1.6  $\mu m$  based on the discussions in Section II. The antenna simultaneously behaves like an inductor at the fundamental frequency,  $f_0$ , and radiates at the other harmonics. Analysis of this antenna is provided in Section IV. Fig. 4(b) and (c) shows a simplified picture of the oscillator-multiplier-antenna system. An ac current source drives a p-i-n diode connected to the antenna. At  $f_0$ , the diode sees an inductive impedance, and at other harmonics, the diode sees the antenna load.

Due to the non-linear nature of multipliers, the large-signal impedance needs to be considered. The large-signal impedance of the diode at 130 GHz is simulated using SpectreRF and is plotted in Fig. 5. Here, the x-axis denotes the dc voltage across the diode. It can be observed that as the bias voltage increases, the diode turns on, and the impedance of the diode drops. The diode-antenna inductor circuit is large-signal impedance matched to the oscillator at the fundamental frequency using  $TL TL_C$ . Since the goal is to maximize the harmonic content at multiple frequencies, additional matching networks to match the antenna and isolate the oscillator core are not used. This is because matching networks are narrow-band and can add loss, which becomes increasingly significant at upper THz frequencies. This may be pursued if a specific harmonic is of interest.

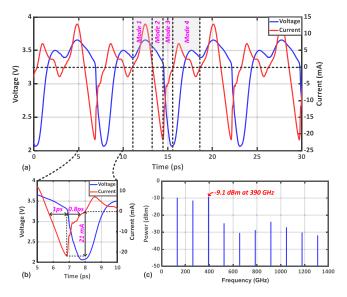

The p-i-n diode multiplier behavior from Fig. 4(a) is simulated using SpectreRF. A broadband SNP file (common file format for storing S-parameter data) models the antenna. The voltage at the antenna node and the current flowing into the p-i-n diode is plotted in Fig. 6(a), and the waveforms are analyzed. In Mode 1, the diode is in forward conduction, and the intrinsic region is filled with excess carriers. The diode enters reverse conduction in Mode 2. By the end of Mode 2, the carriers get depleted, and the diode stops conducting. The inductive antenna is forced to source the current, creating a sharp negative impulse voltage (Mode 3). This current also charges the diode, and it enters forward conduction

Fig. 6. (a) Simulated voltage at the antenna node and current flowing into the p-i-n diode for the circuit in Fig. 2(a). (b) Magnified view. (c) Simulated spectrum of the power flowing into the antenna.

again. In Mode 4, due to the finite Q of the system, the circuit undergoes damped oscillations and eventually settles and reenters forward conduction (Mode 1).

During this drive cycle, the peak negative current is 21 mA, with a 10% fall time and rise time of 1 and 0.8 ps, respectively. This is magnified in Fig. 6(b). A spectrum of the simulated amount of power that enters the antenna is plotted in Fig. 6(c). The antenna efficiency is not considered here. A peak power of -9.1 dBm is observed at the third harmonic.

#### IV. FOLDED DIPOLE ANTENNA—DESIGN AND ANALYSIS

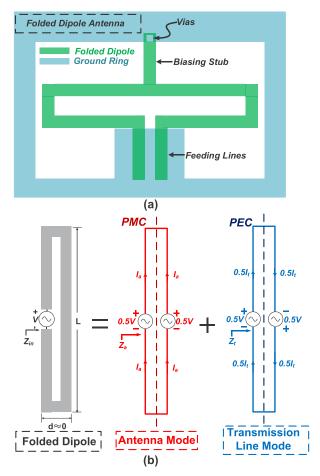

The p-i-n diode requires an inductive load at the fundamental frequency for efficient harmonic generation, and the generated harmonics need to be efficiently radiated. This work achieves both these requirements simultaneously by using a folded dipole antenna. The folded dipole also has harmonic radiation properties, which enables its use over the broad frequency range.

The folded dipole antenna used in this work is shown in Fig. 7(a). It is designed to have good radiation at the third harmonic (390 GHz), with the length,  $L = \lambda/2$  at 390 GHz. A biasing stub line is connected to the antenna in order to bias the oscillator. A ground ring is placed around the antenna for isolation.

The folded dipole antenna is basically an unbalanced TL and can be analyzed by dividing its current into two modes: an antenna mode and a TL mode. This is shown in Fig. 7(b). To simplify the analysis, the spacing d between two individual dipoles is assumed to be negligible. The input impedance of the folded dipole is given by [29]

$$Z_{\rm in} = \frac{4Z_t Z_a}{2Z_a + Z_t} \tag{2}$$

were  $Z_t$  and  $Z_a$  stand for the input impedance of the TL mode and the antenna mode, respectively. Using this method, the impedance and radiation characteristics of the folded dipole antenna at several harmonics are analyzed.

Fig. 7. (a) Folded dipole antenna. (b) Equivalent antenna mode and TL mode of the folded dipole antenna.

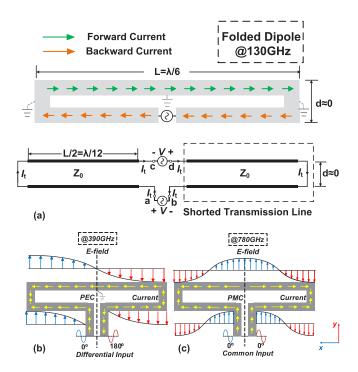

# A. Fundamental Harmonic (130 GHz)

The oscillator excites the antenna differentially at the fundamental harmonic. Because of this, the bias line lies on a perfect electric conductor (PEC) plane with a virtual ground and can be ignored. Fig. 8(a) shows the model of the folded dipole at the fundamental frequency. Since the dipole has  $L=\lambda/2$  at the third harmonic, the effective length of each half side is  $\lambda/12$  at the fundamental. Thus, the length of each half is less compared to the fundamental wavelength, and we can assume that the current distributions on two parallel wires are nearly identical in amplitude but opposite in direction. These two currents can be seen as the forward current and the reverse current of a two-wire TL. Since the two wires are connected at the end, the TL is shorted with a length of  $L=\lambda/12$ . The input impedance is identical to the single-side TL and is given by

$$Z_t = \frac{V}{I_t} = j Z_0 \tan(\beta L/2) \tag{3}$$

where  $Z_0$  and  $\beta$  represent the characteristic impedance and phase constant of the two-wire TL, respectively. Therefore, when  $L/2 = \lambda/12$ , the folded dipole antenna can provide an inductive impedance to the p-i-n diode without requiring an additional matching network. In contrast, when a regular dipole is driven at low frequencies (where  $L < \lambda/2$ ), it will

Fig. 8. (a) Folded dipole antenna behaving like a TL at the fundamental frequency of 130 GHz. (b) Antenna behavior at 390 GHz. (c) Antenna behavior at 780 GHz.

present a capacitive load. This is because the regular dipole behaves like a TL, which transforms a high-impedance open through an  $L < \lambda/2$  line to a capacitive impedance that lies on the bottom half of the Smith chart.

# B. Third Harmonic (390 GHz)

The folded dipole antenna is designed to have optimum radiation at 390 GHz, and the length, L, is chosen to be  $\lambda/2$  at 390 GHz. According to the TL mode analysis,  $Z_t$  can be written as

$$Z_t = \frac{V}{I_t} = [jZ_0 \tan(\beta L/2)]_{(L=\lambda/2)} = \infty.$$

(4)

Therefore, the total input impedance is derived as follows:

$$Z_{\rm in} = 4Z_d \tag{5}$$

where  $Z_d$  is the impedance of an isolated dipole antenna. Equation (5) shows that the input impedance of the folded dipole is four times that of a regular dipole antenna. The current and electric field distribution of the folded dipole antenna at 390 GHz are given in Fig. 8(b). Note that the TL mode is extensively suppressed at this frequency since the currents in the two parallel wires are the same in amplitude and direction. Therefore, it can be regarded as two regular dipoles placed near each other, resulting in good radiation combining.

This analysis can be generalized to any odd multiples of 390 GHz, such as 1170 and 1950 GHz. Although the antenna is electrically longer than  $L = \lambda/2$  at these frequencies, the currents in the extra electrical length cancel each other and do not affect radiation.

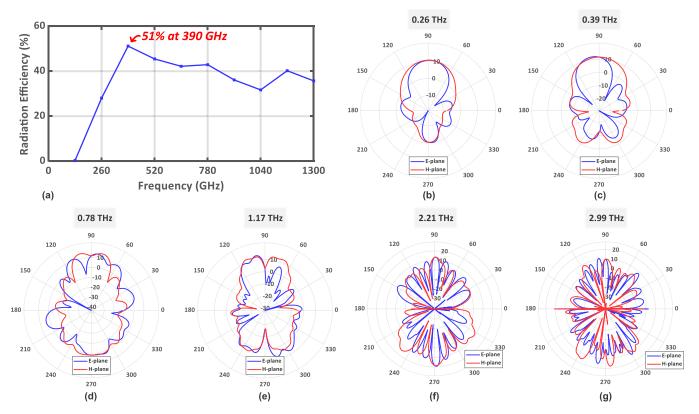

Fig. 9. (a) Simulated antenna efficiency. (b)–(g) Simulated radiation pattern of the antenna at 0.26, 0.39, 0.78, 1.17, 2.21, and 2.99 THz, respectively. The radial axis shows directivity.

#### C. Even Harmonics

The analysis of the folded dipole is challenging at even harmonics. The even harmonics generated from the p-i-n diode multiplier are in-phase, and the antenna is driven in common mode. This means that the bias line and the ground-isolation ring will impact radiation behavior.

At frequencies that are even multiples of 390 GHz, the electrical length of the folded dipole is a multiple of  $\lambda$ . For example, at the sixth harmonic, the length  $L=\lambda$  and the current and E-field distributions are shown in Fig. 8(c). The currents on the two main lines are identical in amplitude and direction. However, the currents flow in opposite directions at the left/right side of the antenna. Ideally, the radiations will cancel each other. However, because of the silicon lens, the two halves behave as two individual folded monopoles placed away from the axis of the lens and will produce a beam that does not fully get canceled. Moreover, the bias line and the ground ring will have currents that cause radiation. Because of this, the antenna radiates in both horizontal polarization (HP) and vertical polarization (VP).

At other even harmonics, which are not multiples 390 GHz, the antenna behavior becomes very challenging to predict and is not analyzed here. However, as observed in simulations and measurements, the antenna radiates in both HP and VP.

# D. Radiation Pattern and Efficiency

To better demonstrate the performance of the folded dipole antenna, the radiation pattern and efficiency at different harmonics are simulated using CST studio. A high-resistive hyper-hemispherical silicon lens is used, which reduces substrate modes and enhances the directivity. The antenna with the lens takes unreasonable simulation times at THz frequencies. To reduce simulation time, the simulations are performed using a lens with a 0.6 mm radius up to 1.3 THz. Beyond this, a lens radius of 0.3 mm is used. The simulated efficiency and radiation patterns are plotted in Fig. 9. It can be seen that the radiation efficiency at 130 GHz is close to zero, thus validating that the folded dipole behaves more like a TL instead of an antenna at this frequency. The antenna has the highest efficiency of 51% at 390 GHz. The radiation efficiency remains largely unaffected beyond 390 GHz due to minimal changes in both ohmic loss in copper and the dielectric loss in the substrate. The antenna radiation pattern is clean at 260 and 390 GHz. Multiple sidelobes start to appear above 1 THz. Due to the small wavelength at these frequencies, the antenna becomes electrically very large  $(L > \lambda)$  and behaves as multiple small antennas, all of which provide beams that are focused in different directions by the lens.

To conclude the antenna analysis, although the folded dipole antenna behaves best at 390 GHz, it can still radiate at other harmonics with good efficiency and reasonable radiation pattern. The antenna also behaves like an inductor at 130 GHz, which is essential for multiplier operation.

# E. Wireless Locking

Some THz applications, such as spectroscopy and coherent detection, require precise frequency and phase alignment with good phase noise [30]. This may be achieved using

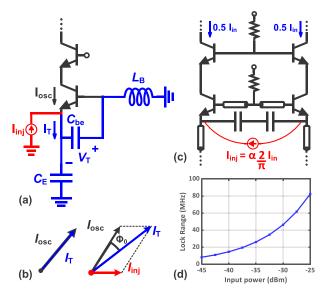

Fig. 10. (a) Half-circuit of oscillator core under external injection  $I_{\text{inj}}$ . (b) Current phasors. (c) Oscillator under an injection current at the second harmonic. (d) Calculated lock range versus injection power.

a phase-locked loop (PLL) or a frequency multiplier chain. These, however, are challenging to build at THz frequencies, consume high dc power, and offer limited frequency tuning. This work demonstrates harmonic wireless injection locking. A harmonic of the fundamental oscillation frequency is injected wirelessly into the chip and is used for locking. Wireless locking does not take any additional dc power. By tuning the frequency of the external source, the entire frequency range of the on-chip oscillator can be covered. Wireless locking also enables frequency synchronization among an array of independent chips.

This work uses an external source at twice the fundamental frequency,  $2f_0$ , to lock the chip. The external source is radiated to the top side of the chip so that it does not block the backside radiation coming from the chip. The folded dipole antenna receives this external signal in its common mode. The 260-GHz locking signal in this work is generated using commercial test equipment. A separate silicon chip may be employed to generate this signal.

The injection locking analysis from [31] and [32] is extended to this work. Fig. 10(a) shows a half-circuit of the oscillator core when injected with an external current source  $I_{\rm inj}$ . The tank has a quality factor of 9, as per simulations. The resultant tank current  $I_T$  consists of the transconductor current  $I_{\rm osc}$  and the injected current  $I_{\rm inj}$ .  $I_{\rm inj}$  creates a phase difference between  $I_T$  and  $I_{\rm osc}$ , shifting the oscillation frequency to  $f_{\rm inj}$  by making the tank compensate for the introduced excess phase. These currents are visualized in Fig. 10(b), and all the phasors are normalized to  $I_{\rm inj}$ .

The wireless injection signal received at  $2f_0$  generates a common-mode injection current,  $I_{\rm in}$ , flowing toward the core, as shown in Fig. 10(c). This current mixes with the fundamental oscillator current in the core [31], and results in a differential injection current  $I_{\rm inj}$ , around the fundamental frequency

$$I_{\rm inj} = \alpha \frac{2}{\pi} I_{\rm in} \tag{6}$$

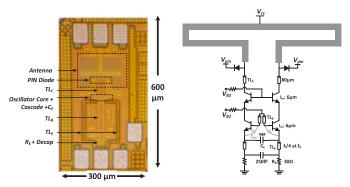

Fig. 11. Die micrograph indicating the circuit components.

Fig. 12. (a) Measurement setup used for characterizing the chip using VDI mixers. (b) Measured tuning range at 390 GHz.

where  $\alpha$  is a loss factor that accounts for the fraction of  $I_{\rm in}$  that reaches the core and gets mixed. Simulations show  $\alpha$  to be 0.125. Using the analysis in [31], under the weak injection assumption, we estimate the one-sided lock range to be

$$f_L \approx \frac{f_0}{2Q} \frac{I_{\rm inj}}{I_{\rm osc}} = \frac{f_0}{\pi Q} \frac{\alpha I_{\rm inj}}{I_{\rm osc}}.$$

(7)

The calculated double-sided lock range at the third harmonic, 390 GHz, is plotted in Fig. 10(d). These calculations match simulations at high injected powers (>-10 dBm). At lower injected powers, the simulation takes unreasonably long to converge.

# V. MEASUREMENTS

The design was fabricated in GlobalFoundires 90-nm SiGe BiCMOS process (9HP—regular variant V1.2). This process has n-p-n transistors with  $f_T = 300$  GHz,  $f_{\rm max} = 360$  GHz, and BV<sub>CEO</sub> = 1.7 V [33]. A die micro-graph is shown in Fig. 11. The design occupies an area of 0.18 mm<sup>2</sup> (including pads) and consumes 70-mW dc power in nominal operation. The chip is mounted on a custom-designed PCB, and a hyperhemispherical silicon lens of a 6 mm radius is attached to the backside of the chip. An undoped high-resistive dual-side-polished (DSP) silicon wafer of 0.5-mm thickness is placed between the chip and the lens.

# A. Radiation Measurements

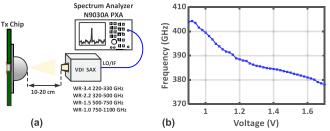

The antenna is designed to radiate efficiently at 390 GHz; hence, the chip is characterized mainly at that frequency. Fig. 12(a) shows the measurement setup used to characterize the effective isotropic radiated power (EIRP). The chip is kept at a far-field distance of 20 cm from a Virginia Diodes (VDI) WR 2.2 spectrum analyzer extender (SAX). The VDI SAX is used in the spectrum analyzer extension mode with an

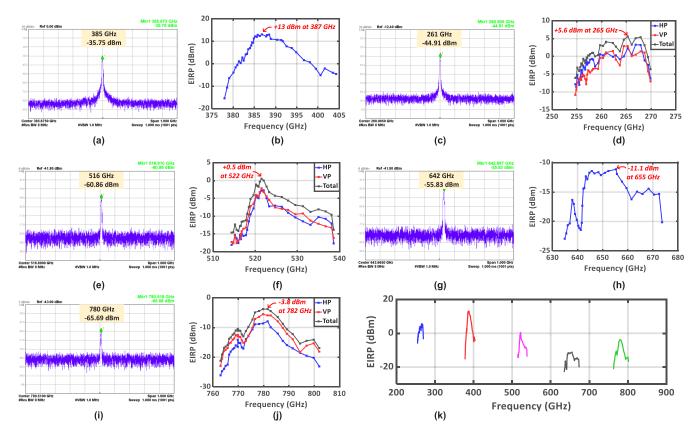

Fig. 13. (a)-(j) Measured tones and the corresponding EIRP spectrum at harmonics of 130 GHz. (k) EIRP variation across multiple harmonics.

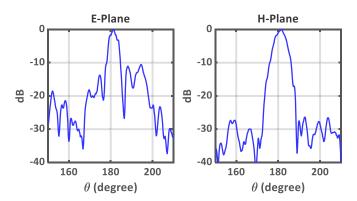

Fig. 14. Measured radiation pattern along the E-plane and H-plane at 390 GHz.

Agilent N9030A spectrum analyzer. The measured spectrum at 385 GHz is plotted in Fig. 13(a). The oscillation frequency is varied by changing the base voltage, and the voltage tuning curve is plotted in Fig. 12(b). A 6% tuning range covering a span of 24 GHz is obtained at 390 GHz.

The EIRP is measured at different harmonics of the fundamental frequency, from 260 (second harmonic) to 780 GHz (sixth harmonic). Multiple VDI SAXs are used to cover the whole band (WR3.4, WR2.2, WR1.5, and WR1). For the WR3.4 and WR2.2 measurements, the chip is kept at a 20-cm distance, while for WR1.5 and WR1, the chip is kept at a 10-cm distance from the VDI SAX. The measured tones across the bands are plotted in Fig. 13(a), (c), (e), (g), and (i). The base voltage is varied, and the radiated powers are

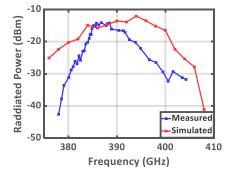

Fig. 15. Measured and simulated radiated powers at the third harmonic.

measured across the tuning range. It should be noted that the chip radiates along the HP for odd harmonics. For even harmonics, the chip radiates along both HP and VP. This matches the conclusions from the antenna analysis section.

The EIRP is calculated by de-embedding the free-space path loss, VDI downconversion loss, VDI antenna gain, and cable loss. The measured EIRP around different harmonics are plotted in Fig. 13(b), (d), (f), (h), and (j). The highest EIRP of +13 dBm is observed for the third harmonic at 387 GHz. This matches the expectations and simulation results since the antenna radiates optimally at that frequency. The chip radiates along two orthogonal polarizations for the even harmonics, and the total EIRP is obtained by summing them. At the second harmonic, a peak EIRP of +5.6 dBm is measured at 265 GHz. At the fourth harmonic, a peak EIRP of +0.5 dBm

Fig. 16. (a) Measurement setup used to demonstrate wireless locking. (b) Photograph of the measurement setup. (c) Measured unlocked tone at 386 GHz. (d) Measured locked tone at 386 GHz.

is measured at 522 GHz. A peak EIRP of -11.1 dBm is measured at 655 GHz for the fifth harmonic. Finally, a peak EIRP of -3.8 dBm is measured at 782 GHz for the sixth harmonic. The seventh harmonic could not be measured as the VDI extender has a high conversion loss at this frequency (0.91 THz). Fig. 13(k) shows the EIRP spectra across all these measured frequencies.

The radiation pattern of the chip is measured at 390 GHz. The chip is mounted on a rotatable stage kept at 20 cm from the VDI SAX and the powers are measured at different angles. The measured radiation patterns across the E-plane and H-plane are given in Fig. 14. The directivity is calculated to be 27.2 dB using the directivity formula from [34]. After deembedding the directivity from EIRP, the peak radiated power at 387 is calculated to be -14.2 dBm. The measured and simulated radiated powers are plotted in Fig. 15 and they align reasonably well. The peak power has been reduced by 3 dB, and we attribute it to potential device and circuit modeling errors.

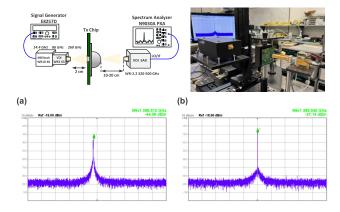

# B. Wireless Locking Measurements

Wireless harmonic injection locking is demonstrated in this work, where the mm-wave oscillator is locked wirelessly using an external source at a harmonic of the fundamental frequency. Fig. 16(a) shows the setup used for wireless injection locking. A 260-GHz external signal is used to injection lock the on-chip oscillator. A multiplier chain consisting of a Millitech WR10 multiply-by-6 module and VDI WR3 tripler generates about −6 dBm at 260 GHz. The wireless injection source is kept at a 2-cm distance from the front side of the chip. Fig. 16(b) shows a photograph of the setup. The measured third harmonic tone around 386 GHz, without and with wireless locking enabled, is shown in Fig. 16(c) and (d), respectively. It should be noted that the spectrum analyzer resolution bandwidth is reduced to 510 kHz in order to highlight the effect of wireless locking. In the unlocked tone, the power is spread across multiple-frequency bins. The locked tone is sharp, and all the power is present in a single-frequency bin. The frequency of the injection source is varied, and a doublesided wireless lock range of 42 MHz is measured at the third harmonic.

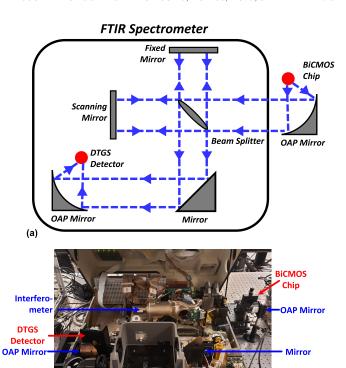

Fig. 17. (a) FITR spectrometer measurement setup. (b) Photograph of the FTIR setup.

# C. FTIR Measurements

(b)

An FTIR spectrometer is used in this work in order to measure the radiation at frequencies beyond 1 THz. A Nicolet 8700 FTIR spectrometer is used in linear scan mode with a room-temperature pyroelectric deuterated triglycine sulfate (DTGS) detector. This detector has a responsivity of 300 V/W at far-infrared frequencies.

Fig. 17(a) shows the measurement setup. The chip is placed at the focus of an off-axis parabolic (OAP) mirror. The OAP mirror collimates the beam and sends it to an interferometer inside the FTIR spectrometer. Here, the beam passes through a beam splitter. One beam is reflected from a stationary mirror, while the other reflects off a scanning mirror, which is controlled through a PC. The reflected beams are then focused on a polarization-insensitive DTGS detector. During this process, interference takes place between the beams. Based on the relative positions of the stationary and the scanning mirror, the beams add up in different phases. For a mono-tone signal, the measured time-domain waveform at the detector output would have peaks and nulls separated by a time "t" corresponding to the scanning mirror moving a distance equaling half the wavelength of the signal. This scanning process is repeated over multiple cycles, and the measured time-domain signal is converted to the frequency domain through a Fourier transform. A photograph of the setup used is given in Fig. 17(b). The measurement is performed at room temperature, and the external beam path is unpurged.

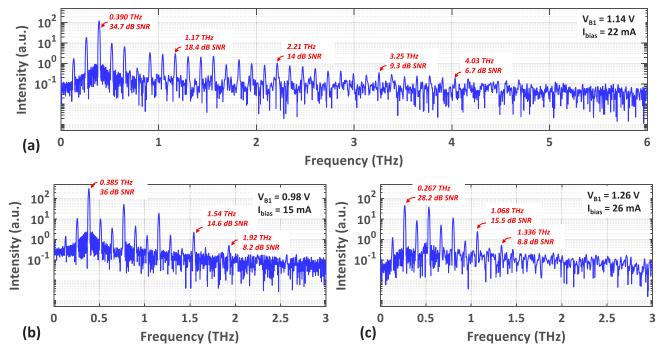

The intensity spectrum is measured at multiple bias points; at each point, 50 interferograms are averaged to produce a spectrum. The interferograms are apodized using a symmetric

Fig. 18. Intensity spectrum generated from the FTIR spectrometer. These spectra are plotted at bias of (a)  $V_{B1} = 1.14$  V, (b)  $V_{B1} = 0.98$  V, and (c)  $V_{B1} = 1.26$  V.

Happ-Genzel window function, which provides a good tradeoff between spectral resolution and sidelobe suppression. The FTIR spectral resolution is 7.5 GHz. Fig. 18(a) shows the results for a bias of  $V_{B1} = 1.14$  V. Strong harmonics are present above 1 THz, with all the harmonics of 0.13 THz observable up to 4 THz having an SNR of 34.7, 18.4, 14, 9.3, and 6.7 dB at 0.39, 1.17, 2.21, 3.25, and 4.03 THz, respectively. The SNR is calculated by comparing the spectral peak to the noise floor. Beyond 4.03 THz, although we do see occasional peaks, some of the intermediate harmonics are not detected. The third harmonic at 390 GHz is the strongest, which matches the simulations and the measurements performed with the VDI. Also, note that at  $V_{B1} = 1.14$  V, the circuit draws 22-mA current, which approximately matches the simulated current required for biasing the transistors at peak  $f_{\text{max}}$ . In Fig. 18(b), measured at a bias of  $V_{B1} = 0.98 \text{ V}$ , the third, sixth, ninth, 12th, and 15th harmonics at 0.385, 0.77, 1.155, 1.54, and 1.925 THz, respectively, are observable; 1.925 THz has a good SNR of 8.2 dB. In Fig. 18(c), measured at a bias of  $V_{B1} = 1.26$  V, the even harmonics at multiples of 0.267 THz are strong. It should be noted that only  $V_{B1}$  is varied between Fig. 18(a) and (c), and the other biases are unchanged. Changing  $V_{B1}$  changes not just the oscillation frequency but also the amount of power that the Colpitts oscillator generates. Because of this, the p-i-n diode is driven with different powers and thus undergoes reverse recovery at different time instances in its RF drive cycle. This affects the generated waveforms, which can explain the variation in relative strengths of harmonics among Fig. 18(a)–(c). It should also be noted that there is some uncertainty in the relative strengths of the peaks in the FTIR spectrum. The collection efficiency in FTIR optics is not uniform from 0.4 to 4 THz because of factors such as beam collimation efficiency, atmospheric absorption,

TABLE I

TUNING RANGE FROM FTIR SPECTRUM

| Harmonic Index | Frequency (GHz) | Tuning Range (GHz) |  |  |  |

|----------------|-----------------|--------------------|--|--|--|

| 3              | 381 – 403       | 22                 |  |  |  |

| 6              | 761 – 806       | 45                 |  |  |  |

| 9              | 1142 – 1220     | 78                 |  |  |  |

| 12             | 1513 – 1591     | 78                 |  |  |  |

attenuation from the mirrors and the beam splitter, and the variation in DTGS detector responsivity.

Changing the base voltage  $V_{B1}$  also varies frequency. The tuning range for the tones at 0.39, 0.78, 1.17, and 1.56 THz is reported in Table I. The tuning ranges are not integer multiples of each other. This is because the frequency resolution of the FTIR interferometer is limited to 7.5 GHz. Also, some higher order tones are weak and cannot be detected at the edge of the tuning range.

It should be noted that this experiment used a room-temperature DTGS detector. A liquid-helium-cooled bolometer is a more sensitive detector and could be used. The FTIR spectral resolution may also be reduced. This can potentially detect higher order tones, provided that the signal below 1 THz is filtered to prevent the detector saturation.

A comparison with other silicon and compound semiconductor-based radiators above 1 THz is given in Table II. To the best of the author's knowledge, this is the only silicon-based radiator with measures tones beyond 2.5 THz. The other silicon radiators such as [15] use a

| Reference                        | This Work                          | [15]                                    | [11]                               | [12]                           | [14]                                | [21]                  | [16]                   | [17]                      | [18]              |

|----------------------------------|------------------------------------|-----------------------------------------|------------------------------------|--------------------------------|-------------------------------------|-----------------------|------------------------|---------------------------|-------------------|

| Highest measured Frequency (THz) | 4.03                               | 2.45                                    | 1.01                               | 0.92                           | 1.85                                | 1.1                   | 2.76                   | 1.64                      | 1.92              |

| Method                           | PIN Diode<br>multiplier            | Harmonic<br>Oscillator                  | Harmonic<br>Oscillator             | BJT<br>Frequency<br>Multiplier | Varactor<br>Multiplier              | Digital to<br>Impulse | SBD Multiplier         | SBD<br>Multiplier         | RTD<br>Oscillator |

| Receiver Used                    | Thermal Pyroelectric DTGS Detector | Liquid<br>Helium<br>Cooled<br>Bolometer | VDI WR1.0<br>Zero Bias<br>Detector | VDI PM4<br>Power<br>Meter      | VDI WR0.65<br>Zero Bias<br>Detector | VDI WR1.0<br>SAX      | VDI PM4<br>Power Meter | VDI PM5<br>Power<br>Meter | N/A               |

| Locking                          | Wireless<br>Locking                | Unlocked                                | Unlocked                           | Wired<br>Locking               | Wired<br>Locking                    | Wired<br>Locking      | Wired Locking          | Wired<br>Locking          | Unlocked          |

| RF Input Power<br>(mW)           | 0                                  | 0                                       | 0                                  | 6.3                            | 63                                  | 31                    | 500                    | 40                        | 0                 |

| DC Power (mW)                    | 70                                 | N/A                                     | 1100                               | 5.7                            | 0                                   | 40                    | 0                      | 0                         | N/A               |

| Technology                       | 90nm SiGe<br>BiCMOS                | 65nm CMOS                               | 130nm SiGe<br>BiCMOS               | 130nm SiGe<br>BiCMOS           | 65nm<br>CMOS                        | 90nm SiGe<br>BiCMOS   | GaAs                   | GaAs                      | Si-InP            |

TABLE II COMPARISON TABLE

sensitive liquid-helium-cooled bolometer detector and could not still detect tones above 2.5 THz. The THz sources presented in [16] and [17] are waveguide modules designed using GaAs diodes pumped by external GaN amplifiers.

This chip can be used for a variety of sensing applications, such as imaging [21], gas spectroscopy [30], [35], and Doppler radar [2]. It can be wirelessly locked to an external reference, and a small resolution bandwidth can be used at the receiver side to maximize the received SNR. The broadband nature of this chip can enable applications such as hyperspectral imaging.

Although the radiated power above 1 THz is less, the p-i-n diode harmonic generation approach presented here can be adapted to other technologies to generate high power. It should also be noted that the p-i-n diodes in the GlobalFoundries 9HP process reuse the vertical profile from the n-p-n transistors. Thus, it is reasonable to assume that as SiGe HBT processes become faster and provide higher  $f_{\rm max}$ , the performance of p-i-n diode multipliers will also improve. The p-i-n diode multipliers can also replace the conventional Schottky diode multipliers in a faster technology such as GaAs or InP to increase the output power.

#### VI. CONCLUSION

This article presents a SiGe BiCMOS p-i-n diode multiplier capable of generating power from the THz range to the far-infrared range. The reverse recovery of a p-i-n diode is used in this work, to generate strong higher order harmonics. A peak EIRP of 13 dBm is measured at 387 GHz, and an EIRP of -3.8 dBm is measured at 782 GHz. An FTIR spectrometer with a room-temperature DTGS detector is used to characterize the higher order harmonics chip. Measurements show tones up to 4 THz, with the highest tone at 4.03 THz

having an SNR of 6.7 dB. Wireless injection locking is also demonstrated in this work, with a lock range of 42 MHz at the third harmonic, around 390 GHz.

#### ACKNOWLEDGMENT

The authors would like to thank GlobalFoundries for chip fabrication support.

#### REFERENCES

- [1] M. Tonouchi, "Cutting-edge terahertz technology," *Nature Photon.*, vol. 1, no. 2, pp. 97–105, Feb. 2007.

- [2] S. Razavian, S. Thomas, M. Hosseini, and A. Babakhani, "Micro-Doppler detection and vibration sensing using silicon-based THz radiators," *IEEE Sensors J.*, vol. 22, no. 14, pp. 14091–14101, Jul. 2022.

- [3] T. S. Rappaport et al., "Wireless communications and applications above 100 GHz: Opportunities and challenges for 6G and beyond," *IEEE Access*, vol. 7, pp. 78729–78757, 2019.

- [4] F. Vatansever and M. R. Hamblin, "Far infrared radiation (FIR): Its biological effects and medical applications," *Photon. Lasers Med.*, vol. 1, no. 4, pp. 255–266, Jan. 2012.

- [5] K. Sengupta, T. Nagatsuma, and D. M. Mittleman, "Terahertz integrated electronic and hybrid electronic-photonic systems," *Nature Electron.*, vol. 1, no. 12, pp. 622–635, Dec. 2018.

- [6] B. S. Williams, "Terahertz quantum-cascade lasers," *Nature Photon.*, vol. 1, no. 9, pp. 517–525, 2007.

- [7] N. T. Yardimci and M. Jarrahi, "Nanostructure-enhanced photoconductive terahertz emission and detection," *Small*, vol. 14, no. 44, Nov. 2018, Art. no. 1802437.

- [8] S. N. Ong et al., "22 nm FD-SOI technology with back-biasing capability offers excellent performance for enabling efficient, ultra-low power analog and RF/millimeter-wave designs," in *Proc. IEEE Radio Freq. Integr. Circuits Symp. (RFIC)*, Jun. 2019, pp. 323–326.

- [9] T. Zimmer et al., "SiGe HBTs and BiCMOS technology for present and future millimeter-wave systems," *IEEE J. Microw.*, vol. 1, no. 1, pp. 288–298, Jan. 2021.

- [10] B. Razavi, "A 300-GHz fundamental oscillator in 65-nm CMOS technology," *IEEE J. Solid-State Circuits*, vol. 46, no. 4, pp. 894–903, Apr. 2011.

- [11] Z. Hu, M. Kaynak, and R. Han, "High-power radiation at 1 THz in silicon: A fully scalable array using a multi-functional radiating mesh structure," *IEEE J. Solid-State Circuits*, vol. 53, no. 5, pp. 1313–1327, May 2018.

- [12] H. Aghasi, A. Cathelin, and E. Afshari, "A 0.92-THz SiGe power radiator based on a nonlinear theory for harmonic generation," *IEEE J. Solid-State Circuits*, vol. 52, no. 2, pp. 406–422, Feb. 2017.

- [13] K. Statnikov, J. Grzyb, B. Heinemann, and U. R. Pfeiffer, "160-GHz to 1-THz multi-color active imaging with a lens-coupled SiGe HBT chipset," *IEEE Trans. Microw. Theory Techn.*, vol. 63, no. 2, pp. 520–532, Feb. 2015.

- [14] Z. Ahmad, M. Lee, and K. O. Kenneth, "1.4 THz, -13 dBm-EIRP frequency multiplier chain using symmetric- and asymmetric-CV varactors in 65 nm CMOS," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Jan. 2016, pp. 350–351.

- [15] R. Al Hadi et al., "Multi-spectral terahertz interferometric imaging based on a monolithic retroactive silicon chip," in *Proc. IEEE Int. Conf. Microw., Antennas, Commun. Electron. Syst. (COMCAS)*, Nov. 2017, pp. 1–4.

- [16] A. Maestrini et al., "Frequency tunable electronic sources working at room temperature in the 1 to 3 THz band," in *Proc. SPIE*, vol. 8496, 2012, pp. 77–85.

- [17] J. V. Siles, K. B. Cooper, C. Lee, R. H. Lin, G. Chattopadhyay, and I. Mehdi, "A new generation of room-temperature frequency-multiplied sources with up to 10 × higher output power in the 160-GHz-1.6-THz range," *IEEE Trans. Terahertz Sci. Technol.*, vol. 8, no. 6, pp. 596–604, Nov. 2018.

- [18] T. Maekawa, H. Kanaya, S. Suzuki, and M. Asada, "Oscillation up to 1.92 THz in resonant tunneling diode by reduced conduction loss," *Appl. Phys. Exp.*, vol. 9, no. 2, Feb. 2016, Art. no. 024101.

- [19] R. Hall, S. Hamilton, and S. Krakauer, "Impulse-shunt mode harmonic generation," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 1966, pp. 66–67.

- [20] R. D. Hall and S. M. Krakauer, "Microwave harmonic generation and nanosecond pulse generation with the step-recovery diode," *Hewlett Packard J.*, vol. 16, no. 4, pp. 1–8, 1964.

- [21] S. Razavian and A. Babakhani, "Silicon integrated THz comb radiator and receiver for broadband sensing and imaging applications," *IEEE Trans. Microw. Theory Techn.*, vol. 69, no. 11, pp. 4937–4950, Nov. 2021.

- [22] L. Dauphinee, M. Copeland, and P. Schvan, "A balanced 1.5 GHz voltage controlled oscillator with an integrated LC resonator," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Jun. 1997, pp. 390–391.

- [23] H. Li and H.-M. Rein, "Millimeter-wave VCOs with wide tuning range and low phase noise, fully integrated in a SiGe bipolar production technology," *IEEE J. Solid-State Circuits*, vol. 38, no. 2, pp. 184–191, Feb. 2003.

- [24] S. Thomas et al., "Broadband 0.4-4 THz generation in 90 nm SiGe BiCMOS," in *Proc. IEEE BiCMOS Compound Semiconductor Integr. Circuits Technol. Symp. (BCICTS)*, Oct. 2022, pp. 199–202.

- [25] D. M. Pozar, Microwave Engineering. Hoboken, NJ, USA: Wiley, 2011.

- [26] M. R. T. Tan, S. T. Wang, D. E. Mars, and J. L. Moll, "12 ps GaAs double heterostructure step recovery diode," *Electron. Lett.*, vol. 28, no. 7, pp. 673–675, Mar. 1992.

- [27] A. W. DiVergilio, J. J. Pekarik, and V. Jain, "An electrothermal PIN diode model with substrate injection," in *Proc. IEEE Bipolar/BiCMOS Circuits Technol. Meeting (BCTM)*, Sep. 2014, pp. 207–210.

- [28] K. Schunemann and J. Müller, "A charge-control model of the pin diode," *IEEE Trans. Electron Devices*, vol. ED-23, no. 10, pp. 1150–1158, Oct. 1976.

- [29] C. A. Balanis, Antenna Theory: Analysis and Design. Hoboken, NJ, USA: Wiley, 2015.

- [30] M. M. Assefzadeh et al., "Terahertz trace gas spectroscopy based on a fully-electronic frequency-comb radiating array in silicon," in *Proc.* Conf. Lasers Electro-Optics (CLEO), Jun. 2016, pp. 1–2.

- [31] B. Razavi, "A study of injection locking and pulling in oscillators," *IEEE J. Solid-State Circuits*, vol. 39, no. 9, pp. 1415–1424, Sep. 2004.

- [32] B. Hong and A. Hajimiri, "A phasor-based analysis of sinusoidal injection locking in LC and ring oscillators," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 66, no. 1, pp. 355–368, Jan. 2019.

- [33] J. J. Pekarik et al., "A 90 nm SiGe BiCMOS technology for mm-wave and high-performance analog applications," in *Proc. IEEE Bipo-lar/BiCMOS Circuits Technol. Meeting (BCTM)*, Sep. 2014, pp. 92–95.

- [34] R. Han and E. Afshari, "A CMOS high-power broadband 260-GHz radiator array for spectroscopy," *IEEE J. Solid-State Circuits*, vol. 48, no. 12, pp. 3090–3104, Dec. 2013.

- [35] I. Gordon et al., "The HITRAN2020 molecular spectroscopic database," J. Quant. Spectrosc. Radiat. Transf., vol. 277, Jan. 2022, Art. no. 107949.

**Sidharth Thomas** (Graduate Student Member, IEEE) received the B.Tech. degree in electronics and communication engineering from IIT Roorkee, Roorkee, India, in 2020, and the M.Sc. degree in electrical and computer engineering from the University of California at Los Angeles, Los Angeles, CA, USA, in 2022, where he is currently pursuing the Ph.D. degree.

During his undergraduate studies, he did research at the Technion–Israel Institute of Technology, Haifa, Israel, and the University of Toronto, Toronto,

ON, Canada, in 2018 and 2019, respectively, where he worked on neuromorphic computing and biomedical integrated circuit (IC) design. His research interests include high-frequency integrated circuit design for wireless communication, imaging, and sensing applications.

Mr. Thomas received the IIT Roorkee ECE Department Gold Medal in 2020, the UCLA Guru Krupa Fellowship in 2020, and the IEEE MTT-S Pre-Graduate/Graduate Fellowship in 2022.

Sam Razavian (Student Member, IEEE) received the B.Sc. degree in electrical engineering from the Sharif University of Technology, Tehran, Iran, in 2016, and the M.Sc. and Ph.D. degrees in electrical and computer engineering from the University of California at Los Angeles, Los Angeles, CA, USA, in 2019 and 2022, respectively.

He was an RFIC Design Intern with Qualcomm Inc., San Jose, CA, USA, from 2020 to 2021, where he worked on various RF circuit blocks. His research has resulted in various publications in the

International Solid-State Circuits Conference (ISSCC), the Radio Frequency Integrated Circuits Symposium (RFIC), the International Microwave Symposium (IMS), and IEEE TRANSACTIONS ON MICROWAVE THEORY AND TECHNIQUES (TMTT). His current research focus is on millimeter-wave and terahertz transmitters and receivers for different applications, including broadband sensing, hyperspectral imaging, and high-speed Communication.

Dr. Razavian received the 2021–2022 IEEE SSCS Predoctoral Achievement and the 2022 MTT-S Graduate Fellowship Awards.

Wei Sun (Student Member, IEEE) received the B.S. degree in electrical engineering from the University of Electronic Science and Technology of China, Chengdu, China, in 2021. He is currently pursuing the Ph.D. degree with the University of California at Los Angeles, Los Angeles, CA, USA.

His current research interests include terahertz integrated circuits and on-chip antenna design for applications of sensing and communication.

Benyamin Fallahi Motlagh (Student Member, IEEE) received the B.S. degree in electrical engineering from the Sharif University of Technology, Tehran, Iran, in 2021. He is currently pursuing the Ph.D. degree in electrical and computer engineering with the University of California at Los Angeles, Los Angeles, CA, USA.

His current research interests include millimeterwave and terahertz integrated circuits for wireless communication, imaging, and sensing.

Anthony D. Kim (Student Member, IEEE) received the B.Sc. degree in electrical and computer engineering and the M.Sc. degree from the University of California at Los Angeles (UCLA), Los Angeles, CA, USA, in June 2018 and June 2020, respectively, where he is currently pursuing the Ph.D. degree with the Terahertz and Infrared Photonics Group, supervised by Prof. Benjamin S. Williams.

His research focuses on designing terahertz quantum-cascade vertical-external-cavity surfaceemitting lasers for local oscillators in heterodyne

spectroscopic systems. His research interests also include quantum-cascade lasers, terahertz photonics and imaging, and metasurfaces.

Yu Wu (Student Member, IEEE) received the B.S. degree in physics from Nanjing University, Nanjing, China, in June 2017. She is currently pursuing the Ph.D. degree in electrical engineering with the University of California at Los Angeles, Los Angeles, CA, USA.

Her research interests include investigating terahertz semiconductor lasers, metamaterials, and frequency combs.

**Benjamin S. Williams** (Senior Member, IEEE) received the Ph.D. degree in electrical engineering and computer science from the Massachusetts Institute of Technology (MIT), Cambridge, MA, USA, in 2003.

From 2003 to 2006, he was a Post-Doctoral Associate with the Research Laboratory of Electronics, MIT. In 2007, he joined the Department of Electrical Engineering, University of California at Los Angeles, Los Angeles, CA, USA, where he is currently a Professor and a Henry Samueli Fellow.

His research interests include quantum cascade lasers, intersubband and intersublevel devices in semiconductor nanostructures, terahertz metamaterials, and plasmonics.

Dr. Williams was a recipient of the Apker Award from the American Physical Society, the Young Investigator Award from the Defense Advanced Research Projects Agency, the Early Career Award from the National Science Foundation, and the Presidential Early Career Award for Scientists and Engineers. He is an Associate Editor of the IEEE TRANSACTIONS ON TERAHERTZ SCIENCE AND TECHNOLOGY.

Aydin Babakhani (Senior Member, IEEE) received the B.S. degree from the Sharif University of Technology, Tehran, Iran, in 2003, and the M.S. and Ph.D. degrees in electrical engineering from the California Institute of Technology, Pasadena, CA, USA, in 2005 and 2008, respectively.

He was an Assistant Professor of electrical and computer engineering and a Louis Owen Junior Chair Assistant Professor with Rice University, Houston, TX, USA, from 2011 to 2016 and from 2016 to 2017, respectively. He was a Post-

Doctoral Scholar with the California Institute of Technology in 2009. He was a Research Scientist with the IBM Thomas J. Watson Research Center, Ossining, NY, USA, in 2010. He was an Associate Professor with the Department of Electrical and Computer Engineering, Rice University, where he is currently the Director of the Rice Integrated Systems and Circuits Laboratory. He is also a member of the DARPA Microsystems Exploratory Council and a Co-Founder of MicroSilicon, Inc., Houston. He is also an Associate Professor with the Department of Electrical and Computer Engineering, University of California at Los Angeles (UCLA), Los Angeles, CA, USA, where he is also the Director of the Integrated Sensors Laboratory. He has authored or coauthored more than 85 articles in peer-reviewed journals and conference proceedings. He holds 21 issued or pending patents. His research is supported by NSF, DARPA, AFOSR, ONR, the W. M. Keck Foundation, SRC, and more than ten companies.

Dr. Babakhani was a recipient of multiple best paper awards, including the Best Paper Award at the IEEE SiRF Conference in 2016, the Best Paper Award at the IEEE RWS Symposium in 2015, the Best Paper Award at the IEEE MTT-S IMS Symposium in 2014, the Second Place in the Best Paper Awards at the IEEE APS Symposium 2016 and IEEE MTT-S IMS Symposium 2016. He was also a recipient of the prestigious NSF CAREER Award in 2015, the Innovation Award from Northrop Grumman in 2014, the DARPA Young Faculty Award in 2012, the California Institute of Technology Electrical Engineering Department's Charles Wilts Best Ph.D. Thesis Prize for his work entitled "Near-Field Direct Antenna Modulation," the Microwave Graduate Fellowship in 2007, the Grand Prize in the Stanford-Berkeley-Caltech Innovators Challenge in 2006, the Analog Devices, Inc., Outstanding Student Designer Award in 2005, the California Institute of Technology Special Institute Fellowship, the Atwood Fellowship in 2003, and the Gold Medal Winner at the National Physics Competition in 1998 and the 30th International Physics Olympiad, Padua, Italy, in 1999.