# An Efficient 0.4 THz Radiator with 20.6 dBm EIRP and 0.2% DC-to-THz Efficiency in 90nm SiGe BiCMOS

Sidharth Thomas, Sam Razavian, Aydin Babakhani (UCLA)

Abstract — This paper presents an efficient 0.4 single-element radiator implemented 90nm in BiCMOS. It consists of a PIN diode quadrupler, where a mm-wave Colpitts oscillator at 100 GHz drives a PIN diode switching-reactance-multiplier into reverse recovery. Because of this, the PIN diode abruptly switches between two impedance states and produces strong harmonics. Harmonic injection locking is also presented in this work, where two quadrupler cells are mutually interlocked, and their fourth harmonic power at 0.4 THz combines at the antenna. The radiator achieves a peak EIRP of +20.6 dBm and -5.8 dBm radiated power at 398 GHz, with a 10.7 % tuning range, and consumes 130 mW DC power. This work has a DC-to-THz generation efficiency of 0.2%, the highest reported efficiency above 320 GHz, and achieves the highest power and EIRP generated by a single-element radiator.

## Keywords - PIN diode, multiplier, THz source, SiGe

#### I. Introduction

The THz band (0.1-10 THz) has several unique properties, making it a potential candidate for imaging, spectroscopy, and communication applications. These applications require efficient high-power THz generation over a wide frequency range. Due to the limited  $f_T/f_{max}$  of transistors, direct THz generation is not feasible, and harmonic generation using non-linear devices such as transistors or varactor diodes is popularly used [1-4]. However, these devices have weak non-linearity, limiting the amount of generated THz power. PIN diodes have shown strong non-linearity and have been used for THz generation [5], [6].

A large-scale array implementation, with free space power combining, can be employed to boost the radiated THz power. However, this approach faces major challenges: (1) Arrays consume high DC power. (2) Inter-element frequency and phase synchronization become challenging at THz frequencies. (3) When used with a silicon lens, arrays have less directivity than a single-element radiator due to lens off-axis misalignment. Because of this, a single-element radiator can provide superior EIRP than an array for the same DC power [7].

This work presents an efficient 0.4 THz single-element radiator based on PIN diode switching reactance frequency multipliers (SRM). Due to reverse recovery, PIN diodes are strongly non-linear and are hence used here to maximize DC-to-THz generation efficiency. To improve the power, on-chip power combining at the antenna node is adopted, where two quadruplers are mutually interlocked, and the 0.4 THz signal adds in-phase. Performing power combining at

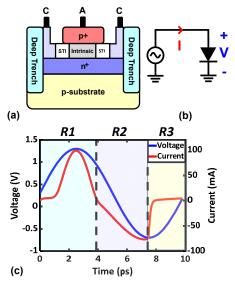

Fig. 1. (a) PIN diode illustration (b) PIN diode excited by a voltage source (c) Current through the PIN diode when excited by a 100 GHz voltage source

the antenna ensures low loss, and the THz signal is directly radiated.

## II. PIN DIODE AND REVERSE RECOVERY

The reverse recovery of PIN diodes is used in this work for efficient THz generation. A PIN diode consists of p+ and n+ regions, separated by an intrinsic 'I' region. The presence of the 'I' region differentiates a PIN diode from conventional diodes. A standard PIN diode from GlobalFoundries 90nm process is used here and is illustrated in Fig. 1 (a). Fig. 1 (b), (c) demonstrate the operation of a PIN diode when a large-signal sinusoidal voltage is applied across it. In the forward mode of operation (R1), the diode conducts, and the I-region is filled with electrons and holes to facilitate forward conduction. Because of these excess carriers, the diode remains ON and continues current conduction in the reverse mode (R2) until all excess carriers are depleted. This is different from a conventional diode, where there is no carrier storage, and the diode stops conducting as soon as it leaves R1. Once the carriers in the PIN diode are depleted, the current snaps to zero (R3), exhibiting reverse recovery. This switching is abrupt, and the generated waveform is rich in harmonics. During a typical drive cycle, the diode operates across the conduction regions (R1 and R2) and the OFF state region (R3). In R1 and R2, ideally, the diode can store any amount of charge at a constant

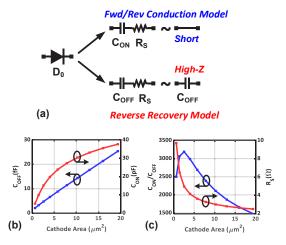

Fig. 2. (a) Large signal RF equivalent circuit model of a PIN diode (b)  $C_{OFF}$  and  $C_{ON}$  vs diode cathode area (c)  $C_{ON}/C_{OFF}$  and  $R_S$  vs diode cathode area

voltage (turn-on voltage of the diode). In R3, the diode behaves like a small capacitance.

A large-signal equivalent for the PIN diode is presented to understand the circuit functionality better. Fig. 2 (a) shows a simplified large-signal RF model of the diode. During forward and reverse conduction (Regions R1 and R2), the diode presents low impedance and behaves as a large capacitance  $C_{ON}$  in series with the diode impedance  $R_S$ . Ideally, this can be approximated as a short. When turned OFF (Region R3), the diode presents a high impedance and behaves as a small capacitance  $C_{OFF}$  in series with  $R_S$ . Ideally, this can be approximated as just  $C_{OFF}$ . The parameters  $C_{ON}$ ,  $C_{OFF}$ , and  $R_S$  for various diode sizes are plotted in Fig. 2 (b), (c).

## III. CIRCUIT DESIGN

The PIN diode quadrupler design is explained in this section. It consists of a mm-wave oscillator at 100 GHz that drives a PIN diode. Two quadruplers are interlocked, and the power at 0.4 THz is combined and radiated through an on-chip antenna.

### A. Switching Reactace Multiplier

PIN diode multipliers are Switched Reactance Multipliers (SRMs), where the diode switches abruptly from a short to a high impedance state. The fast switching behavior enables efficient THz generation using PIN didoes. This differs from conventional varactor or transistor-based multipliers where the reactance variation, although non-linear, is gradual (Variable Reactance Multiplier, VRM). SRMs were designed in the past using discrete microwave step-recovery diodes (SRD) [8]. However, they are not available in modern silicon processes. This work extends the SRM theory to PIN diodes since they behave similarly to SRDs under large-signal operation.

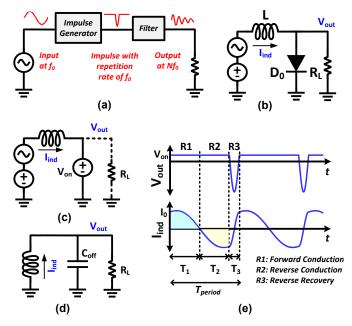

Fig. 3 (a) illustrates a general SRM circuit. It consists of an impulse generator circuit that is excited at a frequency  $f_0$ . This generates an impulse that can be filtered to extract the harmonic of interest at 'Nf<sub>0</sub>'. The impulse train generator

Fig. 3. (a) A switched reactance frequency multiplier (b) PIN diode impulse generator (c) Equivalent circuit during R1 and R2. (d) Equivalent circuit during R3. (e) V<sub>out</sub> and inductor current

circuit is shown in Fig. 3 (b). A PIN diode is connected to an RF source through an inductor and to a load R<sub>L</sub>. The non-linear time-varying behavior of the PIN diode can be analyzed by replacing the diode with the linear switching model from Fig. 2 (a), and applying boundary conditions. The simplified circuit is shown in Fig. 3 (c), (d). This circuit is solved using linear analysis, and the resulting diode voltage (V<sub>out</sub>) and inductor current (I<sub>ind</sub>) are plotted in Fig. 3 (e). Regions R1, R2, and R3 correspond to forward conduction, reverse conduction, and reverse recovery mode. During forward and reverse conduction (R1, R2), the PIN diode is ON and clamped to the diode turn-on voltage Von. Charges stored in the 'I' region of the diode during R1 are depleted during R2, and the diode turns OFF at R3 when this charge becomes zero (Q1 = Q2). We bias the diode such that it carries peak reverse current at the onset of R3. Even though the diode turns OFF, current continuity through the inductor must be maintained. This results in a sharp negative impulse voltage at Vout. The height and width of this impulse depend on C<sub>OFF</sub> and R<sub>L</sub>. This impulse is then filtered to extract the harmonic of interest at Nf<sub>0</sub>.

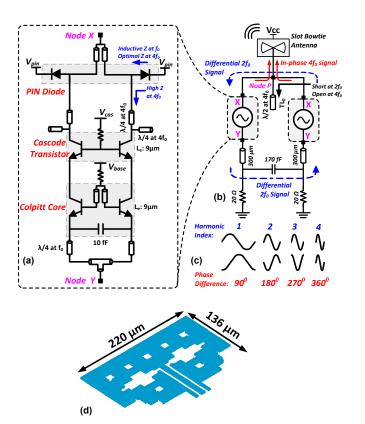

#### B. THz Transmitter Design

Fig. 4 (a) shows the schematic of the PIN diode-based THz SRM quadrupler. It consists of a differential mm-wave Colpitts oscillator, which oscillates at 100 GHz. A cascode stage is used to amplify the oscillator output and isolate the oscillator core. Transmission line (TL) matching networks connect the cascode to the diode and extract the 4th harmonic at 400 GHz. These matching networks ensure that (1) the 100 GHz signal is large-signal matched to the diode and (2) the antenna is matched to the diode at the 4th harmonic at 400 GHz. The amount of generated THz power depends on the diode size.

Fig. 4. (a) PIN diode switched reactance multiplier at 100 GHz (b) Quadrature locking and power combining (c) Odd mode coupling at 2nd harmonic provides quadrature and in-phase signals at 1st and 4th harmonics respectively (d) Slot bowtie antenna

Choosing a diode size that has high  $(C_{ON}/C_{OFF})$  ensures the diode switches between widely different impedance levels. Choosing a diode size with low  $R_S$  ensures high Q. Thus, the diode size, which maximizes the ratio  $(C_{ON}/C_{OFF})/R_S$ , is chosen and this consequently maximizes the generated THz power.

On-chip power combining at the antenna is used in this work. Two quadrupler cells are mutually locked at 100 GHz to boost the power at 400 GHz. Fig. 4 (b) shows the locking mechanism. Node X of both the quadrupler cells are directly connected to the antenna and to an open line TL<sub>0</sub>, which is  $\lambda/2$  length at 400 GHz. Only even harmonics of the quadrupler cells can interact with each other at node X since it lies on the common mode of the individual cells. The oscillators undergo mutual injection locking and can operate in the odd mode or even mode of the second harmonic. However, TL<sub>0</sub> creates a short at node P at the second harmonic. This prevents the even mode signals from coupling. For odd mode, node P is a virtual ground and remains unaffected by TL<sub>0</sub>. Thus odd mode oscillation is sustained at the second harmonic. Consequently, due to harmonic injection locking, the oscillators become quadrature locked at the fundamental frequency and in-phase locked at the 4th harmonic (Fig. 4 (c)). At node Y, since the oscillators cannot be directly connected due to layout constraints, they are connected through 300  $\mu$ m TLs and

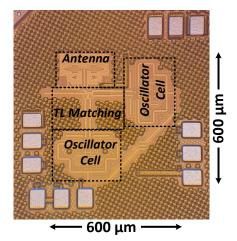

Fig. 5. Die Micrograph

Fig. 6. (a) EIRP measurement setup (b) VDI WR2.2 SAX loss calibration (c) Measured spectrum at 398 GHz (d) Frequency tuning curve (e) EIRP variation vs frequency

coupling capacitors. Resistors are used for biasing.

A slot-bowtie antenna is used in this work. Fig. 4 (d) shows the structure of the antenna. Additional slots are added to the antenna to meet density requirements. The antenna is used with a hyper hemispherical silicon lens. Since only one antenna is used, it can be aligned to the axis of the lens.

#### IV. MEASUREMENT RESULTS

The design is fabricated in GlobalFoundries 90nm SiGe BiCMOS process. It consumes 130 mW DC power in nominal operation. Fig. 5 shows the die micrograph. The design occupies an active area of 0.36 mm<sup>2</sup>.

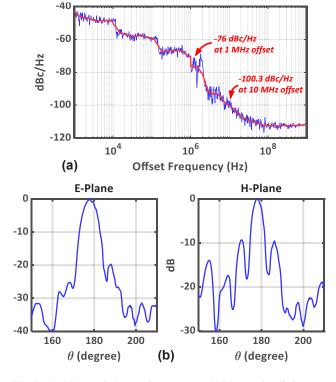

Fig. 7. (a) Measured phase noise spectrum (b) Measured radiation pattern

The chip is wire-bonded to a PCB, and a hyper hemispherical silicon lens is attached. The lens helps improve radiation efficiency by removing substrate modes, and increases the directivity. No substrate thinning is employed. Fig. 6 (a) shows the free space measurement setup. The chip is kept at a 30 cm far-field distance from a VDI WR2.2 mixer (SAX). The conversion loss of the mixer is measured using a VDI WR2.2 signal generator extender (AMC), which is calibrated using a VDI PM5B power meter using the setup shown in Fig. 6 (b). The measured spectrum at 398 GHz is shown in Fig. 6 (c). An EIRP of 20.6 dBm is obtained after de-embedding the losses. The frequency is varied by changing the base and cascode bias. This is plotted in Fig. 6 (d). A tuning range of 42 GHz (10.7 %) is measured. The EIRP variation across frequency is plotted in Fig. 6 (e), and a 6 dB bandwidth of 28 GHz is measured. The measured phase noise spectrum is plotted in Fig. 7 (a). A phase noise of -76 dBc/Hz at 1 MHz offset and -100.3 dBc/Hz at 10 MHz offset is measured. The chip is mounted on a rotational stage to measure the radiation pattern. The radiation pattern in E and H planes are plotted in Fig. 7 (b), and a directivity of 26.4 dB is calculated. The total radiated power is -5.8 dBm.

A comparison with other state-of-the-art silicon-based THz radiators is given in Table 1. This work achieves the highest DC-to-THz efficiency (0.2 %), the highest radiated power per element (-5.8 dBm), and one of the highest EIRP (20.6 dBm). Though [3] has higher EIRP, it is achieved using additional processing steps such as substrate thinning and by using a highly directive custom teflon lens. The radiated power

Table 1. Comparison Table

| References                             | This Work      | [1]H. Saeidi<br>JSSC'22 | [5]S. Razavian<br>ISSCC'22 | [2] H. Jalili<br>JSSC'19 | [3] L. Gao<br>JSSC'22 | [4] Y. Tousi<br>JSSC'15 |

|----------------------------------------|----------------|-------------------------|----------------------------|--------------------------|-----------------------|-------------------------|

| Frequency (GHz)                        | 398            | 416                     | 424                        | 344                      | 450                   | 338                     |

| EIRP (dBm)                             | 20.6           | 14                      | 18.1                       | 4.9                      | 29.1                  | 17.1                    |

| Radiated Power (dBm)                   | -5.8           | -3                      | -5                         | -6.8                     | -3.2                  | -0.9                    |

| Antenna Array size                     | 1              | 4 x 4                   | 2 x 3                      | 2 x 2                    | 4 x 4                 | 4 x 4                   |

| Radiated Power<br>per Element (dBm)    | -5.8           | -15                     | -12.8                      | -12.8                    | -15.24                | -12.9                   |

| DC Power (mW)                          | 130            | 1450                    | 400                        | 450                      | 347                   | 1540                    |

| DC to Radiated<br>Power Efficiency (%) | 0.2            | 0.03                    | 0.08                       | 0.04                     | 0.14                  | 0.05                    |

| Tuning Range (%)                       | 10.7           | 1.7                     | 14.6                       | 15.1                     | 4.6                   | 2.1                     |

| Phase Noise (dBc/Hz)                   | -76<br>(1 MHz) | -88<br>(1 MHz)          | -104<br>(10 MHz)           | -93.1<br>(10 MHz)        | -76.4<br>(1 MHz)      | -93<br>(1 MHz)          |

| Area (mm²)                             | 0.36           | 4.1*                    | 0.98                       | 1.2*                     | 0.55                  | 3.9*                    |

| Lens                                   | Silicon Lens   | No                      | Silicon Lens               | No                       | Custom<br>Teflon Lens | No                      |

| Technology                             | 90 nm<br>SiGe  | 65 nm<br>CMOS           | 90 nm<br>SiGe              | 130 nm<br>SiGe           | 65 nm<br>CMOS         | 65 nm<br>CMOS           |

achieved in this work is comparable to multi-element arrays and this high power can directly drive other on-chip circuits such as mixers and multipliers. Array radiators, with free-space combining, do not offer this.

#### V. CONCLUSION

This work presents a 0.4 THz single-element radiator in 90 nm SiGe BiCMOS. The reverse recovery phenomenon is used in this work to generate efficient THz power. Two multiplier cells are interlocked, and the THz power is combined at the antenna. This work achieves an EIRP of 20.6 dBm, radiated power of -5.8 dBm, and a wide tuning range of 10.7%. It achieves the DC-to-THz efficiency (0.2 %) and the highest radiated power per element (-5.8 dBm) above 320 GHz.

# REFERENCES

- [1] H. Saeidi, S. Venkatesh, C. R. Chappidi, T. Sharma, C. Zhu, and K. Sengupta, "A 4 × 4 Steerable 14-dBm EIRP Array on CMOS at 0.41 THz With a 2-D Distributed Oscillator Network," *IEEE Journal of Solid-State Circuits*, vol. 57, no. 10, pp. 3125–3138, 2022.

- [2] H. Jalili and O. Momeni, "A 0.34-THz Wideband Wide-Angle 2-D Steering Phased Array in 0.13- μ m SiGe BiCMOS," *IEEE Journal of Solid-State Circuits*, vol. 54, no. 9, pp. 2449–2461, 2019.

- [3] L. Gao and C. H. Chan, "A 0.45-THz 2-D Scalable Radiator Array With 28.2-dBm EIRP Using an Elliptical Teflon Lens," *IEEE Journal of Solid-State Circuits*, vol. 57, no. 2, pp. 400–412, 2022.

- [4] Y. Tousi and E. Afshari, "A High-Power and Scalable 2-D Phased Array for Terahertz CMOS Integrated Systems," *IEEE Journal of Solid-State Circuits*, vol. 50, no. 2, pp. 597–609, 2015.

- [5] S. Razavian and A. Babakhani, "A Highly Power Efficient 2x3 PIN-Diode-Based Intercoupled THz Radiating Array at 425GHz with 18.1dBm EIRP in 90nm SiGe BiCMOS," in 2022 IEEE International Solid- State Circuits Conference (ISSCC), vol. 65, 2022, pp. 1–3.

- [6] S. Razavian and A. Babakhani, "Silicon Integrated THz Comb Radiator and Receiver for Broadband Sensing and Imaging Applications," *IEEE Transactions on Microwave Theory and Techniques*, vol. 69, no. 11, pp. 4937–4950, 2021.

- [7] H. Jalili and O. Momeni, "A 0.46-THz 25-Element Scalable and Wideband Radiator Array With Optimized Lens Integration in 65-nm CMOS," *IEEE Journal of Solid-State Circuits*, vol. 55, no. 9, pp. 2387–2400, 2020.

- [8] S. Hamilton and R. Hall, "Shunt-mode harmonic generation using step recovery diodes," *Microwave Journal*, vol. 10, no. 5, pp. 69–78, 1967.