# SAW-Less Direct RF Transmitter With Multimode Noise Shaping and Tri-Level Time-Approximation Filter

Shiyu Su<sup>1</sup>, Member, IEEE, and Mike Shuo-Wei Chen<sup>1</sup>, Senior Member, IEEE

**Abstract**—This article presents a multimode direct radio frequency (RF) transmitter capable of a high in-band dynamic range and a low out-of-band (OOB) noise floor. It features a hybrid digital-to-analog converter (DAC) with a reconfigurable dual-band delta-sigma modulator to lower the quantization noise floor at one or two frequency bands. Additionally, a tri-level time-approximation filter is proposed to further suppress OOB noise with high tunability and stopband attenuation. The objective is to demonstrate a low-noise floor without using a surface acoustic wave (SAW) filter. For a 256-quadratic-amplitude modulation (QAM) signal with 17.4-dBm average output power at a 2.2-GHz carrier, the silicon prototype achieves  $-40$ -dB error vector magnitude (EVM) and  $-169$ -dBc/Hz noise spectral density (NSD) at 68-MHz offset by consuming a total power of 1.2 W.

**Index Terms**—Direct RF transmitter, hybrid digital-to-analog converter (DAC), multimode, noise shaping, surface acoustic wave (SAW)-less, time-approximation filter (TAF).

## I. INTRODUCTION

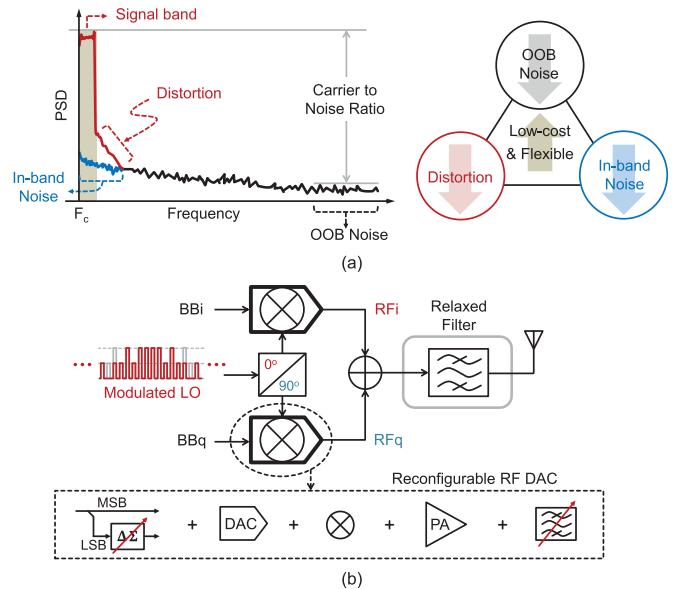

NEXT-GENERATION wireless communication systems demand high-performance radio frequency (RF) integrated circuits that support multi-band and multi-standard applications. Depending on the operating conditions, a transmitter (TX) requires low in-band noise and distortion for high spectral efficiency and low noise levels at specific out-of-band (OOB) frequencies for radio coexistence, as shown in Fig. 1(a). To achieve low in-band noise, distortion, and OOB noise simultaneously is difficult, as they typically trade off against each other. In addition, high flexibility and low cost should always be guaranteed without sacrificing the performance, which makes the design of such a system a challenge.

The software-defined radio TX provides maximal flexibility, thanks to its mostly digital architecture. However, for a TX to have instantaneous bandwidth covering all the communication bands while maintaining a sufficient dynamic range, it is

Manuscript received April 7, 2021; revised August 25, 2021 and September 27, 2021; accepted September 27, 2021. Date of publication October 12, 2021; date of current version February 24, 2022. This article was approved by Associate Editor Kenichi Okada. This work was supported in part by the NSF Switched-Capacitor Radio Frequency Signal Processing for Spectrally-Agile Low-Energy Wireless Transceivers (SpecEES) under Grant EECs-1824442 and in part by DARPA Millimeter Wave Digital Arrays (MIDAS) under Grant FA8650-19-1-7996. (Corresponding author: Shiyu Su.)

The authors are with the Ming Hsieh Department of Electrical and Computer Engineering-Electrophysics, University of Southern California, Los Angeles, CA 90089 USA (e-mail: shiyusu@usc.edu).

Color versions of one or more figures in this article are available at <https://doi.org/10.1109/JSSC.2021.3116933>.

Digital Object Identifier 10.1109/JSSC.2021.3116933

Fig. 1. (a) Design tradeoffs of a TX. (b) Proposed direct RF TX.

usually not cost-efficient. A direct RF TX based on RF/mixing digital-to-analog converters (DACs) provides a better implementation tradeoff by relaxing the design of high-speed DAC while having relatively low analog complexity [1]–[4]. To further enhance the flexibility and in-band dynamic range of the TX, noise shaping or reduction techniques based on a lowpass delta-sigma modulator (DSM) [5]–[10] and pulsedwidth modulation (PWM) [11] are used for digitally intensive direct RF TX. Because of the lack of baseband reconstruction filtering, all unwanted signals at the baseband are upconverted to RF by the direct RF TX. Therefore, a sharp analog bandpass filter is required for noise and spurs attenuation at the RF band. No matter whether it is on-chip or off-chip, this filter is typically costly for high selectivity. The situation worsens when delta-sigma and PWMs are used, as more high-frequency components are generated due to the modulation.

To relax the bandpass analog filter requirement with less implementation overhead (i.e., without using bulky passive components), a bandpass DSM [12] is used to create spectral notches for suppressing OOB noise. Since the notches are allocated OOB, the DSM trades off the in-band dynamic range. Charge-based TXs [13], [14] and semi-digital finite-impulse response (FIR) filters [7]–[9], [15]–[18] provide decent OOB

noise attenuations, but both have limited flexibility on the filter response. Recently, a time-approximation filter (TAF) technique [10] has been used to embed a reconstruction filter in the frequency up-conversion process. Essentially, this direct RF TX approximates an FIR filter's impulse response in the time domain by gating some of the pulses of the local oscillator (LO) waveform. While a TAF efficiently achieves high OOB noise attenuation and filter reconfigurability, the time resolution requirement of the time approximation increases with the peak variation in the target FIR filter's coefficients and likely demands a higher system clock rate.

In this article, we describe the design and implementation of a reconfigurable direct RF TX architecture that supports a high in-band dynamic range and/or low OOB noise floor at desired frequencies [19], as shown in Fig. 1(b). Our analysis will focus on the two key techniques of the proposed TX, which are: 1) a multimode hybrid DAC with reconfigurable dual-band DSM that can create in-band and/or OOB spectral notches to support different communication scenarios and 2) a tunable tri-level TAF that is codesigned with the DSM to further suppress OOB noise, which achieves higher flexibility and stopband attenuation than the existing TAFs [10] with reasonable tradeoffs.

The remainder of this article is organized as follows. Section II describes the proposed multimode scheme based on a dual-band DSM structure. The tri-level TAF and the codesign of the TAF and the DSM are elaborated in Section III. Detailed circuit implementation is discussed in Section IV, and the measurement results are shown in Section V.

## II. MULTIMODE NOISE SHAPING

Delta-sigma modulation is one of the most popular noise shaping techniques in wireless communication systems. Thanks to oversampling and noise shaping, a DSM can achieve a high signal-to-noise ratio (SNR) with fewer bits. In this section, we discuss the applications of DSM in TXs and elaborate on the proposed multimode DSM for a hybrid DAC structure.

### A. Conventional Delta-Sigma Modulator for TX

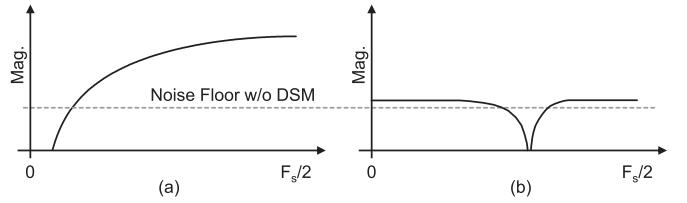

Direct RF TX relaxes high-dynamic-range analog circuits by leveraging the high-speed, high-efficiency digital signal processing provided by technology scaling. However, the high-speed and high-resolution DAC becomes the bottleneck of the system due to the large DAC array. DSM is herein used to reduce the analog complexity by truncating the number of bits and shaping the additive truncation noise out of the band of interest. Note that this bit width reduction is also favored by switching power amplifiers for superior power efficiency. Fig. 2(a) presents a noise transfer function (NTF) of a lowpass DSM. Within the band around the dc, the DSM output signal achieves lower noise than the intrinsic quantization noise floor of the DSM input signal, thanks to the frequency notches. Similarly, bandpass DSM is used in combination with digital intermediate frequency mixing to avoid performance degradation due to LO leakage and I and Q mismatch error [8], [20]. A dual-rate hybrid DAC structure with lowpass [21], [22]

Fig. 2. (a) Lowpass and (b) bandpass NTFs of a DSM.

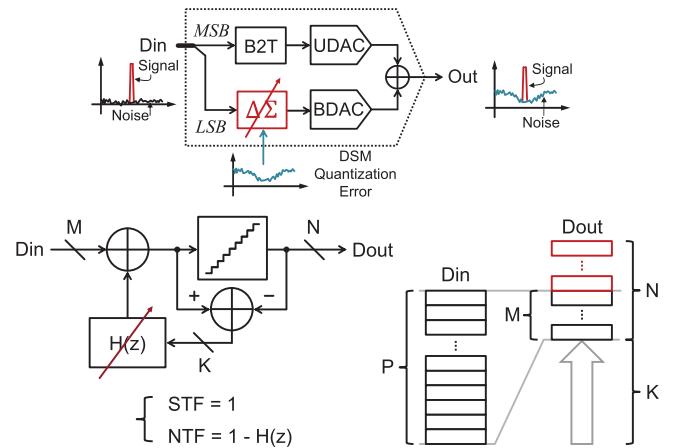

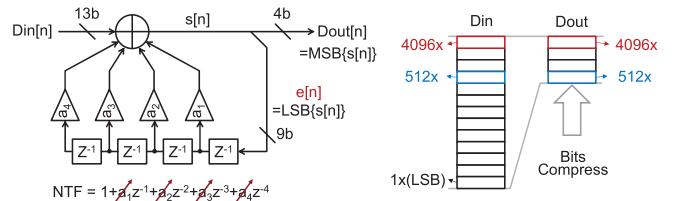

Fig. 3. Hybrid DAC and error-feedback DSM.

and bandpass [23] DSMs was proposed to break the tradeoff between resolution and operation speed, which also enables advanced error compensation techniques for both static and dynamic DAC errors.

Despite the type of DSM, it is typically used for in-band SNR enhancement. Roverato *et al.* [12] proposed to decouple the signal band and the passband of a DSM and use the frequency notches of NTF for OOB noise attenuation. Reconfigurable dynamic element matching (DEM) is used to alleviate the spectral growth at the notch frequency by shaping DAC element mismatch errors. Depending on the magnitude of the mismatch errors, the shaped errors may degrade the signal-band SNR. Nevertheless, the prior DSMs only support one type of application, i.e., either lowpass/bandpass for high in-band SNR or bandpass for low OOB noise, which cannot meet the increasing demands on multi-standard and multi-band communications.

### B. Multimode Delta-Sigma Modulation

In this work, we use a hybrid DAC structure for its intrinsic linear operation and opportunity for digital pre-distortion (DPD). As shown in Fig. 3, the input digital signal is split into the MSB and LSB path. The LSB path is reduced to fewer bits via a DSM, while the MSB path remains unchanged. The DSM is implemented in an error-feedback structure to ensure an all-pass signal transfer function (STF) and to achieve a multimode NTF via programming the loop filter  $[H(z)]$  coefficients. Based on the signal bandwidth and in-band noise requirements,  $K$  bits are truncated from a  $P$ -bit input (Din). The final  $N$ -bit output (Dout) may be larger than  $(P - K)$  bits, depending on the number of overflow bits, which is determined by the maximum gain of NTF. The multimode DSM supports

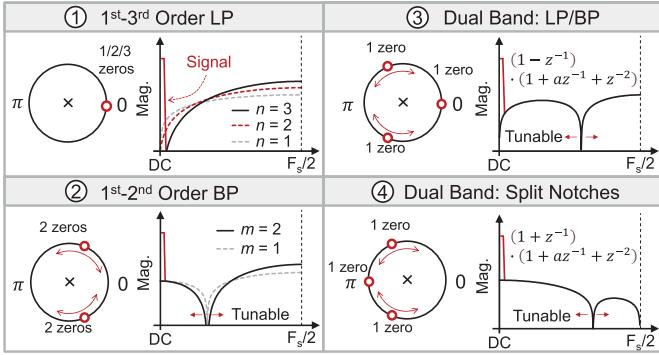

Fig. 4. Zero-pole plots for different modes.

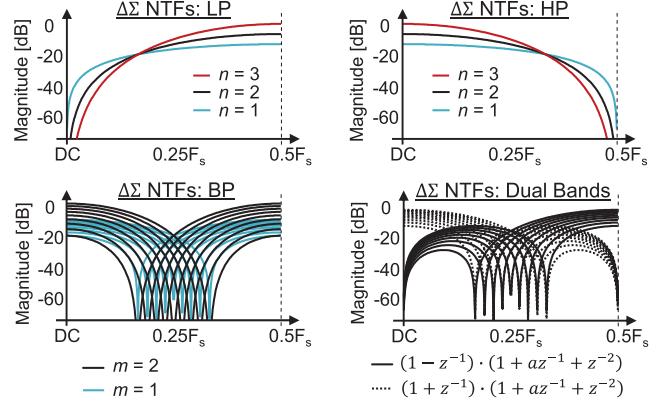

lowpass (LP), highpass (HP), bandpass (BP), and dual-band NTFs, which can be expressed as

$$\text{NTF}(z) = \begin{cases} (1 \pm z^{-1})^n \\ (1 + az^{-1} + z^{-2})^m \\ (1 \pm z^{-1})(1 + az^{-1} + z^{-2}) \end{cases} \quad (1)$$

where  $n \in \{1, 2, 3\}$ ;  $m \in \{1, 2\}$ ; and  $a \in [-1, 1]$ . The zero-pole plots of the NTFs for different operation modes are depicted in Fig. 4. According to (1), all the poles locate at the origin and all the zeros are on the unit circle. In the single-band mode, zeros are located at the same position and moved along the unit circle. Dual-band operation is achieved by splitting the zeros, where one zero is fixed for in-band SNR enhancement while the others are tunable for OOB noise attenuation.

To determine the number of output bits ( $N$ ) of the DSM, we first need to calculate the maximum gain of the NTF over all filter response configurations. From (1), the maximum gain is dominated by the second-order bandpass NTF, i.e.,  $(1 + az^{-1} + z^{-2})^2$ . Assuming  $a = 2 \cos \omega_i$ , where  $\omega_i$  presents the notch frequency, the NTF gain can be obtained from the infinity-norm

$$\|\text{NTF}\|_\infty = \max_{\omega} |\text{NTF}(e^{j\omega})| = [2(1 + |\cos \omega_i|)]^2. \quad (2)$$

Given a certain  $N$  as the design specification and normalizing the input full scale to unity, the sum of the shaped truncation error (i.e.,  $2^{-M} \|\text{NTF}\|_\infty$ ) and the input signal (i.e., unity) should not be larger than the output full scale (i.e.,  $2^N - 1$ ). Consider the worst case when the sum equals to the output full scale, we have

$$2^{-M} [2(1 + |\cos \omega_i|)]^2 + 1 = 2^{N-M}. \quad (3)$$

Therefore,

$$N = \log_2 \{ [2(1 + |\cos \omega_i|)]^2 + 2^M \}. \quad (4)$$

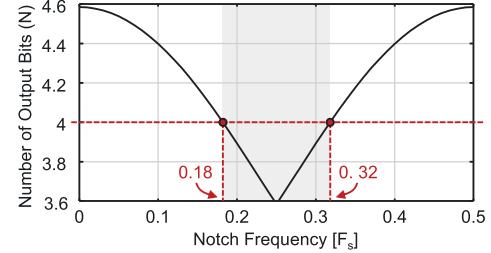

In this work,  $M = 3$  for target signal bandwidth and sufficient stability. With (4), we get the relationship between the number of output bits and the notch frequency, as shown in Fig. 5. For a typical DSM, assuming that the input signal is at full scale, the output will at least have one overflow bit due to the additive DSM noise. Therefore, we keep only one overflow bit for minimum implementation overhead, which leads to  $N = 4$ . To ensure that the output bits do not exceed 4,

Fig. 5. Effective output bits over notch frequency.

Fig. 6. NTFs of the proposed DSM.

the notches of the NTF should be bounded between  $0.18 \times F_s$  and  $0.32 \times F_s$  (Fig. 5). Fig. 6 shows all the implemented NTFs based on (1) and the other design constraints. Different orders of NTFs are available for various design tradeoffs. To further push the achievable notch frequency, one can either increase  $N$  or reduce the order of DSM NTF. There are tradeoffs between implementation cost, bandwidth, and flexibility. Based on (4), the minimum DAC output bits ( $N_{\min}$ ) required to cover the Nyquist band are obtained when  $\cos \omega_i = 0$  or  $\pi$ . In this example shown in Fig. 5, 4.6 DAC output bits are needed for the whole Nyquist band. For higher order NTF, the required number of bits at DAC output will increase accordingly.

### III. TRI-LEVEL TAF

For aggressive in-band noise enhancement, a high-order DSM is typically used and it leads to high OOB noise, which may violate the spectrum emission mask. For DSM to attenuate OOB noise, one can insert frequency notches into the DSM NTF. However, in the application of extremely stringent noise requirements, such as frequency-division duplexing (FDD) systems, frequency notches may be insufficient for noise attenuation due to the circuit non-idealities. Furthermore, the bandwidth of noise attenuation is also limited if solely relying on the frequency notches. In a nutshell, additional noise attenuation is needed. For a multimode DSM, it demands a highly reconfigurable filter. Therefore, a TAF is used for its compelling stopband attenuation and flexibility, thanks to its mostly digital operation [10]. To further enhance the TAF performance in terms of stopband attenuation and flexibility, we propose a cost-efficient tri-level TAF. In the rest of this section, the design tradeoffs of tri-level TAF and the co-design of tri-level TAF and the multimode DSM are discussed.

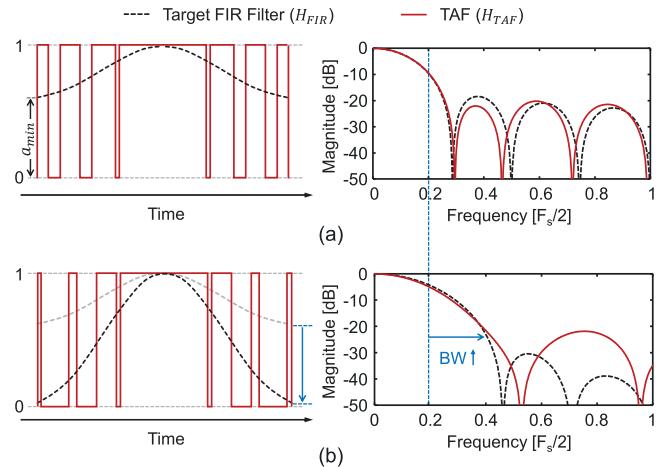

Fig. 7. Concept of TAF.

Fig. 8. TAF pattern generation.

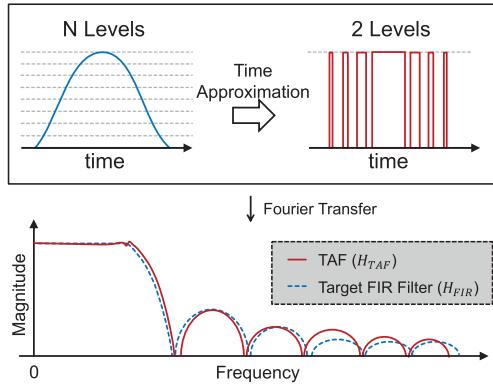

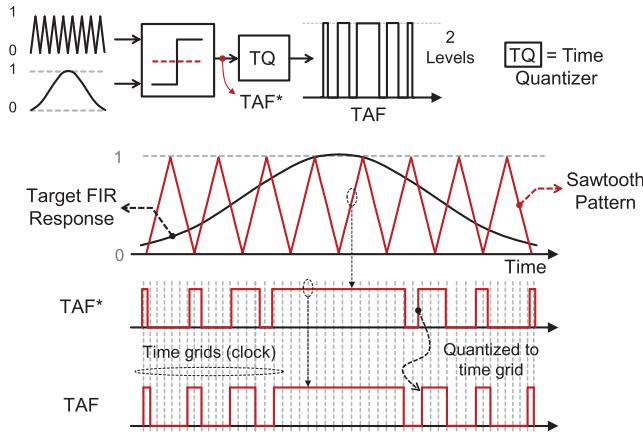

### A. Overview of TAF

The idea of TAF is to approximate the amplitude-varying impulse response of an analog FIR filter with a constant amplitude but a time-varying binary impulse response, such that the frequency responses are similar within a certain band of interest, as shown in Fig. 7. The TAF pattern generation is presented in Fig. 8. Based on the specifications, the impulse response of a target FIR filter is first designed with standard digital filter design flows, such as the FDA tool in MATLAB. The coarse time approximation is done via PWM. The target FIR impulse response is compared with a periodic sawtooth pattern to generate the binary TAF pattern. According to [10], there is an intrinsic gain mismatch between the target FIR (i.e.,  $H_{FIR}$ ) and the TAF (i.e.,  $H_{TAF}$ ) even assuming the time resolution for approximation is infinite, which is estimated by

$$G_{\text{mis}} = 20 \log_{10} \left| \frac{H_{TAF}}{H_{FIR}} \right| \approx 20 \log_{10} \left| \frac{\text{sinc}(a_{\min} T_{\text{tap}} f)}{\text{sinc}(T_{\text{tap}} f)} \right| \quad (5)$$

where  $T_{\text{tap}}$  is the tap delay, and  $a_{\min} \in [0, 1]$  is the minimum filter coefficient of the target FIR filter. The mismatch at dc is zero and increases with frequency. For the cases when  $a_{\min}$  is sufficiently large, i.e.,  $a_{\min}$  is close to 1, the impact of this mismatch on the filtering is ignorable ( $G_{\text{mis}} \sim 0$ ) within the band of interest. In the realistic circuit implementation,

Fig. 9. Impulse and frequency responses of different TAFs. (a) Narrowband TAF with a large  $a_{\min}$ . (b) Wideband TAF with a small  $a_{\min}$ .

the minimum achievable timing resolution for approximation is limited by the system clock rate. After the PWM, a time quantizer snaps the transition edges of the TAF pattern to the rising edge of the clock. The time quantization error introduced here also deviates the frequency response of the TAF from the target FIR filter.

Fig. 9 shows examples of how TAF approximates the target FIR filter response. Here, we assume there are 64 time grids within a period of the TAF's impulse response. For the target FIR filter with a relatively large minimum filter coefficient, the TAF can approximate the filter reasonably well, as shown in Fig. 9(a). If we want to extend the bandwidth of the target FIR filter [Fig. 9(b)], the impulse response covers a wider range of magnitudes (i.e., its minimum coefficient is relatively small), and the TAF can lose its accuracy as also suggested by (5). One approach to resolve this issue is to increase the time resolution for the approximation, which requires a faster clock, and hence poses challenges for TAF pattern generation, system linearity, and efficiency. This motivates the proposed tri-level TAF [19] to alleviate the intrinsic gain mismatch and deviation due to finite time resolution in a more efficient and implementation-friendly way, which will be elaborated in Section III-B.

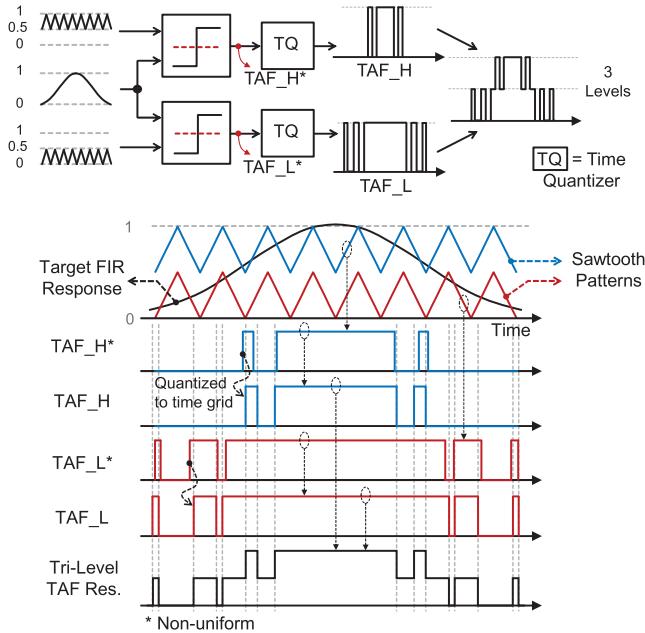

### B. Tri-Level TAF

The tri-level TAF response generation is shown in Fig. 10. Two nonuniform binary patterns (TAF\_H\* and TAF\_L\*) are generated by comparing the target FIR filter impulse response to two sawtooth patterns; each of the patterns generated exercises half of the full scale. Like the TAF, the transition edges of the nonuniform patterns are snapped to the time grids defined by the clock and lead to TAF\_H and TAF\_L. The combination of these two patterns is the impulse response of the tri-level TAF. Note that the above-mentioned impulse response generation is precomputed without extra implementation overhead. Instead of doubling the clock frequency, the tri-level TAF introduces one more amplitude level to effectively increase the approximation accuracy (time resolution) by two times compared with a binary TAF. Moreover, the tri-level TAF

Fig. 10. Tri-level TAF pattern generation.

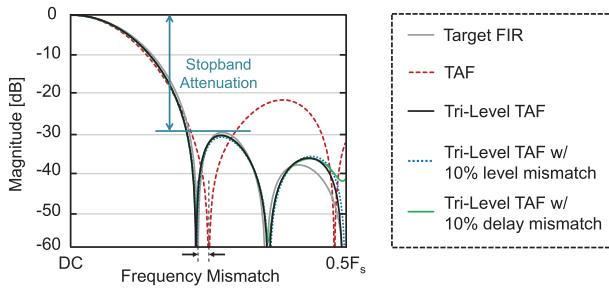

Fig. 11. Frequency responses.

also reduces the intrinsic gain mismatch of a TAF by avoiding a short timing pulse for approximating small filter coefficients. In general, we can estimate the worst case intrinsic gain mismatch of a  $L$ -level TAF to the first order as

$$G_{\text{mis}} \approx 20 \log_{10} \left| \frac{\text{sinc}[(L-1)a_{\min} T_{\text{tap}} f]}{\text{sinc}(T_{\text{tap}} f)} \right|. \quad (6)$$

For example, the  $a_{\min} T_{\text{tap}}$  term in (5) becomes  $2a_{\min} T_{\text{tap}}$  if tri-level TAF is used, which leads to a smaller  $G_{\text{mis}}$  given a certain frequency. The frequency responses of different filters are presented in Fig. 11. The tri-level TAF shows a better approximation and stopband attenuation over the conventional binary TAF.

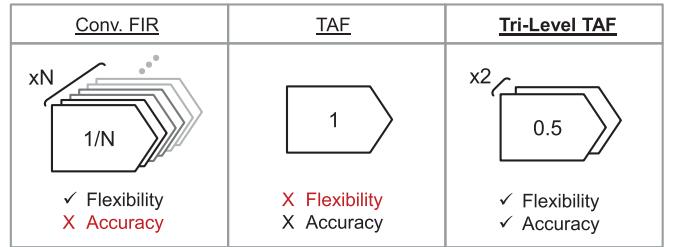

The design tradeoffs of different filters are compared in Fig. 12. The amplitude-varying FIR filter is relatively flexible, thanks to the fine resolution, while a large DAC array is required to present different amplitude levels. The circuit complexity increases due to the DAC array, and the mismatch between elements degrades the filter performance. The TAF response is binary; hence, it requires only a single DAC element, which avoids the matching issue [10]. However, the flexibility of the TAF is limited due to the finite time

Fig. 12. Design tradeoff comparison.

Fig. 13. NTFs of the direct RF TX.

resolution available in the realistic implementation. Compared with a binary TAF with the same clock frequency (i.e., the same time grids), the tri-level TAF shows an improved accuracy of time approximation, leading to better stopband attenuation for a wider span of filter configurations. This also allows for better alignment of the frequency notches of the tri-level TAF to the DSM NTF, leading to superior OOB noise suppression. To achieve tri-level operation, two split DAC elements are needed. The time approximation and reduced amplitude levels relax the matching requirement of a tri-level TAF compared with a conventional analog FIR filter, which typically has fine amplitude levels. Based on the Monte Carlo simulation, and assuming the two DACs have a worse case amplitude mismatch ( $\sim 10\%$ ) that is more than six standard deviations from the average amplitude level, an ignorable impact on the tri-level TAF performance is observed, i.e., less than 0.5-dB difference in terms of stopband attenuation (Fig. 11). Similarly, tri-level TAF transfer function with 10% of sampling period ( $1/F_s$ ) delay mismatch between the two DACs is shown in Fig. 11. In the real implementation, the amplitude and delay mismatch can be controlled well below 10% with proper sizing and interdigitated layout. On the other hand, the timing mismatch between different filter coefficients is negligible compared with the time quantization error in both the TAF and tri-level TAF.

### C. Combine Noise Shaping With Tri-Level TAF

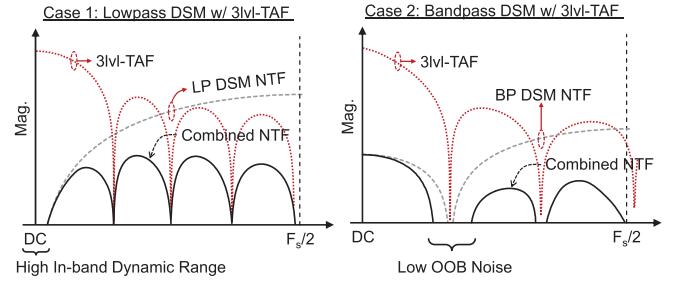

Co-designing the DSM's NTF and the tri-level TAF provides maximal flexibility in supporting different communication scenarios, including creating a low in-band and/or OOB noise floor at multiple frequencies, as required by TDD, FDD, or carrier aggregation. In general, the notches of a tri-level TAF can be either aligned to the DSM notches to enhance noise reduction or solely used to attenuate the shaped noise of DSM.

Fig. 14. System block diagram.

Two representative cases using lowpass and bandpass DSM NTFs with different tri-level TAF responses are presented in Fig. 13. In case 1, the DSM is set to lowpass mode for high in-band dynamic range, and the tri-level TAF is reconfigured for optimal DSM noise reduction at OOB. Likewise, TAF can be used for filtering OOB noise when the DSM is in the dual-band mode. In case 2, all the notches of the DSM NTF are located at the same frequency for OOB noise reduction. One notch of the tri-level TAF is tuned to the same frequency as the DSM notches for deeper and wider bandwidth noise attenuation, while the other notches reduce far-out noise.

#### IV. CIRCUIT IMPLEMENTATION

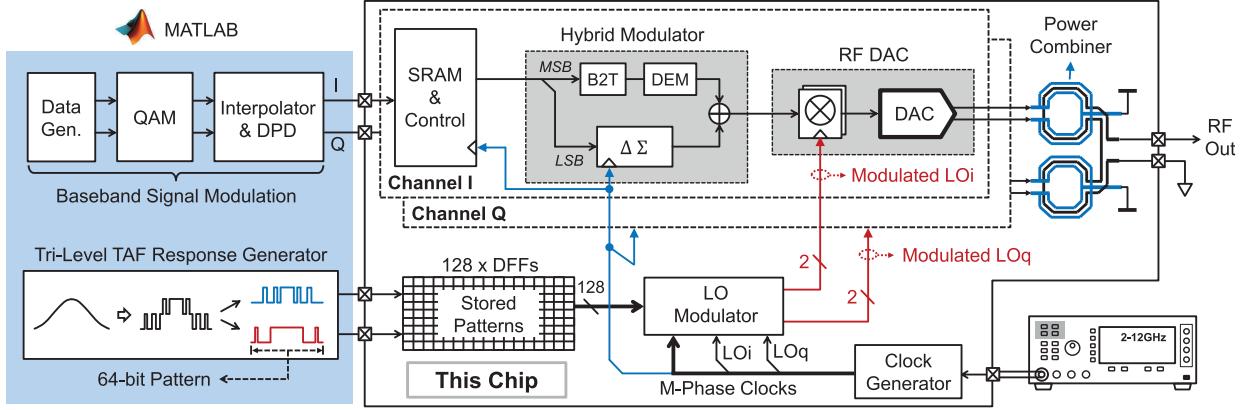

##### A. System Block Diagram

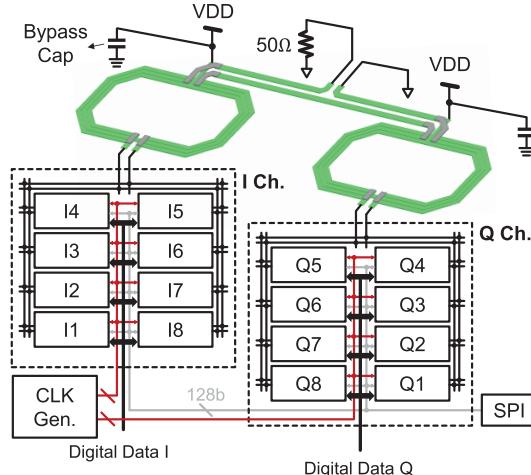

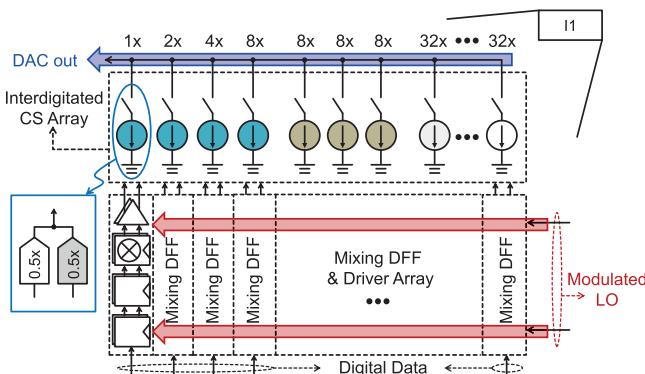

The simplified system block diagram of the proposed direct RF TX is shown in Fig. 14. The test vectors are generated in MATLAB and stored in an on-chip SRAM. A DPD is used to compensate for local mismatches and gain compression when the output power is high. The quadrature data read from the SRAM are processed by the hybrid modulator and passed to the RF DACs. The hybrid modulator splits the input signal into MSB and LSB. The binary MSB bits are then thermometer-coded and shuffled by DEM for better linearity. The LSB bits remain binary and are reduced to fewer bits via the DSM. The processed signals are synchronized and directly converted to the RF signal by the RF DAC, which consists of mixing D flip-flops (DFFs) and current-steering cells. At the DAC output, an on-chip wideband quadrature power combiner is used to sum the I/Q power, convert the differential signals to single-ended, and terminate the final output signal to the  $50\text{-}\Omega$  equipment. Similarly, the tri-level TAF pattern is precomputed via the proposed approximation scheme, split into two binary patterns with a length of 64 bits, and sequentially sent into the on-chip DFF array. The LO modulator takes the stored TAF patterns and generates the modulated LOs for both I and Q channels with the uniform LOs and the multiphase clocks.

##### B. Tri-Level Data Path and LO Modulator

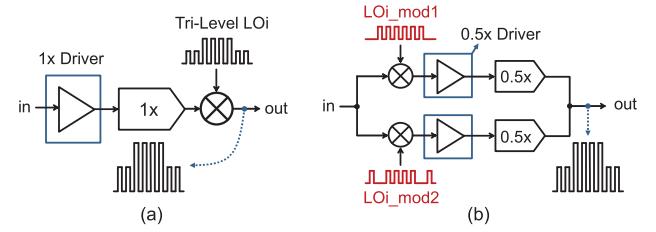

The two possible ways to implement an RF DAC element are shown in Fig. 15. For the more analog approach shown

Fig. 15. (a) Single and (b) Split DAC implementation for tri-level TAF.

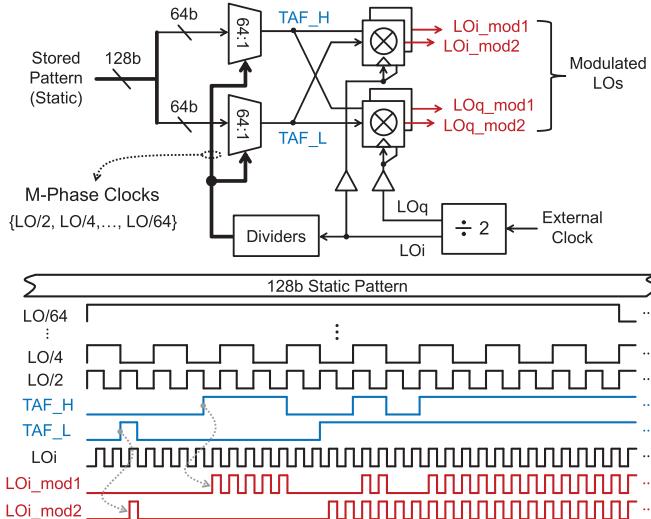

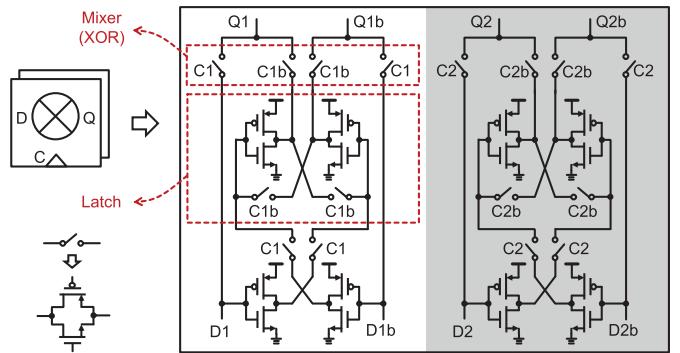

in Fig. 15(a), upconversion is done after the DAC through a tri-level LO and an analog mixer. To minimize analog complexity and non-linearity, we proposed splitting the DAC element into two half cells, each controlled by a chopped input signal. The binary LOs, i.e.,  $\text{LOi\_mod1}$  and  $\text{LOi\_mod2}$ , are decomposed from the tri-level LO. This way, the tri-level TAF operation is effectively achieved at the output of the DACs, as shown in Fig. 15(b). Fig. 16 presents the generation of modulated LOs. The 128-bit stored TAF patterns are periodically read out by two 64-to-1 multiplexer (MUXs) via a wraparound counter (dividers), acting as a cyclic modulator. The 1-bit stream ( $\text{TAF\_H}$  and  $\text{TAF\_L}$ ) from the MUX then multiplies with the uniform LO ( $\text{LOi}$  and  $\text{LOq}$ ) via a mixing DFF, which deglitches the signal from the combinational operation and turns the lowpass TAF into a bandpass TAF centered at the carrier frequency.

##### C. Quadrature Power DAC

Fig. 17 presents the proposed quadrature TX. An eight-way time-interleaved (TI) DAC is implemented to allow a longer duration for the tri-level TAF impulse response and to effectively provide more time steps for time approximation. According to the analysis in [10], the timing skew between TI channels has an ignorable impact on the filter performance. Still, it can result in interleaving spurs at every  $F_s/M$ , where  $M$  is the number of TI channels. Ignoring the DAC output reconstruction filtering and considering the worst case, i.e., the signal bandwidth is more than 80 MHz at 800 MS/s, a digital-to-time converter with 60-fs tuning resolution is implemented for each TI channel to compensate for the TI skew, which

Fig. 16. LO modulator.

Fig. 17. I/Q DAC and combiner.

Fig. 18. Single-channel DAC.

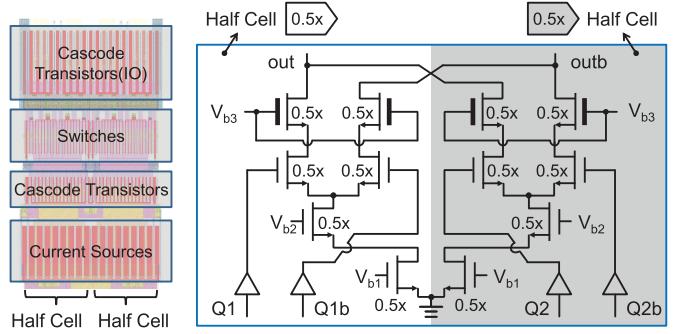

ensures less than 100-dBc interleaving spur. The output power of the I and Q DACs is combined through a wideband transformer. Fig. 18 presents a channel of the TI DAC. The DAC array consists of 15 thermometer-coded  $32 \times$  MSB branches,

Fig. 19. Split current-steering cell.

Fig. 20. Split mixing latch.

Fig. 21. Single-channel programmable dual-band DSM.

three thermometer-coded  $8 \times$  branches, and four LSB branches to accommodate design tradeoffs. The LSB branches are controlled by the DSM output signal, which requires high precision. For better matching, these current branches are sized sufficiently large with interdigitated layout. The DAC controls are generated by mixing DFF arrays, which perform input data synchronization and upconversion. The modulated LOs and the DAC output are routed in opposite directions for area-efficient timing alignment. The unit current-steering cell consists of two equally weighted half cells, which are placed and routed close to each other for minimum mismatches and sharing the common ground (Fig. 19). The digital input signals of the current-steering cell are generated from two splits of mixing latches [24], which are also laid out together to minimize the mismatch-induced timing skew, as shown in Fig. 20.

#### D. Dual-Band DSM

Fig. 21 presents the bandpass DSM in the LSB path of the hybrid DAC. The DSM takes the 12b LSB from the 18b input signal and reserves one more bit for the calibration

Fig. 22. Eight-way TI implementation of the dual-band DSM.

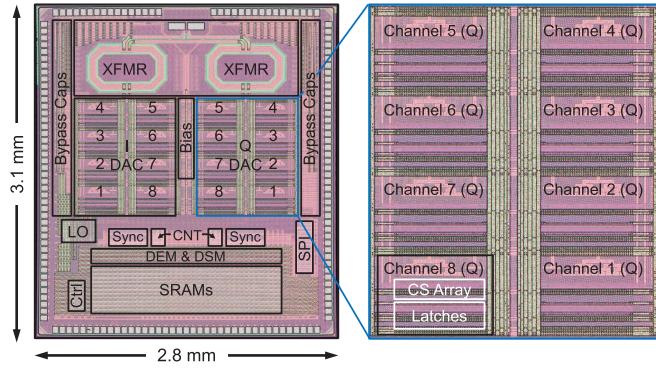

Fig. 23. Die micrograph.

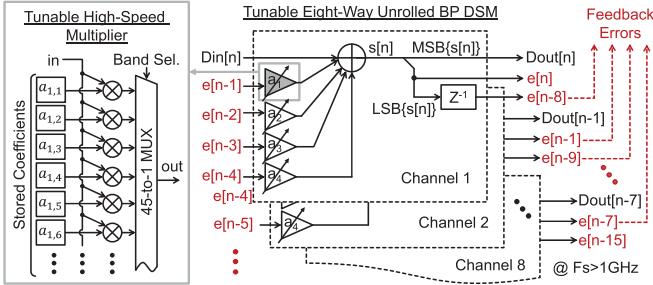

margin, and then truncates the signal to 4b to reduce the analog complexity. Multimode operation is achieved by reconfiguring the DSM NTF. The NTF can have two tunable complex zeros at the same location or one tunable complex zero with a real zero at dc or Nyquist frequency. The DSM can also be tuned from first to third order to trade off the in-band and OOB noise performance. To achieve a throughput more than 1 GS/s, we use an eight-way unrolled DSM, with each channel operating at 125 MS/s, as shown in Fig. 22. For a high-speed tunable gain stage with a wide tuning range (i.e., 45 configurations in this prototype), an MUX-based multiplier is used with a minimized critical path. In addition, multiplications are performed by shifting and summation for simplicity and shortened critical paths.

## V. MEASUREMENT RESULTS

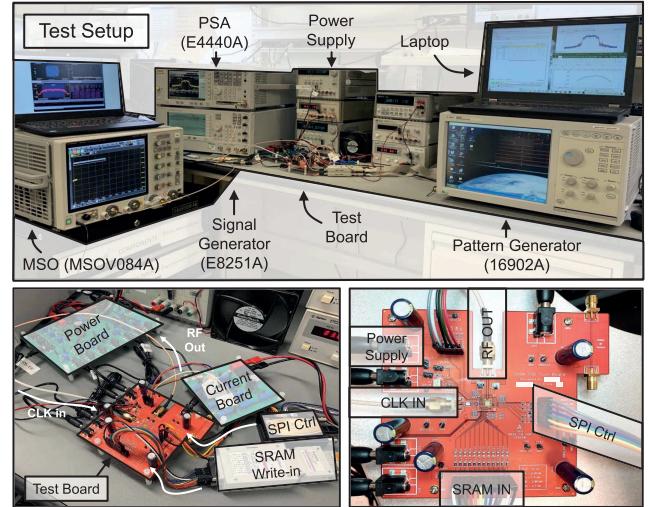

Fig. 23 shows the chip micrograph of the TX prototype fabricated in a 65-nm CMOS. The measurement setup is presented in Fig. 24. The die is attached to the printed circuit board (PCB) via chip-on-board bonding to reduce the clock and data trace for wideband operation. A E8251A signal generator provides the 1–12-GHz clock. SPI is controlled by an USBee pattern generator, while a 16902A pattern generation module with sufficient memory is used for SRAM data write-in. The RF output switches between the E4440A spectrum analyzer and the MSOV084A mixed-signal oscilloscope for noise measurement and demodulation, respectively.

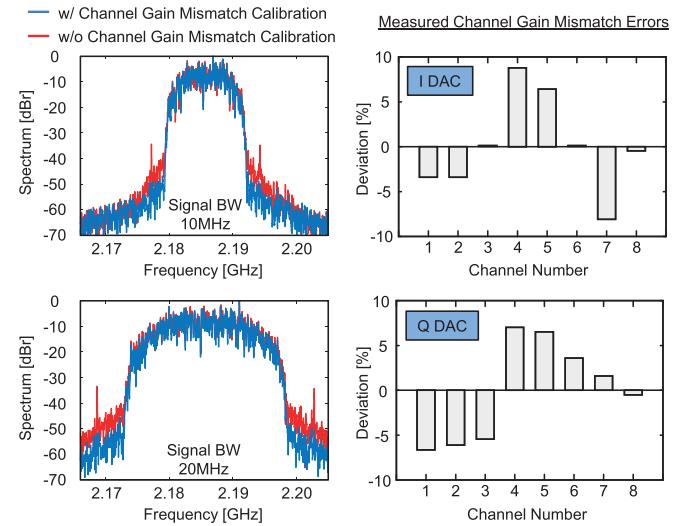

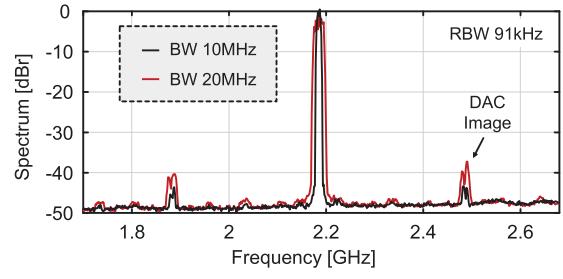

Foreground calibration for the gain mismatches between the TI channels is performed before prior to the other testing. Fig. 25 presents the measured spectra of 256-quadratic-

Fig. 24. Measurement setup.

Fig. 25. Measured spectra and channel mismatch errors.

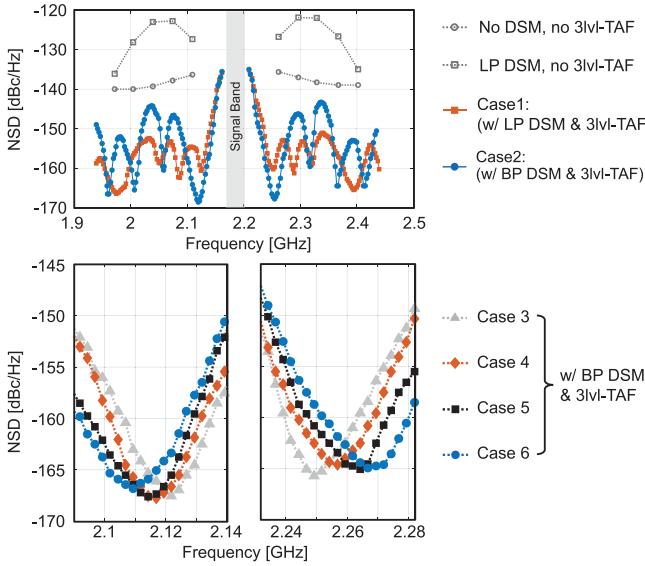

amplitude modulation (QAM) signals and the associated gain mismatch errors of all the TI channels, including I and Q DACs. The measured noise spectral density (NSD) is shown in Fig. 26. With a 2-MHz 256-QAM signal, the DSM is configured at third-order lowpass for high in-band resolution, and the tri-level TAF is configured for optimal OOB noise suppression (case 1). The OOB NSD measures less than  $-150$  dBc/Hz over the Nyquist band. To achieve a lower noise floor at a specific band, we reconfigure the DSM's NTF to bandpass and tune the notches of the DSM and tri-level TAF to the same band of interest. As a result, the lowest NSD achieves  $-169$  dBc/Hz at 68-MHz offset (cases 2, 3) without a surface acoustic wave (SAW) filter. The associated average NSD over 10- and 20-MHz bandwidth measures  $-168$  and  $-166$  dBc/Hz, respectively. For different applications, the notch frequency of the tri-level TAF can be tuned to achieve optimal system performance. The fine-tuning resolution of the proposed tri-level

Fig. 26. Measured NSD.

Fig. 27. Measured spectra and constellation plots.

TAF allows the filter notch to shift with a frequency step of  $\sim 3$  MHz (cases 3–6).

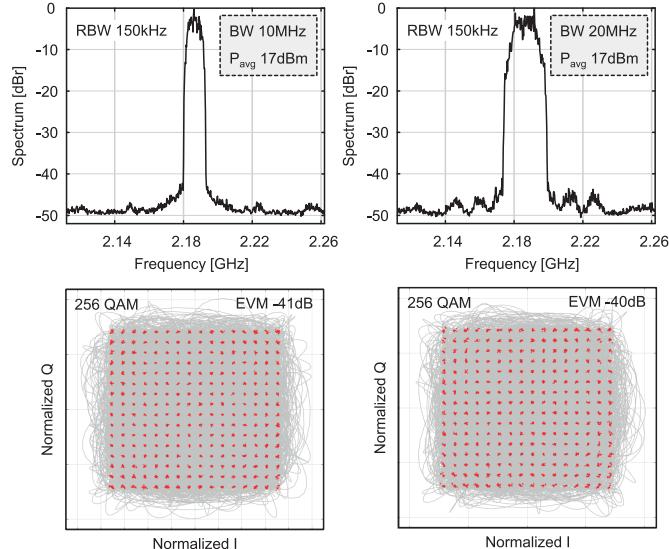

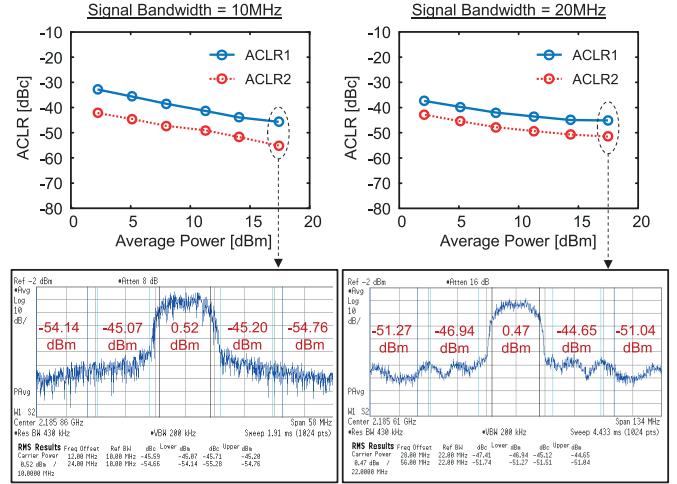

Fig. 27 shows the measured spectra and constellation plots with 10- and 20-MHz 256-QAM signals at 2.2 GHz. Error vector magnitude (EVM) measures  $-41$  and  $-40$  dB, respectively, with 17.4-dBm average output power. We attenuate the signal before sending it to the spectrum analyzer to ensure ignorable signal distortion due to the equipment. This extra attenuation will be compensated back when calculating the actual signal power of the TX. Fig. 28 shows the measured adjacent channel leakage ratio (ACLR) over the average output power with the QAM signals and shows a representative spectrum at peak average power. Fig. 29 shows the measured wideband spectra that cover up to the third Nyquist zone. The chip performance is summarized in Table I and compared with

Fig. 28. Measured ACLR.

Fig. 29. Measured wideband spectra with 256-QAM signals.

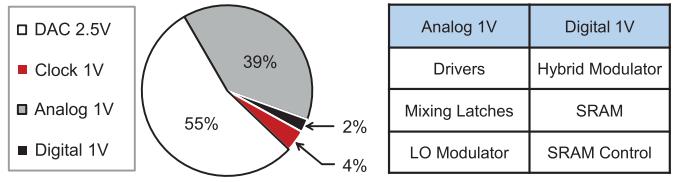

Fig. 30. Measured power breakdown.

the state-of-the-art high-performance TXs, which include both digital and analog architectures. The proposed noise-shaping technique and tri-level TAF effectively achieved a decent OOB noise floor without using additional inductor-based or SAW filters. The measured power consumption breakdown of the TX is shown in Fig. 30. The current-steering cells (i.e., DAC) take 55% of the power from a 2.5-V supply. Other critical blocks, such as DAC and LO drivers, mixing latches, and LO modulator, operate at 1 V for lower power and higher speed. According to the post-layout simulations, the power consumption of the LO modulator occupies less than 9% of the total power consumption of these 1-V building blocks. All the synthesized digital circuits, including SRAMs, SRAM control, and the hybrid modulator, operate at 1 V with a separate supply and consume 31-mW total power, of which the hybrid modulator takes 18.5 mW.

TABLE I

PERFORMANCE SUMMARY AND COMPARISON TO PRIOR ARTS

| Specifications               |                               | This work                       |               | [25]<br>Qi<br>ISSCC'20 | [26]<br>Tang<br>ISSCC'19 | [27]<br>Liu<br>ISSCC'18 | [4]<br>Mehrpoor<br>JSSC'18 | [12]<br>Roverato<br>JSSC'17 | [28]<br>Fulde<br>ISSCC'17 | [29]<br>Bhagavatula<br>ISSCC'17 | [14]<br>Filho<br>ISSCC'16       | [30]<br>Giannini<br>ISSCC'11 | [31]<br>Boos<br>ISSCC'11 | [7]<br>Pozsgay<br>ISSCC'08       |

|------------------------------|-------------------------------|---------------------------------|---------------|------------------------|--------------------------|-------------------------|----------------------------|-----------------------------|---------------------------|---------------------------------|---------------------------------|------------------------------|--------------------------|----------------------------------|

| Architecture                 |                               | Digital IQ                      |               | Analog IQ              | Analog IQ                | Analog IQ               | Digital IQ                 | Digital IQ                  | Digital Polar             | Analog IQ                       | Digital IQ                      | Analog IQ                    | Digital IQ               | Digital IQ                       |

| Matching Network             |                               | On-chip                         |               | On-chip                | On-chip                  | On-chip                 | Off-chip                   | On-chip                     | On-chip                   | On-chip                         | Off-chip                        | On-chip                      | On-chip                  | Off-chip                         |

| On-chip PLL                  |                               | No                              |               | No                     | Yes                      | Yes                     | No                         | No                          | Yes                       | No                              | No                              | No                           | Yes                      | Yes                              |

| Process                      | [nm]                          | 65                              |               | 28                     | 28                       | 14                      | 40                         | 28                          | 28                        | 14                              | 28                              | 40                           | N/A                      | 65                               |

| Active Area                  | [mm <sup>2</sup> ]            | 2.4                             |               | 0.31                   | 8.3 <sup>(a)</sup>       | 1                       | 0.21                       | 0.82                        | 1.3                       | 1.1                             | 0.22                            | 0.98                         | 2                        | 0.35                             |

| Supply                       | [V]                           | 1/2.5                           |               | 1/1.8                  | 1.2/1.8                  | N/A                     | 1.1/2                      | 0.9/1.5                     | 1/1.1/1.3                 | 1/1.8                           | 0.9/1.1                         | 1.1/2.5                      | 1.2/2.5                  | 1.2                              |

| Resolution                   | [bits]                        | 9-18                            |               | N/A                    | N/A                      | N/A                     | 9                          | 10                          | 15                        | N/A                             | 12                              | N/A                          | 14                       | 11                               |

| F <sub>s</sub> Range         | [MS/s]                        | 125-750                         |               | N/A                    | N/A                      | N/A                     | 250-750                    | 850-900                     | 700-2800                  | N/A                             | 500                             | N/A                          | >1000                    | 1350                             |

| F <sub>LO</sub>              | [GHz]                         | 2.2                             |               | 2.54                   | 2.59                     | 2.53                    | 3                          | 0.9                         | 2.54                      | 0.79                            | 2.4                             | 1.85                         | 1.9                      | 2.45                             |

| P <sub>out</sub>             | [dBm]                         | 17.4                            |               | 3                      | 6.3                      | 3.1                     | 1                          | 3                           | 6                         | 4.9                             | -3.5                            | 2.6                          | 6                        | 2.6                              |

| $\eta_{sys}$                 | [%]                           | 4.5                             |               | 2.8                    | 2.7                      | 1.8                     | 0.86                       | 1.3                         | 2.6                       | 2.6                             | 1.8                             | 1.4                          | 3                        | 0.72                             |

| P <sub>DC</sub>              | mW                            | 1221                            |               | 70.5                   | 158.1                    | 113.2                   | 146                        | 150                         | 155                       | 120                             | 24.8                            | 126.4                        | 133.2                    | 254.3                            |

| Bandwidth                    | [MHz]                         | 10                              | 20            | 20                     | 20                       | 57                      | 20                         | 20                          | 20                        | 20                              | 20                              | 20                           | 4                        | 17                               |

| EVM                          | [dB]                          | -41                             | -40           | -34.4                  | -40                      | N/A                     | -30                        | N/A                         | -31.7                     | -32                             | -36                             | -31.7                        | -28                      | -32.4                            |

| ACLR1                        | [dB]                          | -46                             | -45           | -44.4                  | -45                      | -44.7                   | -44                        | -61                         | -44.3                     | -42                             | -47                             | -38.4                        | -49                      | -42.8                            |

| ACLR2                        | [dB]                          | -55                             | -51           | N/A                    | N/A                      | N/A                     | N/A                        | N/A                         | -54.2                     | N/A                             | -59                             | -59                          | N/A                      | -46.2                            |

| Noise Floor                  | [dBm/Hz]                      | -151.6 <sup>(b)</sup><br>@68MHz |               | -155                   | -152.6<br>@80MHz         | -154.7<br>@80MHz        | -139                       | -155                        | -146                      | -150.1 <sup>(c)</sup><br>@31MHz | -162.5 <sup>(d)</sup><br>@45MHz | -159.9<br>@80MHz             | -154<br>@45MHz           | -142.4 <sup>(e)</sup><br>@500MHz |

|                              | [dBc/Hz]                      | -169 <sup>(b)</sup><br>@68MHz   |               | -158                   | -158.9<br>@80MHz         | -157.8<br>@80MHz        | -140                       | -158                        | -152                      | -155 <sup>(c)</sup><br>@31MHz   | -159 <sup>(d)</sup><br>@45MHz   | -162.5<br>@80MHz             | -160<br>@45MHz           | -145 <sup>(e)</sup><br>@500MHz   |

| OOB Noise Suppression Scheme | Noise Shaping + Tri-level TAF |                                 | Analog Filter | Analog Filter          | Analog Filter            | Sinc <sup>1-3</sup>     | Noise Shaping              | Sinc                        | Analog Filter             | Sinc <sup>2</sup>               | Analog Filter                   | Sinc                         | 2-tap FIR                |                                  |

| Modulation                   | SC<br>256 QAM                 |                                 | SC<br>256 QAM | LTE<br>QPSK            | LTE<br>/                 | SC<br>64 QAM            | LTE<br>/                   | LTE20<br>64 QAM             | LTE<br>/                  | Multi-tone<br>64 QAM            | LTE<br>/                        | WCDMA<br>/                   | OFDM<br>64 QAM           |                                  |

- (a) It includes two transmitters for carrier aggregation;

- (b) Measured with a 2-MHz 256-QAM signal and the DSM set to bandpass mode;

- (c) Measured with P<sub>out</sub> = 0 dBm;

- (d) Measured with a 10-MHz 500-MS/s CW;

- (e) Measured with P<sub>out</sub> = -4 dBm.

SC – Single Carrier

N/A – Not available

P<sub>out</sub> – Average output power

$\eta_{sys}$  = P<sub>out</sub>/P<sub>DC</sub>

P<sub>DC</sub> – Total power consumption

## VI. CONCLUSION

In this work, we present a direct RF TX incorporating the hybrid DAC architecture using a reconfigurable dual-band DSM, which can create in-band and/or OOB spectral notches to support various communication scenarios. In addition, the TX applies the proposed tri-level TAF concept, enabling co-design with the multimode DSM for sharp OOB noise suppression. Tri-level operation allows more flexibility and less implementation overhead compared with the binary TAF. Thanks to the mostly digital operation of both DSM and TAF, the proposed TX is highly flexible, scalable, and less prone to process, voltage, and temperature variations. In addition, the reconfigurability of noise shaping and filtering can be completely done by programming the digital codes without tuning extra analog components, such as a resistor, capacitor, inductor, and current source. As a result, this TX architecture is implementation-friendly and eases design automation.

## REFERENCES

- P. Eloranta, P. Seppinen, S. Kallioinen, T. Saarela, and A. Parssinen, “A multimode transmitter in 0.13  $\mu$ m CMOS using direct-digital RF modulator,” *IEEE J. Solid-State Circuits*, vol. 42, no. 12, pp. 2774–2784, Dec. 2007.

- C. Lu *et al.*, “A 24.7 dBm all-digital RF transmitter for multimode broadband applications in 40 nm CMOS,” in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2013, pp. 332–333.

- M. S. Alavi, R. B. Staszewski, L. C. N. de Vreede, and J. R. Long, “A wideband 2  $\times$  13-bit all-digital I/Q RF-DAC,” *IEEE Trans. Microw. Theory Techn.*, vol. 62, no. 4, pp. 732–752, Apr. 2014.

- M. Mehrpoor, M. Hashemi, Y. Shen, L. C. N. de Vreede, and M. S. Alavi, “A wideband linear I/Q-interleaving DDRM,” *IEEE J. Solid-State Circuits*, vol. 53, no. 5, pp. 1361–1373, May 2018.

- S. M. Taleie, T. Copani, B. Bakkaloglu, and S. Kiaei, “A bandpass  $\Delta$   $\Sigma$  RF-DAC with embedded FIR reconstruction filter,” in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2006, pp. 2370–2379.

- A. Jerng and C. G. Sodini, “A wideband  $\Delta$   $\Sigma$  digital-RF modulator for high data rate transmitters,” *IEEE J. Solid-State Circuits*, vol. 42, no. 8, pp. 1710–1722, Aug. 2007.

- A. Pozsgay, T. Zouves, R. Hossain, M. Boulemnaker, V. Knopik, and S. Grange, “A fully digital 65nm CMOS transmitter for the 2.4-to-2.7GHz WiFi/WiMAX bands using 5.4GHz  $\Delta$   $\Sigma$  RF DACs,” in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2008, pp. 360–619.

- A. Frappe, A. Flament, B. Stefanelli, A. Kaiser, and A. Cathelin, “An all-digital RF signal generator using high-speed  $\Delta$   $\Sigma$  modulators,” *IEEE J. Solid-State Circuits*, vol. 44, no. 10, pp. 2722–2732, Oct. 2009.

- R.-C. Marin, A. Frappe, B. Stefanelli, P. Cathelin, A. Cathelin, and A. Kaiser, “Digital RF transmitter with single-bit  $\Delta$   $\Sigma$  M-driven switched-capacitor RF DAC and embedded band filter in 28-nm FD-SOI,” *IEEE Trans. Microw. Theory Techn.*, vol. 67, no. 7, pp. 3200–3209, Jul. 2019.

- [10] S. Su and M. S.-W. Chen, "A time-approximation filter for direct RF transmitter," *IEEE J. Solid-State Circuits*, vol. 56, no. 7, pp. 2018–2028, Jul. 2021.

- [11] M. Park, M. H. Perrott, and R. B. Staszewski, "An amplitude resolution improvement of an RF-DAC employing pulsedwidth modulation," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 58, no. 11, pp. 2590–2603, Nov. 2011.

- [12] E. Roverato *et al.*, "All-digital LTE SAW-less transmitter with DSP-based programming of RX-band noise," *IEEE J. Solid-State Circuits*, vol. 52, no. 12, pp. 3434–3445, Dec. 2017.

- [13] P. E. P. Filho, M. Ingels, P. Wambacq, and J. Craninckx, "An incremental-charge-based digital transmitter with built-in filtering," *IEEE J. Solid-State Circuits*, vol. 50, no. 12, pp. 3065–3076, Dec. 2015.

- [14] P. E. P. Filho, M. Ingels, P. Wambacq, and J. Craninckx, "A 0.22 mm<sup>2</sup> CMOS resistive charge-based direct-launch digital transmitter with -159dBc/Hz out-of-band noise," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Jan. 2016, pp. 250–252.

- [15] D. K. Su and B. A. Wooley, "A CMOS oversampling D/A converter with a current-mode semidigital reconstruction filter," *IEEE J. Solid-State Circuits*, vol. 28, no. 12, pp. 1224–1233, Dec. 1993.

- [16] W. M. Gaber, P. Wambacq, J. Craninckx, and M. Ingels, "A CMOS IQ direct digital RF modulator with embedded RF FIR-based quantization noise filter," in *Proc. ESSCIRC (ESSCIRC)*, Sep. 2011, pp. 139–142.

- [17] S. Fukuda, S. Miya, M. Io, K. Hamashita, and B. Nauta, "Direct-digital modulation (DIDIMO) transmitter with -156dBc/Hz Rx-band noise using FIR structure," in *Proc. ESSCIRC (ESSCIRC)*, Sep. 2012, pp. 53–56.

- [18] R. Bhat, J. Zhou, and H. Krishnaswamy, "Wideband mixed-domain multi-tap finite-impulse response filtering of out-of-band noise floor in watt-class digital transmitters," *IEEE J. Solid-State Circuits*, vol. 52, no. 12, pp. 3405–3420, Dec. 2017.

- [19] S. Su and M. S.-W. Chen, "10.2 A SAW-less direct-digital RF modulator with tri-level time-approximation filter and reconfigurable dual-band delta-sigma modulation," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2020, pp. 174–176.

- [20] D. B. Barkin, A. C. Y. Lin, D. K. Su, and B. A. Wooley, "A CMOS oversampling bandpass cascaded D/A converter with digital FIR and current-mode semi-digital filtering," *IEEE J. Solid-State Circuits*, vol. 39, no. 4, pp. 585–593, Apr. 2004.

- [21] S. Su *et al.*, "A 12 bit 1GS/s dual-rate hybrid DAC with an 8GS/s unrolled pipeline delta-sigma modulator achieving >75dB SFDR over the Nyquist band," *IEEE J. Solid-State Circuits*, vol. 50, no. 4, pp. 896–907, Apr. 2015.

- [22] S. Su *et al.*, "A 12-bit 2GS/s dual-rate hybrid DAC with pulsed-error pre-distortion and in-band noise cancellation achieving >74dB SFDR and <80dBc IM3 up to 1GHz in 65nm CMOS," *IEEE J. Solid-State Circuits*, vol. 51, no. 12, pp. 2963–2978, Dec. 2016.

- [23] S. Su and M. S.-W. Chen, "A 16-bit 12-GS/s single-/dual-rate DAC with a successive bandpass delta-sigma modulator achieving <67-dBc IM3 within DC to 6-GHz tunable passbands," *IEEE J. Solid-State Circuits*, vol. 53, no. 12, pp. 3517–3527, Dec. 2018.

- [24] C. Erdmann *et al.*, "16.3 A 330 mW 14b 6.8GS/s dual-mode RF DAC in 16nm FinFET achieving -70.8dBc ACPR in a 20MHz channel at 5.2GHz," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2017, pp. 280–281.

- [25] G. Qi, H. Shao, P.-I. Mak, J. Yin, and R. P. Martins, "10.1 A 1.4-to-2.7GHz FDD SAW-less transmitter for 5G-NR using a BW-extended N-path filter-modulator, an isolated-BB input and a wideband TIA-based PA driver achieving <157.5dBc/Hz OB noise," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2020, pp. 172–174.

- [26] C.-C. Tang *et al.*, "21.4 An LTE—A multimode multiband RF transceiver with 4RX/2TX inter-band carrier aggregation, 2-carrier 4×4 MIMO with 256QAM and HPUE capability in 28nm CMOS," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2019, pp. 351–352.

- [27] Q. Liu *et al.*, "A 1.4-to-2.7GHz high-efficiency RF transmitter with an automatic 3FLO-suppression tracking-notch-filter mixer supporting HPUE in 14nm FinFET CMOS," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2018, pp. 172–174.

- [28] M. Fulde *et al.*, "A digital multimode polar transmitter supporting 40 MHz LTE carrier aggregation in 28 nm CMOS," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, San Francisco, CA, USA, Feb. 2017, pp. 218–219.

- [29] V. Bhagavatula *et al.*, "13.3 A SAW-less reconfigurable multimode transmitter with a voltage-mode harmonic-reject mixer in 14nm FinFET CMOS," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2017, pp. 220–221.

- [30] V. Giannini, M. Ingels, T. Sano, B. Debaillie, J. Borremans, and J. Craninckx, "A multiband LTE SAW-less modulator with -160dBc/Hz RX-band noise in 40nm LP CMOS," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2011, pp. 374–376.

- [31] Z. Boos *et al.*, "A fully digital multimode polar transmitter employing 17b RF DAC in 3G mode," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2011, pp. 376–378.

**Shiyu Su** (Member, IEEE) received the B.S. degrees from Beijing University of Post and Telecommunication, Beijing, China, and Queen Mary, University of London, London, U.K., in 2011, and the M.S. and Ph.D. degrees from the University of Southern California (USC), Los Angeles, CA, USA, in 2013 and 2019, all in electrical engineering.

His research interests include high-speed data converters, wireless transceiver, digital phase-locked loop, advanced computing, and analog/mixed-signal design automation.

Dr. Su was the recipient of IEEE Solid-State Circuits Society (SSCS) Predoctoral Achievement Award for 2017–2018 and IEEE Solid-State Circuits Society (SSCS) Student Travel Grant Award for 2019–2020. He was a Ming Hsieh Institute Scholar from 2019 to 2020.

**Mike Shuo-Wei Chen** (Senior Member, IEEE) received the B.S. degree from the National Taiwan University, Taipei, Taiwan, in 1998 and the M.S. and Ph.D. degrees from the University of California, Berkeley, Berkeley, CA, USA, in 2002 and 2006, all in electrical engineering.

He is a Professor with the Department of Electrical and Computer Engineering, University of Southern California (USC), Los Angeles, CA. As a graduate student researcher, he proposed and demonstrated the asynchronous SAR ADC architecture, which has

been adopted today for low-power high-speed analog-to-digital conversion products in industry. At USC, he leads an analog mixed-signal circuit group, focusing on data converter, wireless, wireline, computing, and design methodology. His research group has been exploring new circuit architectures that excel beyond the technology limitation, as exemplified in their recent works in PA, ADC, DAC, PLL, and nonuniform sampling. From 2006 to 2010, he has been a member of Analog IC Group at Atheros Communications (now Qualcomm Atheros), San Jose, CA, working on mixed-signal and RF circuits for various wireless communication products.

Dr. Chen was the recipient of Qualcomm Faculty Award in 2019, NSF Faculty Early Career Development (CAREER) Award and DARPA Young Faculty Award (YFA) both in 2014, Analog Devices Outstanding Student Award for recognition in IC design in 2006, and UC Regents' Fellowship at Berkeley in 2000. He also achieved an honorable mention in the Asian Pacific Mathematics Olympiad, 1994. He is currently serving as a Distinguished Lecturer for IEEE Solid-State Circuits Society (SSCS).