This is the author's peer reviewed, accepted manuscript. However, the online version of record will be different from this version once it has been copyedited and typeset.

PLEASE CITE THIS ARTICLE AS DOI: 10.1063/5.0142229

## NiO junction termination extension for high-voltage (>3 kV) $\text{Ga}_2\text{O}_3$ devices

Ming Xiao,<sup>1,a),b)</sup> Boyan Wang,<sup>1,a)</sup> Joseph Spencer,<sup>1,2,3</sup> Yuan Qin,<sup>1</sup> Matthew Porter,<sup>1</sup> Yunwei Ma,<sup>1</sup> Yifan Wang,<sup>1</sup> Kohei Sasaki,<sup>4</sup> Marko Tadjer,<sup>3</sup> and Yuhao Zhang<sup>1,2,b)</sup>

<sup>1</sup>*Center for Power Electronics Systems, The Bradley Department of Electrical and Computer Engineering, Virginia*

*Polytechnic Institute and State University, Blacksburg, VA 24061 USA*

<sup>2</sup>*Department of Material Science and Engineering, Virginia Polytechnic Institute and State University, Blacksburg, VA 24061 USA*

<sup>3</sup>*US Naval Research Laboratory, Washington, DC 20375 USA*

<sup>4</sup>*Novel Crystal Technology, Inc., Sayama 350-1328, Japan*

Edge termination is the enabling building block of power devices to exploit the high breakdown field of wide bandgap (WBG) and ultra-wide bandgap (UWBG) semiconductors. This work presents a heterogeneous junction termination extension (JTE) based on p-type nickel oxide (NiO) for gallium oxide ( $\text{Ga}_2\text{O}_3$ ) devices. Distinct from prior JTEs usually made by implantation or etch, this NiO JTE is deposited on the surface of  $\text{Ga}_2\text{O}_3$  by magnetron sputtering. The JTE consists of multiple NiO layers with various lengths to allow for a graded decrease in effective charge density away from the device active region. Moreover, this surface JTE has broad design window and process latitude, and its efficiency is drift-layer agnostic. The physics of this NiO JTE is validated by experimental applications into NiO/ $\text{Ga}_2\text{O}_3$  p-n diodes fabricated on two  $\text{Ga}_2\text{O}_3$  wafers with different doping concentrations. The JTE enables a breakdown voltage over 3.2 kV and a consistent parallel-plate junction field of 4.2 MV/cm in both devices, rendering a power figure of merit of 2.5~2.7 GW/cm<sup>2</sup>. These results show the great promise of the deposited JTE as a flexible, near ideal edge termination for WBG and UWBG devices, particularly those lacking high-quality homojunctions.

---

<sup>a)</sup> Ming Xiao and Boyan Wang contributed equally to this work.

<sup>b)</sup> To whom correspondence should be addressed. Electronic mail: mxiao@vt.edu, yhzhang@vt.edu

This is the author's peer reviewed, accepted manuscript. However, the online version of record will be different from this version once it has been copyedited and typeset.

PLEASE CITE THIS ARTICLE AS DOI: 10.1063/5.0142229

Power electronics are advancing rapidly driven by deployment of wide bandgap (WBG) and ultra-wide bandgap (UWBG) semiconductors and the associated device innovations.<sup>1</sup> Gallium oxide ( $\text{Ga}_2\text{O}_3$ ) has recently emerged as a promising UWBG power semiconductor, due to its high critical breakdown electric field ( $E_C$ ), controllable doping, and the availability of large diameter wafers.<sup>2,3</sup> In addition to the demonstration of high breakdown voltage ( $BV$ ) over 8 kV<sup>4</sup> and high current over 100 A,<sup>5</sup>  $\text{Ga}_2\text{O}_3$  devices have also been packaged<sup>6,7</sup> and switched in power converters.<sup>8,9</sup>

For power devices, edge termination holds the key for exploiting the high  $E_C$  of WBG/UWBG materials.<sup>10</sup> The junction termination extension (JTE) is a successful edge termination widely used in industrial WBG devices.<sup>11,12</sup> The JTE is based on p-n junctions, where the oppositely doped region compensates the charge of the drift region and thereby weakens the surface electric field (E-field). Despite the JTE's success in Si and WBG devices, the development of  $\text{Ga}_2\text{O}_3$  JTE is hindered by the lack of p-type doping.<sup>13</sup> Existing edge terminations in  $\text{Ga}_2\text{O}_3$  devices rely on field plates,<sup>14–16</sup> implanted traps,<sup>4,17,18</sup> deep mesa,<sup>19</sup> and trench structures.<sup>20</sup> Whereas, the studies in WBG devices have revealed that JTE can enable the superior efficiency<sup>21</sup> (i.e., the device  $BV$  over the ideal  $BV$ ) and robustness<sup>22</sup> as compared to the non-junction-based termination such as field plate.

Nickel oxide (NiO) is an alternative p-type WBG material (bandgap 3.4~4 eV<sup>13</sup>). Recently, NiO has been applied to form heterogenous p-n junction in GaN<sup>23–26</sup> and  $\text{Ga}_2\text{O}_3$  devices. Since the first report,<sup>27</sup> NiO/ $\text{Ga}_2\text{O}_3$  p-n diodes have achieved multi-kilovolt  $BV$  with a low differential specific on-resistance ( $R_{\text{ON,SP}}$ ).<sup>4,8,28–31</sup> Most of these diodes have a natural NiO termination with relatively high doping concentration. The efficiency of such highly-doped, single-layer termination is very sensitive to the NiO doping and thickness.<sup>32–34</sup> Improved JTE designs demonstrated in WBG devices include the multizone JTE,<sup>32–34</sup> graded JTE,<sup>11</sup> and etched JTE,<sup>35</sup> the common feature of which is a graduate decrease in charge density away from the active region.

In this work, we present a NiO-based JTE comprising multiple NiO layers deposited on the surface of the  $\text{Ga}_2\text{O}_3$  drift region. The NiO JTE is lightly doped and has graded decrease in sheet charge density, both enabling broad design window and process latitude. In addition, this deposited JTE differs from the prior JTEs that are formed by implantation, diffusion, or etching. The surface deposition process has minimal damage to  $\text{Ga}_2\text{O}_3$  as compared to the dry etching and obviates the high-temperature activation usually required for implantation. Moreover, the efficiency of this deposited NiO JTE is independent of the doping and thickness of the  $\text{Ga}_2\text{O}_3$  drift region.

In this letter, the JTE's physics is first presented by simulations. Subsequently, NiO/ $\text{Ga}_2\text{O}_3$  p-n diodes are used as the demonstrative vehicle for the JTE's experimental demonstration and evaluation. To show the JTE's wide applicability,  $\text{Ga}_2\text{O}_3$  diodes are fabricated on two wafers with different donor concentration ( $N_D$ ) in the drift region, and their  $BV$  and junction blocking field are compared. Note that the reason of choosing p-n diode over Schottky barrier diode (SBD) to experimentally evaluate the JTE's capability is to avoid the leakage-induced premature breakdown widely reported in  $\text{Ga}_2\text{O}_3$  SBDs.<sup>36–38</sup>

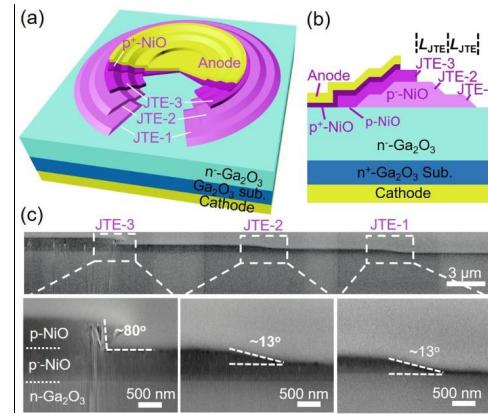

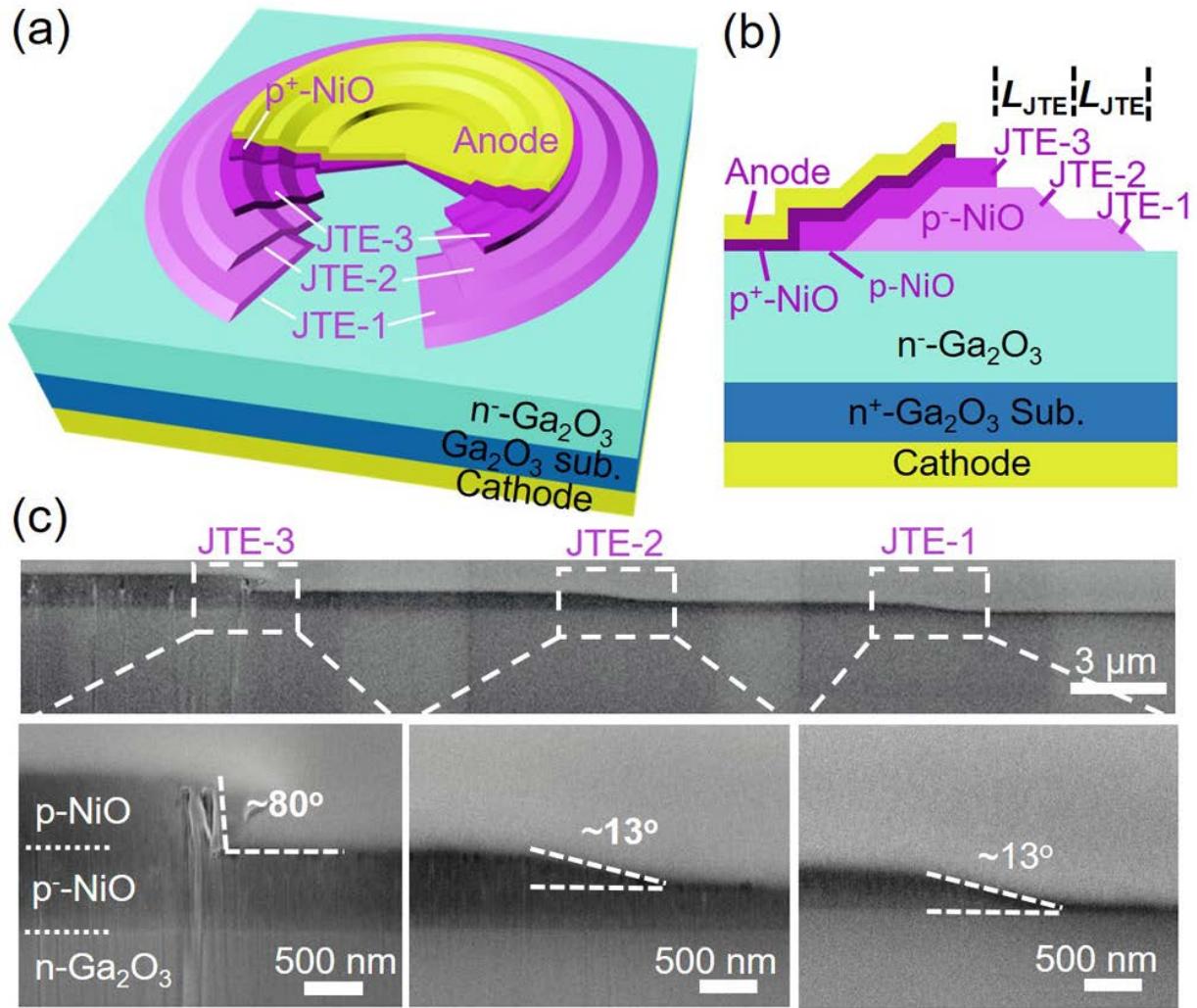

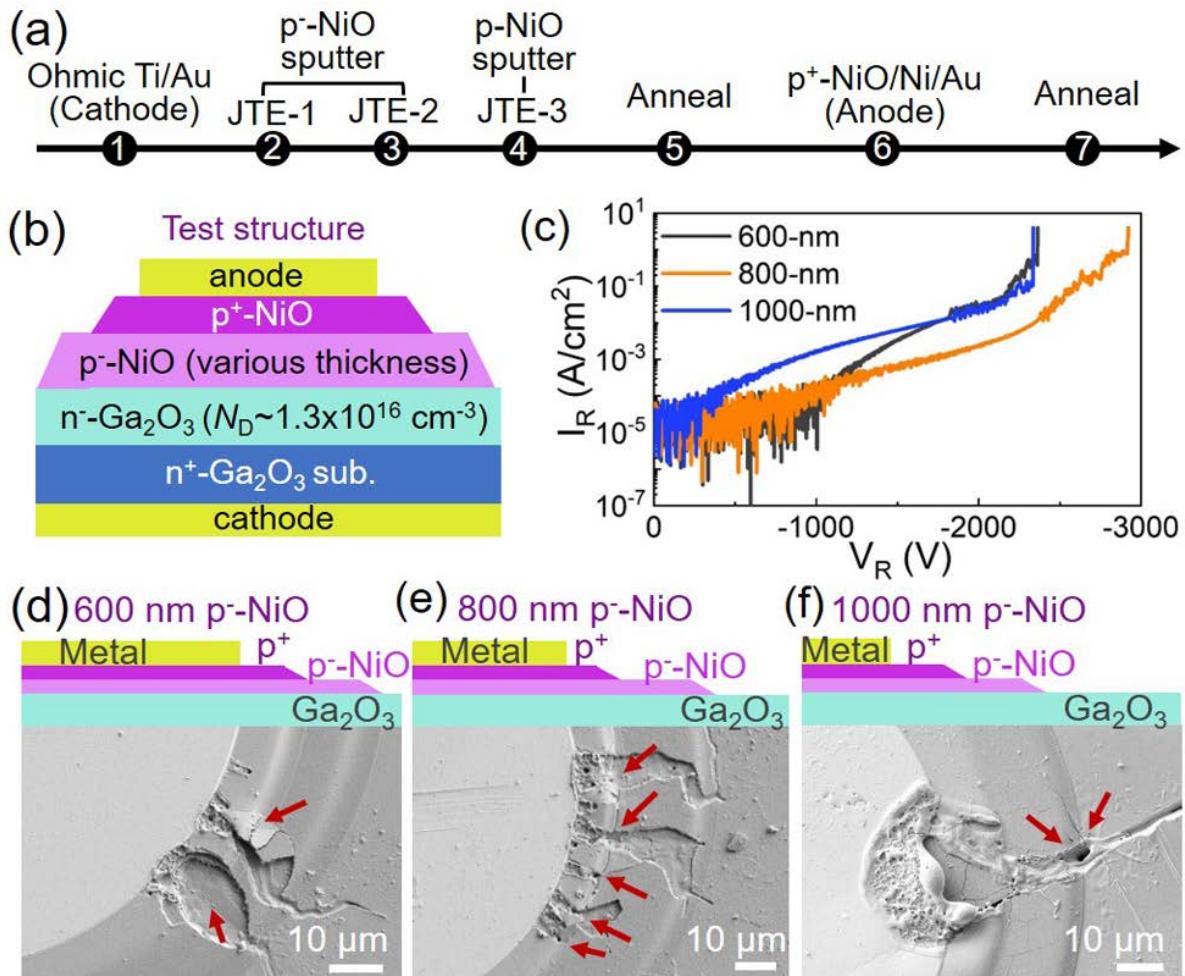

As shown in Fig. 1(a) and (b), the proposed NiO JTE comprises lightly-doped p<sup>-</sup>NiO and highly-doped p<sup>+</sup>-NiO layers. The p<sup>-</sup>-NiO layers are fully depleted at the device  $BV$  to compensate the depletion charge in Ga<sub>2</sub>O<sub>3</sub>, thereby spreading out the crowded E-field at the device edge and reducing the surface E-field. To produce a graded charge profile, the lengths of p<sup>-</sup>-NiO layers decrease from the bottom to the top with an identical incremental length ( $L_{JTE}$ ) for each layer. The sidewall angle of each p<sup>-</sup>-NiO layer is preferable to be small to avoid abrupt changes in charge density. This charge transition can be also smoothed by increasing the number of p<sup>-</sup>-NiO layers. For simplicity, a bi-layer p<sup>-</sup>-NiO region (i.e., JTE-1 and -2) with small sidewall angles is studied in this work, which could achieve near ideal performance with optimal designs. While p<sup>-</sup>-NiO layers fulfill the main JTE functionality, the p<sup>+</sup>-NiO layer interfaces the p<sup>-</sup>-NiO JTE with the anode layer (i.e., p<sup>+</sup>-NiO in the p-n diode). At  $BV$ , this p<sup>+</sup>-NiO cover is only partially depleted, thereby confining the high E-field within itself. Meanwhile, this partially-depleted p<sup>+</sup>-NiO layer can still reduce the E-field at the top surface of p<sup>-</sup>-NiO similar to some counterparts in p-GaN,<sup>10,39</sup> thereby serving as a weak JTE (i.e., JTE-3). As an illustration of the practical JTE, Fig. 1(c) shows the cross-sectional scanning electron microscopy (SEM) images of the fabricated NiO JTE (the fabrication details will be elaborated later).

FIG. 1. (a) 3-D and (b) cross-sectional schematics of the NiO/Ga<sub>2</sub>O<sub>3</sub> p-n diode with the proposed NiO JTE. (c) Cross-sectional SEM images of the entire JTE region fabricated in this work and the edge of each JTE layer.

Three parameters are critical to the JTE functionality, the acceptor concentration ( $N_A$ ) and thickness ( $t_{JTE}$ ) of each p<sup>-</sup>-NiO layer, as well as the  $L_{JTE}$ . Considering a simplified 1-D model in the vertical direction: according to Gauss's law, the optimal sheet charge density in p<sup>-</sup>-NiO can be derived from the full p<sup>-</sup>-NiO depletion at the device  $BV$ <sup>11</sup>

$$qnN_A^{opt}t_{JTE}^{opt} = E_M \epsilon_N \quad (1)$$

where  $n$  is the number of p<sup>-</sup>-NiO JTE layers,  $N_A^{opt}$  and  $t_{JTE}^{opt}$  are the optimal  $N_A$  and  $t_{JTE}$ ,  $E_M$  is the surface E-field in Ga<sub>2</sub>O<sub>3</sub> at the device  $BV$  ( $E_M \leq E_c$ ), and  $\epsilon_N$  is the Ga<sub>2</sub>O<sub>3</sub> permittivity. To probe the E-field distribution, TCAD simulations are performed

This is the author's peer reviewed, accepted manuscript. However, the online version of record will be different from this version once it has been copyedited and typeset.

PLEASE CITE THIS ARTICLE AS DOI: 10.1063/5.0142229

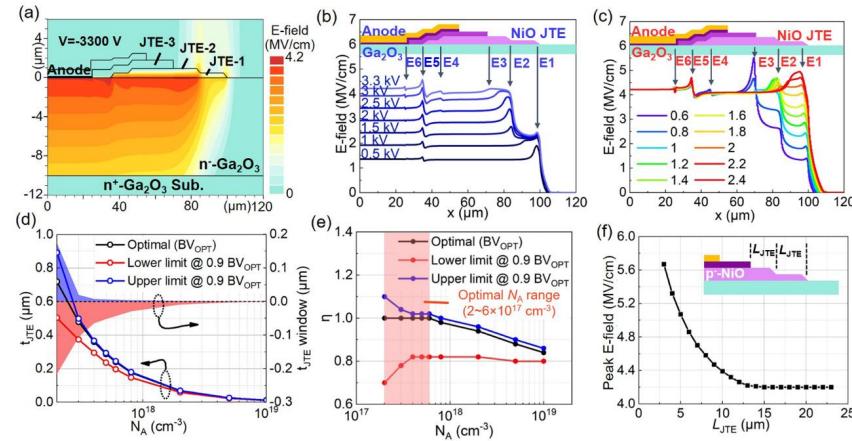

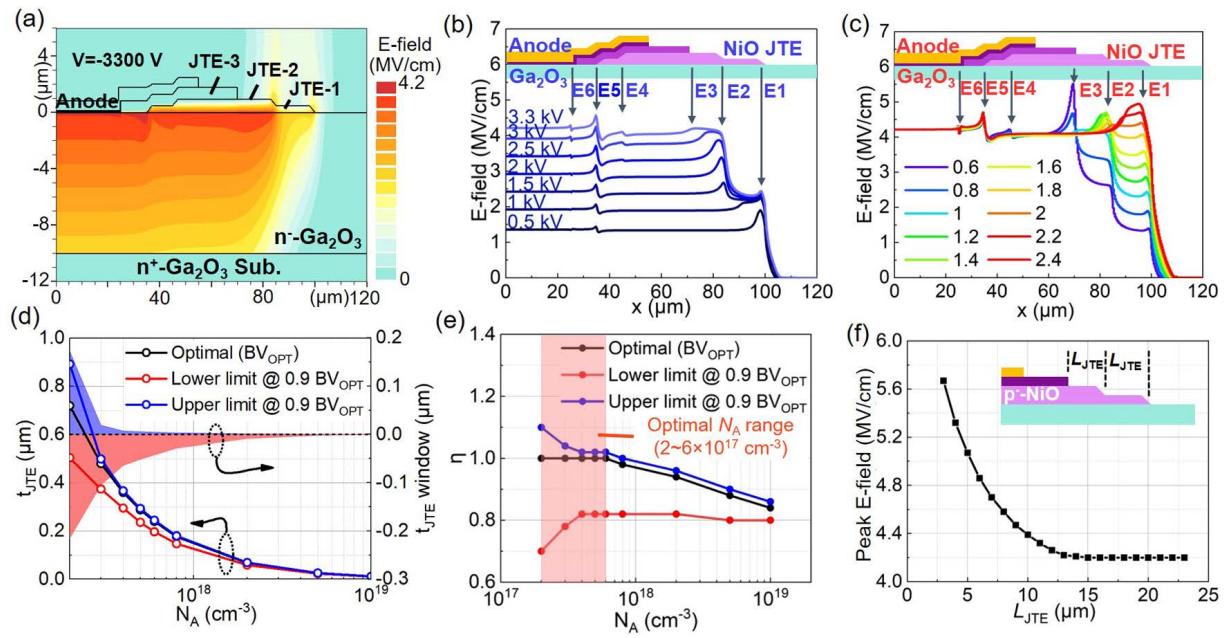

FIG. 2. (a) Simulated E-field contour in a  $\text{Ga}_2\text{O}_3$  p-n diode with an optimal NiO JTE design biased at  $-3.3$  kV. (b) Surface E-field profile in  $\text{Ga}_2\text{O}_3$  at the reverse biases increased from  $0.5$  to  $3.3$  kV. (c) Surface E-field profile in  $\text{Ga}_2\text{O}_3$  at  $-3.3$  kV for various  $N_A$  ranging from  $0.6N_A^{\text{opt}}$  to  $2.4N_A^{\text{opt}}$  while keeping  $t_{\text{JTE}} = t_{\text{JTE}}^{\text{opt}}$  in the p-NiO layers. (d) The  $t_{\text{JTE}}$  for the highest  $BV$  ( $BV_{\text{opt}}$ ), as well as the upper and lower limits of  $t_{\text{JTE}}$  and the associated  $t_{\text{JTE}}$  window for  $90\%$  of the  $BV_{\text{opt}}$ , for several  $N_A$  ranging from  $10^{17}$  to  $10^{19} \text{ cm}^{-3}$ . (e) The  $\eta$  of three  $t_{\text{JTE}}$  leading to  $BV_{\text{opt}}$  and  $90\%BV_{\text{opt}}$  as a function of  $N_A$ . (f) Peak E-field as a function of  $L_{\text{JTE}}$  based on the design in (a)-(b).

Next, we explore the design window of  $N_A$  and  $t_{\text{JTE}}$ , which determines the JTE's process latitude. Here we define a ratio between the JTE's sheet charge density and its 1-D optimal value given by (1), i.e.,  $\eta = N_A t_{\text{JTE}} / (N_A^{\text{opt}} t_{\text{JTE}}^{\text{opt}})$ . Fig. 2(c) shows the  $\text{Ga}_2\text{O}_3$  surface E-field profile at  $3.3$  kV for various  $N_A$  ranging from  $0.6N_A^{\text{opt}}$  to  $2.4N_A^{\text{opt}}$  while keeping  $t_{\text{JTE}} = t_{\text{JTE}}^{\text{opt}}$ . The peak E-fields at the JTE's outer edges (E1-E3) are found to be sensitive to  $\eta$ , while those at the inner edges (E4-E6) changes minimally. When  $\eta < 1$ , the peak E-field grows below the JTE-3's outer edge (E3); when  $\eta > 1$ , the E-field between E1 and E2 ramps up, and the peak E-field location migrates to the JTE-1's outer edge. Subsequently, simulations are performed to traverse a large design space of  $N_A$  and  $t_{\text{JTE}}$ . The  $t_{\text{JTE}}$ 's lower and upper limits to reach  $90\%$  of the optimal (highest)  $BV$  ( $BV_{\text{opt}}$ ) are identified for several  $N_A$  in the range of  $10^{17}$ - $10^{19} \text{ cm}^{-3}$ . Here the  $BV$  is extracted when the peak  $E_M$  at E1-E3 reaches a pre-

This is the author's peer reviewed, accepted manuscript. However, the online version of record will be different from this version once it has been copyedited and typeset.

PLEASE CITE THIS ARTICLE AS DOI: 10.1063/5.0142229

selected compliance of 4.2 MV/cm. While in theory this compliance selection can be arbitrary up to  $E_C$ , here the 4.2 MV/cm is based on experimental devices (to be illustrated later). As shown in Fig. 2(d), the  $t_{JTE}$  window for a 10%  $BV_{OPT}$  tolerance quickly drops as  $N_A$  increases, from 390 nm at  $2 \times 10^{17} \text{ cm}^{-3}$  to 29 nm at  $10^{18} \text{ cm}^{-3}$  and 0.9 nm at  $10^{19} \text{ cm}^{-3}$ . This suggests the low  $N_A$  is key to enabling a broad process latitude for  $t_{JTE}$  in experimental devices.

Simulations are also used to examine if the 1-D design by (1) indeed leads to the highest efficiency in the 2-D JTE structure. As shown in Fig. 2(e),  $\eta = 1$  and  $t_{JTE}^{opt}$  leads to  $BV_{OPT}$  when  $N_A \leq 6 \times 10^{17} \text{ cm}^{-3}$ ; however, at higher  $N_A$ , the  $t_{JTE}$  for  $BV_{OPT}$  is smaller than  $t_{JTE}^{opt}$ , reaching  $\sim 0.97 t_{JTE}^{opt}$  at  $10^{18} \text{ cm}^{-3}$  and  $0.84 t_{JTE}^{opt}$  at  $10^{19} \text{ cm}^{-3}$ . This is because, the 1-D model in (1) represents the optimal design for the bi-layer p<sup>+</sup>-NiO region and not necessarily for the JTE-1's outer extension. At higher  $N_A$ , the sharper peak E-field could emerge in the JTE-1 and JTE-2's outer edge region (i.e., E1 and E2), which has to be suppressed by a smaller  $t_{JTE}$ . This  $t_{JTE} < t_{JTE}^{opt}$  design actually compromises the JTE efficiency due to a smaller  $E_M$  in the bi-layer p<sup>+</sup>-NiO region according to (1). This trade-off further illustrates the importance of using low  $N_A$  to fulfill the full JTE capability. Fig. 2(e) also shows the  $\eta$  window for the 90%  $BV_{OPT}$ , revealing a generally narrower window for the excessive  $t_{JTE}$  than the insufficient  $t_{JTE}$ .

Finally, the impact of  $L_{JTE}$  is shown in Fig. 2(f). the peak E-field first reduces as  $L_{JTE}$  increases and then nearly saturates. An  $L_{JTE}$  range of 10~15  $\mu\text{m}$  can achieve a good trade-off between the JTE's efficiency and real estate. Note that, in the above design and optimization (e.g., eqn. (1)), the  $t_{GaO}$  and  $N_D$  of the Ga<sub>2</sub>O<sub>3</sub> drift region are not involved. Simulations confirms the independence of the JTE's efficiency on the Ga<sub>2</sub>O<sub>3</sub> drift region assuming that the identical  $E_M$  is realized at the junction.

To verify the JTE's physics, experimental p-n diodes are fabricated on two 2-inch Ga<sub>2</sub>O<sub>3</sub> wafers with an identical  $t_{GaO}$  of 10  $\mu\text{m}$  and different  $N_D$  of  $1.3 \times 10^{16} \text{ cm}^{-3}$  (wafer A) and  $8 \times 10^{15} \text{ cm}^{-3}$  (wafer B) grown by Novel Crystal Technology. The diameter of the anode main p-n junction (p<sup>+</sup>-NiO/Ga<sub>2</sub>O<sub>3</sub> area) is 100  $\mu\text{m}$ . These  $N_D$  are extracted by C-V measurements of the SBDs fabricated on two wafers. Fig. 3(a) shows the main process flow for NiO/Ga<sub>2</sub>O<sub>3</sub> p-n diodes. After the formation of backside cathode, two p<sup>+</sup>-NiO layers are deposited to the desirable  $t_{JTE}$  by the RF magnetron sputtering at room temperature using the NiO target. After forming JTE-1 and JTE-2, p-NiO layer is sputtered to form JTE-3, followed by a post-sputter annealing at 275 °C in N<sub>2</sub> to stabilize the  $N_A$  in NiO and improve the NiO/Ga<sub>2</sub>O<sub>3</sub> interface quality. The anode layer p<sup>+</sup>-NiO and anode contact are then formed, followed by a final annealing. Note that a bilayer resist<sup>35</sup> is used for NiO lift-off, and the undercut length of the bottom resist can be used to tune the NiO sidewall angle formed in the sputtering process (the longer the undercut, the more pronounced lateral deposition, and the smaller the sidewall angle). As shown in Fig. 1(c), a sidewall angle of  $\sim 13^\circ$  and  $\sim 80^\circ$  is formed for the JTE-1/2 and JTE-3, respectively.

The hole concentration in NiO is known to positively correlate to the oxygen partial pressure in sputtering,<sup>40</sup> and our recent works show such correlation also holds for  $N_A$ .<sup>26</sup> Hence, the p<sup>+</sup>-NiO is sputtered in the pure Ar atmosphere (60 sccm), while p-

NiO and  $p^+$ -NiO are sputtered in the Ar/O<sub>2</sub> mixture with an increased O<sub>2</sub> partial pressure (60/3 sccm and 40/20 sccm, respectively). Other sputtering conditions, including the NiO target (99.9% purity target from Kurt J. Lesker), pressure (3 mTorr), RF power (100 W), and temperature (25 °C), are identical for various NiO layers. The  $N_A$  in  $p^+$ -NiO at high E-field is key for the designs of  $BV$  and  $t_{JTE}$ , but its accurate characterization is difficult due to the possible field-dependent ionization. Note that  $N_A$  is expected to also differ significantly from the hole concentration. Here, instead of characterizing  $N_A$ , we employ a single-layer  $p^+$ -NiO JTE (i.e.,  $n=1$ ) to directly determine the optimal  $t_{JTE}$  in multi-layer JTEs.

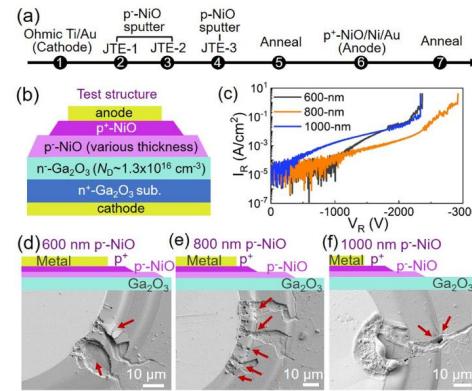

FIG. 3. (a) Main fabrication steps for the Ga<sub>2</sub>O<sub>3</sub> p-n diodes with the NiO JTE. (b) Schematic of the test device structure to determine the optimal p-NiO thickness experimentally. (c) Reverse I-V characteristics of the test devices with three p-NiO thicknesses, and (d) the SEM images of the breakdown spots at the edge of these three test devices. The red arrows suggest the breakdown locations.

Fig. 3(b) shows a Ga<sub>2</sub>O<sub>3</sub> p-n diode test structure with the blanket p-NiO under the anode, the termination of which is equivalently a single-layer p-NiO JTE. The  $BV$  of three such diodes with the p-NiO thickness of 0.6, 0.8 and 1 μm are shown in Fig. 3(c), with the SEM images of the breakdown spots shown in Fig. 3(d). Despite the large burning trace, deep holes usually correspond to the initial percolation paths and the breakdown location. The  $BV$  of the diode with 0.8 μm p-NiO is higher than the other two diodes. In addition, when the thickness increases to 1 μm, the breakdown location moves from the inner edge to the outermost edge, signifying the p-NiO starts to become partially depleted rather than fully depleted. These results suggest the optimal thickness of a single-layer p-NiO JTE to be ~0.8 μm. According to (1), the optimal  $t_{JTE}$  of each layer in a bi-layer p-NiO JTE ( $n=2$ ) is ~0.4 μm, which is used in experimental device fabrication. The thickness of p-NiO and  $p^+$ -NiO is not critical to the JTE functionality and is selected as 600 nm and 180 nm, respectively.

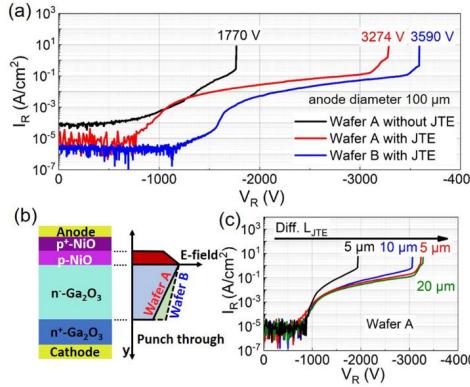

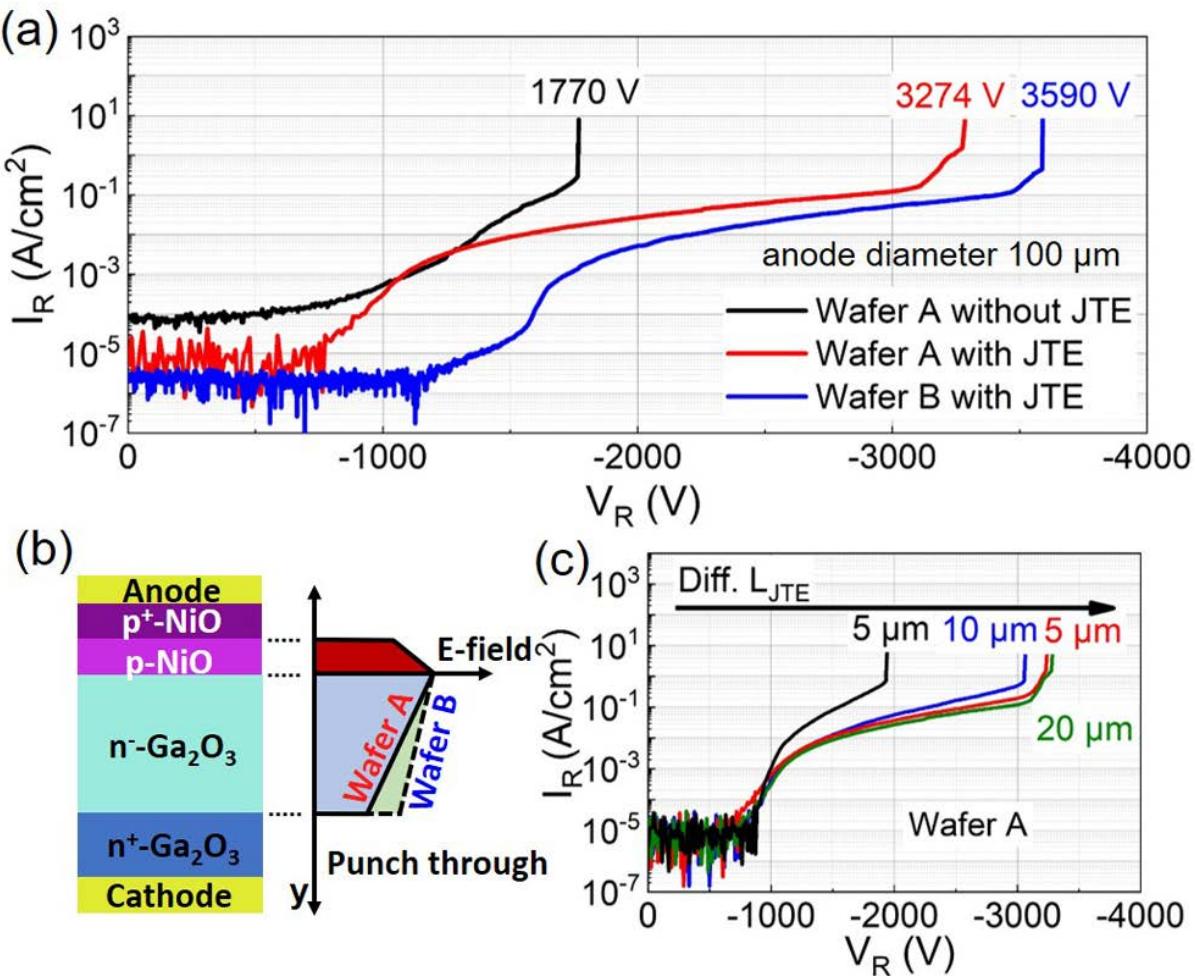

Fig. 4(a) shows the reverse I-V characteristics of the p-n diodes fabricated on the wafers A and B, revealing a  $BV$  of ~3.3 kV and ~3.6 kV, respectively. The  $BV$  is higher than the p-n diodes without any JTE [see Fig. 4(a)] and with a single-layer JTE [see Fig. 3(c)], verifying the superior efficiency of the multi-layer NiO JTE. To probe if the  $BV$  distinction on the wafers A and

This is the author's peer reviewed, accepted manuscript. However, the online version of record will be different from this version once it has been copyedited and typeset.

PLEASE CITE THIS ARTICLE AS DOI: 10.1063/5.0142229

$B$  is due to  $N_D$  or the JTE efficiency, the ideal parallel-plate junction E-field (i.e., the average  $E_M$ ) is calculated based on the punch-through E-field profile [see Fig. 4(b)]:

$$BV = E_M t_{Gao} - qN_D t_{Gao}^2 / (2\epsilon_N) \quad (2)$$

FIG. 4. (a) Reverse I-V characteristics of the Ga<sub>2</sub>O<sub>3</sub> p-n diodes with the optimal JTE fabricated on the wafers A and B as well as a diode without JTE on the wafer A. (b) Illustration of the E-field profile in the diodes on two wafers. (c) Reverse I-V characteristics of the diodes with different  $L_{JTE}$  of 5, 10, 15, and 20  $\mu\text{m}$ .

The average  $E_M$  calculated for diodes on two wafers is found to be both  $\sim 4.2$  MV/cm. This validates the independence of the JTE efficiency on the Ga<sub>2</sub>O<sub>3</sub> drift region. With this consistent  $E_M$  in Ga<sub>2</sub>O<sub>3</sub>, we estimate the  $N_A$  in p<sup>+</sup>-NiO to be  $\sim 3 \times 10^{17}$  cm<sup>-3</sup> based on (1). According to simulation results in Fig. 2(d), the  $t_{JTE}$  window for the 10%  $BV$  tolerance is predicted to be  $\sim 125$  nm at this  $N_A$ , being  $\sim 30\%$  of its optimal value. This validates the large process latitude of the proposed JTE implemented with a low  $N_A$ . In addition, the  $BV$  of the fabricated diodes with different  $L_{JTE}$  are also measured. As shown in Fig. 4(c),  $BV$  first increases with  $L_{JTE}$  and then saturates after  $L_{JTE}$  exceeds 10  $\mu\text{m}$ . This trend is consistent with the simulation results in Fig. 2(f).

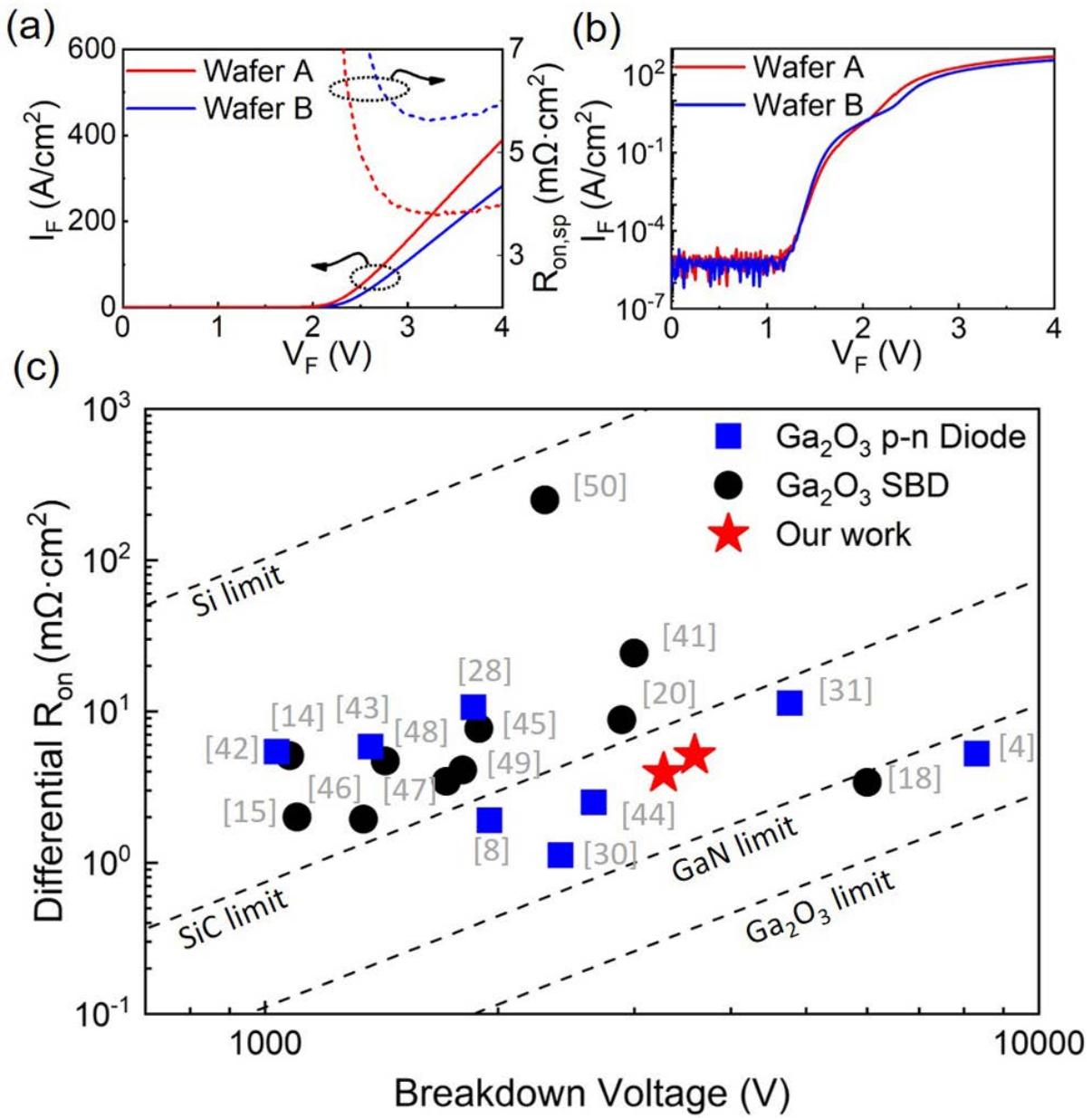

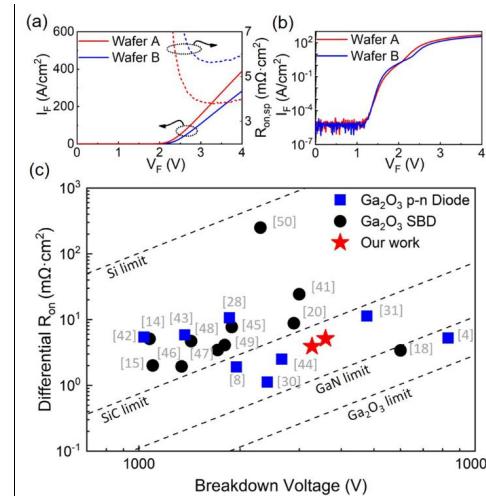

Finally, the JTE has minimal impact on device  $R_{ON,SP}$  and allows for the superior trade-off between  $BV$  and  $R_{ON,SP}$ . Fig. 5(a) and (b) show the forward I-V characteristics of the Ga<sub>2</sub>O<sub>3</sub> p-n diodes on the wafers A and B, revealing a differential  $R_{ON,SP}$  of 3.9 m $\Omega$ ·cm<sup>2</sup> and 5.7 m $\Omega$ ·cm<sup>2</sup>, respectively. The on/off ratio of both diodes is over 10<sup>9</sup>, and their turn-on voltage is identical. The  $R_{ON,SP}$  of both diodes are dominated by the drift region, and their difference is attributable to the  $N_D$  distinction. The p<sup>+</sup>-NiO anode layer contributes very little to  $R_{ON,SP}$ . This is confirmed by characterization of the reference SBDs with the same JTE and anode area, the  $R_{ON,SP}$  of which was found to be nearly identical to p-n diodes fabricated on the same wafer. Hence, this p<sup>+</sup>-NiO layer showcases a viable design to integrate the surface-deposited NiO JTE to the active device region for future diodes and transistors. Fig. 5(c) benchmarks the trade-off between  $BV$  and the differential  $R_{ON,SP}$  of our diodes on two wafers

This is the author's peer reviewed, accepted manuscript. However, the online version of record will be different from this version once it has been copyedited and typeset.

PLEASE CITE THIS ARTICLE AS DOI: 10.1063/5.0142229

and other  $\text{Ga}_2\text{O}_3$  diodes in the literature.<sup>4,8,14,15,18,20,28,30,31,41–50</sup> Our diodes show a power figure of merit ( $BV^2/R_{ON,SP}$ ) of 2.5~2.7 GW/cm<sup>2</sup> that has surpassed the 1-D SiC limit and is comparable to the state of the art of  $\text{Ga}_2\text{O}_3$  diodes.

FIG. 5. Forward I-V characteristic of  $\text{Ga}_2\text{O}_3$  diodes on the two wafers in (a) linear and (b) semi-log scale. (c) Differential  $R_{ON,SP}$  versus  $BV$  trade-off of  $\text{Ga}_2\text{O}_3$  p-n diodes and SBDs with  $BV > 1$  kV.

In summary, this work presents the physics and experimental demonstration of a near-ideal NiO JTE for  $\text{Ga}_2\text{O}_3$  devices. The JTE consists of multiple lowly-doped NiO layers deposited on the surface of  $\text{Ga}_2\text{O}_3$  drift region, the geometry of which enables a graded charge decrease away from the active region. The fabrication of this surface NiO JTE is implantation- and etch-free and holds broad process latitude. The functionality of this NiO JTE is drift region agnostic.  $BV$  over 3.3 kV and a parallel-plate junction E-field of 4.2 MV/cm are demonstrated in the diodes fabricated on two  $\text{Ga}_2\text{O}_3$  wafers. These results show the great promise of the NiO JTE as a flexible, effective building block for devices based on  $\text{Ga}_2\text{O}_3$  and other WBG/UWBG materials lacking high-quality, selective-area homojunctions.

#### ACKNOWLEDGMENTS

We acknowledge the collaboration with Silvaco on device simulation. This work was supported in part by National Science Foundation under Grants ECCS-2100504 and ECCS-2230412 and in part by the Center for Power Electronics Systems High Density Integration Industry Consortium.

#### Author Declarations

This is the author's peer reviewed, accepted manuscript. However, the online version of record will be different from this version once it has been copyedited and typeset.

PLEASE CITE THIS ARTICLE AS DOI: 10.1063/5.0142229

The authors have no conflicts to disclose.

#### Author Contributions

Y.Z., M.X. and B.W. conceived the device concept and planned the study. B.W. and M.X. led the device fabrication, data collection and analysis, and device simulations. Q.Y. and Y.M. contributed to device fabrication. J.S. and M.T. contributed to the data analysis. M.P. and Y.W. contributed to the simulation. K.S. grew the  $\text{Ga}_2\text{O}_3$  wafers. Y.Z. and M.X. wrote the manuscript. All the authors discussed the results and reviewed the manuscript.

#### Data Availability

The data that support the findings of this study are available within the article.

#### REFERENCES

- <sup>1</sup> Y. Zhang, F. Udrea, and H. Wang, *Nat. Electron.* **5**, 723 (2022).

- <sup>2</sup> S.J. Pearton, J. Yang, P.H. Cary IV, F. Ren, J. Kim, M.J. Tadjer, and M.A. Mastro, *Appl. Phys. Rev.* **5**, 011301 (2018).

- <sup>3</sup> A.J. Green, J. Speck, G. Xing, P. Moens, F. Allerstam, K. Gummelius, T. Neyer, A. Arias-Purdue, V. Mehrotra, A. Kuramata, K. Sasaki, S. Watanabe, K. Koshi, J. Blevins, O. Bierwagen, S. Krishnamoorthy, K. Leedy, A.R. Arehart, A.T. Neal, S. Mou, S.A. Ringel, A. Kumar, A. Sharma, K. Ghosh, U. Singisetty, W. Li, K. Chabak, K. Liddy, A. Islam, S. Rajan, S. Graham, S. Choi, Z. Cheng, and M. Higashiwaki, *APL Mater.* **10**, 029201 (2022).

- <sup>4</sup> J. Zhang, P. Dong, K. Dang, Y. Zhang, Q. Yan, H. Xiang, J. Su, Z. Liu, M. Si, and J. Gao, *Nat. Commun.* **13**, 1 (2022).

- <sup>5</sup> R. Sharma, M. Xian, C. Fares, M.E. Law, M. Tadjer, K.D. Hobart, F. Ren, and S.J. Pearton, *J. Vac. Sci. Technol. A* **39**, 013406 (2021).

- <sup>6</sup> M. Xiao, B. Wang, J. Liu, R. Zhang, Z. Zhang, C. Ding, S. Lu, K. Sasaki, G.-Q. Lu, C. Buttay, and Y. Zhang, *IEEE Trans. Power Electron.* **36**, 8565 (2021).

- <sup>7</sup> B. Wang, M. Xiao, J. Knoll, C. Buttay, K. Sasaki, G.-Q. Lu, C. Damarino, and Y. Zhang, *IEEE Electron Device Lett.* **42**, 1132 (2021).

- <sup>8</sup> F. Zhou, H. Gong, W. Xu, X. Yu, Y. Xu, Y. Yang, F. Ren, S. Gu, Y. Zheng, R. Zhang, J. Ye, and H. Lu, *IEEE Trans. Power Electron.* **37**, 1223 (2021).

- <sup>9</sup> H. Gong, F. Zhou, X. Yu, W. Xu, F.-F. Ren, S. Gu, H. Lu, J. Ye, and R. Zhang, *IEEE Electron Device Lett.* **43**, 773 (2022).

- <sup>10</sup> M. Xiao, Y. Ma, K. Liu, K. Cheng, and Y. Zhang, *IEEE Electron Device Lett.* **42**, 808 (2021).

- <sup>11</sup> A.V. Bolotnikov, P.G. Muzykov, Q. Zhang, A.K. Agarwal, and T.S. Sudarshan, *IEEE Trans. Electron Devices* **57**, 1930 (2010).

- <sup>12</sup> J. Liu, M. Xiao, R. Zhang, S. Pidaparthi, C. Drowley, L. Baubut, A. Edwards, H. Cui, C. Coles, and Y. Zhang, *IEEE Electron Device Lett.* **41**, 1328 (2020).

- <sup>13</sup> J.A. Spencer, A.L. Mock, A.G. Jacobs, M. Schubert, Y. Zhang, and M.J. Tadjer, *Appl. Phys. Rev.* **9**, 011315 (2022).

- <sup>14</sup> K. Konishi, K. Goto, H. Murakami, Y. Kumagai, A. Kuramata, S. Yamakoshi, and M. Higashiwaki, *Appl. Phys. Lett.* **110**, 103506 (2017).

- <sup>15</sup> N. Allen, M. Xiao, X. Yan, K. Sasaki, M.J. Tadjer, J. Ma, R. Zhang, H. Wang, and Y. Zhang, *IEEE Electron Device Lett.* **40**, 1399 (2019).

- <sup>16</sup> S. Roy, A. Bhattacharyya, P. Ranga, H. Splawn, J. Leach, and S. Krishnamoorthy, *IEEE Electron Device Lett.* **42**, 1140 (2021).

- <sup>17</sup> C.-H. Lin, Y. Yuda, M.H. Wong, M. Sato, N. Takekawa, K. Konishi, T. Watahiki, M. Yamamuka, H. Murakami, Y. Kumagai, and M. Higashiwaki, *IEEE Electron Device Lett.* **40**, 1487 (2019).

- <sup>18</sup> P. Dong, J. Zhang, Q. Yan, Z. Liu, P. Ma, H. Zhou, and Y. Hao, *IEEE Electron Device Lett.* **43**, 765 (2022).

- <sup>19</sup> S. Dhara, N.K. Kalarickal, A. Dheenan, C. Joishi, and S. Rajan, *Appl. Phys. Lett.* **121**, 203501 (2022).

- <sup>20</sup> W. Li, K. Nomoto, Z. Hu, D. Jena, and H.G. Xing, *IEEE Electron Device Lett.* **41**, 107 (2019).

- <sup>21</sup> D. C. Sheridan, G. Niu, J. N. Merrett, J. D. Cressler, J. B. Dufrene, J. B. Casady, and I. Sankin, in 2001 13<sup>th</sup> International Symposium on Power Semiconductor Devices & IC's (ISPSD), pp. 25–28.

This is the author's peer reviewed, accepted manuscript. However, the online version of record will be different from this version once it has been copyedited and typeset.

PLEASE CITE THIS ARTICLE AS DOI: 10.1063/5.0142229

<sup>22</sup> J. Liu, R. Zhang, M. Xiao, S. Pidaparthi, H. Cui, A. Edwards, L. Baubut, C. Drowley, and Y. Zhang, IEEE Trans. Power Electron. **36**, 10959 (2021).

<sup>23</sup> N. Kaneko, O. Machida, M. Yanagihara, S. Iwakami, R. Baba, H. Goto, and A. Iwabuchi, in 2009 21<sup>st</sup> International Symposium on Power Semiconductor Devices & IC's (ISPSD), pp. 191-194.

<sup>24</sup> L. Li, X. Wang, Y. Liu, and J.-P. Ao, J. Vac. Sci. Technol. A **34**, 02D104 (2016).

<sup>25</sup> Y. Ma, M. Xiao, Z. Du, X. Yan, K. Cheng, M. Clavel, M.K. Hudait, I. Kravchenko, H. Wang, and Y. Zhang, Appl. Phys. Lett. **117**, 143506 (2020).

<sup>26</sup> M. Xiao, Y. Ma, Z. Du, Y. Qin, K. Liu, K. Cheng, F. Udrea, A. Xie, E. Beam, B. Wang, J. Spencer, M. Tadjer, T. Anderson, H. Wang, and Y. Zhang, in 2022 IEEE International Electron Devices Meeting (IEDM) (2022), p. 35.6.1-35.6.4.

<sup>27</sup> Y. Kokubun, S. Kubo, and S. Nakagomi, Appl. Phys. Express **9**, 091101 (2016).

<sup>28</sup> H. Gong, X. Chen, Y. Xu, F.-F. Ren, S. Gu, and J. Ye, Appl. Phys. Lett. **117**, 022104 (2020).

<sup>29</sup> X. Lu, X. Zhou, H. Jiang, K.W. Ng, Z. Chen, Y. Pei, K.M. Lau, and G. Wang, IEEE Electron Device Lett. **41**, 449 (2020).

<sup>30</sup> Y. gang Wang, H. Gong, Y. Lv, X. Fu, S. Dun, T. Han, H. Liu, X. Zhou, S. Liang, and J. Ye, IEEE Trans. Power Electron. (2021).

<sup>31</sup> J.-S. Li, C.-C. Chiang, X. Xia, T.J. Yoo, F. Ren, H. Kim, and S. Pearton, Appl. Phys. Lett. **121**, 042105 (2022).

<sup>32</sup> W. Sung, E. Van Brunt, B.J. Baliga, and A.Q. Huang, IEEE Electron Device Lett. **32**, 880 (2011).

<sup>33</sup> D.C. Sheridan, G. Niu, and J.D. Cressler, Solid State Electron. **45**, 1659 (2001).

<sup>34</sup> G. Feng, J. Suda, and T. Kimoto, IEEE Trans Electron Devices **59**, 414 (2012).

<sup>35</sup> R. Ghandi, B. Buono, M. Domeij, G. Malm, C.-M. Zetterling, and M. Ostling, IEEE Electron Device Lett. **30**, 1170 (2009).

<sup>36</sup> W. Li, D. Saraswat, Y. Long, K. Nomoto, D. Jena, and H.G. Xing, Appl. Phys. Lett. **116**, 192101 (2020).

<sup>37</sup> W. Li, K. Nomoto, D. Jena, and H.G. Xing, Appl. Phys. Lett. **117**, 222104 (2020).

<sup>38</sup> B. Wang, M. Xiao, J. Spencer, Y. Qin, K. Sasaki, M.J. Tadjer, and Y. Zhang, IEEE Electron Device Lett. **44**, 221 (2023).

<sup>39</sup> M. Xiao, Y. Ma, K. Cheng, K. Liu, A. Xie, E. Beam, Y. Cao, and Y. Zhang, IEEE Electron Device Lett. **41**, 1177 (2020).

<sup>40</sup> S. Nandy, B. Saha, M.K. Mitra, and K.K. Chattopadhyay, J. Mater. Sci. **42**, 5766 (2007).

<sup>41</sup> Z. Hu, H. Zhou, Q. Feng, J. Zhang, C. Zhang, K. Dang, Y. Cai, Z. Feng, Y. Gao, and X. Kang, IEEE Electron Device Lett. **39**, 1564 (2018).

<sup>42</sup> H. Gong, Z. Wang, X. Yu, F. Ren, Y. Yang, Y. Lv, Z. Feng, S. Gu, R. Zhang, and Y. Zheng, IEEE J. Electron Devices Soc. **9**, 1166 (2021).

<sup>43</sup> H. Gong, F. Zhou, W. Xu, X. Yu, Y. Xu, Y. Yang, F. Ren, S. Gu, Y. Zheng, R. Zhang, H. Lu, and J. Ye, IEEE Trans. Power Electron. **36**, 12213 (2021).

<sup>44</sup> W. Hao, Q. He, X. Zhou, X. Zhao, G. Xu, and S. Long, in 2022 IEEE 34th International Symposium on Power Semiconductor Devices and ICs (ISPSD), (2022), pp. 105-108.

<sup>45</sup> H. Gong, X. Yu, Y. Xu, X. Chen, Y. Kuang, Y. Lv, Y. Yang, F. Ren, Z. Feng, S. Gu, Y. Zheng, R. Zhang, and J. Ye, Appl. Phys. Lett. **118**, 202102 (2021).

<sup>46</sup> Q. Yan, H. Gong, J. Zhang, J. Ye, H. Zhou, Z. Liu, S. Xu, C. Wang, Z. Hu, and Q. Feng, Appl. Phys. Lett. **118**, 122102 (2021).

<sup>47</sup> Y. Lv, Y. Wang, X. Fu, S. Dun, Z. Sun, H. Liu, X. Zhou, X. Song, K. Dang, and S. Liang, IEEE Trans. Power Electron. **36**, 6179 (2020).

<sup>48</sup> C.-H. Lin, Y. Yuda, M.H. Wong, M. Sato, N. Takekawa, K. Konishi, T. Watahiki, M. Yamamuka, H. Murakami, and Y. Kumagai, IEEE Electron Device Lett. **40**, 1487 (2019).

<sup>49</sup> Q. He, X. Zhou, Q. Li, W. Hao, Q. Liu, Z. Han, K. Zhou, C. Chen, J. Peng, and G. Xu, IEEE Electron Device Lett. **43**, 1933 (2022).

<sup>50</sup> J. Yang, F. Ren, M. Tadjer, S. Pearton, and A. Kuramata, ECS J Solid State Sci Technol **7**, Q92 (2018).

This is the author's peer reviewed, accepted manuscript. However, the online version of record will be different from this version once it has been copyedited and typeset.

PLEASE CITE THIS ARTICLE AS DOI: 10.1063/5.0142229

This is the author's peer reviewed, accepted manuscript. However, the online version of record will be different from this version once it has been copyedited and typeset.

PLEASE CITE THIS ARTICLE AS DOI: 10.1063/5.0142229

This is the author's peer reviewed, accepted manuscript. However, the online version of record will be different from this version once it has been copyedited and typeset.

PLEASE CITE THIS ARTICLE AS DOI: 10.1063/5.0142229

This is the author's peer reviewed, accepted manuscript. However, the online version of record will be different from this version once it has been copyedited and typeset.

PLEASE CITE THIS ARTICLE AS DOI: 10.1063/5.0142229

This is the author's peer reviewed, accepted manuscript. However, the online version of record will be different from this version once it has been copyedited and typeset.

PLEASE CITE THIS ARTICLE AS DOI: 10.1063/5.0142229