# Methodology for Analyzing Coupling Mechanisms in RFI Problems Based on PEEC

Xu Wang , Student Member, IEEE, Anfeng Huang, Member, IEEE, Wei Zhang , Reza Yazdani, DongHyun Kim, Member, IEEE, Takashi Enomoto, Taketoshi Sekine, Kenji Araki, Senior Member, IEEE, Jun Fan, Fellow, IEEE, and Chulsoon Hwang, Senior Member, IEEE

Abstract—In this article, a method for analyzing coupling mechanisms in radio frequency interference (RFI) problems is proposed. The partial element equivalent circuit (PEEC) method is first used to derive the retarded inductances and capacitances between different mesh cells. With the introduction of a novel partitioning algorithm, the capacitive coupling and inductive coupling between arbitrary layout parts can be quantified based on the magnitude of the displacement current and induced voltage drop. The accuracy of the PEEC models is validated by comparison with different commercial tools. The proposed coupling mechanism analysis flow provides a useful prelayout tool for RFI risk analysis.

Index Terms—Coupling mechanisms, partial element equivalent circuit (PEEC), prelayout, radio frequency interference (RFI).

## I. INTRODUCTION

The coupling mechanism analysis is an important subject in the electromagnetic compatibility research community. As the integration density in electronic devices increases, near-field coupling between different components becomes more severe. Unintentional coupling significantly degrades the system performance, as observed in receiver desensitization due to near-field coupling between digital circuits and radio frequency antennas [1], and noise picked up by high-speed interconnects from voltage regulator modules [2].

The partial element equivalent circuit (PEEC) method is a circuit-oriented full-wave algorithm based on the mixed potential integral equation (MPIE) formulation [3], which converts a field problem into a circuit problem. PEEC method has been widely used for different applications, such as parasitic extraction, conduction emission, electromagnetic interference (EMI), and electrostatic discharge (ESD) modeling. Typical

Manuscript received 24 August 2022; revised 27 November 2022 and 22 February 2023; accepted 3 March 2023. Date of publication 18 April 2023; date of current version 13 June 2023. This work was supported by the National Science Foundation nder Grant IIP-1916535. (Corresponding author: Chulsoon Hwang.)

Xu Wang, Anfeng Huang, Wei Zhang, Reza Yazdani, DongHyun Kim, Jun Fan, and Chulsoon Hwang are with the EMC Laboratory, Missouri University of Science and Technology, Rolla, MO 65409 USA (e-mail: xw7dh@mst.edu; ah4d8@umsystem.edu; wznkm@umsystem.edu; ry2kw@um.edu; dkim@mst.edu; jfan@mst.edu; hwangc@mst.edu).

Takashi Enomoto, Taketoshi Sekine, and Kenji Araki are with the Sony Global Manufacturing Operations Corporation, Tokyo 108-0075, Japan (e-mail: Takashi.Enomoto@sony.com; taketoshi.sekine@sony.com; Kenji.Araki@sony.com).

Color versions of one or more figures in this article are available at https://doi.org/10.1109/TEMC.2023.3263968.

Digital Object Identifier 10.1109/TEMC.2023.3263968

TABLE I

SUMMARY OF TYPICAL APPLICATION OF PEEC METHOD

| Topic                                 | Literature          |

|---------------------------------------|---------------------|

| High-speed interconnect modeling      | [12] [13] [14]      |

| Conduction emission modeling          | [15]                |

| Parasitic extraction in power devices | [9] [16] [17]       |

| ESD modeling                          | [18]                |

| MOR techniques                        | [5] [6] [7] [8]     |

| Composite object modeling             | [19] [20] [21] [22] |

| Radiation resistance model            | [23] [24]           |

|                                       |                     |

applications of PEEC method are summarized in Table I. While the PEEC approach provides clear physical insight into the coupling analysis, it suffers from an excessive number of generated circuits, which grows exponentially with the number of mesh cells.

Model order reduction (MOR) method are commonly used to reduce the number of circuits required for simulation, such as the Lanczos and Arnoldi algorithms, circuit transformation approach, direct mesh-based MOR, fast-multipole method, physic-based macromodel, and so on [4], [5], [6], [7], [8], [9]. Although the number of circuits has been sufficiently reduced, there are up to thousands of circuit elements between geometric partitions after the reduction [6]. For layout engineers, component placement is commonly used in the predesign stage to mitigate the RFI problem [10], [11]. For example, a 10-dB RFI reduction is achieved by rotating the Wi-Fi antenna. Therefore, it is desirable to develop a method to quantify the strength of coupling between distributive geometries to guide the layout modifications.

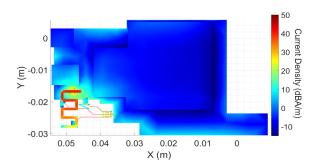

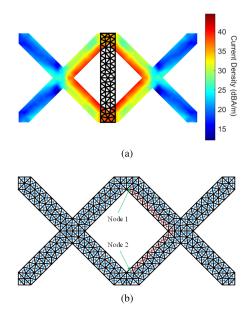

To characterize the capacitive coupling and inductive coupling between the distributive geometries, a method is presented in [15] by extracting the inductances and capacitances between the surface partitions (generated using Voronoi's algorithm). However, the RFI problem studied in this article poses several challenges to traditional partitioning methods: 1) The concept of capacitance between the antenna partition and victim trace partition is generally not valid. To extract a unique capacitance between objects, the potential of each partition should be constant [9]. Fig. 1 shows the potential distribution of an antenna element simulated with our in-house PEEC solver, which indicates the difficulty of representing capacitive coupling to the antenna partition with a single capacitance. 2) In the RFI problem, the currents excited by the antenna structure, as shown in Fig. 2, may spread over the ground plane, which makes it difficult to identify

0018-9375  $\odot$  2023 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See https://www.ieee.org/publications/rights/index.html for more information.

Fig. 1. Potential distribution of an antenna element.

Fig. 2. Conduction current distribution.

current paths and extract partition-based inductances [9], [15]. To the best of our knowledge, a partitioning-based coupling mechanism analysis framework for the RFI problem has not been reported.

The purpose of this article is threefold.

- 1) Verify the accuracy of the retarded partial element equivalent circuit (rPEEC) model for RFI problem modeling.

- 2) Propose a mesh-dependent and partition-based coupling mechanism analysis framework based on the PEEC method, which allows the quantification of the capacitive coupling and inductive coupling between distributive geometries. (After the simulation, a partition-based analysis is used to obtain the displacement currents and inductive voltage drops for the victim partitions rather than extracting inductances and capacitances between surface partitions, which is generally invalid for RFI problems.)

- Discuss how the proposed method may be used to efficiently examine the different RFI reduction strategies, such as adding filtering circuits and making layout changes.

The rest of this article is organized as follows. Section II introduces the theoretical background, including the PEEC formulation, heatmap analysis, partitioning algorithm, and coupling analysis methodology. Section III verifies the proposed method with an RFI-induced buzz noise problem in a camera module [25], [26]. Section IV presents the applications of the proposed method, including adding a filtering circuit and modifying the layouts. Section V outlines this work's limitations and areas of improvement. Finally, Section VI concludes this article.

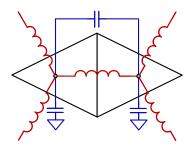

Fig. 3. Equivalent circuits for triangular cells.

#### II. THEORETICAL BACKGROUND

#### A. PEEC Formulation

In this article, planar triangular cells are used to discretize the simulation model because of its accuracy and flexibility to model arbitrary geometric surfaces [27], [28], [29], [30]. Similar to [29] and [30], the Rao–Wilton–Glisson basis function and the pulse basis function are used to expand the surface current density and surface charge density, respectively. The equivalent circuit model for the triangular cell is described in Fig. 3, where capacitance is defined between two triangular cells (nodal-wise quantity), and inductance is defined between the currents that flow across the common edges of the triangle pairs (branchwise quantity).

The discretized MPIE equation has the standard form of the modified nodal analysis (MNA)

$$\begin{bmatrix} j\omega \boldsymbol{C} & \boldsymbol{\Lambda}^T \\ -\boldsymbol{\Lambda} & j\omega \boldsymbol{L} \end{bmatrix} \begin{bmatrix} \boldsymbol{\Phi} \\ \mathbf{I} \end{bmatrix} = \begin{bmatrix} \boldsymbol{0} \\ \boldsymbol{V}_{\boldsymbol{e}} \end{bmatrix}$$

(1)

where C is the nodalwise (cell-) short-circuit capacitance matrix, L is the branch-wise (edgewise) inductance matrix,  $\Phi$  is the unknown potential vector, I is the unknown current vector,  $V_e$  is the external voltage source vector, and  $\Lambda$  is the connectivity matrix, which connects the edgewise and cellwise quantities and is defined as

$$\Lambda_{nm} = \begin{cases}

1 & \text{if cell m is the positive side of nth edge} \\

-1 & \text{if cell m is the negative side of nth edge} \\

0 & \text{otherwise.}

\end{cases}$$

The calculation of the PEEC model for the triangular cell can be found in [30]. The full-wave Green's function, rather than its static counterparts, is adopted here to account for the retardation effects

$$G(\mathbf{r}, \mathbf{r}') = \frac{e^{-jkR}}{4\pi R} \tag{3}$$

where  $R = |\mathbf{r} - \mathbf{r}'|$  is the distance between the source point  $(\mathbf{r})$  and the field point  $(\mathbf{r}')$ . Various equivalent circuit models are available for the retarded PEEC model in the frequency domain to facilitate Simulation Program with Integrated Circuit Emphasis (SPICE) simulations [3], e.g., the current-source-based model and the potential-based model for capacitance. Here, we use the complex capacitance and complex inductance definitions to represent the retardation effect for the capacitive and inductive

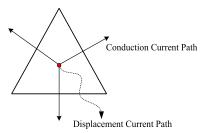

Fig. 4. Displacement current.

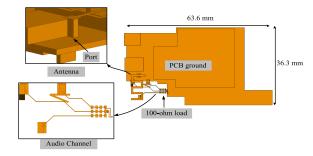

Fig. 5. Simulation model for the RFI problem. The audio traces capture the radio-frequency signal from the Wi-Fi antenna.

coupling [29]. The MNA equation is solved with a built-in direct matrix solver in MATLAB rather than the SPICE engines.

## B. Heatmap Analysis

In the proposed coupling analysis framework, the capacitive and inductive coupling hotspots are found using the displacement heatmap and potential heatmap, respectively. In our rPEEC model, the triangular cells are circuit nodes that absorb the conduction current and displacement current, as shown in Fig. 4. The displacement current for each node (triangular cell) can be determined from the branchwise conduction current vector

$$i_{\rm dis} = -\mathbf{\Lambda}^T \mathbf{I} \tag{4}$$

where  $i_{\rm dis}$  is the nodalwise displacement current vector.

The potential map is the potential distribution on the entire geometry. The hotspot of the capacitive coupling is shown by the displacement current map, and the inductive coupling is shown by the voltage drop in the potential map.

## C. Partitioning Concept

This section introduces a partitioning strategy, which is the key procedure in the proposed coupling mechanism analysis methodology. The mesh of the aggressor and victim geometry parts can be divided according to the layout area of interest after the simulation, in contrast to earlier research that divided the geometry according to the conduction current path [9]. In addition, we do not have to limit our partitions to be electrically small, e.g., smaller than one-tenth of wavelength.

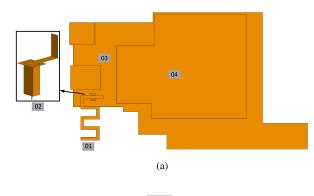

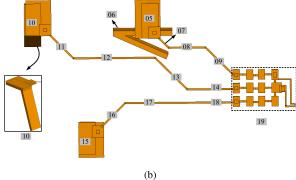

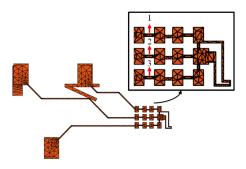

The simulation model studied in this article is shown in Fig. 5. For simplicity's sake, the Wi-Fi antenna, print circuit board (PCB) structure, and audio traces are modeled with zero-thickness metal patches with triangular meshes. For closely

Fig. 7. Partition example.

Fig. 6. Partition definitions of the simulation model. (a) Aggressor, partition 1 to 4. (b) Victim, partition 5 to 19.

placed components and conductors, the thickness of the conductor needs to be considered due to the proximity effect. There are three audio lanes in the model: one ground trace and two signal traces. The Wi-Fi antenna is placed above the traces. The antenna structure and PCB grounds are the aggressors, and the audio channels are the victims.

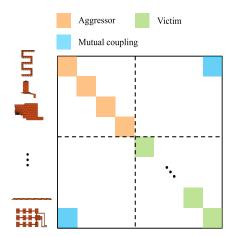

The partition definitions for the aggressor and victim are shown in Fig. 6(a) and 6(b). The mesh of the aggressor part is divided into four partitions: a horizontal patch, a vertical connection, ground area 1, and ground area 2. Meanwhile, the mesh of the victim structure is divided into 15 partitions, including trace sections and pins.

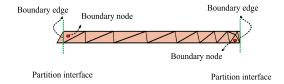

To further analyze the induced voltage drop over a victim partition or the displacement current between partitions, the circuit nodes and branches within the partitions must be determined. This step is performed by specifying a bounding box and then querying the triangles within the bounding box. The current branches and circuit nodes that belong to a partition can be determined using the point-in-polygon algorithm [31]. The interfaces between different partitions are the triangle edges shared by the partitions so that the current entering and leaving the partitions can be recorded. Triangular cells that attach to

Fig. 8. Relationship between geometry partitions and matrix blocks of the partial elements. Of note, all matrix blocks are computed and considered for simulation while only parts of them are shown here.

the interface can be used to record the potential. An example is shown in Fig. 7, which is part of the audio trace. A conceptual depiction of the relationship between the geometrical partitions and the circuit matrix is shown in Fig. 8.

## D. Capacitive Coupling Analysis

The displacement current between two partitions is evaluated by utilizing the submatrix of the capacitance matrix and the potential vector. Let us consider two partitions, K and S, that consist of M and N triangles, respectively.

The two-terminal capacitance between cells m and n can be derived from the short-circuit capacitance matrix as [3]

$$c_{mn} = -C_{mn} \tag{5}$$

where  $C_{mn}$  is the short-circuit capacitance between the mth and the nth cells. The two-terminal capacitance between cell m and the ground node is

$$c_{m0} = C_{mm} - \sum_{n=1}^{P} C_{mp} \tag{6}$$

where P is the cell number for the entire structure.

The displacement current between cell m and cell n flowing through the two-terminal capacitor can be calculated as

$$i_{\text{dis},mn} = j\omega c_{mn}(\phi_m - \phi_n). \tag{7}$$

The total displacement current between two partitions is a linear superposition of the displacements between cells, which is

$$i_{\text{dis},KS} = \sum_{m=1}^{M} \sum_{n=1}^{N} i_{\text{dis}}$$

(8)

# E. Inductive Coupling Analysis

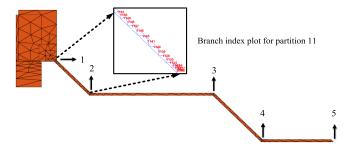

The inductive coupling strength is quantified by the induced voltage drop on the victim partition (between the boundary nodes). An appropriate and effective current path must be established before the inductive coupling can be examined. A flex

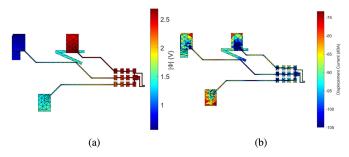

Fig. 9. (a) Current distribution of the meshed ground plane. The black triangles indicate the triangular cells on the trace. (b) Effective current path on a mesh partition (red edges). The blue edges represent the edges of the graph.

PCB, as shown in Fig. 9, is used as an example to demonstrate the inductive voltage drop calculation. When the trace is referenced to a meshed ground plane, the current on the meshed ground plane is concentrated at the edges due to the proximity effect between the trace and ground [see Fig. 9(a)]. To find the critical current path between the predefined boundary nodes, the circuit topology for a mesh partition can be converted to an equivalent network graph consisting of edges and nodes, as shown in Fig. 9(b). The weight of the edge is inversely proportional to the magnitude of the branch current

$$w_n = \frac{1}{|I_n|} \tag{9}$$

where  $w_n$  denotes the weight of the nth edge, and  $I_n$  denotes the nth branch current. The weights can be used as the distances along the edges in the graph, and then the dominant conduction current path can be determined using the shortest path algorithm [32].

Let us consider an aggressor partition S with N branches and a victim partition K with M branches on its effective current path. The induced voltage on the branch m caused by partition S can be calculated by

$$V_{mS} = \sum_{n=1}^{N} j\omega L_{mn} i_n \tag{10}$$

where n is the branch index in partition S,  $i_n$  is the nth branch current, and  $L_{mn}$  is the mutual inductance between branches m and n.

Then, the induced voltage over partition K (on the effective current path) is

$$V_{KS} = \sum_{m=1}^{M} V_m. {11}$$

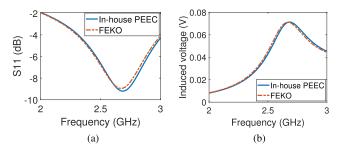

Fig. 10. Comparison of the rPEEC model and full-wave simulation. (a) S11. (b) Noise voltage.

Fig. 11. Heatmaps of the victim partitions. (a) Potential. (b) Displacement current.

Note that all circuit branches within the aggressor partition are used, whereas only the branches along the effective current path are used for the victim partition. This approach differs from the capacitive coupling analysis method, in which all cells are used for both the aggressor and the victim partition.

# III. VALIDATION

The antenna-to-audio channel coupling problem is simulated from 2 to 3 GHz. A comparison of the return loss and the induced voltage at the load, simulated with the commercial software FEKO [33] and the in-house PEEC algorithm, is shown in Fig. 10(a) and 10(b), respectively. Good correlation is achieved, indicating the accuracy of the rPEEC model. The coupling mechanism at 2.65 GHz is analyzed in detail later, where the audio traces can receive the maximum noise.

Fig. 11(a) and 11(b) shows the potential heatmap and displacement current heatmap for the victim structure. There is a significant potential change along the trace sections, whereas the potential on the pin structure remains constant, indicating that the inductive coupling occurs mainly on the trace. In contrast, the displacement current heatmap shows that both the jack pins and the trace segment near the antenna draw significant displacement currents from the other geometries.

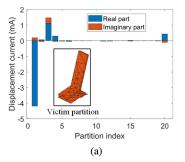

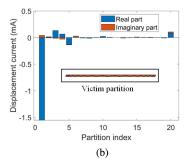

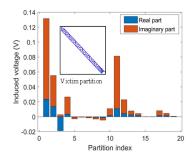

To further quantify the coupling strength, a partition-to-partition capacitive and inductive coupling analysis was performed for the second lane of audio structures. The capacitive coupling to partition 10 (the pin at the end of the second lane) and partition 12 (part of the second lane), which are the capacitive coupling hotspots on the second lane, is shown in Fig. 12. Histograms of the real and imaginary parts of the displacement currents between the partitions allow for the identification and quantification of the two main capacitive coupling paths

Fig. 12. Displacement current to victim partitions. (a) Partition 10. (b) Partition 12.

TABLE II

DISPLACEMENT CURRENT BETWEEN PARTITIONS

|              | 10    | 11    | 12    | 13    | 14    |

|--------------|-------|-------|-------|-------|-------|

| Partition No | (mA)  | (mA)  | (mA)  | (mA)  | (mA)  |

| 1            | 4.184 | 0.783 | 1.558 | 0.275 | 0.146 |

| 2            | 0.082 | 0.009 | 0.017 | 0.004 | 0.003 |

| 3            | 1.174 | 0.052 | 0.134 | 0.128 | 0.197 |

| 4            | 0.304 | 0.015 | 0.072 | 0.103 | 0.127 |

| 5            | 0.033 | 0.007 | 0.134 | 0.044 | 0.005 |

| 6            | 0.045 | 0.004 | 0.020 | 0.034 | 0.021 |

| 7            | 0.001 | 0.000 | 0.010 | 0.013 | 0.001 |

| 8            | 0.003 | 0.000 | 0.013 | 0.034 | 0.009 |

| 9            | 0.003 | 0.000 | 0.004 | 0.012 | 0.017 |

| 10           | \     | 0.024 | 0.004 | 0.004 | 0.003 |

| 11           | 0.029 | \     | 0.006 | 0.000 | 0.000 |

| 12           | 0.024 | 0.006 | \     | 0.009 | 0.003 |

| 13           | 0.004 | 0.000 | 0.009 | \     | 0.010 |

| 14           | 0.003 | 0.000 | 0.003 | 0.009 | \     |

| 15           | 0.029 | 0.002 | 0.008 | 0.006 | 0.006 |

| 16           | 0.004 | 0.000 | 0.003 | 0.003 | 0.002 |

| 17           | 0.007 | 0.001 | 0.005 | 0.013 | 0.012 |

| 18           | 0.004 | 0.000 | 0.002 | 0.003 | 0.015 |

| 19           | 0.015 | 0.001 | 0.009 | 0.016 | 0.030 |

| GND          | 0.446 | 0.029 | 0.087 | 0.093 | 0.118 |

(antenna patch and ground region 1). Table II summarizes the magnitude of the displacement current absorbed by all the victim partitions of the second audio lane.

In addition, the inductive coupling for a section of the second audio lane is evaluated. Fig. 13 shows the inductive voltage drop on the victim (partition 11) brought by all partitions. The dominant inductive coupling path includes partition 1 (horizontal patch of the antenna), 2 (vertical connect of the antenna), 11 (victim trace section itself), and 12 (nearby trace section). It is worth noting that the displacement current between partition 2 (the vertical connection between the antenna and ground plane) and the victim partitions are close to zero, but there is significant inductive coupling between these partitions.

Fig. 13. Inductive voltage drop on partition 11.

Fig. 15. Inductance extraction with the postprocessing procedure.

Fig. 16. Filter circuit is placed between pads. A total of three cases are investigated.

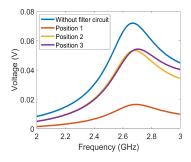

Fig. 17. Received noise voltage with filter circuits at different locations.

## TABLE III CONDUCTION CURRENT

| Local branch index | 1     | 2     | 3     | 4     | 5     |

|--------------------|-------|-------|-------|-------|-------|

| Current (mA)       | 2.484 | 3.155 | 4.552 | 4.585 | 4.309 |

To verify the partition-to-partition capacitive coupling analysis procedure, the sum of the displacement currents between partitions is compared with the conduction current difference at the partition interface (known from the direct PEEC simulation). Table III summarizes the conduction currents entering and leaving each victim partition. The local branch indices used in the table are defined in Fig. 14. The comparison in Table IV shows that the total displacement currents calculated from the partition-to-partition analysis are almost identical to the

Fig. 14. Local circuit branch index on the second lane of the audio channel. The branches at the partitions' interfaces are used to record the information of the conduction current.

TABLE IV

DISPLACEMENT CURRENT FROM PARTITIONS

| Method                 | 10    | 11    | 12    | 13    | 14    |

|------------------------|-------|-------|-------|-------|-------|

| Partition-based (mA)   | 2.484 | 0.677 | 1.401 | 0.033 | 0.279 |

| Current difference(mA) | 2.484 | 0.671 | 1.396 | 0.034 | 0.277 |

TABLE V INDUCTANCE EXTRACTION

| Extraction method        | $L_{14,14}(nH)$ | $L_{14,18}(nH)$ |

|--------------------------|-----------------|-----------------|

| Q3D                      | 2.425           | 0.656           |

| Post-processing approach | 2.48            | 0.691           |

conduction current difference between the boundary branches. The current comparisons indicate successful decomposition of the capacitive coupling paths.

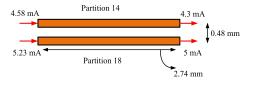

Similar to the capacitive coupling analysis, the partition-to-partition inductive coupling can also be validated through the comparison of the sum of inductive voltage drop caused by the geometry partitions and the potential difference between the boundary nodes. Here, we use another approach to validate the inductive coupling analysis. The inductive coupling between partitions 14 and 18 is further validated by the comparison with a quasi-static circuit solver [34]. As shown in Fig. 15 the conduction current entering and leaving partitions 14 and 18 is close; therefore, a single partial inductance can be used to model the inductive coupling (self and mutual) between partitions 14 and 18. The partial inductance can be calculated as

$$L_{mn} = \frac{V_{mn}}{j\omega i_n} \tag{12}$$

where  $V_{mn}$  is the induced voltage on partition m caused by partition n and  $i_n$  is the conduction current on partition n. The retrieved partial inductances obtained by the postprocessing approach and Q3D show a good correlation, as presented in Table V.

In summary, the proposed partitioning-based analysis can provide several advantages for the coupling mechanism analysis. First, the types of coupling and dominant coupling path between the geometrical partitions can be distinguished. Second, the coupling level between the aggressor and victim partitions can be quantified. Finally, the efficiency of the coupling mechanism is considered. The evaluation of capacitive coupling and inductive coupling involves only matrix-vector products, and the overall

TABLE VI DISPLACEMENT CURRENT BETWEEN ANTENNA PATCH AND PINS

| Index                     | 5     | 10    | 15    |

|---------------------------|-------|-------|-------|

| Displacement current (mA) | 0.704 | 4.184 | 4.983 |

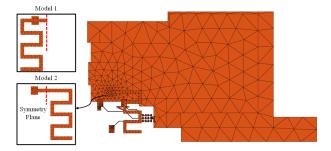

Fig. 18. Modifications to the layout: Model 1 represents the initial simulation model, whereas Model 2 mirrors the antenna patch (partition 1) along a symmetry plane.

calculation takes less than one second, resulting in high efficiency.

#### IV. APPLICATION

Adding filtering circuits and modifying layouts are commonly used to mitigate the interference problem [11], [25]. This section demonstrates how the suggested method may be used to efficiently evaluate the effectiveness of various RFI mitigation techniques.

# A. Filter Circuit

An inductor in series can serve as a high-frequency filter circuit. As shown in Fig. 16, a 100-nH inductor (0402 package) is placed at three different locations.

For the PEEC method, the simulations take less than 1 min for each configuration since the inductor's effect can be incorporated by modifying the existing inductance matrix. By contrast, with the parallel FEKO solver, it takes around 6 min to get similar results. The PEEC approach allows for the efficient simulations of scenarios involving various filtering circuit placements (in this case, at least six times faster than the commercial tool). As shown in Fig. 17, the received noise voltage can be greatly reduced by introducing the filtering circuit on trace 1.

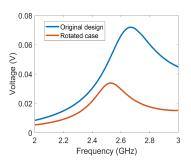

### B. Modifying Layout

In [11] and [35], the RFI problem is mitigated by transforming and rotating the entire module, such as antennas and IC. Through the partitioning approach, it is demonstrated that an efficient and effective mitigation method may be proposed by modifying the geometric partitions.

Through the partition-to-partition analysis, as given in Table VI, the capacitive coupling is mainly due to the patch partition and the pins on the second and third traces. As a proof of concept, the antenna patch partition is mirrored along the XZ plane with no other geometry changes (Fig. 18), which may reduce the capacitive coupling between the antenna and audio traces. The inductances and capacitances between partition 1

TABLE VII SUMMARY OF NODES AND BRANCHES

|                 | partition 1 | other partitions |

|-----------------|-------------|------------------|

| No. of nodes    | 84          | 2532             |

| No. of branches | 84          | 3657             |

TABLE VIII

CIRCUITS SIZE COMPARISON

|                   | Model 1            | Model 2 (Need update) |

|-------------------|--------------------|-----------------------|

| No. of capacitors | $2616 \times 2616$ | $84 \times 2532$      |

| No. of inductors  | $3741 \times 3741$ | $84 \times 3657$      |

Fig. 19. Received noise voltage for different layouts.

and the other partitions are the only ones in the inductance and capacitance matrices that need to be changed for the new layout, which reduce the circuit extraction time by 30 times, as summarized in Tables VII and VIII . The received voltage comparison is shown in Fig. 19 and around 6 dB reduction is observed for the new layout.

## V. DISCUSSION

In this article, a systematic methodology for coupling mechanism analysis is proposed. Due to the difficulty of extracting the partition-based capacitances and inductances, the capacitive coupling and inductive coupling are analyzed using a meshdependent post-processing approach.

Future improvement of this work may take the dielectric objects into consideration and apply it to the signal integrity and power integrity modeling. A promising method is the PEEC model derived from the Poggio–Miller–Chang–Harrington–Wu–Tsai formulation [36].

# VI. CONCLUSION

This article proposes a simple, efficient, and layout-oriented approach to analyze the coupling mechanism in RFI problem. This approach is applicable to both quasi-static and full-wave regimes, since retardation effects can be included in the rPEEC model. Using matrix blocks of partial elements, currents, and potential vectors of different geometrical partitions, the capacitive current and inductive voltage drop between different partitions can be quantified. In addition, the coupling mechanism can be analyzed between different partitions without the need to break the geometry into smaller structures or to add ports or macronodes to each partition.

#### ACKNOWLEDGMENT

The author Xu Wang would like to thank Dr. Albert Ruehli for his helpful discussions and support during this work.

#### REFERENCES

- H. Wang, V. Khilkevich, Y.-J. Zhang, and J. Fan, "Estimating radiofrequency interference to an antenna due to near-field coupling using decomposition method based on reciprocity," *IEEE Trans. Electromagn. Compat.*, vol. 55, no. 6, pp. 1125–1131, Dec. 2013.

- [2] G. Ouyang, X. Ye, and T.-T. Nguyen, "Switching voltage regulator noise coupling to signal lines in a server system," in *Proc. IEEE Int. Symp. Electromagn. Compat.*, 2010, pp. 72–78.

- [3] A. Ruehli, G. Antonini, and L. Jiang, Circuit Oriented Electromagnetic Modeling Using the PEEC Techniques. Hoboken, NJ, USA: Wiley, 2017.

- [4] P. Feldmann and R. Freund, "Efficient linear circuit analysis by Pade approximation via the Lanczos process," *IEEE Trans. Comput.-Aided Des. Integr. Circuits Syst.*, vol. 14, no. 5, pp. 639–649, May 1995.

- [5] J. Wang and K.-L. Wu, "A derived physically expressive circuit model for multilayer RF embedded passives," *IEEE Trans. Microw. Theory Techn.*, vol. 54, no. 5, pp. 1961–1968, May 2006.

- [6] Y. Dou and K.-L. Wu, "Direct mesh-based model order reduction of PEEC model for quasi-static circuit problems," *IEEE Trans. Microw. Theory Techn.*, vol. 64, no. 8, pp. 2409–2422, Aug. 2016.

- [7] G. Antonini and D. Romano, "Efficient frequency-domain analysis of PEEC circuits through multiscale compressed decomposition," *IEEE Trans. Electromagn. Compat.*, vol. 56, no. 2, pp. 454–465, Apr. 2014.

- [8] D. Romano and G. Antonini, "Partitioned model order reduction of partial element equivalent circuit models," *IEEE Trans. Compon. Packag. Manuf. Technol.*, vol. 4, no. 9, pp. 1503–1514, Sep. 2014.

- [9] N. Bondarenko et al., "Development of simple physics-based circuit macromodel from PEEC," *IEEE Trans. Electromagn. Compat.*, vol. 58, no. 5, pp. 1485–1493, Oct. 2016.

- [10] Q. Huang, F. Zhang, T. Enomoto, J. Maeshima, K. Araki, and C. Hwang, "Physics-based dipole moment source reconstruction for RFI on a practical cellphone," *IEEE Trans. Electromagn. Compat.*, vol. 59, no. 6, pp. 1693–1700, Dec. 2017.

- [11] Q. Huang et al., "A novel RFI mitigation method using source rotation," *IEEE Trans. Electromagn. Compat.*, vol. 63, no. 1, pp. 11–18, Feb. 2021.

- [12] A. E. Ruehli and A. C. Cangellaris, "Progress in the methodologies for the electrical modeling of interconnects and electronic packages," *Proc. IEEE*, vol. 89, no. 5, pp. 740–771, May 2001.

- [13] P. J. Restle, A. E. Ruehli, S. G. Walker, and G. Papadopoulos, "Full-wave PEEC time-domain method for the modeling of on-chip interconnects," *IEEE Trans. Comput.-Aided Des. Integr. Circuits Syst.*, vol. 20, no. 7, pp. 877–886, Jul. 2001.

- [14] Y. S. Cao et al., "Inductance extraction for PCB prelayout power integrity using PMSR method," *IEEE Trans. Electromagn. Compat.*, vol. 59, no. 4, pp. 1339–1346, Aug. 2017.

- [15] G. Gabriadze et al., "Enhanced PEEC model based on automatic Voronoi decomposition of triangular meshes," *IEEE Trans. Electromagn. Compat.*, vol. 62, no. 5, pp. 2196–2208, Oct. 2020.

- [16] I. F. Kovačević, T. Friedli, A. M. Müsing, and J. W. Kolar, "3-D electromagnetic modeling of parasitics and mutual coupling in EMI filters," *IEEE Trans. Power Electron.*, vol. 29, no. 1, pp. 135–149, Jan. 2013.

- [17] R. Torchio, F. Lucchini, J.-L. Schanen, O. Chadebec, and G. Meunier, "FFT-PEEC: A fast tool from CAD to power electronics simulations," *IEEE Trans. Power Electron.*, vol. 37, no. 1, pp. 700–713, Jan. 2022.

- [18] J. Park, J. Lee, B. Seol, and J. Kim, "Fast and accurate calculation of system-level ESD noise coupling to a signal trace by PEEC model decomposition," *IEEE Trans. Microw. Theory Techn.*, vol. 65, no. 1, pp. 50–61, Jan. 2017.

- [19] A. E. Ruehli and H. Heeb, "Circuit models for three-dimensional geometries including dielectrics," *IEEE Trans. Microw. Theory Techn.*, vol. 40, no. 7, pp. 1507–1516, Jul. 1992.

- [20] Y. Jiang, Y. Dou, and K.-L. Wu, "Generalized PEEC model for conductor-dielectric problems with radiation effect," *IEEE Trans. Microw. Theory Techn.*, vol. 68, no. 1, pp. 27–38, Jan. 2020.

- [21] L. Lombardi, D. Romano, and G. Antonini, "Efficient numerical computation of full-wave partial elements modeling magnetic materials in the PEEC method," *IEEE Trans. Microw. Theory Techn.*, vol. 68, no. 3, pp. 915–925, Mar. 2020.

- [22] D. Romano, I. Kovačević-Badstübner, M. Parise, U. Grossner, J. Ekman, and G. Antonini, "Rigorous dc solution of partial element equivalent circuit models including conductive, dielectric, and magnetic materials," *IEEE Trans. Electromagn. Compat.*, vol. 62, no. 3, pp. 870–879, Jun. 2020.

- [23] L. K. Yeung and K.-L. Wu, "Generalized partial element equivalent circuit PEEC modeling with radiation effect," *IEEE Trans. Microw. Theory Techn.*, vol. 59, no. 10, pp. 2377–2384, Oct. 2011.

- [24] C.-C. Chou, W.-C. Lee, and T.-L. Wu, "A rigorous proof on the radiation resistance in generalized PEEC model," *IEEE Trans. Microw. Theory Techn.*, vol. 64, no. 12, pp. 4091–4097, Dec. 2016.

- [25] W. Zhang et al., "A SPICE-compatible model to simulate RFI-Induced buzz noise problem in a camera," *IEEE Trans. Electromagn. Compat.*, vol. 64, no. 4, pp. 987–998, Aug. 2022.

- [26] Y. Zhong, "Measurement-based quantification of buzz noise in wireless devices," in Proc. Joint Int. Symp. Electromagn. Compat. Sapporo Asia-Pacific Int. Symp. Electromagn. Compat. 2019, pp. 552–555.

- [27] S. Rao, D. Wilton, and A. Glisson, "Electromagnetic scattering by surfaces of arbitrary shape," *IEEE Trans. Antennas Propag.*, vol. 30, no. 3, pp. 409–418, May 1982.

- [28] A. Rong and A. C. Cangellaris, "Generalized PEEC models for threedimensional interconnect structures and integrated passives of arbitrary shapes," in *Proc. IEEE 10th Topical Meeting Elect. Perform. Electron. Packag.*, 2001, pp. 225–228.

- [29] J. Fan, J. Drewniak, H. Shi, and J. Knighten, "DC power-bus modeling and design with a mixed-potential integral-equation formulation and circuit extraction," *IEEE Trans. Electromagn. Compat.*, vol. 43, no. 4, pp. 426–436, Nov. 2001.

- [30] D. Liu, Common Mode Curr. Estimation for Cable Bundle Inside a Veh.. Rolla, MO, USA: Missouri Univ. Sci. Technol., 2013.

- [31] K. Hormann and A. Agathos, "The point in polygon problem for arbitrary polygons," *Comput. Geometry*, vol. 20, no. 3, pp. 131–144, 2001.

- [32] Mathworks, "MATLAB," Accessed: May 8, 2022. [Online]. Available: https://www.mathworks.com/help/matlab/ref/graph.shortestpath.html

- [33] Altair, "FEKO," Accessed: May 8, 2022. [Online]. Available: https://www.altair.com/feko/

- [34] ANSYS, "Q3D," Accessed: May 8, 2022. [Online]. Available: https://www.ansys.com/products/electronics/ansys-q3d-extractor

- [35] C. Hwang and Q. Huang, "IC placement optimization for RF interference based on dipole moment sources and reciprocity," in *Proc. Asia-Pacific Int. Symp. Electromagn. Compat.*, 2017, pp. 331–333.

- [36] D. Gope, A. E. Ruehli, C. Yang, and V. Jandhyala, "(s) PEEC: Timeand frequency-domain surface formulation for modeling conductors and dielectrics in combined circuit electromagnetic simulations," *IEEE Trans. Microw. Theory Techn.*, vol. 54, no. 6, pp. 2453–2464, Jun. 2006.

Xu Wang (Student Member, IEEE) received the B.S and M.S degrees in electrical engineering from the University of Electronic Science and Technology of China, Chengdu, China, in 2015 and 2018, respectively. He is currently working toward the Ph.D. degree in electrical engineering with the Missouri University of Science and Technology, Rolla, MO, USA.

His current research interests include partial element equivalent circuit modeling and development of radiation emission models for components and devices

Anfeng Huang (Member, IEEE) was born in Guangxi, China, in July 1992. He received the B.E. and M.S. degrees in electrical engineering from Xidian University, Shaanxi, China, in 2014 and 2017, respectively, and the Ph.D. degree in electrical engineering from the Missouri University of Science and Technology, Rolla, MO, USA, in 2022.

He is currently with Detooltech, Ningbo, China. His current research interests include EMI in power electronics, magnetic material characterization, and advanced measurement techniques.

Wei Zhang received the B.S. degree in electronic information engineering from Central South University, Changsha, China, in 2014, the M.S. degree in electronic science and technology from Beihang University, Beijing, China, in 2017, and Ph.D. degree in electrical engineering from EMC Laboratory, Missouri university of Science and Technology, Rolla, MO, USA, in 2022.

She is currently with Marvell Technology as a package SIPI Engineer. Her research interests include SIPI, system EMC, and RFI.

**Reza Yazdani** received the Ph.D. degree in telecommunication engineering from the K. N. Toosi University of Technology, Tehran, Iran, in 2021.

In January 2022, he joined the Missouri University of Science and Technology (formerly University of Missouri-Rolla), Rolla, MO, USA, where he is currently a Postdoctoral Fellow with Electromagnetic Compatibility Laboratory. His research interests include antenna design, RF desense, EMI, and signal integrity in high-speed digital systems.

**DongHyun (Bill) Kim** (Member, IEEE) received the B.S., M.S., and Ph.D. degrees in electrical engineering from the Korea Advanced Institute of Science and Technology (KAIST), Daejeon, South Korea, in 2012, 2014, and 2018, respectively.

In 2018, he joined the Missouri University of Science and Technology (formerly University of Missouri-Rolla), Rolla, MO, USA, and is currently an Assistant Professor with the Missouri S&T EMC Laboratory, Rolla, MO, USA. His current research interests include nanometer-scale devices, through-

silicon via technology, dielectric material characterization and signal integrity, power integrity, temperature integrity, electromagnetic compatibility, and electrostatic discharge in 2.5-D/3-D IC systems.

Dr. Kim was the recipient of the IEEE Region 5 Outstanding Young Professional (formerly GOLD) Award, IEEE St. Louis Section Outstanding Young Engineer Award, IEEE APEMC Outstanding Young Scientist Award, and DesignCon Best Paper Award. He was the corecipient of DesignCon Early Career Best Paper Award and IEEE EMC Symposium Best Paper Award. He is currently the Vice Chair of the IEEE EMC Society TC-10 (Signal Integrity and Power Integrity) and IEEE St. Louis Section.

**Takashi Enomoto** received the B.S. degree in electrical engineering from the Kyoto Institute of Technology, Kyoto, Japan, in 1989.

In 1989, he joined Sony Corporation, Tokyo, Japan, as an Electrical Engineer. His research interests include development of ESD/RFI measurement and simulation techniques.

**Taketoshi Sekine** received the B.S. degree in chemistry from Nagoya University, Japan, in 1994, and the M.S. and Ph.D. degrees in arts and science from the University of Tokyo, Japan, in 1996 and 1999, respectively.

He is currently an EMC and optical device Engineer with Sony Global Manufacturing and Operations Corporation. His research interests includes material research, development of photonic devices and development of EMC-design technique at a research institution and several manufacturers.

Dr. Sekine is a Member of the IEEE EMC Society, Physical Society of Japan, and the Chemical Society of Japan.

**Kenji Araki** (Senior Member, IEEE) received the B.S. and M.S. degrees in electrical engineering from Hosei University, Koganei, Japan, in 1991 and 1993, respectively, and the Ph.D. degree in electrical engineering from the University of Electro-Communications, Chofu, Japan, in 2009.

He joined Sony Corporation, Tokyo, Japan, as an Electrical Engineer in 1993, and is currently a General Manager of Sony Global Manufacturing and Operations Corporation. His research interests include signal integrity, power integrity, electromagnetic in-

terference, electrostatic discharge, radio frequency interference, and simulation for electromagnetic compatibility.

Dr. Araki is a Senior Member of the Institute of Electronics, Information and Communication Engineers of Japan. He was the recipient of IEEE EMC Society Technical Achievement Award in May 2018.

Jun Fan (Fellow, IEEE) received the B.S. and M.S. degrees in electronic engineering from Tsinghua University, Beijing, China, in 1994 and 1997, respectively, and the Ph.D. degree in electrical engineering from the Missouri University of Science and Technology (formerly University of Missouri-Rolla), Rolla, MO, USA, in 2000.

From 2000 to 2007, he was with NCR Corporation, San Diego, CA, USA, as a Consultant Engineer. In July 2007, he joined the Missouri University of Science and Technology and became a tenured Professor

in 2016. From October 2018 to August 2020, he was the Cynthia Tang Missouri Distinguished Professor in computer engineering. He was the Director of the Missouri S&T EMC Laboratory, and the Director of the National Science Foundation (NSF) Industry/University Cooperative Research Center (I/UCRC) for Electromagnetic Compatibility (EMC) from 2013 to 2020. He was a Senior Investigator of Missouri S&T Material Research Center. His research interests include hardware design and fundamental research for electromagnetic compatibility (including signal and power integrity) at the levels of integrated circuit, package, PCB and system, and development of specialized design tools and innovative measurement technologies.

Dr. Fan was a Member of the Board of Directors of the IEEE EMC Society, Chair of the Technical Advisory Committee and TC-9 Computational Electromagnetics Committee, and a Distinguished Lecturer. He is the inaugural Editor-in-Chief of the IEEE TRANSACTIONS ON SIGNAL AND POWER INTEGRITY and an Associate Editor for the IEEE TRANSACTIONS ON ELECTROMAGNETIC COMPATIBILITY. He was the Technical Paper Chair and Technical Program Chair for a few IEEE International Symposia on EMC, General Chair for IEEE International Conference on Signal and Power Integrity, Founding Chair of the SC-4 EMC for Emerging Wireless Technologies Special Committee, and so on. He was the recipient of the IEEE EMC Society Technical Achievement Award in August 2009 and the Richard R. Stoddart Award for Outstanding Performance in 2022.

**Chulsoon Hwang** (Senior Member, IEEE) received the B.S., M.S., and Ph.D. degrees in electrical engineering from the Korea Advanced Institute of Science and Technology (KAIST), Daejeon, South Korea, in 2007, 2009, and 2012, respectively.

From 2012 to 2015, he was a Senior Engineer with Samsung Electronics, Suwon, South Korea. In July 2015, he joined the Missouri University of Science and Technology (formerly University of Missouri-Rolla), Rolla, MO, USA, where he is currently an Associate Professor. His research interests include

RF desense, signal/power integrity in high-speed digital systems, EMI/EMC, hardware security and machine learning.

Dr. Hwang was the recipient of the AP-EMC Young Scientist Award, Google Faculty Research Award, and Missouri S&T's Faculty Research Award. He was a corecipient of seven best paper/best student paper awards from various conferences, including the IEEE EMC+SIPI, the AP-EMC, and the DesignCon.