# High-Speed Differential Via Optimization using a High-Accuracy and High-Bandwidth Via Model

Chaofeng Li

EMC Laboratory

Missouri University of Science

and Technology

Rolla, USA

clf83@mst.edu

Muqi Ouyang

EMC Laboratory

Missouri University of Science

and Technology

Rolla, USA

ouyangm@mst.edu

Kevin Cai

Unified Computing System

Cisco Systems, Inc

San Jose, CA, USA

kecai@cisco.com

Bidyut Sen

Unified Computing System

Cisco Systems, Inc

San Jose, CA, USA

bisen@cisco.com

Manish Kizhakkeveettil Mathew

EMC Laboratory

Missouri University of Science

and Technology

Rolla, USA

mkmbzm@mst.edu

Seyedmehdi Mousavi

EMC Laboratory

Missouri University of Science

and Technology

Rolla, USA

smousavi@mst.edu

**Abstract**— A physics-based equivalent model of the high-speed differential via pair with high accuracy and high bandwidth is proposed for the first time. The proposed physics-based equivalent circuit model of the differential via pair includes the effect of adjacent ground (GND) vias. The proposed model is verified using 3D full-wave numerical simulation results. In addition, the change in electrical performance due to change in anti-pad radius, the via pitch and the GND-via- to-differential-via distance is analyzed. Based on the analysis, electrical performance of differential via pair can be accurately and rapidly optimized with respect to design parameters, such as the via pitch, the anti-pad radius and the GND-via-to-differential-via distance using the proposed model, to provide pre-layout design guide for high-speed channel designers. By using the proposed high-accuracy and high-bandwidth physics-based via model, the via optimization time can be drastically reduced with high accuracy.

**Keywords**—High-speed via optimization, differential via, high-accuracy, high-bandwidth

## I. INTRODUCTION

With trend in technology scaling down and the data rate increasing continuously, high-speed channel design and optimization have become more challenging [1]. Maintaining signal integrity is an inevitable challenge for high-speed printed circuit board (PCB) designers during the product development stage [2]. In high-speed channels, vertical interconnects, commonly known as vias, are used to route signals on different layers for different channels, which are typical impedance discontinuity inducing components in high-speed channels, which can result in profound signal integrity and power integrity issues. Thus, it is essential to design the vias with high electrical performance, to meet required impedance, return loss, and insertion loss specifications.

Generally, 3D full-wave simulation software, such as HFSS and CST, are used for the optimization of the via transition. Based on 3D full-wave simulation, the via stub

resonance, the impact of non-functional pads and the ground via numbers were investigated in [3]. The time domain impedance (TDR) for the through hole vias, the blind vias and the buried vias was studied in [4]. Due to the structural complexity of the via transition and high number of design parameters for optimization, the via optimization by 3D full-wave simulation is very time consuming. Many equivalent models for high-speed differential via pair have been developed to reduce the optimization time. A differential via pair modeling methodology was introduced in [5], where accuracy decreases after 20 GHz. Moreover, some modeling strategies of the high-speed via was investigated in paper [6] and non-function pads placement optimization for high-speed channel based on multiple reflection theory was proposed [7],[8]. However, to apply techniques introduced in [7] and [8], accurate high-speed differential via model is required.

To help reduce the high-speed channel design time, this paper introduces the high-speed differential via optimization based on a physics-based via model with high accuracy and high bandwidth, which can work up to 70 GHz, for the first time. The proposed physics-based equivalent model of differential via verified by 3D full-wave simulation (ANSYS HFSS). Unlike the conventional physics-based via models, the proposed equivalent circuit model considers the impact of the higher-order modes in the parallel-plate for increased accuracy in high frequency region. In addition, the change in electrical performance with respect to change in the anti-pad radius, the via pitch and the ground (GND)-via-to-differential-via distance are analyzed. The electrical performance of differential via pair can be accurately and rapidly optimized based on the proposed model, to save time during high-speed channel design.

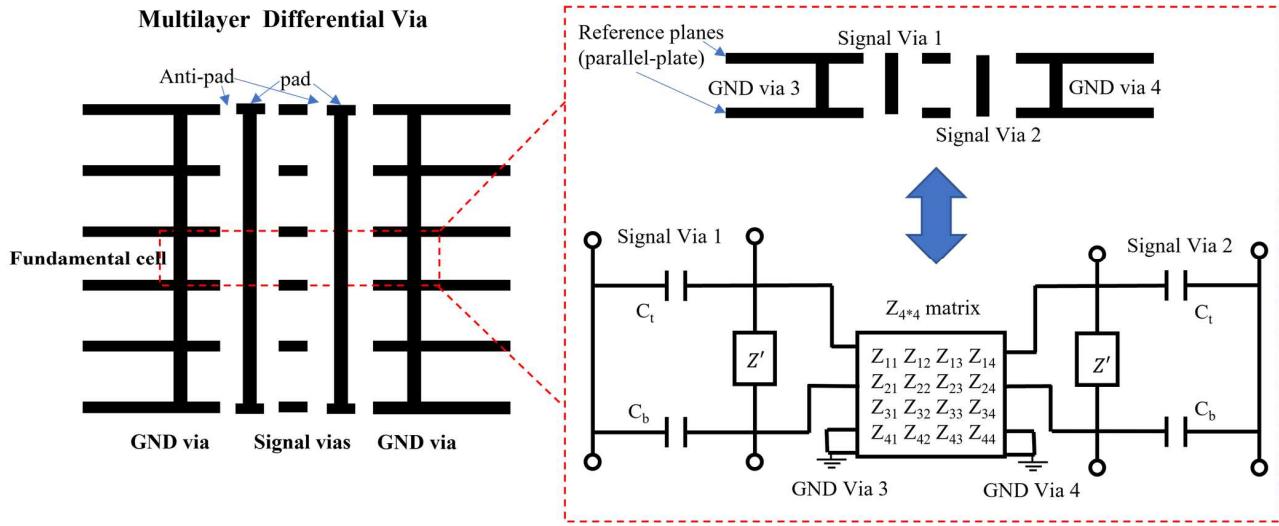

Fig. 1. Proposed physics-based equivalent circuit model of the differential via with individual anti-pad.

## II. THE PROPOSED DIFFERENTIAL VIA PAIR MODEL

A high-accuracy and high-bandwidth single signal via model was proposed in [9]. The application range of the high-accuracy and high-bandwidth via model was investigated in [10]. Based on the high-accuracy and high-bandwidth equivalent circuit model of single signal via, the physics-based equivalent circuit model of the differential via pair with the individual anti-pad is proposed in this paper, as shown in Figure 1, which corresponds to differential via pair segment crossing a cavity enclosed by two reference plates. The equivalent circuit model includes four capacitors for the via-to-parallel-plate coupling, the high-order mode parallel-plate impedances  $Z'$  for each signal via, and the 4 by 4 Z matrix for the coupling of all vias due to fundamental parallel-plate mode. In the 4 by 4 Z matrix, the self-impedance  $Z_{ii}$  represents the fundamental parallel-plate impedance for each via while the mutual-impedance  $Z_{ij}$  represents the via coupling due to the fundamental parallel-plate mode. The key difference with the previous method [6] is that the proposed equivalent model considers the impact of higher-order parallel-plate modes, to achieve high accuracy for high bandwidth application.

The coupling capacitance between the via and the parallel plate has been analyzed in the past, and the via-to-plate capacitance calculations are proposed in [11],[12], and[13]. In this paper, the coupling capacitances are calculated based on [12].

The self-impedance  $Z_{ii}$  represents the coupling between the via and the parallel-plate due to the fundamental parallel-plate mode, which can be calculated in terms of the modal fields. When the parallel plate is infinitely large or the boundary condition of the plate consists of perfectly matched layers (PMLs), the self-impedance can be calculated as [14]

, where  $i$  is the via number,  $r_0^i$  is the radius of the  $i_{th}$  via.  $k_0 = k' - jk''$ , which is a complex wavenumber.  $k' = \omega\sqrt{\mu_0\epsilon_0\epsilon_r}$  and  $k'' = \omega\sqrt{\mu_0\epsilon_0\epsilon_r}(\tan\delta + \frac{d_s}{h})/2$ , and  $\omega$  is the angular frequency.  $\epsilon_0$  and  $\mu_0$  are the permittivity and permeability of free space, respectively.  $\epsilon_r$  is relative permittivity,  $\tan\delta$  is the loss tangent of the dielectric material,  $d_s = \sqrt{2/\omega\mu_0\sigma}$  is the skin depth of conductor with conductivity of  $\sigma$ .  $h$  and  $t$  are the parallel-plate height and plate thickness, respectively.  $H_0^2$  and  $H_1^2$  is the zero-order and first-order Hankel function of the second kind, relatively. When the parallel plate is finite or the boundary condition of the plate is a perfect electric or magnetic conductor (PEC or PMC) boundary, the self-impedance  $Z_{ii}$  can be calculated based on the cavity method [15].

The mutual-impedance  $Z_{ij}$  represents the coupling between the vias due to the fundamental parallel-plate mode, which can also be calculated by the modal fields. When the parallel plate is infinitely large, we can calculate the mutual-impedance as [14]

$$Z_{ij} = \frac{k_0^2 a_0 H_0^2(k_0 r_{ij}) h J_0(k_0 r_0^j)}{2\pi r_0^i j \omega \epsilon_0 \epsilon_r k_0 a_0 H_1^2(k_0 r_0^i)} \quad (6)$$

Where  $j$  is the via number,  $r_0^j$  is the radius of the  $j_{th}$  via,  $r_{ij}$  is the pitch size of the  $i_{th}$  via and of the  $j_{th}$  via.  $J_0$  is the zero-order Bessel function. When the parallel plate is finite, the mutual impedance can be calculated based on the cavity method [15].

The high-order parallel-plate modes impedances  $Z'$  for each signal via can also be calculated in terms of the modal fields, which are excited at the anti-pad boundary. For the higher-

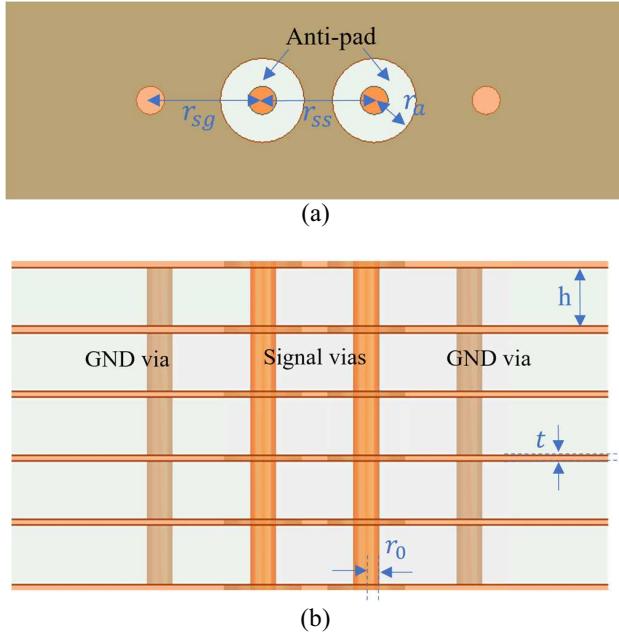

Fig. 2. Differential via with GND vias in 6 layers board. (a) top view, (b) side view.

order modes, only  $TM_{0n}$  modes are considered here. Because the via structure we consider is circular and symmetric, only  $TM_{0n}$  modes (higher-order modes, which are axially isotropic modes) are excited [16]. The impedance  $Z'$  is calculated as

$$Z' = \frac{h \sum_{n=1}^N k_n H_1^2(k_n r_a)}{j 2 \pi r_a \omega \epsilon_0 \epsilon_r \sum_{n=1}^N H_1^2(k_n r_a)} \quad (8)$$

where  $k_n = \sqrt{k_0^2 - (n\pi/h)^2}$ ,  $n$  represents the mode number,  $N$  is the total number of higher-order modes it counts for the via modeling. The derivation of  $Z'$  can be found in the reference [9].

### III. VERIFICATION AND OPTIMIZATION

In this section, the proposed equivalent circuit model of differential via pair with adjacent GND vias is verified 3D full-wave numerical simulation. Change in electrical performance due additional high-order parallel plate modes is analyzed. Based on the proposed model, the differential via pair's electrical performance can be optimized by parametric analysis on the via pitch, the anti-pad radius and GND-via-to-differential-via distance.

Figure 2 shows the top view and the side view of the differential via pair with GND vias with 6 GND layers, for 3D full-wave numerical simulation. All via radius are  $r_0$  while the anti-pad radius is  $r_a$ , the parallel-plate high is  $h$  and each plate thickness is  $t$ . The signal via pitch is  $r_{ss}$  and the via pitch for the signal via and the GND via is  $r_{sg}$ . The boundary condition for the model is PML.

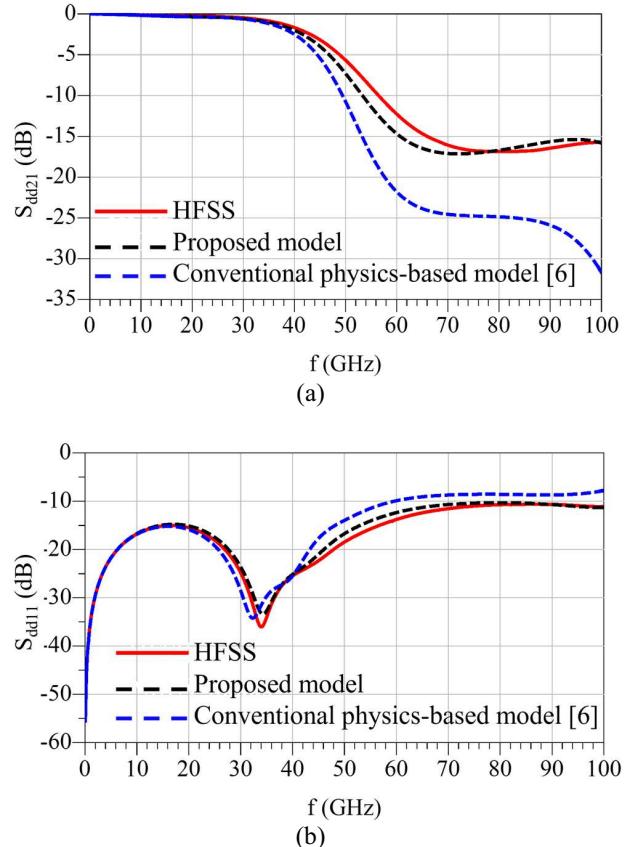

Fig. 3. Differential S-parameters comparison for different methods: (a) Differential insertion loss  $S_{dd21}$ . (b) Differential return loss  $S_{dd11}$ .

#### A. Effect of High-Order Parallel Plate Modes

In first set of analysis, the  $r_0$  and  $r_a$  are 5 mils and 10 mils, respectively. Meanwhile, the  $h$  and the  $t$  are 10 mils and 1 mil, the  $r_{ss}$  and  $r_{sg}$  are both 40 mils. The total thickness of the model is 56 mils. The comparison between the differential insertion loss and the differential return loss of the differential via model are plotted in Figure 3, between the proposed equivalent model and HFSS results. The red solid curve are the results from the 3D full-wave numerical simulation, ANSYS HFSS, the black dotted curve are the results from the proposed equivalent model while the blue dotted curve represents the results from the conventional physics-based equivalent model [6].

We can observe that the differential S-parameters from the proposed equivalent model shows high correlation with the 3D full-wave numerical simulation, up to 100 GHz. However, the differential S-parameters from the conventional physics-based equivalent model shows much larger difference with the simulation results above 40 GHz because it does not consider the high-order parallel-plate modes impedance  $Z'$ . The proposed equivalent model's high accuracy at high frequency is verified. In addition, the importance of high-order parallel-plate modes for high frequency via modeling is also verified.

Identify applicable funding agency here. If none, delete this text box.

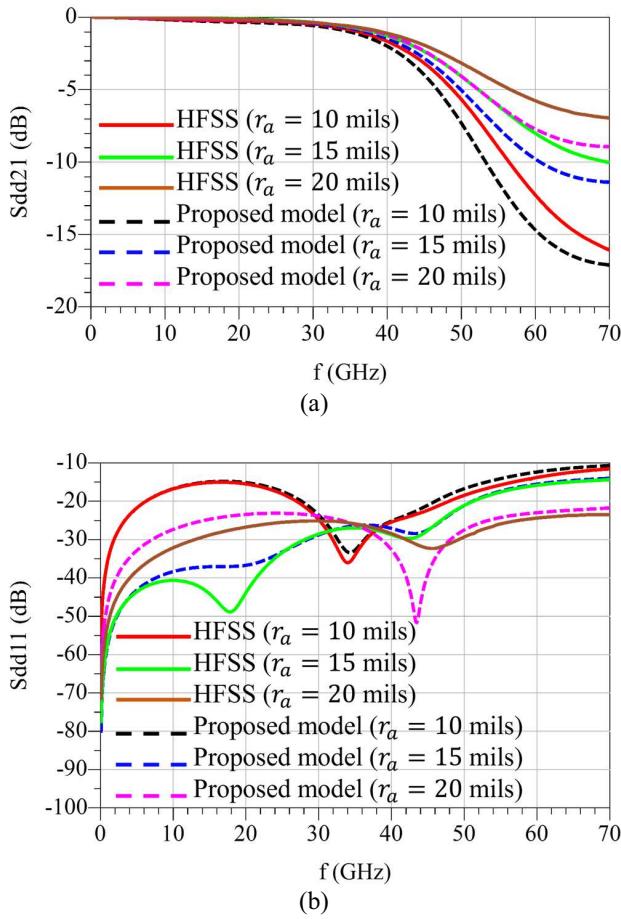

Fig. 4. Differential S-parameters comparison for various anti-pad radii. (a) Differential insertion loss  $S_{dd21}$ , (b) Differential return loss  $S_{dd11}$ .

### B. Parametric Analysis on Anti-pad Radius

To investigate the effect of changes in anti-pad radius, the anti-pad radius is swept from 10 mils to 20 mils with a step of 5 mils in the second case. All other geometrical parameters of the differential via are unchanged from the first case in sub-section A. The differential S-parameters of the differential via are plotted in Figure 4.

The differential insertion loss from the proposed model shows high level of correlation with the simulation results up to 70 GHz. The differences in differential insertion loss between the proposed model and the simulation is less than 2 dB. The differential return loss from the proposed model also shows relatively a high level of correlation with simulation results, with the exception of a few frequency points where the magnitude is below -30 dB.

Additionally, the differential insertion loss decreases with the increase of the anti-pad radius. The differential return loss can be decreased below 30 GHz and can be increased above 40 GHz with the increase of the anti-pad radius.

The proposed model accurately model the effect of change in anti-pad radius on electrical performance.

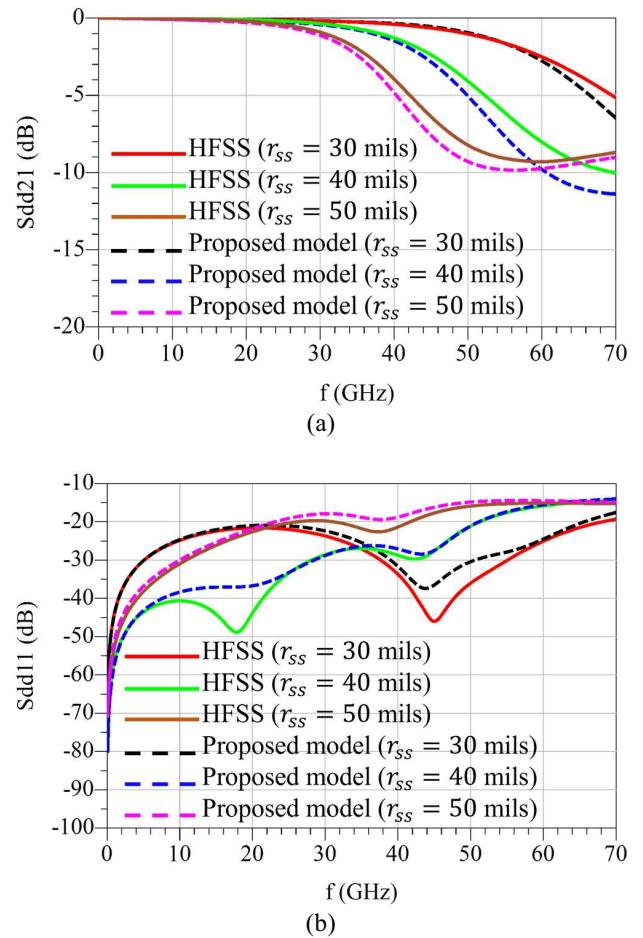

Fig. 5. Differential S-parameters comparison for various via pitches. (a) Differential insertion loss  $S_{dd21}$ , (b) Differential return loss  $S_{dd11}$ .

### C. Parametric Analysis on Via Pitch

The effect of change in via pitch on the differential via's electrical performance is analyzed in the third case. The  $r_{ss}$  is equal to the  $r_{sg}$ . They are both swept from 30 mils to 50 mils with a step of 10 mils. The anti-pad radius for the signal via is 30 mils. Except the anti-radius and the via pitch size, other geometrical parameters of the differential via remain unchanged as the configurations in the first case. The differential S-parameter comparison of the differential via is plotted in Figure 5.

From the differential S-parameter comparison, it is verified again that the proposed model can accurately model the differential via up to 70 GHz, both for differential insertion loss and the differential return loss. Differential insertion loss and the differential return loss of the differential via can decrease for a larger via pitch above 30 GHz. However, for the frequencies below 20 GHz, the larger via pitch can result in increased the differential return loss.

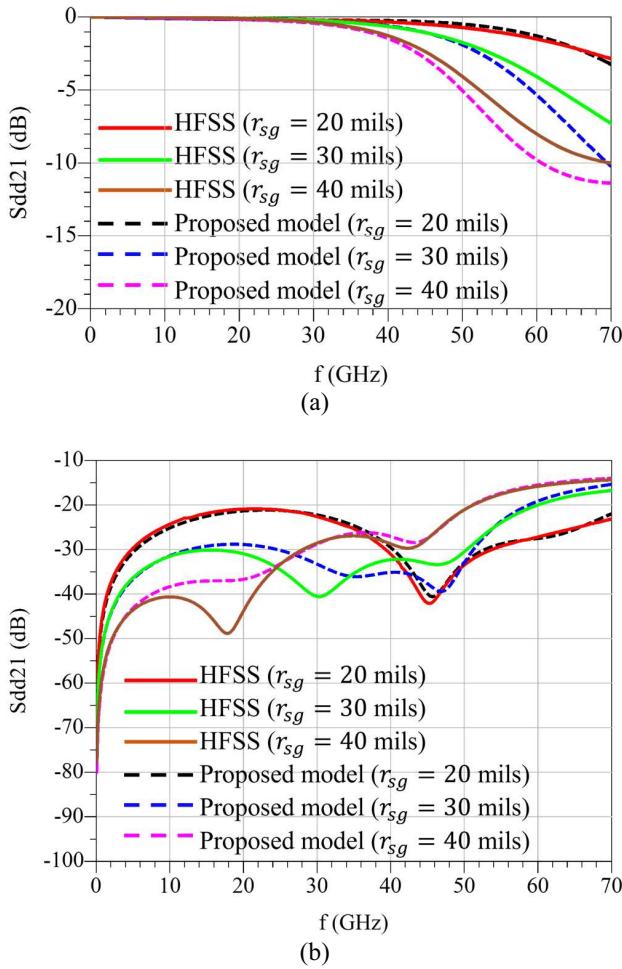

Fig. 6. Differential S-parameters comparison for various GND-via-to-differential-via distances. (a) Differential insertion loss  $S_{dd21}$ , (b) Differential return loss  $S_{dd11}$ .

#### D. Parametric Analysis on GND Via Distance

For fourth set of analysis, the signal via pitch  $r_{ss}$  is fixed as 40 mils, but the pitch  $r_{sg}$  of signal via and the GND via is swept from 20 mils to 40 mils, with 10 mils step. Similarly, the geometry configurations of the differential via remains unchanged as the differential via in third set of analysis. The differential S-parameters are plotted in Figure 6.

The proposed model continues to show high correlation to simulation. The distance  $r_{sg}$  between the signal via and the GND via can also affect the differential via's electrical performance. Unlike the third set of analysis, the small GND-via-to-differential-via distance can help decrease the differential insertion loss and the differential return loss in the frequencies above 30 GHz because the return current return loop size for the differential via pair decreases as the GND-via-to-differential-via distance decreases.

The proposed equivalent model of the differential via pair with adjacent GND vias is verified up to 70 GHz. The effects of the anti-pad radius, the via pitch and GND-via-to-differential-

Table I. Comparison of Computational Resources Cost (per case A)

| Method            | Memory Cost (GB) | CPU Time (hours) |

|-------------------|------------------|------------------|

| Simulation (HFSS) | 29               | 2.1              |

| Proposed model    | 0.2              | 0.02             |

via distance are analyzed. In addition, the computational resource cost of the first set of analysis in 3D full-wave FEM simulation and the proposed model are compared in table I. The simulation was conducted in a server with 3.45 GHz CPU and 512 GB RAM memory. The proposed method is shows higher time and resource efficiency when compared to 3D full-wave simulation with comparable level of accuracy. PCB designers can use the proposed model to optimize high speed channels with at reduced computational resources and time.

#### IV. CONCLUSION

High-accuracy and high-bandwidth physics-based equivalent circuit model of differential via pair with the individual anti-pad and adjacent GND vias is proposed in the paper, for the first time. The accuracy of the proposed equivalent circuit model is verified using comparison to 3D full-wave numerical simulation over multiple cases studies with different anti-pad radius, via pitch size and GND-via-to-differential-via distance up to 70 GHz. Differential via can be optimized by increasing the anti-pad radius or decreasing the via pitch size. Decreasing the GND-via-to-differential-via distance can also help improve the differential via's electrical performance. When compared to 3D full-wave numerical simulation, the proposed model can save computational resources and time. The proposed differential via model will allow high speed channel designers to optimize differential via with different parameters with reduced computation resources and time. Most importantly, the proposed model also provides physical insight to guide differential via optimization for high-speed channels.

#### V. ACKNOWLEDGEMENTS

This work was supported in part by the National Science Foundation (NSF) under Grant IIP-1916535.

#### REFERENCES

- [1] J. Fan, X. Ye, J. Kim, B. Archambeault and A. Orlandi, "Signal Integrity Design for High-Speed Digital Circuits: Progress and Directions," in *IEEE Transactions on Electromagnetic Compatibility*, vol. 52, no. 2, pp. 392-400, May 2010, doi: 10.1109/TEMC.2010.2045381..

- [2] B. Pu, J. He, A. Harmon, Y. Guo, Y. Liu and Q. Cai, "Signal Integrity Design Methodology for Package in Co-packaged Optics Based on Figure of Merit as Channel Operating Margin," *2021 IEEE International Joint EMC/SI/PI and EMC Europe Symposium*, 2021, pp. 492-497, doi: 10.1109/EMC/SI/PI/EMCEurope52599.2021.9559168.

- [3] Y. Deng, Z. Li, Y. Yu, B. Li, X. Wang and Z. Wu, "S Parameters Optimization of High-Speed Differential Vias Model on A Multilayer PCB," *2022 23rd International Conference on Electronic Packaging Technology (ICEPT)*, 2022, pp. 1-4, doi: 10.1109/ICEPT56209.2022.9873518.

- [4] J. N. Hu, N. K. H. Huang and B. -C. Tseng, "Via Design Optimization for Server Applications," *2020 International Symposium on Electromagnetic Compatibility - EMC EUROPE*, 2020, pp. 1-3, doi: 10.1109/EMCEUROPE48519.2020.9245736.

- [5] L. Simonovich, E. Bogatin and Y. Cao, "Differential Via Modeling Methodology," in *IEEE Transactions on Components, Packaging and*

*Manufacturing Technology*, vol. 1, no. 5, pp. 722-730, May 2011, doi: 10.1109/TCPMT.2010.2103313.

[6] J. Xu et al., "A survey on modeling strategies for high-speed differential Via between two parallel plates," *2017 IEEE International Symposium on Electromagnetic Compatibility & Signal/Power Integrity* (EMCSI), 2017, pp. 527-531, doi: 10.1109/ISEMC.2017.8077926.

[7] M. Ouyang et al., "Optimizing the Placement of Non-Functional Pads on Signal Vias Using Multiple Reflection Analysis," *2022 IEEE International Symposium on Electromagnetic Compatibility & Signal/Power Integrity* (EMCSI), 2022, pp. 169-174, doi: 10.1109/EMCSI39492.2022.9889339.

[8] M. Ouyang et al., "Novel Formulations of Multireflections and Their Applications to High-Speed Channel Design," in *IEEE Transactions on Signal and Power Integrity*, vol. 1, pp. 43-54, 2022, doi: 10.1109/TSIPI.2022.3176592..

[9] C. Li, K. Cai, M. Ouyang, Q. Gao, B. Sen and D. Kim, "Mode-Decomposition-Based Equivalent Model of High-Speed Vias up to 100 GHz," in *IEEE Transactions on Signal and Power Integrity*, doi: 10.1109/TSIPI.2023.3268255.

[10] C. Li, et al. "Mode-Decomposition-Based Equivalent Via (MEV) Model and MEV Model Application Range Analysis," *2023 Joint APEMC and NCEMIC*, 2023.

[11] Y. Zhang, J. Fan, G. Sellli, M. Cocchini, and F. Paulis, "Analytical evaluation of via-plate capacitance for multilayer printed circuit boards and packages," *IEEE Trans. Microw. Theory Tech.*, vol. 56, no. 9, pp. 2118–2128, Sep. 2008, doi: 10.1109/TMTT.2008.2002237.

[12] M. Friedrich, C. Bednarz, and M. Leone, "Improved expression for the via-plate capacitance based on the magnetic-frill model," *IEEE Trans. Electromagn. Compat.*, vol. 55, no. 6, pp. 1362–1364, Dec. 2013, doi: 10.1109/TEMC.2013.2265041.

[13] M. Friedrich, M. Leone, and C. Bednarz, "Exact analytical solution for the via-plate capacitance in multi-layer structures," *IEEE Trans. Electromagn. Compat.*, vol. 54, no. 5, pp. 1097–1104, Oct. 2012, doi: 10.1109/TEMC.2012.2189573.

[14] A. R. Chada, Y. Zhang, G. Feng, J. L. Drewniak and J. Fan, "Impedance of an infinitely large parallel-plane pair and its applications in engineering modeling," *2009 IEEE International Symposium on Electromagnetic Compatibility*, 2009, pp. 78-82, doi: 10.1109/ISEMC.2009.5284626.

[15] X. Duan, R. Rimolo-Donadio, H. -D. Brüns and C. Schuster, "Circular Ports in Parallel-Plate Waveguide Analysis With Isotropic Excitations," in *IEEE Transactions on Electromagnetic Compatibility*, vol. 54, no. 3, pp. 603-612, June 2012, doi: 10.1109/TEMC.2011.2170998.

[16] Y.-J. Zhang, A. R. Chada, and J. Fan, "An improved multiple scattering method for via structures with axially isotropic modes in an irregular plate pair," *IEEE Trans. Electromagn. Compat.*, vol. 54, no. 2, pp. 457–465, Apr. 2012, doi: 10.1109/TEMC.2011.2162524.