# Fast and Energy-Efficient Non-Volatile III-V-on-Silicon Photonic Phase Shifter Based on Memristors

Zhuoran Fang,\* Bassem Tossoun, Antoine Descos, Di Liang, Xue Huang, Geza Kurczveil, Arka Majumdar, and Raymond G. Beausoleil

Silicon photonics has evolved from lab research to commercial products in the past decade as it plays an increasingly crucial role in data communication for next-generation data centers and high-performance computing. Recently, programmable silicon photonics has also found new applications in quantum and classical information processing. A key component of programmable silicon photonic integrated circuits (PICs) is the phase shifter, traditionally realized via thermo-optic or free-carrier effects that are weak, volatile, and power hungry. A non-volatile phase shifter can circumvent these limitations by requiring zero power to maintain the switched phases. Previously non-volatile phase modulation is achieved via phase-change or ferroelectric materials, but the switching energy remains high (pico to nano joules) and the speed is slow (micro to milliseconds). Here, a non-volatile III-V-on-silicon photonic phase shifter based on a HfO2 memristor with sub-pJ switching energy (≈400 fl), representing over an order of magnitude improvement in energy efficiency compared to the state of the art, is reported. The non-volatile phase shifter can be switched reversibly using a single 100 ns pulse and exhibits excellent endurance over 800 cycles. This technology can enable future energy-efficient programmable PICs for data centers, optical neural networks, and quantum information processing.

1. Introduction

The silicon photonic phase shifter is a fundamental building block of programmable photonic integrated circuits (PICs).<sup>[1-3]</sup>

Z. Fang, B. Tossoun, A. Descos, D. Liang, X. Huang, G. Kurczveil, R. G. Beausoleil

Hewlett Packard Labs

Hewlett Packard Enterprise

Milpitas, CA 95035, USA

E-mail: rogefzr@uw.edu

Z. Fang, A. Majumdar

Department of Electrical and Computer Engineering

University of Washington

Seattle, WA 98195, USA

A. Majumdar

Department of Physics

University of Washington

Seattle, WA 98195, USA

The ORCID identification number(s) for the author(s) of this article can be found under https://doi.org/10.1002/adom.202301178

DOI: 10.1002/adom.202301178

For certain applications such as electrooptic modulators, the phase shifters need to operate fast and are generally achieved by free-carrier dispersion<sup>[4]</sup> or electro-optic effect,[5,6] which are ultra-fast but the extent of index change is small. On the other hand, applications such as light routing between functional devices and post-fabrication trimming, do not require high speed but need large changes in index. These functionalities are traditionally achieved using thermo-optic effects<sup>[7]</sup> and micro-electromechanical systems (MEMS).[8] A major limitation of all these methods is their volatile nature – a constant power (≈mW) or bias (>20 V) must be applied to maintain the switched states. For programmable photonics, it is highly desirable to have non-volatile phase shifters that require zero<sup>[9,10]</sup> or minimal power<sup>[11]</sup> to maintain the switched states, and the information is retained when the bias is removed. For example, non-volatile phase shifters based on phase change materials[9,12] are very compact and allow true "set-and-forget" operation, but they require relatively high

switching energy (≈nJ) and suffer from slow switching speed (≈hundreds of ns to µs). The high temperature (≈900 K) required to switch the phase change materials can also have reliability concerns. Non-volatile ferroelectric phase shifters based on Barium Titanate<sup>[11]</sup> can achieve multilevel operation and low loss, but the electro-optic effect is weak, and the switching speed is even slower, requiring 10<sup>4</sup> pulses with a total duration of hundreds of microseconds for initializing the states. Although MEMS are shown to exhibit a non-volatile effect and have a compact footprint ( $L_{\pi} \approx 17 \, \mu \text{m}$ ), they require large driving voltage (>20 V) and the switching time can take up to a few seconds imposed by the slow I-V sweep<sup>[13]</sup> to achieve adhesion latching. Lastly, plasmonic memristor switches have been demonstrated to exhibit the latching effect,<sup>[14,15]</sup> but the high insertion loss (≈10 dB) from the metal absorption makes it prohibitive for cascaded phase shifters. Previously III-V-on-silicon photonic phase shifters have been demonstrated for applications in high-speed modulators, [16,17] but they are based on volatile effect (i.e., free carrier dispersion) so are not ideal for programmable PICs that only require infrequent update of phase states. Table S1 (Supporting Information) presents a comparison of non-volatile programming technologies in PICs. Here, we demonstrate a non-volatile phase shifter

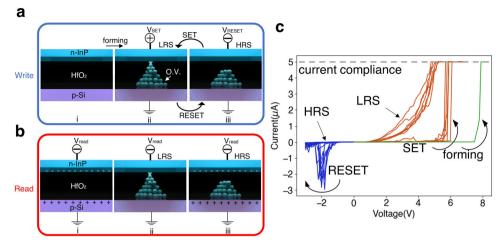

**Figure 1.** Written and read states in a III-V-HfO<sub>2</sub>-Si memristor. a) Schematics illustrating how the states in InP-HfO<sub>2</sub>-Si memristor are written. HRS (LRS), high resistance state (low resistance state). O.V. (oxygen vacancies). b) Schematics showing reading the InP-HfO<sub>2</sub>-Si memristor at states shown in (a). A constant negative read bias is applied to the n-InP in (i, ii, and iii). c) Current-voltage relationship of the forming (green), SET (orange), and RESET (blue) operations. The voltage is the write bias. The grey dash line indicates the 5 μA current compliance to prevent device damage. Seven I-V SET and RESET cycles are plotted on top of each other to show good cyclability.

on the III-V-on-silicon heterogeneous platform enabled by the memristor effect. [18–21] The non-volatility arises from resistively switching the InP-HfO2-Si memristor between high-resistance-state (HRS) and low-resistance-state (LRS) using a single 100 ns long voltage pulse. The phase shifter exhibits a switching energy as low as  $\approx\!400$  fJ, representing over an order of magnitude reduction compared to the state-of-the-art, [9,11] and an excellent endurance of over 800 cycles. Moreover, the III-V-on-silicon heterogeneous platform is fully compatible with foundry processes, [22] potentially enabling seamless integration with laser sources and the energy-efficient large-scale programmable PICs.

#### 2. Working Principle of the III-V-HfO<sub>2</sub>-Si Memristor

The memristor is based on the heterogeneous integration between III-V n-type InP and p-type silicon sandwiching a high dielectric constant HfO<sub>2</sub>, [20,23] see Figure 1a(i). In Figure 1a(i), the memristor is in its as-fabricated state, and applying a negative bias V<sub>read</sub> on the n-InP while keeping the p-Si grounded (i.e., forward bias) will cause carrier accumulation at the oxidesemiconductor interface (Figure 1b(i)), which essentially operates as a MOS (metal-oxide-semiconductor) capacitor. On the other hand, if a large enough positive bias is applied, oxygen vacancies (O.V.) diffuse inside the oxide layer and, at a certain threshold, a conduction filament (CF) consisting of oxygen vacancies is formed<sup>[24]</sup> (see Figure 1a(ii)). Such process is termed "electroforming" and can be visualized in Figure 1c green line where the current suddenly increases at ≈7.5 V and hits the current compliance enforced by the source meter. The voltage in Figure 1c is the bias applied to the n-InP. After forming, the memristor is switched into the LRS, and the MOS capacitor effect is suppressed due to the charge leakage. This is reflected in the Figure 1b(ii) where the forward bias no longer causes carrier accumulation. To return the memristor to HRS, a bias with opposite polarity (i.e., negative) is applied to the n-InP that causes Joule heating and the retraction of oxygen vacancies, eventually giving rise to the rupture of the CFs. The operation is called RE-

SET and is revealed by blue lines in Figure 1c, where the current rapidly increases to  $\approx 2.5 \, \mu A$  at  $\approx -2 \, V$  before collapsing to near zero. Since Joule heating depends on the power, if the CFs rupture was only caused by the Joule heating, then we would have seen the CFs rupture during the voltage ramp down after the CFs form as a higher power is measured (Figure 1c orange lines). The absence of filament breaking at positive bias shows that the RE-SET operation is a compound phenomenon of both field effect and Joule heating that enables the switching at a lower voltage than the SET.<sup>[25]</sup> Reversing the polarity causes the retraction of oxygen vacancies which facilitates the rupture of the filaments. Indeed, electrochemical migration of oxygen vacancies has been regarded as the driving mechanism behind bipolar switching where the SET and RESET polarities are opposite. [26] The rupture of the CFs brings the memristor back to the HRS and the MOS capacitor effect is restored (Figure 1a(iii) and b(iii)). The memristor can then be switched to the LRS again by applying a positive bias to the n-InP but at a lower voltage (5-6 V), as shown by the orange lines in Figure 1c. This is because the CFs do not rupture completely during RESET (Figure 1a(iii)) and fewer oxygen vacancies need to be displaced by the field to re-connect the CFs. Figure 1c shows that SET and RESET operations are repeated for seven consecutive cycles between HRS and LRS.

# 3. A Memristor-Based III-V-on-Silicon Heterogeneous Photonic Platform

The ability to switch a MOS capacitor on and off using a memristor provides a way to realize non-volatile phase tuning in a microring resonator by controlling the carriers in the accumulation layer formed at the waveguide (**Figure 2a**). Thus, the optical modulation happens via the free-carrier dispersion effect, while the non-volatility comes from the memristor controlling the MOS capacitor, which in turn controls the ability to form an accumulation layer of free carriers. The 250 nm tall,  $1.2 \, \mu m$  wide silicon waveguide is formed by partially etching to a 100 nm slab on one side and fully etched to the buried oxide (BOX) on the other side. A

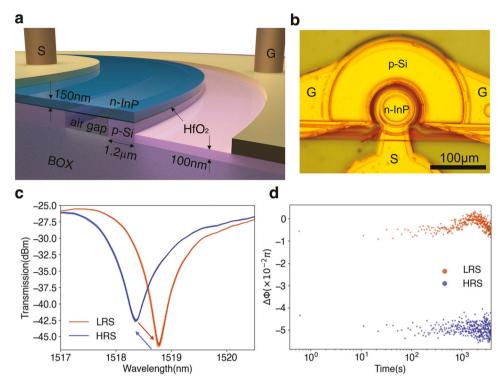

Figure 2. Non-volatile phase tuning of microring resonator using memristors. a) Schematic of the memristive microring MOS capacitor modulator. BOX stands for buried oxide. S (G), signal (ground) electrode. b) Optical micrograph of the microring. c) Reversible switching of microring resonance using memristors. The switching conditions are 7 V, 200 ns pulse width, 8 ns trailing edge for SET and -3 V, 200 ns pulse width, 8 ns trailing edge for RESET. Three consecutive cycles are plotted where the shaded area indicates the standard deviation between the cycles and the solid line indicates the average. d) Time stability test over 1 h of the SET and RESET phase states. The optical spectrum is measured every 10 s to calculate the resonance wavelength.  $\Delta\Phi$  denotes the optical phase shift. A constant -3 V bias at 100 nA current compliance is applied to read the optical states in the above measurements.

150 nm n-InP epitaxial layer is transferred to the silicon layer via a standard wafer bonding technique<sup>[27]</sup> with 9.6 nm thick HfO<sub>2</sub> as the interface oxide<sup>[23]</sup> (see Experimental Section for fabrication details). The HfO<sub>2</sub> acts simultaneously as a gate oxide that forms an MOS capacitor with the Si and InP and a memristor switching layer. The air gap is left in the Si layer to confine the MOS capacitor to the fundamental TE mode area in the Si waveguide and hence reduce the total capacitance for a fast electro-optic response.<sup>[28]</sup> Figure 2b shows the fabricated microring resonator integrated with the memristor. The SEM and TEM images of the heterostructures were reported in our previous work based on the same batch of devices reported here. [23] In the as-fabricated state, the memristor is in the HRS and the negative read bias causes carrier accumulation at the oxide-semiconductor interfaces (Figure 1b(i)). The effective index of the optical mode in the Si waveguide underneath therefore changes by the free carrier dispersion effect which in turn leads to an optical phase shift. Setting the memristor to the LRS leads to the formation of CFs (Figure 1a(ii)) and hence the read voltage can no longer cause carrier accumulation due to the charge leakage (Figure 1b(ii)), and the free carrier induced phase shift is turned off.

Figure 2c shows the reversible switching of a 10  $\mu$ m radius microring resonator between LRS and HRS states for three consecutive cycles using the device structure shown in Figure 2a,b. Pulses are used instead to switch the memristors, allowing faster operation<sup>[29]</sup> compared to the I-V sweep. The shaded regions of

the spectra indicate the standard deviation between the three switching cycles, clearly revealing excellent cycle-to-cycle reproducibility. A constant read bias of -3 V and current compliance of 100 nA are applied when taking all the optical measurements in this work unless otherwise stated. The resonances at zero read bias for both the SET and RESET states are shown in Figure S1 (Supporting Information). In the LRS, the MOS capacitor is off and -3 V read bias only induces a minimal blueshift (see Figure S1, Supporting Information). As the memristor is reset into the HRS, the MOS capacitor is turned on and a blueshift of 0.44 nm is observed under the constant -3 V read bias, corresponding to a phase shift of  $0.09\pi$  for a phase shifter length of 47 µm. The  $L_{\pi}$  is hence estimated to be  $\approx 0.5$  mm – half the length of a ferroelectric-based non-volatile phase shifter.[11] The insertion loss introduced by the carrier dispersion is only 0.28 dB or 0.006 dB μm<sup>-1</sup>, which is comparable to chalcogenide PCMs.<sup>[9]</sup> We further show in Figure 2d that the phase tuning is indeed non-volatile by monitoring the resonance wavelengths over 1 h at a - 3 V read bias. The two-phase levels remain stable over time, with only minimal drift due to the temperature fluctuations, which indicates that the charge leakage is negligible. Section S4 (Supporting Information) shows that the resonances measured after 24 h overlap perfectly with the original spectrum for both the SET and RESET states. However, charge leakage will be an issue for analog operation where charge will leak at the intermediate states and eventually return to the original state. In this case,

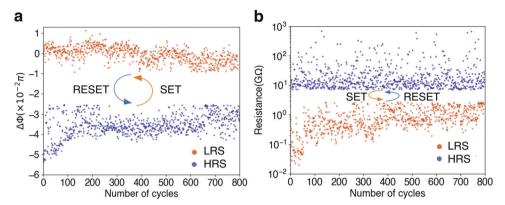

Figure 3. Endurance of the memristor-based non-volatile phase shifter. a) Cyclability of the phase shifter for 800 consecutive cycles or 1,600 switching events. The switching conditions are 15 V, 100 ns pulse width, 8 ns trailing edge for SET and -3 V, 100 ns pulse width, 8 ns trailing edge for RESET.  $\Delta\Phi$  denotes the optical phase shift. b) Simultaneous resistance readout of the memristor switching measured at -0.7 V read bias over the 800 cycles. The pulse conditions are the same as in (a).

the phase shifter must operate in a carrier injection mode where the phase shift is controlled by the current injection, but at a cost of increased free carrier absorption and power consumption.

Device endurance is a key metric in assessing the durability of any non-volatile phase shifter. Here, we performed over 800 cycles or 1,600 transitions on the phase shifter without significant degradation in the performance, see Figure 3a. The experimental setup and procedure are detailed in Experimental Section. The failure mechanism of the phase shifter is discussed in Section S5 (Supporting Information). A phase shift of  $\approx 0.03\pi$  can still be measured after 800 cycles. Meanwhile, in the electrical domain, the current is also monitored in each cycle to estimate the resistance. An HRS/LRS ratio of 10x is measured across the 800 cycles where both LHS and RHS exhibit a high resistance of >1 G $\Omega$ , indicating minimal leakage current (<1 nA) under the read bias. The good match between the endurance in optical and electrical domains verifies that the non-volatile phase tuning indeed originates from the memristor switching. Since both states exhibit high resistance (i.e., low switching current  $\approx \mu A$ ) and the switching time is short (≈100 ns), we extract a low switching energy of 1.3 pJ for SET and 0.4 pJ for RESET (see Section S2, Supporting Information, for the estimation of switching energy) by averaging across multiple devices, representing over an order of magnitude reduction in switching energy compared to the state of the art.[9,11] Such low switching energy is an intrinsic advantage of memristor - since the CFs responsible for the switching are only nanometer scale, [30] minimal current (≈µA) and time (100 ns) is required to form and break the filaments. In comparison, PCMs typically require nano-joules to switch due to the micro-scale size. [9,10] The lower RESET energy compared to SET is because the RESET is caused by a compound effect of Joule heating and polarity, as discussed earlier. Flipping the polarity causes the retraction of oxygen vacancies, so the RESET pulse requires lower voltage and hence smaller amount of current to rupture the filaments. Fundamentally speaking, the memristor switching does suffer from one to two-order magnitude variation in resistance, [29] which was also observed in Figure 3b, due to the stochasticity in the formation of conduction filaments, particularly when there is no current limiting transistor. However, the optical phase shift does not vary as much as the resistance does because we applied a 100 nA current compliance when the optical state was read, which limited how much the phase shift could vary. Since we are showing a photonic phase shifter, the variation in resistance will be irrelevant in actual applications.

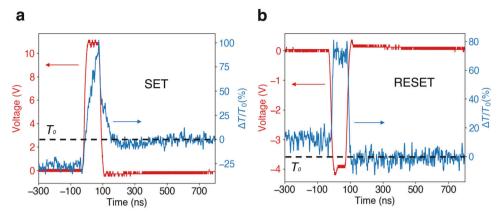

Finally, we show that the SET and RESET have submicrosecond optical response time, see Figure 4. The experimental setup for the real-time measurement can be found in Experimental Section. Note that a constant read bias of -2 V is applied to the Signal during the switching to make sure there is a measurable contrast from the non-volatile switching. Notably, a single 100 ns pulse is enough to trigger both the SET and RESET, compared to hundreds of microseconds required for  $\mathsf{PCMs}^{[9,10]}$  and milliseconds for ferroelectric materials.<sup>[11]</sup> We define the time when the optical transmission starts to change significantly upon the electrical pulse as the onset of the optical response and the time when the optical response goes to  $T_0$  as the end of the optical response (see Figure 4). For SET, the pulse starts at -30 ns, and the optical response restores to  $T_0$  at  $\approx$ 400 ns, so the total response time is ≈430 ns. For RESET, the onset of the optical response is -18 ns, and the optical response restores to  $T_0$  at  $\approx$ 118 ns, so the total response time for RESET is  $\approx$ 136 ns. The different response times and dynamics come from the distinct physical effects responsible for SET and RESET in a memristor. When setting the memristor, carrier depletion happens first due to the reverse bias (see Figure 1b(ii)) and then carrier injection quickly follows once the CFs form. However, since the MOS capacitor is already in the carrier-depleted state at zero bias, further carrier depletion hardly gives any optical change. In fact, the slower "spike" optical response and long relaxation time observed in Figure 4a are caused by the carrier injection along with the slow thermo-optic effect after the formation of CFs, which is a typical signature of a PIN diode<sup>[31]</sup> at high current injection. The non-volatile switching is visualized by a permanent change in optical transmission after the transient effect dies out, indicated by the black dash line. On the other hand, when resetting the memristor the optical response changes almost simultaneously with the voltage pulse without any delay or relaxation due to the rapid carrier accumulation (Figure 4b). The fast response is a signature of the carrier accumulation effect where GHz speed has been measured in the MOS capacitor modulator.[16] The change of

Figure 4. Real-time optical switching response of the phase shifter. a) Dynamics of the SET operation together with the voltage pulse that triggers the switching. *T* is the transmission at the microring through port. The black dash line indicates the optical state after the transient effect dies out. The pulse conditions are 11 V, 100 ns pulse width, 8 ns trailing edge. b) Dynamics of the RESET operation and the voltage pulse that triggers the switching. The pulse conditions are -4.5 V, 100 ns pulse width, 8 ns trailing edge. A constant –2 V read bias is applied in both SET and RESET which is not shown in the figure.

dynamics from a typical carrier injection to a carrier accumulation response clearly shows that the non-volatile optical switching is caused by the memristor. It is worth noting that the filament formation in fact occurs at the onset of the voltage pulse (Figure 4a), implying that sub-nanosecond switching is possible which has been reported in electronic memristors.<sup>[32]</sup>

the oxide to cause filamentation. The *Q* factor can be improved in the future by lowering the doping concentration or increasing the bonding oxide thickness, but at the cost of increased switching voltage. Instead of doping the entire ring, we can also dope a section to reduce the loss, but the phase-tuning efficiency will be reduced.

#### 4. Conclusion

To summarize, we have demonstrated a non-volatile III-V-on-Si phase shifter with ultra-low switching energy (≈400 fJ) and fast response time (≈100 ns). The non-volatile phase shifter also has an excellent endurance of over 800 cycles or 1,600 transitions. The superior performance is made possible by the well-studied electronic memristive effects<sup>[18]</sup> that have long been explored for non-volatile storage<sup>[33]</sup> and in-memory computing.<sup>[34]</sup> Our results show that memristor can be an energy-efficient, fast, and reliable technology to realize non-volatile phase tuning in PICs. Although the current device only operates in a binary fashion, it is already sufficient to realize applications such as on-chip optical routing<sup>[35]</sup> and LiDAR<sup>[36]</sup> which only require  $\pi$  phase shifters to switch all light from one port to the other. Binary switching also simplifies the control of the CMOS circuit as no additional digitalto-analog converters (DACs) are required. We believe the device performance can be further improved by adding a transistor to implement fast current compliance during pulsing, also known as the 1T1M (1-Transistor-1-Memristor) configurations.[37] The transistor can prevent current overshoot during the high-voltage SET pulse, which is essential to reduce the possibility of device failure (see Section S4, Supporting Information). Additionally, by controlling the bias applied to the gate of the transistor, different current limits can be implemented which makes analog operation possible. [38] One can also achieve linear analog operation by adding a TaO<sub>v</sub> electro-thermal modulation layer in contact with the HfO2 which can decrease the rate of change of electric field in the CF gap region. [39] The relatively low Q factor of the ring is limited by the high silicon doping (1  $\times$  10<sup>16</sup> cm<sup>-3</sup>) across the entire ring that ensures that most electric field is dropped across

# 5. Experimental Section

Device Fabrication: The fabrication<sup>[28,40]</sup> started with a 100 mm diameter SOI substrate with 250 nm thick, lightly p-doped ( $1 \times 10^{16} \text{ cm}^{-3}$ ) top Si layer, and 1 µm thick buried oxide layer (BOX). First, a photolithography step defined the heavily doped p++ regions in Si to form an ohmic contact with the metal. The  $1 \times 10^{20}$  cm<sup>-3</sup> Boron doping level was targeted after the ion implantation process and doping activation annealing at 1050 °C. Then the process of pattern and dry etching was followed through the top Si layer to form the ring-shaped air trench for electrical and optical isolation along with vertical outgassing channels<sup>[27]</sup> that ensured proper bonding. To produce the interface HfO<sub>2</sub> for bonding, a plasma activation step in dielectric deposition was introduced. [41] Upon depositing  $\approx$  4.8 nm HfO2 on III-V and Si samples in ALD, III-V/HfO2, and Si/HfO2 samples were manually bonded together to form the heterogeneous MOS capacitor structure, followed by a 300 °C annealing step. SiO<sub>2</sub> (250 nm) was then deposited to form a hard mask. Microring patterns of 20 µm diameters were then defined by DUV photolithography and transferred down to the SiO<sub>2</sub> hard mask layer, through III-V layers, and finally into the Si layer by a selfaligned sequential dry etch process. This step with a previously patterned air trench in Si also resulted in a 1.2 μm wide Si waveguide underneath the InP (Figure 1a). Another run of photolithography and III-V dry etch were used to remove all III-V material outside the microrings. Metallization to form the terminals on n-InP and p++-Si was followed by a metal lift-off process and a rapid thermal anneal at 360 °C for 30 s. Finally, the wafer was encapsulated by 300 nm thick SiO2, followed by etching contact via all three terminals and forming thick metal probes to conclude the fabri-

Experimental Setup and Measurements: The wafer was placed on a thermally stabilized stage (at 20 °C) and optically probed with a vertical fiber setup via grating couplers defined on the wafer. The devices were electrically addressed via GSG RF probes (CascadeMicrotech ACP-40). The optical spectrum was taken by sweeping the input tunable laser (Santec TSL-510) and collecting the output using a photodetector (Newport 884-FC)

ADVANCED OPTICAL MATERIALS 21951071, 0, Downloaded from https://onlinelibrary.wiley.com/doi/10.1002/adom.202301178 by University Of Washington, Wiley Online Library on [16/102023]. See the Terms and Conditions (https://onlinelibrary.wiley.com/terms-and-conditions) on Wiley Online Library for rules of use; OA articles are governed by the applicable Creative Commons I

and power meter (Newport 2936-R). The SET and RESET pulses, both with 100 ns pulse width and 8 ns trailing edge, were applied using the HVPGU (high voltage semiconductor pulse generation unit) in the B1500A semiconductor analyzer at the maximum 1  $\mbox{M}\mbox{O}$  load impedance. After applying the pulses, the current was read with the SMU (source measurement unit) of B1500A at a bias of -0.7 V to estimate the resistance while the optical spectrum was taken using the TSL and power meter. An automated script was used to find the resonance wavelength that corresponded to transmission minima from the spectrum data. The setup schematics are shown in Section S6 (Supporting Information).

To perform the real-time optical response measurement, the phase shifter was biased at  $-2\,\mathrm{V}$  using the SMU so that carrier accumulation was induced inside the device (see Section S6, Supporting Information). The SET and RESET pulses were applied via the HVSPGU. The output from the grating couplers was amplified by an EDFA and filtered by a wavelength filter. The optical signal from the wavelength filter was detected by a 70 GHz high-speed photodiode (MACOM P-70A) and measured by an oscilloscope.

### **Supporting Information**

Supporting Information is available from the Wiley Online Library or from the author.

## **Acknowledgements**

The author would like to thank Dr. Catherine Graves and Dr. Giacomo Pedretti at HPE for their useful discussion on improving the endurance of the memristors. The author would like to thank the research group of Prof. John E. Bowers at UCSB for sharing testing instruments. Z.F. and A.M. are supported by the ONR-YIP grant.

# **Conflict of Interest**

The authors declare no conflict of interest.

#### **Author Contributions**

B.T. and D.L. conceived the projects. Z.F. led the electrical and optical measurements and wrote the script for the endurance test. B.T. prepared the setup for the experiment and helped with the measurements. A.D. helped with the tool automation and performed wafer-scale device screening. D.L. and X.H. designed and fabricated the memristor-based phase shifters. G.Z. took optical microscope images for the devices. B.T., G.Z., and A.M. supervised the overall progress of the projects. Z.F. wrote the manuscript with input from A.M. and all the authors.

#### **Data Availability Statement**

The data that support the findings of this study are available from the corresponding author upon reasonable request.

#### **Keywords**

memristor, non-volatile memory, programmable photonics, silicon photonics

Received: May 20, 2023 Revised: September 19, 2023 Published online:

- [1] J. M. Arrazola, V. Bergholm, K. Brádler, T. R. Bromley, M. J. Collins, I. Dhand, A. Fumagalli, T. Gerrits, A. Goussev, L. G. Helt, J. Hundal, T. Isacsson, R. B. Israel, J. Izaac, S. Jahangiri, R. Janik, N. Killoran, S. P. Kumar, J. Lavoie, A. E. Lita, D. H. Mahler, M. Menotti, B. Morrison, S. W. Nam, L. Neuhaus, H. Y. Qi, N. Quesada, A. Repingon, K. K. Sabapathy, M. Schuld, et al., *Nature* 2021, 591, 54.

- [2] Y. Shen, N. C. Harris, S. Skirlo, M. Prabhu, T. Baehr-Jones, M. Hochberg, X. Sun, S. Zhao, H. Larochelle, D. Englund, M. Soljacic, *Nat. Photonics* 2017, 11, 441.

- [3] W. Bogaerts, D. Pérez, J. Capmany, D. A. B. Miller, J. Poon, D. Englund, F. Morichetti, A. Melloni, *Nature* 2020, 586, 207.

- [4] G. T. Reed, G. Mashanovich, F. Y. Gardes, D. J. Thomson, Nat. Photonics 2010, 4, 518.

- [5] L. Alloatti, R. Palmer, S. Diebold, K. P. Pahl, B. Chen, R. Dinu, M. Fournier, J.-M. Fedeli, T. Zwick, W. Freude, C. Koos, J. Leuthold, *Light: Sci. Appl.* 2014, 3, e173.

- [6] M. He, M. Xu, Y. Ren, J. Jian, Z. Ruan, Y. Xu, S. Gao, S. Sun, X. Wen, L. Zhou, L. Liu, C. Guo, H. Chen, S. Yu, L. Liu, X. Cai, *Nat. Photonics* 2019, 13, 359.

- [7] M. R. Watts, J. Sun, C. Derose, D. C. Trotter, R. W. Young, G. N. Nielson, Opt. Lett. 2013, 38, 733.

- [8] C. Errando-Herranz, A. Y. Takabayashi, P. Edinger, H. Sattari, K. B. Gylfason, N. Quack, IEEE J. Sel. Top. Quantum Electron. 2020, 26, 1.

- [9] Z. Fang, R. Chen, J. Zheng, A. I. Khan, K. M. Neilson, S. J. Geiger, D. M. Callahan, M. G. Moebius, A. Saxena, M. E. Chen, C. Rios, J. Hu, E. Pop, A. Majumdar, *Nat. Nanotechnol.* 2022, 17, 1.

- [10] C. Ríos, Q. Du, Y. Zhang, C.-C. Popescu, M. Y. Shalaginov, P. Miller, C. Roberts, M. Kang, K. A. Richardson, T. Gu, S. A. Vitale, J. Hu, *PhotoniX* 2022, 3, 26.

- [11] J. Geler-Kremer, F. Eltes, P. Stark, D. Stark, D. Caimi, H. Siegwart, B. Jan Offrein, J. Fompeyrine, S. Abel, *Nat. Photonics* **2022**, *16*, 491.

- [12] Z. Fang, R. Chen, J. Zheng, A. Majumdar, IEEE J. Sel. Top. Quantum Electron. 2022, 28, 1.

- [13] P. Edinger, A. Y. Takabayashi, C. Errando-Herranz, U. Khan, C. Antony, G. Talli, P. Verheyen, W. Bogaerts, N. Quack, K. B. Gylfason, in 35th Intl. Conf. on Micro Electro Mechanical Syst. Conf. (MEMS), IEEE, New Jersey, USA 2022.

- [14] C. Hoessbacher, Y. Fedoryshyn, A. Emboras, A. Melikyan, M. Kohl, D. Hillerkuss, C. Hafner, J. Leuthold, Optica 2014, 1, 198.

- [15] A. Emboras, J. Niegemann, P. Ma, C. Haffner, A. Pedersen, M. Luisier, C. Hafner, T. Schimmel, J. Leuthold, *Nano Lett.* 2016, 16, 709.

- [16] T. Hiraki, T. Aihara, K. Hasebe, K. Takeda, T. Fujii, T. Kakitsuka, T. Tsuchizawa, H. Fukuda, S. Matsuo, Nat. Photonics 2017, 11, 482.

- [17] D. Liang, J. E. Bowers, Light: Adv. Manuf. 2021, 2, 59.

- [18] D. B. Strukov, G. S. Snider, D. R. Stewart, R. S. Williams, *Nature* **2008**,

- [19] S. Cheung, B. Tossoun, Y. Yuan, Y. Peng, G. Kurczveil, Y. Hu, X. Xian, D. Liang, R. G. Beausoleil, in Conf. on Lasers and Electro-Optics, Optica Publishing Group, WA, USA 2022.

- [20] B. Tossoun, X. Sheng, J. P. Strachan, D. Liang, R. G. Beausoleil, in Smart Photonic and Optoelectronic Integrated Circuits 2022, SPIE, WA, USA 2022.

- [21] B. Tossoun, D. Liang, S. Cheung, Z. Fang, X. Sheng, J. P. Strachan, R. G. Beausoleil, 2023, https://doi.org/10.48550/arXiv.2303.05644.

- [22] N. Margalit, C. Xiang, S. M. Bowers, A. Bjorlin, R. Blum, J. E. Bowers, Appl. Phys. Lett. 2021, 118, 220501.

- [23] X. Huang, D. Liang, C. Zhang, G. Kurczveil, X. Li, J. Zhang, M. Fiorentino, R. Beausoleil, in *IEEE Photonics Conf. (IPC)*, IEEE, New Jersey, USA 2017.

- [24] J. J. Yang, D. B. Strukov, D. R. Stewart, Nature Nanotech 2013, 8, 13.

- [25] Y. Zhang, G.-Q. Mao, X. Zhao, Y. Li, M. Zhang, Z. Wu, W. Wu, H. Sun, Y. Guo, L. Wang, X. Zhang, Q. Liu, H. Lv, K.-H. Xue, G. Xu, X. Miao, S. Long, M. Liu, *Nat. Commun.* 2021, 12, 7232.

- [26] A. Sawa, Mater. Today 2008, 11, 28.

ADVANCED OPTICAL MATERIALS 21951071, 0, Downloaded from https://onlinelibrary.wiley.com/doi/10.1002/adom.202301178 by University Of Washington, Wiley Online Library on [16/10/2023]. See the Terms

and Conditions (https:

www.advancedsciencenews.com www.advopticalmat.de

- [27] D. Liang, J. E. Bowers, J. Vacuum Sci. Technol. B: Microelectron. Nanometer Struct. Proc. 2008, 26, 1560.

- [28] D. Liang, X. Huang, G. Kurczveil, M. Fiorentino, R. G. Beausoleil, Nat. Photonics 2016, 10, 719.

- [29] M. Lanza, R. Waser, D. Ielmini, J. J. Yang, L. Goux, J. Suñe, A. J. Kenyon, A. Mehonic, S. Spiga, V. Rana, S. Wiefels, S. Menzel, I. Valov, M. A. Villena, E. Miranda, X. Jing, F. Campabadal, M. B. Gonzalez, F. Aguirre, F. Palumbo, K. Zhu, J. B. Roldan, F. M. Puglisi, L. Larcher, T.-H. Hou, T. Prodromakis, Y. Yang, P. Huang, T. Wan, Y. Chai, et al., ACS Nano 2021, 15, 17214.

- [30] H. Jiang, L. Han, P. Lin, Z. Wang, M. H. Jang, Q. Wu, M. Barnell, J. J. Yang, H. L. Xin, Q. Xia, Sci. Rep. 2016, 6, 28525.

- [31] J. Zheng, Z. Fang, C. Wu, S. Zhu, P. Xu, J. K. Doylend, S. Deshmukh, E. Pop, S. Dunham, M. Li, A. Majumdar, Adv. Mater. 2020, 32, 2001218.

- [32] A. C. Torrezan, J. P. Strachan, G. Medeiros-Ribeiro, R. S. Williams, Nanotechnology 2011, 22, 485203.

- [33] H.-S. P. Wong, H.-Y. Lee, S. Yu, Y.-S. Chen, Y. Wu, P.-S. Chen, B. Lee, F. T. Chen, M.-J. Tsai, Proc. IEEE 2012, 100, 1951.

- [34] W. Wan, R. Kubendran, C. Schaefer, S. B. Eryilmaz, W. Zhang, D. Wu, S. Deiss, P. Raina, H. Qian, B. Gao, S. Joshi, H. Wu, H.-S. P. Wong, G. Cauwenberghs, *Nature* 2022, 608, 504.

- [35] L. Lu, S. Zhao, L. Zhou, D. Li, Z. Li, M. Wang, X. Li, J. Chen, Opt. Express 2016, 24, 9295.

- [36] C. Rogers, A. Y. Piggott, D. J. Thomson, R. F. Wiser, I. E. Opris, S. A. Fortune, A. J. Compston, A. Gondarenko, F. Meng, X. Chen, G. T. Reed, R. Nicolaescu, *Nature* 2021, 590, 256.

- [37] Yang Yin Chen, B. Govoreanu, L. Goux, R. Degraeve, A. Fantini, G. S. Kar, D. J. Wouters, G. Groeseneken, J. A. Kittl, M. Jurczak, L. Altimime, IEEE Trans. Electron Devices 2012, 59, 3243.

- [38] F. Miao, W. Yi, I. Goldfarb, J. J. Yang, M.-X. Zhang, M. D. Pickett, J. P. Strachan, G. Medeiros-Ribeiro, R. S. Williams, ACS Nano 2012, 6, 2312.

- [39] W. Wu, H. Wu, B. Gao, P. Yao, X. Zhang, X. Peng, S. Yu, H. Qian, in 38th IEEE Symp. on VLSI Technology, IEEE, Honolulu, USA 2018, pp. 103–104.

- [40] D. Liang, S. Srinivasan, G. Kurczveil, B. Tossoun, S. Cheung, Y. Yuan, A. Descos, Y. Hu, Z. Huang, P. Sun, T. Van Vaerenbergh, C. Zhang, X. Zeng, S. Liu, J. E. Bowers, M. Fiorentino, R. G. Beausoleil, *IEEE J. Sel. Top. Quantum Electron.* 2022, 28, 1.

- [41] V. Chobpattana, J. Son, J. J. M. Law, R. Engel-Herbert, C.-Y. Huang, S. Stemmer, Appl. Phys. Lett. 2013, 102, 022907.