# Number of Turns Optimization for On-Chip Power Inductor Using a 3-D Physical Model

Mohammad K. Al-Smadi, *Student Member, IEEE*, Jaber A. Abu Qahouq, *Senior Member, IEEE*, and Sushma Kotru, *Senior Member, IEEE*

The University of Alabama

Department of Electrical and Computer Engineering

Tuscaloosa, Alabama 35487, USA

**Abstract**—High inductance-density with high saturation current on-chip integrated power inductors support achieving high-density integrated power conversion. To guide the design of on-chip planar power inductor, a 3-D physical model in ANSYS®/Maxwell® is developed and utilized in this paper to evaluate the effect of copper winding number of turns on two of the main power inductor performance metrics, namely the inductance value/density and the saturation current. The tradeoff between the inductance value/density and the saturation current as a function of the copper winding number of turns is evaluated using the presented physical model.

**Keywords**— *Inductance, power inductor, saturation current, physical model, turns, number of turns, 3-D model, simulation, power electronics, magnetic, miniaturization, modeling, ferrite, on-chip.*

## I. INTRODUCTION

The demand for high-performance and high-density switching power conversion is increasing in a wide range of applications such as portable electronics, energy storage and battery management systems, and electric vehicles [1-14]. Switching power electronic converters and inverters utilize magnetic components such as transformers and inductors. Generally, power inductor accounts for a large portion of the entire device/circuit size and/or volume. Therefore, with the increasing need for miniaturized power conversion, power inductor miniaturization while maintaining high performance and efficient power conversion is increasingly becoming important. On-chip and planar integrated power inductors are a promising solution to miniaturize the power conversion circuit and to realize power system in package (PSiP) and power system on chip (PSoC) [7, 9, 11, 15-17].

Both inductance value and saturation current value depend on multiple design parameters that need to be optimized to achieve a target inductor design performance metrics for a certain application. Design parameters include, but are not limited to, copper winding number of turns, air gap between copper winding and ferrite cores, ferrite core permeability, and copper winding and ferrite cores footprints and thicknesses. Utilizing magnetic ferrite materials results in improving the inductance value compared with air-core inductor [3, 18-20]. However, this comes at the expense of lowering saturation current. Achieving larger saturation current values requires using a larger size of ferrite layers [5].

To optimize the parameters and guide the design for on-chip

power inductor, 3-D physical modeling and simulation can be utilized. In this paper, the effect of number of winding turns on the inductance value or density and saturation current (two performance metrics) for a planar-structured on-chip power inductor is investigated. To guide the design, a 3-D physical model in ANSYS®/Maxwell® is developed. The tradeoff between inductance value and saturation current for a given power inductor footprint and volume as a function of the copper winding number of turns is evaluated. The 3-D physical model can be also utilized to visualize the flux density distribution for various inductor designs (i.e., with different number of turns and at different current values).

Section II presents the on-chip power inductor structure and specifications. Simulation results for on-chip power inductor with different number of turns are presented and discussed in Section III. The conclusion is given in Section IV.

## II. ON-CHIP POWER INDUCTOR STRUCTURE, MATERIAL AND SPECIFICATIONS

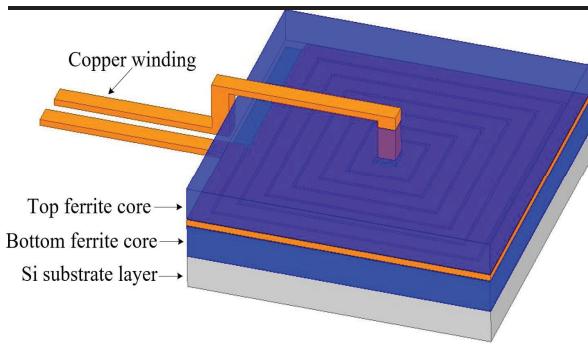

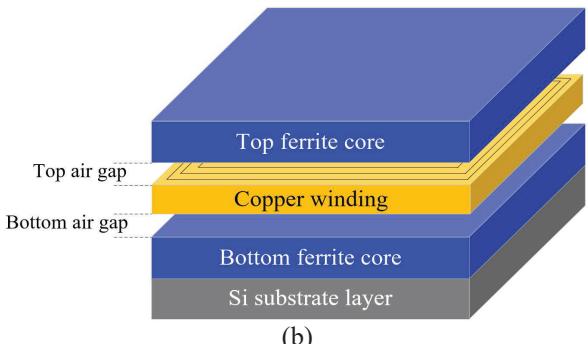

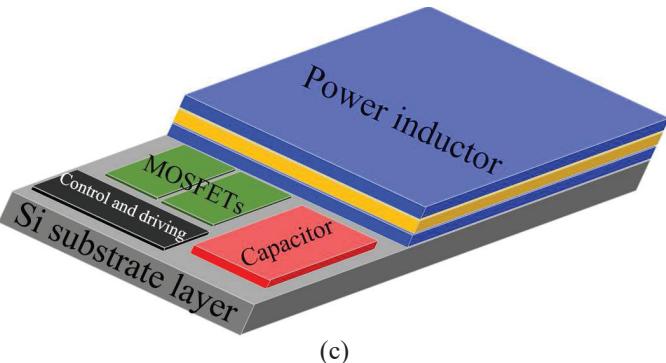

The on-chip power inductor design considered in this paper has three main different layers (integrated on a silicon wafer), namely, bottom ferrite core layer, copper winding layer, and top ferrite core layer. The structure for the on-chip power inductor is illustrated in Fig. 1. As shown, a planar structure is considered for the copper winding. In this structure, the copper winding is sandwiched between a top ferrite core layer and a bottom ferrite core layer. Fig. 1(b) illustrates how the layers are placed to construct the planar on-chip integrated power inductor. Fig. 1 (c) illustrates how an on-chip power inductor is integrated in a switching power converter (mainly includes the power inductor, capacitor, two MOSFETs, controller, and MOSFET gate driver) on Si substrate layer.

The ferrite material considered for the on-chip power inductor design is Ni-Zn type that has a permeability  $\mu$  of 100 and a saturation flux density  $B_s$  of 0.28 T. The ferrite material specifications (permeability and saturation flux density) are based on the fabrication results presented in [21]. The air gap between the top ferrite core and copper winding (top air gap in Fig. 1b) and the air gap between the bottom ferrite core and the copper winding (bottom air gap in Fig. 1b) are set to be equal. An air gap value of 10  $\mu$ m is used for both the top air gap and the bottom air gap. The effect of using different values for the top and bottom air gaps is investigated in [22]. Table I summarizes the specifications for the on-chip power inductor design.

TABLE I

Planar on-chip integrated power inductor design specifications

| Layer                        | Specifications                                                                       |

|------------------------------|--------------------------------------------------------------------------------------|

| Top and bottom ferrite cores | Material                                                                             |

|                              | Permeability $\mu$                                                                   |

|                              | Saturation flux density $B_s$                                                        |

|                              | Dimensions (Length $\times$ Width $\times$ Thickness)<br>Air gap with copper winding |

| Copper winding               | 5.2 mm $\times$ 5.2 mm $\times$ 0.525 mm<br>10 $\mu$ m                               |

|                              | Outer dimensions (Length $\times$ Width)<br>Thickness                                |

|                              | 5.2 mm $\times$ 5.2 mm<br>100 $\mu$ m                                                |

|                              | Number of turns<br>Winding width<br>Winding gap                                      |

| Varies (see Table II)        |                                                                                      |

| Varies (see Table II)        |                                                                                      |

| Varies (see Table II)        |                                                                                      |

(a)

(b)

(c)

Fig. 1. On-chip integrated power inductor structure. (a) assembled inductor (b) layer placement (c) illustration for on-chip power inductor in a switching power converter (not to scale).

TABLE II

Copper winding specifications

| Number of turns | Winding width (mm) | Winding gap (mm) |

|-----------------|--------------------|------------------|

| 3               | 0.7                | 0.05             |

| 5               | 0.4                | 0.08             |

| 7               | 0.3                | 0.05             |

| 10              | 0.2                | 0.05             |

The specifications for the copper winding are summarized in Table II. The saturation current and inductance value are investigated at different values for the number of copper winding turns (3 turns, 5 turns, 7 turns, and 10 turns). In Table II, the winding gap represents the distance between the copper winding turns. The copper winding width and gap are adjusted such that the footprint area covered by the copper winding is almost equal to the desired footprint area of the device and the top and bottom ferrite cores.

### III. 3-D PHYSICAL MODEL SIMULATION RESULTS OF THE ON-CHIP POWER INDUCTOR

Based on the specifications listed in Table I and Table II for the power inductor, a 3-D physical model in Ansys®/Maxwell® is developed and utilized to investigate the effect of winding number of turns on the inductance value and the saturation current in order to guide the design. The inductance value and the saturation current value are obtained for the on-chip power inductor for different values of number of turns. The simulation results are summarized in Table III. The overall inductor dimensions are 5.2 mm (length)  $\times$  5.2 mm (width)  $\times$  1.17 mm (height). This means that the inductor cross sectional area and volume are 27.04 mm<sup>2</sup> and 31.64 mm<sup>3</sup>, respectively. Based on the obtained inductance values, the inductance area density (H/m<sup>2</sup>) and volume density (H/m<sup>3</sup>) are calculated and summarized in Table III. The results in Table III show how the inductance value is proportional to the number of turns for this power inductor design.

TABLE III

Simulation results for on-chip power inductor with different number of turns

| Number of turns | Inductance   | Inductance density<br>nH/mm <sup>2</sup> | nH/mm <sup>3</sup> | Saturation current (A) |

|-----------------|--------------|------------------------------------------|--------------------|------------------------|

| 3               | 221.6 nH     | 8.20                                     | 7.00               | 14                     |

| 5               | 524.8 nH     | 19.41                                    | 16.59              | 9                      |

| 7               | 949.46 nH    | 35.11                                    | 30.01              | 7                      |

| 10              | 1.85 $\mu$ H | 68.42                                    | 58.47              | 5                      |

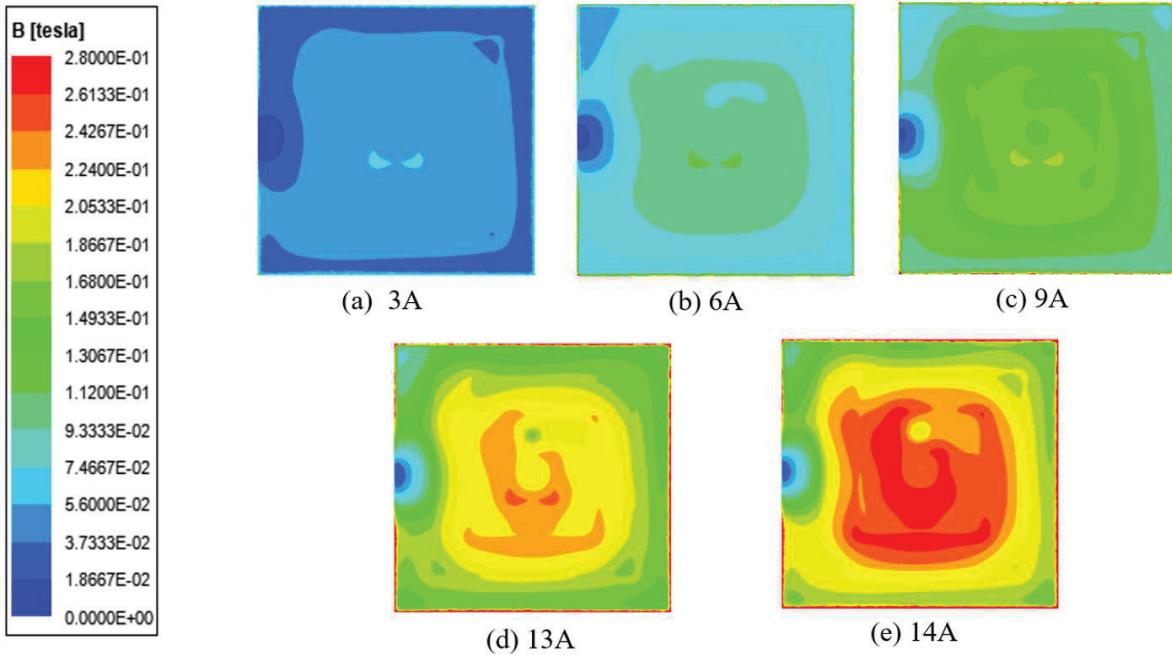

Fig. 2. Flux density  $B$  distribution of the bottom ferrite core layer for 3-turn on-chip power inductor under different DC input currents (a) 3A, (b) 6A, (c) 9A, (d) 13A, and (e) 14A.

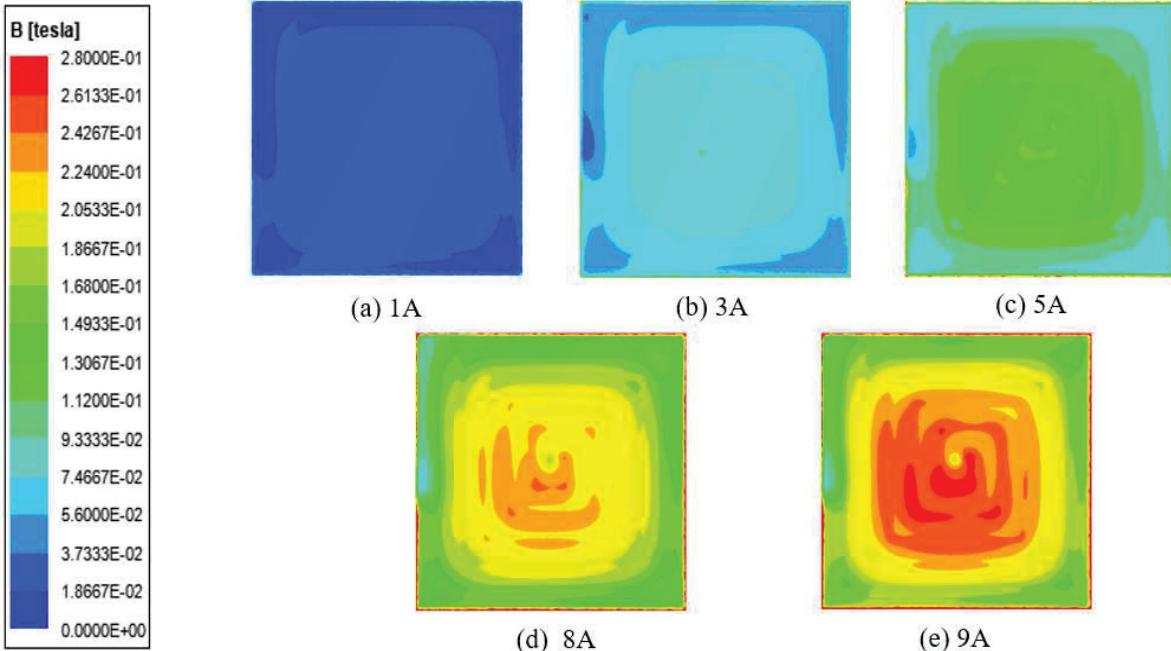

Fig. 3. Flux density  $B$  distribution of the bottom ferrite core layer for 5-turn on-chip power inductor under different DC input currents (a) 1A, (b) 3A, (c) 5A, (d) 8A, and (e) 9A.

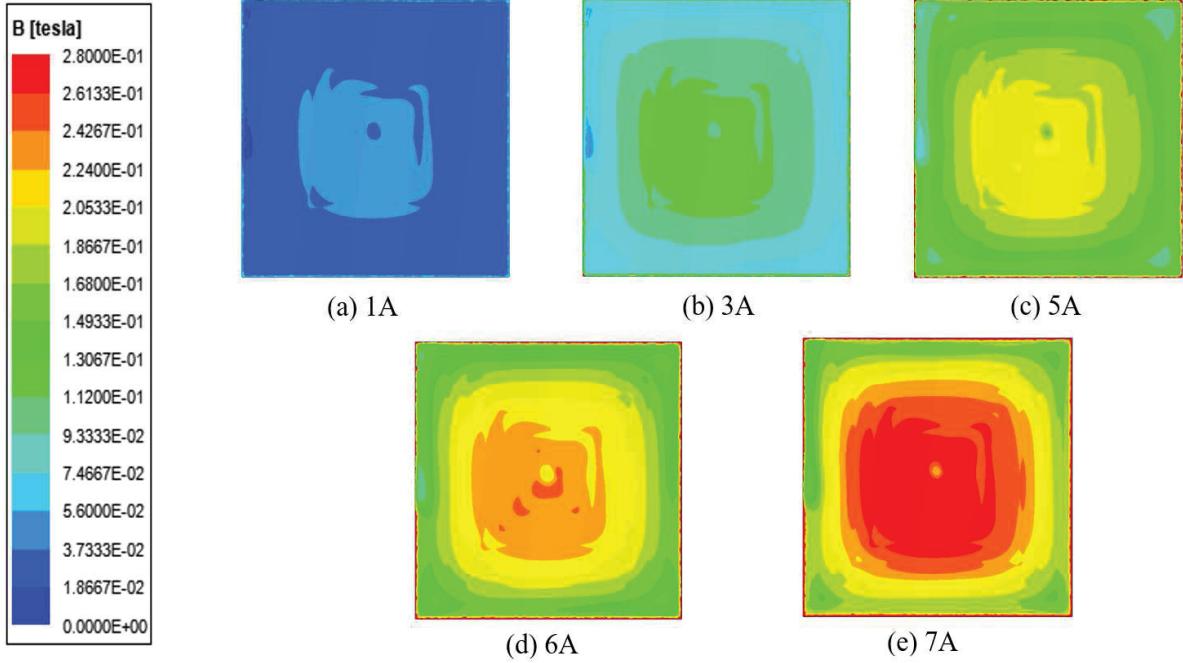

Fig. 4. Flux density  $B$  distribution of the bottom ferrite core layer for 7-turn on-chip power inductor under different DC input current values (a) 1A, (b) 3A, (c) 5A, (d) 6A, and (e) 7A.

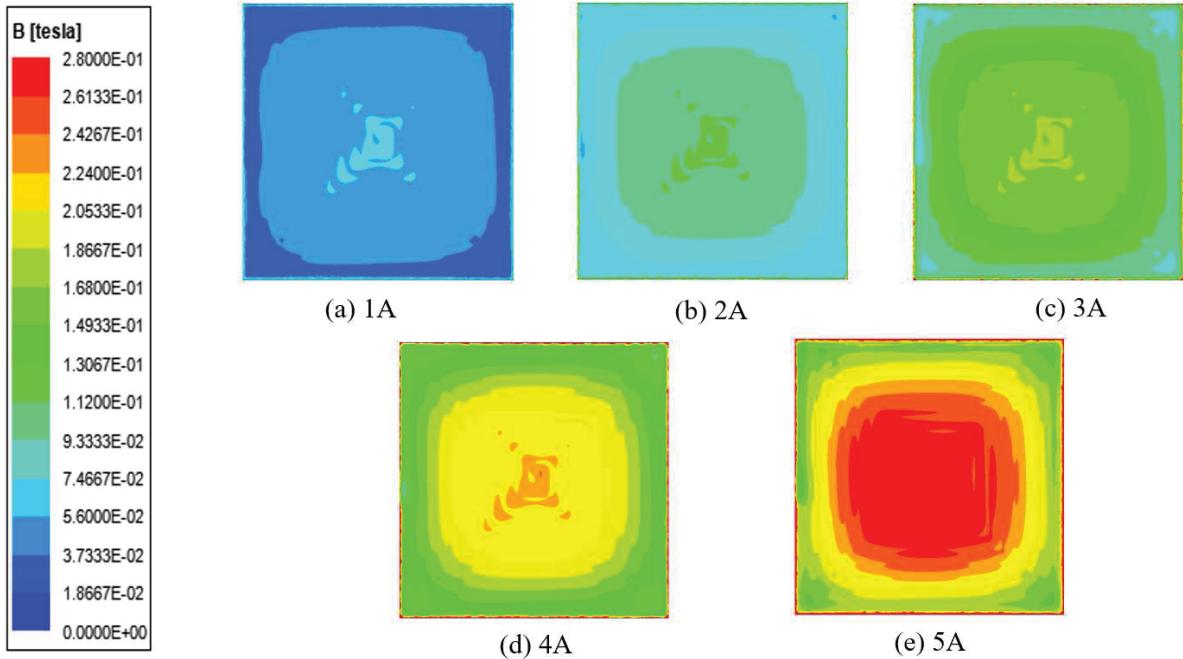

Fig. 5. Flux density  $B$  distribution of the bottom ferrite core layer for 10-turn on-chip power inductor under different DC input current values (a) 1A, (b) 2A, (c) 3A, (d) 4A, and (e) 5A.

The bottom layer's flux density  $B$  distributions for different number of turns are shown in Fig. 2, Fig. 3, Fig. 4, and Fig. 5. From Fig. 2 through Fig. 5, the flux density  $B$  of the bottom ferrite layer increases as the number of copper winding turns is increased. In Fig. 3 (e), for example, the red part indicates that the bottom ferrite is saturated at 9 A. In other words, the flux density reached the saturation value of 0.28 T. This also means that the corresponding inductor winding current (9 A) is the saturation current when the number of turns is equal to 5. In

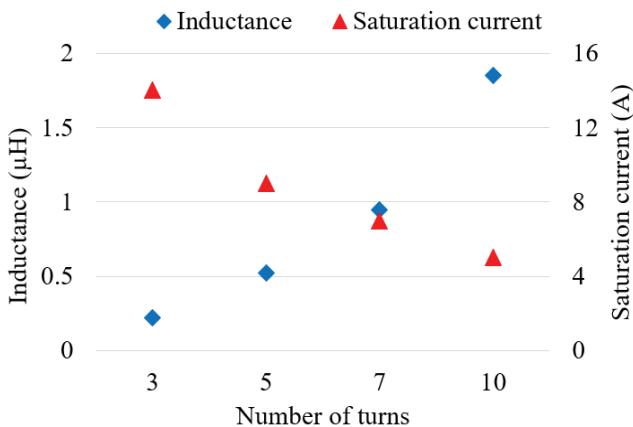

other words, the inductor's winding current is increased until the flux density is equal to 0.28 T to estimate the saturation current. The same procedure can be followed to obtain the saturation current for the inductor with different number of turns. From Fig. 2 to Fig. 5, the saturation current values are 14 A for 3 turns, 9 A for 5 turns, 7 A for 7 turns, and 5 A for 10 turns. Based on the obtained values for the inductance and the saturation current values, a tradeoff between the inductance value and the saturation current can be made when fabricating the complete

Fig. 6. Tradeoff between inductance value and saturation current value at different numbers of inductor winding turns.

device. The higher the number of turns is, the higher is the inductance value (and hence the higher are the inductance area and volume densities), and the lower is the saturation current. Fig. 6 illustrates this tradeoff using the results obtained from the simulation.

#### IV. CONCLUSION

On-chip physical modeling and simulation can be utilized to guide the design and optimize the on-chip power inductor parameters prior to the fabrication process. In this paper, the effect of number of turns of an on-chip power inductor on the inductance value and saturation current value is studied using 3-D physical model in Ansys®/Maxwell®. The tradeoff between the inductance value and the saturation current as a function of number of turns is evaluated.

#### ACKNOWLEDGEMENT

This material is based upon work supported in part by the National Science Foundation under Grant No. 1708690. Any opinions, findings and conclusions or recommendations expressed in this material are those of the author(s) and do not necessarily reflect the views of the National Science Foundation.

#### REFERENCES

- [1] M. K. Al-Smadi and J. A. Abu Qahouq, "Evaluation of Current-Mode Controller for Active Battery Cells Balancing With Peak Efficiency Operation," *IEEE Transactions on Power Electronics*, vol. 38, no. 2, pp. 1610-1621, 2023, doi: 10.1109/TPEL.2022.3211905.

- [2] M. Alimadadi, S. Sheikhaei, G. Lemieux, S. Mirabbasi, W. G. Dunford, and P. R. Palmer, "A fully integrated 660 MHz low-swing energy-recycling DC-DC converter," *IEEE Transactions on Power Electronics*, vol. 24, no. 6, pp. 1475-1485, 2009.

- [3] D. H. Bang and J. Y. Park, "Ni-Zn Ferrite Screen Printed Power Inductors for Compact DC-DC Power Converter Applications," *IEEE Transactions on Magnetics*, vol. 45, no. 6, pp. 2762-2765, 2009, doi: 10.1109/TMAG.2009.2020550.

- [4] Z. Dang, Y. Cao, and J. A. Abu Qahouq, "Reconfigurable magnetic resonance-coupled wireless power transfer system," *IEEE Transactions on Power Electronics*, vol. 30, no. 11, pp. 6057-6069, 2015.

- [5] Z. Dang and J. A. Abu Qahouq, "On-chip coupled power inductor for switching power converters," in *2014 IEEE Applied Power Electronics Conference and Exposition-APEC 2014*, 2014: IEEE, pp. 2854-2859.

- [6] Z. Dang and J. A. Abu Qahouq, "Permanent-magnet coupled power inductor for multiphase DC-DC power converters," *IEEE Transactions on Industrial Electronics*, vol. 64, no. 3, pp. 1971-1981, 2016.

- [7] T. Hashimoto, M. Shiraishi, N. Akiyama, T. Kawashima, T. Uno, and N. Matsuura, "System in package (SiP) with reduced parasitic inductance for future voltage regulator," *IEEE Transactions on Power Electronics*, vol. 24, no. 6, pp. 1547-1553, 2009.

- [8] H. Jia, J. Lu, X. Wang, K. Padmanabhan, and Z. J. Shen, "Integration of a monolithic buck converter power IC and bondwire inductors with ferrite epoxy glob cores," *IEEE transactions on Power Electronics*, vol. 26, no. 6, pp. 1627-1630, 2010.

- [9] C. O. Mathúna, N. Wang, S. Kulkarni, and S. Roy, "Review of integrated magnetics for power supply on chip (PwrSoC)," *IEEE Transactions on Power Electronics*, vol. 27, no. 11, pp. 4799-4816, 2012.

- [10] J.-W. Park and M. G. Allen, "Ultralow-profile micromachined power inductors with highly laminated Ni/Fe cores: application to low-megahertz DC-DC converters," *IEEE Transactions on magnetics*, vol. 39, no. 5, pp. 3184-3186, 2003.

- [11] J. D. Van Wyk and F. C. Lee, "On a future for power electronics," *IEEE Journal of Emerging and Selected Topics in Power Electronics*, vol. 1, no. 2, pp. 59-72, 2013.

- [12] Z. Xia and J. A. Abu Qahouq, "Ageing characterization data of lithium-ion battery with highly deteriorated state and wide range of state-of-health," *Data in Brief*, vol. 40, p. 107727, 2022/02/01/ 2022, doi: <https://doi.org/10.1016/j.dib.2021.107727>.

- [13] Z. Xia and J. A. Abu Qahouq, "Lithium-Ion Battery Ageing Behavior Pattern Characterization and State-of-Health Estimation Using Data-Driven Method," *IEEE Access*, vol. 9, pp. 98287-98304, 2021, doi: 10.1109/ACCESS.2021.3092743.

- [14] Z. Xia, J. A. Abu Qahouq, and S. Kotru, "Evaluation of Permanent Magnet Distribution Schemes for Toroid Power Inductor with Increased Saturation Current Using 3D Physical Models," in *2019 IEEE Applied Power Electronics Conference and Exposition (APEC)*, 17-21 March 2019 2019, pp. 2894-2899, doi: 10.1109/APEC.2019.8722198.

- [15] D. Disney and Z. J. Shen, "Review of silicon power semiconductor technologies for power supply on chip and power supply in package applications," *IEEE Transactions on Power Electronics*, vol. 28, no. 9, pp. 4168-4181, 2013.

- [16] S. C. Ó. Mathúna, T. O'Donnell, N. Wang, and K. Rinne, "Magnetics on silicon: An enabling technology for power supply on chip," *IEEE Transactions on Power Electronics*, vol. 20, no. 3, pp. 585-592, 2005.

- [17] F. Waldron, R. Foley, J. Slowey, A. N. Alderman, B. C. Narveson, and S. C. Ó. Mathúna, "Technology roadmapping for power supply in package (PSiP) and power supply on chip (PwrSoC)," *IEEE Transactions on Power Electronics*, vol. 28, no. 9, pp. 4137-4145, 2012.

- [18] R. Meere, N. Wang, T. O'Donnell, S. Kulkarni, S. Roy, and S. C. O'Mathuna, "Magnetic-core and air-core inductors on silicon: A performance comparison up to 100 MHz," *IEEE transactions on magnetics*, vol. 47, no. 10, pp. 4429-4432, 2011.

- [19] W. A. Roshen, "Analysis of planar sandwich inductors by current images," *IEEE Transactions on Magnetics*, vol. 26, no. 5, pp. 2880-2887, 1990.

- [20] W. A. Roshen and D. E. Turcotte, "Planar inductors on magnetic substrates," *IEEE Transactions on Magnetics*, vol. 24, no. 6, pp. 3213-3216, 1988.

- [21] Z. Hayashi, Y. Katayama, M. Edo, and H. Nishio, "High-efficiency DC-DC converter chip size module with integrated soft ferrite," *IEEE Transactions on Magnetics*, vol. 39, no. 5, pp. 3068-3072, 2003.

- [22] Z. Xia, J. A. Abu Qahouq, and S. Kotru, "3-D Physical Model for On-chip Power Inductor Design with Evaluation of Airgap Variation Effect," in *2021 IEEE Applied Power Electronics Conference and Exposition (APEC)*, 2021: IEEE, pp. 1725-1729.