# **‘Two-terminal MoS<sub>2</sub> Memristor and the Homogeneous Integration with MoS<sub>2</sub> Transistor for Neural Network**

Shuai Fu<sup>†</sup>, Ji-Hoon Park<sup>‡</sup>, Hongyan Gao<sup>†</sup>, Tianyi Zhang<sup>‡</sup>, Xiang Ji<sup>‡</sup>, Tianda Fu<sup>†</sup>, Lu Sun<sup>†</sup>, Jing Kong<sup>‡</sup>, Jun Yao<sup>†,§,⊥,\*</sup>

---

<sup>†</sup>Department of Electrical Computer and Engineering, University of Massachusetts, Amherst, MA 01003, USA.

<sup>‡</sup>Department of Electrical Engineering and Computer Science, Massachusetts Institute of Technology, Cambridge, MA 02139, USA.

<sup>§</sup>Institute for Applied Life Sciences (IALS), University of Massachusetts, Amherst, MA 01003, USA.

<sup>⊥</sup>Department of Biomedical Engineering, University of Massachusetts, Amherst, MA 01003, USA.

\* Corresponding author. Emails: [juny@umass.edu](mailto:juny@umass.edu) (J.Y.)

## ABSTRACT

Memristors are promising candidates for constructing neural networks. However, their dissimilar working mechanism to that of the addressing transistors can result in a scaling mismatch, which may hinder efficient integration. Here, we demonstrate two-terminal MoS<sub>2</sub> memristors that work with a charge-based mechanism similar to that in transistors, which enables the homogeneous integration with MoS<sub>2</sub> transistors to realize one-transistor-one-memristor addressable cells for assembling programmable network. The homogenously integrated cells are implemented in a 2×2 network array to demonstrate the enabled addressability and programmability. The potential for assembling scalable network is evaluated in a simulated neural network using obtained realistic device parameters, which achieves over 91% pattern recognition accuracy. This study also reveals a generic mechanism and strategy that can be applied to other semiconducting devices for the engineering and homogeneous integration of memristive systems.

**Keywords:** memristor, neural network, MoS<sub>2</sub>, 2D materials, transistor

## ToC Graphic

Memristors have tunable conductance that can emulate the state modulation in neural systems.<sup>1-3</sup> Computing architectures constructed from them can incorporate their state variables to yield in-memory computation, which are considered more efficient than conventional von Neumann systems.<sup>1-4</sup> Although a broad category of memristors have been discovered and studied, a typical shared challenge in implementing them for scalable integration resides in the stochastic device performance.<sup>2, 3</sup> This is attributed to a ‘destructive’ mechanism involved in many devices, in which the atomic structural rearrangement (often at local scale) associated with state change can be dispersive and irreversible,<sup>5, 6</sup> resulting in performance nonuniformity across device and time. The filamentary nature in many memristors also suggests that the programming input (*e.g.*, current) does not scale proportionally with device size,<sup>7-10</sup> as opposed to that in the associated addressing device (*e.g.*, transistor) in the architecture. This scaling mismatch presents a challenge for high-density integration because the addressing device may not shrink accordingly to provide the necessary driving current. The problem can be prominent as many existing memristors require large programming current.<sup>11-13</sup>

The nondestructive charge-based mechanism in transistors ensures the reliability and scalability, making them a mature technology.<sup>14</sup> Constructing memristive device from transistor structures can therefore harness these benefits to improve integration. Charge injection in the floating gate is often employed to tune the channel conduction for modulable states. These floating-gate transistors have been used to construct programmable computing systems, including programmable digital logics demonstrated first with semiconductor nanowires,<sup>15, 16</sup> and then two-dimensional (2D) materials.<sup>17</sup> Analog neural networks have also been proposed based on floating-gate transistors.<sup>18</sup> However, state modulation through a third gate terminal deviates from the simplicity offered by the two-terminal configuration in typical memristors, which is deemed advantageous for constructing computing network.

The feasibility of constructing a two-terminal, charge-based memristor from transistor structure was suggested from a two-terminal nonvolatile memory device made from a semiconducting carbon nanotube.<sup>19</sup> It was demonstrated that the drain voltage, besides producing an in-plane field for conduction, also yielded an out-of-plane field that pumped charge into the dielectric layer to modulate the channel conduction. The effect was also observed in graphene, although the modulation was not as large due to its lack of a bandgap.<sup>20</sup> Later developments employed 2D materials with inherent bandgap to yield a large On/Off ratio for constructing two-terminal nonvolatile memories.<sup>21</sup> However, all these studies focused on the digital state modulation in the devices. Analog conductance modulation was only recently demonstrated in a two-terminal MoS<sub>2</sub> transistor structure by using exfoliated graphene and

boron nitride as the charge trapping and tunneling layers, respectively, with the demonstration limited to single device for emulating synaptic behavior.<sup>22</sup>

Here, we demonstrate two-terminal charge-based MoS<sub>2</sub> memristors and the homogeneous integration with MoS<sub>2</sub> transistors to realize one-transistor-one-memristor (1T1R) addressable cells for assembling programmable network. The synaptic weight in the MoS<sub>2</sub> memristor can be modulated with four-bit precision against the noise level, while the MoS<sub>2</sub> transistor enables selective addressing and programming of the memristor. The 1T1R cells are implemented in a 2×2 crossbar array to demonstrate the enabled programmability. The potential for assembling scalable network is evaluated in simulated neural network using obtained realistic device parameters, which achieves a pattern recognition rate of >91%.

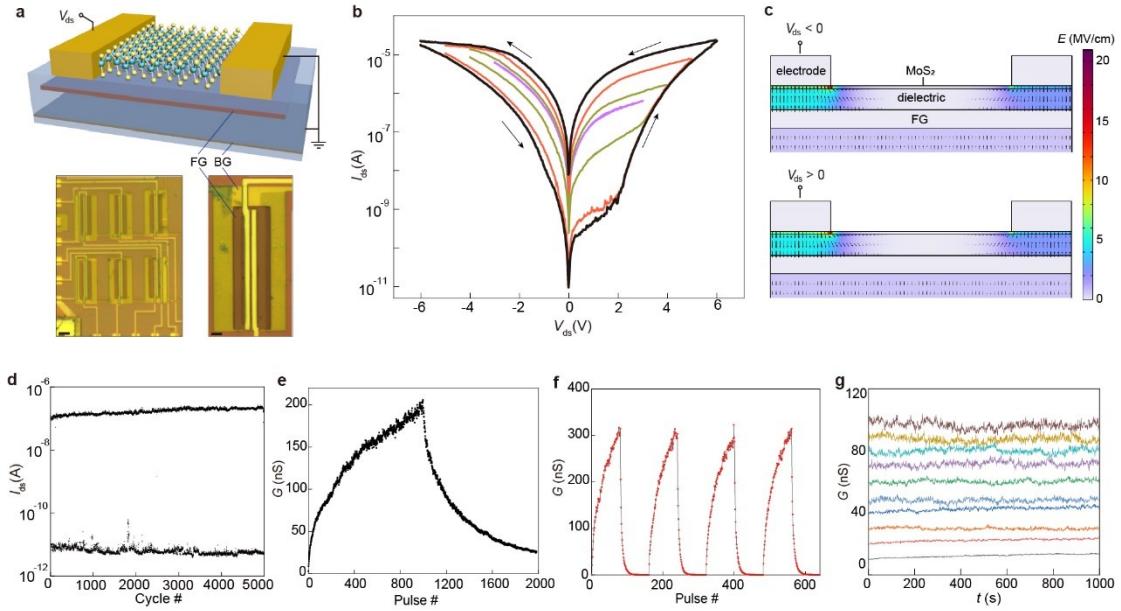

We first studied the two-terminal memristive effect in an individual MoS<sub>2</sub> transistor structure, which was fabricated from polycrystalline monolayer MoS<sub>2</sub> synthesized by the metal-organic chemical vapor deposition (MOCVD) method as described previously<sup>23</sup> (Figure 1a). The MoS<sub>2</sub> layer was contacted by a pair of source and drain electrodes, with a channel length of 1 μm and a width of 50 μm. A 5-nm Au layer, separated by a 7-nm Al<sub>2</sub>O<sub>3</sub> tunneling layer,<sup>24</sup> was defined underneath to serve as the charge-trapping layer. A bottom gate, further beneath the trapping layer and separated by a 30-nm Al<sub>2</sub>O<sub>3</sub> insulating layer, was defined as the global reference (e.g., ground).

For the two-terminal measurement, a drain voltage ( $V_{ds}$ ) was applied, with both the source and global reference grounded. In a series of current-voltage ( $I$ - $V$ ) sweeps (black curves, Figure 1b), the device changed from a high-resistance state (HRS) to a low-resistance state (LRS) during a forward voltage sweep (0→6 V). The device maintained the LRS during the backward voltage sweep (6→0 V), showing nonvolatile state modulation. The voltage sweeps in the negative region (0→-6; -6→0 V) showed an opposite trend, with the device changing from an LRS to an HRS. Together, these  $I$ - $V$  characteristics featured typical memristor behavior.

We performed following investigations to reveal the charge-based origin of the memristive effect. First, single-crystalline MoS<sub>2</sub> flake was also used to fabricate a device of the same structure, which showed  $I$ - $V$  curves with a similar memristive effect (see Supporting Information Figure S1). The result excluded the possibility of the memristive effect being caused by grain-boundary-mediated migration of defects in the polycrystalline MoS<sub>2</sub>.<sup>26, 27</sup> Second, the field distribution in the device structure was simulated, which revealed a large vertical component (~ 4.6 MV/cm) at the drain injection boundary (Figure 1c). This vertical

field component is sufficient for charge injection through the tunneling layer.<sup>28</sup> Specifically, a negative drain voltage creates an upward field that attracts electron to the trapping layer (upper panel, Figure 1c), which is expected to produce an effective negative gate effect and reduce the conduction in the *n*-type MoS<sub>2</sub> channel to produce a Reset process. Conversely, a positive drain voltage creates a downward field that depletes the electron in the trapping layer (bottom panel, Figure 1c), which is expected to increase the channel conduction to produce a Set process. These expectations were consistent with the experimental observation (Figure 1b). Reducing the amplitude of  $V_{ds}$  led to a decrease in the vertical field component (see Supporting Information Figure S2), which is expected to reduce the memristive effect. This was again consistent with the experimental results, in which the *I*-*V* hysteresis became less prominent with the decrease in the amplitude of  $V_{ds}$  (color curves, Figure 1b). Third, this generic mechanism of drain-induced charge injection was further supported by two-terminal devices fabricated from other semiconducting nanomaterials such as Si and Ge/Si nanowires<sup>15, 16, 29, 30</sup> which demonstrated a similar memristive effect (see Supporting Information Figure S3). The MoS<sub>2</sub>-based device showed a lower switching voltage than these nanowire-based devices, possibly because the 2D flat MoS<sub>2</sub>-substrate interface has better charge injection efficiency compared to the 1D nanowire-substrate contact.

Similar to other memristors, the conductance state in the MoS<sub>2</sub> device can be modulated by pulsed programming (*i.e.*,  $V_{ds}$  pulse). In a series of Set-and-Reset cycles (Figure 1d), the device showed distinct LRS and HRS. A confined distribution was observed in both the LRS and HRS, consistent with the expectation from a nondestructive charge-based mechanism that can reduce dispersity in device performance. Controlling the amount of charge injection to the trapping layer through the number of  $V_{ds}$  pulses led to the continuous modulation of the conductance states in the device (Figure 1e). The linearity in the modulation was comparable to or better than previous MoS<sub>2</sub> memristors based on ion/defect migrations<sup>26, 27, 31, 32</sup> (see Supporting Information Figure S4). This analog modulation was reversible and repeatable (Figure 1f), with the programmed states maintaining a stable value over time (Figure 1g). These results suggested that the device can be employed to function as a synaptic weight in a neural network. Note that the noise (Figure 1g) was revealed to have the 1/*f* origin (see Supporting Information Figure S5), which increases with the increase of conductance.<sup>33</sup> Nevertheless, the relative noise level remained within the range of 2%, which did not significantly affect emulated neural function to be discussed later. The noise is expected to be suppressed by reducing surface contaminates or interfacial defects.<sup>33</sup>

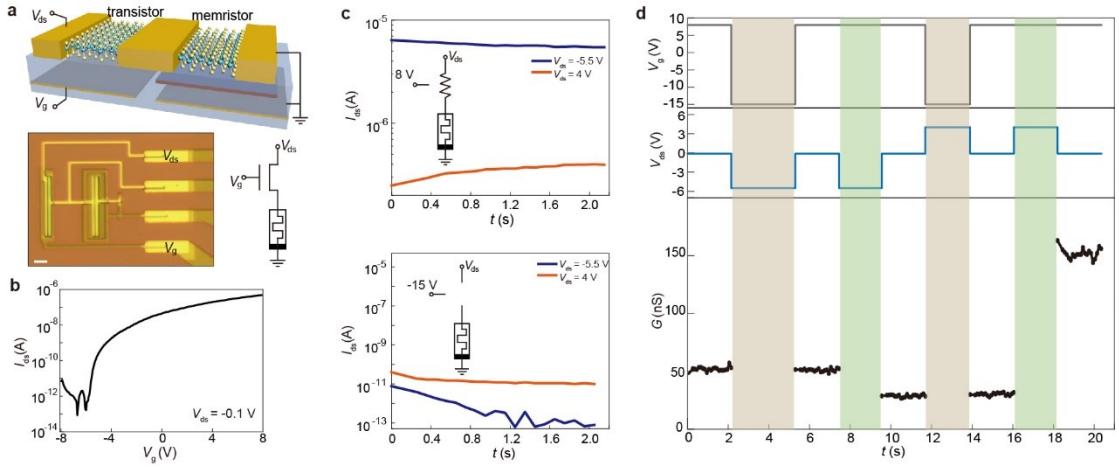

The programming current in many filamentary memristors does not scale with device size,

<sup>7-10</sup> preventing a proportionate scaling in the addressing device (e.g., transistor). The charge-based mechanism in the memristor provides an opportunity for proportionate scaling between the memristor and addressing transistor, enabling effective integration. Importantly, homogeneous integration by constructing both devices from the same material can further improve parameter matching and ease fabrication. Thus, we studied the feasibility of constructing both device elements in the 1T1R programmable cell from the same MoS<sub>2</sub> material. Specifically, we adopted similar structural parameters for the addressing MoS<sub>2</sub> transistor and MoS<sub>2</sub> memristor due to material homogeneity (Figure 2a). The constructed MoS<sub>2</sub> transistor showed typical *n*-type behavior in the current-and-gate ( $I_{ds}$ - $V_g$ ) transport curve, featuring an On/Off ratio  $>10^5$  (Figure 2b) convenient for selector function.<sup>34</sup> For selective programming in the 1T1R cell, the transistor is first turned On (e.g., with  $V_g = +8$  V) and then a Reset/Set voltage is applied to its drain. This drain voltage is expected to largely drop across the MoS<sub>2</sub> memristor if its programmable resistance range is chosen to be much larger than the On resistance in the MoS<sub>2</sub> transistor. Experimentally, an applied drain voltage of +4 V yielded a gradual current increase in the cell (orange, top panel, Figure 2c), suggesting a successful continuous Set programming in the MoS<sub>2</sub> memristor. Conversely, an applied drain voltage of -5.5 V yielded a gradual current decrease in cell (blue, top panel, Figure 2c), suggesting a successful continuous Reset programming in the MoS<sub>2</sub> memristor. Deselecting the cell by tuning Off the MoS<sub>2</sub> transistor (e.g.,  $V_g = -15$  V) yielded negligible current with applied Set/Reset voltage (bottom panel, Figure 2c), suggesting successful suppression of both current and voltage drop across the MoS<sub>2</sub> memristor to prevent its state change.

The controlled programmability in the 1T1R cell was further demonstrated in a series of pulse programming. As shown in Figure 2d, the initial conductance state  $\sim 50$  nS ( $t = 0$ -2.15 s, bottom panel) in the memristor was retrieved by turning on the transistor ( $V_g = +8$  V, top panel) and applying a read voltage of -0.1 V at the drain (middle panel). If the cell was deselected by turning off the MoS<sub>2</sub> transistor ( $V_g = -15$  V), an applied Reset voltage of -5.5 V at the drain ( $t = 2.15$ -5.3 s) did not alter the state in the memristor ( $t = 5.3$ -7.45 s). If the cell was selected by turning on the transistor ( $V_g = +8$  V), then a Reset voltage of -5.5 V applied at the drain ( $t = 7.45$ -9.55 s) reduced the conductance in the memristor to  $\sim 30$  nS ( $t = 9.55$ -11.7 s). Similarly, if the cell was unselected, an applied Set voltage of 4 V ( $t = 11.7$ -13.9 s) could not alter the memristor state ( $t = 13.9$ -16.05 s). If the cell was selected, then the same applied Set voltage ( $t = 16.05$ -18.2 s) increased the conductance in the memristor to  $\sim 150$  nS ( $t = 18.2$ -20.35 s). These results show that the MoS<sub>2</sub>-based homogeneous 1T1R structure can serve as an addressable cell for constructing a programmable network.

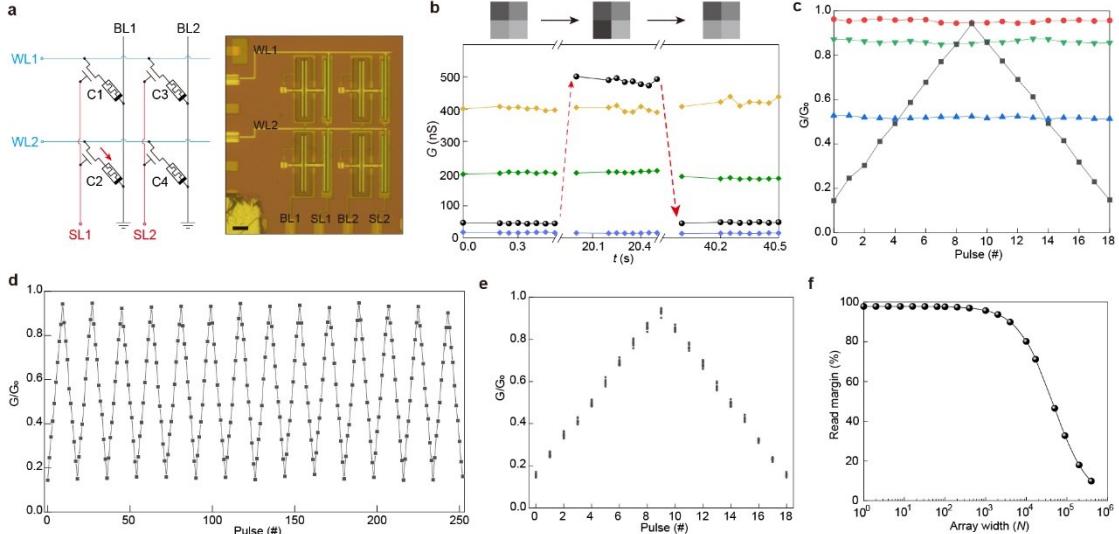

We then implemented the cells in a crossbar array to evaluate the selective programmability for network applications. Since the sneak paths in a crossbar array are essentially composed of  $2 \times 2$  paths,<sup>35</sup> we studied the feasibility in a  $2 \times 2$  array without losing generality (Figure 3a). The array shared the same structure as existing 1T1R memristor network,<sup>34</sup> in which the shared drain input in the row, shared source input in the column, and shared gate control of the transistors (selectors) served as the word line (WL), bit line (BL), and selection line (SL), respectively. For selective programming/reading (e.g., in cell C2), a gate voltage (+8 V) is applied to SL1 to turn on the selectors along the line, and a gate voltage (-15 V) is applied to the remaining SL2 to turn off the selectors along the line. A programming/reading voltage is applied to WL2 with WL1 floating. For the selected cell C2, the operation is expected to be the same as demonstrated in individual cell (Figure 2). The WL2 input is expected to have no effect on C4 since it is deselected, whereas the floating input from WL1 also ensures that C1 and C3 are not programmed/read. The 1T1R addressing scheme described above can be extended to larger array sizes, ensuring that all non-target cells are either deselected or unbiased. This is different from a neural network constructed using the three-terminal Flash memory architecture,<sup>36</sup> in which the Reset programming involves erasing the entire column and rewriting all other cells in that column.

The testing results were consistent with the above analysis. The conductance of the selected C2 cell was changed from  $\sim 50$  nS to  $\sim 500$  nS (black curve, Figure 3b) by applying Set programming pulses of +4 V to WL2 with SL1 selected (+8 V). The conductance states in the remaining cells (color curves) remained unchanged during the process. Similarly, the conductance of the selected C2 cell was changed from  $\sim 500$  nS to  $\sim 50$  nS by applying Reset programming pulses of -5.5 V to WL2 with SL1 selected (+8 V), without altering the states in the remaining cells. These results demonstrate the addressable and reversible programmability that is key to weight update in a neural network. Furthermore, the conductance state in the selected cell can be continuously modulated by the number/width of programming pulses to control the cumulative charge injection in the trapping layer. A 10-state reversible programming in the selected C2 cell was readily achieved with the control of Set/Reset pulses (black curve, Figure 3c). The states in the unselected cells remained unchanged throughout the process (color curves). The state modulation in the selected cell was repeatable (Figure 3d), with each of the programmed states highly converged (Figure 3e). These results show the reliability in the addressing strategy for selective and continuous weight update. Smaller updates with more state levels are possible by using reduced pulse width (Figure 1e). The selective programming in the  $2 \times 2$  array validates that the homogeneous 1T1R MoS<sub>2</sub> cells can be implemented in scalable arrays for programmable networks. The excellent selection ratio in the MoS<sub>2</sub> transistor suggests

that the width ( $N$ ) in a  $N \times N$  array can be scaled to  $>10^5$  to maintain a read margin  $>20\%$  (Figure 3f; see detailed analysis in Supporting Information Figure S6).

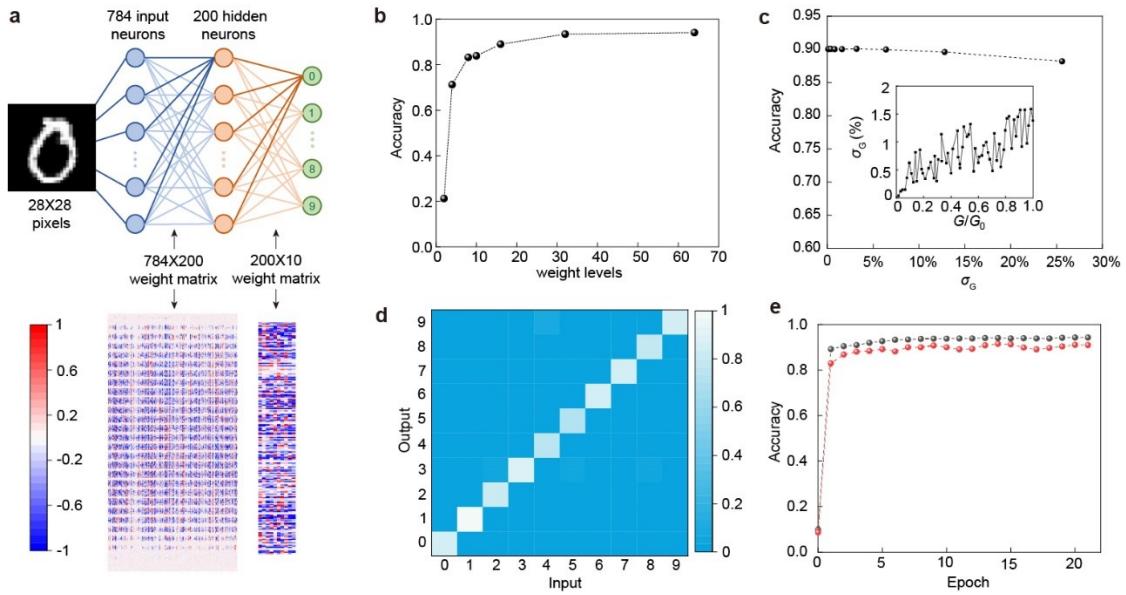

We therefore evaluated the potential of implementing the 1T1R cells in a network for a realistic task (*e.g.*, handwritten digit recognition) based on the revealed device performance. Handwritten digits were obtained from the modified National Institute of Standards and Technology (MNIST) database and were normalized within a  $28 \times 28$  pixel bounding box. A three-layer neural network was employed for the task, consisting of a layer of 784 input neurons (*e.g.*, corresponding to the  $28 \times 28$  input pixel number), a layer of 200 hidden neurons, and a layer of 10 output neurons (top, Figure 4a; see detailed procedure in Supporting Information Figure S7). The synaptic weight matrices were constructed from simulated arrays of  $784 \times 200$  and  $200 \times 10$  MoS<sub>2</sub> 1T1R cells (bottom, Figure 4a). A set of 5000 randomly selected images from the MNIST database was used for training<sup>37</sup> (*e.g.*, an epoch), and a set of 1000 randomly selected images was used for recognition testing.

The weight precision (*i.e.*, state levels in the cell) is expected to affect the recognition accuracy. Our simulation showed that the accuracy increased with the increase of the number of available weight levels in the cell. An accuracy  $>90\%$  was achieved with 16-level or four-bit state modulation in the cell (Figure 4b), which was readily attainable in the MoS<sub>2</sub> memristor (Figure 1e). To get a close representation of realistic situation, noise in the weight was further added. The noise<sup>38</sup> in 64 programmed weight levels from the MoS<sub>2</sub> memristor was measured, showing a dominant distribution within 1.5% (inset, Figure 4c). Noise was randomly added to the 16-state network. The network showed robustness again noise, with a recognition accuracy  $>88\%$  maintained at a noise level of 25% (Figure 4c). The accuracy increased to  $>91\%$  within the noise level of 1.5%, which covered the dominant noise levels in the MoS<sub>2</sub> memristor (inset). Specifically, the network with a 4-bit weight precision and 1.5% noise, corresponding to realistic MoS<sub>2</sub> device performance, showed consistent accuracy for the individual recognitions of the 10 digits (Figure 4d). The overall accuracy was only  $\sim 3\%$  lower compared to an ideal network that had arbitrary weight precision without noise (Figure 4e). These results show the potential of implementing MoS<sub>2</sub> 1T1R cells in realistic neural networks.

The recent development of ultralow contact resistance in MoS<sub>2</sub> devices has expanded the potential for device scaling.<sup>39</sup> The shared transport mechanism and electronic parameters in the MoS<sub>2</sub> transistor and memristor suggest that they can be proportionately scaled in the homogeneous 1T1R integration, if an effective selection (*e.g.*, On/Off ratio) in the transistor and charge trapping in the memristor are retained. To demonstrate the potential, we fabricated

a 1T1R cell in which both the memristor and transistor were reduced to a size of  $1 \times 0.2 \mu\text{m}^2$ . Both devices maintained good performance, enabling selective programming in the 1T1R cell (see Supporting Information Figure S8). Furthermore, recent experimental and simulation studies have showed that both transistor performance and charge-trapping memory effect are retained even when the  $\text{MoS}_2$  channel length is reduced to below 50 nm.<sup>18, 40, 41</sup> These studies indicate that the effective size of the homogeneously integrated 1T1R  $\text{MoS}_2$  cell can be scaled down to sub-100 nm size, which is smaller than existing heterogeneous 1T1R cells with sizes beyond the micrometer scale due to mismatched scaling.<sup>12, 42</sup> Meanwhile, the Off resistance in the transistor/selector determines the sneak-path current level, which also means that its ratio to the upper-bound resistance in the  $\text{MoS}_2$  memristor will affect the scalability.<sup>35</sup> Taking these values from sub-50 nm  $\text{MoS}_2$  transistors in a previous study,<sup>41</sup> our estimate shows that the width ( $N$ ) in an integrated  $N \times N$  array can be over  $10^4$  (see Supporting Information Figure S9), which is larger than existing ones and sufficient for various functions. Improving the  $\text{MoS}_2$  material quality and device engineering, which are of common interest in the field, is expected to improve the potential of 1T1R integration. The two-terminal  $\text{MoS}_2$  memristors also enable the feasibility of integration with two-terminal selectors,<sup>34</sup> including homogeneous  $\text{MoS}_2$ -based selectors,<sup>43</sup> for a simplified crossbar architecture.

Our study also suggests a generic mechanism that can be applied to other semiconducting materials to engineer two-terminal charge-based memristors and enable homogeneous 1T1R integration. This approach has the potential to create a broad category of neuromorphic systems. It is likely that this strategy can be applied to silicon technology for expedited development, because it offers the maturity and well-controlled interface that are crucial for ensuring reliability and uniformity at a large scale for array integration.

## Supporting Information

The Supporting Information is available free of charge at xxx Materials and Methods; Supporting Figures S1-S9 describe additional single-crystalline device performance, field simulation, nanowire device performance, linearity analysis, noise analysis, read margin calculation, neural network emulation, device scaling, and read margin simulation, respectively.

## Author contributions

J.Y. and S.F. conceived the project and designed experiments. S.F. carried out experimental studies in device and circuit fabrication and measurement. J.H.P synthesized the polycrystalline  $\text{MoS}_2$ . T.Z. and J.X. synthesized the single-crystalline  $\text{MoS}_2$ . J.K. oversaw the 2D material production. H.G. helped the fabrication of nanowire devices. T.F. helped the simulation. L.S. helped electrical

measurement. J.Y. and S.F. wrote the manuscript. All authors discussed the results and implications and commented on the manuscript.

### Notes

The authors declare no competing interest.

### Acknowledgements

J.Y. acknowledges the support from National Science Foundation (NSF) DMR-2027102, CBET-1844904, Army Research Office (ARO) W911NF2210027, and Office of Naval Research (ONR) N00014-21-1-2593. J.-H.P., X.J and J.K acknowledge the support from the ARO MURI project under grant number W911NF-18-1-04320431 and the US Army Research Office through the Institute for Soldier Nanotechnologies at MIT, under cooperative agreement no. W911NF-18-2-0048. T.Z. and J.K. acknowledge the support by the U.S. Department of Energy (DOE), Office of Science, Basic Energy Sciences (BES) under award DE-SC0020042 for the synthesis of MoS<sub>2</sub> using CVD method.

## Figure Legends

**Figure 1. Two-terminal memristive effect in MoS<sub>2</sub> device.** **a,** (Top) Schematic of the MoS<sub>2</sub> device structure, in which a floating gate (FG) is defined underneath the MoS<sub>2</sub> channel and a back gate (BG) serving as the global reference is grounded. The bottom panel shows optical images of fabricated MoS<sub>2</sub> device array (left) and an individual device (right). Scale bars, 20  $\mu$ m (left) and 5  $\mu$ m (right). **b,** A series of two-terminal  $I$ - $V$  sweeps in a MoS<sub>2</sub> device, showing drain voltage ( $V_{ds}$ )-dependent hysteresis. **c,** Simulated electric field distribution in the MoS<sub>2</sub> device with  $V_{ds} = -6$  V (top) and  $V_{ds} = 6$  V (bottom). Note that here a 60-nm channel length was used for better display. The simulation showed that the field distribution at the drain region was very close between a 60-nm channel and a 1- $\mu$ m channel. **d,** Programming cycles in the MoS<sub>2</sub> device. A  $\pm 7$  V pulse (5 s) was applied to the drain to program the On/Off state and a -0.1 V was used to read the conductance in each cycle. **e,** Analog conductance modulation by continuously applying 1000 Set pulses (3 V, 60 ms) and 1000 Reset pulses (-6 V, 60 ms) at the drain. The conductance was read out after each programming pulse by -0.1 V. **f,** Repeated analog programming cycles. Each cycle involved 80 Set pulses (3.5 V, 60 ms) and 80 Reset pulses (-6.5 V, 60 ms), with the conductance read out by -0.1 V right after each programming pulse. **g,** Retention in 10 programmed states continuously monitored with -0.1 V.

**Figure 2. Homogeneous integration.** **a**, (Top) Schematic of the homogeneous 1T1R cell integrated from a MoS<sub>2</sub> transistor and a MoS<sub>2</sub> memristor, with the corresponding circuit diagram (bottom right) and the optical image of a fabricated cell (bottom left). Scale bar, 20  $\mu$ m. Note that in the fabricated cell, an addressing electrode was added between the transistor and memristor for the convenience of testing each device separately. **b**, A representative transport curve in the MoS<sub>2</sub> transistor, showing typical *n*-type behavior. **c**, (Top) In a selected cell (transistor On, represented by an equivalent resistor in the Inset), the current gradually increased (orange) and decreased (blue) with applied  $V_{ds}$  of 4 V and -5.5 V, respectively. (Bottom) In the deselected cell (transistor Off, represented by an open circuit in the Inset), the current remained negligible with applied  $V_{ds}$ . The insets show the corresponding equivalent circuits. **d**, Demonstration of selective Set and Reset programming in the cell.

**Figure 3. 2x2 array integration.** **a**, (Left) Circuit diagram of 1T1R-based 2x2 addressable array. (Right) Optical image of a fabricated 2x2 array constructed from MoS<sub>2</sub> 1T1R cells. Scale bar, 20  $\mu$ m. **b**, Selective programming of cell 2 (C2) in the array from the conductance of 50 nS to 500 nS and then back to 50 nS (black curves), with the conductance in the rest cells unchanged (color curves). **c**, The conductance in the selected C2 cell (black dots) was set to 10 increasing levels and then reset to 10 decreasing levels (between 70 – 480 nS). The increasing levels were programmed a series of Set (4 V) pulses of 0.2, 0.4, 0.4, 0.8, 1, 1.2, 1.8, 1.8, and 1.8 s, respectively. The decreasing levels were programmed by a series of Reset (-5.3) pulses of 0.1, 0.1, 0.2, 0.4, 0.6, 1, 2.6, 4.4, and 8.6 s, respectively. Due to the tunneling nature (e.g., injection current has exponential increase with the voltage), much faster programming is possible by using larger voltages.<sup>22</sup> The conductance in the rest cells was unchanged (color dots) during the process. **d**, Repeated programming in the same cell using the same parameters in (c). **e**, The distribution in each of the 10 conductance levels during the repeated programming in (d). **f**, Simulated read margin with respect to the array width ( $N$ ) based on performance parameters in the MoS<sub>2</sub> memristor and transistor (1  $\mu$ m channel length and 50  $\mu$ m channel width).

**Figure 4. Simulated neural network based on MoS<sub>2</sub> 1T1R cells.** **a**, (Top) Structure of a 3-layer neural network for digit recognition, with the weight matrices constructed from two 1T1R crossbar arrays. The bottom panel shows an exemplary set of (4-bit) weight matrices from a trained network. **b**, Recognition rate or accuracy with respect to the available states (weight levels) in each cell in the simulated network. **c**, Recognition accuracy with respect to added noise in the network with 4-bit weight precision (*i.e.*, 16 available states in each cell). The inset shows the actual measured noise  $\sigma_G$  (defined as the standard deviation of the relative conductance fluctuation)<sup>38</sup> in 64 programmed states from a MoS<sub>2</sub> memristor. **d**, Recognition accuracy for each digit using the network of 4-bit weight precision and 1.5% added noise. **e**, Comparison of the recognition accuracy between a realistic network of 4-bit weight precision and 1.5% added noise (red dots) and an ideal one with arbitrary weight precision and no noise (black dots).

## References

1. Zidan, M. A.; Strachan, J. P.; Lu, W. D. The future of electronics based on memristive systems. *Nat Electron* **2018**, *1*, 22-29.

2. Xia, Q. F.; Yang, J. J. Memristive crossbar arrays for brain-inspired computing. *Nat Mater* **2019**, *18*, 309-323.

3. Wang, Z. R.; Wu, H. Q.; Burr, G. W.; Hwang, C. S.; Wang, K. L.; Xia, Q. F.; Yang, J. J. Resistive switching materials for information processing. *Nat Rev Mater* **2020**, *5*, 173-195.

4. Sebastian, A.; Le Gallo, M.; Khaddam-Aljameh, R.; Eleftheriou, E. Memory devices and applications for in-memory computing. *Nat Nanotechnol* **2020**, *15*, 529-544.

5. Sun, W.; Gao, B.; Chi, M. F.; Xia, Q. F.; Yang, J. J.; Qian, H.; Wu, H. Q. Understanding memristive switching via in situ characterization and device modeling. *Nat Commun* **2019**, *10*, 3453.

6. Chen, B.; Lu, Y.; Gao, B.; Fu, Y. H.; Zhang, F. F.; Huang, P.; Chen, Y. S.; Liu, L. F.; Liu, X. Y.; Kang, J. F.; Wang, Y. Y.; Fang, Z.; Yu, H. Y.; Li, X.; Wang, X. P.; Singh, N.; Lo, G. Q.; Kwong, D. L. Physical mechanisms of endurance degradation in TMO-RRAM. *2011 IEEE International Electron Devices Meeting (IEDM)* **2011**, 12.3.1-12.3.4.

7. Yao, J.; Zhong, L.; Natelson, D.; Tour, J. M. In situ imaging of the conducting filament in a silicon oxide resistive switch. *Sci Rep* **2012**, *2*, 242.

8. Kwon, D. H.; Kim, K. M.; Jang, J. H.; Jeon, J. M.; Lee, M. H.; Kim, G. H.; Li, X. S.; Park, G. S.;

Lee, B.; Han, S.; Kim, M.; Hwang, C. S. Atomic structure of conducting nanofilaments in TiO<sub>2</sub> resistive switching memory. *Nat Nanotechnol* **2010**, *5*, 148-153.

9. Fu, T. D.; Liu, X. M.; Gao, H. Y.; Ward, J. E.; Liu, X. R.; Yin, B.; Wang, Z. R.; Zhuo, Y.; Walker, D. J. F.; Yang, J. J.; Chen, J. H.; Lovley, D. R.; Yao, J. Bioinspired bio-voltage memristors. *Nat Commun* **2020**, *11*, 1861.

10. Fu, T. D.; Fu, S.; Yao, J. Recent progress in bio-voltage memristors working with ultralow voltage of biological amplitude. *Nanoscale* **2023**, *15*, 4669-4681.

11. Jiang, H.; Han, L. L.; Lin, P.; Wang, Z. R.; Jang, M. H.; Wu, Q.; Barnell, M.; Yang, J. J. H.; Xin, H. L. L.; Xia, Q. F. Sub-10 nm Ta channel responsible for superior performance of a HfO<sub>2</sub> memristor. *Sci Rep* **2016**, *6*, 28525.

12. Wang, R.; Shi, T.; Zhang, X. M.; Wei, J. S.; Lu, J.; Zhu, J. X.; Wu, Z. H.; Liu, Q.; Liu, M. Implementing in-situ self-organizing maps with memristor crossbar arrays for data mining and optimization. *Nat Commun* **2022**, *13*, 2289.

13. Prezioso, M.; Merrikh-Bayat, F.; Hoskins, B. D.; Adam, G. C.; Likharev, K. K.; Strukov, D. B. Training and operation of an integrated neuromorphic network based on metal-oxide memristors. *Nature* **2015**, *521*, 61-64.

14. Kim, S. K.; Popovici, M. Future of dynamic random-access memory as main memory. *MRS Bull* **2018**, *43*, 334-339.

15. Yan, H.; Choe, H. S.; Nam, S. W.; Hu, Y. J.; Das, S.; Klemic, J. F.; Ellenbogen, J. C.; Lieber, C. M. Programmable nanowire circuits for nanoprocessors. *Nature* **2011**, *470*, 240-244.

16. Yao, J.; Yan, H.; Das, S.; Klemic, J. F.; Ellenbogen, J. C.; Lieber, C. M. Nanowire nanocomputer as a finite-state machine. *Proc Natl Acad Sci USA* **2014**, *111*, 2431-2435.

17. Marega, G. M.; Zhao, Y. F.; Avsar, A.; Wang, Z. Y.; Tripathi, M.; Radenovic, A.; Kis, A. Logic-in-memory based on an atomically thin semiconductor. *Nature* **2020**, *587*, 72-77.

18. Marega, G. M.; Wang, Z. Y.; Paliy, M.; Giusi, G.; Strangio, S.; Castiglione, F.; Callegari, C.; Tripathi, M.; Radenovic, A.; Iannaccone, G.; Kis, A. Low-power artificial neural network perceptron based on monolayer MoS<sub>2</sub>. *ACS Nano* **2022**, *16*, 3684-3694.

19. Yao, J.; Jin, Z.; Zhong, L.; Natelson, D.; Tour, J. M. Two-terminal nonvolatile memories based on single-walled carbon nanotubes. *ACS Nano* **2009**, *3*, 4122-4126.

20. Yao, J. Resistive switching and memory effects in silicon oxide based nanostructures. PhD Thesis, Rice University, pp. 171-173; Houston, Texas, Aug. 2011.

21. Vu, Q. A.; Shin, Y. S.; Kim, Y. R.; Nguyen, V. L.; Kang, W. T.; Kim, H.; Luong, D. H.; Lee, I. M.; Lee, K.; Ko, D. S.; Heo, J.; Park, S.; Lee, Y. H.; Yu, W. J. Two-terminal floating-gate memory with van der Waals heterostructures for ultrahigh on/off ratio. *Nat Commun* **2016**, *7*, 12725.

22. Tang, J.; He, C. L.; Tang, J. S.; Yue, K.; Zhang, Q. T.; Liu, Y. Z.; Wang, Q. Q.; Wang, S. P.; Li, N.; Shen, C.; Zhao, Y. C.; Liu, J. Y.; Yuan, J. H.; Wei, Z.; Li, J. W.; Watanabe, K.; Taniguchi, T.; Shang, D. S.; Wang, S. G.; Yang, W.; Yang, R.; Shi, D. X.; Zhang, G. Y. A reliable all-2D materials artificial synapse for high energy-efficient neuromorphic computing. *Adv Funct Mater* **2021**, *31*, 2022083.

23. Park, J. H.; Lu, A. Y.; Shen, P. C.; Shin, B. G.; Wang, H. Z.; Mao, N. N.; Xu, R. J.; Jung, S. J.; Ham, D.; Kern, K.; Han, Y. M.; Kong, J. Synthesis of high-performance monolayer molybdenum disulfide at low temperature. *Small Methods* **2021**, *5*, 2000720.

24. Yeom, D.; Kang, J.; Lee, M.; Jang, J.; Yun, J.; Jeong, D. Y.; Yoon, C.; Koo, J.; Kim, S. ZnO nanowire-based nano-floating gate memory with Pt nanocrystals embedded in Al<sub>2</sub>O<sub>3</sub> gate oxides. *Nanotechnology* **2008**, *19*, 395204.

25. Li, J. Y.; Zhang, H.; Ding, Y.; Li, J. Y.; Wang, S. Y.; Zhang, D. W.; Zhou, P. A non-volatile AND gate based on  $\text{Al}_2\text{O}_3/\text{HfO}_2/\text{Al}_2\text{O}_3$  charge-trap stack for in-situ storage applications. *Sci Bull* **2019**, *64*, 1518-1524.

26. Sangwan, V. K.; Lee, H. S.; Bergeron, H.; Balla, I.; Beck, M. E.; Chen, K. S.; Hersam, M. C. Multi-terminal memristors from polycrystalline monolayer molybdenum disulfide. *Nature* **2018**, *554*, 500-504.

27. Li, D.; Wu, B.; Zhu, X. J.; Wang, J. T.; Ryu, B.; Lu, W. D.; Lu, W.; Liang, X. G.  $\text{MoS}_2$  memristors exhibiting variable switching characteristics toward biorealistic synaptic emulation. *ACS Nano* **2018**, *12*, 9240-9252.

28. Fry-Bouriaux, L.; Rosamond, M. C.; Williams, D. A.; Davies, A. G.; Walti, C. Field-enhanced direct tunneling in ultrathin atomic-layer-deposition-grown  $\text{Au-Al}_2\text{O}_3\text{-Cr}$  metal-insulator-metal structures. *Phys Rev B* **2017**, *96*, 115435.

29. Gao, H. Y.; Yin, B.; Wu, S. Y.; Liu, X. M.; Fu, T. D.; Zhang, C.; Lin, J.; Yao, J. Deterministic assembly of three-dimensional suspended nanowire structures. *Nano Lett* **2019**, *19*, 5647-5652.

30. Gao, H. Y.; Yang, F. Y.; Sattari, K.; Du, X.; Fu, T. D.; Fu, S.; Liu, X. M.; Lin, J.; Sun, Y. B.; Yao, J. Bioinspired two-in-one nanotransistor sensor for the simultaneous measurements of electrical and mechanical cellular responses. *Sci Adv* **2022**, *8*, eabn2485.

31. Zhu, X. J.; Li, D.; Liang, X. G.; Lu, W. D. Ionic modulation and ionic coupling effects in  $\text{MoS}_2$  devices for neuromorphic computing. *Nat Mater* **2019**, *18*, 141-148.

32. Feng, X. W.; Li, S. F.; Wong, S. L.; Tong, S. W.; Chen, L.; Zhang, P. P.; Wang, L. F.; Fong, X. Y.; Chi, D. Z.; Ang, K. W. Self-selective multi-terminal memristor crossbar array for in-memory computing. *ACS Nano* **2021**, *15*, 1764-1774.

33. Sangwan, V. K.; Arnold, H. N.; Jariwala, D.; Marks, T. J.; Lauhon, L. J.; Hersam, M. C. Low-frequency electronic noise in single-layer  $\text{MoS}_2$  transistors. *Nano Lett* **2013**, *13*, 4351-4355.

34. Shi, L. Y.; Zheng, G. H.; Tian, B. B.; Dkhil, B.; Duan, C. G. Research progress on solutions to the sneak path issue in memristor crossbar arrays. *Nanoscale Adv* **2020**, *2*, 1811-1827.

35. Fu, T. D.; Fu, S.; Sun, L.; Gao, H. Y.; Yao, J. An effective sneak-path solution based on transient-relaxation device. *Adv Mater* **2023**, *35*, 2207133.

36. Han, R. Z.; Xiang, Y. C.; Huang, P.; Shan, Y. H.; Liu, X. Y.; Kang, J. F. Flash memory array for efficient implementation of deep neural networks. *Adv Intell Syst* **2021**, *3*, 2000161.

37. Wang, Y.; Tang, H. W.; Xie, Y. F.; Chen, X. Y.; Ma, S. L.; Sun, Z. Z.; Sun, Q. Q.; Chen, L.; Zhu, H.; Wan, J.; Xu, Z. H.; Zhang, D. W.; Zhou, P.; Bao, W. Z. An in-memory computing architecture based on two-dimensional semiconductors for multiply-accumulate operations. *Nat Commun* **2021**, *12*, 3347.

38. Nandakumar, S. R.; Le Gallo, M.; Boybat, I.; Rajendran, B.; Sebastian, A.; Eleftheriou, E. Mixed-precision architecture based on computational memory for training deep neural networks. *IEEE International Symposium on Circuits and Systems (ISCAS)* **2018**, pp. 1-5.

39. Shen, P. C.; Su, C.; Lin, Y. X.; Chou, A. S.; Cheng, C. C.; Park, J. H.; Chiu, M. H.; Lu, A. Y.; Tang, H. L.; Tavakoli, M. M.; Pitner, G.; Ji, X.; Cai, Z. Y.; Mao, N. N.; Wang, J. T.; Tung, V. C.; Li, J.; Bokor, J.; Zettl, A.; Wu, C. I.; Palacios, T.; Li, L. J.; Kong, J. Ultralow contact resistance between semimetal and monolayer semiconductors. *Nature* **2021**, *593*, 211-217.

40. Liu, H.; Neal, A. T.; Ye, P. D. D. Channel length scaling of  $\text{MoS}_2$  MOSFETs. *ACS Nano* **2012**, *6*, 8563-8569.

41. Arutchelvan, G.; Smets, Q.; Verreck, D.; Ahmed, Z.; Gaur, A.; Sutar, S.; Jussot, J.; Groven, B.; Heyns,

M.; Lin, D.; Asselberghs, I.; Radu, I. Impact of device scaling on the electrical properties of MoS<sub>2</sub> field effect transistors. *Sci Rep* **2021**, *11*, 6610.

42. Li, C.; Belkin, D.; Li, Y. N.; Yan, P.; Hu, M.; Ge, N.; Jiang, H.; Montgomery, E.; Lin, P.; Wang, Z. R.; Song, W. H.; Strachan, J. P.; Barnell, M.; Wu, Q.; Williams, R. S.; Yang, J. J.; Xia, Q. F. Efficient and self-adaptive in-situ learning in multilayer memristor neural networks. *Nat Commun* **2018**, *9*, 2385.

43. Wang, C.-H.; Chen, V.; McClellan, C. J.; Tang, A.; Vaziri, S.; Li, L.; Chen, M. E.; Pop, E.; Wong, H.-S. P. Ultrathin three-monolayer tunneling memory selectors. *ACS Nano* **2021**, *15*, 8484-8491.