# Ultra-Efficient Foundry-Fabricated Resonant Modulators with Thermal Undercut

Anthony Rizzo<sup>1,\*</sup>, Venkatesh Deenadayalan<sup>2</sup>, Matthew van Niekerk<sup>2</sup>, Gerald Leake<sup>3</sup>, Christopher Tison<sup>1</sup>, Asher Novick<sup>4</sup>, Daniel Coleman<sup>3</sup>, Keren Bergman<sup>4</sup>, Stefan Preble<sup>2</sup>, and Michael Fanto<sup>1</sup>

<sup>1</sup>Air Force Research Laboratory Information Directorate, Rome, NY 13441, USA

<sup>2</sup>Microsystems Engineering, Rochester Institute of Technology, Rochester, NY 14623, USA

<sup>3</sup>College of Nanoscale Science and Engineering, University at Albany, Albany, NY 12203, USA

<sup>4</sup>Department of Electrical Engineering, Columbia University, New York, NY 10027, USA

\*anthony.rizzo.7@us.af.mil

**Abstract:** We demonstrate highly efficient vertical junction microdisk modulators with selective substrate undercut in a 300 mm CMOS foundry. The devices achieve record thermo-optic efficiency for sub-5  $\mu\text{m}$  radius, enabling next-generation low-energy, highly-parallel DWDM links. © 2023 The Author(s)

## 1. Introduction and Results

Resonant modulators are essential devices for highly energy-efficient dense wavelength-division multiplexed (DWDM) silicon photonic links due to their inherent wavelength selectivity, compact footprint, and low energy consumption [1]. Enabled by silicon's strong thermo-optic coefficient, integrated micro-heaters are typically necessary for such devices to tune and stabilize the resonant wavelength in the face of fabrication (static) and temperature (dynamic) variations. Previous demonstrations have shown modest electro-optic tuning to accommodate temperature variations on the order of 10 K [2, 3], but this range is an order of magnitude below the electronics-induced localized temperature swings possible in co-packaged optical interconnects. Thus, for realistic scenarios, integrated micro-heaters are required to achieve the necessary tuning range. However, such heaters can consume on the order of 25 mW  $P_\pi$  [4], which is prohibitive for low-power applications. Here, we demonstrate an ultra-efficient vertical junction microdisk modulator with an improvement in thermal tuning efficiency greater than 3× realized through a wafer-scale-compatible selective substrate undercut. Furthermore, the large overlap between the vertical junction and optical whispering gallery mode results in a large modulation efficiency compatible with small CMOS drive voltages. We measure key thermal metrics of  $P_\pi = 8.4$  mW and  $V_\pi = 2.7$  V for a representative 4.5  $\mu\text{m}$  radius device, achieving record thermo-optic efficiency for a sub-5  $\mu\text{m}$  radius resonant modulator while maintaining a CMOS-compatible voltage. The high efficiency, compact footprint, and wide free spectral range (FSR) of the demonstrated device will enable extreme scaling in the wavelength domain with ultra-low energy consumption for future DWDM silicon photonic links.

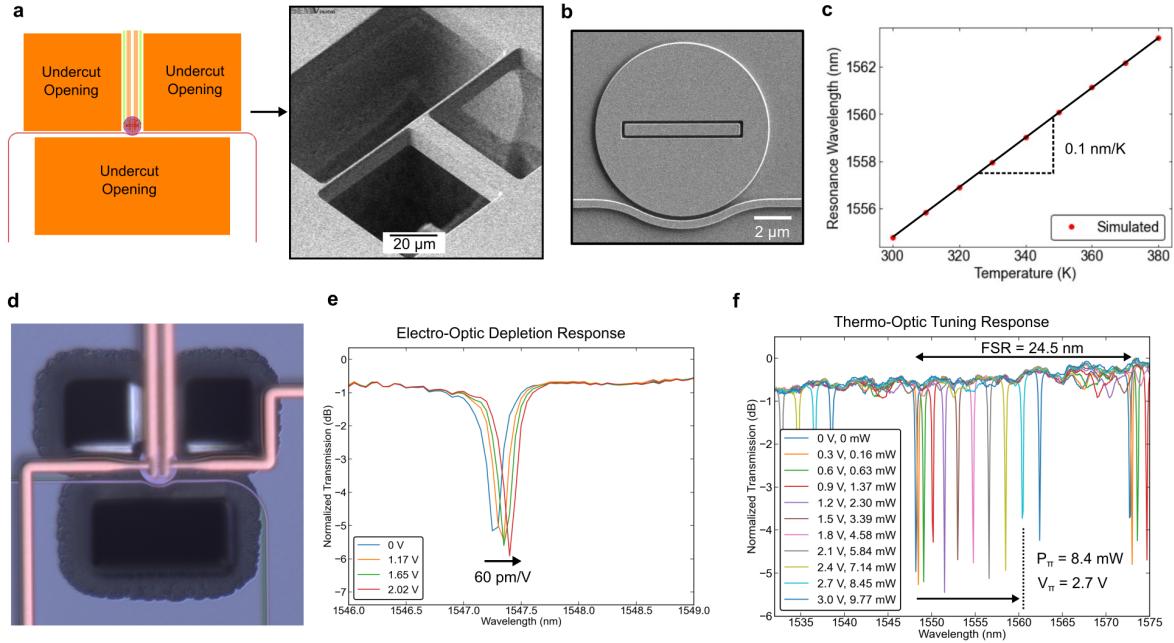

The detailed microdisk modulator device design is detailed in ref. [1]. Trench openings were defined in layout around the device (Fig. 1a) to enable the top-side undercut process. The integrated micro-heaters were designed using a doped silicon resistor in the interior of the disk with a 100 nm wide full silicon etch to isolate the heater from the junction contacts. The devices were fabricated on a dedicated 300 mm wafer run through AIM Photonics and designed for full undercut processing at the wafer-scale. While the development fabrication process on test wafers fully released the designed devices (Fig. 1a), the devices from the first full-build wafer were not fully undercut and thus required additional post-processing to complete the isotropic substrate etch (inductively coupled plasma reactive ion etch to remove the  $\approx 100$  nm of remaining buried oxide and vapor phase xenon difluoride etch to selectively remove the silicon substrate [5]). Wafers using an updated undercut recipe are currently under fabrication and are expected to have fully released devices without any post-processing. The fully released devices were then optically characterized with a v-groove fiber array and electrical multi-contact wedge probes to measure the thermal and modulation efficiencies. Assuming that a  $\frac{\pi}{2}$  phase shift is possible from temperature swings (Fig. 1c) and an additional  $\frac{\pi}{2}$  phase shift is possible from fabrication variations, worst-case tuning of  $\pi$  is required for devices under realistic scenarios. We measure the modulation efficiency to be approximately 60 pm/V, which is on the same order as previous state-of-the-art demonstrations [2, 3]. However, the integrated micro-heater in our device enables a much larger tuning range ( $> \pi$ ) than these previous demonstrations ( $< \frac{\pi}{16}$ ) and only consumes 0.67 mW/nm, yielding a worst-case per-device energy consumption of 8.4 mW. From simulations, we anticipate that this value can be further reduced in next-generation designs to yield  $P_\pi \approx 3$  mW (10× improvement) through optimization of the heater geometry.

Fig. 1. **a**, Device layout with defined undercut trench openings and corresponding SEM from test wafer showing full release of the device. **b**, SEM of the microdisk modulator after silicon patterning in full-build process. **c**, Simulated device temperature sensitivity showing that  $\frac{\pi}{2}$  phase shifts ( $\approx 6$  nm) are possible over an 80 degree range. **d**, Optical microscope image of the fully released device. **e**, Electro-optic depletion response of the device showing a modulation efficiency of  $60 \text{ pm/V}$ . **f**, Thermo-optic response of the undercut device showing a wide uncorrupted FSR and  $P_\pi = 8.4 \text{ mW}$ .

## 2. Conclusion

We have demonstrated ultra-efficient microdisk modulators in a commercial 300 mm foundry using vertical junctions to maximize the modal overlap with the depletion region for efficient high-speed modulation and a selective substrate undercut to realize optimal thermo-optic tuning. The optimized thermal tuning efficiency and modulation efficiency make the device fully compatible with state-of-the-art CMOS electronic voltages under realistic thermal loads, presenting an appealing path towards realizing future massively parallel DWDM co-packaged silicon photonic interconnects.

## References

1. A. Rizzo, S. Daudlin, A. Novick, A. James, V. Gopal, V. Murthy, Q. Cheng, B. Y. Kim, X. Ji, Y. Okawachi *et al.*, “Petabit-scale silicon photonic interconnects with integrated kerr frequency combs,” *IEEE J. Sel. Top. Quantum Electron.* **29**, 1–20 (2022).

2. E. Timurdogan, C. M. Sorace-Agaskar, J. Sun, E. Shah Hosseini, A. Biberman, and M. R. Watts, “An ultralow power athermal silicon modulator,” *Nat. communications* **5**, 1–11 (2014).

3. H. Gevorgyan, A. Khilo, M. T. Wade, V. M. Stojanović, and M. A. Popović, “Miniature, highly sensitive moscap ring modulators in co-optimized electronic-photonic cmos,” *Photonics Res.* **10**, A1–A7 (2022).

4. A. Masood, M. Pantouvaki, G. Lepage, P. Verheyen, J. Van Campenhout, P. Absil, D. Van Thourhout, and W. Bogaerts, “Comparison of heater architectures for thermal control of silicon photonic circuits,” in *10th International Conference on Group IV Photonics*, (IEEE, 2013), pp. 83–84.

5. M. van Niekerk, V. Deenadalayyan, A. Rizzo, G. Leake, D. Coleman, C. C. Tison, M. L. Fanto, K. Bergman, and S. Preble, “Wafer-scale-compatible substrate undercut for ultra-efficient soi thermal phase shifters,” in *2022 Conference on Lasers and Electro-Optics (CLEO)*, (IEEE, 2022), pp. 1–2.

**Acknowledgements:** This work was supported in part by the U.S. Advanced Research Projects Agency–Energy under ENLITENED Grant DE-AR000843 and in part by the U.S. Defense Advanced Research Projects Agency under PIPES Grant HR00111920014. The wafer/chip fabrication and custom device processing were provided by AIM Photonics/SUNY Poly Photonics engineering team and fabricator in Albany, New York.