## LETTER

## Threshold voltage control with high-temperature gate-oxide annealing in ultrawide bandgap AlGaN-channel MOSFETs

To cite this article: Shahab Mollah *et al* 2022 *Appl. Phys. Express* **15** 104001

View the [article online](#) for updates and enhancements.

### You may also like

- [Large periphery AlInN/AlN/GaN metal-oxide-semiconductor heterostructure field-effect transistors on sapphire substrate](#)

M Sultana, S Muhtadi, M Lachab *et al.*

- [Influence of oxygen-plasma treatment on AlGaN/GaN metal-oxide-semiconductor heterostructure field-effect transistors with HfO<sub>2</sub> by atomic layer deposition: leakage current and density of states reduction](#)

R Stoklas, D Gregušová, M Blaho *et al.*

- [Ultrawide bandgap Al<sub>1-x</sub>G<sub>x</sub>N channel heterostructure field transistors with drain currents exceeding 1.3 A mm<sup>-2</sup>](#)

Mikhail Gaevski, Shahab Mollah, Kamal Hussain *et al.*

## Threshold voltage control with high-temperature gate-oxide annealing in ultrawide bandgap AlGaN-channel MOSFETs

Shahab Mollah\*,<sup>1</sup> Kamal Hussain, Abdullah Mamun, Md Didarul Alam,<sup>1</sup> MVS Chandrashekhar, Grigory Simin, and Asif Khan

Department of Electrical Engineering, University of South Carolina, Columbia, SC 29208, United States of America

\*E-mail: [mmollah@email.sc.edu](mailto:mmollah@email.sc.edu)

Received March 2, 2022; revised August 11, 2022; accepted August 21, 2022; published online September 6, 2022

We report threshold voltage ( $V_{TH}$ ) control in ultrawide bandgap  $\text{Al}_{0.4}\text{Ga}_{0.6}\text{N}$ -channel metal oxide semiconductor heterostructure field-effect transistors using a high-temperature (300 °C) anneal of the high- $k$   $\text{ZrO}_2$  gate-insulator. Annealing switched the polarity of the fixed charges at the  $\text{ZrO}_2/\text{AlGaN}$  interface from  $+5.5 \times 10^{13} \text{ cm}^{-2}$  to  $-4.2 \times 10^{13} \text{ cm}^{-2}$ , pinning  $V_{TH}$  at  $\sim (-12 \text{ V})$ , reducing gate leakage by  $\sim 10^3$ , and improving subthreshold swing  $2 \times (116 \text{ mV decade}^{-1})$ . It also enabled the gate to repeatedly withstand voltages from  $-40$  to  $+18 \text{ V}$ , allowing the channel to be overdriven doubling the peak currents to  $\sim 0.5 \text{ A mm}^{-1}$ . © 2022 The Japan Society of Applied Physics

Supplementary material for this article is available [online](#)

II-Nitride HEMTs have attracted attention due to their high-power handling capabilities for compact consumer electronics.<sup>1–4</sup> Chargers with III-Nitride HEMTs designed for phones, tablets, laptops, etc. are half the size of conventional chargers, while offering fast charging capabilities. These devices are also becoming a major part of electric vehicle (EV) controls in modern transportation. Recently, many hybrid and EV automakers are investing in III-Nitride technology to enable higher power conversion efficiency, reduced system cost and weight compared to their traditional silicon counterparts.<sup>5,6</sup> The simultaneous combination of high frequency, high-power density and high-temperature operation capabilities of III-Nitride electronics enables this performance improvement.

For continued scaling to smaller footprints in power electronics, ultrawide bandgap (UWBG)  $\text{Al}_x\text{Ga}_{1-x}\text{N}$  ( $x > 0.3$ ,  $E_G > 3.4 \text{ eV}$ ) electronics are needed. This improvement is predicated on the scaling of the breakdown field with alloy composition.<sup>7,8</sup> Thus  $\text{Al}_x\text{Ga}_{1-x}\text{N}$  ( $x > 0.4$ ) channel high electron mobility field-effect transistors (HFETs) are promising candidates for compact next-generation power electronics.<sup>9–12</sup> However, in addition to the breakdown field, good gate control and low gate leakage are also key requirements.<sup>13,14</sup> Recently using gate dielectrics, both depletion mode (D-mode)<sup>15</sup> and enhancement mode (E-mode)<sup>16</sup> metal oxide semiconductor heterostructure field-effect transistors (MOSFETs) have been demonstrated.

Including a dielectric such as  $\text{SiO}_2$  between the gate metal and barrier/channel region results in the reduction of gate leakage in metal oxide semiconductor HFET's (MOSFET) in both voltage directions.<sup>17</sup> However, this comes at the expense of higher negative threshold voltage ( $V_{TH}$ ), requiring higher operating gate voltages that can potentially lead to higher gate leakage, negating the very benefit the dielectric was supposed to provide. This can be solved using high- $k$  dielectrics which are often deposited using atomic layer deposition (ALD) due to the ease and precision of the thickness control.<sup>18,19</sup> These ALD dielectrics can suppress gate leakage while maintaining a large gate capacitance in thick enough layers to increase the gate operating voltage with only a modest shift in  $V_{TH}$ .<sup>19</sup> However, in these ALD dielectrics, the  $V_{TH}$  shift is governed not only by the geometrical capacitance, but to a large extent by the fixed

charges at the dielectric/AlGaN interface,  $n_{\text{ox,intf}}$ , the distributed fixed charges through the bulk of the dielectric,  $n_{\text{ox,bulk}}$ , and the interfacial trapped charges.<sup>20</sup> These charges present additional variables that must be controlled to achieve the desired  $V_{TH}$  with low gate leakage, which is the subject of this paper.

Post-deposition annealing of ALD dielectrics can influence the crystal quality and reduce fixed charges and the trap density at the oxide/semiconductor interface.<sup>21,22</sup> However, selecting the optimal annealing temperature is a very crucial issue. If the temperature is too low, there is no significant influence on  $n_{\text{ox,intf}}$  and  $n_{\text{ox,bulk}}$ . If the temperature is too high, recrystallization of the ideally amorphous dielectric, can lead to higher leakage currents through the grain boundaries.<sup>23</sup> J. Liu et al. reported that, for  $\text{ZrO}_2$  the onset of crystallization starts around 210 °C and above 350 °C it completely changes to a crystal structure.<sup>21</sup> The anneal temperature for the ideal optical density was found to be around  $\sim 300 \text{ }^\circ\text{C}$ . Thus, for our study reported here, we selected a 300 °C post-deposition anneals of the gate dielectric ( $\text{ZrO}_2$ ) to maximize its influence on the bulk/interface charges and the interface trap density without changing the crystalline structure.

To quantify the influence of  $n_{\text{ox,intf}}$  and  $n_{\text{ox,bulk}}$  on  $V_{TH}$ , in MOSFETs we use.<sup>20,24</sup>

$$V_{th} = \Phi_b - \Phi_f - \Delta E_c - \frac{q t_{\text{ox}}^2}{2 \varepsilon_{\text{ox}}} n_{\text{ox,bulk}} - \frac{q t_{\text{ox}}}{\varepsilon_{\text{ox}}} n_{\text{ox,intf}} - q \left( \frac{t_{\text{ox}}}{\varepsilon_{\text{ox}}} + \frac{t_b}{\varepsilon_b} \right), \quad (1)$$

where  $\Phi_b$  is the metal barrier height,  $\Delta E_c$  is the conduction band discontinuity,  $\Phi_f$  is the energy difference between conduction band and Fermi energy,  $t$  is thickness,  $\varepsilon$  is permittivity and the subscripts b and ox refer to AlGaN barrier and oxide ( $\text{ZrO}_2$ ).  $n_{\text{ox,bulk}}$  represents the bulk oxide charge (per unit volume), and  $n_{\text{ox,intf}}$  represents the oxide/barrier interface charge density. Equation (1) underscores the abovementioned fact that  $n_{\text{ox,bulk}}$  and  $n_{\text{ox,intf}}$  are two key  $V_{TH}$  control parameters in MOSFETs especially in thicker oxides. High- $k$  ALD oxides have already shown superior device performance in UWBG MOSFETs.<sup>25,26</sup> In this report we present an oxide thickness ( $t_{\text{ox}}$ ) dependent study of  $V_{TH}$  values for MOSFETs with annealed and unannealed

high- $k$  ALD  $\text{ZrO}_2$  gate-insulator to separate the contributions from  $n_{\text{ox,bulk}}$  and  $n_{\text{ox,intf}}$ .

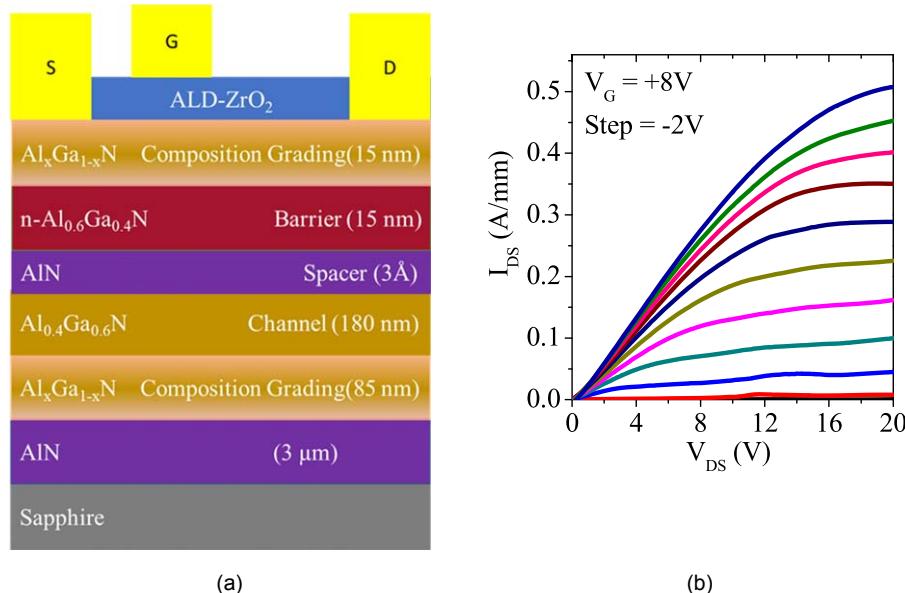

Figure 1(a) shows the schematic epilayer structure and device geometry for this work. The structure was grown over a 3  $\mu\text{m}$  thick high quality AlN/Sapphire template using metalorganic chemical vapor deposition. A reverse graded back barrier  $\text{AlN-Al}_{0.4}\text{Ga}_{0.6}\text{N}$  of 85 nm was grown to ensure pseudomorphic registry and screen defects generated from the growth interface.<sup>16)</sup> It was followed by 180 nm undoped  $\text{Al}_{0.4}\text{Ga}_{0.6}\text{N}$ -channel layer, 0.3 nm thick AlN spacer layer and 15 nm n- $\text{Al}_{0.6}\text{Ga}_{0.4}\text{N}$  barrier layer. UWBG  $\text{Al}_x\text{Ga}_{1-x}\text{N}$  ( $x > 0.4$ ) has low electron affinity ( $\chi_S$ ) that results in high Schottky barrier height ( $\Phi_B = \Phi_m - \chi_S$ ) that in turn results in high contact resistance. To facilitate ohmic contact formation we dope the barrier for reducing the tunneling barrier width for electrons.<sup>17)</sup> The donor concentration in the barrier layer,  $N_d$  is extracted from the linear  $1/C^2$  versus  $V$  characteristics that was found to be  $\sim 5 \times 10^{18} \text{ cm}^{-3}$ . A 15 nm reverse composition graded  $\text{Al}_x\text{Ga}_{1-x}\text{N}$  ( $x = 0.6$  to 0.3) was grown on top of the n- $\text{Al}_{0.6}\text{Ga}_{0.4}\text{N}$  to further facilitate ohmic contact formation by lowering the effective Schottky barrier height from 2.7 eV for  $\text{Al}_{0.6}\text{Ga}_{0.4}\text{N}$  to 0.62 eV for  $\text{Al}_{0.3}\text{Ga}_{0.7}\text{N}$ .<sup>16)</sup> The sheet resistance ( $R_{\text{sh}}$ ) of the as grown 2" wafer was measured by the Lehighton contactless sheet resistance mapping system to be  $\sim 2300 \Omega \text{ sq}^{-1}$  (see supplementary Fig. S1, available online at [stacks.iop.org/APEX/15/104001/mmedia](https://stacks.iop.org/APEX/15/104001/mmedia)). From mercury probe capacitance–voltage ( $C$ – $V$ ) measurement system the depletion voltage was estimated as  $\sim -11 \text{ V}$  (see Fig. S2).

The device processing started with mesa isolation using  $\text{Cl}_2$ -based inductively coupled plasma reactive ion etching. Ohmic contacts were defined by photolithography with subsequent metallization of  $\text{Zr}/\text{Al}/\text{Mo}/\text{Au}$  (15/100/40/30 nm) using E-beam metal deposition.<sup>27,28)</sup> The contacts were annealed at 950  $^{\circ}\text{C}$  for 30 s under  $\text{N}_2$  environment by rapid thermal annealing. The contact and sheet resistances were measured using transmission line model (TLM) test patterns. The ohmic contact resistance ( $R_c$ ) and the sheet resistance ( $R_{\text{sh}}$ ) were found to be 2.1 ohm mm and  $2280 \Omega \text{ sq}^{-1}$  respectively.

$R_{\text{sh}}$  was consistent with the values measured on the wafer using the Eddy current method.

The sample was then diced into four pieces: three pieces were used for fabricating  $\text{ZrO}_2$  MOSHFETs with 10, 20 and 30 nm of oxide thicknesses and the remaining piece was used for the control HFET (no oxide under the gate). The  $\text{ZrO}_2$  film was deposited using a thermal ALD process at 200  $^{\circ}\text{C}$ , with trimethylaluminum (TMA), tetrakis (dimethylamido) zirconium (IV) (TDMAZ) and deionized water as the precursors.<sup>25)</sup> The TDMAZ precursor was also heated to 75  $^{\circ}\text{C}$  in order to achieve a linear growth rate of 0.7  $\text{\AA}/\text{cycle}$ . The deposition was initiated with 15 water pulses prior to the typical AB pulsing sequence to deposit the gate dielectric to ensure saturation of hydroxyl groups at the AlGaN surface required for conformal ALD nucleation.  $\text{ZrO}_2$  was then removed from the ohmic contact area so probe pad can be connected to the ohmic contacts. The details of the ALD deposition process can be found in Ref. 25. The Ni/Au (100/200 nm) gate metal was then patterned by photolithography and deposited by E-beam evaporation using a lift-off process. Transistors with a source-drain spacing of 6  $\mu\text{m}$  and gate length of 1.8  $\mu\text{m}$  were fabricated. Gated TLM structure with gate length 100  $\mu\text{m}$  was also fabricated for  $C$ – $V$  measurement. Similar to the earlier reports on post-deposition annealing of  $\text{ZrO}_2$ ,<sup>11,21–23)</sup> our MOSHFET devices were taken through a two-step post-deposition annealing procedure on a hotplate in  $\text{O}_2$  ambient atmosphere. For high- $k$  dielectrics, as compared to other annealing environments such as  $\text{N}_2$ , the  $\text{O}_2$  annealing has shown a great impact on the positive shift of the threshold voltage. As suggested earlier, this may be due to the passivation of oxygen vacancies at the oxide/semiconductor interface.<sup>29)</sup> The  $\text{O}_2$  annealed devices are also expected to be less prone to drain current degradation because oxygen creates stronger bonding when passivating dangling bonds due to oxygen vacancies. When available, our data on  $\text{O}_2$ -annealed MOSHFET reliability will be published elsewhere. The annealing was performed at 250  $^{\circ}\text{C}$  first and then at 300  $^{\circ}\text{C}$  for 30 min at each temperature. The first annealing temperature was chosen as slightly higher

**Fig. 1.** (Color online) (a) Schematic layout of  $\text{ZrO}_2$  MOSHFET (b) output characteristics of  $\text{Al}_{0.6}\text{Ga}_{0.4}\text{N}/\text{Al}_{0.4}\text{Ga}_{0.6}\text{N}$  MOSHFET with 10 nm  $\text{ZrO}_2$  after annealing.

than the deposition temperature ( $200\text{ }^{\circ}\text{C}$ ). The devices were characterized both before and after the annealing step. At  $250\text{ }^{\circ}\text{C}$  annealing no significant change in device characteristics was noticed; then the temperature was raised to  $300\text{ }^{\circ}\text{C}$ . Thus, the reported results all correspond to the  $300\text{ }^{\circ}\text{C}$  anneal.

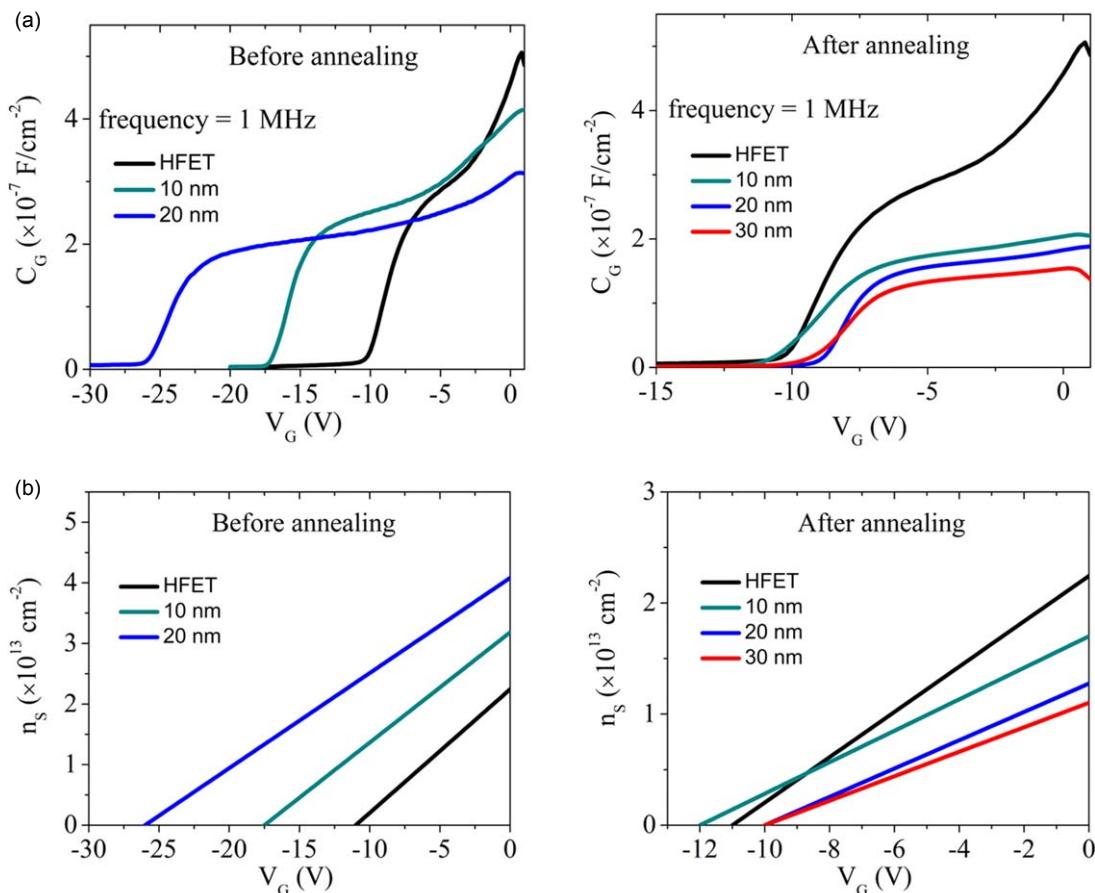

The DC output and transfer characteristics were measured using a parameter analyzer Agilent 4155 C and the  $C\text{-}V$  measurements were done using HP 4284 A LCR meter. Figure 2(a) shows that, at gate voltage  $V_G = +1\text{ V}$  annealing reduces the capacitance value from  $\sim(3\text{--}4) \times 10^{-7}\text{ F cm}^{-2}$  to  $\sim(1.8\text{--}2.2) \times 10^{-7}\text{ F cm}^{-2}$ . The 2DEG charge density ( $n_s$ ) was extracted using the  $C\text{-}V$  measurement on a  $100\text{ }\mu\text{m}$  wide gated TLM structures. Figure 2(b) reflects the corresponding reduction in  $n_s$ . The on-state sheet electron density  $n_s$  was estimated to be  $\sim 1\text{--}4 \times 10^{13}\text{ cm}^{-2}$  for the various devices of this study (see Table I).

From  $C\text{-}V$  characteristics we estimate the  $\text{ZrO}_2$  dielectric constant using the following formula:

$$1/C_G = 1/C_{\text{ox}} + 1/C_b,$$

where  $C_G$  is the measured gate capacitance, values for the unannealed and annealed conditions are  $2.45 \times 10^{-7}$  and  $1.83 \times 10^{-7}\text{ F cm}^{-2}$ , respectively.  $C_b$  is the barrier capacitance which is obtained from the HFET  $C\text{-}V$  characteristics without the  $\text{ZrO}_2$  ( $2.58 \times 10^{-7}\text{ F cm}^{-2}$ ). Given the  $20\text{ nm}$  thickness, the dielectric constant is extracted from  $C_{\text{ox}} = \varepsilon_r \varepsilon_0 / t_{\text{ox}}$  to be  $\varepsilon_r = 115.92$  and  $14.6$  for as deposited and annealed  $\text{ZrO}_2$ .

A typical output characteristic is shown in Fig. 1(b), where good saturation behavior is seen with current densities  $\sim 0.5\text{ A mm}^{-1}$  in the  $1.8\text{ }\mu\text{m}$  gate length devices. Typical output characteristics for HFET and MOSHFET devices with  $20$  and  $30\text{ nm}$   $t_{\text{ox}}$  are presented in the Supplementary Information section (Fig. S3).

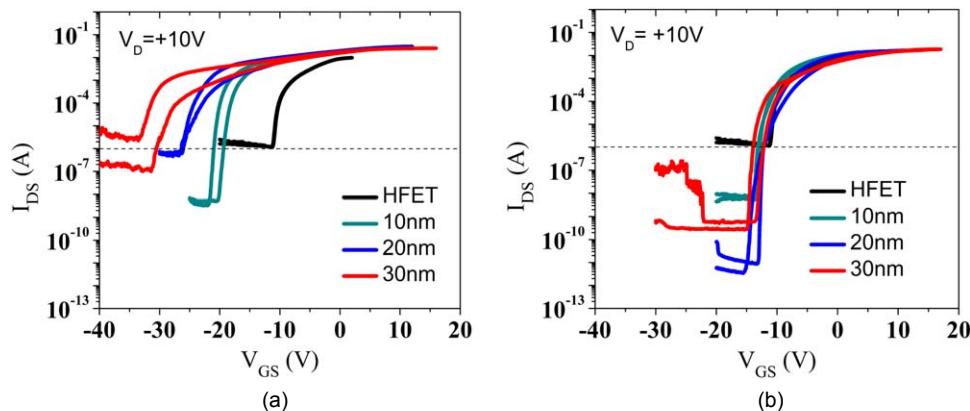

Figure 3 shows the double sweep transfer characteristics of the  $1.8\text{ }\mu\text{m}$  gate length devices with a drain bias  $V_{\text{DS}} = +10\text{ V}$ . It shows hysteresis in both cases of before and after annealing. Annealing does not completely remove the hysteresis but a reduction in hysteresis was observed. Due to their extremely low gate leakage, MOSHFET devices can operate at much higher positive gate voltages as compared to HFETs, which lose the gate control at  $V_G \geq 2\text{ V}$  due to high gate conduction. For the  $30\text{ nm}$  thick dielectric MOSHFET, at  $V_G = +14\text{ V}$  the channel current  $0.5\text{ A mm}^{-1}$  was achieved, which is twice as high as that of HFET (Table I). Further increase in the gate forward bias does not lead to the current increase due to limited 2DEG channel capacity and real-space charge transfer from 2DEG to the dielectric-barrier interface.<sup>30)</sup> As seen from Fig. 3(a), the unannealed MOSHFET devices show a very large threshold shift compared to an HFET.  $V_{\text{TH}}$ , which was defined as the gate voltage  $V_{\text{GS}}$  at which channel current  $I_{\text{DS}} = 1\text{ }\mu\text{A}$ , or  $20\text{ }\mu\text{A mm}^{-1}$ , had a large negative shift immediately after deposition (Table I), increasing monotonically with  $t_{\text{ox}}$ .  $V_{\text{TH}}$  reaches as high as  $-33.7\text{ V}$  for  $30\text{ nm}$  thick  $\text{ZrO}_2$  making devices unusable in practical applications. The leakage current in

**Fig. 2.** (Color online) (a)  $C\text{-}V$  characteristics of  $\text{Al}_{0.6}\text{Ga}_{0.4}\text{N}/\text{Al}_{0.4}\text{Ga}_{0.6}\text{N}$  HFET and MOSHFETs before and after annealing (b) 2DEG carrier density as a function of gate voltage of  $\text{Al}_{0.6}\text{Ga}_{0.4}\text{N}/\text{Al}_{0.4}\text{Ga}_{0.6}\text{N}$  HFET and MOSHFETs before and after annealing.

**Table I.** Summary of MOSHFET device characteristics with different  $ZrO_2$  thickness before and after the  $300\text{ }^\circ\text{C}$  anneal.

| HFET                                                 | 10 nm                                      |                                             | 20 nm                                      |                                              | 30 nm                                       |                                              |                                              |

|------------------------------------------------------|--------------------------------------------|---------------------------------------------|--------------------------------------------|----------------------------------------------|---------------------------------------------|----------------------------------------------|----------------------------------------------|

|                                                      | Before                                     | After                                       | Before                                     | After                                        | Before                                      | After                                        |                                              |

| $I_D$ ( $\text{A mm}^{-1}$ )                         | 0.24 at $V_G = +2\text{ V}$                | 0.55 at $V_G = +8\text{ V}$                 | 0.509 at $V_G = +8\text{ V}$               | 0.558 at $V_G = +12\text{ V}$                | 0.515 at $V_G = +12\text{ V}$               | 0.595 at $V_G = +15\text{ V}$                | 0.504 at $V_G = +18\text{ V}$                |

| $I_G$ ( $\text{A}$ )                                 | $5 \times 10^{-6}$ at $V_G = -20\text{ V}$ | $6 \times 10^{-11}$ at $V_G = -20\text{ V}$ | $8 \times 10^{-9}$ at $V_G = -20\text{ V}$ | $1.1 \times 10^{-9}$ at $V_G = -20\text{ V}$ | $4 \times 10^{-11}$ at $V_G = -20\text{ V}$ | $1.7 \times 10^{-9}$ at $V_G = -40\text{ V}$ | $1.5 \times 10^{-9}$ at $V_G = -40\text{ V}$ |

| Off-state current ( $\text{A}$ ) from transfer curve | $2 \times 10^{-6}$                         | $4 \times 10^{-9}$                          | $6 \times 10^{-9}$                         | $5 \times 10^{-7}$                           | $2 \times 10^{-11}$                         | $2 \times 10^{-7}$                           | $6 \times 10^{-10}$                          |

| $V_T$ ( $\text{V}$ )                                 | -10.8                                      | -20.8                                       | -13.1                                      | -25.5                                        | -12.1                                       | -33.7                                        | -12.2                                        |

| SS (mV decade $^{-1}$ )                              | 378                                        | 252                                         | 210                                        | 575                                          | 105                                         | 255                                          | 116                                          |

| $N_s$ ( $\text{cm}^{-2}$ )                           | $2.2 \times 10^{13}$                       | $3.2 \times 10^{13}$                        | $1.7 \times 10^{13}$                       | $4.08 \times 10^{13}$                        | $1.3 \times 10^{13}$                        | $4 \times 10^{13}$                           | $1.1 \times 10^{13}$                         |

the off-state for MOSHFETs (for all  $t_{\text{ox}}$ ) is reduced by more than two orders as compared to the control HFET.

Post-deposition annealing showed drastic improvement in the  $V_{\text{TH}}$  in all MOSHFETs where the biggest  $V_{\text{TH}}$  shift occurs in 30 nm  $ZrO_2$  from -33.7 to -12.2 V. Interestingly, after the anneal,  $V_{\text{TH}}$  only showed a weak  $t_{\text{ox}}$  dependence, suggesting that the interfacial charge  $n_{\text{ox,intf}}$  has been significantly changed. The significantly lower negative  $V_{\text{TH}}$  translated to a reduction in the on-state 2DEG  $n_s$  from  $\sim 2\text{--}3 \times 10^{13}$  to  $\sim 1 \times 10^{13} \text{ cm}^{-2}$ , in rough proportion to the  $V_{\text{TH}}$  shift. The off-state current, determined primarily by gate leakage,<sup>31</sup> decreased further for the thicker oxides to  $\ll 1\text{ nA}$ ,  $\sim 10^3$  reduction from that for the HFET. The off-state current for the thinnest 10 nm oxide increased slightly, although it remained in the nA range. We ascribe this unusual outlier to a dramatic change in the  $ZrO_2/\text{AlGaN}$  interface,  $n_{\text{ox,intf}}$ , which we will discuss further when quantifying the various charges responsible for the  $V_{\text{TH}}$  shifts. As expected, the 2-terminal gate-source leakage characteristics showed a behavior similar to that of the off-state leakage current (Fig. S4).

The subthreshold swing (SS) for MOSHFETs (all  $t_{\text{ox}}$ ) improved significantly after annealing to a value as low as 105 mV decade $^{-1}$  for the device with 20 nm thick  $ZrO_2$ . The improvement in SS is primarily due to the reduction in gate leakage described above, with high gate leakage masking the channel current at the lowest levels. We believe, the ALD oxide annealing lowers the interface trap density leading to reduced hysteresis and improved SS values.<sup>32</sup>

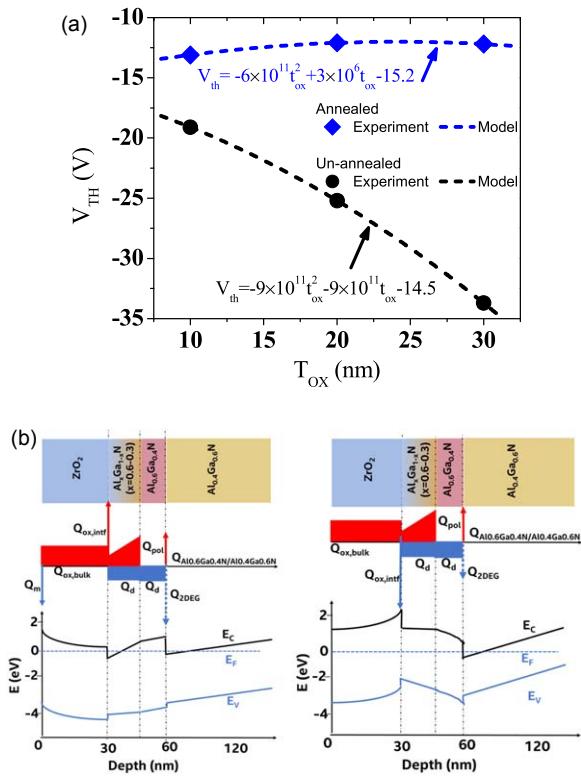

To separate the influence of  $n_{\text{ox,bulk}}$  and  $n_{\text{ox,intf}}$ ,  $V_{\text{TH}}$  of unannealed and annealed MOSHFETs are plotted as a function of  $t_{\text{ox}}$  in Fig. 4(a). In Eq. (1)  $V_{\text{TH}}$  is described by a quadratic polynomial of  $t_{\text{ox}}$  where the linear term gives

$n_{\text{ox,intf}}$  while the quadratic term gives  $n_{\text{ox,bulk}}$ . A second order polynomial fit to the experimental  $V_{\text{TH}}$  versus  $t_{\text{ox}}$  gave excellent agreement with the equation. The  $n_{\text{ox,bulk}} = +2.5 \times 10^{19} \text{ cm}^{-3}$  in unannealed MOSHFETs decreases only slightly to  $+1.7 \times 10^{19} \text{ cm}^{-3}$  after annealing. In contrast, annealing flipped the polarity of the large  $n_{\text{ox,intf}} = +5.5 \times 10^{13} \text{ cm}^{-2}$  to  $n_{\text{ox,intf}} = -4.2 \times 10^{13} \text{ cm}^{-2}$ , a very large change of  $\sim (-10^{14} \text{ cm}^{-2})$ . In bulk oxide, most positive negative dipoles cancel each other, thus interface charges constitute the main charge related to the dielectric layer.<sup>33</sup> We speculate that, annealing switches the polarity of the dipoles thus the net charge density at the interface becomes  $-4.2 \times 10^{13} \text{ cm}^{-2}$  after annealing as opposed to  $+5.5 \times 10^{13} \text{ cm}^{-2}$  in the case of the unannealed condition. Figure 4(b) shows the band diagram with the locations of these charges in the structure. This large negative  $n_{\text{ox,intf}}$  induced by post-deposition annealing at  $300\text{ }^\circ\text{C}$  is responsible for partially depleting the channel 2DEG, reducing  $n_s$ , and making  $V_{\text{TH}}$  less negative. This reduced  $n_s$ , we believe is also responsible for the  $\sim 20\%$  decrease in the peak drain current that was observed after the  $300\text{ }^\circ\text{C}$  annealing. However, this is much lower than the  $2\text{--}3\times$  decrease in  $n_s$ , indicating that because of the annealing, the channel mobility may have increased  $\sim 2\times$ . In the past, we studied the electron mobility of ultrawide bandgap HFETs and MOS-HFETs with different high-k dielectric layers.<sup>26</sup> Although the mobility temperature dependencies differed for HFET and MOSHFETs, the typical mobility range was the same for both device types. In this work, we used two-step PDA, which we believe is the main difference leading to mobility enhancement. The physical mechanism for mobility increase is the improved morphology of the dielectric and barrier layers and dielectric-barrier-channel interfaces, which, in turn, reduces interface scattering of the 2DGE electrons.

**Fig. 3.** (Color online) Double sweep transfer (IDS-VGS) characteristics of HFET and high-k  $ZrO_2$  MOSHFETs before (a) and after (b)  $300\text{ }^\circ\text{C}$  annealing.

**Fig. 4.** (Color online) (a)  $V_{TH}$  of unannealed and annealed MOSHFETs with  $ZrO_2$  thickness of 10, 20 and 30 nm. The dots show experimental value and dashed lines show fitting to analytical model. (b) Band diagram of  $Al_{0.6}Ga_{0.4}N/Al_{0.4}Ga_{0.6}N$  MOSHFET showing the location and polarity of bulk and interface charges before (left) and after (right) annealing.  $Q_d$ ,  $Q_m$ ,  $Q_{pol}$  represent the doping charge, metal charge and polarization charge, respectively, while others have their typical meaning.

In summary, we demonstrate a  $2\times$  improvement in channel current using post-deposition annealing of the ALD  $ZrO_2$  gate dielectric in UWBG AlGaN-channel MOSHFETs. The annealing mostly eliminated negative threshold voltage shift caused by the dielectric layer and enabled operation at high forward gate bias, up to +18 V compared to +2 V for the Schottky gate HFET, as a result doubling the HFET maximum channel current. Our anneal process also reduced the off-state leakage, improved the SS, while bringing  $V_{TH}$  into a range useful for practical applications. We show the improvement to be primarily due to a large change in fixed charge density at the  $ZrO_2/AlGaN$  interface induced by the annealing. The resulting  $n_{ox,intf} = -4.2 \times 10^{13} \text{ cm}^{-2}$  partially depleted the channel 2DEG to bring  $V_{TH}$  under control, while maintaining the current handling and the extremely low gate leakage currents. This paper shows the viability of  $ZrO_2$  gate dielectrics for UWBG AlGaN-channel MOSHFETs for high-power applications.

**Acknowledgments** This research was supported by ONR MURI program (Contract No. N00014-18-1-2429) monitored by Mr. Lynn Petersen and ARO contract W911NF-18-1-0029 monitored by Dr. M. Gerhold. The characterization was partially

supported by the National Science Foundation (NSF), ECCS Award Nos. 1711322, 1810116, and 1831954. We also acknowledge the UofSC ASPIRE program.

**ORCID IDs** Shahab Mollah [ID](https://orcid.org/0000-0002-2848-2959) Md Didarul Alam [ID](https://orcid.org/0000-0002-0673-6081)

- 1) J. L. Hudgins, G. S. Simin, E. Santi, and M. A. Khan, *IEEE Trans. Power Electron.* **18**, 907 (2003).

- 2) U. K. Mishra, P. Parikh, and Y. F. Wu, *Proc. IEEE* **90**, 1022 (2002).

- 3) M. Asif Khan, X. Hu, A. Tarakji, G. Simin, and J. Yang, *Appl. Phys. Lett.* **77**, 1339 (2000).

- 4) N. Tipirneni, A. Koudymov, V. Adivarahan, J. Yang, G. Simin, and M. A. Khan, *IEEE Electron Device Lett.* **27**, 716 (2006).

- 5) T. Kachi, *Jpn. J. Appl. Phys.* **53**, 100210 (2014).

- 6) M. Su, C. Chen, and S. Rajan, *Semicond. Sci. Technol.* **28**, 074012 (2013).

- 7) J. Y. Tsao et al., *Adv. Electron. Mater.* **4**, 1600501 (2018).

- 8) S. Muhtadi, S. M. Hwang, A. L. Coleman, A. Lunev, F. Asif, V. S. N. Chava, M. V. S. Chandrashekhar, and A. Khan, *Appl. Phys. Express* **10**, 011004 (2016).

- 9) T. Razzak et al., *Appl. Phys. Lett.* **116**, 023507 (2020).

- 10) H. Xue et al., *Solid State Electron.* **164**, 107696 (2020).

- 11) H. Xue, K. Hussain, T. Razzak, M. Gaevski, S. H. Sohel, S. Mollah, V. Talesara, A. Khan, S. Rajan, and W. Lu, *IEEE Electron Device Lett.* **41**, 677 (2020).

- 12) S. Muhtadi, S. Hwang, A. Coleman, F. Asif, A. Lunev, M. V. S. Chandrashekhar, and A. Khan, *Appl. Phys. Lett.* **110**, 193501 (2017).

- 13) B. J. Baliga, *Power Semiconductor Devices* (PWS Publishing Company, New York, 1996).

- 14) Y. Kong, J. Zhou, C. Kong, Y. Zhang, X. Dong, H. Lu, T. Chen, and N. Yang, *IEEE Electron Device Lett.* **35**, 336 (2014).

- 15) M. Gaevski, S. Mollah, K. Hussain, J. Letton, A. Mamun, M. U. Jewel, M. V. S. Chandrashekhar, G. Simin, and A. Khan, *Appl. Phys. Express* **13**, 094002 (2020).

- 16) S. Mollah, K. Hussain, A. Mamun, M. Gaevski, G. Simin, M. V. S. Chandrashekhar, and A. Khan, *Appl. Phys. Express* **14**, 014003 (2021).

- 17) X. Hu, S. Hwang, K. Hussain, R. Floyd, S. Mollah, F. Asif, G. Simin, and A. Khan, *IEEE Electron Device Lett.* **39**, 10 (2018).

- 18) M. T. Bohr, R. S. Chau, T. Ghani, and K. Mistry, *IEEE Spectr.* **44**, 29 (2007).

- 19) S. Rai, V. Adivarahan, N. Tipirneni, A. Koudymov, J. Yang, G. Simin, and M. A. Khan, *J. Appl. Phys.* **45**, 4985 (2006).

- 20) M. Tapajna and J. Kuzmík, *Appl. Phys. Lett.* **100**, 113509 (2012).

- 21) J. Liu, J. Li, J. Wu, and J. Sun, *Nanoscale Res. Lett.* **14**, 154 (2019).

- 22) J. Benick, A. Richter, T. T. A. Li, N. E. Grant, K. R. McIntosh, Y. Ren, K. J. Weber, M. Hermle, and S. W. Glunz, 35th IEEE Photovoltaic Specialists Conf., p. 000891.

- 23) D. H. Aguilar, L. C. T. Gonzalez, L. M. T. Martinez, T. Lopez, P. Quintana, and J. Solid, *State Chem.* **158**, 349 (2000).

- 24) Y. Zhang, M. Sun, S. J. Joglekar, T. Fujishima, and T. Palacios, *Appl. Phys. Lett.* **103**, 033524 (2013).

- 25) S. Mollah et al., *Semicond. Sci. Technol.* **34**, 125001 (2019).

- 26) S. Mollah et al., *Phys. Status Solidi A* **217**, 1900802 (2020).

- 27) N. Yafune, M. Nagamori, H. Chikaoka, F. Watanabe, K. Sakuno, and M. Kuzuhara, *Jpn. J. Appl. Phys.* **49**, 04DF10 (2010).

- 28) N. Yafune et al., *Jpn. J. Appl. Phys.* **50**, 100202 (2011).

- 29) Y. L. Yang, W. Zhang, C. Y. Cheng, and W. K. Yeh, *Act. Passive Electron. Compon.* **2012**, 872494 (2012).

- 30) S. Saygi, A. Koudymov, V. Adivarahan, J. Yang, G. S. Simin, M. Asif Khan, J. Deng, R. Gaska, and M. S. Shur, *Appl. Phys. Lett.* **87**, 043505 (2005).

- 31) X. Lu, H. Jiang, C. Liu, X. Zou, and K. M. Lau, *Semicond. Sci. Technol.* **31**, 055019 (2016).

- 32) W. Amir et al., *Sci. Rep.* **11**, 22401 (2021).

- 33) S. Mollah, M. Gaevski, K. Hussain, A. Mamun, M. V. S. Chandrashekhar, G. Simin, and A. Khan, *Appl. Phys. Lett.* **117**, 232105 (2020).