## Low temperature, highly stable ZnO thin-film transistors

Rodolfo A. Rodriguez-Davila <sup>a,b</sup>, Richard A. Chapman <sup>a</sup>, Zeshaan H. Shamsi <sup>a</sup>, S.J. Castillo <sup>b</sup>, Chadwin D. Young <sup>a</sup>, Manuel A. Quevedo-Lopez <sup>a,\*</sup>

<sup>a</sup> Department of Material Science and Engineering, the University of Texas at Dallas, 800 West Campbell Road, Richardson, TX 75080, USA

<sup>b</sup> Departamento de Investigación en Física, Universidad de Sonora, Blvd. Luis Encinas y Rosales S/N, Hermosillo, Sonora 83000, Mexico

### ARTICLE INFO

#### Keywords:

ZnO

TFT

Reliability

Nanofilm

Stability

Photolithography

### ABSTRACT

A low-temperature and straightforward fabrication process for ZnO thin-film transistors (TFTs) with near-zero aging and negligible instability enabled by using an ultrathin oxide as a top-passivation layer is demonstrated. The process features bottom-gate top-contacts ZnO TFTs with ultrathin HfO<sub>2</sub> or Al<sub>2</sub>O<sub>3</sub> as passivation layers on top of the TFT followed by post-fabrication annealing (PFA). Devices with ultra-thin capping films of Al<sub>2</sub>O<sub>3</sub> followed by a 150 °C PFA show threshold voltage shift ( $\Delta V_{TH}$ ) of <1% after bias stress and negligible shift after aging. The devices show saturation threshold voltage ( $V_{TH-SAT}$ ) of 2.70 V, saturation mobilities larger than 10 cm<sup>2</sup>/V·s, and current  $I_{ON}/I_{OFF}$  ratios  $>10^6$ . On the contrary, devices without nanofilm show similar performance to those with Al<sub>2</sub>O<sub>3</sub> but show more considerable instability to aging and bias stress ( $\Delta V_{TH} > 5\%$ ). Also, devices with HfO<sub>2</sub> as a capping layer shows severe instability ( $\Delta V_{TH} > 40\%$ ). A degradation mechanism to explain the improved aging and reliability performance is also discussed.

### 1. Introduction

Thin Film transistors based on oxides show superiority concerning silicon transistors in processing temperature, transparency, and compatibility with roll-to-roll and large-area fabrication processes. These advantages have generated much attention in the transparent and flexible electronics field to develop various applications. In general, the primary heralded alternative to conventional amorphous silicon TFT technology is the metal-oxide semiconductors, and some of the most promising oxides include ZnO, [1] InZnO, [2,3] ZnSnO, [4,5] and InGaZnO. [6,7] However, metal-oxide TFTs still show instabilities, such as instability induced by ambient, positive and negative bias, temperature, and light. This instability is usually due to carrier concentration changes in the metal-oxide from the adsorption and further chemical reaction with moisture (H<sub>2</sub>O) and oxygen (O<sub>2</sub>) from the ambient [8–11] or during the TFT fabrication. [9,12–15] Furthermore, the electric field applied during typical TFT operation might accelerate the adsorption, migration, and diffusion of O<sub>2</sub> and H<sub>2</sub>O, enhancing the TFT instability. [7,16]

The demonstration of low-temperature and stable oxide-based thin-film transistors without further increasing the fabrication complexity is highly desirable. Relatively simple approaches such as depositing a protective layer on the metal-oxide-semiconductor surface exposed to

the atmosphere have been evaluated, such as inorganic passivation/protection (SiO<sub>2</sub>, SiN<sub>x</sub>). Still, these films' deposition degrades the semiconductor due to the harsh processing environments and required temperatures [17–22]. Regularly, the reduction of degradation occurs using extended high-temperature post-deposition annealing. [19,23] Nevertheless, the annealing limits the technology's application to rigid substrates and limits oxide semiconductors' to high temperatures. Organic films have also been used to improve metal-oxide stability, but the uniformity and homogeneity of these organic films are challenging to control, resulting in instability in device performance. [16,24–27]

In this work, ultrathin inorganic (HfO<sub>2</sub>, Al<sub>2</sub>O<sub>3</sub>) nanofilms (referred to as NF in the manuscript) deposited on top of fully fabricated nanocrystalline-ZnO based TFTs are investigated, and the resulting performance and reliability systematically evaluated to enable thin-film transistors with  $\Delta V_{TH} < 1\%$  after bias stress, negligible aging,  $V_{TH-SAT}$  of 2.7 V, saturation mobilities larger than ten cm<sup>2</sup>/V·s, and current  $I_{ON}/I_{OFF}$  ratios  $>10^6$ . The conduction band offset (CBO) is about  $\sim 2.2$  eV [28,29] and  $\sim 3.0$  eV [28,30] for HfO<sub>2</sub>/ZnO and Al<sub>2</sub>O<sub>3</sub>/ZnO, respectively. The band gap for ZnO, HfO<sub>2</sub>, and Al<sub>2</sub>O<sub>3</sub> are 3.2, 5.6, and 7.0 eV, respectively [31–33]. In addition, the electron and hole effective masses are close to the following values: (a) ZnO are  $m_e^* = 0.3 m_0$  and  $m_h^* = 0.59 m_0$ ; (b) Al<sub>2</sub>O<sub>3</sub> are  $m_e^* = 0.4 m_0$ , and  $m_h^* = 6.0 m_0$  [34]; and (c) HfO<sub>2</sub> are  $m_e^* = 0.11 m_0$  and  $m_h^* = 0.58 m_0$  [35,36], however, they

\* Corresponding author.

E-mail address: [mquevedo@utdallas.edu](mailto:mquevedo@utdallas.edu) (M.A. Quevedo-Lopez).

could be as heavier as  $m_e^* = 1.91 m_0$  and  $m_h^* = 9.9 m_0$  in a cubic cell [37]. All these values are referenced concerning the electron-free mass,  $m_0$ .

## 2. Materials and methods

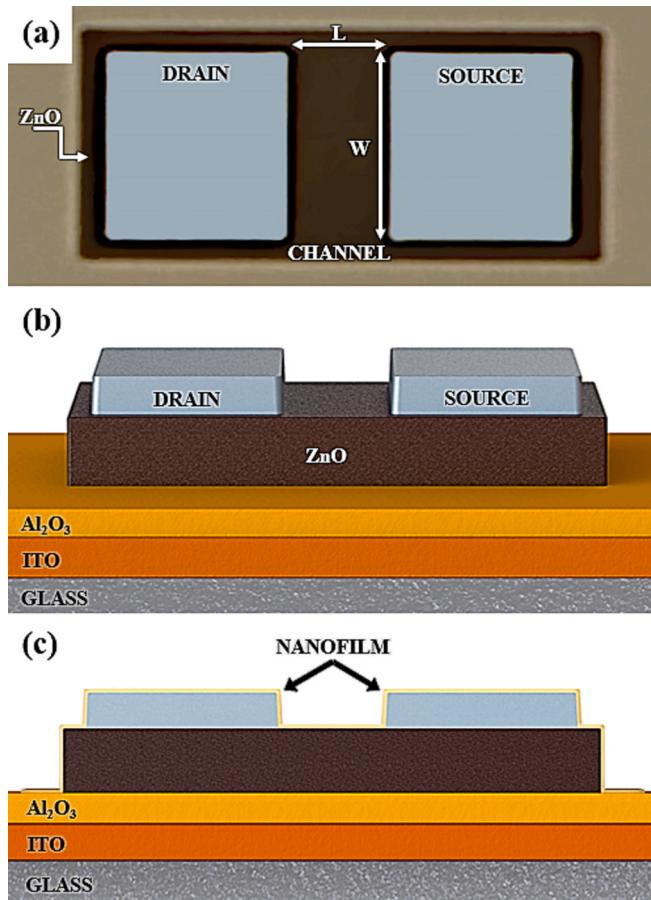

The fabrication of the thin-film transistors occurred with conventional photolithography. Fig. 1a shows the TFTs' plan view image, while Fig. 1b shows a 3D representation. The substrate is glass coated with 100 nm of Indium-tin-oxide (ITO) with resistivity  $<6.8 \times 10^{-4} \Omega \cdot \text{cm}$ . Before the dielectric deposition, the ITO surface is treated with oxygen-based reactive-ion-etching (RIE) to eliminate any contamination. Immediately after the RIE treatment, 15 nm of  $\text{Al}_2\text{O}_3$  are atomic layer deposited (ALD) with a substrate temperature of 100 °C. Trimethylaluminum and water are the precursors. Next,  $\text{ZnO}$  (50 nm) is pulsed laser deposited. The substrate temperature and  $\text{O}_2$  partial pressure are 100 °C, and 2.67 Pa, respectively. The ablation occurred with a calibrated energy density of 1 J/cm<sup>2</sup>. Source and drain electrodes are then defined by thermal evaporation of aluminum (100 nm) and patterned. Finally, each transistor's  $\text{ZnO}$  channel is isolated from neighbor devices using a wet etching process (Fig. 1b). TFTs are referred to as "as-fabricated" up to this step. Finally, the sample is divided into four pieces for the NF deposition with either none,  $\text{HfO}_2$  (10 nm, 100 °C), or  $\text{Al}_2\text{O}_3$  (10 nm, 100 °C). Fig. 1c shows a cross-section of the TFTs with the nanofilm.

The nanofilms are atomic layer deposited. Before the deposition process, the chamber pressure was controlled to 67 Pa using a constant  $\text{N}_2$  flow. Water vapor serves as the oxygen source, whereas trimethylaluminum (TMA, 97% purity) and tetrakisdimethylamido hafnium

(TDMAHf, 99.99% purity) are the metal-organic precursors for aluminum and hafnium, respectively. The pulse times were 15, 15, 50 ms for water, TMAH, and TDMAHf precursors, respectively. The purge time is 60 s for metal-organic precursors and 20 s for water. A total of 110 cycles results in 10 nm of both inorganic films. Following the nanofilm deposition step, the samples were annealed in a 90/10%  $\text{N}_2/\text{O}_2$  atmosphere at 150 °C and 250 °C for 1 h.

The devices' characterization occurred at room temperature (RT), dark, and air environment using a Keithley 4200-SCS semiconductor parameter analyzer. The reliability analyses were performed applying 5 V to the gate ( $V_{GS}$ ) and drain ( $V_{DS}$ ) simultaneously for 600 s. The stress was interrupted with interspersed  $I_{DS}-V_{GS}$  data characteristics collected from  $V_{GS} = -1.5$  to 5 V and  $V_{DS} = 5$  V, along with a pre-stress  $I_{DS}-V_{GS}$  collected just before bias stressing. To further study the barrier properties, aging was induced by further annealing the samples at 100 °C for 1 h in 90/10%  $\text{N}_2/\text{O}_2$ . The study of the nanofilms' structure occurred using grazing angle X-ray (GIXRD) with a monochromatic copper source ( $\text{Cu K}\alpha 1$  1.54056 Å) and an incidence angle of 0.5°.

## 3. Results and discussion

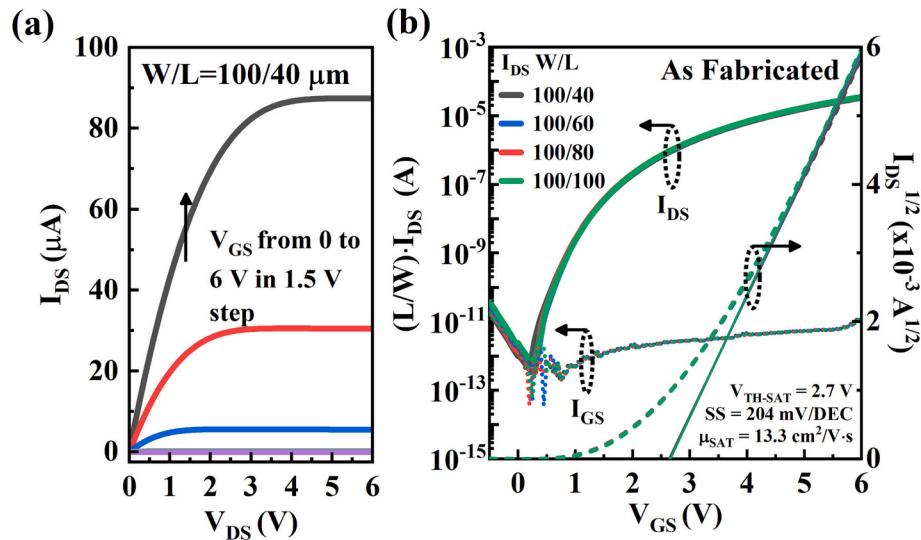

The as-fabricated  $\text{ZnO}$  TFTs without nanofilm nor PFA are used as the reference devices for the results and discussion. The  $I_{DS}-V_{DS}$  for these devices ( $W/L = 100/40$ ) is shown in Fig. 2a and the normalized ( $W/L$ ) transfer characteristics in Fig. 2b. The transfer characteristics are precisely the same indicating negligible parasitic effects. The current ratio ( $I_{ON}/I_{OFF}$ ) is more significant than  $10^8$ , with leakage current in the range of  $10^{-13} \text{ A}$ .

The saturation threshold voltage ( $V_{TH-SAT}$ ) and the saturation mobility ( $\mu_{SAT}$ ) are calculated by linear fitting the  $I_{DS}^{0.5}$  vs.  $V_{GS}$  plot for  $V_{DS} > V_{GS} - V_{TH-SAT}$ . [38] The right axis in Fig. 2b shows the linear fit using Eq. 1. The extracted  $V_{TH-SAT}$  and  $\mu_{SAT}$  are  $2.7 \pm 0.1$  V and  $13.3 \pm 0.4$   $\text{cm}^2/\text{V}\cdot\text{s}$ , respectively. The subthreshold swing obtained using eq. 2 is  $204 \pm 12$  mV/DEC.

$$I_{DS} = \frac{\mu_{SAT} C_{OX} W}{2L} (V_{GS} - V_{TH-SAT})^2 \quad (1)$$

$$SS = \left. \frac{dV_{GS}}{d(\log I_{DS})} \right|_{Max} \quad (2)$$

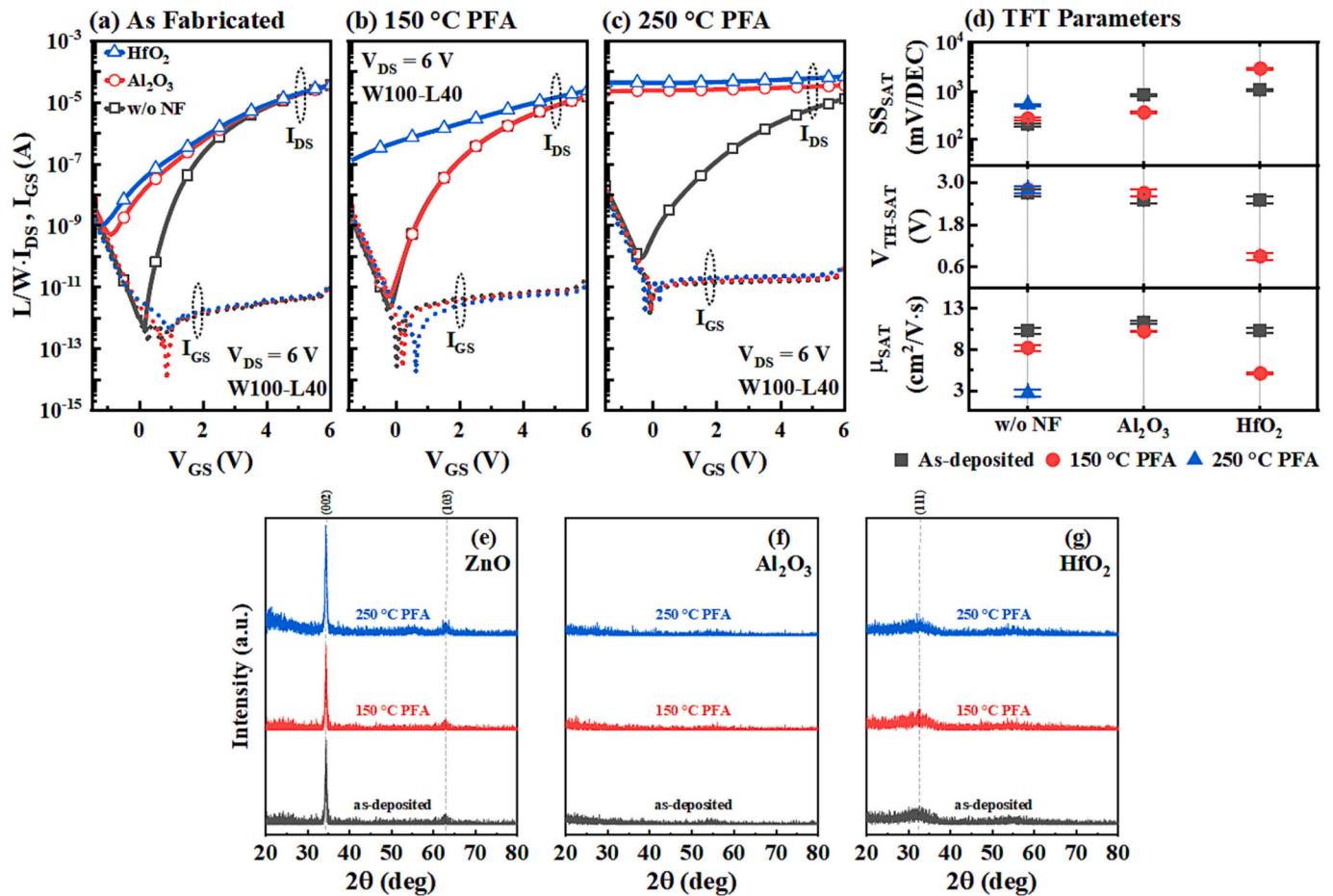

Fig. 3a compares as-fabricated (open squares) transfer characteristics to devices with the nanofilms before PFA. Neither  $V_{TH-SAT}$  nor  $\mu_{SAT}$  are significantly affected by the NF; however, both  $I_{OFF}$  and the SS increase for TFTs with NF. In our device configuration, due to the full depletion of electrons in the channel, the  $I_{OFF}$  is defined by the ultra-thin  $\text{ZnO}$  (i.e.,  $\text{ZnO}$  thickness). Thus,  $I_{OFF}$  can potentially be affected by conduction near the top of  $\text{ZnO}$ . Therefore, the  $\Delta I_{OFF}$  and  $\Delta SS$  can be correlated to changes in the density of trap states, not solely at the bottom-channel interface but also positive charges at the top (TP), close to the S/D. The increase in  $I_{OFF}$  indicates the formation of a top conductive channel because of the NF deposition, which affects the performance of as-fabricated TFTs. It is important to note that the NF deposition is at low temperature and might have a more fixed positive charge, thereby inducing the top channel as reflected in the higher  $I_{OFF}$  in Fig. 3a. [19]

The structural properties of the NF are in Fig. 3 (e - g). The as-fabricated  $\text{ZnO}$  is polycrystalline and has a wurtzite structure with a (0002) preferential orientation (JCPDS # 36-1451), as in Fig. 3e. On the other hand,  $\text{Al}_2\text{O}_3$  and  $\text{HfO}_2$  show amorphous and polycrystalline structures, respectively.  $\text{HfO}_2$  has a broad peak around 32.7° corresponding to the (111) monoclinic unit cell (JCPDS # 06-0318).

### 3.1. Device behavior after post-fabrication anneal (90/10 $\text{N}_2/\text{O}_2$ )

As discussed in the experimental section, a post-fabrication anneal (PFA) is performed at either 150 or 250 °C for 1 h. in 90/10  $\text{N}_2/\text{O}_2$  ambient to reduce any defects introduced during the NF deposition.

Fig. 1. (a) Microscope top view image and (b) 3D illustration of the fabricated TFTs without nanofilm. (c) Cross-section illustration of the TFTs with top nanofilm. The top nanofilm encapsulates  $\text{ZnO}$ , source, and drain.

Fig. 2. Electrical performance of the reference ZnO TFT (without-top nanofilm and no-post-fabrication anneal). (a)  $I_{DS}$  vs.  $V_{DS}$  Output characteristics of a  $W = 100$  and  $L = 40\text{ }\mu\text{m}$ . (b) Representative transfer characteristics of 4 different ZnO TFTs geometries. Dotted lines represent gate current ( $I_{GS}$ ).

Fig. 3.  $I_{DS}$  vs.  $V_{GS}$  transfer characteristic under different top nanofilm conditions (no-bias stress): (a) as fabricated, (b) 150 °C, and (c) 250 °C post-fabrication anneal (PFA). (d)  $V_{TH,SAT}$ ,  $\mu_{SAT}$ , and  $SS_{SAT}$  parameters as a function of the nanofilm condition for different PFA (Each point is the average of 45 devices, Standard deviation is also shown in the figure). The degradation of the TFT performance with 250 °C PFA is probably due to both interfaces' deterioration. (e) to (g) XRD results for ZnO, Al<sub>2</sub>O<sub>3</sub>, and HfO<sub>2</sub> with and without PFA.

Fig. 3 (b) and (c) show the  $I_{DS}$ - $V_{GS}$  characteristics for devices after 150 °C and 250 °C PFA, respectively. The extracted TFT parameters for samples with PFA are shown in Table 1.

The  $V_{TH,SAT}$  increases from 2.7 to 2.8 V for devices without the NF and 150 °C PFA. Also, there is no significant change in threshold voltage after 250 °C PFA, when compared to 150 °C.  $I_{OFF}$  slightly increases with

**Table 1**

Relation of device performance as a function of top nanofilm and post-annealing condition.

| Parameter                          | No Post Deposition Anneal |                                |                   | 150 °C PFA           |                                |                   | 250 °C PFA        |                                |                  |

|------------------------------------|---------------------------|--------------------------------|-------------------|----------------------|--------------------------------|-------------------|-------------------|--------------------------------|------------------|

|                                    | w/o NF                    | Al <sub>2</sub> O <sub>3</sub> | HfO <sub>2</sub>  | w/o NF               | Al <sub>2</sub> O <sub>3</sub> | HfO <sub>2</sub>  | w/o NF            | Al <sub>2</sub> O <sub>3</sub> | HfO <sub>2</sub> |

| $V_{TH-SAT}$ (V)                   | $2.7 \pm 0.1$             | $2.5 \pm 0.1$                  | $2.5 \pm 0.1$     | $2.8 \pm 0.1$        | $2.7 \pm 0.1$                  | $0.9 \pm 0.1$     | $2.8 \pm 0.1$     | –                              | –                |

| $\Delta V_{TE}$ (V)                | $2.2 \pm 0.1$             | $2.1 \pm 0.1$                  | $2.1 \pm 0.1$     | $2.7 \pm 0.1$        | $2.6 \pm 0.2$                  | $2.1 \pm 0.1$     | $3.6 \pm 0.1$     | –                              | –                |

| $\mu_{SAT}$ (cm <sup>2</sup> /V•s) | $13.3 \pm 0.4$            | $11.3 \pm 0.2$                 | $10.3 \pm 0.3$    | $8.2 \pm 0.4$        | $10.2 \pm 0.1$                 | $5.1 \pm 0.1$     | $2.7 \pm 0.4$     | –                              | –                |

| $\mu_{FE}$ (cm <sup>2</sup> /V•s)  | $17.4 \pm 0.4$            | $15.5 \pm 0.7$                 | $14.3 \pm 0.6$    | $11.6 \pm 0.7$       | $13.9 \pm 0.2$                 | $12.1 \pm 0.2$    | $4.1 \pm 0.1$     | –                              | –                |

| $SS_{SAT}$ (mV/DEC)                | $204 \pm 12$              | $828 \pm 40$                   | $1060 \pm 46$     | $271 \pm 16$         | $361 \pm 17$                   | $2883 \pm 98$     | $520 \pm 28$      | –                              | –                |

| $SS_{LIN}$ (mV/DEC)                | $181 \pm 7$               | $1052 \pm 21$                  | $1330 \pm 22$     | $254 \pm 16$         | $319 \pm 18$                   | $2975 \pm 51$     | $570 \pm 27$      | –                              | –                |

| $R_{SH-ON}$ ( $\Omega/\square$ )   | $4.4 \times 10^4$         | $4.9 \times 10^4$              | $4.7 \times 10^4$ | $7.0 \times 10^4$    | $6.0 \times 10^4$              | $6.1 \times 10^4$ | $2.1 \times 10^5$ | –                              | –                |

| $R_{SH-OFF}$ ( $\Omega/\square$ )  | $4.3 \times 10^{12}$      | $4.2 \times 10^7$              | $1.8 \times 10^7$ | $2.8 \times 10^{10}$ | $4.7 \times 10^9$              | $1.9 \times 10^6$ | $1.3 \times 10^9$ | –                              | –                |

<sup>1</sup>  $V_{TE}$  is the threshold voltage extracted from the extrapolation of the linear portion of the  $I_{DS}-V_{GS}$ , from maximum slope to zero current for small  $V_{DS}$  voltages ( $V_{DS} = 0.1$  V).

annealing temperature, and  $SS_{SAT}$  increases 32.8% and 154.9% after 150 and 250 °C PFA, respectively. The increase in  $SS$  indicates the filling of trap states near the bottom of the ZnO. These trap states can be a result of the formation of oxygen vacancies, [39–41] hydrogen [42,43], carbon [44,45], or roughness induced defects due to substrate instabilities [38] at the bottom-channel. This increase in the density of interface traps causes an increase of the Coulomb scattering, which causes a decrease in electron mobility, as observed in Fig. 3d.

Devices with Al<sub>2</sub>O<sub>3</sub> NF followed by 150 °C PFA show two orders of

magnitude decrease in  $I_{OFF}$ , a reduction of 56% in  $SS$ , and an 8% increase in  $V_{TH-SAT}$  compared to the reference samples. This result indicates that the anneal reduced positively fixed, thereby mitigating the top conductive channel. [46]

For devices with HfO<sub>2</sub> NF, the  $I_{OFF}$  increases two orders of magnitude, and  $SS$  increases 172%, after 150 °C PFA compared with the reference samples but shows a negative  $V_{TH-SAT}$  shift of ~2 V. This denotes the addition of positive oxide charge. Impurities likely cause this additional charge from the low-temperature deposition process.

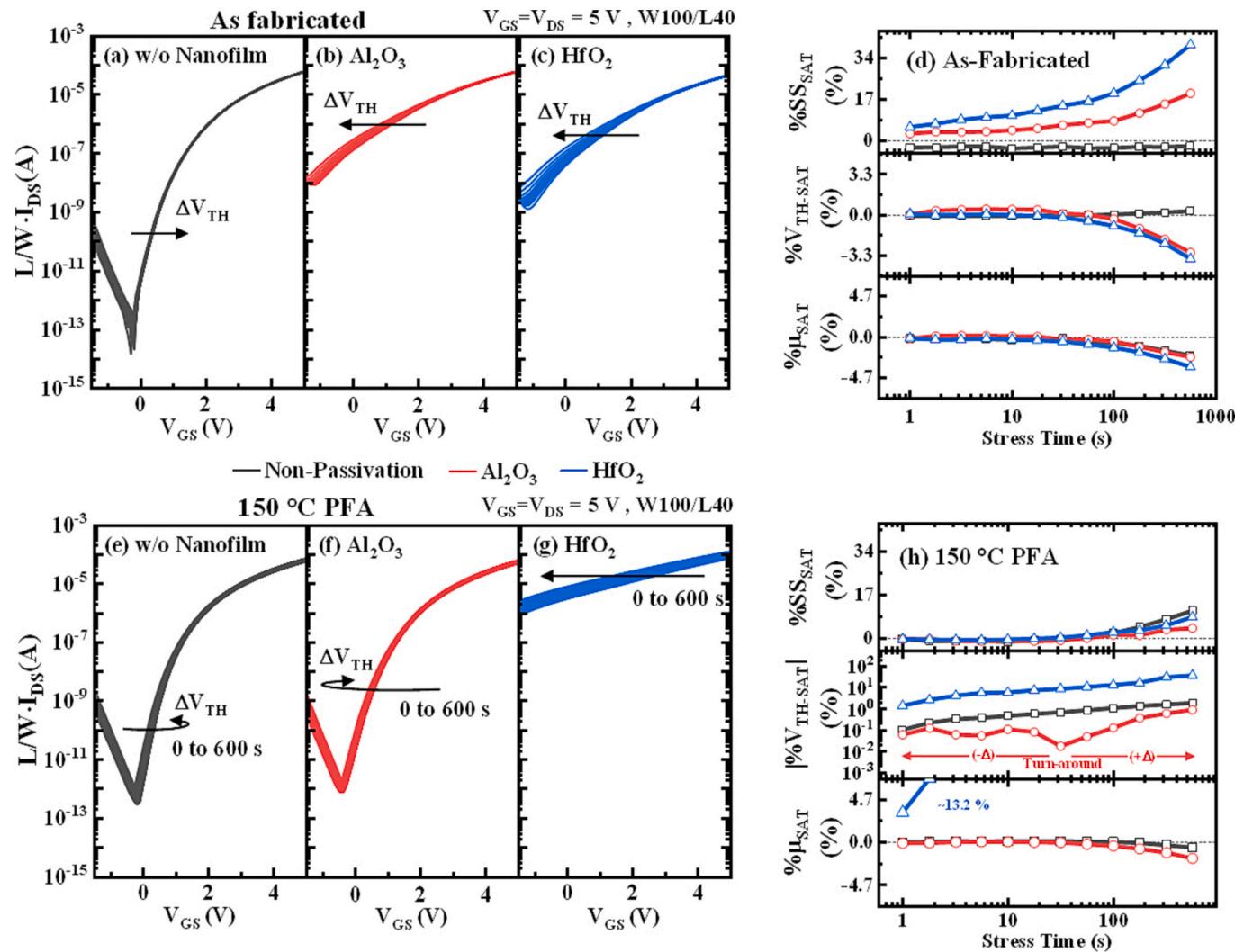

**Fig. 4.** Typical transfer characteristics for bias stress ( $V_G = V_D = 5$  V). (a) to (c) are for the as-fabricated devices; (e) to (g) are for 150 °C PFA; (d) and (h) shows the time evolution of the percentage changes in  $V_{TH-SAT}$ ,  $\mu_{SAT}$ , and  $SS_{SAT}$  parameters for as fabricated and after 150 °C PFA, respectively.

Contrary to  $\text{Al}_2\text{O}_3$ , these impurities can readily diffuse in  $\text{HfO}_2$  NFs due to its nanocrystalline character. [47,48] These positively charged contaminants are likely located in close proximity to the NF/ZnO interface resulting in the formation of a top conductive layer [39,49–52] and increasing the carrier concentration in ZnO, resulting in negative  $\Delta V_{TH}$ . It is important to note that there is no degradation in the drain saturation current in the 4–6 V range (Fig. 3 a-b). The fact that the drain current is not reduced, even with the increase in SS and  $I_{OFF}$ , demonstrates top channel conduction and requires a more negative gate voltage to turn the TFT off. [46] If there are generated defects acting as interfacial traps that increased SS and  $I_{OFF}$ , then there would have been a noticeable decrease in the drain saturation current, as typically seen in the literature. [53,54] Devices with  $\text{Al}_2\text{O}_3$ - and  $\text{HfO}_2$ - nanofilms show severe degradation after 250 °C PFA. This degradation could be due to the diffusion of atoms at the interface semiconductor/dielectric, leading to oxygen vacancies and hydrogen or carbon diffusion. [39,42,51,55,56]

### 3.2. Device stability under a positive bias stress

The 250 °C PFA is detrimental to all the devices regardless of NF; thus, they were not further analyzed. However, the sample with 150 °C PFA and  $\text{Al}_2\text{O}_3$  NF show substantial improvement from its as fabricated counterpart. Next, bias stress studies are used to study the NF's impact on device stability and reliability for not annealed and 150 °C PFA devices. The figure of merit for the analyses is the percentage threshold voltage shift ( $\%V_{TH-SAT}$ ) measured concerning the initial or  $t = 0$  s value. Similar calculations were used for  $\%SS$  and  $\%\mu_{SAT}$ . Fig. 4 (a) to (c) shows the representative transfer characteristics, while Fig. 4d shows the change of the figure of merits with stress time for the as-fabricated samples.

#### 3.2.1. Bias stress in unannealed devices

The positive  $\%V_{TH-SAT}$  of the reference sample (Fig. 4a) indicates that negative charge trapping occurs in the bottom-channel with minimum or negligible impact due to the top channel. States responsible for trapping can be either interface states, oxide/ dielectric states, or both. The  $\%SS$  is not affected in TFTs without NF; therefore, the dominant  $\%V_{TH-SAT}$  mechanism in these devices is due to oxide trapped states. This mechanism is also present in TFTs with NFs, given that all devices have the same MOS structure. However, the magnitude and direction of  $\%SS$  and  $\%V_{TH-SAT}$  are different, suggesting that the NF, and ultimately the top channel, play an essential role in the degradation mechanism. [39]

The  $\%V_{TH-SAT}$  is negative in TFTs with  $\text{Al}_2\text{O}_3$ - (Fig. 4b) and  $\text{HfO}_2$ - (Fig. 4c) nanofilm, indicating an increase in positive charge concentration. The change of  $I_{OFF}$  also suggests a more conductive channel, while the  $\Delta SS$  hints that the charge is near the interface under these bias stress conditions. This charge might be due to generated defects at the top-channel and near the drain with the prolonged bias stress. [57] Because  $|V_{TH-SAT}|$  in  $\text{HfO}_2$  is bigger than  $\text{Al}_2\text{O}_3$ , the charge trapping density is more significant in  $\text{HfO}_2$ . This concentration difference can be related to the nanocrystalline and amorphous character of  $\text{HfO}_2$  and  $\text{Al}_2\text{O}_3$ , respectively (Fig. 3).

#### 3.2.2. Bias stress after 150 °C post-fabrication anneal

Representative transfer characteristics after stress for the TFTs after 150 °C PFA are in Fig. 4 (e) to (g). The quantification of changes in device performance is in Fig. 4h. For non-passivated devices, the  $\%V_{TH-SAT}$  is positive for the initial 100 s, suggesting that the instability is due to negative-charge accumulation in the bottom  $\text{Al}_2\text{O}_3/\text{ZnO}$  interface. This behavior is the dominant degradation mechanism of ZnO-based TFTs. [58] However, after 100 s of stress,  $\%V_{TH-SAT}$  becomes negative, suggesting that a more conductive channel is forming. This can be due to the absorption of moisture, nitrogen, and carbon from the atmosphere in the exposed non-passivated top surface. These molecules can induce dangling bonds and vacancies during the prolonged bias stress, which overcomes the negative trapping occurring at the bottom interface.

Devices with  $\text{HfO}_2$  (Fig. 4g) nanofilms show a negative  $\%V_{TH-SAT}$ ,

increased  $\%SS$  and reduced  $\%\mu_{SAT}$ . This suggests that the top channel is becoming more conductive, creating additional degradation besides the negative charge trapping at the bottom channel. The polycrystalline character of these films can be beneficial for forming defects because of grain boundaries, resulting in considerable more charge accumulation.

On the contrary, devices with  $\text{Al}_2\text{O}_3$ -NF show the smallest  $\%SS_{SAT}$  (+3.9%),  $\%V_{TH-SAT}$  (+0.8%) and  $\%\mu_{SAT}$  (-1.75%) (Fig. 4f). These devices show a unique turnaround effect. This behavior could be due to a competing mechanism that results in  $\%V_{TH-SAT}$  neutralization. At the beginning of the stress, the top channel's increased conductivity dominates the degradation, resulting in a negative  $\%V_{TH-SAT}$ . The prolonged field applied during the bias stress can increase the concentration of defects at the top channel (dangling bonds and vacancies), but the amorphous character of the  $\text{Al}_2\text{O}_3$  limits the creation of many new trap states, contrary to what is observed in  $\text{HfO}_2$ . Simultaneously, the conventional negative charge trapping mechanism occurs at the bottom interface, resulting in positive  $\%V_{TH-SAT}$ . The competition of these mechanisms at the top and bottom interfaces results in instability neutralization, as observed in Fig. 4f.

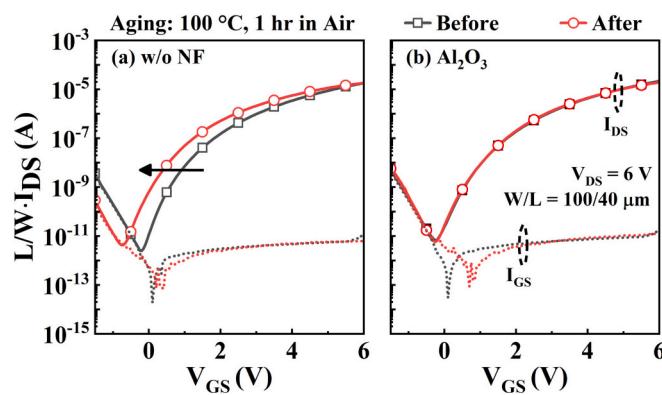

### 3.3. Device aging in air

The accelerated aging study consists of device annealing (100 °C, 1 h). Fig. 5 shows the TFT performance before and after aging.  $V_{TH-SAT}$  and  $\mu_{SAT}$  decrease 32.1% and 8.1%, respectively, for devices without NF. SS increases by 8.7%. The increase in  $I_{OFF}$  and SS after aging indicates an increase in trap states in the top channel. The negative change of  $V_{TH-SAT}$  indicates a more conductive channel after aging. As mentioned, the adsorption of moisture and contaminants in the ambient onto the exposed ZnO surface can occur. These contaminants can be positively charged and shift  $V_{TH-SAT}$  negatively by the accumulation of this charge.

Devices with  $\text{Al}_2\text{O}_3$  NF show no deterioration in TFT performance after aging, as shown in Fig. 5b. Therefore,  $\text{Al}_2\text{O}_3$  neutralizes the instability induced by prolonged bias stress and forms an excellent barrier against diffusion. This results in highly stable devices with excellent performance for large-area, low temperature, and novel electronic applications.

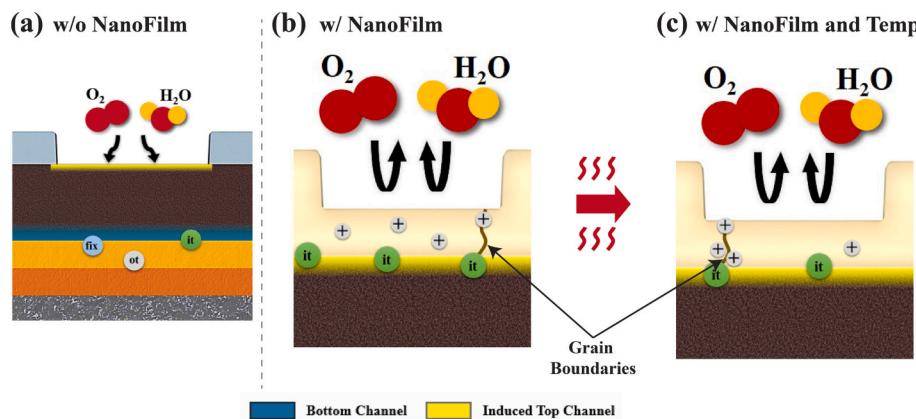

### 3.4. Proposed degradation mechanism

Fig. 6 shows the proposed mechanism for the behavior observed. Devices without NF (Fig. 6a) are affected by moisture and probably hydrocarbons in the air. These contaminants can adhere to the exposed ZnO channel's surface and induce the formation of a top-channel. The incorporation of the NF/protection layer blocks these molecules' adsorption onto the ZnO top surface, as shown in Fig. 6b. Nevertheless,

Fig. 5. Aging impact comparison for different samples: (a) Without top nanofilm, and (b)  $\text{Al}_2\text{O}_3$  nanofilms. The reference used for each condition is the device with 150 °C PFA. Devices with  $\text{Al}_2\text{O}_3$ -NF show zero-aging induced shifting.

**Fig. 6.** Proposed instability mechanism for different top surface conditions and annealing/aging. The cross-section for the different conditions analyzed: (a) Without nanofilm; (b) with nanofilm; and (c) with nanofilm plus temperature influence. The top nanofilm (b) blocks the diffusion of molecules (a) in ambient ( $H_2O$ ,  $N_2$ ,  $O_2$ , etc.). The deposition of the top nanofilm induced the formation of a top channel [yellow in (b)] in addition to the modulated bottom channel [Blue in (a)]. The presence of grain boundaries [in (b) and (c)] enables migration of positive charge near the top interface resulting in devices with larger instability. IT = interface traps; + = oxide traps; V = oxygen vacancies. For  $Al_2O_3$ , the (b) and (c) grain boundary mechanism is substantially suppressed due to fewer grain boundaries than  $HfO_2$ . (For interpretation of the references to colour in this figure legend, the reader is referred to the web version of this article.)

the addition of these low-temperature high- $k$  dielectrics may inherently introduce a positive charge in the oxide, which causes the development of a conductive layer at the top surface. These positive charges in the NF would attract electrons from the  $ZnO$ , effectively creating a top-channel, similar to devices without top NF.

Despite the barrier effectiveness of the NFs used, the concentration of oxide traps can be affected due to temperature (PFA or aging), and it is clearly dependent on the material. The filling of trap states is limited in  $Al_2O_3$  films, probably due to its amorphous structure, while the  $HfO_2$  might increase due to its polycrystalline character. [59–61] The results from the deposition of an inorganic amorphous film demonstrate the balance between defects and vacancies that exist, as shown in this research. The presence of grain boundaries allows more migration of positive charges and lowers the quality of interfaces in close proximity to the top  $ZnO$  surface, resulting in devices with more substantial instability.

#### 4. Conclusion

This work provides a novel method to enable a low-temperature and simple fabrication process for  $ZnO$  thin-film transistors (TFTs) with negligible aging and reduced instability after electrical stress. Devices with ultra-thin  $Al_2O_3$  films followed by a 150 °C PFA show threshold voltage shift ( $\Delta V_{TH}$ ) of <1% after bias stress and negligible shift after aging for 1000 s with a saturation threshold voltage ( $V_{TH-SAT}$ ) of 2.7 V, saturation mobilities larger than ten  $cm^2/V\cdot s$ , and current ratios >10<sup>6</sup>. The results suggest that  $Al_2O_3$  or  $HfO_2$  deposition without PFA increases the conductivity at the top-channel interface, degrading device performance compared to devices without nanofilm. The neutralization of trapped charge occurs by performing a post-fabrication anneal. Annealing the devices at 250 °C severely impacts the TFT performance with and without top nanofilm, while a 150 °C annealing shows substantial improvement, particularly for  $Al_2O_3$  nanofilms. The negligible  $\Delta V_{TH-SAT}$  for  $Al_2O_3$ -nanofilms indicates a competing effect with negative trap states at the bottom-channel and positive trap states at the top-channel, resulting in effective charge neutralization increasing the device stability. With low-temperature fabrication,  $Al_2O_3$  nanofilms are an excellent barrier for devices against ambient conditions. Furthermore, for the stress time used in this work,  $Al_2O_3$  nanofilms limited the bias stress instability of devices. This result is remarkable for large-area electronic applications where prolonged or heavy usage could be achieved, even with fabrication that uses low-temperature processing.

#### Funding sources

This work was supported in part by the National Science Foundation CAREER Award under the NSF award number ECCS-1653343, and

AFOSR project FA9550-18-1-0019 and RD Research Technology USA, LLC. The research reported here was partially supported by The University of Texas System and Mexico's Consejo Nacional de Ciencia y Tecnología (CONACYT) through the ConTex Postdoctoral Fellowship Program. The opinions expressed are those of the authors and do not represent the views of these funding agencies.

#### Credit author statement

- Rodolfo A. Rodriguez-Davila: Writing- Original draft preparation, Conceptualization, Methodology, Investigation, Formal Analysis.

- Richard A. Chapman: Data curation, Data Analysis, Investigation, Validation.

- Zeshaan H. Shamsi: Investigation, Conceptualization.

- S. J. Castillo: Investigation, Editing, Supervision, Funding Acquisition.

- Chadwin D. Young: Supervision, Writing - Reviewing & Editing, Funding Acquisition.

- Manuel A. Quevedo-Lopez: Validation, Writing - Reviewing, Editing, Funding Acquisition.

#### Declaration of Competing Interest

The authors declare the following financial interests/personal relationships which may be considered as potential competing interests:

Rodolfo Antonio Rodriguez Davila reports financial support was provided by National Council on Science and Technology. Rodolfo Antonio Rodriguez Davila reports financial support was provided by Rubio Pharma y Asociados, SA de CV. Manuel Quevedo reports financial support was provided by AFOSR. Chadwin Young reports financial support was provided by National Science Foundation.

#### Data availability

Data will be made available on request.

#### Acknowledgments

The authors thank CONACYT for the fellowship support of R.A. Rodriguez-Davila and Rubio Pharma y Asociados, SA de CV.

#### Appendix A. Supplementary data

Supplementary material: The PDF contains relevant information for the fabrication process flow, TFT layout and aspect ratios, Comparison of transfer characteristics in linear and saturation regimen. Supplementary data to this article can be found online at [https://doi.

[org/10.1016/j.mee.2023.112063](https://doi.org/10.1016/j.mee.2023.112063)].

## References

- [1] M. Wang, X. Li, X. Xiong, J. Song, C. Gu, D. Zhan, Q. Hu, S. Li, Y. Wu, IEEE Electron Device Lett. 40 (2019) 419.

- [2] H. Lee, C. Jyothi, S. Baang, J.-H. Kwon, J.-H. Bae, J. Korean Phys. Soc. 69 (2016) 1688.

- [3] H.J. Kim, Y.-G. Kim, S.P. Park, D. Kim, N.-E. Kim, J.S. Choi, H.J. Kim, SID Symposium Digest of Technical Papers 48, 2017, p. 180.

- [4] J. Li, C. Huang, C. Zhao, D. Zhong, J. Zhang, X. Li, IEEE Trans. Electron Devices 64 (2017) 4959.

- [5] X. Yang, S. Jiang, J. Li, J.-H. Zhang, X.-F. Li, RSC Adv. 8 (2018), 20990.

- [6] K. Nomura, H. Ohta, A. Takagi, T. Kamiya, M. Hirano, H. Hosono, Nature 432 (2004) 488.

- [7] D. Wang, M. Furuta, Beilstein J. Nanotechnol. 9 (2018) 2573.

- [8] T. Arai, J. Soc. Inf. Disp. 20 (2012) 156.

- [9] J. Jeong, H. Yang, J. Jeong, Y.-G. Mo, H. Kim, Appl. Phys. Lett. 93 (2008), 123508.

- [10] D. Hong, J.F. Wager, J. Vac. Sci. Technol. B 23 (2005) 125.

- [11] J.-S. Park, J.K. Jeong, H.-J. Chung, Y.-G. Mo, H.D. Kim, Appl. Phys. Lett. 92 (2008), 072104.

- [12] M. Fakhri, H. Johann, P. Görnn, T. Riedl, ACS Appl. Mater. Interfaces 4 (2012) 4453.

- [13] A. Illiberi, R. Scherpenborg, M. Theelen, P. Poodt, F. Roozeboom, J. Vac. Sci. Technol. A 31 (2013), 061504.

- [14] M. Fakhri, P. Görnn, T. Weimann, P. Hinze, T. Riedl, Appl. Phys. Lett. 99 (2011), 123503.

- [15] P. Görnn, T. Riedl, W. Kowalsky, J. Phys. Chem. C 113 (2009) 11126.

- [16] H. Yoo, Y. Tak, W.-G. Kim, Y.-G. Kim, H. Kim, J. Mater. Chem. C 6 (2018) 6187.

- [17] P.-T. Liu, Y.-T. Chou, L.-F. Teng, Appl. Phys. Lett. 95 (2009), 233504.

- [18] T.C. Chen, et al., Appl. Phys. Lett. 97 (2010), 192103.

- [19] Y.-Y. Lin, C.-C. Hsu, M.-H. Tseng, J.-J. Shyue, F.-Y. Tsai, ACS Appl. Mater. Interfaces 7 (2015) 22610.

- [20] R. Chen, W. Zhou, M. Zhang, H.-S. Kwok, Thin Solid Films 564 (2014) 397.

- [21] J.S. Park, et al., Appl. Phys. Lett. 96 (2010), 262109.

- [22] H.-S. Seo, J.-U. Bae, D.-H. Kim, Y. Park, C.-D. Kim, I.B. Kang, I.-J. Chung, J.-H. Choi, J.-M. Myoung, Electrochem. Solid-State Lett. 12 (2009) H348.

- [23] M. Fakhri, N. Babin, A. Behrendt, T. Jakob, P. Görnn, T. Riedl, Adv. Mater. 25 (2013) 2821.

- [24] S. Choi, J. Jang, J. Kim, M. Han, IEEE Electron Device Lett. 33 (2012) 381.

- [25] L. Huiling, L. Ting, Z. Shengdong, 2016 13th IEEE International Conference on Solid-State and Integrated Circuit Technology (ICSICT), 2016, p. 638.

- [26] S. Choi, J.W. Jo, J. Kim, S. Song, J. Kim, S. Park, Y.H. Kim, ACS Appl. Mater. Interfaces 9 (2017) 26161.

- [27] T. Toda, G. Tatsuoka, Y. Magari, M. Furuta, IEEE Electron Device Lett. 37 (2016) 1006.

- [28] H.-L. Lu, M. Yang, Z.-Y. Xie, Y. Geng, Y. Zhang, P.-F. Wang, Q.-Q. Sun, S.-J. Ding, D. Wei Zhang, Appl. Phys. Lett. 104 (2014).

- [29] Q. Chen, M. Yang, Y.P. Feng, J.W. Chai, Z. Zhang, J.S. Pan, S.J. Wang, Appl. Phys. Lett. 95 (2009).

- [30] D. Garcia-Alonso, S. Smit, S. Bordihn, W.M.M. Kessels, Semicond. Sci. Technol. 28 (2013), 082002.

- [31] D.P. Norton, Y.W. Heo, M.P. Ivill, K. Ip, S.J. Pearson, M.F. Chisholm, T. Steiner, Mater. Today 7 (2004) 34.

- [32] M.A. Martínez-Puente, P. Horley, F.S. Aguirre-Tostado, J. López-Medina, H. A. Borbón-Núñez, H. Tiznado, A. Susarrey-Arce, E. Martínez-Guerra, Mater. Sci. Eng. B 285 (2022), 115964.

- [33] E.O. Filatova, A.S. Konashuk, J. Phys. Chem. C 119 (2015) 20755.

- [34] T.V. Perevalov, A.V. Shaposhnikov, V.A. Gritsenko, H. Wong, J.H. Han, C.W. Kim, JETP Lett. 85 (2007) 165.

- [35] M. R. Osanloo, M. V. D. Put, A. Saadat, and W. Vandenberghe, (2021).

- [36] S. Monaghan, P.K. Hurley, K. Cherkaoui, M.A. Negara, A. Schenk, Solid State Electron. 53 (2009) 438.

- [37] J.C. Garcia, L.M.R. Scolfaro, J.R. Leite, A.T. Lino, V.N. Freire, G.A. Farias, E.F. da Silva Jr., Appl. Phys. Lett. 85 (2004) 5022.

- [38] R.A. Rodriguez-Davila, R.A. Chapman, P. Bolshakov, C.D. Young, M. Quevedo-Lopez, Microelectron. Eng. 217 (2019), 111114.

- [39] J. Kim, J. Jeong, S.M. Jeong, Electron. Lett. 51 (2015) 2047.

- [40] Y.V. Li, K.G. Sun, J.I. Ramirez, T.N. Jackson, IEEE Electron Device Lett. 34 (2013) 1400.

- [41] Y. Wang, Q. Ma, L. Zheng, W. Liu, S. Ding, H. Lu, D.W. Zhang, IEEE Trans. Electron Devices 63 (2016) 1893.

- [42] Y. Nam, H.-O. Kim, S.H. Cho, S.-H. Ko Park, RSC Advances 8 (2018) 5622.

- [43] Y. Nam, H.-O. Kim, S.H. Cho, C.-S. Hwang, T. Kim, S. Jeon, S.-H. Ko Park, J. Inf. Display 17 (2016) 65.

- [44] D.N. Goldstein, J.A. McCormick, S.M. George, J. Phys. Chem. C 112 (2008) 19530.

- [45] J.D. Ferguson, A.W. Weimer, S.M. George, Thin Solid Films 371 (2000) 95.

- [46] P. Bolshakov, A. Khosravi, P. Zhao, P.K. Hurley, C.L. Hinkle, R.M. Wallace, C. D. Young, Appl. Phys. Lett. 112 (2018), 253502.

- [47] D.M. Hausmann, R.G. Gordon, J. Cryst. Growth 249 (2003) 251.

- [48] D.S.S. Gieraltowska, E. Guziewicz, M. Godlewski, G. Luka, B.S. Witkowski, L. Wachnicki, E. Lusakowska, T. Dietl, M. Sawicki, Acta Phys. Pol. A 119 (2011) 333–336.

- [49] S. Hong, S.P. Park, Y.-G. Kim, B.H. Kang, J.W. Na, H.J. Kim, Sci. Rep. 7 (2017) 16265.

- [50] T.-H. Cheng, S.-P. Chang, S.-J. Chang, J. Electron. Mater. 47 (2018) 6923.

- [51] H. Y. Noh, J. Kim, J.-S. Kim, M.-J. Lee, and H.-J. Lee, 9, 75 (2019).

- [52] S. Oh, J. H. Baeck, J. U. Bae, K.-S. Park, and I. B. Kang, 108, 141604 (2016).

- [53] P. Bolshakov, R.A. Rodriguez-Davila, M. Quevedo-Lopez, C.D. Young, 2019 IEEE International Reliability Physics Symposium (IRPS), 2019, p. 1.

- [54] R.A. Rodriguez-Davila, I. Mejia, M. Quevedo-Lopez, C.D. Young, 2018 IEEE International Symposium on the Physical and Failure Analysis of Integrated Circuits (IPFA), 2018, p. 1.

- [55] M.W. Chase, et al., NIST-JANAF Thermochemical Tables, 4th Edition edn, American Chemical Society, 1998, p. pt. 1.

- [56] J. Speight, Lange's Handbook of Chemistry, 70th, Anniversary edition, McGraw-Hill Companies, Incorporated, 2004.

- [57] J.Y. Bak, Y. Kang, S. Yang, H.-J. Ryu, C.-S. Hwang, S. Han, S.-M. Yoon, Sci. Rep. 5 (2015) 7884.

- [58] R.A. Rodriguez-Davila, I. Mejia, R.A. Chapman, C.D. Young, M. Quevedo-Lopez, IEEE Trans. Electron Devices 66 (2019) 3861.

- [59] D. Gupta, Mater. Sci. Forum 1 (1984) 257.

- [60] W. Shen, N. Kumari, G. Gibson, Y. Jeon, D. Henze, S. Silverthorn, C. Bash, S. Kumar, J. Appl. Phys. 123 (2018), 085113.

- [61] R.H. Doremus, J. Appl. Phys. 100 (2006), 101301.