| 1        | Investigating Wet Chemical Oxidation Methods to Form SiO <sub>2</sub>                                                                                 |  |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 2        | Interlayers for Self-Aligned Pt-HfO2-Si Gate Stacks                                                                                                   |  |

| 3        |                                                                                                                                                       |  |

| 4        | Amy C. Brummer <sup>1</sup> , Siddharth Kurup <sup>2</sup> , Daniel Aziz <sup>3</sup> , Michael A. Filler <sup>3</sup> , Eric M. Vogel <sup>1,*</sup> |  |

| 5        |                                                                                                                                                       |  |

| 6        | <sup>1</sup> Georgia Institute of Technology: School of Materials Science and Engineering                                                             |  |

| 7        | <sup>2</sup> Georgia Institute of Technology: School of Electrical and Computer Engineering                                                           |  |

| 8        | <sup>3</sup> Georgia Institute of Technology: School of Chemical & Biomolecular Engineering                                                           |  |

| 9        |                                                                                                                                                       |  |

| 10<br>11 | *corresponding email: eric.vogel@mse.gatech.edu                                                                                                       |  |

| 12       | Abstract:                                                                                                                                             |  |

| 13       | Self-aligned metal-oxide-semiconductor (MOS) capacitors are studied with several low                                                                  |  |

| 14       | temperature, wet chemical silicon dioxide (SiO <sub>2</sub> ) interlayers to understand their impact of                                               |  |

| 15       | electrical performance. Self-aligned MOS capacitors are fabricated with a bottom-up                                                                   |  |

self-aligned metal-oxide-semiconductor (MOS) capacitors are studied with several low temperature, wet chemical silicon dioxide (SiO<sub>2</sub>) interlayers to understand their impact on electrical performance. Self-aligned MOS capacitors are fabricated with a bottom-up patterning technique that uses a poly(methyl methacrylate) brush and dopant-selective KOH etch combined with area-selective atomic layer deposition (AS-ALD) of hafnium dioxide (HfO<sub>2</sub>) and Pt. The wet chemical pre-treatments used to form the SiO<sub>2</sub> interlayer include HF-last, 80 °C H<sub>2</sub>O, and SC-2. Capacitance-voltage measurements of these area-selective capacitors exhibit a HfO<sub>2</sub> dielectric constant of ~19, irrespective of pre-treatment. After a forming gas anneal, the average interface state density decreased between 1.8 and 7.5 times. The minimum observed D<sub>it</sub> is 1 x 10<sup>11</sup> eV<sup>-1</sup>cm<sup>-2</sup> for the HF-last treatment. X-ray photoelectron spectroscopy shows an increase in stoichiometric SiO<sub>2</sub> in the interfacial layer after the anneal. Additional carbon is also observed; however, comparison with capacitors fabricated in a non-selective process reveals minimal impact on performance.

PLEASE CITE THIS ARTICLE AS DOI: 10.1116/6.0002762

### I. INTRODUCTION

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

Alignment between the edge of a gate stack and the edge of the underlying doped source-drain regions of the silicon (Si) channel is a critical issue for the fabrication of high-performance transistors. Excess overlap results in large fringe capacitance and reduced device speed while too much underlap can result in extra series resistance.<sup>1,2</sup> Achieving proper alignment within an integrated high-k/metal gate stack can require complex integration schemes such as the replacement metal gate technique.<sup>3</sup> Processing and integration becomes even more challenging for gate-all-around transistors with either vertical<sup>4</sup> or lateral<sup>5</sup> silicon nanowires, where numerous process steps are required to align the gate stack over the channel (e.g., selectively etching a gap across the channel and depositing a dummy gate for source/drain doping, then replacing the dummy gate with a high-k gate stack). The ability to form self-aligned device structures, such as MOS capacitors, would simplify fabrication of gate-all-around transistors and benefit a variety of emerging device applications, including vertical nanowire transistors monolithically integrated into the back end of line (BEOL)<sup>6</sup> and flexible electronics that require lower process temperatures and patterning techniques that are more scalable than conventional photolithography.<sup>7</sup>

Atomic layer deposition (ALD) allows for low-temperature and area-selective deposition of thin films closely aligned with patterns on the underlying substrate, largely irrespective of geometry. The most common techniques for area-selective ALD (AS-ALD) involve using self-assembled monolayers (SAMs)<sup>8-15</sup> or other polymeric materials<sup>16-21</sup> to deactivate the surface by preventing the chemisorption of the ALD precursors. These techniques typically require photolithography to apply the masking

1

2

3

4

5

14

15

16

17

18

19

20

21

22

23

material, either to pattern the surface modification layer<sup>13,16-18</sup> or to pattern the deposition of different materials that have intrinsic chemical differences. 10,12,21,22 Our previous work demonstrated a fabrication process that combines a bottom-up

patterning technique with AS-ALD to deposit hafnium dioxide (HfO<sub>2</sub>) and platinum (Pt)

thin films based on the local carrier concentration of the underlying Si substrate, ultimately forming self-aligned MOS capacitors.<sup>23</sup> The bottom-up patterning techniques 6

7 is a derivative of selective co-axial lithography via etching of surfaces (SCALES).<sup>24,25</sup>

8 Patterning with SCALES begins with a poly(methyl methacrylate) (PMMA) brush grown

9 from a Si surface via atom-transfer radical polymerization. We selectively remove the

10 polymer film from the lightly doped Si regions by etching with an aqueous potassium

11 hydroxide (KOH) solution. The PMMA film remains attached to the heavily doped Si

12 regions which then serves as a mask for AS-ALD of HfO<sub>2</sub> and Pt. The resulting self-

13 aligned MOS capacitors yielded expected capacitance-voltage behavior.

A thin SiO<sub>2</sub> layer is often required to form a low defect density interlayer between Si and high-k dielectrics, <sup>26,27</sup> as well as to improve ALD nucleation of HfO<sub>2</sub>. <sup>28</sup> To form this interlayer, a high-temperature thermal oxidation technique is typically used. However, high temperature thermal oxidation is not possible with the current SCALES process because the polymer cannot withstand high process temperatures. Other chemical oxidation methods have also been studied to improve ALD film nucleation and reduce interface state density, including treatments such as hydrogen peroxide, standard cleans 1 and 2 (SC-1 and SC-2 from RCA clean), nitric acid and heated water (H<sub>2</sub>O). <sup>28,29</sup>

In this work, self-aligned (area-selective deposition) Pt-HfO<sub>2</sub>-Si MOS capacitors are compared with conventional (non-selective deposition) capacitors to investigate the

### 1 impact of a variety wet chemical processes (i.e., HF etch, 80 °C H<sub>2</sub>O, and SC-2) for

- 2 forming the SiO<sub>2</sub> interlayer. Physical characterization methods (i.e., ellipsometric

- 3 spectroscopy and x-ray photoelectron spectroscopy) are used to understand the

- 4 relationship between the various SiO<sub>2</sub> interlayer formation techniques and the electrical

- 5 performance of the capacitors. Capacitance-voltage characteristics exhibit similar

- 6 performance between area-selective and non-selective capacitors, and average interface

- 7 state density is reduced to 1.9 x 10<sup>11</sup> eV<sup>-1</sup>cm<sup>-2</sup> after a forming gas anneal (FGA). X-ray

- 8 photoelectron spectroscopy indicates an increase in the amount of stoichiometric SiO<sub>2</sub> in

- 9 the interfacial layer after the FGA. Additional carbon is also observed in the area-

- selective interfacial layer after the FGA which does not significantly impact performance.

### 11 II. EXPERIMENTAL METHODS

### 12 A. Non-selective capacitor fabrication

For conventional "non-selective" capacitors, Si(100) with a p-type doping level of

$\sim 10^{18}$  cm<sup>-3</sup> was used. A modified RCA clean was first performed: 1 min in dilute SC-1 (5

15 DI H<sub>2</sub>O:1 H<sub>2</sub>O<sub>2</sub>:0.25 NH<sub>4</sub>OH) at 75 °C, 30 s HF etch, and 10 min in SC-2 (5 DI H<sub>2</sub>O:1

16 H<sub>2</sub>O<sub>2</sub>:1 HCl) at 75 °C. The fabrication process for the area-selective capacitors requires a

17 less aggressive organic clean than the typical SC-1 treatment to minimize damage to the

18 PMMA mask. For consistency, a modified version of the typical RCA clean was used for

both the non-selective and area-selective capacitors. This clean was followed by an HF

etch (30 s in 1% HF) to remove the native oxide prior to formation of the SiO<sub>2</sub> interlayer.

21 Three different wet chemical oxidation techniques were investigated as pre-treatments to

form the thin SiO<sub>2</sub> interlayer: HF-last treatment (30 s in 1% HF followed by DI H<sub>2</sub>O

23 rinse), hot water (30 s in 1% HF then 10 min in ultra-pure DI H<sub>2</sub>O at 80 °C), and SC-2

PLEASE CITE THIS ARTICLE AS DOI: 10.1116/6.0002762

- 1 treatment (30 s in 1% HF then 10 min in 5 DI H<sub>2</sub>O:1 H<sub>2</sub>O:1 HCl at 75 °C). These

- 2 chemical oxides are compared with a high temperature rapid thermal processing (RTP)

- 3 oxidation (30 s in 1% HF, 3 min in RTP furnace flowing 5 SCCM O<sub>2</sub> at 900 °C, 1% HF

- 4 etch to reduce thickness).

- 5 Immediately following oxidation, the samples were transferred to the ALD

- 6 chamber (Cambridge Fiji ALD system with argon as a carrier/purging gas and a total

- 7 chamber pressure of 0.45 Torr) to deposit ~6 nm of thermal HfO<sub>2</sub> at 200 °C using 55

- 8 cycles of tetrakis(dimethylamido)hafnium (TDMAHf) and H<sub>2</sub>O. The exposure times for

- 9 TDMAHf and H<sub>2</sub>O were 0.25 and 0.06 s, respectively, followed by purge times of 20 and

- 10 15 s. Electron-beam evaporation was used to deposit 75 nm of Pt through a shadow mask,

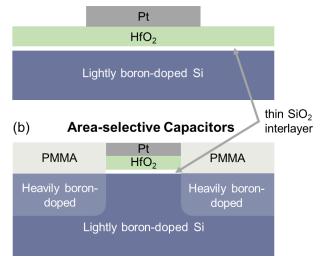

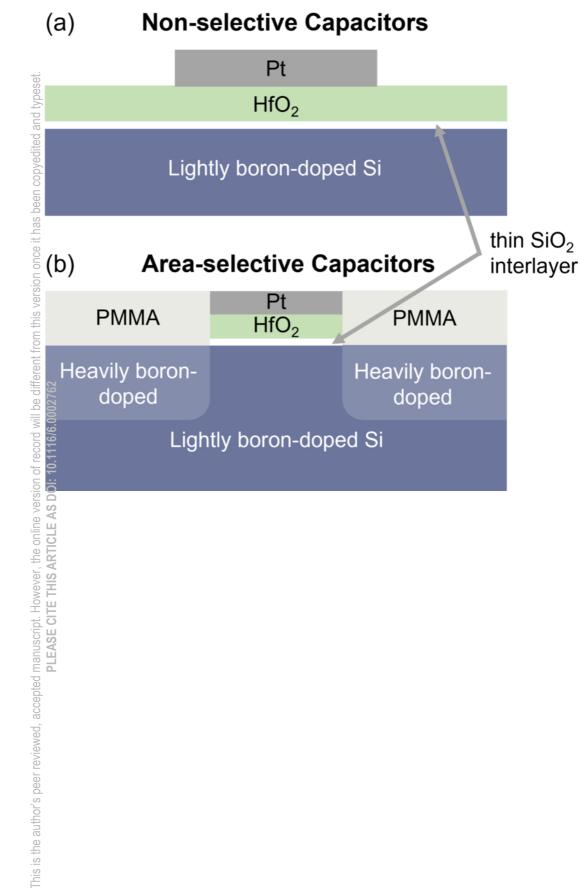

- forming approximately 85 µm x 85 µm square MOS capacitors. Figure 1a shows the

- device structure. The final process step was a forming gas anneal (FGA, 5 SCCM, 96%

- 13 N<sub>2</sub> / 4% H<sub>2</sub>) for 30 min at 400 °C, and results are shown for annealed and unannealed

- 14 capacitors.

15

PLEASE CITE THIS ARTICLE AS DOI: 10.1116/6.0002762

### Fig. 1. Schematic diagrams representing the cross-sectional device structure for non-

2 selective capacitors (a) and area-selective capacitors (b).

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

1

### B. Area-selective capacitor fabrication

To fabricate the self-aligned "area-selective" capacitors, p-type Si(100) was patterned with a thick SiO<sub>2</sub> mask and then doped with boron via solid state diffusion (2 h at 1050 °C, B<sub>2</sub>O<sub>3</sub> source) to fabricate heavily boron-doped (~10<sup>20</sup> cm<sup>-3</sup>) substrates with lightly boron-doped ( $\sim 10^{18}$  cm<sup>-3</sup>) approximately 100  $\mu m$  x 100  $\mu m$  square regions and one additional 4 mm x 12 mm area adjacent to the capacitors for physical characterization. Given the junction depth of about 1 µm, we expect boron to diffuse laterally a similar amount. The final device dimensions are 96 µm x 96 µm. This doping profile enables the use of SCALES and AS-ALD to form the self-aligned structures. With the SCALES process, a poly(methyl methacrylate) (PMMA) brush anchored to the Si surface was synthesized<sup>24</sup> across the entire substrate and selectively removed from the lightly-doped regions via cycles of exposure to potassium hydroxide (KOH) solution (1 mL 45 wt% KOH:3 mL IPA:8.5 mL DI H<sub>2</sub>O) to etch the Si and acetone to solvate the PMMA. The substrate was then cleaned with the same modified RCA clean described previously, followed by 1% HF etch and thin SiO<sub>2</sub> oxidation using the same oxidation treatments described in the non-selective capacitor methods. However, the thermal oxidation requires very high temperature which degrades the PMMA film used for patterning, so only the chemical oxide pre-treatments were used to fabricate the area-selective capacitors. After oxidation, samples were transferred to the ALD chamber for selective deposition of HfO<sub>2</sub> and Pt on the exposed lightly doped Si. HfO<sub>2</sub> was deposited with 55

cycles of thermal HfO<sub>2</sub> ALD at 200 °C using the same recipe as the non-selective

PLEASE CITE THIS ARTICLE AS DOI: 10.1116/6.0002762

- 1 capacitors. Following the HfO<sub>2</sub> deposition, Pt was deposited with 300 cycles of thermal

- 2 Pt ALD at 300 °C using (trimethyl)methylcyclopentadienylplatinum(IV) (MeCpPtMe<sub>3</sub>)

- and O<sub>2</sub>. The exposure times for MeCpPtMe<sub>3</sub> and O<sub>2</sub> were 1 and 10 s, respectively,

- 4 followed by purge times of 10 s. This fabrication process is described in detail in

- 5 previous work.<sup>23,24</sup> Figure 1b shows the resulting device structure. The final process step

- 6 was a FGA (5 SCCM, 96% N<sub>2</sub> / 4% H<sub>2</sub>) for 30 min at 400 °C, and results are shown for

- 7 annealed and unannealed capacitors.

### 8 C. Electrical Characterization

- 9 Capacitance-voltage (C-V) and conductance-voltage (G-V) measurements were

- 10 conducted with a Keithley 4200-SCS semiconductor analyzer and Cascade Microtech

- probe station. Capacitance and conductance were measured at 100 kHz with a voltage

- sweep from 2 V to -2 V. Capacitance and conductance data was normalized to device

- area. The conductance method was used to extract interface state density (D<sub>it</sub>), assuming

- a small standard deviation in the semiconductor surface potential, using the equation:<sup>30</sup>

$$15 D_{it} \approx \frac{2.5}{q} \left(\frac{G_p}{\omega}\right)_{max} (1)$$

- where q is electronic charge,  $\omega$  is angular frequency, and  $G_p$  is the conductance peak after

- extracting and correcting for series resistance using the relationships defined by Vogel et.

- al.31 The measured capacitance (Cm) and conductance (Gm) were corrected using the

- 19 following relationships:

$$20 C_c = \frac{c_m}{(1 - G_m R_s)^2 + \omega^2 C_m^2 R_s^2} (2)$$

$$21 G_c = \frac{\omega^2 C_m C_c R_s - G_m}{G_m R_s - 1} (3)$$

PLEASE CITE THIS ARTICLE AS DOI: 10.1116/6.0002762

### where C<sub>c</sub> is corrected capacitance, G<sub>c</sub> is corrected conductance and R<sub>s</sub> is series resistance.

- 2 Series resistance was extracted by numerically iterating the R<sub>s</sub> value in the corrected

- 3 conductance equation until G<sub>c</sub> is minimized throughout accumulation (or approximately

- 4 equal to tunneling conductance). After G<sub>c</sub> is obtained for 5 capacitors from each

- 5 interlayer type, the average D<sub>it</sub> value is plotted with error bars indicating the standard

- 6 deviations.

7

### D. Physical Characterization

- 8 Spectroscopic ellipsometry was used to measure film thickness. Spectroscopic

- 9 ellipsometry was performed with a Woollam M-2000 ellipsometer, and CompleteEase

- software (J.A. Woollam) was used for all spectra fitting for the SiO<sub>2</sub> and HfO<sub>2</sub> films. X-

- ray photoelectron spectroscopy (XPS) was used to physically characterize the

- composition of the SiO<sub>2</sub>/HfO<sub>2</sub> thin films. XPS measurements were performed with a

- 13 Thermo Scientific K-Alpha X-ray photoelectron spectrometer system with a

- monochromatic Al Kα source using a spot size of 400 μm and pass energy of 50 eV. The

- Si(2p) peak at 99.4 eV corresponding to elemental Si bonds from the substrate was used

- as a reference peak, and the spectra were shifted to correct the effects of experimental

- charging. XPS spectra from the capacitors did not detect the SiO<sub>2</sub> interlayer underneath

- 18 the HfO<sub>2</sub> layer and Pt electrode due to the limited penetration depth of XPS (~5-10 nm).<sup>32</sup>

- 19 To overcome this, separate samples with a thinner HfO<sub>2</sub> film and without the Pt film were

- 20 fabricated for XPS measurements. The substrates were prepared in the same way as the

- capacitor samples with only 30 cycles of HfO<sub>2</sub> ALD and no Pt deposition, and XPS

- spectra were obtained immediately after processing. Additionally, the spot size for both

- the ellipsometric and XPS measurements is larger than the area-selective capacitor device

PLEASE CITE THIS ARTICLE AS DOI: 10.1116/6.0002762

### size, so the measurements were performed on the larger patterned area adjacent to the

- 2 capacitor devices. We assume the film thickness to be relatively uniform across the

- 3 growth regions of the patterned substrate.

### 4 III. RESULTS AND DISCUSSION

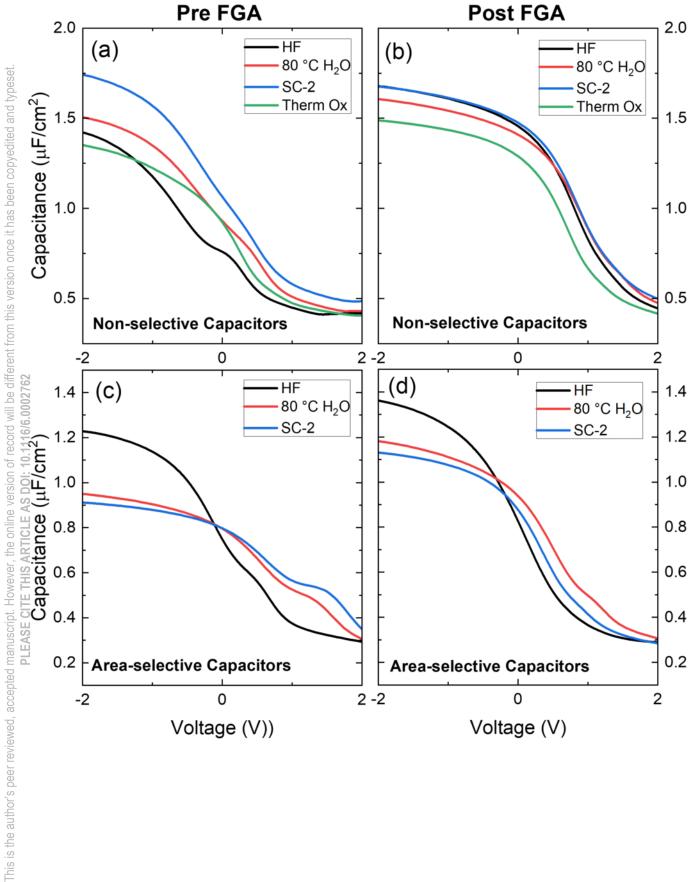

- 5 Figure 2 shows representative curves of C-V behavior for non-selective and area-

- 6 selective capacitors before and after the FGA. The C-V curves exhibit expected behavior

- 7 for MOS capacitors. A difference in maximum capacitance measured for each pre-

- 8 treatment is noted in addition to presence of interface states. Small variations in SiO<sub>2</sub>

- 9 thickness for different oxidation methods are likely responsible for the differences in the

- measured maximum capacitances. Ellipsometry measurements during fabrication indicate

- that the HfO<sub>2</sub> film thickness for all of the non-selective capacitors was 6.2 nm with the

- following SiO<sub>2</sub> interlayer thicknesses from each pre-treatment: 0.7 nm from HF, 1.1 nm

- from 80 °C H<sub>2</sub>O, 1 nm from SC-2, and 1.4 nm from thermal oxidation. Similarly for all

- of the area-selective capacitors, the HfO<sub>2</sub> film was 6.1 nm thick with slightly thicker SiO<sub>2</sub>

- interlayer thicknesses: 1.0 nm from HF, 1.5 nm from 80 °C H<sub>2</sub>O, and 1.5 nm from SC-2.

- Ellipsometry measurements show a slightly thicker SiO<sub>2</sub> layer for the area-selective

- capacitors, corresponding to a 0.3-0.5 nm difference in thickness. The differences in

- thickness between the selective and non-selective cases may be due to a difference in

- surface roughness from the KOH etching, which can result in overestimation of film

- 20 thickness for ellipsometry.<sup>33</sup> And the extra process steps for the area-selective capacitors

- 21 can cause changes in surface properties that impact oxidation.

PLEASE CITE THIS ARTICLE AS DOI: 10.1116/6.0002762

Fig. 2. Capacitance-voltage characteristics of non-selective (a and b) and area-selective (c and d) Pt-HfO<sub>2</sub>-Si MOS capacitors before (a and c) and after (b and d) a FGA. Each graph shows a representative C-V curve of one capacitor with each SiO<sub>2</sub> interlayer treatment: HF, 80 °C H<sub>2</sub>O, SC-2, and thermal oxide (non-selective only).

Both sample sets show improved performance after the FGA as indicated by the reduced stretch out of the curves. The slight differences in maximum capacitance after the FGA can likely be attributed to a combination of factors including formation of Hf silicate at the interface,<sup>34</sup> increased dielectric constant due to polycrystallization,<sup>35</sup> and diffusion of carbon residue to the surface (*vide infra*). Combining the measured SiO<sub>2</sub> and HfO<sub>2</sub> thicknesses with maximum capacitances between 1.3 and 1.7  $\mu$ F/cm<sup>2</sup> yields an estimate of a relative dielectric constant of ~20 for the non-selective HfO<sub>2</sub> films, which is expected for ALD HfO<sub>2</sub>.<sup>36</sup> Similarly for the area-selective HfO<sub>2</sub> films with maximum

PLEASE CITE THIS ARTICLE AS DOI: 10.1116/6.0002762

- 1 capacitances measured between 0.9 and 1.2  $\mu$ F/cm<sup>2</sup>, a relative dielectric constant of ~19

- 2 is estimated, which is very similar to that of the non-selective capacitors.

3

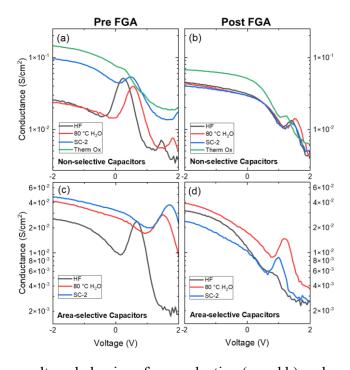

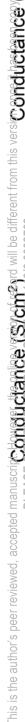

Fig. 3. Conductance-voltage behavior of non-selective (a and b) and area-selective (c and d) Pt-HfO<sub>2</sub>-Si MOS capacitors before (a and c) and after (b and d) a FGA. Each graph

- 6 shows a representative G-V curve of one capacitor with each SiO<sub>2</sub> interlayer treatment:

- 7 HF, 80 °C H<sub>2</sub>O, SC-2, and thermal oxide (non-selective only).

8

9

10

11

12

13

14

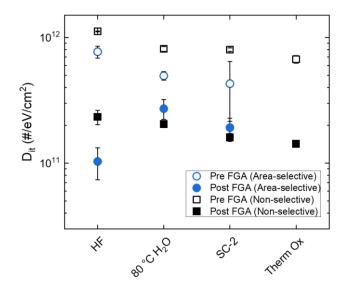

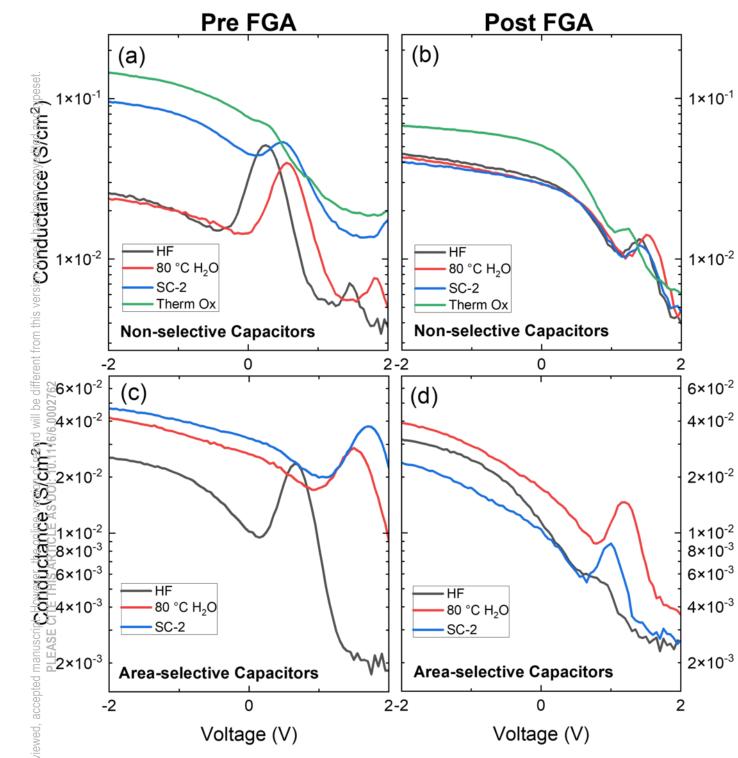

The humps observed in the pre-FGA capacitance curves indicate significant interface state density ( $D_{it}$ ), so conductance measurements are used to better investigate  $D_{it}$ . Figure 3 shows the voltage dependance of measured conductance ( $G_m$ ) for a device with each oxidation technique for both the non-selective and area-selective capacitors. The peaks seen in the  $G_m$  curves are attributed to interface states.  $D_{it}$  is extracted for 5

11

capacitors for each interlayer type before and after FGA as shown in Fig. 4. The interface

PLEASE CITE THIS ARTICLE AS DOI: 10.1116/6.0002762

16

### state density is observed to decrease significantly with the FGA. The average Dit

- decreases from  $8.5 \times 10^{11} \, eV^{-1} cm^{-2}$  to  $1.9 \times 10^{11} \, eV^{-1} cm^{-2}$  for the non-selective capacitors

- 3 and from  $5.7 \times 10^{11} \text{ eV}^{-1}\text{cm}^{-2}$  to  $1.9 \times 10^{11} \text{ eV}^{-1}\text{cm}^{-2}$  for the area-selective capacitors.

- 4 These post FGA values are similar to what is typically observed for HfO<sub>2</sub>/Si gate stacks

- 5  $(\sim 10^{11} \text{ eV}^{-1}\text{cm}^{-2})$ . <sup>37,38</sup> The D<sub>it</sub> for the wet chemical SiO<sub>2</sub> interlayers is similar to that of the

- 6 thermal oxide, and there is no significant difference between the non-selective and area-

- 7 selective samples. The results show that the area-selective process does not have a

- 8 negative impact on electrical performance relative to the non-selective process, and using

- 9 any of the wet chemical interlayer techniques results in formation of an interface that

- 10 functions similarly to the thermal oxide interlayer. However, the standard deviations of

- the D<sub>it</sub> are larger for the area-selective processes as compared to the non-selective

- process. The extra processing steps for the area-selective capacitors (i.e., polymer

- synthesis and KOH etch) likely roughen the surface and leave carbon residue unevenly

- distributed across the Si surface. This can result in more extrinsic defects and impurities

- in some regions of the substrate, leading to more variability in electrical performance.

Fig. 4. Estimated D<sub>it</sub> values for non-selective (black) and area-selective (blue) Pt-HfO<sub>2</sub>-Si

MOS capacitors before and after the FGA.

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

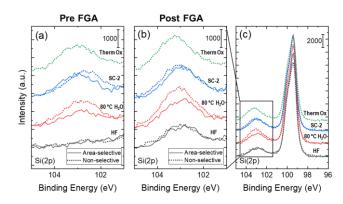

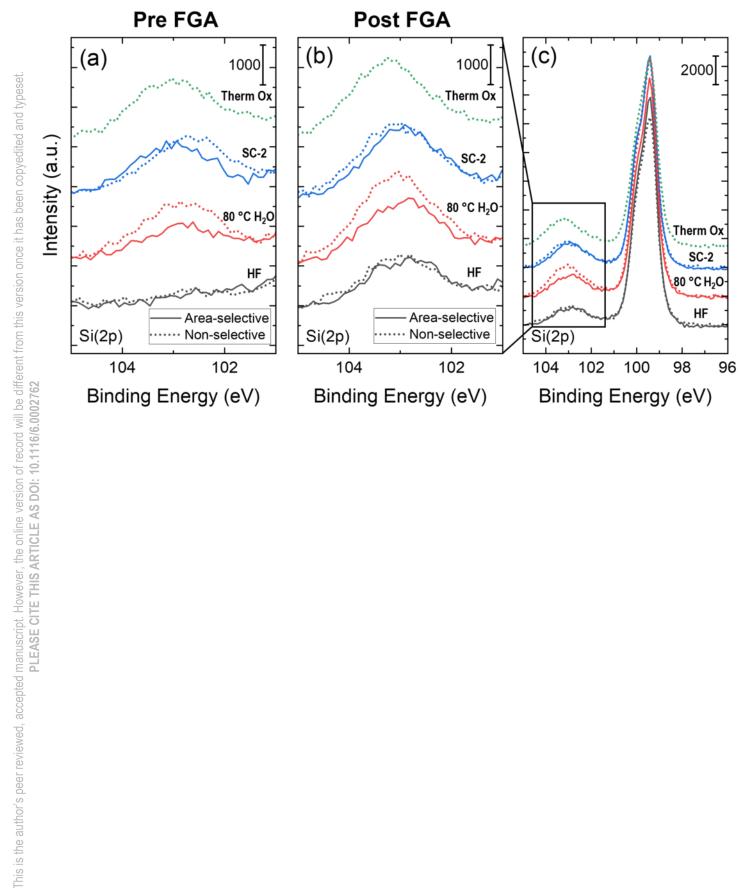

XPS is used to physically characterize the oxide-semiconductor interface of the capacitor structure to understand the impact of the processing on the composition of the interlayer. Figure 5 shows XPS spectra of the Si(2p) region obtained from HfO<sub>2</sub>/SiO<sub>2</sub>/Si substrates that were treated with the same initial processing steps as the capacitors (i.e., modified RCA clean, interlayer oxidation, HfO<sub>2</sub> ALD, and FGA for the non-selective set; PMMA, KOH etch, modified RCA clean, interlayer oxidation, HfO<sub>2</sub> ALD, and FGA for the area-selective set). All substrates show the expected elemental Si doublet peak near 99.4 eV (seen in Fig. 5c for substrates after FGA) due to the bulk Si substrate. The oxidized Si(2p) peak for stoichiometric SiO<sub>2</sub> would be expected near 103.5 eV (referenced to elemental Si at 99.4 eV).<sup>39</sup> Peaks representing lower oxidation states of Si (Si<sup>1+</sup>, Si<sup>2+</sup>, Si<sup>3+</sup>) and Hf silicate compounds have binding energies between 99.4 eV and 103.5 eV. 40-42 With the exception of the pre-anneal HF-treated substrates, all samples have a small peak near 103.5 eV (seen in Fig. 5). These peaks are broader and slightly closer to the elemental Si peak than a stoichiometric SiO<sub>2</sub> peak would be, indicating they are likely a convoluted peak consisting of multiple overlapping peaks attributed to SiO<sub>2</sub>, Si suboxides in multiple oxidation states (SiO<sub>x</sub>), and Hf silicate compounds. With the HF pre-treatment, no clear Si(2p) suboxide photoelectron peak is observed before the FGA (but a subtle left-side shoulder of the elemental Si(2p) peak allowed for fitting of a very small suboxide peak for comparison). This suggests very

Si(2p) suboxide peak at 103.0 eV and 102.8 eV for the non-selective deposition substrate

minimal formation of an interlayer during ALD. After the FGA, the appearance of an

PLEASE CITE THIS ARTICLE AS DOI: 10.1116/6.0002762

7

9

12

13

14

15

16

17

18

19

and the area-selective deposition substrate, respectively, indicates formation of an

2 interfacial layer between the Si and HfO<sub>2</sub> film, which is typically seen with annealing of

3 HfO<sub>2</sub> films. 43,44 Excess oxygen in the HfO<sub>2</sub> film in the form of hydroxyl groups can react

4 with Si at the interface to form an interlayer upon thermal treatment. 43 Oxygen impurity

5 in the forming gas is also a possibility, which could allow for diffusion of oxygen through

6 the HfO<sub>2</sub> layer to facilitate SiO<sub>2</sub> growth at the interface.<sup>45</sup>

8 Fig. 5. Si(2p) XPS spectra of non-selective (dotted line) and area-selective (solid line)

- HfO<sub>2</sub> films on Si with different SiO<sub>2</sub> interfacial layers before (a) and after (b) the FGA;

- 10 (a) and (b) show a narrower region to see the oxidized Si(2p) peaks in more detail; (c)

- shows the full Si(2p) spectrum of all substrates after the FGA.

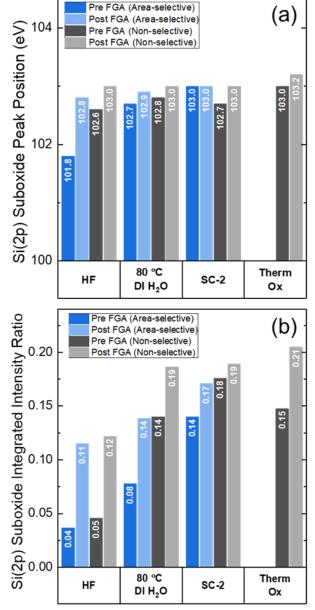

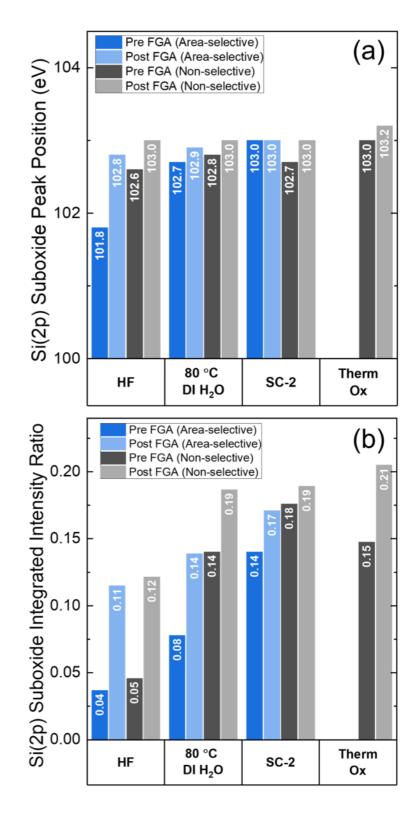

After the FGA, an increase in the peak area of the Si(2p) suboxide photoelectron peak is observed for all interlayer types and most of the peaks blueshift. Figure 6a shows the peak positions of the Si(2p) suboxide peak for each interlayer type before and after annealing. Figure 6b shows the ratio of integrated intensity of the suboxide Si(2p) peak normalized to the integrated intensity of the elemental Si(2p) peak before and after the FGA for each interlayer type. In general, we see the Si(2p) suboxide peak shift to a binding energy 0.2-0.3 eV higher after the FGA. The integrated intensity ratio of the Si

suboxide peak shows a 30-80% increase for the 80 °C H<sub>2</sub>O treated substrates, 10-20%

2 increase for the SC-2 treated substrates, and 40% increase for the thermal oxide treated

3 substrate. This increased intensity and shift towards the binding energy of stoichiometric

4 SiO<sub>2</sub> (i.e., 103.5 eV) for most cases suggests formation of higher quality SiO<sub>2</sub> at the

5 interface after the FGA. The level of D<sub>it</sub> depends on numerous factors, including surface

6 roughness, the stoichiometry and thickness of the interfacial SiO<sub>2</sub> layer, and presence of

7 hydrogen. The differences in the binding energy of the Si(2p) peak does not explain the

8 differences for the D<sub>it</sub> as a function of interlayer type. However, we do observe a shift

9 post FGA that correlates to the improved electrical performance. Suboxide states of Si

induce strain and dangling bonds at the interface, which can trap charges and lead to

electronic interface defects. 46 The FGA leading to more stoichiometric SiO<sub>2</sub> at the

interface is therefore consistent with a reduced interface state density.

PLEASE CITE THIS ARTICLE AS DOI: 10.1116/6.0002762

5

6

Fig. 6. XPS peak positions of the suboxide Si(2p) peak (a) and ratio of XPS integrated

- 2 intensity of the suboxide Si(2p) peak to integrated intensity of elemental Si(2p) peak (b)

- 3 before and after the FGA for area-selective deposition and non-selective deposition

- 4 HfO<sub>2</sub>/SiO<sub>2</sub>/Si substrates treated with different SiO<sub>2</sub> interlayer formation techniques.

- The Si(2p) suboxide peak from the SC-2 treated area-selective deposition

- 7 substrate is the only one that does not shift position after the FGA. For the SC-2 pre-

PLEASE CITE THIS ARTICLE AS DOI: 10.1116/6.0002762

1 treatment, the Si(2p) spectra from the non-selective deposition substrate indicate a Si

2 suboxide peak shift from 102.7 eV to 103.0 eV after annealing, but the position of the Si

3 suboxide peak from the area-selective deposition substrate remains unchanged at 103.0

4 eV. The integrated area ratio of the peak did increase, however, suggesting an increase in

5 the amount of interfacial SiO<sub>x</sub> consistent with what we observe with the other substrates.

6

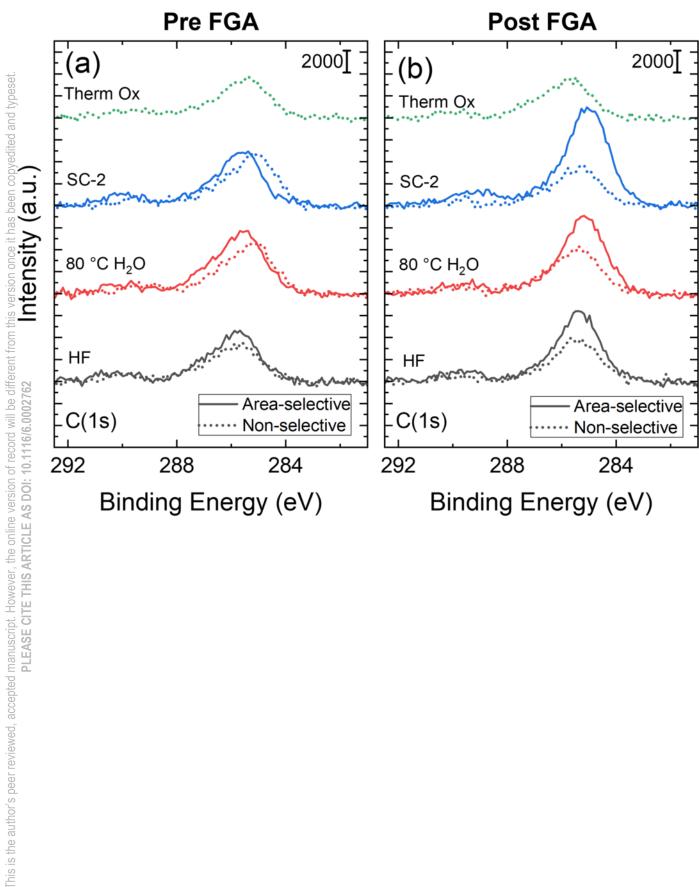

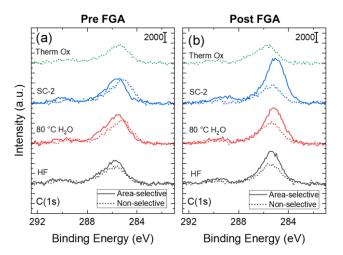

Fig. 7. C(1s) XPS spectra of non-selective (dotted line) and area-selective (solid line)

8 HfO<sub>2</sub> films on Si with different SiO<sub>2</sub> interfacial layers before (a) and after (b) the FGA.

9

11

12

13

14

15

16

17

XPS spectra in the C(1s) region for all substrates are shown in Fig. 7. The HfO<sub>2</sub> ALD precursor (TDMAHf) contains methyl carbon groups, so a small amount of carbon is expected in the HfO<sub>2</sub> film in addition to adventitious carbon. Figure 6a shows very similar spectra for all substrates before the FGA, with the small expected C(1s) photoelectron peaks at 285 eV and 289 eV.<sup>47</sup> After annealing however, there is a notable difference between the non-selective and area-selective capacitors. While the C(1s) spectra from the non-selective capacitors show no change in carbon content after

annealing, the C(1s) spectra from the area-selective capacitors all show larger carbon

# PLEASE CITE THIS ARTICLE

8

15

16

17

18

19

20

21

22

23

| et e                                                                           |                             |

|--------------------------------------------------------------------------------|-----------------------------|

| S                                                                              |                             |

| Φ                                                                              |                             |

| 9                                                                              |                             |

| Ψ,                                                                             |                             |

| 0                                                                              |                             |

| a                                                                              |                             |

|                                                                                |                             |

| 60                                                                             |                             |

| $\pm$                                                                          |                             |

| 0                                                                              |                             |

| 8                                                                              |                             |

| 0                                                                              |                             |

| 0                                                                              |                             |

| 0                                                                              |                             |

| e                                                                              |                             |

| 9                                                                              |                             |

| Ŏ                                                                              |                             |

|                                                                                |                             |

| Œ                                                                              |                             |

|                                                                                |                             |

| <u>:</u>                                                                       |                             |

| Φ                                                                              |                             |

| nce                                                                            |                             |

| 0                                                                              |                             |

|                                                                                |                             |

| 0                                                                              |                             |

| . <u>S</u>                                                                     |                             |

| _                                                                              |                             |

| 9                                                                              |                             |

| S                                                                              |                             |

| - 2                                                                            |                             |

| Ţ                                                                              |                             |

| OM                                                                             |                             |

| Ö                                                                              |                             |

| Ţ                                                                              |                             |

| +                                                                              |                             |

|                                                                                |                             |

| 9                                                                              |                             |

| Φ                                                                              | N                           |

| 生                                                                              | 62                          |

| 0                                                                              |                             |

| pe (                                                                           | 02                          |

|                                                                                | 9                           |

| =                                                                              | 0                           |

| $\leq$                                                                         | 9                           |

| 0                                                                              | 79                          |

| O                                                                              | =                           |

| 0                                                                              | ÷                           |

| ற                                                                              | $\overline{}$               |

| 4                                                                              | 0                           |

| 0                                                                              | $\overline{}$               |

|                                                                                |                             |

|                                                                                |                             |

| U                                                                              | <u>::</u>                   |

| .0                                                                             | 00                          |

|                                                                                |                             |

| Versio                                                                         | AS DOI:                     |

| e versio                                                                       | AS D                        |

| Versio                                                                         | AS D                        |

| nline versio                                                                   | LE AS D                     |

| online versio                                                                  | LE AS D                     |

| online versio                                                                  | TICLE AS D                  |

| nline versio                                                                   | LE AS D                     |

| , the online versio                                                            | TICLE AS D                  |

| online versio                                                                  | S ARTICLE AS D              |

| ver, the online versio                                                         | S ARTICLE AS D              |

| ver, the online versio                                                         | HIS ARTICLE AS D            |

| ver, the online versio                                                         | THIS ARTICLE AS D           |

| wever, the online versio                                                       | THIS ARTICLE AS D           |

| wever, the online versio                                                       | THIS ARTICLE AS D           |

| However, the online version                                                    | E THIS ARTICLE AS D         |

| ript. However, the online versio                                               | CITE THIS ARTICLE AS D      |

| cript. However, the online versio                                              | E CITE THIS ARTICLE AS D    |

| script. However, the online versio                                             | SE CITE THIS ARTICLE AS D   |

| nuscript. However, the online versio                                           | EASE CITE THIS ARTICLE AS D |

| anuscript. However, the online versio                                          | EASE CITE THIS ARTICLE AS D |

| nuscript. However, the online versio                                           | EASE CITE THIS ARTICLE AS D |

| d manuscript. However, the online versio                                       | EASE CITE THIS ARTICLE AS D |

| ed manuscript. However, the online versio                                      | EASE CITE THIS ARTICLE AS D |

| pted manuscript. However, the online versio                                    | EASE CITE THIS ARTICLE AS D |

| epted manuscript. However, the online versio                                   | EASE CITE THIS ARTICLE AS D |

| ccepted manuscript. However, the online versio                                 | EASE CITE THIS ARTICLE AS D |

| cepted manuscript. However, the online versio                                  | EASE CITE THIS ARTICLE AS D |

| , accepted manuscript. However, the online versio                              | EASE CITE THIS ARTICLE AS D |

| ed, accepted manuscript. However, the online versio                            | EASE CITE THIS ARTICLE AS D |

| ed, accepted manuscript. However, the online versio                            | EASE CITE THIS ARTICLE AS D |

| ed, accepted manuscript. However, the online versio                            | EASE CITE THIS ARTICLE AS D |

| viewed, accepted manuscript. However, the online versio                        | EASE CITE THIS ARTICLE AS D |

| eviewed, accepted manuscript. However, the online versio                       | EASE CITE THIS ARTICLE AS D |

| r reviewed, accepted manuscript. However, the online versio                    | EASE CITE THIS ARTICLE AS D |

| er reviewed, accepted manuscript. However, the online versio                   | EASE CITE THIS ARTICLE AS D |

| eer reviewed, accepted manuscript. However, the online versio                  | EASE CITE THIS ARTICLE AS D |

| peer reviewed, accepted manuscript. However, the online versio                 | EASE CITE THIS ARTICLE AS D |

| s peer reviewed, accepted manuscript. However, the online versio               | EASE CITE THIS ARTICLE AS D |

| or's peer reviewed, accepted manuscript. However, the online versio            | EASE CITE THIS ARTICLE AS D |

| hor's peer reviewed, accepted manuscript. However, the online versio           | EASE CITE THIS ARTICLE AS D |

| uthor's peer reviewed, accepted manuscript. However, the online versio         | EASE CITE THIS ARTICLE AS D |

| author's peer reviewed, accepted manuscript. However, the online versio        | EASE CITE THIS ARTICLE AS D |

| e author's peer reviewed, accepted manuscript. However, the online versio      | EASE CITE THIS ARTICLE AS D |

| author's peer reviewed, accepted manuscript. However, the online versio        | EASE CITE THIS ARTICLE AS D |

| e author's peer reviewed, accepted manuscript. However, the online versio      | EASE CITE THIS ARTICLE AS D |

| is the author's peer reviewed, accepted manuscript. However, the online versio | EASE CITE THIS ARTICLE AS D |

| the author's peer reviewed, accepted manuscript. However, the online versio    | EASE CITE THIS ARTICLE AS D |

| 1 | peaks. After the FGA, the atomic percentage of carbon ranges from 6-8% for the non-                 |

|---|-----------------------------------------------------------------------------------------------------|

| 2 | selective substrates and from 9-12% for the area-selective substrates. This larger atomic           |

| 3 | percentage of carbon in the area-selective substrates is likely due to carbon residue               |

| 4 | leftover from the patterned PMMA diffusing up through the HfO <sub>2</sub> film or laterally across |

| 5 | the substrate. The average $D_{it}$ of the area-selective and non-selective capacitors is similar,  |

| 6 | so this extra carbon present on the surface and in the film does not lead to more                   |

| 7 | electrically active defects at the interface. However, the area-selective capacitors do             |

9 The polymer synthesis and KOH etch processing steps for the area-selective deposition

exhibit more variation in performance, indicated by larger standard deviations for Dit.

10 substrates can leave more extrinsic defects and impurities in some regions of the 11

12 procedure after patterning the PMMA film should be investigated with future work to

substrate, leading to more variability in electrical performance. A more thorough cleaning

13 minimize the excess carbon observed in the film to ensure more reliable performance

between devices. 14

### IV. SUMMARY AND CONCLUSIONS

In summary, Pt-HfO<sub>2</sub>-Si MOS capacitors are studied to compare self-aligned area-selective structures with conventional non-selective devices. Various chemical oxidation techniques, including HF-last, 80 °C H<sub>2</sub>O, and SC-2 treatment, are used to form an SiO<sub>2</sub> interfacial layer to compare with a high temperature thermal oxidation. The areaselective capacitors perform as well as the non-selective capacitors, and all oxidation treatments exhibit similar electrical performance, with interface state densities near 2 x 10<sup>11</sup> eV<sup>-1</sup>cm<sup>-2</sup> after a FGA. XPS data for the HfO<sub>2</sub>-Si interface indicates an increase in

4

5

14

21

### 1 SiO<sub>2</sub> in the interfacial layer after the FGA, which is consistent with the improved

- 2 interface state density. XPS data also shows presence of extra carbon after annealing the

- area-selective samples, but this does not significantly impact performance.

### 6 ACKNOWLEDGMENTS

- 7 This work was supported by the Department of Defense (DOD) through the National

- 8 Defense Science & Engineering Graduate (NDSEG) Fellowship Program, Defense

- 9 Advanced Research Projects Agency (W911NF2110298), and the National Science

- 10 Foundation (CMMI-1916953). This work was performed in part at the Georgia Tech

- 11 Institute for Electronics and Nanotechnology, a member of the National Nanotechnology

- 12 Coordinated Infrastructure (NNCI), which is supported by the National Science

- Foundation (ECCS-2025462).

### 15 AUTHOR DECLARATIONS

- 16 Conflicts of Interest (required)

- 17 The authors have no conflicts to disclose.

### 18 DATA AVAILABILITY

- 19 The data that support the findings of this study are available from the corresponding

- author upon reasonable request.

### 22 REFERENCES

<sup>1</sup> J. W. Yang, P. M. Zeitzoff, and H. H. Tseng, IEEE Trans. Electron Devices 54, 1464 (2007).

- S. S. Rodriguez, J. C. Tinoco, A. G. Martinez-Lopez, J. Alvarado, and J. P. Raskin,

IEEE Trans. Electron Devices 60, 3710 (2013).

- <sup>3</sup> A. Veloso, L. Å. Ragnarsson, M. J. Cho, K. Devriendt, K. Kellens, F. Sebaai, S. Suhard,

S. Brus, Y. Crabbe, and T. Schram, "Gate-last vs. gate-first technology for

- 5 aggressively scaled EOT logic/RF CMOS," 2011 Symposium on VLSI Technology -

- 6 Digest of Technical Papers, Kyoto, Japan, 2011, pp. 34-35.

- C. Li, H. Zhu, Y. Zhang, Q. Wang, X. Yin, J. Li, G. Wang, Z. Kong, X. Ai, and L. Xie,

Nano Lett. 21, 4730 (2021).

- <sup>5</sup> H. Mertens, R. Ritzenthaler, A. Hikavyy, M. S. Kim, Z. Tao, K. Wostyn, S. A. Chew,

- 10 A. De Keersgieter, G. Mannaert, and E. Rosseel, "Gate-all-around MOSFETs based

- on vertically stacked horizontal Si nanowires in a replacement metal gate process on

- bulk Si substrates," 2016 IEEE Symposium on VLSI Technology, Honolulu, HI,

- 13 USA, 2016, pp. 1-2.

- <sup>6</sup> S. Datta, S. Dutta, B. Grisafe, J. Smith, S. Srinivasa, and H. Ye, IEEE Micro 39, 8

(2019).

- <sup>7</sup>D. Akinwande, N. Petrone, and J. Hone, Nat. Commun. 5, 5678 (2014).

- 8 S. Seo, B. C. Yeo, S. S. Han, C. M. Yoon, J. Y. Yang, J. Yoon, C. Yoo, H. J. Kim, Y. B.

Lee, and S. J. Lee, ACS Appl. Mater. Interfaces 9, 41607 (2017).

- <sup>9</sup> R. Chen, H. Kim, P. C. McIntyre, and S. F. Bent, Appl. Phys. Lett. 84, 4017 (2004).

- 20 <sup>10</sup> R. Chen, H. Kim, P. C. McIntyre, D. W. Porter, and S. F. Bent, Appl. Phys. Lett. 86,

21 191910 (2005).

- <sup>11</sup> K. J. Park, J. M. Doub, T. Gougousi, and G. N. Parsons, Appl. Phys. Lett. 86, 051903

(2005).

- <sup>12</sup> F. S. Minaye Hashemi, C. Prasittichai, and S. F. Bent, ACS Nano 9, 8710 (2015).

- 25 <sup>13</sup> W. H. Kim, K. Heo, Y. K. Lee, T. M. Chung, C. G. Kim, S. Hong, J. Heo, and H. Kim,

J. Electrochem. Soc. 158, D1 (2011).

- <sup>14</sup> H. B. R. Lee, W. H. Kim, J. W. Lee, J. M. Kim, K. Heo, I. C. Hwang, Y. Park, S.

Hong, and H. Kim, J. Electrochem. Soc. 157, D10 (2010).

- 15 R. Wojtecki, J. Ma, I. Cordova, N. Arellano, K. Lionti, T. Magbitang, T. G. Pattison,

X. Zhao, E. Delenia, and N. Lanzillo, ACS Appl. Mater. Interfaces 13, 9081 (2021).

- 31 <sup>16</sup> E. Färm, M. Kemell, M. Ritala, and M. Leskelä, J. Phys. Chem. C 112, 15791 (2008).

- 32 <sup>17</sup> E. Färm, M. Kemell, E. Santala, M. Ritala, and M. Leskelä, J. Electrochem. Soc. 157, K10 (2010).

- 34 <sup>18</sup> A. Sinha, D. W. Hess, and C. L. Henderson, J. Vac. Sci. Technol. B 24, 2523 (2006).

- 35 <sup>19</sup> V. Suresh, M. S. Huang, M. P. Srinivasan, C. Guan, H. J. Fan, and S. Krishnamoorthy,

36 J. Phys. Chem. C 116, 23729 (2012).

- 37 <sup>20</sup> A. Sinha, D. W. Hess, and C. L. Henderson, J. Vac. Sci. Technol. B 25, 1721 (2007).

- 1 <sup>21</sup> T. G. Pattison, A. E. Hess, N. Arellano, N. Lanzillo, S. Nguyen, H. Bui, C. Rettner, H. Truong, A. Friz, and T. Topuria, ACS Nano 14, 4276 (2020).

- 3 <sup>22</sup> M. Fang and J. C. Ho, ACS Nano 9, 8651 (2015).

- <sup>23</sup> A. C. Brummer, A. T. Mohabir, D. Aziz, M. A. Filler, and E. M. Vogel, Appl. Phys.

Lett. 119, 142901 (2021).

- <sup>24</sup> A. T. Mohabir, D. Aziz, A. C. Brummer, K. E. Taylor, E. M. Vogel, and M. A. Filler,

Nanotechnology 33, 105604 (2022).

- 8 <sup>25</sup> A. T. Mohabir, G. Tutuncuoglu, T. Weiss, E. M. Vogel, and M. A. Filler, ACS Nano 14, 282 (2020).

- <sup>26</sup> B. H. Lee, L. Kang, R. Nieh, W. J. Qi, and J. C. Lee, Appl. Phys. Lett. 76, 1926 (2000).

- 11 <sup>27</sup> S. Sayan, E. Garfunkel, and S. Suzer, Appl. Phys. Lett. 80, 2135 (2002).

- 12 <sup>28</sup> M. L. Green, M. Y. Ho, B. Busch, G. Wilk, T. Sorsch, T. Conard, B. Brijs, W.

- Vandervorst, P. Räisänen, and D. Muller, J. Appl. Phys. 92, 7168 (2002).

- 14 <sup>29</sup> H. Angermann, Appl. Surf. Sci. 312, 3 (2014).

- 30 D. K. Schroder, Semiconductor material and device characterization. (John Wiley & Sons, 2015).

- 17 <sup>31</sup> E. M. Vogel, W. K. Henson, C. A. Richter, and J. S. Suehle, IEEE Trans. Electron Devices 47, 601 (2000).

- 19 <sup>32</sup> F. A. Stevie and C. L. Donley, J. Vac. Sci. Technol. A 38, 063204 (2020).

- 20 <sup>33</sup> D. Aspnes, J. Theeten, and F. Hottier, Phys. Rev. B 20, 3292 (1979).

- 21 <sup>34</sup> G. He, L. Zhang, and Q. Fang, J. Appl. Phys. 100, 083517 (2006).

- 35 S. W. Jeong, H. Lee, K. Kim, M. You, Y. Roh, T. Noguchi, W. Xianyu, and J. Jung,

Thin Solid Films 515, 526 (2006).

- <sup>36</sup> H. Kim, K. C. Saraswat, and P. C. McIntyre, J. Mater. Res. 20, 3125 (2005).

- 37 J. P. Han, E. M. Vogel, E. Gusev, C. D'Emic, C. A. Richter, D. W. Heh, and J. S.

Suehle, IEEE Electron Device Lett. 25, 126 (2004).

- 38 S. Dueñas, H. Castán, H. Garcia, J. Barbolla, K. Kukli, J. Aarik, and A. Aidla,

Semicond. Sci. Technol. 19, 1141 (2004).

- 39 D. S. Jensen, S. S. Kanyal, N. Madaan, M. A. Vail, A. E. Dadson, M. H. Engelhard,

and M. R. Linford, Surf. Sci. Spectra 20, 36 (2013).

- 31 <sup>40</sup> G. Pant, P. Punchaipetch, M. Kim, R. M. Wallace, and B. E. Gnade, Thin Solid Films 32 460, 242 (2004).

- 41 P. Punchaipetch, G. Pant, M. Quevedo-Lopez, H. Zhang, M. El-Bouanani, M. Kim, R.

Wallace, and B. Gnade, Thin Solid Films 425, 68 (2003).

- 35 <sup>42</sup> O. Renault, D. Samour, J. F. Damlencourt, D. Blin, F. Martin, S. Marthon, N. Barrett,

36 and P. Besson, Appl. Phys. Lett. 81, 3627 (2002).

10 11

15

20

25

28

### 43 A. Deshpande, R. Inman, G. Jursich, and C. G. Takoudis, J. Appl. Phys. 99, 094102 (2006).

- 44 M. T. Ho, Y. Wang, R. T. Brewer, L. S. Wielunski, Y. J. Chabal, N. Moumen, and M. Boleslawski, Appl. Phys. Lett. 87, 133103 (2005).

- 5 <sup>45</sup> K. Kukli, T. Pilvi, M. Ritala, T. Sajavaara, J. Lu, and M. Leskelä, Thin Solid Films 491, 328 (2005).

- <sup>46</sup> B. Stegemann, K. M. Gad, P. Balamou, D. Sixtensson, D. Vössing, M. Kasemann, and H. Angermann, Appl. Surf. Sci. 395, 78 (2017).

- 9 <sup>47</sup> J. C. Hackley and T. Gougousi, Thin Solid Films 517, 6576 (2009).

### 12 FIGURE CAPTIONS

- Fig. 1. Schematic diagrams representing the cross-sectional device structure for non-

- selective capacitors (a) and area-selective capacitors (b).

- Fig. 2. Capacitance-voltage characteristics of non-selective (a and b) and area-selective (c

- and d) Pt-HfO<sub>2</sub>-Si MOS capacitors before (a and c) and after (b and d) a FGA. Each

- graph shows a representative C-V curve of one capacitor with each SiO<sub>2</sub> interlayer

- 19 treatment: HF, 80 °C H<sub>2</sub>O, SC-2, and thermal oxide (non-selective only).

- Fig. 3. Conductance-voltage behavior of non-selective (a and b) and area-selective (c and

- d) Pt-HfO<sub>2</sub>-Si MOS capacitors before (a and c) and after (b and d) a FGA. Each graph

- shows a representative G-V curve of one capacitor with each SiO<sub>2</sub> interlayer treatment:

- 24 HF, 80 °C H<sub>2</sub>O, SC-2, and thermal oxide (non-selective only).

- Fig. 4. Estimated D<sub>it</sub> values for non-selective (black) and area-selective (blue) Pt-HfO<sub>2</sub>-Si

- 27 MOS capacitors before and after the FGA.

- 29 Fig. 5. Si(2p) XPS spectra of non-selective (dotted line) and area-selective (solid line)

- 30 HfO<sub>2</sub> films on Si with different SiO<sub>2</sub> interfacial layers before (a) and after (b) the FGA;

- 31 (a) and (b) show a narrower region to see the oxidized Si(2p) peaks in more detail; (c)

- 32 shows the full Si(2p) spectrum of all substrates after the FGA.

### ACCEPTED MANUSCRIPT

### Journal of Vacuum Science & Technology

This is the author's peer reviewed, accepted manuscript. However, the online version of record will be different from this version once it has been copyedited and typeset.

PLEASE CITE THIS ARTICLE AS DOI: 10.1116/6.0002762

- Fig. 6. XPS peak positions of the suboxide Si(2p) peak (a) and ratio of XPS integrated

- 2 intensity of the suboxide Si(2p) peak to integrated intensity of elemental Si(2p) peak (b)

- 3 before and after the FGA for area-selective deposition and non-selective deposition

- 4 HfO<sub>2</sub>/SiO<sub>2</sub>/Si substrates treated with different SiO<sub>2</sub> interlayer formation techniques.

5

- 6 Fig. 7. C(1s) XPS spectra of non-selective (dotted line) and area-selective (solid line)

- 7 HfO<sub>2</sub> films on Si with different SiO<sub>2</sub> interfacial layers before (a) and after (b) the FGA.

8

### Science & Technology A Journal of Vacuum

### ACCEPTED MANUSCRIPT

### Journal of Vacuum Science & Technology A

### Journal of Vacuum Science & Technology A

### ACCEPTED MANUSCRIPT

### Journal of Vacuum

# Science & Technology A

This is the author's peer reviewed, accepted manuscript. However, the online version of record will be different from this version once it has been copyedited and typeset. PLEASE CITE THIS ARTICLE AS DOI: 10.1116/6.0002762

### Science & Technology A Journal of Vacuum