Contents lists available at ScienceDirect

# Microprocessors and Microsystems

journal homepage: www.elsevier.com/locate/micpro

# A run-time verification method with consideration of uncertainties for cyber–physical systems

Mohammadreza Mehrabian <sup>a</sup>,\*, Mohammad Khayatian <sup>b</sup>, Aviral Shrivastava <sup>c</sup>, Patricia Derler <sup>d</sup>, Hugo Andrade <sup>e</sup>

- a South Dakota School of Mines and Technology, USA

- b Vecna Robotics, USA

- <sup>c</sup> Arizona State University, USA

- d PARC, a Xerox Company, USA

- e AMD Inc., USA

#### ARTICLE INFO

#### Keywords: Cyber–physical systems IoT Run-time verification Real-time systems Robotics Temporal logic

#### ABSTRACT

Since many Cyber-Physical Systems (CPS) interact with the real world, they are safety- or mission- critical. Temporal specification languages like STL (Signal Temporal Logic) have been developed to capture the properties that built CPS must meet. However, the existing temporal logics/languages do not provide a natural way to express the tolerance with which the timing properties must be met. As a consequence of this, the specified properties may be vague, the ensuing CPS design may end up being over- or under-provisioned, and the validation of whether the built CPS meets the specified CPS properties may turn out to be erroneous. To address these issues, a run-time verification methodology is proposed, that allows users to explicitly specify the tolerance with which timing properties must be met. To ensure the correctness of measurement-based validation of a built CPS, this article: (i) proposes a test to determine if a given measurement system can validate the properties specified in TTL, and (ii) proposes a measurement-based testing methodology to provide one-sided guarantee that the built CPS meets the specified CPS properties. The guarantees are one-sided in the sense that when the measurement-based testing concludes that the properties are met, then they are guaranteed to be met (so not false positive). However, when the measurement-based testing concludes that the properties were not met, then they may have met (there can be false negative). In order to validate our claims, we built a model of flying paster (part of the printing press that swaps in a new roll of paper when the current roll is about to finish) using Arduino Mega 2560 and two Hansen brushed DC motors and specified the timing constraints among the various events in this system, along with the tolerances with which they should be met in TTL. We generated the testing logic and validated that we get no false positive, even though we encounter 4.04% false negative. The rate of false negatives can be reduced to be less than any arbitrary value by using more accurate measurement equipment.

### 1. Introduction

Cyber–Physical Systems (CPS) are systems that integrate the interaction of computational and physical worlds and enable intelligent and automated sensing and control. Many current and envisioned CPS, like intelligent traffic management systems [3,4], smart grids [5], drones [6], etc., have safety–critical requirements that must always be met. Many specifications<sup>1</sup> concerning the safety and performance

of CPS are related to the timing of the system where the correctness is not only tied to providing the correct response but also at the right time [7,8]. Since specification of a timing constraint using our natural language can be ambiguous, several types of temporal logic have been proposed to formally specify the timing behavior of a system. LTL (Linear Temporal Logic) [9] is used to capture properties of Boolean predicates, MTL (Metric Temporal Logic) [10] can capture

<sup>\*</sup> Corresponding author.

E-mail addresses: mohammadreza.mehrabian@sdsmt.edu (M. Mehrabian), mkhayati@asu.edu (M. Khayatian), aviral.shrivastava@asu.edu (A. Shrivastava), patricia.derler@parc.com (P. Derler), hugo.andrade@amd.com (H. Andrade).

<sup>&</sup>lt;sup>1</sup> Terminology note: In this paper, we use the term "constraint" to imply what the system must do/achieve, and "specification" to imply the limits of the system components. For example, while building an autonomous vehicle, the timing constraint may be that the vehicle should be able to drive at 80 kmph, but engine specification may be that it can only achieve 60 kmph.

system properties using Boolean predicates in continuous time and STL (Signal Temporal Logic) [11] can specify system properties in terms of real-valued signals over continuous time.

The main limitation of the existing temporal logics/languages that we identify in this article is that they do not explicitly consider the tolerance with which the specified constraint must be met.2 For example, suppose there is a timing constraint that a signal y(t) must become high 200 ms after the signal x(t) becomes high. This timing constraint can be represented in STL as  $\square \left(\uparrow x(t)^3 \rightarrow \diamond_{\lceil 200 \text{ ms} \rceil} (\uparrow y(t))\right).^4$  However, this timing constraint is vague — since it does not specify the tolerance with which the constraint must be met. Time is inherently continuous and therefore the delay between two events cannot be exactly equal to a real-value. Moreover, every measurement device has non-zero uncertainty in measurement and the exact (real) time of the occurrence of an event cannot be reestablished from a record of the timestamps at which they were measured to occur [12], and therefore the given property can only be evaluated to a certain finite uncertainty. The right constraint should have been that — signal v(t) must become high 200 ms  $\pm 10$  ms after the signal x(t) becomes high.

Another example is distributed synchronized cameras where 3 cameras must take a picture at the same time from different angles to combine and perform 3-D scene reconstruction. The constraint for this system can be written in STL as  $\Box(\uparrow t_A \to \diamond(\uparrow t_B) \to \diamond(\uparrow t_C))$ . Here,  $t_A$ ,  $t_B$ , and  $t_C$  are the times of the shutter events on the 3 different cameras. Note that this timing specification also does not specify the required precision (millisecond, microsecond, or nanosecond precision) with which the timing constraint must be met. If these constraints are interpreted strictly, then it is impossible to build such a system. In the absence of tolerance specification, it is impossible to figure out if a built CPS is over or under-designed.

Furthermore, if the tolerances are not specified, it is hard for the verification teams to determine if a built CPS meets the specified properties. For example, if the timing constraints must be met with a tolerance of nanoseconds, but the measurement system can only measure with millisecond precision, then it is clearly not possible to use the measurement system to validate the CPS properties. By having tolerance in the specification, it is clear in the verification step to choose the right systems. If the acceptable uncertainty is not formally determined in the system specifications, verification teams may need to study the system or use informal methods to figure it out.

Finally, we show that even if have a precise-enough measurement system, because of the inherent uncertainty in measurements it is impossible to guarantee that a built CPS meets the specified timing properties if the tolerance with which the properties must be met are not specified. In fact, type I (false positive), and type II (false negative) observations are possible. This means that even if the measurement system says that a property is being met, it may actually not be met, and even if the measurement system says that a property is not being met, it may actually be met. For safety–critical properties, the type I misjudgement (false positive) can be especially dangerous.

In summary, the contributions of this article are:

The article argues that the tolerance with which timing properties

must be met by a CPS, must be specified along with the CPS properties, otherwise the property specification may be vague, and

the validation of whether the built CPS meets the specified CPS

properties may be erroneous, and the ensuing CPS design may

end up being over-provisioned or sub-optimal. The method in this

paper uses a specification language, TTL (Timestamp Temporal

- Logic) [13], proposed in 2017, that allows the users to explicitly specify the tolerance with which timing constraints must be met.

- The proposed approach considers several factors of the measurement system, including the precision of digital-to-analog and analog-to-digital converters and clock synchronization accuracy that affect the precision of timestamps, to determine if the measurement system can be used to validate if a built CPS meets its timing properties specified in TTL or not.

- We propose a verification methodology that given the precision of measurement equipment, will ensure that type I misjudgements cannot happen. This is achieved at the cost of more type II misjudgements (false negatives). However, the rate of type II misjudgements (false negatives) can be reduced to arbitrary levels by improving the precision of the measurement equipment.

To demonstrate the usefulness of our approach we developed a Flying Paster system — the part of the printing press that swaps the active roll of paper with a new one when the active roll is about to run out of paper and breaker tripping in power systems. We implemented a model of flying paster using Arduino Atmega 2560 and two DC motors, and specified the safety and performance-related timing specifications without tolerances in STL and with tolerances in TTL.

By using our approach, we determine that the original monitoring system (using Arduino Atmega 2560s) was not accurate enough to validate the required properties. The uncertainty in the monitoring system (i.e.,  $106~\mu s$ ) was more than the precision required by the properties ( $100~\mu s$ ) of the flying paster application. In fact, the data acquisition system could only sample at 10~kS/s, while to validate the timing constraints of flying paster with tolerance of  $100~\mu s$ , we needed at least a sampling rate of 20~kS/s. We switched to National Instruments NI-cRio that allows more than 20 Kilo samples per second sampling rate, and we were able to validate the properties over the built CPS.

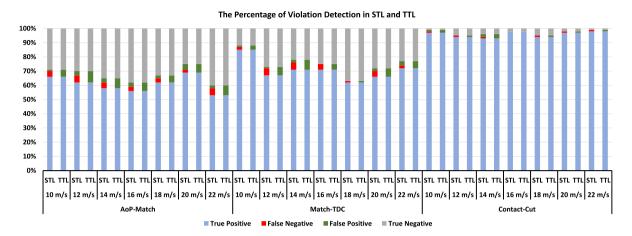

We developed the logic for validating whether the built flying paster system meets the timing properties. Experimental results show that there were no false positives (the number of cases where the built CPS does not meet the specification, but the monitoring system could not catch it) when we used logic derived from TTL specification that contains tolerances. However, the logic derived from the STL specification that does not contain tolerances showed about 2.61% rate of false positives. These false positives can be very dangerous for safety–critical properties.

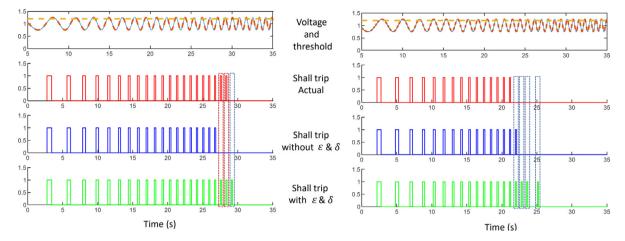

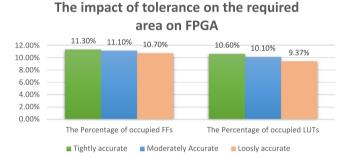

We performed similar experiments on a MATLAB model of power breaker circuit. Power breakers are required for cutting off the electricity power in case of over-current. In order to prevent failure, it should satisfy some temporal properties like "the breaker should trip if the duration at which the voltage is above 1.2 p.u. (per unit) is greater than 160 ms.". In this experiment, we could demonstrate that without considering tolerance as a part of statements in temporal logic, three violations were not detected by the monitoring system (i.e., around 13%). However, since TTL considers uncertainties in the statements, there were no undetected violations, even though there were about 4% false negatives (cases when the monitoring system reported that the timing constraint was not met, but actually they were met). However, as mentioned before, the rate of false negatives can be reduced to below any arbitrary value by choosing a better measurement system. In the last experiment, we used tolerable errors in STL expressions and showed that to implement the required circuit on FPGA, TTL implementation needs fewer resources.

#### 2. Related work

One approach to verify the temporal specifications of CPS is runtime verification where the system's behavior is monitored during its operation [14]. In order to verify the timing specifications of real-time systems, it is firstly required to express the system temporal behavior in a formal language like Temporal Logic (TL). Temporal

$<sup>^2</sup>$  We use the term *tolerance* to specify how much deviation from the ideal/nominal behavior is acceptable and we use the term *uncertainty* to capture the variation in the measured values.

$<sup>^3 \</sup>uparrow x(t)$  shows the rising edge when x(t) becomes high (i.e., there is an event on x(t)) [1].

<sup>&</sup>lt;sup>4</sup>  $\diamond_{[a]}$  or  $\diamond_{=a}$  is the *Punctual* form of  $\diamond_{[a,b]}$  when b=a [2].

Logic, proposed in [15], is a system of rules to represent the system behavior and reason about propositions qualified in terms of time. Pnueli [16,17] and Owicki et al. [18] have proposed Temporal Logic for the specification and verification of reactive systems. Linear Temporal Logic (LTL) [19], Computation Tree Logic (CTL) [20,21], Metric Temporal Logic (MTL) [10], Metric interval Temporal Logic (MITL) [22], Timed Propositional Temporal Logic (TPTL) [23], and Signal Temporal Logic (STL) [11] have been proposed to define the timing specifications of real-time systems. Although, the introduced temporal logic formalisms are very useful and expressive for representing the temporal specifications of real-time systems, representing uncertainties is still challenging.

Some of the common languages to express temporal specifications of CPS are LTL, MTL, and STL where they comprise three major timing operators (*Globally, Eventually*, and *Until*) for expressing any level-based timing constraint. However, the expressions are often combined and/or nested and must be evaluated recursively. Additionally, although those logic languages have the capability to express event-based timing constraints, combined temporal expressions are constructed out of a variety of level-based timing constraints. In order to represent only one event (rising or falling), we should use past and future operators together in one expression.<sup>5</sup>

In 2006, Fainekos proposed the robust interpretation of MTL over continuous-time signals taking values in metric spaces [24]. Since the classical methods to test temporal logic just involve boolean abstraction, when a specification is either satisfied or violated, it is not possible to know its degree. In essence, the robustness degree function gives a real value that indicates how far is a signal from violating or satisfying a specification using a metric  $\rho$  [25]. This technique is a significant improvement in falsification approaches [26,27]. Using Booleanziner rules, it is practical to transform STL formulas to MITL and define STL robustness in a similar approach [28]. In the domain of uncertainty, the robustness techniques can consider  $\rho$  as the maximum robust value for a specification and then, by considering  $\rho$  value, monitor the signal to know if it has satisfied the specification. In this regard, there are some algorithms and tools [22,29,29] for online monitoring of CPS. The algorithms basically make a parse tree for the formula and give a range to show the robustness of the monitored signal value. Although temporal logic robustness can be used to express uncertainty on values (spatial robustness) in MTL/STL, it does not have a direct definition to express the existing uncertain values (robustness) in time domain. In order to consider uncertainties in time domain, we can consider time robustness to know how robustly the formula is satisfied or violated with respect to time. In the other words, if the time robustness of a monitored signal is known, it is intuitively possible to consider a part of that (or its entire) as uncertainty. The approach proposed in 2010 [30] maps every spatial robustness to temporal. It has two definitions for left/right robustness<sup>6</sup> when a specification is either satisfied or violated. To calculate the robustness value, the algorithm receives two sort of different values, (i) a sequence of variable step-size time-tamped values of the monitored signal and, (ii) a time function with a finite sequence of points where its derivative is changed. Then, based on the signal values and the time derivatives, the time robustness can be calculated incrementally. Although the method calculates time robustness in an explicit way, it is computationally expensive for online monitoring since its complexity is of the order of the sum of the signal's sampling frequency. Furthermore, because the methods based on MTL/STL use both past and future operands to express signal events, representing events needs long and cumbersome expressions.

In Propositional Linear Temporal Logic (pLTL) [31], it is required to find an optimal solution for temporal specification in the system behavior to judge its correctness. As a fact, the time complexity of finding

an optimal solution for a pLTL specification is doubly exponential in the number of prepositions in a single statement. There is a similar issue in using STL. One solution is to use Mixed Integer Linear Program (MIPL). However, MIPL is an NP-hard problem to solve. [32] proposed a method as a probabilistic extension to STL to evaluate complex specifications. Indeed, for uncertain and changing environments, a probabilistic variant of STL is proposed to express safety constraints on random variables. This approach presents an efficient receding horizon algorithm to maximize the probability of satisfaction of a temporal specification. In PrSTL, a time-bounded specification  $\psi$  is assigned to a system (e.g., CPS). PrSTL allows for computing the probability of satisfaction given a sequence of states over the target system. The ideal in this logic is estimating the true states of targets and because the estimates over the target states are given in the form of probability distributions, the signal evaluation is done in terms of probability. Nevertheless, these works only evaluate the signal in the form of probability distributions instead of the robustness or traditional Boolean evaluation based on stochastic methods with solid judgements. Moreover, they assume the state of the system is always fully known [33].

In the domain of analog mixed signals, AMS-LTL [34] is an extension of STL that uses the notion of events as atomic properties for the predicates in which an event is to express a change in the truth of the propositions. This logic proposes auxiliary state machines and auxiliary functions, two types of formalisms, for Analog and Mixed-Signal (AMS) assertions (e.g., a user can create properties or asserted behavior for AMS). It has been shown that the complexity of satisfaction/violation using the monitoring algorithm for AMS-LTL is EXPSPACE-complete.<sup>7</sup>

One popular solution for verifying the behavior of CPS is simulating the CPS and running the monitoring system beside it and see if the requirements are met at run-time. In this domain, the conventional monitoring methods generally use the same formalisms (i.e. STL/MTL/MITL) to express timing requirements in the monitoring processes. Since those languages do not explicitly/intrinsically express the tolerable error as a part of language, the developed monitoring system might be overestimated, large, or heavy in most of cases and may leave the violation of some monitored timing specifications undetected. Some tools for analyzing the timing requirements in CPS have been implemented in Breach [35], and S-Taliro [36]. Both tools record simulation data and evaluate timing constraints considering the simulation.

Recognizing the high overhead, AMT [37] proposed an incremental approach to compute the constraints at a segment granularity. An incremental method was proposed by Deshmukh et al. [38] where timing constraints are evaluated by traversing the parse tree generated for STL formulas. They optimize calculations by eliminating repetitive computations. Since all of these examples are implemented in simulation, they have the access to the real values and hence, do not consider the uncertainties in their computations.

Beside the previous approaches that work in simulation, there are some examples implemented on FPGA. *Selyunin* et al. [39] proposed a framework for generating monitors with recovery from a class of highlevel STL specifications. This method firstly simplifies the STL formula, converts them into equi-satisfiable past operators, and then using an offline evaluation. The code is synthesized in a digital reconfigurable hardware. It uses SystemC simulation kernel to run the monitor on pre-recorded traces. R2U2 is another method implemented on FPGA for a security threat detection [40]. *Schumann* et al. proposed a technique receiving the properties of an Unmanned Aerial Vehicle (UAV) using MTL/LTL statements and then diagnosis security attacks by a Bayesian Network model. Indeed, the authors construct FPGA monitors for security requirements and specify possible attacks that a UAV might undergo.

$<sup>^{5} \</sup>uparrow \psi = (\psi \land (\neg \psi S \ \top)) \lor (\neg \psi \land (\psi \mathcal{U} \ \top))$  for rising edges and  $\downarrow \psi = (\neg \psi \land (\psi S \ \top)) \lor (\psi \land (\neg \psi \mathcal{U} \ \top))$  for falling edge.

<sup>&</sup>lt;sup>6</sup> Similar to Latency constraint we propose in this paper.

$<sup>^7</sup>$  In complexity theory, EXPSPACE is the set of all decision problems solvable by a deterministic Turing machine in O(2p(n)) space, where p(n) is a polynomial function of n.

While the aforementioned methods do not discuss about the efficiency of the FPGA implementation, Reinbacher et al. in 2013 presented an algorithmic framework, for monitoring temporal specifications expressed in past-time MTL/LTL. They showed that their work optimized the required memory space since the needed storage for the signal history is bounded by  $\lceil \log_2(n) \rceil$  where n is elapsed time from when the monitoring is started. Jakšić et al. [41] implemented a monitoring method called Counters algorithm on FPGA. The Counters algorithm reduces the computation complexity from  $O(n^2)$  to  $O(n\log(n))$ , where n is the size of time interval of the temporal constraints. This technique converts future STL operators into past expressions and translates all constraints such that their interval starts from zero. Then, a counter is dedicated to measuring the duration of a positive pulse in each interval. The number of needed counters depends on the variability of the monitored signal and the length of the interval bound (a).

Although these methods showed a way to reduce memory usage, the storage remains a concern (even for bounded constraints). Since it is not possible to express the maximum allowed deviation for measured and computed values, the designer/verification developers implement their monitoring methods as precise as possible while it is not always required. Intuitively, such implementation needs more resources in comparison with the methods that adjust their precision degree considering use-defined allowed tolerance. Moreover, by relaxing the conditions with considering tolerance, it becomes possible to take uncertainties into account and cover the corner cases and provide a guarantee to make sure the monitoring approach is able to catch all timing violations.

#### 3. Problems in run-time verification using existing temporal logics

Several temporal logics like CTL, LTL, MTL, and STL have been developed to specify the properties that a built CPS must meet. STL is most applicable to express the properties of CPS since it allows the specification of properties of real-valued signals in continuous time. In this section, we discuss about one of the common challenges in using STL expressions in the online monitoring of temporal specifications. In order to illustrate that, there is an example in the following section.

#### 3.1. An example for time uncertainty in event detection

In STL, a CPS designer can express specifications like (examples taken from [42]):

$$\psi = \Box (x(t) < 3.5).$$

This STL statement specifies that the value of the signal x(t) should never go above 3.5 V.

Another example is:

$$\psi = \textstyle \bigsqcup_{[2,6]} (|x(t)| < 2)$$

This STL statement specifies that in the next 2s to 6s, the value of the signal x(t) remains between -2 V and 2 V.

The issue that we want to draw attention to is that STL specifications do not provide a mechanism for the CPS designer to explicitly specify the tolerance with which these specifications should be met. This is the case, even though STL claims to model continuous time. Without the tolerance specification, it is impossible to correctly validate if a built CPS meets its timing constraints or not.

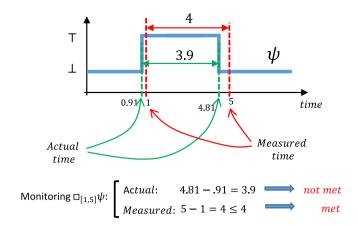

Consider the example shown in Fig. 1. The figure depicts a signal  $\psi$  that should be monitored by a verification system to see if it satisfies the STL statement,  $\Box_{[1,5]}\psi$ . The STL statement expresses a property that is considered to be met at time t iff, in the next 1 to 5 s (i.e. t+1 to t+5), the signal (psi) is true continuously.

The diagram (Fig. 1) depicts that  $\psi$  becomes true at real-time 0.91 s and becomes false again at 4.81 s. If we do the calculation to determine the satisfaction of  $\Box_{[1,5]}\psi$  at t=0, we will conclude that the temporal

**Fig. 1.** The problem of monitoring a STL timing statement. Since in the discretization process an interval is just converted into a single value, the final evaluation can be wrong if the uncertainty in the measurement device is not taken into account.

specification has not been satisfied, since  $\psi$  was not true from 4.81 s to 5 s.

However, if we use a digital monitoring circuit with a sampling period ( $\delta=0.2$  s), then we reach a different conclusion. Suppose the sampling times (time steps) are  $\{0,0.2,0.4,\ldots\}$  s. The sampling system will first record that the signal  $\psi$  is true will be at the 1 s mark. It will last record that the signal was true will be at the 5 s mark. So  $\square_{[1,5]}\psi$  is found to be met.

False positive misjudgement (type I error) can cause serious problems, particularly in safety–critical applications because the measurement system concludes that the timing constraint is met, while in reality it is not met! This problem is severe because the probability of type I errors (or false positive evaluations) only decreases with the precision of the measurement equipment, but is not eliminated. Thus it is hard to guarantee the safety of the CPS.

One possible solution to fix this issue, for existing temporal logics e.g. STL/MTL/MITL, is to account for the measurement error by manually modifying the time intervals of the timing operators. However, this approach will be hard for nested/complex temporal statements, there is no specific method to consider tolerance in those languages, and if the tolerance is considered case-by-case, for each case there is a need to have a proof for the correctness. Since TTL semantics converts temporal specifications into mathematical conditions, it is possible to have general proofs for complex and nested specifications. Furthermore, since representing temporal specifications in STL needs more temporal operators, it needs more space on FPGA to design and verify in comparison with using TTL.

### 4. Tolerance in timestamp temporal logic (TTL)

All digital devices have a level of measurement uncertainty (say  $\delta$ ) and STL statements cannot be monitored correctly without considering the uncertainty ( $\delta$ ) in the statements. For example, if we want to check if a signal falls from high to low with a measurement system that has a sampling period of 0.2 s, then if the measurement system registers that the signal went from high to low at say the 5 second mark, then it is impossible to say when between 4.8 s and 5 s the signal went from low to high. The best we can say is that the signal went from high to low somewhere between 4.8 s and 5 s. In this case, we say that the uncertainty in the measurement of the time at which the signal went from high to low is  $\delta=0.2$  s. Note that the uncertainty can be low for a system, but it cannot be eliminated for any real measurement system. Just assuming the left timestamp (4.8s in this case) or the right timestamp (5 s in this case) – both approaches are not right and can lead to the wrong evaluation of the safety condition.

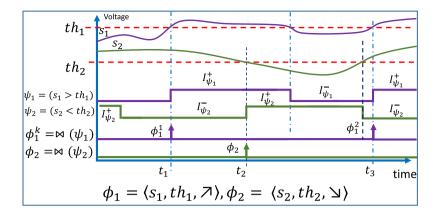

Fig. 2. The process to events from analog signals by threshold crossing. Each signal is compared with a threshold and the satisfaction is shown by a Boolean signal.

The only way to avoid wrong evaluations is to add conservativeness to the condition calculations. This can be done, if we know an upperbound on  $\delta$ . However, specifying the error of the measurement devices does not make sense in the temporal constraints of an application.  $\delta$  is a property of a measurement system. From the application perspective, it makes more sense to define a **tolerance** or  $\epsilon$  – with which the timing constraints must be met. Then a measurement device can be deemed to be capable or not of being able to evaluate the satisfaction of a timing constraint (with a given tolerance), if the measurement uncertainty is within the tolerance of the timing constraint.

Timestamp Temporal Logic (TTL) provides a definitional extension of STL that more intuitively expresses the timing specifications of distributed CPS and allows for a more natural expression of timing tolerance. It provides room for considering tolerance as a part of language and enables accurate monitoring.

# 4.1. Event representation in TTL

Simple events in TTL are defined as signal transitions from one state to another. In order to extract events for a real-time system, we utilize the classical discretization/quantization process. In such a process, there are three major parts (i) sampling, discretizing in time using regular sampling with an interval  $\delta_{ADC}$ , (ii) quantization, uniform scalar quantization with a step q, and (iii) interpolation, detecting the threshold crossing to extract events [43]. Since system  $\Omega$  is hybrid, we assume that the monitored signal is band-limited and does not produce infinite events occurring in a finite time (Zeno behavior [44]). Moreover, the conversion is done using uniform sampling in Analog to Digital Converters (ADC). Considering such signals and the quantization process, in the interpolation, we are able to calculate the maximum error in space (d) and time ( $\delta_{ADC}$ ) [45]. Section 6.4 discuss the way to accumulate the total uncertainty by considering  $\varepsilon_{ADC}$ .

For example, a signal event generated by threshold crossing on analog signals is presented by a triplet,  $\langle s, th, \nearrow or \searrow \rangle$ , which is 1 (T) at the time when the signal, s, crosses a threshold, th (crossing from below  $\nearrow$  or from above  $\searrow$ ), and 0 ( $\bot$ ) everywhere else. The time of the event is called a timestamp and is represented by a real number. A signal event can be a singleton or repetitive. In a singleton signal event, there is only one event ( $\phi$ ) which is represented by a single timestamp while repetitive signal events are expressed by a sequence of timestamps  $\{\phi^1, \phi^2, \dots, \phi^n\}_{(n \in \mathbb{N})}$ .

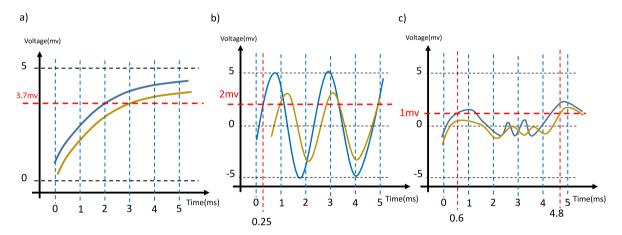

Finding out the timestamps of simple events, like  $\langle s, th, \nearrow or \searrow \rangle$  is a three-step process. Fig. 2 outlines the process. The top 2 curves in the graph depict comparing two signals  $(s_1 \text{ and } s_2)$  with their corresponding thresholds  $(th_1 \text{ and } th_2)$ , and that results in the middle 2 Boolean signals  $(\psi_1 \text{ and } \psi_2)$ . The Boolean signals  $(\psi_1 \text{ and } \psi_2)$  can be divided into time intervals during which the value of the signal is true or false, indicated by  $\mathcal{I}^+$  and  $\mathcal{I}^-$ . The time of the rising event

$\begin{aligned} \textbf{Table 1} \\ \textbf{Grammar of TTL.} \\ \psi &:= v \end{aligned} & | \neg \psi \\ & | \psi_1 \wedge \psi_2 \\ & | \Box \psi \\ & | \psi_1 U \psi_2 \\ & | \mathcal{L}(\phi_1, \phi_2, \epsilon) \triangledown l \\ & | \mathcal{L}(\phi_1, \phi_2, \ldots, \phi_n, \epsilon) \\ & | \mathcal{L}(\phi_1, \phi_1, \ldots, \phi_n, \epsilon)$

$|\mathcal{P}(\phi_1, \phi_2, \varepsilon_f, \varepsilon_p) \nabla p$

on the Boolean signals ( $\psi_1$  and  $\psi_2$ ) then represents the occurrence of the specified event, and can be obtained by differentiator. In fact, the Boolean signal  $\psi_1$ , gives the last 2 curves in the figure. Thus,  $\hat{\phi} = \bigotimes(\psi)$ , where the value of  $\phi \in \hat{\phi}$  is  $\top$  when  $\psi(t^+) \oplus \psi(t) \land \neg \psi(t) = \top$ , and  $\bot$  otherwise.  $\oplus$  is XOR and  $t^+$  refers to the right neighborhood of signal at time t in continuous domain. Then, using the function  $\tau(\phi)^8$  we can extract the event's timestamp.

Extracting a signal event from a real-valued signal over the continuous time-domain is done by comparing the values of the signal with a threshold, th, and then, passing the output through the *Differentiate Operator* ( $\bowtie$ ) in the discrete time-domain. As it is depicted in Fig. 2, signals  $s_1$  and  $s_2$  are firstly converted into Boolean signals after comparing with their corresponding thresholds  $(th_1, th_2)$ , and then by applying the differentiate operator,  $\bowtie$  sequence of timestamps  $\phi_1$  and  $\phi_2$  are generated.

# 4.2. Expressing tolerance in TTL syntax

The TTL syntax is defined based on STL with extensions to enable expressing events, natural specification, and considering tolerance. TTL operators are built based on high-level operators that specify timing requirements on both the value of a formula and the occurrence time of events. The output of TTL operators is finally a Boolean value.

**Definition 4.1.** The satisfaction relation  $(s,t) \models \psi$ , indicating that signal s satisfies  $\psi$  starting from position t.

**Definition 4.2.** Given the sets  $\chi$  of events and the set **V** of atomic propositions, the set  $TTL_{\chi}(V)$  of TTL formulas (event-based) is inductively defined using the following grammar shown in Table 1: where  $v \in V$ ,  $\phi_1, \phi_2, \dots, \phi_n \in \chi, v \in \{\langle, \rangle, =\}$  and  $l, f, p, \varepsilon, \varepsilon_f, \varepsilon_p \in \mathbb{R}^+ + \{0\}$ .

In the rest of this section, we describe the meaning of each operator existing in the grammar.

<sup>&</sup>lt;sup>8</sup> We will explain it in Section 5

- The atomic v proposition is true if there is a time at which a threshold crossing exists.

- $\neg \psi$  is true iff  $\psi = \bot$ .

- The output of each TTL operator is a Boolean continuous signal.

Hence the STL operators can be applied to them.<sup>9</sup> Therefore, □

and U receive Boolean signals and return Boolean as well.

- If the evaluated two TTL formulas,  $\psi_1$  and  $\psi_2$  are both true,  $\psi_1 \wedge \psi_2 = \top$ .

- $\mathcal{L}(\phi_1,\phi_2,\varepsilon)$  calculates the latency between two events  $\phi_1$  and  $\phi_2$ . (i)  $\phi_1$  and  $\phi_2$  are singleton, <sup>10</sup> (ii)  $\phi_1$  occurs before  $\phi_2$ , and (iii) the difference between the actual occurrence of two events,  $\phi_1$  and  $\phi_2$  should be less/greater than or equal to l with the user-defined tolerance value uncertainty of  $\varepsilon$ .

- $C(\phi_1, \phi_2, \dots, \phi_n, \varepsilon)$  specifies that the event  $\phi_i$  occurs before event  $\phi_{i+1}$   $(1 \le i \le n)$ , with a tolerance of  $\varepsilon$ .  $\varepsilon$  determines the acceptable minimum distance between the events.

- $S(\phi_1, \phi_2, \dots, \phi_n, \varepsilon)$  specifies that the events  $\phi_1$  to  $\phi_n$  occur at the same time within a time duration of  $\varepsilon$ .

- $\mathcal{F}(\phi, \varepsilon_f)$  specifies that the occurrence frequency of event  $\phi^{11}$  should be less/greater than or equal to f within an tolerance value of  $\varepsilon_f$  (in Hz).

- $\mathcal{P}(\phi_1,\phi_2,\varepsilon_f,\varepsilon_p)$  specifies that the phase difference between two repeating events  $\phi_1$ , and  $\phi_2$  on two different signals is less/greater than or equal to p, where,  $\varepsilon_f$  is tolerance in the frequency domain and  $\varepsilon_p$  is the tolerance in phase.

#### 5. Conditions for guaranteed verification by monitoring

In this section, we explain the mathematical equations and proof to have the right expressions with considering Tolerance and Uncertainty in this section. The equations for Latency operator are explained here. At the end of this section, we demonstrate how TTL fixes the problem in monitoring by using  $\varepsilon$ .

However, before starting to explain the details of the language, there are some parameters that should be defined.

#### 5.1. Problem definition

In this work, we take a very general approach to monitor a traced continuous signal u of the system  $\Omega$ , with considering a temporal specification,  $\psi$ . t is the dense time, and u(t) represents the signal value at time t in voltage.

#### 5.1.1. The type of signals and discretization process

Let  $\mathbb{D}$  be a value domain, Boolean ( $\mathbb{B}$ ), or Real-value ( $\mathbb{R}$ ) signal.

**Continuous-Time Signals:** A continuous signal s maps the continuous time domain (dense time) to a real-valued domain. Since CPS monitoring is usually based upon finite traces [46], the signal length is r expressed by |s| = r.

**Definition 5.1.** Signal s is a map.  $s : \mathbb{T} \to \mathbb{R}$ ,  $\mathbb{T}$  is a set of non-negative real numbers as time,  $\mathbb{R}_{>0}$ , and  $\mathbb{R}$  is the value of continuous signals.

The interval for the entire signal is I = [0, r). Its value at time t where  $t \in \mathbb{R}_{\geq 0}$  is s(t).

A sequence of disjoint non-empty intervals  $I:\{I_0,I_1,I_2,\dots,I_k\},I_i\cap I_j=\varnothing$  is a time partition compatible with a finitely-varying continuous-time Boolean signal converted into discrete using  $\Gamma$  function,  $\Gamma:\mathbb{R}\to\{\bot,\top\}$  that makes a discrete signal using a threshold value, th:

$$\Gamma_s = \begin{cases} \top, & \text{if } s \ge th \\ \bot, & \text{otherwise} \end{cases}$$

(1)

If x is a continuous Boolean signal, and if  $\bigcup_{j=0}^k I_j = [0,r)$  and  $\forall I_j$  in the form of  $(t_j,t_{j+1}), [t_j,t_{j+1}], (t_j,t_{j+1}],$  or  $[t_j,t_{j+1}]$  such that  $t \leq t_{j+1}$ , for all t and t', x(t) = x(t').

**Discrete-Time Signals:** A discrete-time signal  $\sigma$  is a sequence of samples of a continuous-time Boolean signal x and made by the function  $g: \mathbb{R} \to \mathbb{B}$ . The value of  $\sigma$  at position i for continuous signal x is  $\sigma_x[i]$  and equals a Boolean value where  $i \in \mathbb{N}$ .

There are different discretization methods and we discuss periodic or uniform sampling here, which is the type of sampling used most often in practice. It can be expressed by  $\Gamma_s(\theta) = \sigma_s(\theta.\delta_{ADC})$  s.t.  $\theta \in \mathbb{N}$ .  $\sigma_s$  is the discrete time signal of continuous signal s. We name  $\theta$  as *Timestamp*. Moreover, the time interval  $\delta_{ADC}$  between successive samples is called the sampling period or sample interval and it is  $\frac{1}{f_s}$ .  $f_s$  is the sampling rate (samples per second) or the sampling frequency (hertz). As we will explain in Section 6.4, it is a part of total uncertainty which is  $\delta$ .

Therefore, we have function  $\Gamma: s(t) \xrightarrow{\delta_{ADC}, th} \sigma$ .

Moreover, as a requirement to provide the one-way guarantee for run-time verification, we assume that the value of a monitored signal changes at a *constant rate* between every two captured samples.

**Definition 5.2.** The temporal logic formula,  $\psi_s$ , is the system specification for signal s(t) behavior.

In the monitoring process, there is a real signal (ground truth) continuous signal, s(t), and a discrete signal,  $\sigma_s[\theta]$ . In monitoring, since the real value of the signal is not known (because of quantization/discretization) there is an error value. This error may cause uncertainty in the system implementations and also monitoring.

The informal definition of each part is explained below:

- s is a continuous signal over continuous time t.

- $\psi$  is a Boolean signal over continuous time. It can be *true* (positive pulse) or *false* (negative pulse) for a duration of time.

- $\delta_{ADC}$  is the sampling time to convert a continuous signal to discrete. It can be taken as measurement error as well because it is the maximum error in the discretization process.

- $T(\phi)$  is a function that receives the event  $\phi$  and returns its actual time of occurrence in the continuous domain. It is a real number.

- τ(φ) receives the event φ and returns the event's timestamp in discrete domain. Its return value is an integer number.

- $\varepsilon$ : is the user-defined tolerance value to cover the existing measurement errors in Cyber–Physical Systems. By this value, we make the temporal property more conservative since the measurement error can cause uncertainties. Its value in all operators is  $\varepsilon > 0$  and a part of syntax because no measurement system is perfect.

- ⋈ is differentiator operator and converts a Boolean signal into events (ŷ = ⋈(σ)).<sup>12</sup>

#### 5.2. TTL operators

In this section we have formal definitions for each operator in TTL. The maximum latency constraint is expressed by the following statement in TTL:

**Maximum Latency:**  $\mathcal{L}(\phi_1, \phi_2, \varepsilon) < l, 0 < \varepsilon < l$

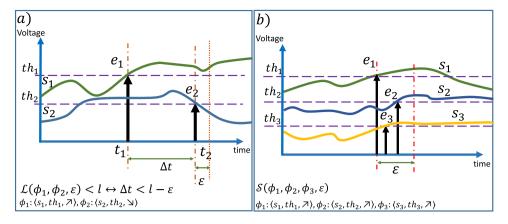

If  $T(\phi)$  represents the actual occurrence time of event  $\phi$  in *real numbers*, we have  $0 < T(\phi_2) - T(\phi_1)$  and  $T(\phi_2) - T(\phi_1) < l - \varepsilon$ .  $T(\phi_2) - T(\phi_1)$  is required to be less than  $l - \varepsilon$  so as to guarantee that the latency between the two events  $\phi_1$ , and  $\phi_2$  is less than l. Fig. 3.a shows how the latency constraint is calculated in the continuous time. Now, the question remains, what are the conditions under which we can guarantee that  $T(\phi_2) - T(\phi_1) < l - \varepsilon$  is satisfied in a discrete system.

$<sup>^{9}</sup>$  As mentioned before,  $\psi$ s are Boolean signals whereas  $\phi$ s are events

$<sup>^{10}\,</sup>$  They occur once in a specific duration.

$<sup>^{11}</sup>$   $\phi$  is repetitive here and  $\phi^i$  corresponds to the *i*th occurrence of the event  $\phi$ .

$<sup>^{12}</sup>$   $\hat{\phi}$  is a sequence of events.

Fig. 3. The effect of tolerance in Latency and Simultaneity calculations. Figure (a) shows a Latency constraint and (b) is the demonstration for Simultaneity operator in TTL.

In formal, continuous signal *s* at time *t* should satisfy this relation:  $(s,t) \models \mathcal{L}(\phi_1,\phi_2,\varepsilon)$  iff  $T(\phi_2) - T(\phi_1) < l - \varepsilon$ .

In order to answer this question, we should look at CPS again. Most CPS implementations and measurement systems sample signals (with a fixed sampling time of  $\delta$ ) and, therefore, capture a timestamp as the occurrence of the event. The actual time of an event is inferred from the timestamp within an error  $\delta$ . The measurement error has several sources such as quantization, sampling time, analog to digital converter (ADC) resolution [47]. If  $\tau(\phi)$  represents the *integer* timestamp at which the event  $\phi$  is captured, and both  $T(\phi)$  and  $\tau(\phi)$  are initiated to zero when the system starts to operate, then  $\tau(\phi) = \begin{bmatrix} T(\phi) \\ \delta \end{bmatrix}$  is the relation between  $T(\phi)$  and  $\tau(\phi)$ .

Therefore, we know that  $T(\phi_1)=(\delta\tau(\phi_1)-\delta,\delta\tau(\phi_1))$  and similarly  $T(\phi_2)=(\delta\tau(\phi_2)-\delta,\delta\tau(\phi_2))$ . Hence, their subtraction to find the latency between two events  $\phi_1$  and  $\phi_2$  will be bounded between  $\delta(\tau(\phi_2)-\tau(\phi_1))-\delta$  and  $\delta(\tau(\phi_2)-\tau(\phi_1))+\delta$ . In fact:

$$\delta(\tau(\phi_2) - \tau(\phi_1)) - \delta < T(\phi_2) - T(\phi_1) < \delta(\tau(\phi_2) - \tau(\phi_1)) + \delta \tag{2}$$

Also, we already know that in order to be conservative, it is enough if we have:

$$T(\phi_2) - T(\phi_1) < l - \varepsilon \tag{3}$$

to guarantee the time difference between events is certainly less than *l*. Therefore, based on Eqs. (2) and (3):

$$\delta \tau(\phi_2) - \delta \tau(\phi_1) - \delta < l - \varepsilon \tag{4}$$

Since we know that  $0 < \delta \tau(\phi_2) - \delta \tau(\phi_1)$ ,  $0 < l - \varepsilon + \delta$ . Hence, to have the guarantee for Eq. (3), we should test:

$$\tau(\phi_2) - \tau(\phi_1) < \frac{l - \varepsilon}{\delta} + 1 \tag{5}$$

and the condition is (by considering Eqs. (2) and (4)) is  $\varepsilon - \delta < l$ .

On the other hand, in inequality (4), if  $\varepsilon < \delta$ , since we are adding a positive number to l ( $\delta \tau (\phi_2) - \delta \tau (\phi_1) < l - (\varepsilon - \delta)$ ), it does not guarantee (4). Therefore, we should have  $\delta < \varepsilon$ . As a fact, if inequality (5) is not true, inequality (3) might still be true. However, by considering  $\varepsilon > \delta$  we make sure if (5) is true, (3) is definitely true as well. This relation between  $\varepsilon$  and  $\delta$  makes sense because in Eq. (5), the added value ( $\delta$ ) due to the discretization process is compensated by  $\varepsilon$ . In the above equations, (5) is a property of **measurement** and  $\delta < \varepsilon$  is the property of **measurement system**.

Therefore, we have:

$$(s,t) \models \mathcal{L}(\phi_1, \phi_2, \varepsilon)$$

(6)

Regarding inequity(5), if we consider  $\delta < \varepsilon$  since the accepted error is greater than the actual error, we can ensure that if there is a violation

in the Latency constraint, we can catch it. In fact, without considering  $\varepsilon$ , there is a gray area in which it is not clear to know whether the Latency constraint is violated or met.

**Minimum Latency:**  $l < \mathcal{L}(\phi_1, \phi_2, \varepsilon)$

By considering Eq. (2), we have  $l+\varepsilon-\delta<\delta(\tau(\phi_2)-\tau(\phi_1))$ . If  $\varepsilon<\delta$ , we cannot guarantee that the time difference between two events is greater than l. Therefore,  $\delta<\varepsilon$ . Similar to the maximum latency specification, there will be an error of  $\delta$  between the actual time and the captured timestamp of events. Hence, we have:

$$\frac{l+\varepsilon}{\delta}-1<\tau(\phi_2)-\tau(\phi_1),\delta<\varepsilon \tag{7}$$

**Exact Latency:**  $\mathcal{L}(\phi_1, \phi_2, \varepsilon) = l$

The constraint means that  $T(\phi_2)-T(\phi_1)=l\pm \varepsilon$  or  $l-\varepsilon < T(\phi_2)-T(\phi_1)< l+\varepsilon$ . A monitoring system can ensure this specification by checking if  $\frac{l-\varepsilon}{\delta}+1\le \tau(\phi_2)-\tau(\phi_1)\le \frac{l+\varepsilon}{\delta}-1$ . By  $\varepsilon$ , we defined a specific duration to shrink the time for satisfaction regarding  $\delta$ . Again, if  $\varepsilon<\delta$  we cannot guarantee to catch all violations. Hence, the measurement system is considered to be able to evaluate the specification correctly if  $\delta<\varepsilon$ .

#### 5.3. TTL-based run-time verification approach detects all timing violations

As an example to demonstrate the advantage of TTL over STL in monitoring approaches, let us take a look at Fig. 1 and its example again. In Section 3, we explained the issue in which the monitoring device cannot detect the violation. However, since TTL considers the measurement error, it can solve the false positive problem using  $\varepsilon$ . As a fact, TTL is able to express the width of a signal pulse by considering rising and falling edges. In Fig. 1, we can replace  $\Box_{[1,5]}\psi$  by minimum latency,  $\mathcal{L}(\langle s_1(t), 2.5, \nearrow \rangle, \langle s_1(t), 2.5, \searrow \rangle) > 4s$ . From the example (in Section 3), we know  $\delta = 0.2$  and can take  $\varepsilon = 0.4$ . Based on the numbers on Fig. 1 and  $\delta$  and  $\varepsilon$ , we have  $\tau(\langle s_1(t), 2.5, \nearrow \rangle) = \left\lceil \frac{2}{0.2} \right\rceil = 10$  and  $\tau(\langle s_1(t), 2.5, \searrow \rangle) = \left\lceil \frac{6}{0.2} \right\rceil = 30$ .

$$\begin{split} \mathcal{L}(\langle s_1(t), 2.5, \nearrow \rangle, \langle s_1(t), 2.5, \searrow \rangle, 0.4) &> 4s \\ \iff \frac{l+\varepsilon}{\delta} - 1 &< \tau(\langle s_1(t), 2.5, \searrow \rangle) - \tau(\langle s_1(t), 2.5, \nearrow \rangle) \end{split}$$

$$\left\lceil \frac{4+0.4}{0.2} \right\rceil - 1 < 30 - 10 \Longrightarrow 21 \nleq 20$$

Accordingly, the monitoring system shows the timing constraint is violated when it is really violated. Therefore, while STL mistakenly shows the temporal requirement is met, TTL is able to correctly catch the violation.

This conversion, *Globally* to *Latency* can be generalized for the other two operators in STL. In fact, in order to utilize the capabilities of TTL, it is possible to have corresponding operators for *Eventually* and *Until* as well. This conversion can be done by considering the rising and falling edges on the Boolean signals.

Since the subtraction is calculated, the maximum error is  $\delta$ .

To summarize, we can express the STL (or MITL) operators in TTL as below. If we consider  $\phi_r$  and  $\phi_f$  as the rising and falling edges,  $\langle \phi_{[a,b]} \psi \rangle$  $\square_{[a,b]}\psi$ , and  $\psi_1\mathcal{U}_{[a,b]}\psi_2$  are defined as below:

$$\langle f_{[a,b]} \psi \longrightarrow \mathcal{L}_{[a,b]} (\phi_r, \phi_f, \varepsilon) > 0, \varepsilon > \delta$$

$$\square_{[a,b]} \psi \longrightarrow \mathcal{L}_{[a,b]}(\phi_r,\phi_f,\varepsilon) > b-a,\varepsilon > \delta$$

$$\begin{split} &\mathcal{L}_{[a,b]}(\phi_{1_r},\phi_{1_f},\varepsilon)>0 \wedge \mathcal{L}_{[a,b]}(\phi_{2_r},\phi_{2_f},\varepsilon)>0 \wedge \mathcal{L}_{[a,b]}(\phi_{2_r},\phi_{1_f},\varepsilon)>0, \varepsilon>\delta \\ &\text{where } (s,t) \models \mathcal{L}(\phi_1,\phi_2,\varepsilon)>l \text{ then } \frac{l+\varepsilon}{\delta}-1 < \tau(\phi_2)-\tau(\phi_1) \text{ iff } \theta_1=\tau(\phi_1),\theta_2=\tau(\phi_2) \text{ s.t. } \theta_1,\theta_2\in[t+a,t+b] \end{split}$$

#### 5.4. TTL provides a one-way guarantee in CPS monitoring

Since the TTL operators can be used in monitoring systems to verify the operation of safety-critical applications, they must be able to catch all timing violations. On the other side, we know TTL specifies the timing constraints within a tolerance value ( $\varepsilon$ ). Accordingly, some satisfactions might fall in the tolerable duration category which we refer to as the gray area. If a timing constraint is met within the gray area, our rule detects them as violated since it may be evaluated as met just because of uncertainty in the measurement system. Based on such rule, some detected timing violations will be false negative cases (when a violation is reported while it is met) but there will be no false positive. Therefore, from this point of view, TTL provides a one-way guarantee for run-time verification. The rate of false negative is directly dependant on the size of the gray area.

Providing the one-way guarantee mean that if the evaluation system says a timing constraint is met, we are certain that it is actually met given the specified tolerance by the designer and the existing uncertainty of the measurement devices. Having zero false positive is valuable for safety-critical systems. It is worth noting that providing a two-way guarantee is not possible due to the existence of uncertainty in the monitoring system. Our approach provides the one-way guarantee at the cost of being more conservative and having more false negatives.

#### 5.5. TTL rules

In the rest of this section, we show the rules for TTL temporal operators to guarantee the monitoring accuracy (proofs for Latency are in Section 5) and summarize all in Table 2.

**Maximum Latency:**  $\mathcal{L}(\phi_1, \phi_2, \varepsilon) < l, 0 < \varepsilon < l$  we already showed that if we have  $\tau(\phi_2) - \tau(\phi_1) < \frac{l-\varepsilon}{\delta} + 1$ ,  $\delta < \varepsilon$  the maximum latency is

**Minimum Latency:**  $l < \mathcal{L}(\phi_1, \phi_2, \varepsilon)$  if we have  $\frac{l+\varepsilon}{\delta} - 1 < \tau(\phi_2) - 1$  $\tau(\phi_1), \delta < \varepsilon$ , the minimum latency is guaranteed.

**Exact Latency**:  $\mathcal{L}(\phi_1, \phi_2, \varepsilon) = l$  is guaranteed if we have  $\frac{l-\varepsilon}{\varepsilon} + 1 \le l$  $\tau(\phi_2) - \tau(\phi_1) \le \frac{l+\varepsilon}{\varepsilon} - 1, \ \delta < \varepsilon.$

**Chronological**:  $C(\phi_1, \phi_2, ..., \phi_n, \varepsilon)$  means that  $\varepsilon < T(\phi_{i+1}) - T(\phi_i)$ . A measurement system with accuracy of  $\delta$  will be able to ensure the specification by monitoring  $\frac{\varepsilon}{\delta}-1<\tau(\phi_{i+1})-\tau(\phi_i)$  only if  $\delta<\varepsilon$ . **Simultaneity:**  $S(\phi_1,\phi_2,\dots,\phi_n,\varepsilon)$  means that the time difference

between each pair of events is less than  $\varepsilon$ , or by the other words

$$max(T(\phi_1), T(\phi_2), \dots, T(\phi_n)) - min(T(\phi_1), T(\phi_2), \dots, T(\phi_n)) < \varepsilon$$

A measurement system with accuracy of  $\delta$  will be able to ensure the specification by monitoring

$$\max\left(\tau(\phi_1), \tau(\phi_2), \dots, \tau(\phi_n)\right) - \min\left(\tau(\phi_1), \tau(\phi_2), \dots, ts(\phi_2)\right) < \frac{\varepsilon}{\delta} + 1$$

The added  $\delta$  value (everything is normalized by  $\delta$ ) is just to consider the measurement error value compensated by  $\varepsilon$ . Additionally, as before, the measurement is valid only if  $\delta < \varepsilon$ . Fig. 3.b demonstrate the Simultaneity calculation.

**Minimum Frequency**:  $f < \mathcal{F}(\phi, \varepsilon_f)$

This temporal specification defines the minimum frequency for a repetitive event on a signal and can be converted into the time domain. In fact in the time domain, it means  $T(\phi^n) - T(\phi^{n-1}) < \frac{1}{f \pm \varepsilon_f}$  where  $\phi^i$ corresponds to the *i*th occurrence of the event  $\phi$  on the same signal. To simplify, we have:  $T(\phi^n) - T(\phi^{n-1}) < \frac{1}{f + \epsilon_f}$ . Similar to latency,

$$\begin{split} \tau(\phi^n) - \tau(\phi^{n-1}) &< \frac{1}{\delta(f + \varepsilon_f)} + 1, \ \delta < \frac{1}{\varepsilon_f}. \\ \text{Maximum Frequency: } \mathcal{F}(\phi, \varepsilon_f) &< f \end{split}$$

In time domain, this operator defines the minimum period for a repet-

In time domain, this operator defines the minimum period for a repetitive event. Indeed, we should have  $\frac{1}{f-\varepsilon_f} < T(\phi^n) - T(\phi^{n-1})$ .

Therefore,  $\frac{1}{\delta(f-\varepsilon_f)} - 1 < \tau(\phi^n) - \tau(\phi^{n-1})$  where  $\delta < \frac{1}{\varepsilon_f}$ ,  $\varepsilon_f < f$ .

Exact Frequency:  $F(\phi, \varepsilon_f) = f$ Exact frequency means  $T(\phi^n) - T(\phi^{n-1}) = \frac{1}{f\pm\varepsilon_f}$  in time domain. By simplifying the equations, we have  $\frac{1}{f+\varepsilon_f} < T(\phi^n) - T(\phi^{n-1}) < \frac{1}{f-\varepsilon_f}$ ,

Considering the measurement error of  $\delta$ , the system must monitor  $\frac{1}{\delta(f+\epsilon_f)}+1<\tau(\phi^n)-\tau(\phi^{n-1})<\frac{1}{\delta(f-\epsilon_f)}-1$ , and the monitoring is valid only if  $\delta < \frac{1}{\varepsilon_f}$ ,  $\varepsilon_f < f$ .

**Minimum Phase:**  $p < \mathcal{P}(\phi_1, \phi_2, \varepsilon_f, \varepsilon_p)$

If events  $\phi_1$  and  $\phi_2$  occur at the **same frequency** (exact frequency) then Phase can be defined. 14 This constrain defines the desired latency between consequent events on two different event sources ( $\phi_1$  and  $\phi_2$ ).

Hence, based on this concern, we must satisfy two conditions: (i)  $\mathcal{F}(\phi_1, \varepsilon_f) = \mathcal{F}(\phi_2, \varepsilon_f)$ , and (ii)  $p - \varepsilon_p < T(\phi_2^n) - T(\phi_1^n)$ .

From condition (i), we have  $|(T(\phi_1^n) - T(\phi_1^{n-1})) - (T(\phi_2^n) - T(\phi_2^{n-1}))|$  $<\frac{1}{\varepsilon_f}$ . If we assume  $A: T(\phi_1^n) - T(\phi_1^{n-1})$  and  $B: T(\phi_2^n) - T(\phi_2^{n-1})$ , we have:  $-\frac{1}{\epsilon_f} < A - B < \frac{1}{\epsilon_f}$ . Hence, there are two cases, (a)  $A < \frac{1}{\epsilon_f} + B$ , and (b)  $B - \frac{1}{\varepsilon_f} < A$ . From Eq. (2), we know that

$$\delta(\tau(\phi_1^n) - \tau(\phi_1^{n-1})) - \delta < A < \delta(\tau(\phi_1^n) - \tau(\phi_1^{n-1})) + \delta$$

$$\delta(\tau(\phi_2^n) - \tau(\phi_2^{n-1})) - \delta < B < \delta(\tau(\phi_2^n) - \tau(\phi_2^{n-1})) + \delta$$

To be conservative, in (a), A should be in its maximum value and *B* should be in its Minimum value. Therefore,  $\delta(\tau(\phi_1^n) - \tau(\phi_1^{n-1})) + \delta < \frac{1}{\varepsilon_f} + \delta(\tau(\phi_2^n) - \tau(\phi_2^{n-1})) - \delta$ , and in (b),  $\delta(\tau(\phi_2^n) - \tau(\phi_2^{n-1})) + \delta < \frac{1}{\varepsilon_f} + \delta(\tau(\phi_2^n) - \tau(\phi_2^{n-1})) + \delta < \delta(\tau(\phi_2^n) - \tau(\phi_2^{n-1})) + \delta < \delta(\tau(\phi_2^n) - \tau(\phi_2^n)) + \delta < \delta(\tau(\phi_2^n) - \tau(\phi_2^n)) + \delta(\tau(\phi_2^n)$  $\delta(\tau(\phi_1^n) - \tau(\phi_1^{n-1})) - \delta.$

Thus, the pre-conditions for satisfaction of Phase constraint are:

$$\tau(\phi_1^n) - \tau(\phi_1^{n-1}) - (\tau(\phi_2^n) - \tau(\phi_2^{n-1})) < \frac{1}{\delta \varepsilon_f} - 2$$

(8)

$$\tau(\phi_2^n) - \tau(\phi_2^{n-1}) - (\tau(\phi_1^n) - \tau(\phi_1^{n-1})) < \frac{1}{\delta \varepsilon_{\ell}} - 2 \tag{9}$$

From condition (ii), the specification implies that  $\frac{p+\varepsilon_p}{\delta}-1<\tau(\phi_2^n) \tau(\phi_1^n)$ . Since the monitoring system must ensure that  $p + \varepsilon_p < T(\phi_2^n)$  $T(\phi_1^n)$  is monitored correctly, the monitoring system will be implemented as  $p' + \varepsilon_p' - 1 < \tau(\phi_2^n) - \tau(\phi_1^n)$  where  $p' = \frac{p}{\delta}$  and  $\varepsilon_p' = \frac{\varepsilon_p}{\delta}$ . To check if the measurement system can evaluate the timing specification,  $\delta < \frac{1}{\varepsilon_f}$  and  $\delta < \varepsilon_p$  statements should hold.

**Maximum Phase:**  $P(\phi_1, \phi_2, \varepsilon_f, \varepsilon_p) < p$

For this specification, the two frequencies of  $\phi_1$  and  $\phi_2$  should be equal within a tolerance.  $T(\phi_2^n) - T(\phi_1^n) where <math>\phi_1^i$  and  $\phi_2^i$  correspond to the *i*th occurrence of the events  $\phi_1$  and  $\phi_2$  respectively. Similar to the minimum phase, the monitoring system should monitor  $\tau(\phi_2^n) - \tau(\phi_1^n) <$  $p' - \varepsilon'_{p} + 1$ .

**Exact Phase:**  $\mathcal{P}(\phi_1, \phi_2, \varepsilon_f, \varepsilon_p) = p$

This TTL operator means  $T(\phi_2^n) - T(\phi_1^n) = p \pm \varepsilon_p$  or  $p - \varepsilon_p < \infty$  $T(\phi_2^n) - T(\phi_1^n) . Considering the error in the measurement system,$ we have  $p' - \varepsilon'_p + 1 < \tau(\phi_2) - \tau(\phi_1) < p' + \varepsilon'_p - 1$ .

<sup>&</sup>lt;sup>14</sup> Otherwise, having Phase constraint is meaningless.

Table 2

The conditions that must be met in the monitoring system to guarantee the meeting of TTL constraints.

| TTL Temporal Operators                                       | Monitoring condition when the constraint is met                                                                                                                                                                                                                      |

|--------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $v \vDash \psi$                                              | iff $v = T$ $\forall t \ge 0$ $(s,t) \models \psi$                                                                                                                                                                                                                   |

| $\mathcal{L}(\phi_1, \phi_2, \varepsilon) < l$               | $\tau(\phi_2) - \tau(\phi_1) < \frac{l-\epsilon}{\delta} + 1, \ \delta < \epsilon, \ 0 < \epsilon < l$                                                                                                                                                               |

| $l < \mathcal{L}(\phi_1, \phi_2, \varepsilon)$               | $\frac{l+\varepsilon}{\delta} - 1 < \tau(\phi_2) - \tau(\phi_1), \delta < \varepsilon, \ 0 < \varepsilon < l$                                                                                                                                                        |

| $\mathcal{L}(\phi_1,\phi_2,\epsilon)=l$                      | $\frac{l-\varepsilon}{\delta} + 1 < \tau(\phi_2) - \tau(\phi_1) < \frac{l+\varepsilon}{\delta} - 1, \ \delta < \varepsilon, \ 0 < \varepsilon < l,$                                                                                                                  |

| $C(\phi_1,\phi_2,\ldots,\phi_n,\varepsilon)$                 | $\frac{\varepsilon}{\delta} - 1 < \tau(\phi_{i+1}) - \tau(\phi_i), \ \delta < \varepsilon$                                                                                                                                                                           |

| $S(\phi_1, \phi_2, \dots, \phi_n, \epsilon)$                 | $\max\left(\tau(\phi_1),\tau(\phi_2),\ldots,\tau(\phi_n)\right) - \min\left(\tau(\phi_1),\tau(\phi_2),\ldots,ts(\phi_2)\right) < \frac{\epsilon}{\delta} + 1, \ \delta < \epsilon$                                                                                   |

| $f < \mathcal{F}(\phi, \varepsilon_f)$                       | $\tau(\phi^n) - \tau(\phi^{n-1}) < \frac{1}{\delta(f + \varepsilon_f)} + 1, \ \delta < \frac{1}{\varepsilon_f}, \ \varepsilon_f < f$                                                                                                                                 |

| $\mathcal{F}(\phi, \varepsilon_f) < f$                       | $\frac{1}{\delta(f-\varepsilon_f)} - 1 < \tau(\phi^n) - \tau(\phi^{n-1}), \ \delta < \frac{1}{\varepsilon_f}, \ \varepsilon_f < f$                                                                                                                                   |

| $\mathcal{F}(\phi, \varepsilon_f) = f$                       | $\frac{\frac{1}{\delta(f-\epsilon_f)}-1<\tau(\phi^n)-\tau(\phi^{n-1}),\ \delta<\frac{1}{\epsilon_f},\ \epsilon_f< f}{\frac{1}{\delta(f+\epsilon_f)}+1<\tau(\phi^n)-\tau(\phi^{n-1})<\frac{1}{\delta(f-\epsilon_f)}-1,\ \delta<\frac{1}{\epsilon_f},\ \epsilon_f< f}$ |

| $p<\mathcal{P}(\phi_1,\phi_2,\varepsilon_f,\varepsilon_p)$   | $p' + \varepsilon'_p - 1 < \tau(\phi_1^n) - \tau(\phi_1^n), \ \delta < \frac{1}{\varepsilon_f} \text{ and } \delta < \varepsilon_p, \ \varepsilon'_p = \frac{\varepsilon_p}{\delta}, \ p' = \frac{p}{\delta}$                                                        |

| $\mathcal{P}(\phi_1,\phi_2,\varepsilon_f,\varepsilon_p) < p$ | $\tau(\phi_2^n) - \tau(\phi_1^n) < p' - \varepsilon_p' + 1, \ \delta < \frac{1}{\varepsilon_\ell} \text{ and } \delta < \varepsilon_p, \ \varepsilon_p' = \frac{\varepsilon_p}{\delta}, \ p' = \frac{p}{\delta}$                                                     |

| $\mathcal{P}(\phi_1,\phi_2,\varepsilon_f,\varepsilon_p)=p$   | $p' - \varepsilon'_p + 1 < \tau(\phi_2) - \tau(\phi_1) < p' + \varepsilon'_p - 1, \ \delta < \frac{1}{\varepsilon_f} \text{ and } \delta < \varepsilon_p, \ \varepsilon'_p = \frac{\varepsilon_p}{\delta}, \ p' = \frac{p}{\delta}$                                  |

Note that the events in *Frequency* and *Phase* formulas are necessarily periodic, whereas in the other timing specifications, they should be singleton.

All aforementioned operators and their meanings are summarized in Table 2.

# 6. How to know a monitoring equipment is good enough to verify a specific CPS

This section is an effort towards standardizing the process of testing the timing properties of CPS where a design of a testbed is outlined. The testbed can be used to test the CPS to check if all the timing constraints are being met or not in a systematic and correct manner to enable correct-by-construction (CbC) synthesis of the testbed. The testbed – like the distributed CPS it is trying to test – is also a distributed CPS, with each node (of the testbed) monitoring the required signals from the CPS node. Hardware timestamping and IEEE 1588 Precision Time Protocol (PTP) synchronization of the clocks among the CPS components provides observations at the same timescale through vast geographies, without losing accuracy with time. In this section, there is also a discussion about the key timing parameters of the testbed that will affect the time testing capability. In this regard, it studies the specifications that must be met by the testbed, such that the testbed can validate the timing constraints.

The most important design parameters of the distributed testbed that affect the errors in the timing measurements are described below.

# 6.1. Analog to digital converter (ADC) parameters

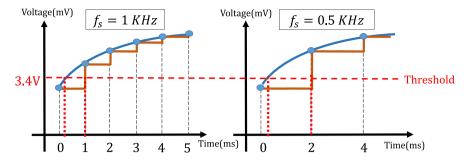

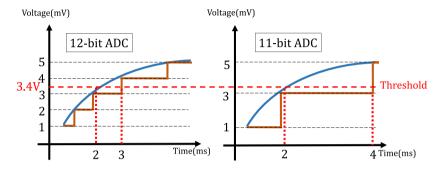

The testbed monitors all signals by sampling them because they should be digitalized to use on the cyber side. This is done by Analog to Digital Converters (ADCs) on the probes. The sampling rate of an ADC,  $f_s$ , is expressed as samples per second, or Hertz (Hz). In order to be able to monitor a signal correctly, the sampling rate must be sufficiently high to capture the fastest observable dynamics of interest in the signal. Suppose we intend to find out the time at which a signal rises above 3.4 V. Fig. 4 shows this signal, monitored with two different sampling rates. On the left with sampling rate of  $f_s = 1$  kHz, the threshold crossing time of the signal is detected as t = 1 ms. However, on the right, with sampling rate of  $f_s = 0.5$  kHz, the threshold crossing time of the signal is detected as t = 2 ms.

Since an ADC converts the voltage signal into digitized sampled events, the accuracy of measurement is also limited by the number of bits used to express the sampled value,  $nbits_{ADC}$ , and the voltage range of the ADC,  $VR_{ADC}$ . An n-bit ADC can represent  $2^n$  values. A 12-bit ADC that measures the range of 0 V to 5 V has steps of  $\approx 1$  mV. The precision of the ADC is defined in terms of resolution of the ADC, or  $V_{ADC}$  can be calculated as:  $V_{ADC} = \frac{VR_{ADC}}{2^{nblis}ADC}$ . The resolution of the ADC can affect the time at which the monitoring device detects an event on a signal. Fig. 5 illustrates the conversion of an analog signal to digital

samples with various resolutions,  $VR_{ADC}$  of 5 V. If the user wants to detect the time when a signal rises above 4 V, then in the left diagram, with  $nbits_{ADC} = 12$ , the time at which the threshold crossing is detected is t = 3 ms, while in the right diagram, with  $nbits_{ADC} = 11$ , the time at which the threshold crossing is detected is t = 4 ms.

#### 6.2. Input impedance

Wiring a signal to a DAQ device adds a load to the CPS circuit under test, which causes a change in the shape of the monitored signal. For pure resistive loads, this change is a simple voltage drop while for general loads, the shape of the monitored signal is changed based on the equivalent resistance and reactance of the measuring device (including capacitance effect of the cables) and the SUT. As a result, based on the rate of change in the value of the signal, the measurements of the signal may be delayed or its amplitude may be attenuated.  $Z_{in}$  is defined as the CPS equivalent circuit from the terminal connected to the testbed. The test and measurement device must have a sufficiently high input impedance to minimize perturbation of the measurement process on the signal.

Fig. 6.b shows the monitored signal perturbed by the loading effect of wiring the measurement device to the SUT. The threshold detection time of the original signal is before the threshold detection time of the monitored signal.

#### 6.3. Clock fractional frequency offset

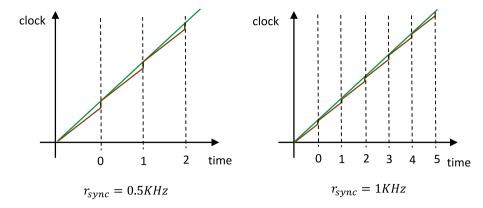

A clock's fractional frequency offset is defined as  $f_{clock} = \frac{f_{inst} - f_0}{f_0}$ , where  $f_{inst}$  is the instantaneous clock frequency, and  $f_0$  is the nominal clock frequency. Thus, this is the unitless instantaneous fractional offset from the nominal frequency of an oscillator [48]. Environmental conditions such as voltage and temperature variations or mechanical vibrations, can affect the rate at which an oscillator runs. Typically, the fractional frequency offset of a clock,  $f_{clock}$ , is expressed in Parts Per Million (PPM), indicating the maximum amount of error in one million time units. Thus, the uncertainty after an elapsed time  $t_{elapsed}$  due to a fractional frequency offset of  $f_{clock}$  is  $t_{elapsed} \times f_{clock}$ . For instance, a clock with 5 PPM error, has 5  $\mu$ s error after 1 s, an uncertainty of about 0.5 s after a day, or about 2.5 min after a year. 7 depicts this issue.

Since all clocks deviate from each other, distributed clocks must be synchronized to a reference to have an agreement on time and have a unique and time notion. Synchronization protocols match the clock of a device to a reference clock. However, no synchronization protocol is perfect, and there is a synchronization uncertainty  $t_{sync}$ , that depends on several factors, including the number of bits used to represent the time, when the time stamping is done (e.g., in the hardware or in software), network jitter, network asymmetries delays, etc. [49]. The Network Time Protocol or NTP [50] can usually keep time synchronized to within tens of milliseconds over the public Internet ( $t_{sync} \approx$

Fig. 4. A digitized analog signal at two different sampling rates. Given a threshold of 3.4 V, the threshold crossing time is detected at different times depending on the sampling rate.

**Fig. 5.** An analog signal sampled using two ADCs that have the same range (0 V to 5 V) and different resolutions. (a) a 12-bit ADC is used. (b) a 11-bit ADC is used. The threshold crossing time in the left figure is at t = 3 ms while it is different in the right figure for the same signal (the threshold crossing is at t = 4 ms).

Fig. 6. (a) Voltage drop on a DC signal connected to a resistive load. (b) Voltage drop and shift on an AC signal connected to a load that has both reactive and resistive components. (c) Change in the shape of an arbitrary signal due to the loading effect.

10 ms). The Precision Time Protocol, PTP [51], can provide time synchronization over a LAN with sub-microsecond accuracy. PTP with the White Rabbit [52] extension used for the CERN Large Hadron Collider, can synchronize to sub-nanosecond accuracy. For CPS distributed over a wide area with high precision and accuracy needs, GNSS (Global Navigation Satellite Systems) can provide 100 ns accuracy.

Another important parameter is the rate of synchronization,  $r_{sync}$ , which is the number of times per second (e.g., in units of Hz) that synchronization is performed. Every time we perform synchronization, the time offsets are within  $t_{sync}$  of each other. But from thereon, until the next synchronization, the clock times will move apart at the rate of  $f_{clock}$ , if the local clock uses the protocol to adjust its time but not its frequency. The worst-case clock offset,  $\epsilon_{wcco}$ , while the system clock is synchronized via the time synchronization protocol in steady-state and while all other environmental conditions are stable, can be calculated as:  $\epsilon_{wcco} = t_{sync} + \frac{f_{clock}}{r_{sync}}$ . Note that the units are in time, since  $f_{clock}$  is unitless and the reciprocal of  $r_{sync}$  is in units of time (see Fig. 7).

#### 6.4. Analysis to calculate the total uncertainty

In order to determine whether timing behavior is verifiable by a given testbed, it is important to understand the sources of timing measurement uncertainty, described as  $\delta$  in the timing constraint specification.

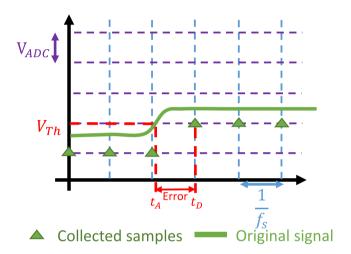

Consider a distributed CPS, with an exact latency constraint  $\mathcal{L}(e_1,e_2,\epsilon)=l$  for events  $e_1$  and  $e_2$ , where  $e_1$  occurs on signal  $s_1$  and  $e_2$  on  $s_2$  respectively. These events are detected at different nodes of the CPS. The latency constraint states that, given  $t_1$  as the occurrence of  $e_1$ , the time at which  $e_2$  occurs should be equal to  $t_1+l\pm\epsilon$ . The testbed must capture the time at which an event occurs. However, the measured time will be erroneous. This can due to the several factors, including the sampling frequency  $f_s$ , the ADC resolution  $V_{ADC}$ , and the clock error,  $\delta_{ucco}$ .

Consider an event described by the tuple  $\langle s_1, v_t, rising \rangle$ , marking the threshold  $v_t$  crossing of signal  $s_1$  on a rising edge. Since the ADC output

Fig. 7. The effect of synchronization frequency  $(r_{sync})$  on the clock uncertainty...

Fig. 8. Worst-case error between actual occurrence time and detection time for an ADC with sampling frequency  $f_s$  and fixed threshold detection based on an integer multiple of the ADC resolution.

is a multiple of the supported resolution, the testbed may not be able to detect the exact point of the threshold crossing. Thus, the threshold value must be mapped to the nearest upper bound of the value. Since all sampled data are collected at known points in time (integer multiples of  $\frac{1}{f_s}$ ), a threshold crossing is detected with a maximum error  $\delta_{ADC} = \frac{1}{f_s}$ . Fig. 8 illustrates the worst-case error  $\frac{1}{f_s}$  in an example.

Since all samples are timestamped using the local clock of the measurement system, clock synchronization error ( $\delta_{wcco}$ ) must be taken into account. Thus, the maximum time error between the actual event occurrence and the detected event occurrence is the sum of the ADC error and the clock synchronization error:  $\delta_{total} \leq \delta_{wcco} + \delta_{ADC}$ .

Since there will be at most  $\delta_{total}$  error in both the measurements of  $e_1$  and  $e_2$ , then the testbed can confidently verify whether the exact latency constraint is being met or not. Other types of constraints (e.g., simultaneity, frequency, phase, etc.) are also expressed with a temporal error tolerance and one can similarly reason and verify the temporal behavior.

#### 7. Empirical evaluation

In order to demonstrate the usefulness of the proposed monitoring approach, three CPS applications have been used. Flying paster is a part of a printing press that swaps a full paper roll when the current paper roll is running out of paper. Flying paster is a distributed CPS with a variety important timing constraints that should be met. The other application is the breaker tripping in a power system when a fault

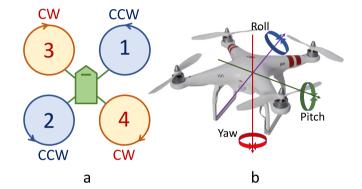

occurs. For coordination of breakers in a Distributed Energy System (DES), they should meet a set of timing constraints. The last application is a quadcopter in which the time specifications for its motors have been monitored

#### 7.1. Flying paster application

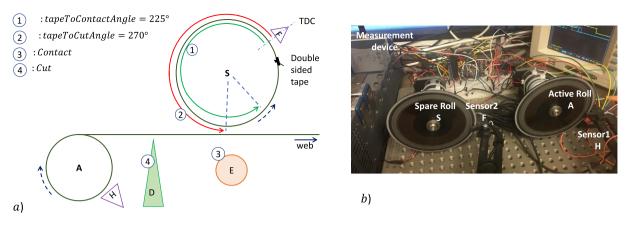

A flying paster is part of a printing press, a distributed system enabling continuity of operation through the automatic exchange of an expiring paper roll with a new roll. Fig. 9.a shows a schematic of the flying paster with the active roll A, which feeds the web. When the radius of paper in roll A is less than a given threshold, the roll is replaced by the spare roll S. The radius of the paper around roll A,  $(r_A)$ , is measured by the sensor H. When this radius falls below a given threshold, the Approaching Out of Paper (AOP) event  $(\phi_{AOP})$ is generated, which initiates the paper roll replacement process by starting the rotation of roll S. A strip of adhesive tape on the paper roll S is used to attach the paper from roll S to roll A. The location of the tape is detected by sensor F, which creates the  $\gamma$  event  $(\phi_{\gamma})$ . The frequency of the  $\gamma$  event is used to calculate the angular velocity,  $\omega_S$ , of S. Once the linear velocities of roll S and A are equal, a **Match** event  $(\phi_{Match})$  is generated. Then, sensor F generates the event TopDead Center (TDC) to indicate the detection of the tape. Two complete rotations of S after event **TDC**, the idler wheel E pushes the paper from roll A towards roll S, at which point the paper from roll S adheres to the outgoing paper from roll A. This event, ( $\phi_{Contact}$ ), occurs after roll Sperformed two rotations plus 255 degrees, tapeToContactAngle = 225°. Immediately after it, the Cutter D cuts the paper from A. This is called the **Cut** event  $(\phi_{Cut})$ , and occurs when roll S has two rotations plus  $tapeToCutAngle = 270^{\circ}$  after TDC.

#### 7.1.1. Flying paster implementation

A picture of the implementation of a scaled model of the flying paster is shown in Fig. 9.b. Rolls A and S in Fig. 9.a are implemented using two Hansen DC motors dialed (0–360 degree) disks, driven by two Arduino Mega2560 boards. Disks have a hole at zero degrees, which is detected by a photo-micro sensor. Photo-micro sensors implement the sensor H, and F and are installed next to the disks. The paper is modeled in software with the initial length of 125 m and 0.05 mm of thickness so that the initial diameter for both rolls is 9 cm (radius of 4.5 cm). The  $\bf AoP$  event is generated when the radius of A becomes less than 2.5 cm.

# 7.1.2. Flying paster specification in STL

Based on the desired operation of the flying paster, its timing specifications are expressed in STL as follows. Noted that:

- *A*: Active roll.

- S: Spare roll.