# Channels Engineering in Magnetic Recording: From Theory to Practice

Shayan Srinivasa Garani, *Senior Member, IEEE*, and Bane Vasić, *Fellow, IEEE*

**Abstract**—Information theory, coding theory and signal processing have significantly shaped magnetic read/write channels engineering through a chronological sequence of innovations and research advancements, cognizant of the underlying physical processes. In this magazine article, we provide an overview of magnetic recording technologies leading to the channels engineering aspects, central to this article. We survey important coding and signal processing algorithms along with some design architectures that have made it to practice within hard disk drives (HDDs) for magnetic recording channels. The push towards realizing ultra-high densities ( $> 4\text{Tb/in}^2$ ) on magnetic disks with ultra-high throughput rates ( $> 10\text{Gb/s}$ ) necessitates the development of native two-dimensional (2D) coding and signal processing algorithms and architectures within the framework of two-dimensional magnetic recording (TDMR) along with read head engineering and changes to the recording physics. We also provide an overview of novel channels engineering solutions covering all aspects of TDMR channels driven from a systems science perspective. The innovations and research advances described in this article may serve a broad engineering audience in other areas as well.

**Index Terms**—magnetic recording technologies, read channels engineering.

## I. INTRODUCTION

THE advent of the computer age in the first half of the 20th century has propelled data storage technologies to advance in an unparalleled manner, leading to the birth, sustenance and exponential growth of technologies for both on-chip and off-chip memories. Examples of on-chip memories based on magnetics include ferroelectric random-access memories (FeRAMs), magnetoresistive random-access memories (MRAMs) etc. Hard disk drives (HDDs) are a classic example of an off-chip physical memory. The term data storage system refers to the entire system that interfaces to this off-chip physical memory, i.e., from the operating system, through the disk controller to the physical head/media subsystem.

According to International Data Corporation (IDC), it is expected that there will be more than 55 billion internet of things (IoT)-connected devices by 2025 [1]. Further, with cloud-based systems driven by datacenters and artificial intelligence (AI)-driven computing systems, several tens of billions of devices will be connected through this data-driven network. The 21st century will be the age of data storage

S. S. Garani is with the Department of Electronics Systems Engineering, Indian Institute of Science, Bengaluru, KA, 560012 India e-mail: shayangs@iisc.ac.in.

B. Vasić is with the Department of Electrical and Computer Engineering, University of Arizona, Tucson, AZ, .

Manuscript received March 19, 2023; revised Aug. 26, 2023.

technologies, mirroring how central processing unit (CPU)-based technologies from computer manufacturers propelled in the early part of the 20th century.

Since it is expected that nearly 175 zetta-bytes (ZB) of data will be generated every day by 2025 [2], we need state-of-the-art technologies to cater to this massive need. Along with memories with higher storage capacities, it is expected that these devices come with high throughput, shrinking form factors and low power consumption. Thus, speed, area, power and capacities ought to be within a ballpark for practical applicability of these devices. Though solid state devices (SSDs) are now part of most computer systems within desktops and enterprise solutions, catering to better read/write access times and comparable HDD storage capacities etc., one cannot ignore the role of HDDs in the data storage space since they have the cost per bit advantage [3]. Hybrid memory systems for handling cold and hot data will inevitably need HDDs. Both HDDs and SSDs are part of today's datastorage systems within datacenters.

Today, we have a thriving multibillion-dollar magnetic storage industry, which is ubiquitous and pushing itself continuously, advancing towards reaching the physical limits of magnetic storage [4]. Sustained research and development in several key multidisciplinary areas, such as magnetic materials, recording physics, tribology, channels, and systems engineering, to name a few, have enabled magnetic recording systems to reach capacities beyond 22 TB over multiple platters, using multiple read heads. HDD technology has moved from a 1D paradigm based on longitudinal and perpendicular recording to shingled recording with improvements to head/media design and recording physics. We are witnessing how with shingled magnetic recording (SMR) technology, using two readers, one could achieve storage densities beyond  $1\text{Tb/in}^2$  [5]. TDMR with shingled writing and 2D signal processing and coding can offer significant gains in areal densities [6] along with the necessary read head engineering and recording physics to work with TDMR.

In this magazine article, we will begin with the history of magnetic storage technologies that dates back to more than 140 years and describe how several innovations from coding theory, information theory and signal processing are continuing to shape its existence to remain competitive within the storage world.

### A. History of Magnetic Recording: From a Technology Perspective

Magnetic recording research has witnessed a sustained development of more than 144 years from the early works of a magnetic recording apparatus conceived by Oberlin Smith in 1878 [7]. In his concept, a coil of wire could magnetize a medium, such as steel. By inducing a voltage, the same coil could be used for playback of the recorded pattern on the medium. This simple idea was demonstrated in practice by Valdemar Poulsen, and was eventually made commercially viable in the 1920s by Kurt Stille. Early advancements with electronic amplification, alternating current (AC)-bias recording, etc. helped in reducing the noise and distortion from the recorded signals during playback. Way back in 1928, Pfleumer developed a new recording medium using thin layers of metal powder. Later, magnetite was developed for coating paper. These simple ideas and further improvements to the recording media led to the birth of the magnetic tape that fuelled the entertainment industry. With subsequent media improvements, HDDs were conceived to realize random access that ensured a switch from the conventional sequential batch data processing paradigm. For a comprehensive historical overview of this celebrated technology, the reader is referred to [7].

The International Business Machine (IBM) 350 disk drive was the first commercial HDD with a capacity of 5 MB, weighing 500 lbs and having 50 24' disks. The disks were vertically stacked and rotated at 1200 rpm. A constant gap separation with fluid bearing of 800  $\mu$ in was maintained between the flying read head and the media to sense the data from the medium. The data format was also very simple, using non-return-to-zero, inverted (NRZI) codes with amplitude detection. The timing was ensured by having odd parities augmented with the NRZI bit stream, ensuring the synchronization of the open-loop oscillators. There was no sophisticated signal processing or error control codes within those systems. Several technical advancements led to the first removable HDD, the IBM 1311.

Later versions of HDDs had self-clocking codes coupled with peak detection circuits for sensing the magnetic transitions for decoding the data. A sequence of further technological innovations in the head designs, such as ferrite heads, metal-in-gap (MIG) heads, thin film inductive heads, etc. propelled an exponential growth in areal densities  $\sim 30\%$ , compounded annually. The introduction of  $(d, k)$  runlength-limited (RLL) codes, such as the  $(2, 7)$  RLL code by IBM in 1979 provided improved gains in areal densities (ADs) since these codes could handle intersymbol-interference (ISI) and synchronization issues directly via the encoded data stream. The recording codes for magnetic storage were suited to peak detection [8]. The most important advancement in head technology was to switch from inductive heads to magneto-resistive (MR) heads that provided higher signal strengths independent of the linear velocity, making it ideal for smaller disks that had lower linear velocities<sup>1</sup>. These MR heads were

<sup>1</sup>The reader must note that the throughput is directly linked to the linear velocities. To sustain a constant throughput, the spinning of the disk at the inner diameter must be higher than at the outer diameter, irrespective of the constant angular velocity on the solid disk.

commercially made available in 1985 [9]. For more details on the theory behind magnetic recording, the reader is referred to [10].

Trying to lower the gap between the head and the recording medium, and having improved RLL codes within the peak detection scheme could only saturate the AD gains. To stay competitive, with the ever increasing demand for higher areal densities, one required alternative strategies<sup>2</sup>. The innovative ideas from Kobayashi and Tang [11] on partial response signaling conceived as early as 1975 were just ripe to be tested out for a new generation of channels. Instead of finding ISI baneful, the PRML scheme allowed controlled ISI that could be tackled using Viterbi detection, which was already well-known by then for decoding of convolutional codes. In 1990, the first partial response maximum likelihood (PRML) detector was introduced by IBM, replacing the peak detection circuits. It was advantageous using MR heads, and the partial response maximum-likelihood (PRML) scheme provided additive gains. Very large scale integration (VLSI) technology was already mature by then to build such read channel integrated circuits (ICs) on a single chip. With low-cost and high-yielding chips that could be integrated within the disk controller systems, the PRML channel was a success along with MR heads. The use of analog and digital equalization techniques, PRML detector, RLL codes, and error correcting codes (ECCs) had HDDs geared up towards realizing  $1\text{Gb/in}^2$  areal densities. In fact, during the early 1990s, only a few IBM drives were PRML-based. The IBM 0681 drive with PRML technology achieved a capacity of  $\sim 900\text{MB}$ . By early 1990s, the compounded annual growth rate in the ADs were  $\sim 60\%$  significantly higher than the 30% growth rate seen for the past 3 decades before 1990s. This further increased with the introduction of giant magneto-resistive heads (GMRs) [12].

With the PRML in place, there were several notable innovations in the channels front, such as the noise-predictive maximum likelihood (NPML) [13] engine that used whitening filters to further improve the performance of Viterbi detectors by overcoming the media noise due to transitions from the magnetic domains. These ideas coupled with the design of generalized partial response (GPR) equalization, i.e., a pre-target selection and adaptive equalization techniques, helped realize ADs beyond tens of  $\text{Gb/in}^2$ . To achieve higher ADs, one has to reduce the magnetic grain sizes for recording a bit. Reducing the grain sizes cannot continue unabated since recorded bits can be erased due to the *superparamagnetic* effect [14]. Mindful of these physical constraints, recording physics, head/media engineering and channels engineering had to be conceived to advance the state-of-the-art. We will discuss these technological aspects later in this section. Since a lot

<sup>2</sup>The reader must note that there has been a constant push for innovations in the HDD industry towards achieving higher ADs. These are driven by innovations in all the three major subsystems, namely (a) improved head design, (b) improved media fabrication, and (c) improved channels engineering. Given a head/media combination, efforts in the channels engineering side are pushed towards achieving higher AD gain. When gains from innovations in channels engineering tend to saturate, the head and media are pushed for improved designs, leading to next-generation channels development suited for those head/media designs. This constant push for innovations across all the three major subsystems within the HDD technology has helped constantly improve AD gains and stay competitive in the market.

of channels engineering depends on the underlying recording physics, we will next discuss the physics behind longitudinal and perpendicular recording schemes.

### B. Physics behind Magnetic Recording Channels

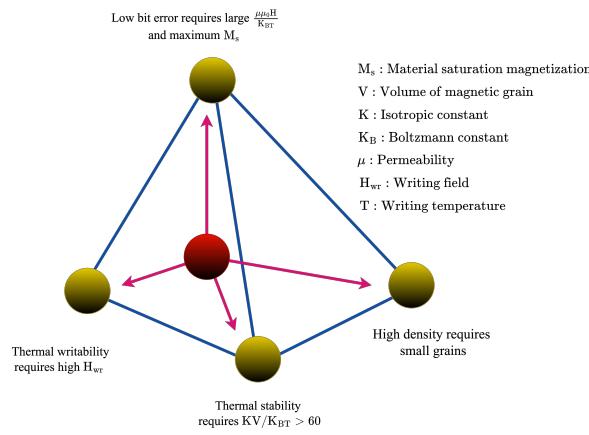

Hysteresis is the key physical property for magnetic memories to hold information. Coercivity of the medium determines its stability against external magnetic fields and thermal issues. Put in simple words, when the magnetic grain sizes are small, they do not hold enough magnetic energy per unit volume, leading to poor signal quality during readback. From a physical perspective, an upper bound for the data storage density is determined by the magnetic *quadrilemma* [4], which we shall describe below:

Figure 1. High ADs require smaller grain sizes. Thermal instability leads to grains switching their magnetization since the magnetic energy per unit volume is less. Further, write instability issues require high writing fields to get the desired level of anisotropy. Providing high writing fields over small grain sizes under high temperatures is not easy to realize. These conflicting requirements lead to the magnetic quadrilemma that dictates the achievable AD from a physics perspective. Adapted from [4].

Consider the extreme case of storing a bit over a magnetic grain, which is the smallest magnetic domain. Figure 1 shows the various conflicting physical requirements for storing data on a magnetic grain. To obtain high storage densities, the grain size must be small. Having smaller grains leads to thermal instability since the magnetic energy per unit volume is less and the magnetization of the grain is lost over time, governed by the Neel relaxation time. Now, there are write instability issues since the external write field must be very high to induce the required anisotropy over the grain. Finally, there are write errors since it is difficult to ensure write heads can provide this field over small grain sizes and high temperatures. This leads to the issue of thermal writeability since the magnetic moment in the medium must be sufficiently large or the writing temperature is not too high. These conflicting requirements will lead to optimization of the physical parameters to assess upper bounds on the achievable density within the classical regime.

Composite media with exchange coupling using soft and hard magnetic layers [15] is used to overcome limitations of writability and thermal stability with conventional write heads. With materials such as CoCrPt-alloys for hard magnetic

layers and a combination of multilayer media structures, the medium has high anisotropy, allowing room for smaller grains. Based on the thermal stability criterion, the areal density of the medium depends on the grain volume and the areal packing fraction of the storage islands. Also, from a thermal-writeability perspective, based on the physical parameters, such as the writing field, writing temperature, Curie temperature of the medium, etc. one can estimate the areal densities in order to sustain the magnetization over a grain without flipping the state under heat-assisted writing (ref. to equation (6) in [4]). It is estimated that the achievable AD for magnetic storage under heat-assisted recording is around  $20\text{Tb/in}^2$  [4]. The reader must note that this assumption is only over one layer of the medium. By stacking layers of magnetic medium, with appropriate recording physics, one can achieve higher ADs.

At this stage, we have not discussed anything related to the noise modeling or statistical description of the read/write processes. Mapping the physical constraints to a communication-theoretic framework will eventually lead to achievable bounds on data storage densities from an information-theoretic view point.

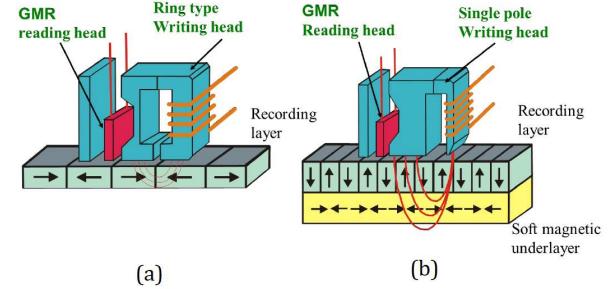

Figure 2. (a) Longitudinal magnetic recording, where the magnets are aligned in the east-west direction. (b) Perpendicular magnetic recording with a soft under layer. The magnets are aligned in the north-south direction. Figure source: Courtesy [16].

1) *Longitudinal Magnetic Recording (LMR)*: In longitudinal magnetic recording (LMR), the magnetic anisotropy is oriented in the thin film plane i.e., in the east-west direction. Figure 2(a) shows the alignment of the magnetic grains. Around  $140\text{Gb/in}^2$  ADs were demonstrated in laboratory setups.

2) *Perpendicular Magnetic Recording (PMR)*: The pioneering work of Iwasaki in 1975 [16] led to perpendicular magnetic recording (PMR), where the magnetic anisotropy is perpendicular to the thin film plane i.e., the magnetic domains are oriented in the north-south direction as shown in Figure 2(b). Present day HDDs are based on PMR technology, which provides significantly higher ADs than LMR up to  $1\text{Tb/in}^2$ . In PMR, there is a soft magnetic underlayer (SUL) which provides a return flux path. Thus, there is a stronger write field gradient using the same head material as the LMR, allowing the medium coercivity to be higher. Larger write field gradient results in smaller transition jitter, thereby improving the signal-to-noise ratio (SNR).

The read head design is the same irrespective of the recording scheme.

### C. New Technologies for Higher Areal Densities

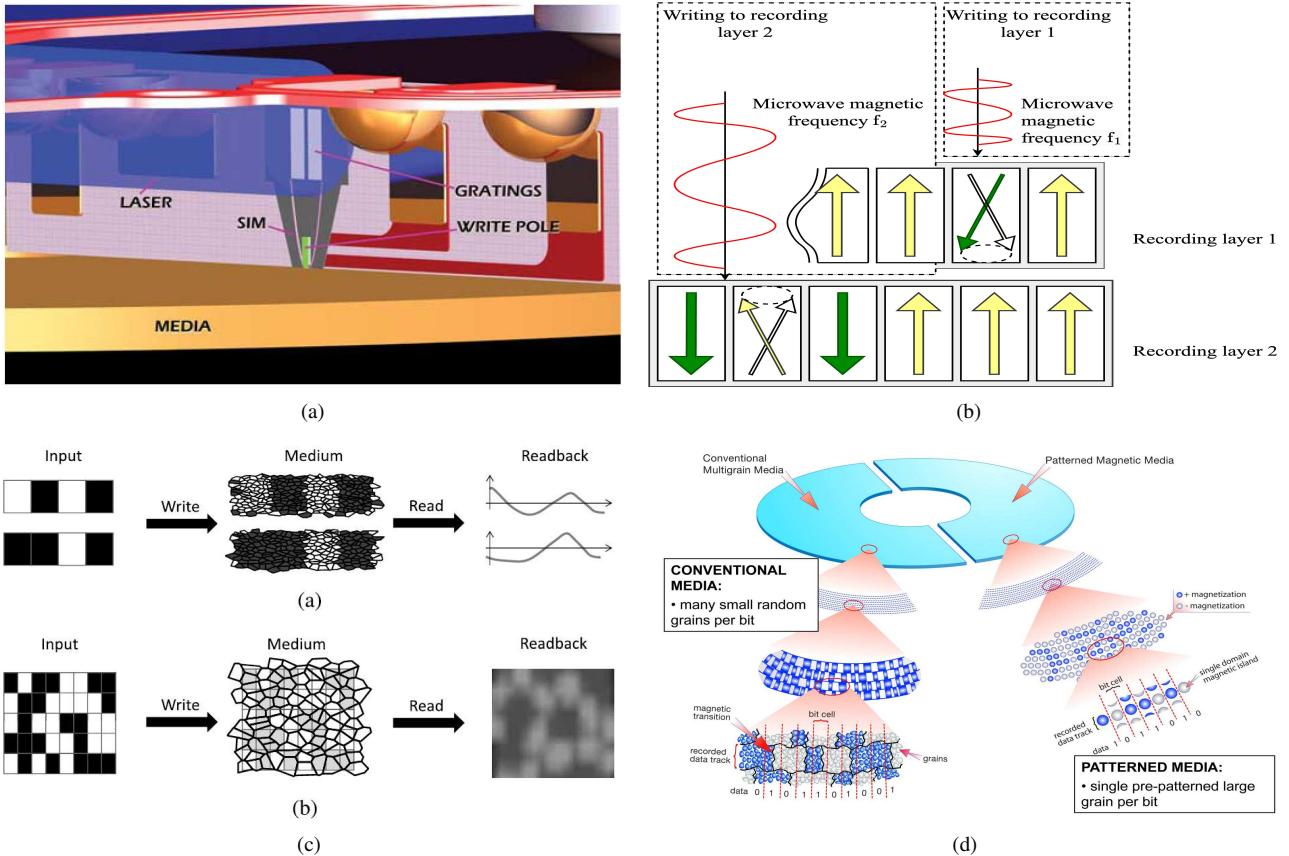

Though PMR-based HDDs have been highly successful since 2005, there is a saturation to the AD gains around  $1\text{Tb/in}^2$ . This led towards research in alternative technologies for furthering AD gains. There have been three major promising technologies: (a) heat-assisted magnetic recording (HAMR) [17] [20], which is driven through recording physics, (b) bit-patterned media (BPM) [21], driven through media innovations, and (c) two-dimensional magnetic recording (TDMR) [22] with innovations from 2D signal processing and coding i.e., from the channels engineering side. Figure 3 shows different magnetic recording technologies, early versions of some of which are already into production.

In HAMR [20], the recording medium is heated above the Curie temperature for a nano timescale. This makes the medium lose its coercivity. Around the same time, the write head writes on the medium. When the medium cools down, it regains its coercivity, thereby retaining the bit written onto it. The key challenge in HAMR drives is nanoscopic guided heat delivery without burning up the write heads. This is accomplished using nano-scale plasmonic waveguides for directing the energy than a direct laser heating of the medium. Sputtering effects over the neighboring cells must be avoided. Figure 3(a) shows the schematic of HAMR. Laboratory HAMR prototypes developed by Seagate have showed areal densities as high as  $2\text{Tb/in}^2$  [23].

There are also works on other energy-assisted magnetic recording (EAMR) schemes, such as microwave-assisted magnetic recording (MAMR) with an eye towards 3D-magnetic storage. In MAMR, the media is composed of multiple layers, similar to layered media in optical discs. Using high-frequency magnetic fields generated by spin torque oscillators, selective switching of grains at a certain depth in a layered medium is possible [24] [25] [26]. Data is recorded in overlapping layers using selective microwave resonant frequencies attuned to these layers (refer to Figure 3(b)). The success of MAMR depends on the strength of the magnetic field and the head-media spacing (gap length). It is envisaged that MAMR can provide ADs to  $10\text{Tb/in}^2$ . In HAMR, lower layers destroy the information in an upper layer. This is circumvented in MAMR. However, MAMR is also prone to similar challenges that HAMR faces.

In BPM, the medium is tessellated into magnetic islands in an orderly manner. Each magnetic island is well-separated with guard bands (shown in Figure 3(d)). Fabrication of such media requires careful lithography, which could be costly. In practice, one could have deleted or fused magnetic islands as part of fabrication defects, requiring significant efforts from channels engineering to work with such media. Write synchronization issues and other aspects make this technology a bit difficult for commercialization.

TDMR is a technology that works with random grains, borrowing from the PMR media technology, unlike BPMR with fixed island sizes. However, instead of writing bits on tracks in the usual 1D manner, tracks are shingled, and data is encoded in 2D. To ensure a sufficiently large magnetization field capable of magnetizing materials with high coercivity, the head is made larger than the track width. However, to achieve a higher areal bit density, the tracks should be very narrow. As a result of narrower tracks, each sweep of the head during writing partially overlaps with the previous track, i.e., writing is noisy.

Unlike traditional recording, where data is organized in well-separated tracks (shown in Figure 3(c).a), in TDMR systems, the data bits are arranged in a 2D array (see Figure 3(c).b). In traditional systems the intersymbol-interference (ISI) is small and along the downtrack, which can be controlled by a sequence detector. In a TDMR system, since the head picks up magnetization from adjacent tracks, there is severe ISI both along a track and across the tracks (inter-track interference (ITI) as a wider head reads data larger than the physical dimensions of a stored bit. Narrow read heads can be fabricated (minimizing ITI) with a penalty in the noise during reads.

2D offers many advantages over 1D. First, one can achieve significantly higher ADs by packing more bits per unit area by using clever 2D coding and signal processing techniques<sup>3</sup>. Next, it is possible to have a relaxed 2D synchronization since the read head is not confined to a narrow single track to handle timing artifacts. Timing issues in the down-track and cross-track directions can be handled as a whole through multi-channel processing. Last, the throughput is significantly higher since an entire array of bits can be read and processed. However, all these advantages towards getting higher ADs come at the cost of designing the array of read heads and processing the signals. It is expected that processing these array of signals requires sophisticated signal processing that could be power and area intensive when implemented on a read channel chip. With advancements in low-power VLSI technologies, both at the device and circuit architectural levels, it is possible to overcome these challenges in pursuit of realizing the promise of TDMR gains. We will describe the channels engineering aspects for TDMR in subsequent sections. The reader must note that TDMR provides additive AD gains over both HAMR/MAMR and BPMR technologies. Thus, it is important to develop native 2D coding and signal processing solutions for TDMR channels for increasing the existing AD limits of HDDs.

### D. Organization of the article

With this broad technological background in mind, we describe the organization of this article. In Section II, we provide an overview of the channel modeling aspects for various magnetic recording technologies. This will help us

<sup>3</sup>The reader must recall that, unlike 1D traditional recording, we have 2D ISI/crosstalk in the down-track and cross-track directions.

Figure 3. (a) Schematic of a HAMR setup with guided LASER beams impinging on the medium. Courtesy: [17]. (b) Schematic of a MAMR setup. Using spin torque oscillators with microwave resonant frequencies tuned to each layer, selective switching of grains in a layered media is possible (Adapted from [18]). (c) Schematic of a TDMR writing and reading process. a) In conventional setup writing and reading is on a single track. b) In TDMR, the data is organized as a 2D array. The 2D readback signal is due to sensing multiple tracks. Severe crosstalk in the readback signal has much of the information required for decoding the original information. Adapted from [6]. (d) Illustration of a BPMR pattern. The medium is fabricated carefully with equally-spaced islands, i.e., ordered grains. Courtesy: Source [19].

connect the physics to a communication-theoretic setup, useful towards building algorithms in practice. In Section III, we survey information-theoretic tools for assessing the mutual information rates (MIR) of MR channels. These results are important to get a feel for achievable ADs under noisy conditions. In Section IV, we discuss the signal processing innovations that had to be conceived with every generation of the read channel. We will provide a summary of various signal processing techniques such as analog pre-filtering, equalization, timing recovery, signal detection, etc. applicable to 1D and 2D channels. In Section V, we discuss the important coding techniques that were practically applicable to HDDs. Specifically, we will highlight the role of algebraic codes and iterative codes that were implemented in practice, within HDDs. We will also discuss modulation codes used in early versions of practical HDDs. We will also highlight the circuit architectural aspects towards realizing the coding algorithms in practice by explaining the importance of algorithmic/system-level tweaks that have had a significant impact in practice. In Section VI, we conclude the article along with our perspectives on the channels engineering aspects for next-generation HDDs.

## II. MODELING FOR MAGNETIC RECORDING CHANNELS

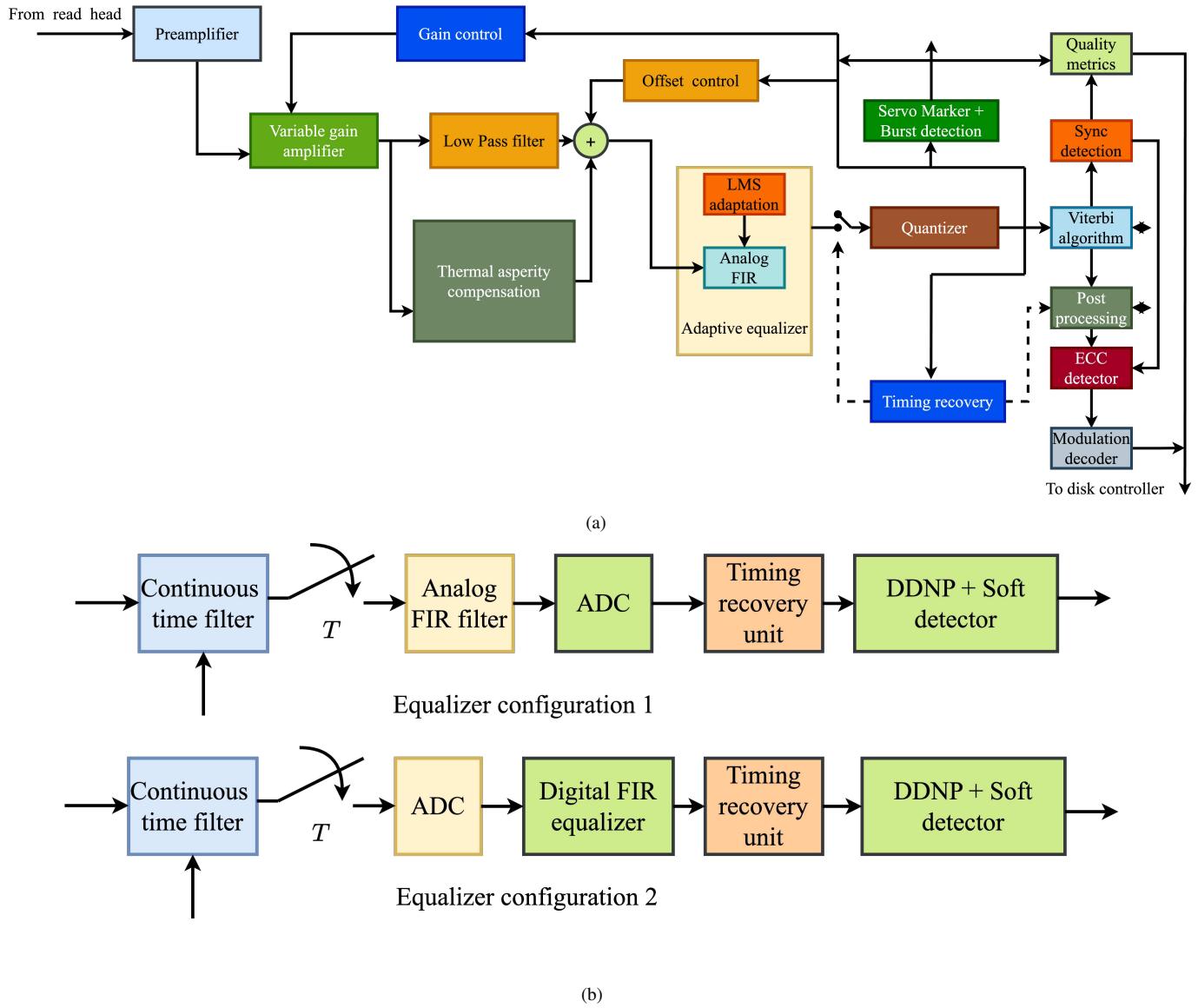

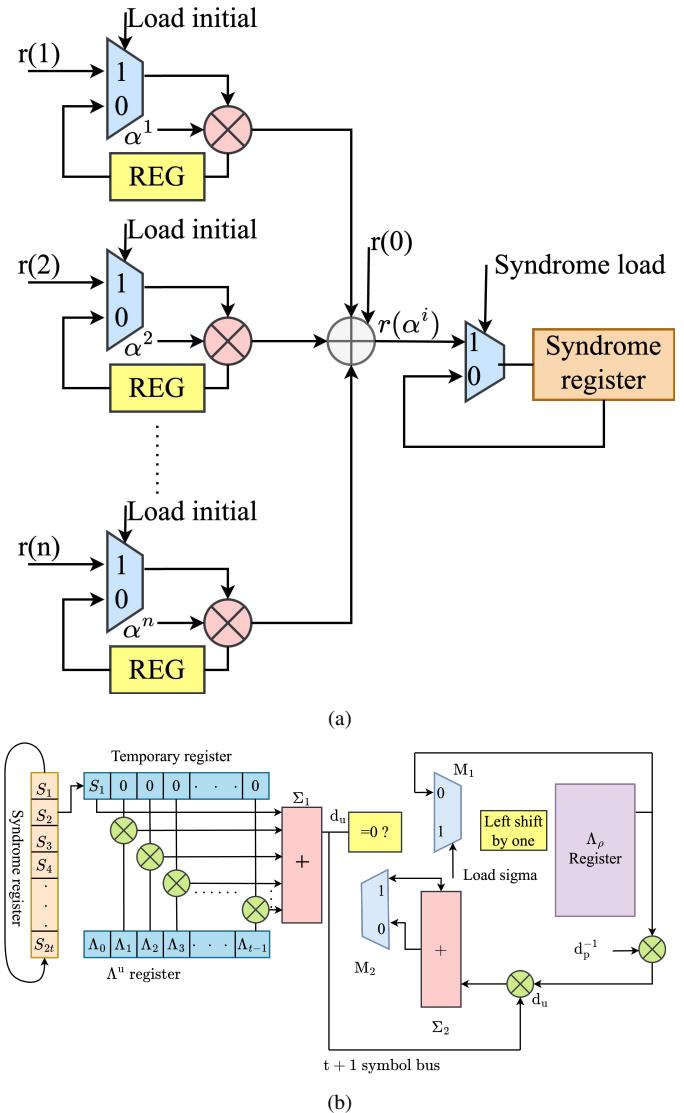

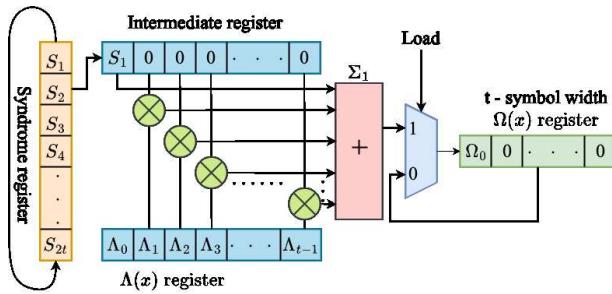

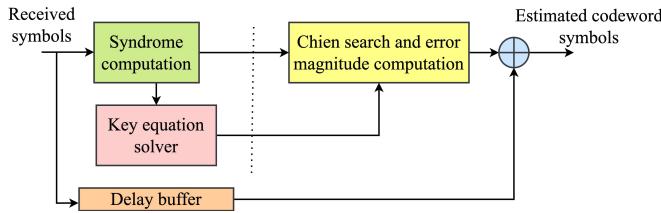

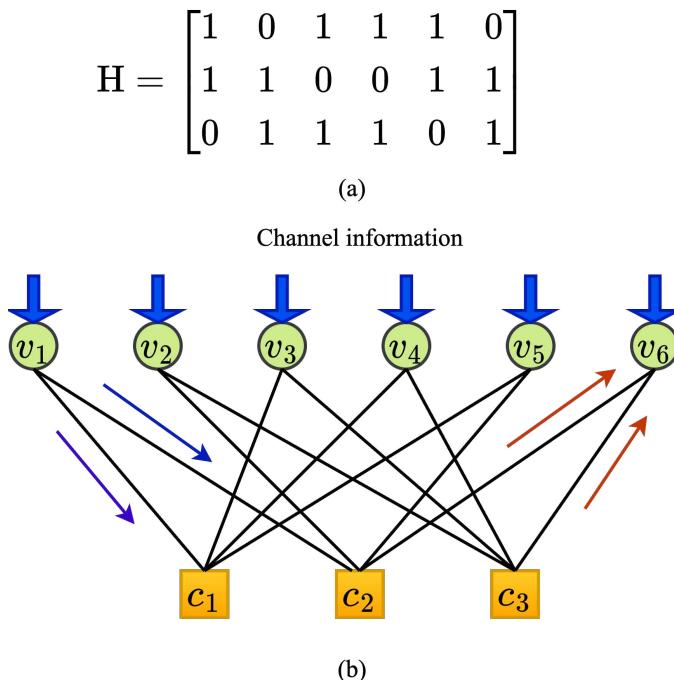

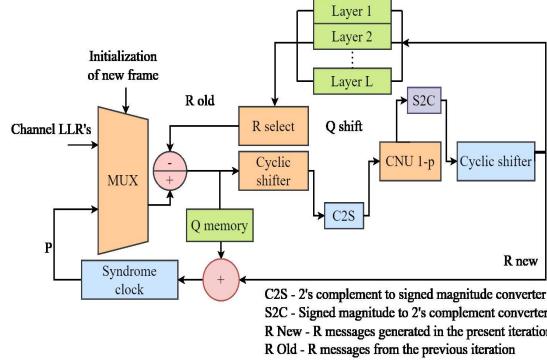

From now onwards, we will focus on the channels engineering aspects of HDDs. Figures 4(a) and 4(b) (Adapted from

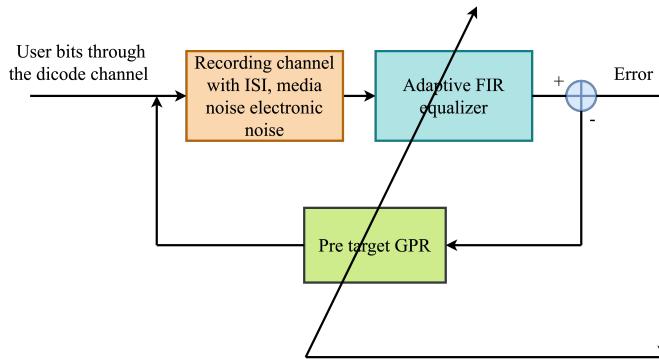

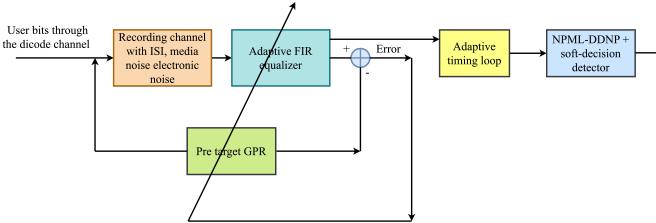

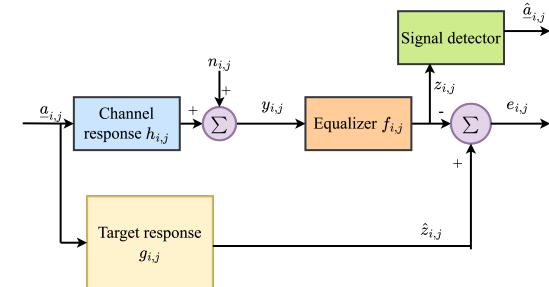

[27], Chapter 15) show the block diagram schematic of a read channel architecture. Information bits are encoded through an error correction coded and then modulated to satisfy the constraints of the channels. These bits are then written on to the medium through the write head after converting the current pulses to flux changes on the medium. After sensing the readback waveform, the signal is passed through a band-limited filter and an adaptive finite impulse response (FIR) equalizer to maintain a partial response (PR) target. Post sampling, the samples are driven by a timing recovery loop and signal detection. The detected bits are then decoded by the modulation code and through the ECC decoder before retrieving the information bits. The post-processor block in Figure 4(a) indicates a turbo loop for soft-decision decoding within the PRML setup. Thus, coding and signal processing algorithms are part of read channel ICs that interface with magnetic disk drives.

The act of storing and retrieving information reliably from a storage device is an instance of a noisy communications channel. With appropriate channel modeling, one can abstract the physical processes within a communication-theoretic framework so that tools from information theory, coding theory and signal processing can be applied towards channels development. A first step towards this effort is signal modeling.

Figure 4. (a) Schematic of a conventional read channel architecture. The signal from the read head goes through a preamp circuit, followed by a continuous-time filter to remove any out of band noise and an analog-to-digital converter (ADC). The signal chain includes an analog FIR equalizer based on the least mean squares (LMS) adaptation engine, adaptive gain and timing loops, and the Viterbi detector with post-processing towards error recovery. (Adapted from [27], Chapter 15). (b) Various configurations of analog and digital FIR equalizers within a PRML detector setup with noise whitening capability, such as using data-dependent noise prediction (DDNP) filters.

#### A. Signal Modeling for LMR and PMR

The playback signal strength depends on the physical parameters specific to a recording scheme.

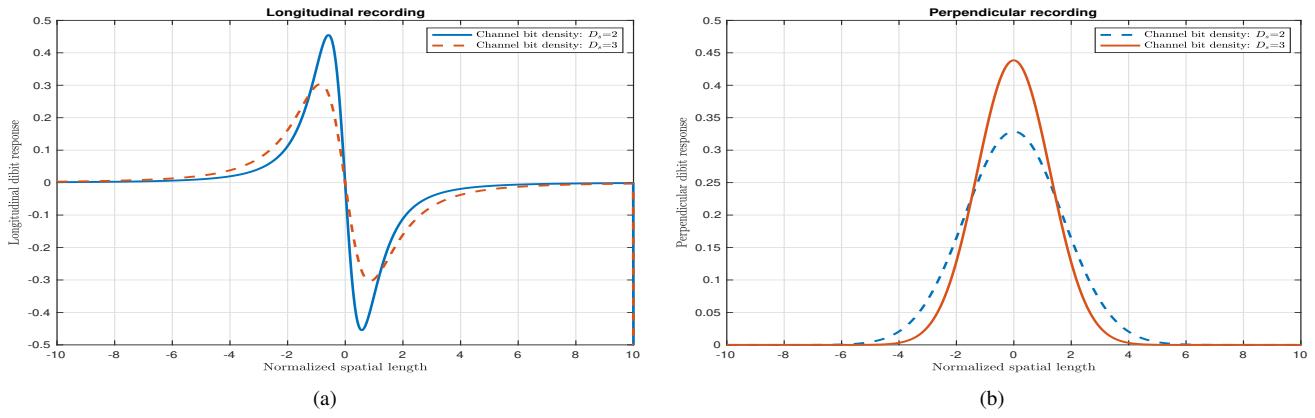

By considering the linear superposition of pulse amplitudes of isolated transition magnetic responses that depend on the written bits, we can abstract the signal model for the ditbit response  $p(t)$  for longitudinal recording over a pair of transitions separated by interval  $T$  as

$$y(t) = \sum_k b_k \underbrace{[h(t - kT) - h(t - (k-1)T)]}_{=p(t)} + n(t), \quad (1)$$

where  $h(t)$  is the Lorentzian model response given by

$$h(t) = \sqrt{\frac{4E_t}{\pi w}} \frac{1}{1 + \left(\frac{2t}{w}\right)^2}, \quad (2)$$

with  $w$  being the pulse width at half-maximum. The peak amplitude of the pulse depends on the properties of the magnetic medium such as the remanent magnetization, air gap length, width of the free layer etc. For more details, the interested reader can refer to [27] (see equation (2.31), Chapter 2 in [27]). In equation (2)  $E_t = \int |h(t)|^2 dt$  represents the normalized energy of the isolated transition response. The noise term  $n(t)$  in (1) represents both the media and electronics noise sources.

Similarly, the transition response for the PMR channel is simplified as

$$h(t, w) = V_p \left( \frac{2\sqrt{\ln(2)}}{w} t \right), \quad (3)$$

where  $V_p$  is the peak value of the isolated transition response. The pulse width  $w$  at half-maximum for PMR depends on the

Figure 5. LMR and PMR transition responses.

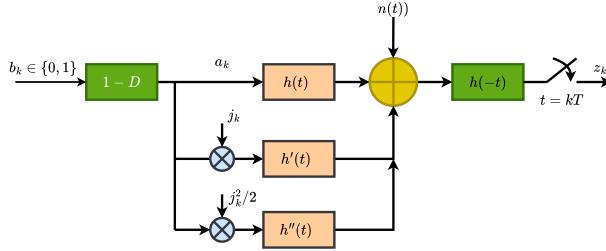

Figure 6. Continuous-time signal model with jitter contributions upto a second order. Adapted from [28].

air gap length, transition width, GMR free layer thickness, etc. To normalize the energy under the impulse response to unity, the peak value  $V_p$  is given by

$$V_p = \frac{1}{2} \left( \frac{\pi}{2w^2 \ln(2)} \right)^{\frac{1}{4}}. \quad (4)$$

Figure 5 shows the sketch of the transition response for both longitudinal and perpendicular recording schemes. Noise modeling from recorded waveforms is important for deriving channel models. Media noise, which is usually colored, arises due to variations in the media magnetization across the grains. The electronics noise, which is usually white, arises due to sensing and preamplifier circuits. Media noise is a consequence of stationary dc remanent noise due to random in-plane anisotropy dispersion (Chapter 2, [27]), noise due to transitions and modulation noise due to surface roughness. The dc remanent noise is absent in perpendicular recording due to loop squareness and the noise due to transitions is the only noise since magnetic grains can fall across bit cell boundaries.

A simple way of obtaining the noise model towards simulations is to have noise perturbations in the position  $t$  and width  $w$  parameters within the transition response  $h(t, w)$  as done in [28]. At a position  $k$ ,

$$h_k(t, w) = h(t - kT + j_k, w + w_k), \quad (5)$$

where  $j_k$  and  $w_k$  are random variables and assumed to be Gaussian distributed with zero mean and variances  $\sigma_j^2$  and  $\sigma_w^2$ , respectively.

By doing a Taylor series approximation of equation (5) using equations (2) and (3), we get the equivalent model described in Figure 6.

With this in place, we are set to define the SNR. The SNR for recording channels is given by

$$\text{SNR} = \frac{E_t}{N + M}, \quad (6)$$

where  $N$  is the electronics noise variance and  $M$  is the media noise variance. The media noise variance is given by

$$M = 2\sigma_j^2 I_j + 2\sigma_w^2 I_w, \quad (7)$$

$$\text{where } I_j = \int_0^\infty \left( \frac{\partial h}{\partial t} \right)^2 dt \text{ and } I_w = \int_0^\infty \left( \frac{\partial h}{\partial w} \right)^2 dw.$$

The linear density or channel bit density (cbd) is given by

$$D_s = \frac{PW_{50}}{T}. \quad (8)$$

Since the data is coded at a rate  $R$ , the user bit density (ubd) is given by

$$\text{ubd} = \text{cbd} \times R. \quad (9)$$

In a practical setup, the systems are oversampled with a factor  $O_s$ . If the SNR is  $S$  dB and the energy in the transition response is  $E_i$ , then, for a given cbd and  $\frac{M}{N+M} = f$ , the electronic noise variance is given by

$$\sigma_e^2 = (1 - f) \frac{E_i \times \text{cbd}}{2} O_s 10^{-0.1S}. \quad (10)$$

Equation (10) is helpful for obtaining the required noise parameters for generating the waveforms towards simulations.

With these details in place, we are now ready towards a simulation model for assessing the performance of the signal chain for LMR and PMR channels. Let us now discuss signal models for advanced channels.

## B. Signal Models for Advanced Channels: A TDMR Case Study

TDMR achieves high AD gains by reducing the bit size in both the directions within the bounds dictated by the magnetic quadrilemma. With bit-sizes to the order of a magnetic grain size, irregularities in the medium defined by the position and geometry of the grains will influence the read and write

processes.

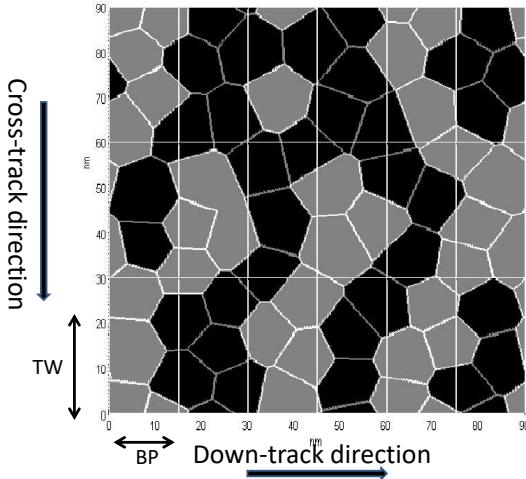

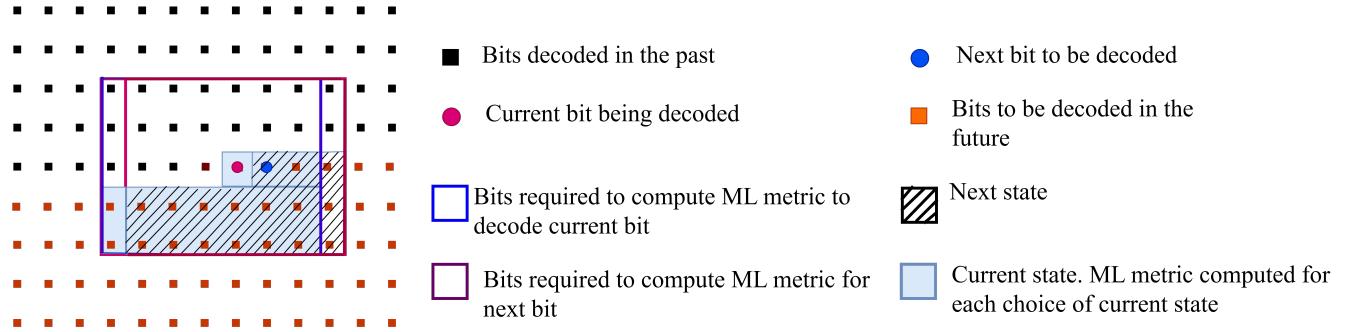

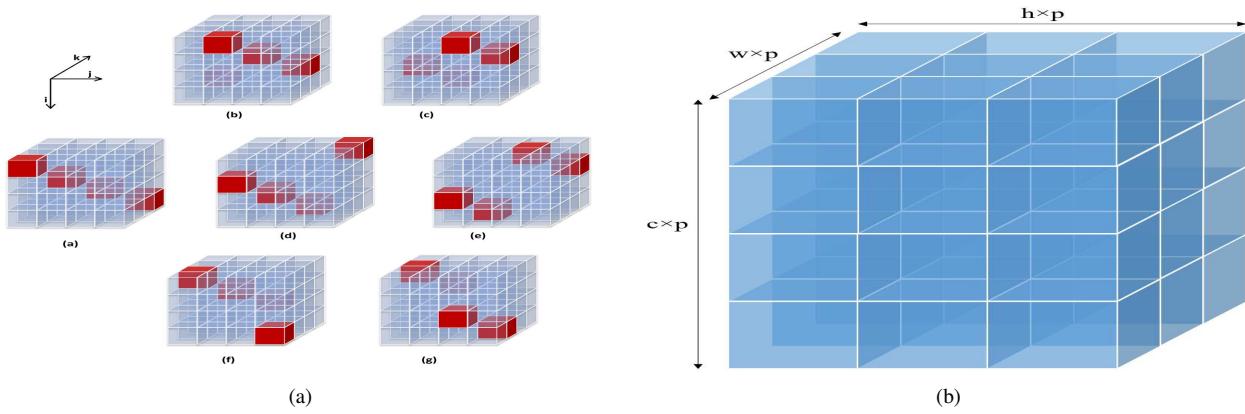

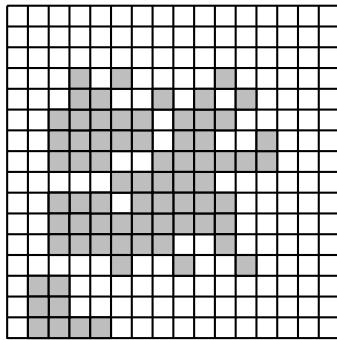

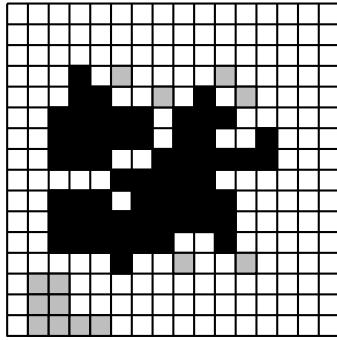

Though there are many simple models for TDMR such as the binary error and erasure model and the discrete grain model [29] [30], we will focus specifically on the Voronoi-based model and discuss the details of this channel model (media model, read and write procedures, and noise characteristics) in depth since it is the accepted model for read channel simulations in the industry, and is used in [31] [32]. Figure 7 shows the Voronoi tiling model for TDMR. Each

Figure 7. An example of the Voronoi channel model. The bit cell width along the track is  $BP=15$  nm. In the cross-track direction, the track width is  $TW=30$  nm. The center-to-center (CTC) spacing is 10 nm. Adapted from [6].

Voronoi region on the magnetic medium represents a grain. The distribution of Voronoi centers is modeled using a point process, typically a Poisson random process. The magnetic domains are formed using the Voronoi regions whose centers are the grain centers. Physics-based micromagnetic models simulate the sizes, shapes, and distribution of the grains close to an actual magnetic recording medium.

The micromagnetic recording model [33]–[35] assumes a granular thin film medium in which grains are uniformly magnetized. This model makes no prior assumptions of a grain shape or location. The magnetostatic and exchange interactions between nearest neighbors are calculated with the knowledge of the grain shape, and the magnetostatic interactions between more distant pairs of grains are computed hierarchically. The time evolution of the magnetization is computed by integrating the Landau-Lifshitz-Gilbert (LLG) equation in spherical polar coordinates using a Krylov ordinary differential equation (ODE) solver [36]. Head-field distributions are precomputed for some direct currents (dc), and the recording sequence is defined by the velocity of the head over the medium and a head current waveform represented by the random bit sequence to be recorded. The field at each point of interest in the medium is then computed by spatially interpolating the head-field distribution. TDMR platform simulations were also done in [37] using the micromagnetic model. Also, the micromagnetic model has been used to predict AD limits in perpendicular

recording [38]. There are other intermediate models based on quasi-micromagnetic simulations [39]. However, the high complexity of micromagnetic model makes it difficult to run simulations for the performance evaluation of coding and signal processing algorithms [39], [40].

We shall now discuss more details about the Voronoi model.

1) *Recording Media Model*: The Voronoi tiles are used to simulate the irregularities of magnetic grains. The distribution of grains on the medium can be modeled using a Poisson-disk process with boundary sampling, as proposed in [41]. Each new grain is randomly generated such that it touches at least one of the existing grains to achieve a close random packing under the CTC constraint. Before a new grain is generated, the boundary that is at a CTC distance from the existing grain centers is identified. The position of a new grain is randomly generated with a uniform probability density on the identified boundary.

According to the Voronoi model, the storage medium comprises tiling of the shifted grain-centers with each region representing the grains. With a rectangular grid over bit cells, each cell of size  $BL \times TW$  represents the size of the bit cell in the downtrack and crosstrack directions. The bit aspect ratio (BAR) which is defined as  $BAR = \frac{TW}{BL}$  governs the minimum resolution of magnetization. The act of writing and reading an information bit from a bit cell, i.e., from a rectangular cell with a given bit length and bit aspect ratio, constitutes an instance of a noisy communication process, i.e., a *noisy channel*. The bit cell area is equivalent to the channel bandwidth. The channel bit density is given by  $\frac{1}{TW \times BL}$  bits/unit-area.

2) *Write Process*: During the writing process, the read head writes the bipolar coded symbol  $x_{i,j}$  by changing the magnetic polarity of all grains whose centers lie within the  $(i,j)^{th}$  bit cell according to the value of bit  $x_{i,j}$ . Magnetic domains are formed by the continuous regions of Voronoi cells with the same polarity of magnetization. The channel input signal  $x(t_1, t_2)$  is given by

$$x(t_1, t_2) = \sum_{i,j} x_{i,j} \Pi_{TW}(t_1 - i \times TW) \Pi_{BL}(t_2 - j \times BL), \quad (11)$$

where  $x_{i,j} \in \{-1, +1\}$  is the symbol which will be written on the  $(i,j)^{th}$  bit cell and

$$\Pi_T(t) = \begin{cases} 1 & \text{if } 0 \leq t < T, \\ 0 & \text{otherwise.} \end{cases} \quad (12)$$

The indices  $t_1$  and  $t_2$  refer to the spatial coordinates on the magnetic disk.

3) *Read Process*: The readback signal depends on the grain magnetization and read head geometry [42] along with crosstalk received from neighboring cells that depends on the grain distribution. Suppose that the read head picks up magnetization only from  $m \times n$  neighboring cells. As a result, the read head output sample  $y_{i,j}$  at the center of the  $(i,j)^{th}$  cell depends only on the polarity of the grains in the  $m \times n$  neighborhood around the  $(i,j)^{th}$  cell, denoted as  $C_{i,j}$ . We use the 2D Gaussian pulse model for the read head sensitivity function. The 2D Gaussian pulse is characterized by the pulse

widths  $PW50_x$  and  $PW50_y$  at half-amplitude in the down-track and cross-track directions.

$$h(x, y) = \frac{\ln 2}{\pi PW50_x PW50_y} \exp \left( -\frac{(\ln 2)x^2}{PW50_x^2} - \frac{(\ln 2)y^2}{PW50_y^2} \right), \quad (13)$$

with  $\int_{-\infty}^{\infty} \int_{-\infty}^{\infty} h(x, y) dx dy = 1$  for normalization.

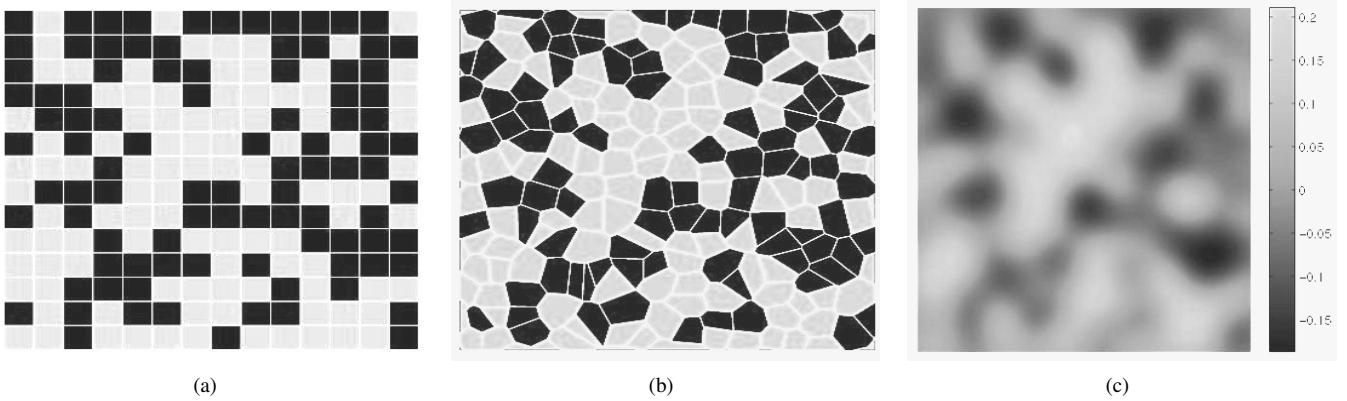

The read head sensitivity function is the contribution of each grain towards the generation of a readback signal. Figure 8 shows the distribution of grains on the medium, magnetization of the Voronoi regions on the medium and the continuous time readback signal without electronic noise.

Let  $h_{i,j}[p, q]$  be the discrete-time read response of the bit at position  $(i, j)$ . The indices  $p, q$  are integers representing samples on the 2D media after sampling. These response coefficients are random and dependent on the position and shape of grains within the bit area. We can compute the average bit-response as

$$h(p, q) = \mathbf{E}_{I, J} [h_{i,j}[p, q]], \quad (14)$$

where  $I$  and  $J$  are random variables indicating the distribution of the positions of grain centers in the down-track and cross-track directions, respectively.

The readback signal sample without considering the electronic noise is given by

$$y_{i,j} = \sum_p \sum_q x_{i-p, j-q} h_{i-p, j-q}[p, q], \quad (15)$$

where  $x_{i,j}$  is the symbol written on the  $(i, j)^{\text{th}}$  bit-cell. Furthermore, the ideal read head output,  $s_{i,j}$ , is obtained by considering the average discrete-time output of the  $(i, j)^{\text{th}}$  bit area as

$$s_{i,j} = \sum_p \sum_q x_{i-p, j-q} h[p, q]. \quad (16)$$

The mean squared value of the read-back signal is computed as  $V_p^2 = \sum_p \sum_q |h[p, q]|^2$ . The media noise comes from the random perturbations of  $h_{i,j}[p, q]$  around the average response  $h[p, q]$ . Therefore, the energy of media noise  $\sigma_m^2$  is computed as

$$\sigma_m^2 = \mathbf{E}_{I, J} \left[ \sum_p \sum_q |h_{i,j}[p, q] - h[p, q]|^2 \right]. \quad (17)$$

For TDMR channels, we have three different SNR notions:

$$\text{SNR} = 10 \log_{10} \left( \frac{V_p^2}{\sigma_m^2 + \sigma_e^2} \right), \quad (18)$$

$$\text{SNR}_{\text{Media}} = 10 \log_{10} \left( \frac{V_p^2}{\sigma_m^2} \right), \quad (19)$$

$$\text{SNR}_{\text{Elec}} = 10 \log_{10} \left( \frac{V_p^2}{\sigma_e^2} \right), \quad (20)$$

SNR refers to the overall SNR, while  $\text{SNR}_{\text{Media}}$  and  $\text{SNR}_{\text{Elec}}$  are the SNRs corresponding to the media and electronic noise sources, respectively.

The noise distribution for different input patterns can be obtained using the Voronoi model to study the impact of how neighboring bit transitions lead to increased noise. Study of the noise distribution is helpful in computing the symmetric information rates and optimization of the TDMR system parameters under various channel conditions [43] [44]. The most harmful patterns are those that have consecutive transitions along the on-track and off-track directions, leading to degraded performance during signal detection [44] [45].

### C. Signal Models for HAMR and BPMR

The read channel model for BPMR can be described by a 2D ISI channel [46]. The contribution of a magnetic island to the readback signal is determined by the integral of the head potential function over that island. The 2D ISI channel is parameterized by two parameters: (a) the down-track crosstalk parameter that is determined by the distance between the shields and the MR element, and (b) the cross-track crosstalk parameter determined by the width of the read head. By obtaining the 2D ISI channel in the form of a matrix, the discrete model for readback signal is obtained using the 2D filter and amplitude coded bits within a linear systems framework [47].

For the write process, since the head size can be more than the spacing between the magnetic islands, there could be write errors, with subsequent islands overwritten. The positioning of the head requires synchronization during writing without which one can have synchronization mismatch during writing due to write clock offsets. Further, due to fused islands [21], one can have insertions or deletions that need to be handled through special codes. All these contribute to *written-in* errors, which must be overcome through proper coding during the write process [48].

In [49], the authors derived a channel model for HAMR using the thermal Williams-Comstock model [50]. The authors in [51], consider modeling the write and read portions using HAMR over a bit-patterned media. In that model, during writing a portion of the grains  $P$  can be flipped according to a flip probability [51] along the reversing field that depends on energy barrier required to flip the magnetization w.r.t the switching field and the temperature.

$$\frac{dP}{dt} = \alpha(1 - P) \exp \left( -\frac{\Delta_e}{k_B T} \right), \quad (21)$$

where  $\alpha$  is a constant. The energy barrier  $\Delta_e$  depends on the magnetic energy  $M(T)$  per unit volume that in turn depends on temperature, anisotropy constant  $K(T)$ , applied field  $H$  and magnetization as a function of temperature  $T$  given by [51]

$$\Delta_e = (K(T) - M(T)) VH. \quad (22)$$

## III. CAPACITY ESTIMATION FOR MAGNETIC RECORDING CHANNELS FROM INFORMATION-THEORETIC TOOLS

The capacity of a data storage system under noisy conditions is the upper limit on the number of bits per unit area that one can store on the magnetic medium with an arbitrarily small

Figure 8. Write/read model for the Voronoi medium: (a) Desired magnetization of an ideal medium. The grains with magnetization +1/-1 are shaded white and black in each of the squares. (b) Magnetization of a non-ideal medium as per the Voronoi model. (c) Readback signal (before sampling). We assume the readback impulse response is a truncated 2D Gaussian pulse of unit energy with half-maximum of 1 bit-period and a span of 3 bit-periods in both dimensions. Adapted from [6].

probability of decoding error. From Shannon's channel coding theorem [52], if we choose a long enough code length  $n$ , one can code the data bits at a rate  $R < C$ , where  $C$  is the channel capacity with an arbitrarily small probability of error  $p_e^{(n)} < \epsilon_n$  and  $\epsilon_n > 0$ . The evaluation of the channel capacity  $C$  is difficult. In general, it is not possible to exactly obtain the capacity for magnetic recording channels since the channel is non-stationary as the error rates can vary across the tracks and with device aging. Also, the stationarity/ergodicity conditions in Shannon's original theorem do not hold in practice for magnetic recording channels. Thus, it is important to come up with reasonable estimates for computing the channel capacity under certain assumptions.

The capacity estimate of the recording channel can serve as a performance benchmark for designing error correction codes and for optimizing the physical parameters of data storage systems [53]–[55]. The reader must also note that a practical way of distilling the tightest coding rate for a practical magnetic recording channel is to increase the coding rate to such an extent that there are errors beyond a threshold<sup>4</sup>. Using bit error rate as the comparison criterion encapsulates the channel and the signal detector using a simple model, such as a binary symmetric channel, which provides a loose lower bound on the information rate. Based on physically abstracted channel models, one could directly compute the mutual information rate with different input distributions under different bit aspect ratios to obtain a lower bound on the achievable storage density as done in [55].

Chan et al. [56] use the grain-flipping probability model to optimize the areal density using a signal chain that includes the partial response equalizer, soft-output Viterbi detector, and low-density parity check decoder. By varying the physical parameters, such as the bit length, track pitch and code rate in the simulations, areal density is evaluated empirically for

<sup>4</sup>This is one of the practical ways engineers fine-tune the coding parameters after an initial estimate of the capacity since the stationary/ergodicity assumptions do not hold in a practical setup. Also, a wide range of coding rates are distilled depending on the device aging properties and various stress tests done in practice.

different head/media configurations. However, the detector is still 1D, which could be still limiting.

The capacity of discrete channels is defined as the maximum MIR over all discrete-input distributions. Various bounds on the capacity of certain 1D discrete input channels with ISI have been proposed [57]–[60]. The MIR or i.i.d. capacity can be computed with reasonable accuracy using Monte Carlo methods.

#### A. Computing Mutual Information Rates: Trellis-based Approach

The information rate for 1D additive white Gaussian noise (AWGN) channels with memory can be computed using the forward recursion of the sum-product (Bahl-Cocke-Jelinek-Raviv, BCJR) algorithm [61].

1) *Capacity Estimate for the 1D Framework*: Post partial response equalization with a pre-target and whitening of the noise, the equivalent magnetic recording channel is approximately a linear ISI channel. We shall describe how to estimate the MIR for an ISI channel. Consider the MIR for  $n$ -uses of the channel, taking inputs  $\mathbf{x}^{(n)}$  and producing outputs  $\mathbf{y}^{(n)}$  given by:

$$I(X; Y) = \lim_{n \rightarrow \infty} \frac{1}{n} I(\mathbf{x}^{(n)}; \mathbf{y}^{(n)}). \quad (23)$$

Now, equation (23) can be computed as

$$I(X; Y) = h(Y) - \underbrace{h(Y|X)}_{=h(Z)}, \quad (24)$$

where  $h(Y) = \lim_{n \rightarrow \infty} \frac{1}{n} h(y^{(n)})$  and  $h(Z) = \lim_{n \rightarrow \infty} \frac{1}{n} h(z^{(n)})$ .

After whitening through NPML [13], the noise statistics are approximately Gaussian distributed  $\mathcal{N}(0, \sigma_x^2)$ ; hence,  $h(Z) = \frac{1}{2} \log_2(2\pi e \sigma_z^2)$ . We are now left with the computation of  $h(Y)$ .

This is where the ideas behind the BCJR algorithm [62] help us. For this, we need to bring in some parameters related to the trellis formalism. Suppose the ISI memory is  $N$  and the input alphabet size is  $|\mathcal{X}|$ . There are  $|\mathcal{X}|^N$  states in the trellis.

The forward probability of ending in a state  $j$  at time  $k$  can be computed as

$$\alpha_k(j) = P(y^k, S_k = j). \quad (25)$$

The term  $\alpha_k(j)$  in can be obtained through the recursion

$$\alpha_k(j) = \sum_i \alpha_{k-1}(j) \gamma_k(i, j), \quad (26)$$

where  $\gamma_k(i, j) = P(S_k = j, y_k | S_{k-1} = i)$  is the branch probability i.e., transitioning from state  $i$  at time instant  $k-1$  to state  $j$  at time instant  $k$ .

The overall probability  $P(y^{(k)})$  can be obtained as

$$P(y^{(k)}) = \sum_j \alpha_k(j). \quad (27)$$

By initializing  $\alpha_0(j)$  for all states  $j$  with the stationary distribution<sup>5</sup> of the inputs, one can efficiently compute  $P(y^{(k)})$  for a certain noise realization. By averaging the computation  $p(y^{(n)})$  over several runs, we can obtain

$$h(Y) = - \lim_{n \rightarrow \infty} \frac{1}{n} \mathbb{E} \left[ \log_2 \left( p(y^{(n)}) \right) \right]. \quad (28)$$

From equations (24)-(28), one can estimate the MIR for ISI channels post noise whitening. The reader must note that when the noise is not fully whitened, one must account for correlations in the noise while computing  $h(Z)$ . Further, in the case of data-dependent noise prediction (DDNP) [63] that comprises a bank of noise whitening filters that depend on each input pattern, the overall entropy rate conditioned to each input pattern can be evaluated based on the local noise statistics from DDNP filters using the MIR estimation ideas we discussed in this subsection.

2) *Capacity Estimate for the 2D Framework:* Similar to the 1D case, the overall 2D channel for TDMR systems can be approximated to a 2D finite-state ISI channel with AWGN after noise whitening, described by

$$y_{i,j} = \sum_{k=1}^M \sum_{l=1}^N h_{k,l} x_{i-k, j-l} + n_{i,j}, \quad (29)$$

where  $x_{i,j} \in \{-1, +1\}$  indicates the magnetization of  $(i, j)^{\text{th}}$  channel's bit cell,  $y_{i,j}$  is the  $(i, j)^{\text{th}}$  read-back sample, and  $n_{i,j}$  is the realization of noise under Gaussian statistics, i.e.,  $\mathcal{N}(\mathbf{0}, \Sigma)$ . The MIR of the TDMR channel with the probability distribution function  $P(\mathbf{y}|\mathbf{x})$  is defined as the mutual information between channel's input  $\mathbf{x} = [x_{i,j}]$  and the output  $\mathbf{y} = [y_{i,j}]$ . We now compute MIR as follows:

$$\text{MIR} = \frac{1}{NM} I(\mathbf{X}; \mathbf{Y}) = \frac{1}{NM} H(\mathbf{Y}) - \frac{1}{NM} H(\mathbf{Y}|\mathbf{X}), \quad (30)$$

where  $H(\cdot)$ ,  $H(\cdot|\cdot)$ , and  $I(\cdot; \cdot)$  in equation (30) are the entropy, conditional entropy, and mutual information terms, respectively. Knowing the channel  $P(\mathbf{y}|\mathbf{x})$ ,  $H(\mathbf{Y}|\mathbf{X})$  can be computed. The problem of obtaining the MIR reduces to

<sup>5</sup>The reader must note that when input sequences are constrained (see for example, RLL constraints) and represented through finite state transition diagrams or equivalently constrained graphs, the stationary distribution of the source can be used as the initial condition.

computing the entropy rate of the channel's output  $H(\mathbf{Y})$ . From Shannon-McMillan-Breimann theorem [64], assuming stationarity and ergodicity, the entropy rate is computed as

$$-\frac{1}{n} \log p(\mathbf{y}) \rightarrow H(Y), \quad (31)$$

as  $n \rightarrow \infty$  with probability 1. By adopting the trellis-based strategy over multiple rows over the 2D array of inputs and outputs, similar to how we outlined the procedure for the 1D case, one could calculate the marginal output distribution  $p(y)$  for large  $n$  for 2D arrays as well. For more details, the reader is referred to [6].

In general, for 2D channels with memory, it is not known whether a stationary ergodic random field will achieve the capacity [65]. Recently, for a special class of 2D channels, Li and Siegel [66] showed that the operational capacity and information capacity (Shannon capacity) are equal and can be achieved by a stationary ergodic random field with input constraints.

### B. GBP based Capacity Estimation Method

Probabilistic graphical models are important in a wide variety of applications from solving combinatorial problems in statistical physics to inference problems in signal processing [67]. These problems can be reformulated equivalently as the computation of marginal probabilities on factor graphs [68] using message passing algorithms, such as the belief propagation (BP) algorithm used in coding theory [69] for decoding low-density parity check (LDPC) codes and in artificial intelligence [70]. Computing marginals of functions on a graphical model has its roots in the broad class of Bayesian inference problems [71].

It is well-known that the BP algorithm gives exact inference only on acyclic graphs, i.e., trees. Further, it is also well-known that BP works poorly on graphs containing a large number of short cycles (subgraphs with girth=4). The problem of TDMR channel capacity estimation can be considered as one of the problems corresponding to a factor graph with many short cycles. There are many cycles in a TDMR channel factor graph, referring to Figure 9, which invalidates the tree-like assumption used in BP, leading to poor performance of the BP algorithm. A new class of message passing algorithms called *generalized belief propagation* (GBP) was introduced by Yedidia, Freeman and Weiss [72] to solve this problem<sup>6</sup>. The GBP estimates are approximately close to the true estimate.

Since GBP benefits from region-to-region message passing instead of the node-to-node message passing algorithm of BP, GBP algorithm can often dramatically outperform the BP algorithm in either accuracy or convergence properties. The output probabilities from a 2D channel actually correspond to a Boltzmann distribution of an Ising Hamiltonian, with pairwise interactions and external random fields [73] [74]. The difficulty in estimating *a posteriori* probabilities lies in estimating the partition function of factor graphs, or similarly, the free energy in statistical physics. For the case of capacity

<sup>6</sup>The reader must note that the estimate obtained through the GBP algorithm is not *exact* in general.

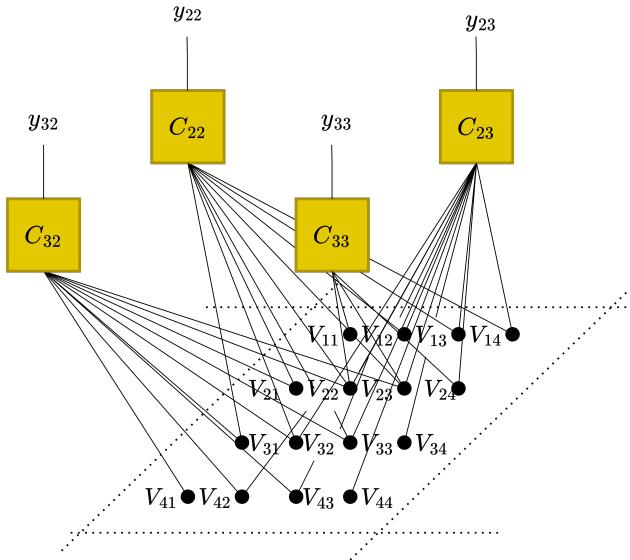

Figure 9. Every  $3 \times 3$  square within the lattice of  $4 \times 4$  comprising variables  $v_{i,j}$  is controlled by a local function  $c_{i,j}$ . The bi-indices  $(i, j)$  indicate the coordinates of the variable node on the lattice. Adapted from [6].

estimation of TDMR channels, the GBP algorithm can be utilized to estimate the marginal distribution from the channel outputs and consequently the channel capacity. GBP algorithm can be used to estimate the MIR for TDMR channels [44].

The GBP algorithm as a message passing algorithm can operate on the region graph of the TDMR channel to compute the marginal probabilities. The belief of each region as an output of the GBP algorithm is an approximation of the marginal probability. As the GBP is a message passing algorithm, we first introduce the graphical representation for the procedure.

The factor graph is a bipartite graph representing the factorization of a function, comprising a set of random variables  $\mathbf{V}$  and a set of local functions (local constraints)  $\mathbf{F}$ . In the factor graph, random variables  $V_i \in \mathbf{V}$  are represented by circles (variable node) and local functions  $f_j \in \mathbf{F}$  are illustrated by squares (factor node). A variable node  $V_i$  is connected to a factor node  $f_j$  if and only if  $V_i$  is an argument of  $f_j$ . Figure 9 depicts the factor graph corresponding to a  $4 \times 4$  grid where each  $3 \times 3$  square region is locally constrained by a factor node.

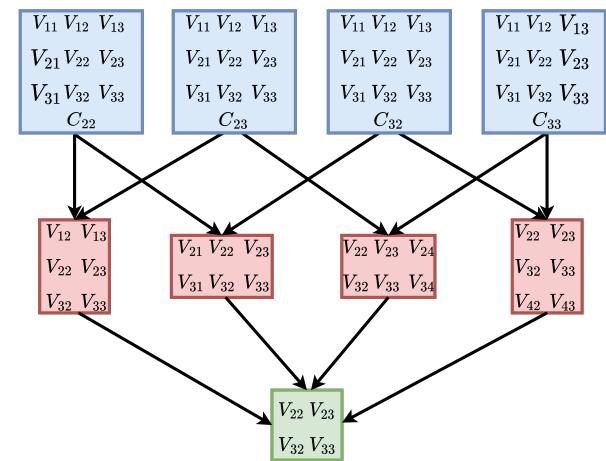

For a given graphical model, the region graph is generated according to the cluster variation method [72] [75]–[77]. A parent region  $R$  is specified by a set of variable nodes and factor nodes such that if  $f_j \in R$ , then all the variable nodes connected to  $f_j$  must be in  $R$ . Figure 10 shows the region graph for the factor graph of 2D ISI constraint shown in Figure 9. In this example, we choose each factor node to be in a separate parent region for simplicity. The variable nodes connected to the factor node also reside in that region. The child regions of a region graph are then constructed by taking the intersection of the parent regions, the intersections of the intersections, and so on through the tree.

In the case of capacity estimation setup, the factor function  $f(\mathbf{x}_{C_{i,j}}) = p(y_{i,j}|\mathbf{x}_{C_{i,j}})$ , and the local constraint is the same for all the parent regions. The partition function  $Z$  and the

Figure 10. Region graph representation of the factor graph in Figure 9. Adapted from [6].

Helmholtz free energy  $F_H$  are related as  $F_H = -\ln Z$ . For the purpose of estimating the information rate, we define the partition function as

$$Z(\mathbf{y}) = \sum_{\mathbf{x}} \prod_{i,j} p(y_{i,j}|\mathbf{x}_{C_{i,j}}) = \sum_{\mathbf{x}} p(\mathbf{y}|\mathbf{x}), \quad (32)$$

where  $f(\mathbf{x}_{C_{i,j}})$  is the factor function explained above.

As previously discussed, the main problem of estimating the MIR reduces to estimating the entropy of the channel output  $\mathbf{y}$ . For this purpose, we use empirical averaging

$$H(\mathbf{Y}) = -\mathbf{E}_{\mathbf{y}} \log p(\mathbf{y}) \approx -\frac{1}{L} \sum_{l=1}^L \log p(\mathbf{y}^{(l)}), \quad (33)$$

where  $L$  is the number of samples  $\mathbf{y}$  drawn according to  $p(\mathbf{y})$ . Applying Bayes' law and using the channel model distribution,  $p(\mathbf{y})$  can be written as

$$p(\mathbf{y}^{(l)}) = \sum_{\mathbf{x}} p(\mathbf{x}) p(\mathbf{y}^{(l)}|\mathbf{x}), \quad (34)$$

where  $\sum_{\mathbf{x}}$  corresponds to a sum over all possible  $\mathbf{x} \in \mathcal{X}$ .

The output entropy term reduces to

$$\begin{aligned} H(Y) &= -\frac{1}{L} \sum_{l=1}^L \log \left( \frac{1}{|\mathcal{X}|} Z(\mathbf{y}^{(l)}) \right) \\ &= \log(|\mathcal{X}|) - \frac{1}{L} \sum_{l=1}^L \log(Z(\mathbf{y}^{(l)})), \end{aligned} \quad (35)$$

with uniform input distribution i.e.,  $p(\mathbf{x}) = \frac{1}{|\mathcal{X}|}$ . Therefore, the problem of estimating the mutual information rate of a TDMR channel reduces to the problem of estimating  $\sum_{\mathbf{x}} p(\mathbf{y}^{(l)}|\mathbf{x}) = Z(\mathbf{y}^{(l)})$  as in (32). The indicator function can be written as the product of local kernels, each having some subset of  $\mathbf{x}$  as an argument i.e.,  $f(\mathbf{x}) = \prod_a f_a(\mathbf{x}_a)$ , where the indices  $a$  of the local kernels correspond, for example, to the set of all the three adjacent bits in the horizontal and vertical directions.

Computing  $Z$  can be done by the finding the region-based free energy estimate. More precisely, the Helmholtz free energy  $F_H$  can be estimated using the region-based free energy approximation technique, giving the partition function  $Z$ . If the GBP is used to compute the beliefs of each region  $b_R(\mathbf{x}_R)$ , using the estimated beliefs, an estimate of the free energy  $\hat{F}_H$  can be computed using

$$\hat{F}_H = \sum_{R \in \mathcal{R}} c_R \sum_{\mathbf{x}_R} b_R(\mathbf{x}_R) \left( \ln b_R(\mathbf{x}_R) - \ln \prod_{a \in A_R} f_a(\mathbf{x}_a) \right), \quad (36)$$

where  $\mathcal{R}$  is the set of all regions,  $c_R$  is the counting number,  $\mathbf{x}_R$  is the set of variables in  $R$  and  $A_R$  is the set of local kernels in region  $R$ . We use parent-to-child messaging with one kind of message passed between regions. The belief of any region is the product of all the local factors in the region, multiplied by the messages coming into that region and to its descendants from outside. Each region  $R$  has a belief  $b_R(\mathbf{x}_R)$  given by [72]

$$\begin{aligned} b_R(\mathbf{x}_R) &= \prod_{a \in A_R} f_a(\mathbf{x}_a) \left( \prod_{P \in \mathcal{P}(R)} m_{P \rightarrow R}(\mathbf{x}_R) \right) \\ &= \left( \prod_{D \in \mathcal{D}(R)} \prod_{P' \in \mathcal{P}(D) \setminus \mathcal{E}(R)} m_{P' \rightarrow D}(\mathbf{x}_D) \right), \quad (37) \end{aligned}$$

where  $A_R$  is the set of elements in region  $R$  and the  $f_a(\mathbf{x}_a)$  are the local factors of region  $R$ .  $\mathcal{P}(R)$  and  $\mathcal{D}(R)$  are, respectively, the parent and descendant regions of  $R$ .  $\mathcal{E}(R) = R \cup \mathcal{D}(R)$  and  $\mathcal{P}(D) \setminus \mathcal{E}(R)$  is the set of all regions that are parents of region  $D$  except for  $R$  and descendants of  $R$ .

With the terms,  $T_{P \setminus R} = \prod_{a \in F_{P \setminus R}} f_a(\mathbf{x}_a)$  and  $T_{N(P, R)} = \prod_{(I, J) \in N(P, R)} m_{I \rightarrow J}(\mathbf{x}_J)$ , the message-update rule in the parent-to-child algorithm is

$$m_{P \rightarrow R}(\mathbf{x}_R) = \frac{\sum_{\mathbf{x}_{P \setminus R}} T_{P \setminus R} T_{N(P, R)}}{\prod_{(I, J) \in D(P, R)} m_{I \rightarrow J}(\mathbf{x}_J)},$$

where the set  $N(P, R)$  indicates all connected pairs of regions  $(I, J)$  such that  $J \in \mathcal{E}(P) \setminus \mathcal{E}(R)$ , while  $I \notin \mathcal{E}(P)$ .  $D(P, R)$  is the set of all connected pairs of regions  $(I, J)$  such that  $J \in \mathcal{E}(R)$ , while  $I \in \mathcal{E}(P) \setminus \mathcal{E}(R)$ .  $F_{P \setminus R}$  is a set of factor nodes in the region  $P \setminus R$ .

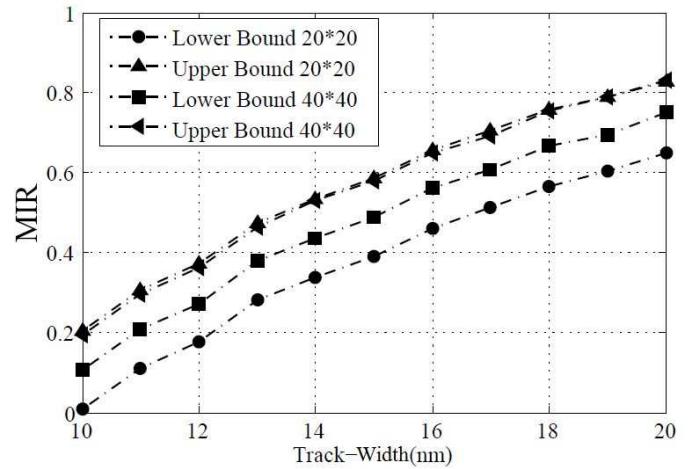

*Example 1:* We estimate the MIR by using the GBP algorithm for an  $M \times N$  array over the Voronoi channel model. We obtain lower and upper bounds on the GBP-based MIR estimation for a Voronoi channel. The lower and upper bounds merge to the actual value for the MIR estimation of the Voronoi channel with increasing dimensions of the 2D array.

*Obtaining the lower bound:* In order to compute the beliefs of the boundary regions, we assume that all the states of the boundary regions are equiprobable. Under this assumption and using the GBP algorithm as described before, we establish a lower bound on the MIR of a TDMR system.

*Obtaining the upper bound:* The boundary information of the medium is known to the MIR estimator. For boundary

Table I

ALL THE PARAMETERS IN THE TABLE ARE IN NANOMETERS. WE DENOTE  $n_1:n_2:n_3 = \{n_1, n_1 + n_2, n_1 + 2n_2, \dots, n_3\}$ . CTC=10NM

|                   | TW      | BL       | PW50 <sub>x</sub> | PW50 <sub>y</sub> |

|-------------------|---------|----------|-------------------|-------------------|

| TDMR <sub>1</sub> | 10:1:20 | 7        | 20                | 14                |

| TDMR <sub>2</sub> | 10:1:20 | 5:0.5:10 | 20                | 10                |

regions, the values of the boundary variable nodes are given and treated as deterministic in the GBP algorithm. For this case, we compute an upper bound on the MIR of the Voronoi channel.

Figure 11. Lower and upper bounds on the MIR for the TDMR<sub>1</sub> system. Increased track width reduces media noise. Adapted from [6].

Figure 11 shows the empirically computed lower and upper bounds for the MIR estimation of the Voronoi channel with random  $20 \times 20$  and  $40 \times 40$  bit arrays generated according to the uniform distribution. The parameters of the TDMR<sub>1</sub> system simulated are given in Table I. It is worth noting that the upper bound converges much faster than the lower bound and both the bounds converge for larger array sizes. In other words, for a large array size, the boundary bits can be considered to be known.

#### IV. SIGNAL PROCESSING FOR RECORDING CHANNELS

The read channel is an interfacing circuit between the read head and the HDD controller. Encoded data from the computer or a network is converted to a bipolar current that passes through electromagnet coils and written as flux changes over the storage medium through the write head. Now, when a read head senses the signal from the disk, the readback signal comprising several artifacts due to timing offsets, ISI, thermal asperities, noise etc. must be processed before the data is decoded back.

Variations in the head-media spacing, variations in the magnetic, electrical and mechanical properties during the sensing process all contribute to gains and offsets in the readback signal, affecting the SNR from the read side. The readback signal is first compensated w.r.t gains and offsets via analog control loops. Also, when the read head hits dust particles on the medium, the readback signal appears to be in the shadow of

a low-frequency signal of higher energy. This is called *thermal asperity*, which can be detected and compensated (refer to Figure 4).

High-frequency noise is removed using a continuous-time (CT) filter, typically a Butterworth or an equiripple linear-phase filter so that the readback signal without aliasing of the high-frequency noise spectrum can be sampled and processed further. The CT filter has programmable cutoff frequencies. Also, to process servo information towards handling timing, the CT filter would have to be switched to allow low cutoff frequencies. All these aspects are part of the analog front end.

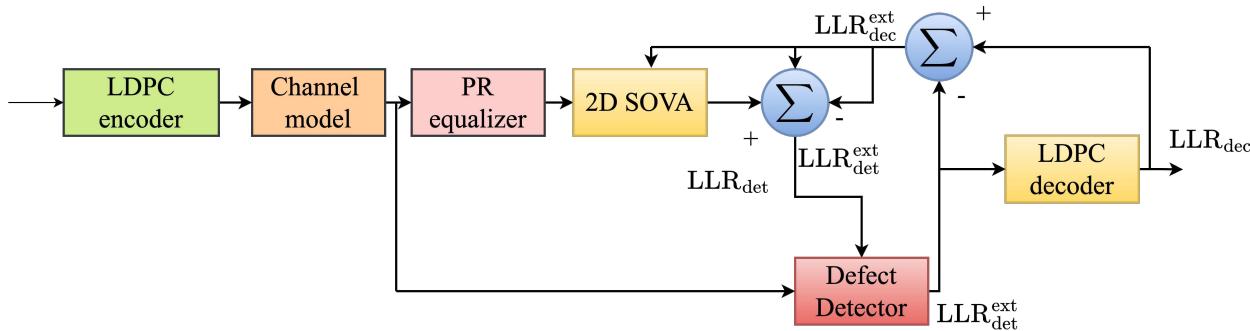

Post-sampling, the readback signal is passed through a timing recovery circuit. Post GPR equalization, the data is processed through a sequence detector. In modern read channels, the sequence detector and the error correction decoder are coupled via a turbo loop within the framework of iterative detection and decoding [78]. We shall now discuss all the details of the signal processing chain, covering both 1D and 2D techniques.

### A. Channel Equalization

Early version of HDDs used analog equalization. With the introduction of PRML channels, equalization is done digitally. The sampled readback signal is first equalized using a linear equalizer before the signal is detected using a maximum-likelihood (ML) detector. The linear equalizer reduces the extent of ISI and achieves a desired overall response called the partial response that controls both the complexity and performance of the ML sequence detector. Additional regularization constraints can be forced on the equalizer so that the pre-target is matched to the channel spectrum.

Figure 12. GPR equalization in 1D. The combined effects of the recording channel and the equalizer are equivalent to a PR channel.

PMR channels have used pre-targets [79] based on polynomials of the form  $(1 - D)^m(1 + D)^n$ . Since the parameters  $m$  and  $n$  influence the choice of the polynomial<sup>7</sup> in terms of performance as well as the complexity of the sequence detector, one could balance the extent of partial response ISI

<sup>7</sup>Historically,  $(1 + D)$  is referred to as PR1,  $(1 - D)(1 + D)$  is referred to as PR4,  $(1 - D)(1 + D)^2$  is referred to as EPR4 etc. in the data storage community.

and the overall system performance. One could also adapt the FIR equalizer and the target as shown in Figure 12.

### B. Timing Recovery for 1D channels

It is important to synchronize the discrete readback samples so that signal detection can be accomplished post PR equalization. The timing recovery module accomplishes this goal by providing the samples at the desired time instants. Timing errors in HDDs are due to accumulated phase errors, frequency errors and jitter. Timing jitters can be modeled as a discrete random process using random walks [80].

Timing recovery algorithms are of two classes: (a) PLL-based [81] and (b) interpolative timing recovery (ITR)-based [82] (Chapter 27 from [27]). We will first review both these techniques for the 1D case before getting to the shingled case and 2D.

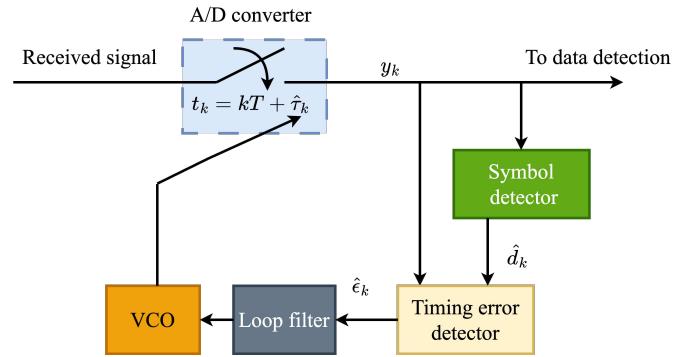

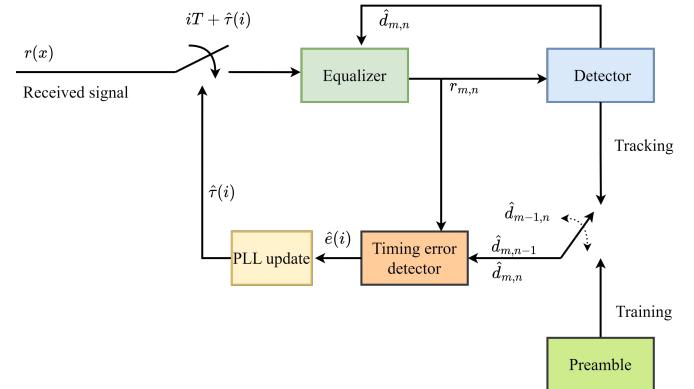

Figure 13. A conventional VCO-based timing recovery. This is part of the loop-Viterbi engine. The timing error estimates from the timing error detector (TED) are passed through the loop filter and a VCO to feed the timing estimates for resampling.

1) *PLL-based Timing Error Detector*: The noisy equalized sample  $y(k)$  is fed to a PLL unit having a phase detector, typically a second order loop filter and a voltage-controlled oscillator (VCO) as shown in Figure 13. The other signal inputs to the phase detector are the ideal/desired values  $\hat{y}(k)$  obtained by filtering known data  $d(k)$  through the PR target. The phase detector obtains the misalignment between the ideal samples and the actual samples from the sampler output. Using the Mueller and Muller estimate [83], the timing gradient is computed as

$$\hat{e}(k) = y(k)\hat{y}(k-1) - y(k-1)\hat{y}(k). \quad (38)$$

The estimated timing error  $\hat{e}(k)$  is now filtered through a second order loop filter with additional delays  $z^{-L}$  to handle any timing loop latencies. The sampling offsets are updated according to the following equations:

$$\hat{\theta}_k = \hat{\theta}_{k-1} + \beta \hat{e}_k, \quad (39)$$

$$\hat{\tau}_{k+1} = \hat{\tau}_k + \alpha \hat{e}_k + \hat{\theta}_k, \quad (40)$$

where  $\alpha$  and  $\beta$  are the PLL parameters for gain adjustment and for controlling the loop bandwidth and convergence rate,  $\hat{\theta}_k$  corresponds to the frequency error and  $\hat{\tau}_k$  is the adjusted

timing offset. The reader must note that a *preamble* is used for training the PLL in the acquisition mode.

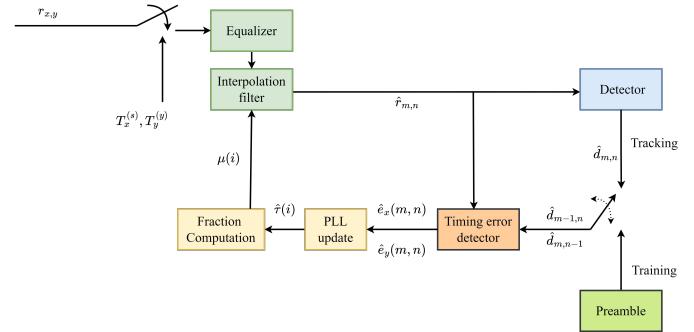

2) *Interpolative Timing Recovery*: The VCO unit of the PLL-based timing recovery can be made digital using the ITR scheme. In this method, received samples are resampled at a higher rate  $\sim 2-5\%$  of the baud rate and interpolated using a digital filter for obtaining the correct timing sample. The digital filter is obtained using the MMSE criterion that minimizes the MSE between ideal and the interpolated samples.

of equation (44) can be obtained using adaptive algorithms such as the LMS algorithm by estimating the coefficients of the adaptive filter when the channel conditions change. In practice, one could use simple interpolative methods, such as a linear interpolator at the cost of performance degradation. Since solving for optimal filters is not practical for high speed circuits, one can design a bank of such filters under quantized phase offsets and use an appropriate filter based on the timing phase estimation.

### C. Signal Detection for MR channels

Early versions of PRML channels used hard decision Viterbi detectors [84] [85]. With the advent of turbo codes [86] and turbo equalization [78], almost all HDDs use the soft-decision Viterbi algorithm (SOVA) [87] [88] for signal detection. Post equalization and timing, the Viterbi algorithm obtains the ML-optimal sequence  $\mathbf{b}$  of length  $N$  from the noisy version of the sequence  $\mathbf{y}$  by finding

The diagram illustrates the signal processing chain in a digital receiver. It starts with a **A/D converter** receiving a **Received signal**. The output of the A/D converter is fed into an **Interpolation filter**. The filter's output is  $y_k$ , which is then sent to a **Symbol detector** and a **Timing error detector**. The **Symbol detector** outputs the detected symbol  $\hat{d}_k$ . The **Timing error detector** outputs the timing error  $\hat{\epsilon}_k$ . The **Timing error detector** also provides feedback to a **Loop filter**. The **Loop filter** outputs the timing error  $\hat{\epsilon}_k$  to a **Digital accumulator**. The **Digital accumulator** outputs the accumulated value  $\hat{\tau}_k$  to an **Interpolator control unit**. The **Interpolator control unit** outputs the interpolation time  $t_k = (m_k + \mu_k)T_s$  to the **Interpolation filter**. The **Interpolation filter** also receives the **Received signal** and the interpolation time  $t_k$  to produce the output  $y_k$ . A **Fixed sampling frequency** is indicated by a feedback loop from the **Symbol detector** back to the **A/D converter**, with a sampling period of  $1/T_s$ .

Figure 14. The interpolative timing recovery unit comprises an interpolation filter which adjusts the timing instants in the oversampled domain based on the sampling phase offsets.

Figure 14 shows the ITR architecture. The sampling time instant  $t_k = kT + \hat{\tau}_k = (m_k + \mu_k)T_s$ . The integer  $m_k$  is a multiple of  $T_s$  and  $\mu_k$  is a fraction of the oversampled time period. With 5% oversampling, the oversampling rate  $f_s = \frac{1}{T_s}$  is typically related as  $E(T) = 1.05T_s$  since  $T$  is non-ideal and is a random variable due to clock jitters.

Without any timing error, binary sequence  $a_k \in \{-1, 1\}$  is filtered through the PR equalizer with PR target  $p(t)$  to yield the samples  $y(kT)$  given by

$$\hat{y}(kT) = \sum_{m=-\infty}^{\infty} a_m p(kT - mT). \quad (41)$$

Using the interpolating filter  $f_{\mu_k}$  for the phase  $\mu_k$  over a span  $n_1 + n_2 + 1$  samples, we have

$$y(kT) = \sum_{l=-n_2}^{n_1} f_{\mu_k}(l) y_{\text{ip}}((m_k - l)T_s), \quad (42)$$

where the interpolated signal  $y_{\text{ip}}(kT - \mu_k T_s - lT_s)$  is given by

$$y_{\text{ip}}(kT - \mu_k T_s - lT_s) = \sum_{i=-\infty}^{\infty} a_{ip} (kT - \mu_k T_s - lT_s - iT) + n(kT - \mu_k T_s - iT_s). \quad (43)$$

The optimal filter  $f_{\mu_k}$  for the sampling phase  $\mu_k$  is solved using

$$\mu_k^* = \min_{\mu_k} \mathbf{E} \left[ (\hat{y}(kT) - y(kT))^2 \right]. \quad (44)$$

The estimation of the initial sampling phase can be done using a preamble and this process is called the digital zero phase start. Further, the reader must note that the solution

Since the signal detection is over a PR target, using the memory of the equivalent ISI channel i.e., corresponding to the PR target, a trellis structure amenable to a desired level of the computational complexity can be chosen. If  $I$  is the memory of the channel ISI, we define the states  $S_k := b_{k-I}^{k-1}$  and  $S_{k-1} := b_{k-I+1}^k$  corresponding to the memory of the Markov process. Over the trellis stages, the conditional probability of the received sequence given the input bit sequence is given by

$$P(\mathbf{y}|\mathbf{b}) = \prod_{k=0}^{N-1} P(y_k|S_k, S_{k-1}). \quad (46)$$

The quantity  $P(y_k|S_k, S_{k-1}) = P(n_k)$  is the probability of the noise sample at time instant  $k$ . Assuming that the noise statistics are Gaussian  $\mathcal{N}(0, \sigma^2)$ , given the received value  $y_k$  and the ideal value  $o_k$ , one could easily compute  $n_k = y_k - o_k$  by plugging it in equation (46). For numerical stability, the computations can be done in the logarithmic domain.

$$\log P(\mathbf{y}|\mathbf{b}) \propto - \sum_{k=0}^{N-1} (y_k - o_k)^2. \quad (47)$$

The state metric  $\text{SM}_k^{(i)}$  for a trellis state  $i$  at time  $k$  is related by the recursion

$$\text{SM}_k^{(i)} = \text{SM}_{k-1}^{(i)} + \text{BM}_k, \quad (48)$$

where  $BM$  is the least among the branch metrics that connects state  $i$  at time  $k$  from any other state  $j$  at time  $k - 1$ . This is commonly referred to as the add-compare-select (ACS) logic. By doing the recursion over the entire length of the trellis after picking up the state metric that is the least among all the states, one could back trace the path, reading the labels of the bits in the reverse order corresponding to the path with the least state metric at time  $N$ . This is the essence of the Viterbi sequence detection.

The SOVA provides soft information by computing the probability of a wrong/complementary decision through the

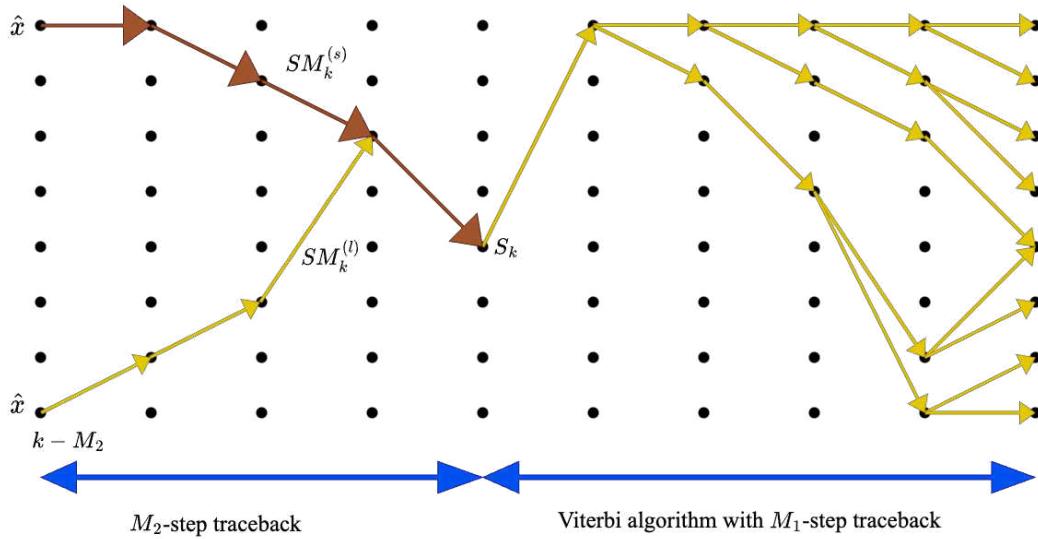

Figure 15. Using a  $M_1$  step traceback, through the Viterbi algorithm ML path is determined. Using a  $M_2$  step traceback, the second best path is found using the SOVA.

survivor paths on the trellis. Specifically, at any time instant  $k$ , following a  $M_1$ -step traceback from the hard decision Viterbi algorithm, the state metric of the survivor is obtained as  $SM_k^{(s)}$ . Now, with a  $M_2$ -step traceback further from the time instant  $k$ , the loser path or the second best ML path yielding a complementary decision has a state metric  $SM_k^{(l)} < SM_k^{(s)}$ .

From the SOVA algorithm, the probability of choosing the second best path over the ML path is  $P_{\text{err}} = \frac{1}{1+e^{\Delta_k}}$ , where  $\Delta_k = SM_k^{(s)} - SM_k^{(l)}$ , corresponding to the log-likelihood ratio or odds for the survivor decision to be correct. The soft decisions that SOVA allows helps in the turbo-equalization process while dealing with an iterative ECC decoder. At this stage, we note that one could obtain the MAP decisions for signal detection based on the elegant BCJR algorithm [61]. However, latencies on the order of the sequence length and area/power complexities limit use of the BCJR in hardware. For the aforementioned reasons, though the SOVA is sub-optimal in performance, it is the state-of-the-art algorithm [89] implemented in read channel ICs. Recently, the authors in [90] have proposed an asynchronous version of the SOVA with an eye towards low-power design.

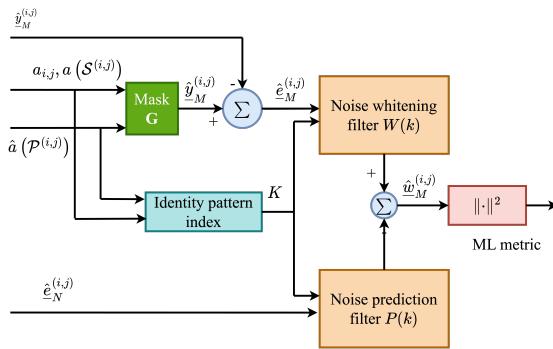

Figure 16. Post equalization and timing, noisy samples obtained as a difference from the ideal samples and the equalized samples are whitened using the NPML/DDNP. The noise statistics extracted is fed to the soft-decision detector within a turbo detector/decoder setup.

To further improve channel reliabilities, subsequent versions of soft-decision-based signal detectors used NPML detection [13]. Figure 16 shows the noise path after adaptive equalization

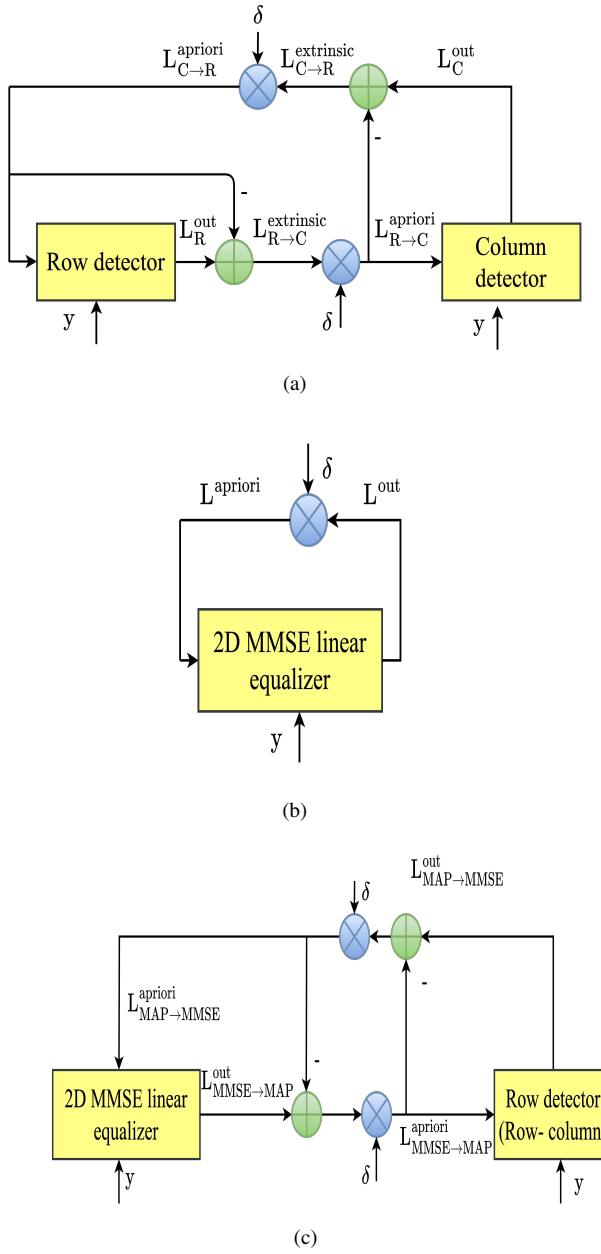

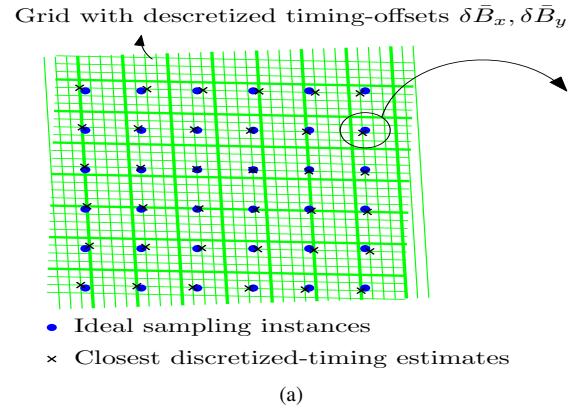

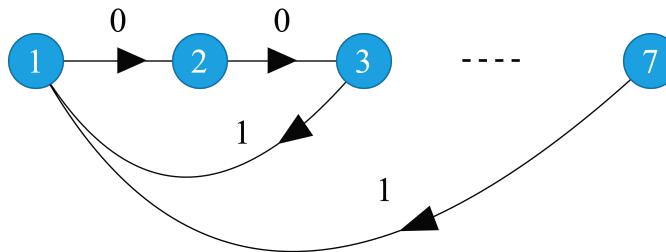

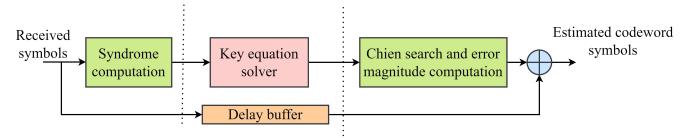

and timing recovery. Colored noise must be whitened and the noise statistics are fed to the detector for branch metric computation. With experimental evidence into pattern-dependent noise arising due to magnetic transitions, the DDNP-detection algorithm was conceived [63]. This is now the standard algorithm residing in HDDs that we shall describe as follows: