# A Generic, High-Performance, Compression-Aware Framework for Data Parallel DNN Training

Hao Wu, Shiyi Wang, Youhui Bai, *Member, IEEE*, Cheng Li, *Member, IEEE*, Quan Zhou, Jun Yi, Feng Yan, *Member, IEEE*, Ruichuan Chen, Yinlong Xu, *Member, IEEE*,

#### Abstract—

Gradient compression is a promising approach to alleviating the communication bottleneck in data parallel deep neural network (DNN) training by significantly reducing the data volume of gradients for synchronization. While gradient compression is being actively adopted by the industry (e.g., Facebook and AWS), our study reveals that there are two critical but often overlooked challenges: 1) inefficient coordination between compression and communication during gradient synchronization incurs substantial overheads, and 2) developing, optimizing, and integrating gradient compression algorithms into DNN systems imposes heavy burdens on DNN practitioners, and adhoc compression implementations often yield surprisingly poor system performance. In this paper, we propose a compression-aware gradient synchronization architecture, CaSync, which relies on flexible composition of basic computing and communication primitives. It is general and compatible with any gradient compression algorithms and gradient synchronization strategies and enables high-performance computation-communication pipelining. We further introduce a gradient compression toolkit, CompLL, to enable efficient development and automated integration of on-GPU compression algorithms into DNN systems with little programming burden. Lastly, we build a compression-aware DNN training framework HiPress with CaSync and CompLL. HiPress is open-sourced and runs on mainstream DNN systems such as MXNet, TensorFlow, and PyTorch. Evaluation via a 16-node cluster with 128 NVIDIA V100 GPUs and a 100Gbps network shows that HiPress improves the training speed over current compression-enabled systems (e.g., BytePS-onebit, Ring-DGC and PyTorch-PowerSGD) by 9.8%-69.5% across six popular DNN models.

| <b>Index Terms</b> —Data parallel DNI | N training, gradient compression |          |

|---------------------------------------|----------------------------------|----------|

| _                                     |                                  | <b>.</b> |

# 1 Introduction

To efficiently train large DNN models over the continuously growing datasets, it has been a norm to employ data parallel DNN training to explore massive parallelism in an increasingly large cluster of GPU nodes [20], [55], [57], [78], [102]. In a typical data parallel setting, each node iterates over its data partition in parallel, and exchanges a large volume of gradients with other nodes per iteration via a gradient synchronization strategy like Parameter Server (PS) [33], [38] or Ring-allreduce [9].

However, in recent years, the fast-growing computing capability, driven by the booming of GPU architecture innovations [60] and domain-specific compiler techniques [16],

- Hao Wu, Shiyi Wang, Youhui Bai (corresponding author), Cheng Li (corresponding author), Quan Zhou and Yinlong Xu are with the Department of Computer Science and Technology, University of Science and Technology of China, Hefei, China. Cheng Li and Yinlong Xu are also with the Anhui Province Key Laboratory of High Performance Computing, and Institute of Artificial Intelligence, Hefei Comprehensive National Science Center.

- E-mail: {mark14, wsy0111, byh0912, zzqq2199}@mail.ustc.edu.cn, {chengli7, ylxu}@ustc.edu.cn

- Feng Yan is with the Computer Science Department and Electrical and Computer Engineering Department of University of Houston.

E-mail: fyan5@central.uh.edu

- Ruichuan Chen is a Distinguished Member of Technical Staff at Nokia Bell Labs.

E-mail: ruichuan.chen@nokia-bell-labs.com

Manuscript received April 19, 2005; revised August 26, 2015.

[19], [70], [72], tends to result in more frequent and heavier gradient synchronization during data parallel DNN training. This trend puts high pressure on the slower-growing bandwidth and reduces the chance of pipelining computation and communication during training. We have found that, even with the latest highly-optimized BytePS [33] and Ring-allreduce [78] synchronization strategies, the communication time for gradient synchronization still accounts for 63.6% and 76.8% of the total time for training the Bert-large and Transformer models across 16 AWS EC2 instances, each with 8 NVIDIA V100 GPUs, in a 100Gbps network. Thus, there is a fundamental tension between gradient communication and computation in data parallel DNN training [75].

Gradient compression algorithms have a great potential to relieve or even eliminate the above tension, since they can substantially reduce the data volume being synchronized with a negligible impact on training accuracy and convergence [5], [44], [84], [94], [96]. This practice of gradient compression is being adopted by the industry. In fact, the efforts from Facebook and AWS to bring gradient compression to mainstream DNN systems have begun since June 2020 [6], [51], [53]. However, our experiment shows that the actual training speedups of compression-enabled DNN systems are far behind their expectations. For instance, applying gradient compression to the aforementioned Transformer training achieves only a 1.3× speedup, 38.1% lower than the expected performance. The gap becomes even larger in a lower-bandwidth network. This surprising observation

drives us to rethink gradient compression from the system perspective.

To fully unleash the benefits of gradient compression, only an efficient compression algorithm is not sufficient. The compressed gradients are not directly aggregatable, and they are not compatible with common optimizations (such as gradient partitioning and batching) used in the conventional gradient synchronization strategies. In the current compression-enabled DNN system designs, the computational overhead introduced by gradient compression is often overlooked and could be greatly amplified along the gradient synchronization path. Therefore, the first challenge we have to address is how to amortize the extra computational overhead along the communication steps during gradient synchronization, whereby the computation and communication may have data dependencies. This requires us to revisit the original design choices across existing gradient synchronization strategies to identify the right granularity of combining and coordinating various gradient compression and communication operators. Second, a sophisticated systematic support for compression awareness is generally lacking. Without such a support, DNN practitioners cannot live up to the full promise of gradient compression to accelerate DNN training. The adoption of gradient compression also becomes difficult because substantial system expertise and manual efforts are required for developing, optimizing, and integrating individual compression algorithm into DNN systems.

In this paper, we address these systems challenges to bridge the gap between gradient compression and synchronization in data parallel DNN training. We first propose a general, composable gradient synchronization architecture, called CaSync, which enables a compression-aware gradient synchronization with a composition of decoupled communication, aggregation, and compression primitives. This fine-grained composition allows us to strike a balance between 1) the effective pipelining of computational and communication tasks to hide communication overhead behind compression-related computation and vice versa, and 2) the efficient bulky execution of smaller tasks. Furthermore, CaSync employs a selective compression and partitioning mechanism to decide whether to compress each gradient and how to partition large gradients (before compression) to optimally leverage pipelining and parallel processing. It is worth mentioning that our CaSync architecture is intentionally designed to be general and not tie to specific gradient compression algorithms and synchronization strategies (e.g., PS or Ring-allreduce) so that its benefits are applicable to existing and potentially future compression algorithms and synchronization strategies.

Second, we advocate that the on-GPU compression is the preferred approach for gradient compression considering GPU has much higher bandwidth and processor density than CPU, and gradients are produced in GPU directly. This creates new opportunities to further optimize the compression-communication pipeline during gradient synchronization. However, developing and optimizing gradient compression algorithms on GPU is non-trivial and usually requires significant system expertise and manual efforts. To relieve the burden on DNN practitioners, we design and develop a gradient compression toolkit named CompLL,

which facilitates the compression algorithm development and its integration on GPU. Complia provides a unified API abstraction and exposes a library of highly-optimized common operators that can be used to construct sophisticated gradient compression algorithms. Complia also offers a domain specific language to allow practitioners to specify their algorithm logic, which is then converted into efficient low-level GPU implementation and automatically integrated into DNN systems with little human intervention.

For easy adoption, we build a compression-aware data parallel DNN training framework called <code>HiPress</code>, with both <code>CaSync</code> and <code>CompLL</code>. <code>HiPress</code> is compatible with mainstream DNN systems (i.e., MXNet, TensorFlow, and PyTorch), and we have open-sourced it at [2].

We evaluate HiPress extensively. First, we use CompLL in HiPress to construct six state-of-the-art compression algorithms (i.e., onebit [76], TBQ [84], TernGrad [94], DGC [44], GradDrop [5] and PowerSGD [87]) with only 22 lines of Compli code on average, and they achieve significant performance speedups over open-source counterparts. We train six widely-used DNN models across the computer vision and natural language processing fields using a 16-node cluster on AWS EC2 with 128 NVIDIA V100 GPUs and 100Gbps network links. Experimental results show that HiPress achieves speed improvements of 17.3%-110.5% and 9.8%-69.5% compared with noncompression systems (including the latest BytePS) and current compression-enabled systems (e.g., BytePS-onebit, Ring-DGC and PyTorch-PowerSGD), respectively. The results in a lower-end 16-node cluster with 32 1080Ti GPUs and 56Gbps network show a similar trend. Lastly, HiPress does not sacrifice the convergence and accuracy claims of exercised algorithms.

## 2 Background and Motivation

## 2.1 Data Parallel DNN Training

A DNN model typically consists of multiple neural network layers, each of which contains a large number of parameters. Training a DNN model needs to iterate over a dataset many times (i.e., epochs) towards convergence [97]. Each epoch is further split into *iterations*. Data parallel DNN training enables each training node to consume data from its own partition of the training dataset. In each iteration, training nodes independently run forward and backward propagation to generate gradients, which are then synchronized with other nodes to update the global model parameters collectively. This group coordination can be done synchronously or asynchronously. The former case often acts as a distributed barrier for convergence guarantees [106], while the latter case eliminates the negative impact of stragglers at the cost of possibly not converging. We focus on synchronous coordination because of its wide adoption [1], [15], [35], [69].

## 2.2 Gradient Synchronization

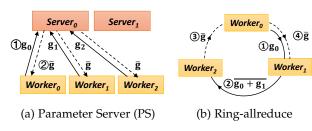

Parameter Server (PS) [38], [68] and AllReduce [9], [78] are two widely-adopted gradient synchronization strategies. **Parameter Server.** In Figure 1a, each node acts as a *server* or a *worker* [38]. Model parameters and gradients are often partitioned across multiple servers for load balancing. When

Fig. 1: Gradient synchronization strategies. For Parameter Server (PS), we only show interactions between  $Server_0$  and workers for clarity.

local training completes, each worker pushes gradients to servers (1), which are then aggregated and updated to model parameters. Afterward, each worker pulls the updated results from servers to trigger the next iteration (2). AllReduce. This strategy uses collective communication primitives. One representative example is Ringallreduce [9], where all nodes are workers and form a logical ring. In Figure 1b, it takes N-1 communication steps along the ring to aggregate gradients ((1-2)) and another N-1steps to disseminate the updated gradient ((3-4)), where Nis the number of workers. Furthermore, Ring-allreduce can batch gradients which are then partitioned again for load balancing. Following this, at each synchronization step, each worker simultaneously sends a partition to its successor and receives another partition from its predecessor to best utilize its bi-directional network bandwidth [67].

## 2.3 Computation and Communication Tension

Modern DNN systems pipeline computation and communication for better performance, e.g., via running the gradient communication and DNN backward computation of two DNN layers in parallel to hide the former overhead behind the latter when possible. However, there exists a fundamental tension between computation and communication [75].

The recent DNN accelerator booming [60] and domain-specific compiler advancement [16], [19], [70], [72] have significantly improved the single-node training speed. Such fast-advancing computing capabilities typically lead to more frequent gradient synchronization and thus put high pressure on the network infrastructure. However, the network upgrade does not keep up the pace of the computation-related advancements [46], [48], [64], [95]. The imbalance between the fast-advancing computing capability and the slower-advancing communication capability increasingly reduces the chance of pipelining the gradient communication and computation.

A few software approaches have been recently proposed to optimize the computation-communication pipeline, ranging from priority-based gradient scheduling and partitioning [69] to advanced synchronization architectures [33], [78]. However, as shown in Table 1, the latest highly-optimized BytePS [33] and Ring-allreduce [78] only achieve scaling efficiencies<sup>1</sup> of 0.71 and 0.47, when training two popular DNN models (Bert-large and Transformer) in a cluster of

TABLE 1: Training performance of Bert-large and Transformer with 16 AWS p3dn.24xlarge instances (8 V100 GPUs each), 100Gbps, BytePS 0.2.5, Horovod 0.19.2, fp32 precision.

|        | System configurations                | Scaling<br>efficiency | Communication ratio |  |

|--------|--------------------------------------|-----------------------|---------------------|--|

| Trans- | Ring-allreduce<br>w/o compression    | 0.47                  | 76.8%               |  |

| formor | Ring-allreduce w/<br>DGC compression | 0.61 (29.8%†)         | 70.3% (8.5%↓)       |  |

| Bert-  | BytePS<br>w/o compression            | 0.71                  | 63.6%               |  |

| large  | BytePS w / onebit compression        | 0.76 (7.0%†)          | 60.9% (4.2%↓)       |  |

16 nodes on AWS EC2 with 128 NVIDIA V100 GPUs and a 100Gbps network. The communication time accounts for up to 76.8% of the total training time for training these two models, with a significant portion not being hidden behind DNN computation. This highlights the fundamental tension between gradient computation and communication persists in data parallel DNN training, even with state-of-the-art approaches and recent bandwidth advancements.

# 2.4 Gradient Compression

Gradient compression is a general approach for reducing the transmitted data volume during gradient synchronization [44], [87], [94], and has a great potential to alleviate the aforementioned communication bottleneck. Indeed, it is being adopted by the industry, and a number of recent efforts from Facebook and AWS have started to integrate gradient compression into modern DNN systems since June 2020 [6], [51], [53].

The gradient compression algorithms generally fall within the *sparsification*, *quantization* and *low-rank* categories. Sparsification leverages the sparsity of gradients and filters out insignificant elements in the gradient matrix [5], [35], [44], and quantization decreases the precision of gradients [84], [94], [96]. For instance, a 1-bit quantization enabled by onebit algorithm [76] could reduce the transmitted data volume by 96.9%. Unlike them, the low-rank methods decompose the original gradient matrix into multiple smaller matrices [18], [87], [89], [103]. For example, PowerSGD [87] aims to approximate the gradient with size NxM by multiplying two matrices with size NxRand RxM respectively. Obviously, the compression ratio of PowerSGD is  $\frac{(N+M)\times R}{N\times M}$ . Many of these algorithms either theoretically prove or empirically validate that adopting them does not affect model convergence and imposes only a negligible impact on accuracy, i.e., a compression-enabled DNN training converges to approximately the same accuracy through the same number of iterations compared with a non-compression training [44], [84], [94].

## 2.5 System Challenges and Opportunities

Surprisingly, our study reveals that, without proper system support, the gradient compression's benefits are diluted significantly at the best, and could even negatively affect the overall DNN training throughput at the worst.

One important reason for this surprising observation is that gradient compression requires non-negligible com-

<sup>1.</sup> Scaling efficiency is defined as  $\frac{\text{actual\_performance}}{N \times \text{single\_GPU\_performance}}$ , where N is the total number of GPUs, with 1 being the best (i.e., linear scaling).

putational overhead. Alongside the gradient synchronization path, an <code>encode</code> operator must precede sending fully or partially aggregated gradients, and a <code>decode</code> operator must follow when receiving compressed gradients. There could be up to 3N-2 extra operators for each gradient synchronized across N workers. These extra operators are needed because it is impossible to directly aggregate over compressed gradients for most of the sparsification and quantization algorithms, due to the existence of metadata (in sparsification-based algorithms) or the potential overflow of operating low-precision numbers (in quantization-based algorithms).

The accumulated compression-related computational cost during gradient synchronization can significantly dilute its benefits of reducing the transmitted data volume. To demonstrate this, we train Bert-large with the onebit compression [76] developed by AWS and integrated into MXNet with BytePS.<sup>2</sup> Table 1 shows that BytePS-onebit achieves a very limited improvement over BytePS. As another example, the DGC compression [44] with 0.1% compression rate (where it is integrated into TensorFlow with the Ringallreduce synchronization strategy) achieves only a 1.3× training speedup for the Transformer model. We discover that such limited improvements are mainly due to the codesign of BytePS and Ring-allreduce with the compression algorithms, whereby the compression logic is separated and scattered across gradient synchronization. Such a codesign also makes it difficult to verify the correctness of the implemented algorithms as well as to generalize to other gradient compression algorithms and synchronization strategies. To enable a general approach, it is important to separate the design of compression algorithms from that of synchronization strategies.

The first challenge to address the aforementioned issues lies in designing a general approach to amortize the extra computational overhead brought by gradient compression (e.g., encode and decode operators) along the communication steps during gradient synchronization. This is difficult due to non-trivial factors including, for instance, the data dependencies between gradient computation and communication, the communication topology such as a bipartite graph for PS and a ring for Ring-allreduce, the compression speed and ratio of different compression algorithms, to name a few. To address this challenge, the key is to identify the right granularity of combining and coordinating various gradient compression and communication operators.

Take Ring-allreduce as an example. It coordinates the communication of all training nodes by running a global, atomic, bulk synchronization operation to complete 2(N-1) point-to-point communication steps for batched gradients. While this design is bandwidth-optimal [67], such a *coarse-grained* approach fails to hide the compression-related overhead behind the communication overhead. Unlike Ring-allreduce, the PS synchronization strategy (including the latest BytePS) exchanges gradients via micro point-to-point communication steps. While such a *fine-grained* approach facilitates a better computation-communication pipelining

to hide compression-related computational overhead, it incurs a larger number of communication steps and in turn a proportionally growing extra computational overhead.

The second challenge is to provide systematic support for developing, optimizing, and integrating gradient compression algorithms into DNN systems. Without this support, the real-world adoption of gradient compression algorithms requires significant system expertise and manual efforts to perform various ad-hoc development and optimization, which is particularly challenging for DNN practitioners. Thus it is quite difficult, if not impossible, for gradient compression to live up to its full promise of accelerating DNN training.

To provide general system support for various algorithms, one critical question to answer is where to perform their computation, e.g., on CPU or GPU? We observe that compression algorithms typically need to scan large gradient matrices multiple times to filter out insignificant gradients, decrease the precision of gradients, or decompose them into multiple sub-matrices with reduced sizes. Therefore, they are extremely memory-intensive and require massive parallelism to achieve fast compression (and decompression). We believe the on-GPU gradient compression is the preferred approach considering GPU's high memory bandwidth and many-core architecture. Furthermore, given that gradients produced by DNN computations are inherently in the GPU memory, the on-GPU compression can greatly alleviate the bandwidth tension of the PCIe bus between GPU and host. As an example, for the onebit compression algorithm [76], its CPU implementation runs 35.6× slower than the GPU-oriented counterpart (our implementation); using the same experimental setup as Table 1, BytePS with the on-CPU onebit introduces 95.2% training overhead than its on-GPU counterpart. Despite of on-GPU advantages, developing, optimizing and integrating on-GPU compression algorithms puts heavy burden on DNN practitioners, and doing it well requires extensive system expertise and the understanding of lower-level GPU hardware and CUDA programming details.

In summary, the above two challenges motivate us to rethink the abstraction for both gradient compression algorithms and compression-aware synchronization strategies, as well as to identify the common design patterns to support easy development, optimization, and integration of compression algorithms in DNN systems for real-world use.

## 3 COMPRESSION-AWARE SYNCHRONIZATION

We propose CaSync, a compression-aware gradient synchronization architecture that provides a *general* support for gradient compression algorithms and synchronization strategies.

#### 3.1 Composable, Pipelined Synchronization

As motivated in Section 2.5, a proper granularity of abstraction for gradient compression algorithms and synchronization strategies is the key to achieve a general yet high-performance gradient synchronization. To identify the right granularity, we employ a composable approach which first decouples all gradient synchronization primitives in a fine-grained manner, and then combines and coordinates them

<sup>2.</sup> The open-source onebit was implemented only on CPU [13]. For a fair comparison, we have implemented and integrated a highly-optimized on-GPU onebit into BytePS.

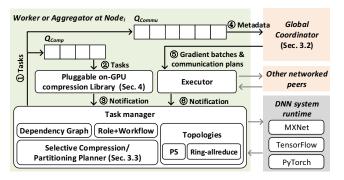

Fig. 2: The CaSync architecture design, where the DNN system runtime is omitted.

according to their data dependencies and order constraints to build an efficient computation-communication pipeline.

We first decouple the communication topology from gradient synchronization strategies. We represent the topology as a directed graph, where the vertex set contains training nodes and the edge set specifies the connections between these nodes. In gradient synchronization, there are fundamentally two node roles, namely, worker and aggregator (with potentially other roles serving for optimizations only). A worker produces gradients from its local DNN computation and initiates the gradient synchronization process. An aggregator aggregates gradients and then relays the aggregate result to workers or other aggregators. Take PS and Ring-allreduce as two examples of gradient synchronization strategies. As shown in Figure 1, for PS, we build bipartite connections between servers (i.e., aggregators) and workers; for Ring-allreduce, each node serves both roles and the clockwise connections are built between these nodes.

We then split the gradient synchronization process into five general primitives, namely, <code>encode</code>, <code>decode</code>, <code>merge</code>, <code>send</code> and <code>recv</code>. Specifically, '<code>encode</code>' and '<code>decode</code>' are two computing primitives for compressing and decompressing gradients, respectively. '<code>merge</code>' is another computing primitive for aggregating multiple gradients into one. '<code>send</code>' and '<code>recv</code>' are two communication primitives for sending and receiving gradients to and from other nodes, respectively. With these general primitives, we can conveniently specify a compression-aware workflow at each worker and aggregator, which defines proper data dependencies or order constraints between these primitives. For instance, '<code>encode</code>' precedes '<code>send</code>' at the worker because of the data dependency that the worker has to compress a gradient before sending it.

Figure 2 shows an overview of the Casync design. With the aforementioned abstraction, we are able to design a holistic gradient synchronization architecture for both workers and aggregators. Each worker or aggregator employs a *task manager* to schedule and execute computing and communication tasks. Specifically, according to the node role, the task manager consults the specified workflow to select which series of computing and communication primitives to execute during gradient synchronization. Afterwards, according to the communication topology (e.g., a PS bipartite graph or a ring), the task manager informs the communication primitives where to send and receive

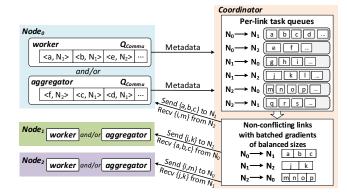

Fig. 3: The workflow of the compression-aware, coordinated bulk synchronization.

compressed gradients.

The above fine-grained abstraction creates opportunities to pipeline computing and communication tasks for improved performance. As shown in Figure 2, at Step 1, the task manager pushes tasks into two task queues:  $Q_{comp}$  for computing tasks, and  $Q_{commu}$  for communication tasks. Tasks in  $Q_{comp}$  and  $Q_{commu}$  are executed in an asynchronous manner for efficient use of computing and networking resources. However, as tasks are spread in two independent task queues and are executed asynchronously, there is a high risk that the data dependencies between tasks are violated. Therefore, one challenge here is how to preserve data dependencies and order constraints when executing tasks from  $Q_{comp}$  and  $Q_{commu}$  asynchronously.

To ensure the proper order, the task manager maintains a dependency graph to manage data dependencies between tasks at runtime. For instance, for a compressed gradient, its 'recv' task must first write to a memory buffer and only then it can be read by the 'decode' task. Upon the completion of a computing task from  $Q_{comp}$  (step ②), it notifies the task manager to clear the following tasks' pending dependencies, and then promotes the execution of any task if all its pending dependencies are cleared (step ③). In doing so, the asynchronous execution of gradient synchronization is driven by the dependency graph among tasks. Note that, the step  $\text{$\textcircled{\$}$-$\textcircled{\$}}$  correspond to a coordinated, compressionaware bulk synchronization mechanism in the next section.

## 3.2 Compression-aware Bulk Synchronization

While the above composable, pipelined synchronization can already improve the training performance significantly, it does not explore the opportunities brought by bulk synchronization — an important feature that is supported by most modern DNN systems. Instead of computing and communicating each gradient at a time, bulk synchronization handles gradients in a batched manner to better take advantage of parallelism and reduce the execution overhead [78]. Here, we extend the conventional bulk synchronization to be compression-aware, and additionally introduce batch compression to compress gradients in a batched manner. Our main goal is to reduce the compression and communication overheads. Compression-aware bulk synchronization is particularly important for small gradients as their compression

and communication overheads are difficult to be compensated by the size reduction brought by compression.

The batch compression in CaSync batches a sequence of compression-related tasks from  $Q_{comp}$  and schedules them together to GPU for compression. This allows a single callback function for a batch of gradients and thus also reduces the CPU-GPU coordination overhead. This is feasible as modern DNN systems often employ the operation fusing technique to produce multiple gradients at once [7].

The bulk communication in CaSync parallelizes the network transmission across training nodes to amortize the communication overheads across gradients. However, deciding the appropriate bulk granularity for communication is challenging. As discussed in Section 2.5, there are pros and cons for both fine-grained and coarse-grained granularity, and a proper balance needs to be struck. Our high-level design is that we slice the gradient synchronization process into monotonically increasing time slots, and select a group of network-idle nodes to join each time slot. In a slot, to avoid bandwidth contention, each selected node sends its gradients to only one other node via its uplink and receives gradients from its downlink. Note that, the transmitted gradients in a time slot may correspond to different communication steps (see Figure 1) in the gradient synchronization process. Together, the goal of this design is to enable the adaptive granularity of communication and the optimized node coordination during gradient synchronization.

Specifically, we introduce a global coordinator to adapt the communication of all gradients indiscriminately (compressed or not) and determine an optimal, coordinated communication plan. The plan should fulfill two goals: 1) maximize the utilization of network bandwidth between pairs of nodes, and 2) balance the size of transmitted gradients. The design of the global coordinator is shown in Figure 3. Each node (e.g.,  $Node_0$  or  $N_0$ ) can serve as a worker or an aggregator or both, and it periodically sends the metadata (gradient\_name, gradient\_size, destination\_node) of the tasks in its communication task queue  $Q_{commu}$  to the global *coordinator*, e.g., 'gradients a, b, c, and d to node  $N_1$ ' and 'gradients e and f to node  $N_2$ ' (gradient sizes omitted for clarity). Upon arrival, the coordinator places these tasks into their respective per-link task queues. Afterward, the coordinator looks up these queues and selects a set of non-conflicting links between nodes (e.g., 3 of 6 links are selected). The coordinator then batches the gradients that need to be transmitted over each selected link with balanced batch sizes, amortizing the communication overhead across gradients. The size of each batch is decided based on a specified timeout or a size threshold, whichever is met first.

Finally, the coordinator broadcasts the information of these gradient batches and coordinated communication plans to the relevant nodes (step ⑤ in Figure 2), so that the executor on each node can execute these plans in a coordinated manner and notify its task manager to clear the dependencies of the tasks in each batch accordingly (step ⑥). Altogether, our compression-aware, coordinated bulk synchronization enables both efficient batch compression on GPU and efficient communication of small gradients.

TABLE 2: Notation in selective compression and partitioning.

| Notation       | Interpretation                                  |

|----------------|-------------------------------------------------|

| $\overline{m}$ | Gradient size in bytes                          |

| K              | Number of gradient partitions                   |

| N              | Number of workers or aggregators                |

| r              | Compression rate                                |

| $T_{enc}(m)$   | Time for compressing an <i>m</i> -byte gradient |

| $T_{dec}(m)$   | Time for decompressing an $m$ -byte gradi-      |

|                | ent                                             |

| $T_{send}(m)$  | Time for transmitting an $m$ -byte gradient     |

TABLE 3: Synchronization parameters and their values.

|             | Algorithm        | $\alpha$ | β   | $\gamma$ |

|-------------|------------------|----------|-----|----------|

| CaSync-Ring | Spars.<br>Quant. | 2(N-1)   | N   | N        |

|             | Low-rank         | 2(11 1)  | 1   | 1        |

| CaSync-PS   | Spars.<br>Quant. | 2N       | K+1 | N+1      |

|             | Low-rank         |          | 1   | 1        |

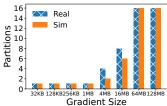

# 3.3 Selective Compression and Partitioning

Reducing data volume being transmitted does not always offset the compression-related overhead even with optimized synchronization strategies. It is more complicated when large gradients require partitioning to leverage parallelism before compression. Therefore, we design a *selective compression and partitioning* mechanism with a cost model to analyze the time cost of synchronizing gradients with and without compression, and then make a selective decision to avoid over-compression penalties and further leverage parallelism and load balancing. The cost model is simple yet unified, and is applicable to different CaSync synchronization strategies.

There are a few parameters used in the cost analysis as defined in Table 2. Here, the compression rate r, as well as the compression cost  $T_{enc}(m)$  and decompression cost  $T_{dec}(m)$ , are specific to compression algorithms and can be easily profiled. Moreover,  $T_{send}(m)$  denotes the network transmission time for an m-byte gradient. We omit merge operators as they are compression-irrelevant.

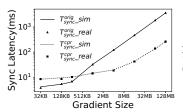

We first analyze the original time to synchronize an m-byte gradient with K partitions but without compression, denoted as  $T_{sync}^{orig}(m,K)$ . Here, we use PS and Ringallreduce designed within CaSync as examples, denoted as CaSync-PS and CaSync-Ring. For simplicity, let N be the number of their respective workers or aggregators. We assume the common practice used in real world where all nodes are homogeneous [68], [69]. Also, the number of gradient partitions, K, is between 1 and N for both strategies, with a discussion of larger K values later. We calculate  $T_{sync}^{orig}(m,K)$  as follows:

$$T_{sync}^{orig}(m,K) = \alpha \times T_{send}(\frac{m}{K}).$$

(1)

Here,  $\alpha$  denotes the total number of serial communication steps for synchronizing a gradient, and its value depends on the given synchronization strategy. As shown in Table 3, the  $\alpha$  value of CaSync-Ring is 2(N-1), since it takes N-1 steps for gradient aggregation and another N-1 steps to disseminate the updated gradient (see Figure 1b), and all K

gradient partitions are synchronized in parallel. Similarly, the  $\alpha$  value of CaSync-PS is 2N, where the communication of gradient partitions is well coordinated so that no network links used are conflicting, i.e., all aggregators run in parallel and each takes N steps to receive gradient partitions from N workers and another N steps to return results (see Figure 1a).

Next, we calculate the time,  $T_{sync}^{cpr}(m,K)$ , to synchronize an m-byte gradient with K partitions and compression:

$$T_{sync}^{cpr}(m,K) = \alpha \times T_{send}(r \times \frac{m}{K}) + \beta \times T_{enc}(\frac{m}{K}) + \gamma \times T_{dec}(r \times \frac{m}{K}). \tag{2}$$

Here, the  $\alpha$  value remains the same, but the communication cost is reduced to  $T_{send}(r \times \frac{m}{K})$  because one needs to send only the compressed gradient partition of the reduced size  $r \times \frac{m}{K}$ . This, however, comes with an extra compressionrelated computational cost. We denote the number of encode and decode operators that do not overlap with gradient transmission as  $\beta$  and  $\gamma$ , whose values are described in Table 3. When using CaSync-Ring to globally synchronize quantized and sparsified gradients, its first aggregation phase requires N-1 encode and N-1 decode operators, and they are non-overlapping because a node can compress a gradient partition only after it has decompressed and aggregated the partition received from its predecessor (i.e., data dependencies). Its second dissemination phase requires only one encode and N-1 decode operators. However, all decode operators except the last one can overlap with gradient transmission. Therefore,  $\beta = (N-1)+1=N$  and also  $\gamma = (N - 1) + 1 = N$ .

However, the application of CaSync-Ring to gradients compressed by low-rank methods behaves differently and leads  $\beta$  and  $\gamma$  to be 1. This is due to the unique characteristics of this kind of gradient compression algorithm; compressed gradients can be directly aggregated along the synchronization path, and thus only one encode operator and one decode operator are needed to compress the target gradient at the first step and decompress the aggregated compressed sub-matrices at the final step, respectively. We omit the analysis for CaSync-PS due to space limit. Note that, our cost model can be relaxed to split a gradient into beyond N partitions to leverage the compression-communication pipeline enabled by CaSync further. To do so, we simply adapt the calculation of  $T_{sync}^{cpr}(m,K)$  by grouping K partitions into  $\lceil \frac{K}{N} \rceil$  batches.

Based on the comparison of  $T_{sync}^{orig}(m, K)$  and  $T_{sync}^{cpr}(m,K)$ , we decide whether it is beneficial to enable compression for a gradient. If so, we also compute the optimal number of partitions for the best performance. This is feasible because: 1) all parameters in Table 2 can be easily obtained or profiled via GPU and network measurements, where we launch the GPU kernels and peer-to-peer communication tasks with respect to different gradient sizes to fit the compression and network cost curves, respectively; 2) the values of  $\alpha$ ,  $\beta$  and  $\gamma$  in Table 3 needed to analyze  $T_{sync}^{cpr}(m, K)$  are determined once a DNN system with its CaSync synchronization strategy is given, and 3) the expressions 1 and 2 are convex functions which make it straightforward to identify the best setting for each gradient. It is worth mentioning that, our cost model assumes a homogeneous environment where all GPUs and network

```

void encode(float* input, uint8* output, params);

void decode(uint8* input, float* output, params);

```

Fig. 4: Unified compression-related API abstraction.

links have the same capacities, and the profiling results are obtained without considering the variance or interference of network and GPUs. We leave the exploration of the impacts of dynamics on the profiling accuracy of our cost model as future work.

Note that most, if not all, gradient compression algorithms (including the six state-of-the-art ones we evaluate) are *layer-wised*. We impose a strict partition-compress-batch order which is applied to each DNN layer independently, and thus it does not affect the accuracy and convergence of original compression algorithms. For few non-layer-wised compression algorithms, we simply turn off the selective compression and partitioning, thus incurring no negative impacts on accuracy and convergence of these algorithms.

# 4 COMPRESSION LIBRARY AND LANGUAGE

As discussed in Section 2.5, on-GPU compression can greatly accelerate compression-related computation, alleviate the bandwidth tension between GPU and host, and create new opportunities to further optimize the gradient synchronization process. However, developing and optimizing gradient compression algorithms on GPU is non-trivial, and integrating them into DNN systems usually requires substantial system expertise and manual efforts. Thus, we design a toolkit Complet, which allows practitioners to easily develop highly-optimized compression algorithms using GPU capability. The Complet-generated code is then consumed by CaSync, thus enabling an automated integration of compression algorithms with CaSync into DNN systems.

#### 4.1 Unified API Abstraction

CompLL provides a unified API abstraction for implementing gradient compression algorithms. As shown in Figure 4, CompLL has two simple APIs: encode and decode, as well as a few algorithm-specific parameters (e.g., compression rate for sparsification, bitwidth or precision for quantization and rank size for low-rank). The encode API takes as input a gradient matrix and generates a compressed gradient as output. In particular, we use uint8 as the type of the output matrix, because we can then cast one or multiple uint8 to any type in CUDA. On the other hand, the decode API unfolds a compressed gradient into its original form.

#### 4.2 Common Operator Library

By studying the state-of-the-art compression algorithms, we observe that they can generally be specified using a few common operators [5], [12], [18], [44], [76], [84], [85], [87], [89], [94], [96], [103]. For instance, these algorithms all need to scan the elements of a gradient. Alongside scanning, they all need to perform operations such as filtering or reducing the scanned elements to produce compressed gradients. With this observation, we generalize a library of common operators that can be used to construct gradient

TABLE 4: List of common operators. G is a gradient matrix, and o is the rank size required by low-rank methods.

| Operator                          | Interpretation                                                                                          |

|-----------------------------------|---------------------------------------------------------------------------------------------------------|

| sort(G, udf)                      | Sort elements in $G$ w.r.t the order given                                                              |

|                                   | by the user-defined function <i>udf</i>                                                                 |

| filter(G, udf)                    | Select elements from <i>G</i> via <i>udf</i>                                                            |

| map(G, udf)                       | Return H where $H[i] = udf(G[i])$                                                                       |

| reduce(G, udf)                    | Return a reduced value of $G$ via $udf$                                                                 |

| random(a, b)                      | Return a random int/float in $[a,b)$                                                                    |

| $concat(a, \cdots)$               | Concatenate values together into a vector                                                               |

| extract(G')                       | Extract metadata from the compressed $G'$                                                               |

| decomp(G, o)                      | Return $P$ , $Q$ such that $PQ^{\top} \approx G$ , where                                                |

| 1 ( ) /                           | $G \in \mathbb{R}^{n \times m}$ , $P \in \mathbb{R}^{n \times o}$ , and $Q \in \mathbb{R}^{m \times o}$ |

| $\operatorname{matmul}(G_0, G_1)$ | Matrix multiplication of $G_0$ and $G_1$                                                                |

compression algorithms, as listed in Table 4. For instance, the  $\mathtt{reduce}(G, \mathtt{maxAbs})$  operator with a user-defined function  $\mathtt{maxAbs}$  computes the maximum absolute value of the gradient matrix G, and the  $\mathtt{decomp}(G, \circ)$  operator decomposes G into two smaller matrices with their sizes properly calculated. We have carefully optimized these common operators regarding memory access and bank conflicts in GPU [27], so that any algorithm implementation based on these operators can automatically inherent our GPU optimizations (see details in Section 5).

## 4.3 Code Synthesis and Domain-specific Language

We provide two ways for practitioners to implement algorithms using CompLL. They can invoke our common operator library directly in their algorithm implementation. This, however, requires them to be familiar with the low-level CUDA programming. To further relieve the burden, we design a simple, C-like domain-specific language (DSL) for practitioners to easily implement their algorithms with the unified API abstraction filled with common operators, without worrying about hardware-oriented implementation and optimization. Specifically, our DSL supports basic data types such as uint1, uint2, uint4, uint8, int32, float, and array, as well as simple numerical computations and function calls to the common operators. Though not supported, our practice shows that it is often unnecessary to include loops in the DSL code as the iterative processing semantics have already been covered by the implementation of common operators.

To show how DSL works, we use it to implement the classic TernGrad compression [94] as an example in Figure 5. Line 1-3 specify bitwidth as the algorithm parameter to determine compression rate. Line 5-8 specify a user-defined function floatToUint to compress a float number into a bitwidth-sized integer. The TernGrad's logic to implement our encode API begins at line 9, and takes the original gradient as input and outputs the compressed gradient. Through line 11-14, the algorithm metadata which is essential for decompression is generated. At line 15, we pass the user-defined function floatToUint to the common operator map to generate the compressed gradient matrix Q. Finally, at line 16, we use the common operator concat to combine all metadata and Q into the output compressed gradient. We omit the implementation of the TernGrad's decompression code in the interest of space.

```

1

param EncodeParams{

2

uint8 bitwidth; // assume bitwidth = 2 for clarity

3

4

float min, max, gap;

5

uint2 floatToUint(float elem) {

6

float r = (elem - min) / gap;

return floor(r + random<float>(0, 1));

8

void encode(float* gradient, uint8* compressed, \

10

EncodeParams params) {

11

min = reduce(gradient, smaller);

12

max = reduce(gradient, greater);

13

gap = (max - min) / ((1 << params.bitwidth) - 1)

14

uint8 tail = gradient.size % (1 << params.

bitwidth);

15

uint2* Q = map(gradient, floatToUint);

compressed = concat(params.bitwidth, tail, \

16

17

min, max, Q);

18

```

Fig. 5: TernGrad's compression logic specified using the API, common operators and DSL of Comple.

TABLE 5: Comparison of implementation and integration costs (measured in lines of code) between open-source (OSS) and Complit-based compression algorithms.

| Algo-    | OSS   |                            | CompLL |                    |                  |   |

|----------|-------|----------------------------|--------|--------------------|------------------|---|

| rithm    | logic | integ-<br>ration logic udf | udf    | # common operators | integ-<br>ration |   |

| onebit   | 80    | 445                        | 21     | 9                  | 4                | 0 |

| TBQ      | 100   | 384                        | 13     | 18                 | 3                | 0 |

| TernGrad | 170   | 513                        | 23     | 7                  | 5                | 0 |

| DGC      | 1298  | 1869                       | 29     | 15                 | 6                | 0 |

| GradDrop | N/A   | N/A                        | 29     | 21                 | 6                | 0 |

| PowerSGD | 307   | 211                        | 15     | 10                 | 2                | 0 |

Next, ComplL's code generator parses the gradient compression algorithm specified in our DSL, traverses its abstract syntax tree, and automatically generates the CUDA implementation. When encountering a function call to common operators, Compli directly substitutes it with our highly-optimized CUDA implementation and then converts the specified parameters into their desired formats. For other operations such as numerical computations, CompLL declares specified variables and copies the necessary numerical computation code accordingly, as our DSL supports a subset of C's syntax. For a variable of type (such as uint1) which is not supported in CUDA, ComplL uses a byte to store it and uses bit operations to extract the actual value. If it is an array of variables of unsupported type, Compli uses consecutive bits of one or more bytes to represent this array compactly, with the minimal zero padding to ensure the total number of bits is a multiple of 8.

#### 4.4 Case Studies and Discussions

To demonstrate the easy algorithm development enabled by Complet, we use it to implement six state-of-the-art compression algorithms: onebit [76], TBQ [84], and TernGrad [94] are quantization algorithms; DGC [44] and GradDrop [5] are sparsification ones; PowerSGD [87] is a low-rank algorithm. Onebit, TBQ, TernGrad, DGC and PowerSGD have open-source (OSS) implementations.

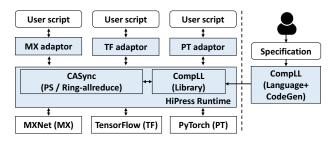

Fig. 6: The overview of HiPress. The shadow boxes are the new components introduced by HiPress.

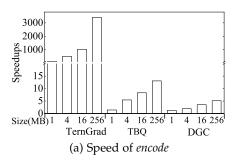

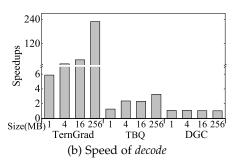

Auto-generated code. Table 5 summarizes the comparison between the open-source and Compliance implementations of these algorithms. The open-source implementations need a lot more code to implement these algorithms, and spend substantial effort to integrate them into DNN systems. In contrast, with Compliance, we use only 3 to 6 common operators to implement these algorithms with fewer than 21 lines of code for user-defined functions and fewer than 29 lines of code for algorithm logic. The algorithm is then translated into GPU code via our code generator and integrated into DNN systems by Compliance evaluations in Section 6.4 to compare the encode and decode operations between Compliance (OSS) baselines.

Expressiveness and extensibility. Beside the classic algorithms listed in Table 5, we exercise more gradient compression algorithms and find that they all can be easily specified and auto-generated by CompLL. For instance, AdaComp [14] needs map, reduce, filter, concat and extract common operators, while 3LC [43] needs reduce, map, concat, filter and extract. As an example, it requires only 69 lines of CompLL's DSL code to express the encode function of 3LC, whose zero-run encoding logic is specified by partitioning the target gradient and applying map and filter over each partition. For future algorithms possibly requiring new operators, CompLL is open and allows registering them into the common operator library for enjoying our automated code generation and integration into DNN systems.

## 5 HIPRESS FRAMEWORK

We incorporate the aforementioned coherent design into an open-source framework HiPress [2] for compression-aware data parallel DNN training. HiPress has 7.5k and 3.3k lines of code in C/C++ and Python, respectively, and is composed of the following main components, as shown in Figure 6.

## 5.1 Major System Components

CaSync. We implement CaSync using Horovod [78], a popular gradient synchronization library used by almost all mainstream DNN systems. CaSync currently supports both PS and Ring-allreduce. We leverage the MPI\_all\_to\_-all [56] and NCCL\_all\_to\_all [62] primitives to execute the bulk communication step introduced in Section 3.2.

We deploy the global *coordinator* on one of the training nodes. Though being a centralized component, its load is always light and the coordination overhead is negligible due to the following reasons: (1) only the gradient metadata is exchanged, and (2) the coordination of one gradient batch runs asynchronously with the bulk synchronization of the previous batches, thus its cost can be always hidden (confirmed in our experiments).

The selective compression and partitioning planer is a standalone component for producing per-gradient compression and partitioning plans. It obtains the variables defined in Section 3.3 from the training scripts (including the synchronization strategy and cluster configurations), the network, and GPU-measurements via the first training iteration. The produced plans are executed by CaSync at runtime.

Complete. We implement decompose common operator using LAPACK [37] and remaining operators using Thrust [61], the CUDA C++ template library, with the following optimizations. (1) Compli reuses gradients produced by DNN computation and only allocates buffers for the much smaller compressed gradients to avoid the GPU memory contention. (2) Compli uses fast share memory rather than global memory, and eliminates bank conflicts [27] by making each thread access disjoint memory banks when possible. We also fuse the decode and merge operators for better performance. To avoid computing resource contention, we allocate CUDA cores for compressionrelated computation, while letting DNN computation kernels make the full use of Tensor cores. Therefore, these two types of computation can run concurrently with no interference.

**Local aggregation.** For multiple GPUs per node, we first aggregate the original gradients among local GPUs, and then synchronize the compressed gradients across nodes. This is because the bandwidth of intra-node connection links (e.g., PCIe, NVLink) is often orders of magnitude higher than the inter-node links. Local aggregation reduces the number of gradients exchanged across nodes for better performance.

#### 5.2 Training Integration and Execution Scheduling

HiPress integrates CaSync and CompLL-generated library into three modern DNN systems TensorFlow, MXNet, and PyTorch. First, CaSync is integrated via Horovod. CompLL creates wrapper functions for encode and decode primitives to obtain pointers to gradients and the algorithmspecific arguments from the training context. CompLL then invokes the CompLL-generated code. Second, we create adaptors to make training workflows compression-enabled by instrumenting the original training scripts with function calls to CaSync. The major challenge we identify here is the mismatch between the existing execution models with coarse-grained dependency tracking mechanisms in DNN systems and the new computation-compressioncommunication pipeline HiPress introduces. To illustrate the problem and our system adaptations, we consider the following two cases.

**MXNet and TensorFlow.** The two systems have their own task manager to overlap the gradient synchronization and

Fig. 7: Ordering constraint optimization. Solid-line/dashed-line arrows represent read/write dependencies, respectively, and other arrows represent causal dependencies.

Fig. 8: The new DNN computation, compression, and communication pipeline in HiPress.

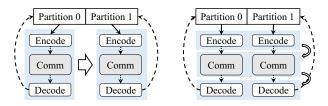

DNN computation. We add a new task queue and a dedicated CPU thread to schedule *encode* and *decode* operators on GPU for further running compression-related computation and DNN computation in parallel, as we observe that the former computation is often memory-intensive. However, the asynchronous execution engines open a challenge, especially when considering gradient partitioning in the context of compression. As described in Section 3.3, our CaSync synchronization may partition gradients before compression. To avoid expensive memory copying, instead of allocating temporary spaces for partitioned gradients, we use offsets pointing to the original gradient in GPU to mimic partitioning. Without a proper design, however, we could impose unnecessary ordering constraints on the synchronization of all partitions. This is because the dependency tracking in existing DNN systems is coarse-grained and not aligned with our memory copying avoidance.

Figure 7 illustrates this problem. On the left side, the synchronization-related operations (i.e., encode, comm (communication) and decode) execute sequentially for a partition. Partition 0's decode has a write dependency on the shared gradient, while the Partition 1's encode imposes a read dependency on the same gradient despite of different partitions. This leads to a situation where the synchronization of the two partitions is serialized (unnecessarily). Instead, on the right side, we divide the synchronization into stages, group operations in one stage, and then pass them to the next stage. This meets proper ordering constraints while allowing for pipelining the synchronization across different partitions of the same gradient.

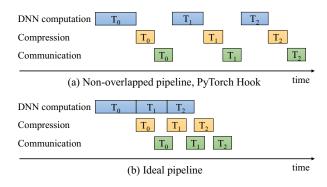

**PyTorch.** Though the asynchronous execution is also supported, PyTorch does not rely on a task manager, instead, it executes gradient synchronization in hook [52]. However, directly calling CaSync in hook would lead to performance

degradation as it precludes the opportunity of overlapping computation and communication, as shown in Figure 8a. This is because the main process can launch the next DNN computation operator as long as the operators in hook, such as <code>encode</code>, <code>bulk communication</code>, and <code>decode operators</code>, complete their execution.

To address the hook issue, we implement a task manager inspired by the execution engine of MXNet and TensorFlow to enable the new computation-compression-communication pipeline. This engine employs multiple queues to manage different tasks, each assigned a dedicated thread for task launching. In addition, we apply the above fine-grained dependency tracking optimization that works with gradient partitioning to PyTorch. Finally, the new pipeline allows the DNN computation to overlap with both compression and communication, as depicted in Figure 8b.

# 5.3 Choosing CaSync-PS or Ring?

Here, we discuss the performance behaviors of the two compression-enabled gradient synchronization methods offered by CaSync across the three categories of compression algorithms. First, for the low-rank algorithms, CaSync-PS has the same performance as CaSync-Ring, due to the following reasons. On one hand, according to Table 3, CaSync-PS takes the same number of transmission, compression and aggregation steps as CaSync-Ring. This is as expected since existing studies [33], [35] including ours prove that their non-compression baselines are semantically equivalent. Furthermore, when compression is enabled, at every intermediate step, compressed gradients are directly aggregatable, and there is no need to perform encode and decode operators. On the other hand, we have implemented CaSync-PS efficiently, which follows the common practice of Ring-allreduce to make use of high performance collective communication primitives. Second, regarding the quantization algorithms, the performance of CaSync-PS is also similar to that of CaSync-Ring, due to the same reasons above.

Finally, contrary to quantization and low-rank algorithms, the two methods can deliver different performance numbers for sparsification ones, mainly because of the data inflation when aggregating gradients. In more detail, upon receiving compressed sparse gradients, often containing top K important elements, the worker or aggregator merges them to form updated gradients, which will contain top K' elements, where K' >= K. This inflation would lead to increases in transmission latency and bandwidth consumption. However, this impacts CaSync-PS less heavily than CaSync-Ring due to the following reasons. CaSync-PS is implemented by the combined use of gather and broadcast, and the inflation only affects the performance of broadcast. As the gradients are partitioned, and balanced across workers, the impacts are not heavy. Dislike this, for CaSync-Ring, inflation happens at every step in its aggregating phase (in total, N-1 steps). To make it comply with the Ring-allreduce semantics, which requires gradients to be same sized during all steps, we have to add an extra encode operator following the merger operator to re-select top K elements. However, this incurs additional computation overhead, compared to CaSync-PS. Note that we

TABLE 6: Statistics of trained models.

| Name              | Total size | Max gradient | # Gradients |

|-------------------|------------|--------------|-------------|

| VGG19 [83]        | 548.05MB   | 392MB        | 38          |

| ResNet50 [29]     | 97.46MB    | 9MB          | 155         |

| UGATIT [34]       | 2558.75MB  | 1024MB       | 148         |

| UGATIT-light [34] | 511.25MB   | 128MB        | 148         |

| Bert-base [21]    | 420.02MB   | 89.42MB      | 207         |

| Bert-large [21]   | 1282.60MB  | 119.23MB     | 399         |

| LSTM [50]         | 327.97MB   | 190.42MB     | 10          |

| Transformer [86]  | 234.08MB   | 65.84MB      | 185         |

can only observe visible performance differences between CaSync-PS and CaSync-Ring when the sparsity rates are considerably low. We leave the further exploration and system optimizations in the future work.

#### 6 EVALUATION

Our evaluation answers the following main questions:

- Can HiPress significantly improve the performance of DNN data parallel training jobs over the baselines?

- What are the performance implications of synchronization optimizations and the auto-generated compression code?

- What are the effects of compression rate and network bandwidth?

- Can CompLL-generated compression algorithms outperform their open-source ones?

- Can CompLL-generated compression algorithms achieve the same training accuracy as their original versions?

#### 6.1 Experimental Setup

Machine configurations. We conduct experiments in both AWS EC2 and local clusters to evaluate <code>HiPress</code> with both high-end and low-end machines. We use 16 p3dn.24xlarge EC2 instances with 128 GPUs. Each instance has 96 vCPU, 8 NVIDIA Tesla V100 GPUs (32GB memory, connected by NVLink), and is connected by a 100Gbps network. We also replicate the same experiments in our local cluster with 16 nodes and 32 GPUs. Each local node has two 16-core Intel E5-2620 processors, 2 NVIDIA 1080 Ti GPUs (connected via a PCIe switch), and is connected by a 56Gbps Infiniband network. EC2 instances and local nodes run Ubuntu 16.04 and CentOS 7.6, respectively, with the remaining software being identical, such as CUDA 11.1, OpenMPI 4.0.3, NCCL 2.10.3, MXNet 1.5.1, TensorFlow 1.15.5, PyTorch 1.10.0, Horovod 0.20.3 and BytePS 0.2.5.

Baselines. We use TensorFlow (TF), MXNet, PyTorch with BytePS and Ring-allreduce (Ring) as no-compression baselines. In the interest of space, we only demonstrate the end-to-end performance with four out of six generated compression algorithms, namely, onebit, DGC, TernGrad and PowerSGD, with different DNN systems. We use the recently developed BytePS(OSS-onebit) [6], [13], Ring(OSS-DGC) [66] and PyTorch(OSS-PowerSGD) [54] from industry as compression-enabled baselines with open-source (OSS) quantization, sparsification and low-rank algorithms respectively. Note that for a fair comparison, we use our highly optimized on-GPU implementation instead of the original on-CPU implementation for onebit algorithm denoted by CompLL-onebit.

TABLE 7: Compression and partitioning plans of CompLL-onebit. In each tuple, the first value decides whether to compress a gradient and the second value indicates the number of partitions.

| Gradient | CaSync-PS           |                     | CaSync-Ring        |                     |

|----------|---------------------|---------------------|--------------------|---------------------|

| size     | 4 Nodes             | 16 Nodes            | 4 Nodes            | 16 Nodes            |

| 4MB      | <yes, 2=""></yes,>  | <yes, 1=""></yes,>  | <yes, 1=""></yes,> | <no, 16=""></no,>   |

| 16MB     | <yes, 4=""></yes,>  | <yes, 6=""></yes,>  | <yes, 4=""></yes,> | <yes, 5=""></yes,>  |

| 392MB    | <yes, 12=""></yes,> | <yes, 16=""></yes,> | <yes, 4=""></yes,> | <yes, 16=""></yes,> |

Models and datasets. Following the literature [33], [75], we choose six widely-used DNN models with three computer vision (ResNet50, VGG19 and UGATIT) and three natural language processing (Bert, Transformer and standard-LSTM). We train ResNet50 and VGG19 with the ImageNet dataset [74], and the remaining models with the selfie2anime [73], RTE [11], WMT17 [77] and wikitext-2 [49] dataset, respectively. We additionally deploy Bert and UGATIT under their light mode with fewer parameters to meet the GPU memory constraint in our local cluster, denoted as Bert-base and UGATIT-light, respectively. The model details are summarized in Table 6.

**Metrics.** We measure the total number of samples processed per second as the training throughput, the latency breakdown of the key steps in the computation-synchronization pipeline, speedups of encode and decode, and the training accuracy and convergence speed.

System configurations. We tune the configurations of baselines for their best performance, e.g., co-locating aggregators and workers for BytePS and CaSync-PS. We deploy all systems with RDMA enabled except BytePS on EC2. This is because BytePS does not support the Elastic Fabric Adapter (EFA) used by EC2 instances at the moment. We keep the per-GPU batch size constant as the number of GPUs are scaled up (*weak scaling*). We set batch sizes across different models by following literature [21], [36], [50], [86], instead of setting them to the largest value that a single GPU can sustain, since a too large batch size may lead to convergence problems [47], [75]. For all four compression algorithms, we inherit the parameter settings from their original papers.

Table 7 shows the optimal thresholds for compressing a gradient and the optimal partition numbers, produced by CaSync based on CompLL-onebit algorithm. According to two synchronization strategies CaSync currently supports and their cluster deployment configurations, we set the value of  $\alpha$ ,  $\beta$  and  $\gamma$  for Casync-PS as 2(N-1), K and N, respectively. This assignment is slightly different from the numbers in Table 3. This is because the evaluated CaSync-PS in Section 6 co-locates aggregators and workers, and the local workers do not need to send its gradients to the co-located aggregator via network activities. For CaSync-Ring against sparsification and quantization algorithms, we set three parameters as 2(N-1), N, and N, while for CaSync-Ring against the PowerSGD algorithm, we set three parameters as 2(N-1), 1, and 1 respectively. The optimal thresholds of selective compression and partition sizes are produced by our cost analysis model. With 16 nodes, CaSync suggests compressing gradients larger than 4MB and splitting the largest VGG gradient into 16 partitions before compression for AWS EC2 platform.

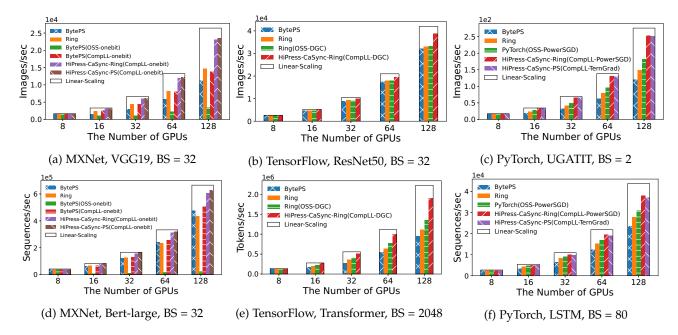

Fig. 9: Throughput comparison of image processing and natural language processing models atop MXNet, TensorFlow, and PyTorch. AWS EC2 V100 instances. 100Gbps cross-node RDMA network. BS stands for per-GPU batch size.

In addition, for the baseline synchronization strategies like BytePS and Horovod (Ring-allreduce enabled), we use their default settings. These baselines are able to tune the number of partitions for maximizing the overall performance [33], [63].

## 6.2 End-to-End Performance

## 6.2.1 AWS EC2 Results

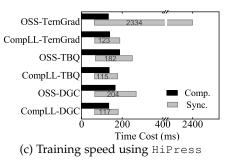

Figure 9 compares the end-to-end training throughput of HiPress and baselines with MXNet, TensorFlow and Py-Torch as the underlying DNN system, respectively, using a total of 128 GPUs.

Atop MXNet. We demonstrate the throughput comparison results using MXNet in Figure 9a and 9d. For the VGG19 model, Ring outperforms BytePS by 31.3-50.3% across all cluster sizes. When not using RDMA, Ring still outperforms BytePS by 19.3-36.6%. These results are not consistent with the BytePS paper, but valid. This is due to we use a newer version of NCCL library that both BytePS and Ring relies on, and we also disable intra-node aggregation in Ring, which leads to better performance. For the Bert-large model, BytePS outperforms Ring by up to 8.9% across all cluster sizes. However, enabling the onebit compression algorithm within BytePS does not bring expected speedups. With the native on-CPU onebit implementation, BytePS (OSS-onebit) performs the worst, and runs far slower than all other system configurations. When migrating compression-related computation from CPU to GPU, BytePS(CompLL-onebit) catches up with noncompression baselines, but brings only limited improvements over the best-performed one, e.g., only up to 7.3% improvement over BytePS. Such surprising result verifies the importance of implementing fast compression algorithms on GPU and designing a compression-aware synchronization strategy to release the full potential of compression algorithms.

Fig. 10: GPU utilization of Ring and HiPress when training Bert-large and UGATIT. The configurations of HiPress are the same as those used in Figure 9d and 9c.

Unlike limited speedups brought by the latest synchronization strategies and open-source versions of compression algorithms, HiPress significantly improves the training throughput over all baselines across all cases. E.g., with 128 GPUs, for VGG19 and Bert-large, HiPress-CaSync-PS(CompLL-onebit) outperforms BytePS, Ring and BytePS (CompLL-onebit) by 110.5% and 32.3%, 60.4% and 44.1%, 69.5% and 23.3%, respectively. HiPress-CaSync-Ring(CompLL-onebit) performs similarly to HiPress-CaSync-PS (CompLL-onebit), and also significantly outperforms all baselines. One important observation is that the improvements of HiPress become larger when the number of GPUs increases. This implies that when the cluster size expands, the communication overhead of the communication-intensive models increases, and thus HiPress becomes even more beneficial.

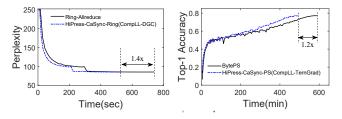

Atop TensorFlow. We evaluate the integration with TensorFlow using the ResNet50 and Transformer models. In Figure 9b, the non-compression BytePS and Ring perform similarly for ResNet50. In contrast, for Transformer, Ring outperforms BytePS by up to 30.9% and 23.5%, when switching on/off RDMA. Transformer's scaling efficiency is

significantly lower than that of ResNet50, since it is more communic-ation-intensive and exchanges more gradients than ResNet50.

Note that BytePS(OSS-onebit) cannot be directly applied to TensorFlow, since it is tightly coupled with MXNet. Thus, we exercise DGC, integrated into Ring-allreduce and TensorFlow. To compare with Ring (OSS-DGC), we configure HiPress with CaSync-Ring rather than CaSync-PS. For the Transformer model, Ring (OSS-DGC) outperforms BytePS and Ring by up to 42.8% and 22.1%, respectively, though brings almost no improvement for ResNet50. Because of the optimized compression-aware synchronization strategy design and the highly-efficient on-GPU DGC code generated by CompLL, HiPress-CaSync-Ring (CompLL-DGC) outperforms Ring(OSS-DGC) by up to 41.1%, and the noncompression baselines such as BytePS and Ring by up to 101.4%, for Transformer. Interestingly, even for ResNet50, HiPress improves its training speed by up to 20.7% over all baselines. This implies that when the cluster size expands, the communication cost of the computation-intensive models also increases, and can benefit from HiPress.

Atop PyTorch. Here, we exercise the UGATIT and LSTM models. Here, we choose PyTorch (OSS-PowerSGD) as the compression-enabled baseline, while BytePs and Ring as the non-compression ones. In Figure 9c and 9f, similar to the results of HiPress atop both MXNet and TensorFlow, HiPress over PyTorch with CaSync-Ps the CompLL-TernGrad algorithm obtains a speedup up to 2.1 × compared to BytePs and Ring, for UGATIT and LSTM. Such consistent results verify that HiPress is a general and high performance compression-aware data parallel framework.

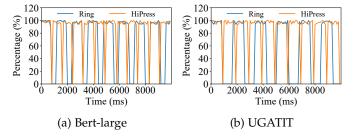

Though the two models are communication-intensive, the open-source PyTorch (OSS-PowerSGD) only outperforms the best-performed Ring baseline by up to 23.3% and 11.6% respectively. This is mainly due to the sequential execution introduced by the hook mechanism (see Section 5.2) and the lack of local aggregation in the native communication library of PyTorch. In contrast, HiPress-CaSync-Ring (CompLL-PowerSGD) further brings 22.9%-39.3% and 9.8%-22.7% improvement for the two DNN models across all setups with different numbers of GPUs in-use, compared to PyTorch (OSS-PowerSGD), thanks to its finegrained task management, local aggregation optimization and high performance auto-generated PowerSGD operators. GPU utilization. Figure 10 compares the GPU resources used for the DNN-related computation of the non-compression baseline Ring and the best-performed HiPress configurations (Figure 9d and 9c). Here, we use nsight instead of nvidia-smi to measure the GPU utilization of training jobs, since the latter does not distinguish the GPU resources used for the DNN computation and gradient synchronization. For the Bert-large and UGATIT model, both Ring and HiPress can use nearly 100% GPU computing resources at the peak. However, the overall GPU usage of Ring is more sparse than HiPress. This is because Ring's GPU utilization drops to zero during gradient transmission, which is time-consuming in data parallel training. However, within HiPress, the fast compressionaware gradient synchronization eliminates the communication bottleneck, which leads the system to spend more time

Fig. 11: Training speedup normalized to BytePS atop MXNet system, in a 16-node local cluster connected via 56Gbps Infiniband network with RDMA enabled.

Fig. 12: Impacts of enabling synchronization optimizations on the time cost of computation and synchronization.

doing useful work.

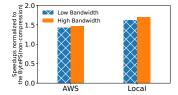

## 6.2.2 Local Cluster Results.

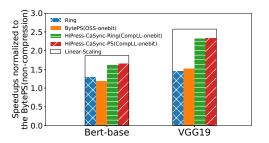

In addition to the high-end servers, low-end clusters with earlier generations of GPUs than V100 and commodity networks slower than the 100Gbps links in AWS have been still in widespread use [8], [23], [41], [42]. To test the applicability of HiPress to low-end servers, we replicate all above experiments in our local cluster with low-end GPUs and RDMA-enabled 56Gbps network links. Similar to the performance improvements of HiPress in the high-end AWS cluster, in our local cluster tests, the combinations of two CaSync synchronization strategies and various CompLL-generated algorithms in HiPress significantly outperform all baselines, and HiPress's performance advantages become more obvious with more GPUs. In the interest of space, we only show the performance speedups of all system configurations when training Bert-base and VGG19 over MXNet, normalized to the non-compression baseline BytePS, see Figure 11. We use the onebit algorithm to reduce the transmitted data volume like in Figure 9a and 9d. Due to the GPU memory constraint, we run Bert-base, a light variant Bert with fewer parameters. With 16 nodes and 32 GPUs, for both communication-intensive models, surprisingly, the state-of-the-art compression-enabled baseline BytePS (CompLL-onebit) runs even 8.5% slower than the non-compression Ring. By contrast, HiPress outperforms the non-compression baselines (i.e., BytePS and Ring) and the compression-enabled baseline BytePS (CompLLonebit) by up to 133.1% and 53.3%, respectively. Thus, HiPress could benefit training jobs with diverse software/hardware configurations, as long as the communication is the bottleneck.

Fig. 13: Speeds of Compliance and training performance effects. The subfigure (c) represents the timeline diagram of the DNN computation (Comp.) and gradient synchronization (Sync.) pipeline. The pipeline is shorter, and the performance is better.

# 6.3 Effectiveness of Various Optimizations

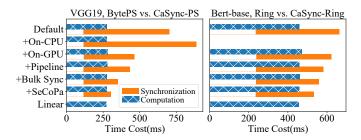

Next, we evaluate the individual performance gains of various synchronization and compression optimizations we introduced. We report the latency breakdown when enabling optimization one by one for training VGG19 and Bert-base across 16 local nodes in Figure 12 (the AWS results look similar and thus are not shown here). We use HiPress (Compliance) as an example with the same setup as Figure 11 (results using other algorithms look similar). We synchronize gradients of VGG19 via CaSync-PS, and Bert-base via CaSync-Ring. *Default* are baselines where the state-of-the-art BytePS or Ring is used without compression.

CompLL auto-generation. Compared to *Default*, surprisingly, directly using the open-source on-CPU onebit (denoted as on-CPU) results in 32.2% more gradient synchronization cost for <code>BytePS</code> on VGG19. This is because the overhead of on-CPU compression operators largely exceeds the communication savings. However, this does not apply to Bert-base since <code>Ring</code> uses GPU and does not work with on-CPU compression. In contrast, our <code>CompLL-onebit</code> (denoted as on-GPU) reduces the synchronization cost by 41.2% and 10.0% for VGG19 and Bert-base, respectively. We also observe that on-GPU <code>CompLL-onebit</code> imposes negligible negative impact on the local DNN computation time, even though they share GPU.