# Ultra-Wide Band Gap $\text{Ga}_2\text{O}_3$ -on-SiC MOSFETs

Yiwen Song, Arkka Bhattacharyya, Anwarul Karim, Daniel Shoemaker, Hsien-Lien Huang, Saurav Roy, Craig McGary, Jacob H. Leach, Jinwoo Hwang, Sriram Krishnamoorthy,\* and Sukwon Choi\*

Cite This: *ACS Appl. Mater. Interfaces* 2023, 15, 7137–7147

Read Online

ACCESS |

Metrics & More

Article Recommendations

**ABSTRACT:** Ultra-wide band gap semiconductor devices based on  $\beta$ -phase gallium oxide ( $\text{Ga}_2\text{O}_3$ ) offer the potential to achieve higher switching performance and efficiency and lower manufacturing cost than that of today's wide band gap power electronics. However, the most critical challenge to the commercialization of  $\text{Ga}_2\text{O}_3$  electronics is overheating, which impacts the device performance and reliability. We fabricated a  $\text{Ga}_2\text{O}_3$ /4H-SiC composite wafer using a fusion-bonding method. A low-temperature ( $\leq 600$  °C) epitaxy and device processing scheme was developed to fabricate MOSFETs on the composite wafer. The low-temperature-grown epitaxial  $\text{Ga}_2\text{O}_3$  devices deliver high thermal performance (56% reduction in channel temperature) and a power figure of merit of ( $\sim 300$  MW/cm $^2$ ), which is the highest among heterogeneously integrated  $\text{Ga}_2\text{O}_3$  devices reported to date. Simulations calibrated based on thermal characterization results of the  $\text{Ga}_2\text{O}_3$ -on-SiC MOSFET reveal that a  $\text{Ga}_2\text{O}_3$ /diamond composite wafer with a reduced  $\text{Ga}_2\text{O}_3$  thickness ( $\sim 1$   $\mu\text{m}$ ) and a thinner bonding interlayer ( $< 10$  nm) can reduce the device thermal impedance to a level lower than that of today's GaN-on-SiC power switches.

**KEYWORDS:** composite substrate, gallium oxide ( $\text{Ga}_2\text{O}_3$ ), power electronics, Raman spectroscopy, steady-state thermoreflectance, thermal management, ultra-wide band gap (UWBG) semiconductor devices

## 1. INTRODUCTION

$\beta$ -Phase gallium oxide ( $\text{Ga}_2\text{O}_3$ ) is an ultra-wide band gap (UWBG) semiconductor ( $E_G \sim 4.8$  eV), which promises significant improvements in the performance and manufacturing cost over today's commercial wide band gap (WBG) power electronic devices based on GaN and SiC.<sup>1</sup> During the past half a decade, significant progress has been made in the  $\text{Ga}_2\text{O}_3$  bulk material synthesis (i.e., only  $\text{Ga}_2\text{O}_3$  offers melt-grown single-crystal substrates like Si wafers, among today's WBG and UWBG semiconductors), epitaxial growth, doping, and the development of homoepitaxial device architectures.<sup>1–3</sup> UWBG  $\text{Ga}_2\text{O}_3$  electronics give promise to allow designers to use fewer devices and smaller passive components in power electronics circuits.<sup>4</sup> Power conversion systems for electric vehicles and charging stations, renewable energy sources, and smart grids will benefit from the  $\text{Ga}_2\text{O}_3$  device technologies.

However, device overheating has become one of the most critical bottlenecks to the commercialization of  $\text{Ga}_2\text{O}_3$  device technologies.<sup>5</sup> In fact, no  $\text{Ga}_2\text{O}_3$  device reported to date has achieved the performance expected by the outstanding electronic properties because a thermally limited technological plateau has been reached.  $\text{Ga}_2\text{O}_3$  possesses a poor anisotropic thermal conductivity (11–27 W/mK),<sup>6,7</sup> which is an order of magnitude lower than those for GaN ( $\sim 150$  W/mK)<sup>8,9</sup> and SiC ( $\sim 400$  W/mK).<sup>10,11</sup> It has been experimentally reported that single-finger  $\text{Ga}_2\text{O}_3$  metal–oxide–semiconductor field

effect transistors (MOSFETs)<sup>12</sup> and modulation-doped FETs (MODFETs)<sup>13,14</sup> exhibit a  $\sim 6\times$  higher channel temperature rise than commercial GaN high-electron-mobility transistors (HEMTs) under identical power dissipation levels. Moreover, recent computational work<sup>15</sup> indicates that self-heating will be significantly aggravated in practical multi-finger devices due to the thermal cross-talk<sup>16</sup> among adjacent current channels. Specifically, it has been predicted that the channel temperature rise of a six-finger  $\text{Ga}_2\text{O}_3$  MOSFET would be further 4 $\times$  higher than that for a single-finger  $\text{Ga}_2\text{O}_3$  device. Such aggravated self-heating in multichannel  $\text{Ga}_2\text{O}_3$  FinFETs as compared to that in single-fin devices has been experimentally demonstrated.<sup>17</sup> This signifies the importance of minimizing the junction-to-package thermal resistance of  $\text{Ga}_2\text{O}_3$  devices.

Efforts to counter the overheating at the package/system level not only increase the system size and weight but also have proven to be ineffective in cooling ultra-high-power density WBG/UWBG devices.<sup>18</sup> Therefore, the electro-thermal co-

Received: November 23, 2022

Accepted: January 17, 2023

Published: January 26, 2023

design of novel device architectures that can simultaneously achieve the lowest thermal resistance and the highest electrical performance is essential to enable the commercialization of UWBG  $\text{Ga}_2\text{O}_3$  device technologies.<sup>18</sup>

In our previous study,<sup>15</sup> a  $\text{Ga}_2\text{O}_3$ /4H–SiC composite wafer was created by taking advantage of a fusion bonding process. The thermal conductivity of the  $\text{Ga}_2\text{O}_3$  layer and the thermal boundary resistance (TBR) at the  $\text{Ga}_2\text{O}_3$ /SiC interface were characterized via a steady-state thermoreflectance (SSTR) technique. Scanning transmission electron microscopy (STEM) and energy-dispersive X-ray spectroscopy (EDX) were used to study the interface quality and chemistry. In this study,  $\text{Ga}_2\text{O}_3$  MOSFETs were fabricated on the composite substrate using low-temperature ( $\leq 600$  °C) metalorganic vapor-phase epitaxy that allowed the first realization of “homoepitaxial”  $\text{Ga}_2\text{O}_3$  MOSFETs on a composite substrate. This growth technique is necessary to prevent interface failure of the composite substrate due to mismatch of the coefficients of thermal expansion. Electrical testing was performed to determine the device output characteristics and breakdown voltages. The enhanced device thermal impedance achieved by integration with the composite wafer was assessed by using nanoparticle-assisted Raman thermometry. A design optimization study has been conducted with an aim to reduce the device thermal impedance of  $\text{Ga}_2\text{O}_3$  transistors below that for a commercial GaN power switch under high-power and frequency switching operation. The outcomes of this work provide guidelines to surpass the ultimate thermal limit of the (laterally configured) UWBG device technology.

## 2. RESULTS AND DISCUSSION

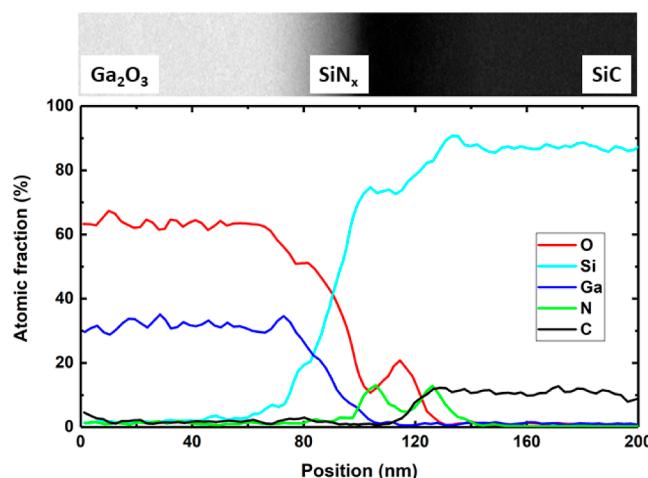

**2.1. Composite Wafer Fabrication.** In our previous study,<sup>15</sup> a  $\text{Ga}_2\text{O}_3$ /4H–SiC composite wafer was fabricated using a fusion bonding process. Here, we provide a summary of the fabrication process and structure of the composite wafer. 15 nm of  $\text{SiN}_x$  was coated on both a (010)-oriented Fe-doped 25 mm diameter  $\text{Ga}_2\text{O}_3$  wafer (which is the preferred orientation to achieve a higher thermal performance)<sup>13,19</sup> and a 50 mm diameter 4H–SiC wafer. To initiate fusion bonding,<sup>20,21</sup> the wafer surfaces were activated in oxygen plasma and joined at room temperature. After this, the integrated material stack was cured at 215 °C in a  $\text{N}_2$  convection oven. The bonded  $\text{Ga}_2\text{O}_3$  wafer was thinned down using a series of lapping plates and a diamond abrasive (9, 3, and 0.25  $\mu\text{m}$  diamond grit size). A silica-based chemical–mechanical polishing (CMP) process was used to achieve an epitaxial-ready surface. A critical advantage of the wafer bonding approach over heteroepitaxy directly on SiC<sup>22</sup> is that it allows subsequent homoepitaxial growth of highest-quality crystalline films without threading dislocations because the starting material is a highest-quality melt-grown  $\text{Ga}_2\text{O}_3$  substrate. The final thickness of the  $\text{Ga}_2\text{O}_3$  was measured via cross-sectional scanning electron microscopy (SEM) of a specimen prepared by focused ion beam (FIB) milling. STEM imaging and EDX mapping were, respectively, used to evaluate the quality and chemistry of the  $\text{Ga}_2\text{O}_3$ /SiC interface. As shown in Figure 1, a 10 nm thick  $\text{SiO}_x$  layer was unintentionally formed between the  $\text{SiN}_x$  bonding layers, contributing to the effective TBR at this interface.<sup>23</sup>

**2.2. Thermophysical Property Measurement.** Here, we provide a summary of the results for thermal characterization performed on a composite wafer with a  $\text{Ga}_2\text{O}_3$  thickness of 6.5  $\mu\text{m}$  in our previous work.<sup>15</sup> The total thermal resistance of the

**Figure 1.** High-angle annular dark-field STEM image near the  $\text{Ga}_2\text{O}_3$ /4H–SiC interface and EDX line map across the  $\text{Ga}_2\text{O}_3$ /4H–SiC interface.

composite wafer is dictated by the thermal conductivities of the 4H–SiC wafer and the  $\text{Ga}_2\text{O}_3$  layer, as well as the TBR at the  $\text{Ga}_2\text{O}_3$ /4H–SiC interface. The directionally averaged thermal conductivity of the 4H–SiC substrate was measured by an SSTR technique,<sup>24</sup> before integration with a  $\text{Ga}_2\text{O}_3$  substrate. The uncertainty in the SSTR measurement results is relatively high; however, the mean value of the measured SiC thermal conductivity agrees well with those reported by Wei et al.<sup>10</sup> The post-integrated  $\text{Ga}_2\text{O}_3$  film’s directionally averaged thermal conductivity was measured by adjusting the probing depth of the SSTR pump laser (which is dictated by the radius of the pump laser<sup>24</sup>) to a level smaller than the thickness of the  $\text{Ga}_2\text{O}_3$  layer. Finally, the TBR across the  $\text{Ga}_2\text{O}_3$ /SiC interface was extracted by performing the SSTR measurement of the composite wafer with a large pump laser diameter that would allow probing of the thermal resistance of a volume that reaches below the surface of the 4H–SiC substrate. A TBR of 47.1  $\text{m}^2\text{K}/\text{GW}$  was derived from this differential SSTR measurement procedure, based on the predetermined thermal conductivities of the 4H–SiC substrate and the  $\text{Ga}_2\text{O}_3$  layer (Table 1). Time-domain thermoreflectance (TDTR; used to

**Table 1. Thermal Properties of the Composite Substrate**

|                                              |                                      |

|----------------------------------------------|--------------------------------------|

| SiC thermal conductivity                     | $306.4 \pm 79.5 \text{ W/mK}$        |

| $\text{Ga}_2\text{O}_3$ thermal conductivity | $19.4 \pm 3.03 \text{ W/mK}$         |

| thermal boundary resistance                  | $47.1 \text{ m}^2\text{K}/\text{GW}$ |

measure the cross-plane thermal conductivity of the  $\text{Ga}_2\text{O}_3$  film)<sup>25,26</sup> and frequency-domain thermoreflectance (FDTR; used to measure the TBR at the  $\text{Ga}_2\text{O}_3$ /SiC interface)<sup>27,28</sup> were used to confirm the SSTR-based TBR results by characterizing a sister sample with the  $\text{Ga}_2\text{O}_3$  layer further thinned down to  $\sim 2 \mu\text{m}$ . The TBR extracted from this approach ( $42.8^{+20.6}_{-10.5} \text{ m}^2\text{K}/\text{GW}$ ) agrees well with the TBR value extracted by SSTR listed in Table 1. It should be noted that the experimental determination of the TBR is challenging due to the low measurement sensitivity;<sup>29</sup> therefore, analytical modeling was also used to confirm the mean value of the TBR measured by SSTR. Details of this combined approach using SSTR, TDTR, and FDTR methods as well as analytical modeling to estimate the effective TBR at the  $\text{Ga}_2\text{O}_3$ /SiC

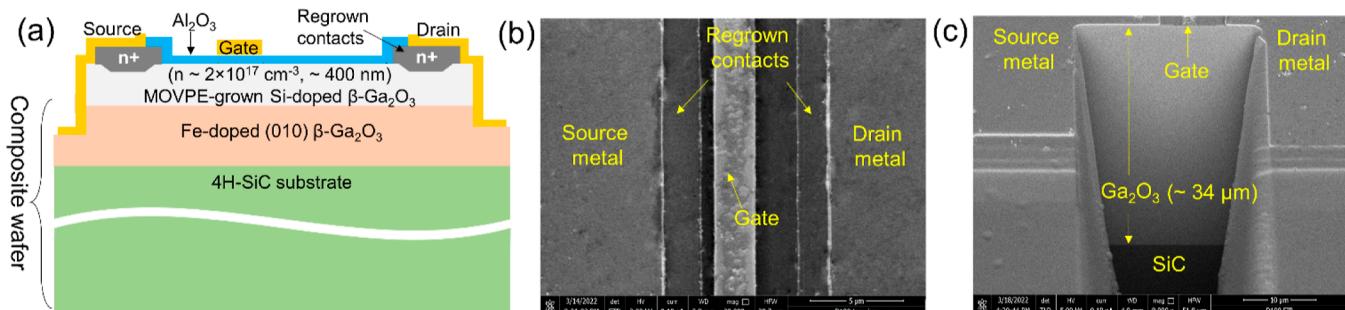

**Figure 2.** (a) Cross-sectional schematic of a Ga<sub>2</sub>O<sub>3</sub> MOSFET fabricated on the composite substrate. (b) Plan-view SEM image of the final device structure. (c) Cross-sectional SEM image of the same device showing the thickness of the Ga<sub>2</sub>O<sub>3</sub> layer.

interface (including the measurement sensitivity analyses) can be found in our previous work.<sup>15</sup>

The TBR of the composite wafer is lower than the value (60 m<sup>2</sup>K/GW) that was shown to be necessary to reduce the junction-to-package thermal resistance of a Ga<sub>2</sub>O<sub>3</sub>-on-SiC device below that of a commercial GaN-on-Si power switch.<sup>13</sup> However, it is 3× higher than the value reported for a Ga<sub>2</sub>O<sub>3</sub>/SiC interface joined with a 30 nm Al<sub>2</sub>O<sub>3</sub> bonding layer.<sup>29</sup> The relatively high TBR is caused by the low thermal conductivities of the SiN<sub>x</sub> bonding layer (1.9 W/mK)<sup>30</sup> and the unintentionally formed SiO<sub>x</sub> (1.1 W/mK)<sup>31</sup> interlayer. Higher thermal performance of the composite wafer can be achieved by optimizing the bonding process, that is, using a higher thermal conductivity bonding material and minimizing its thickness, as well as eliminating the formation of a SiO<sub>x</sub> interlayer.

In this work, as mentioned in the following subsection, a composite wafer with a Ga<sub>2</sub>O<sub>3</sub> thickness of ~34 μm was used for subsequent device processing. This composite wafer was simultaneously fabricated with the composite wafer (with a Ga<sub>2</sub>O<sub>3</sub> thickness of 6.5 μm) reported in our previous work.<sup>15</sup> Therefore, we assume an identical TBR for both composite wafers.

**2.3. Device Fabrication.** To maintain the structural integrity of a composite substrate, it is of critical importance to limit the maximum temperature that occurs during the multiple processing steps associated with device fabrication. For this reason, a low-temperature device processing scheme was developed that keeps the maximum temperature of the entire process below 600 °C. It should be noted that current growth techniques for other electronic grade WBG and UWBG materials systems such as GaN, SiC, and AlGaN do not allow this.<sup>32–34</sup> Device fabrication began with the epitaxial growth of a Si-doped channel. The composite substrate was solvent cleaned in sonication baths of acetone, isopropyl alcohol, and deionized (DI) water. Next, the substrate was dipped in a hydrofluoric acid solution for 15 min and then cleaned using DI water. After cleaning, the sample was loaded into a metalorganic vapor-phase epitaxy (MOVPE) reactor, and a (010) oriented Si-doped Ga<sub>2</sub>O<sub>3</sub> epilayer (~400 nm thick) was grown at 600 °C.<sup>35</sup> An Agnitron Agilis vertical quartz tube MOVPE reactor was used with triethylgallium (TEGa) and O<sub>2</sub> as the precursor gases, argon as the carrier gas, and diluted silane for doping. From Hall measurements, the room-temperature channel sheet charge and mobility were found to be  $1.3 \times 10^{13}$  cm<sup>-2</sup> and 94 cm<sup>2</sup>/Vs, respectively. Due to the sufficient adatom diffusion lengths at this growth condition (i.e., temperature and molar gas flow fluxes), an atomically smooth surface morphology (RMS roughness of  $\sim 0.5 \pm 0.1$

nm) was maintained, and single-crystal films with high crystalline quality and transport properties were realized. The low-temperature MOVPE growth process helps minimize the potential risk of debonding of the composite wafer due to the thermal expansion mismatch between the Ga<sub>2</sub>O<sub>3</sub> and 4H-SiC materials.<sup>15</sup> A cross-sectional schematic of a Ga<sub>2</sub>O<sub>3</sub> metal-oxide-semiconductor field-effect transistor (MOSFET) fabricated on the composite wafer is shown in Figure 2a. Device processing started with mesa isolation using a patterned Ni/SiO<sub>2</sub> hard mask and directional dry etching using an inductively coupled plasma reactive ion etching (ICP-RIE) with SF<sub>6</sub>-Ar plasma chemistry (600 W ICP, 150 RF powers—45 nm/min etch rate for Ga<sub>2</sub>O<sub>3</sub>).<sup>36,37</sup> This was followed by source-drain region patterning using the same Ni/SiO<sub>2</sub> patterning process and contact region recessing using a low-power ICP-RIE SF<sub>6</sub>-Ar (150 W ICP, 50 RF powers—1.5 nm/min etch rate for Ga<sub>2</sub>O<sub>3</sub>).<sup>38</sup> After selectively wet etching Ni, the sample with the patterned SiO<sub>2</sub> mask was loaded into the MOVPE reactor for ohmic contact regrowth. A heavily Si-doped n+ (estimated  $1.4 \times 10^{20}$  cm<sup>-3</sup>) Ga<sub>2</sub>O<sub>3</sub> layer was grown at 600 °C with an approximate thickness of 100 nm.<sup>37</sup> The sample was then cleaned in an HF solution, and the regrowth mask including regrown Ga<sub>2</sub>O<sub>3</sub> was selectively removed from all regions except the source-drain regions. This was followed by Ohmic metal evaporation of Ti/Au/Ni (20/100/50 nm) on the n+ regions by photolithography and lift-off. The contacts were then annealed in a rapid thermal processing (RTP) furnace at 450 °C for 1.5 min in a N<sub>2</sub> ambient environment. A thermal atomic layer deposition (ALD)-grown Al<sub>2</sub>O<sub>3</sub> layer (at 250 °C) with a target thickness of 25 nm was blanket deposited to form the gate insulator. Then, a Ni/Au/Ni (30/100/30 nm) metal stack was evaporated to form the gate electrode. Finally, the Al<sub>2</sub>O<sub>3</sub> over the source-drain metal pad regions was removed using a photoresist mask and CF<sub>4</sub>-O<sub>2</sub>-N<sub>2</sub> ICP-RIE dry etching. It is to be noted that (apart from benefitting from the low-temperature processes), the composite substrate shows strong ruggedness against the standard device processing steps (such as ultrasonication in solvents, acid cleaning, wet and dry etching, and dielectric/metal deposition), as well as patterning processes. This confirms its compatibility with the standard device processing methods used to fabricate homoepitaxial devices on bulk Ga<sub>2</sub>O<sub>3</sub> wafers.

The device dimensions were verified by top-side SEM imaging (Figure 2b). The L<sub>GS</sub> and L<sub>G</sub> were fixed at ~0.7 nm and ~2.1 μm, respectively, while the L<sub>GD</sub> was varied from ~2.5 to 55 μm. The thickness of the Ga<sub>2</sub>O<sub>3</sub> layer was determined to be ~34 μm using cross-sectional SEM imaging (Figure 2c). From transfer length method (TLM) measurements, the

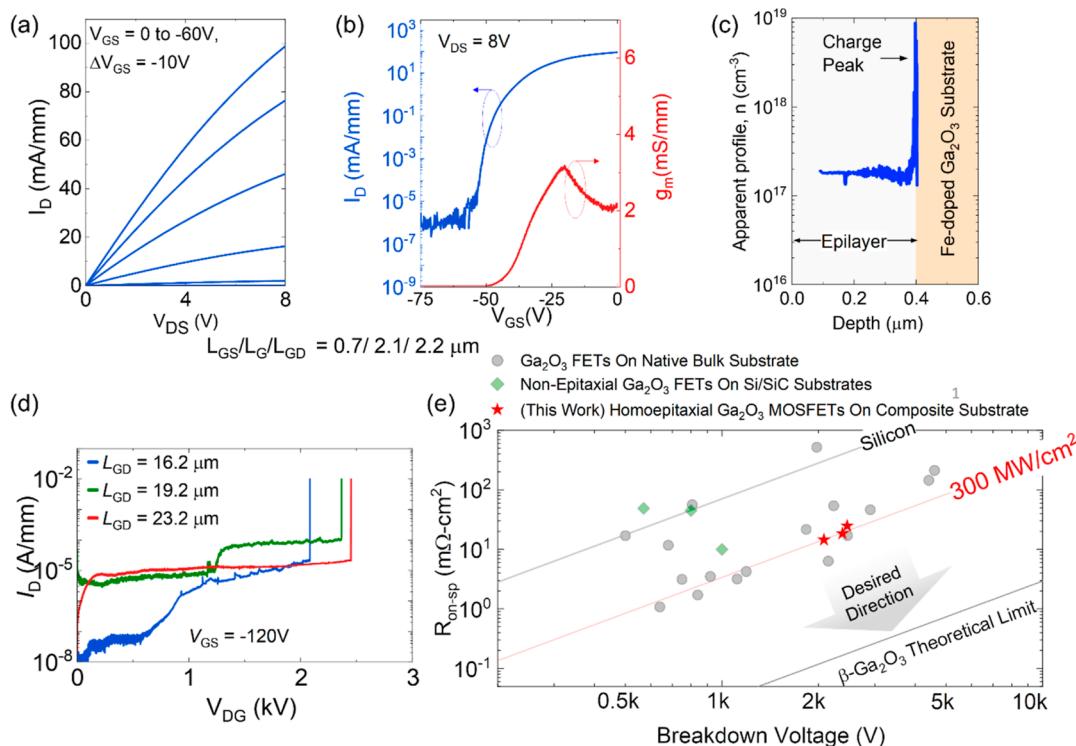

**Figure 3.** (a) DC output and (b) transfer curves of the Ga<sub>2</sub>O<sub>3</sub> MOSFET fabricated on the composite substrate. (c) Channel charge profile extracted from C–V measurements. (d) Off-state breakdown characteristics of the Ga<sub>2</sub>O<sub>3</sub> MOSFETs with various  $L_{GD}$  values. (e) Benchmarking of the MOSFET fabricated on the composite substrate against homoepitaxial Ga<sub>2</sub>O<sub>3</sub> FETs<sup>36–49</sup> and devices fabricated on other bonded substrates<sup>50–52</sup> in the literature.

contact resistance to the channel was determined to be  $\sim 1.6 \pm 0.2 \Omega \cdot \text{mm}$ . Figure 3a,b shows the direct current (DC) output and transfer curves, respectively, for a device with  $L_{GD} \sim 2.5 \mu\text{m}$ . A device with  $L_{GD} \sim 2.5 \mu\text{m}$  exhibits a drain current of  $\sim 100 \text{ mA/mm}$  at a drain–source voltage of 8 V and a gate bias of 0 V. The ON resistance from the linear region of the output curve is  $\sim 65 \Omega \cdot \text{mm}$ . From the transfer curve, the device shows clear pinch-off characteristics, and the ON/OFF ratio is  $\sim 10^8$ . The device showed a large threshold voltage of  $-50$  V, most likely due to the presence of a remnant active parasitic channel at the epilayer/Ga<sub>2</sub>O<sub>3</sub> (of the composite substrate) interface. Figure 3c shows the channel charge profile that is extracted from capacitance–voltage (C–V) measurements. A clear charge peak can be seen at the epilayer–substrate interface, potentially originating from the polishing step used to thin down the bonded Ga<sub>2</sub>O<sub>3</sub> wafer. The magnitude of this parasitic charge was spatially nonuniform across the composite wafer. This is also revealed by the nonuniform threshold (or pinch-off) voltage of transistors fabricated on the composite substrate, which varied from  $-40$  to  $-85$  V. This observation indicates a parasitic charge of  $3\text{--}8 \times 10^{12} \text{ cm}^{-2}$  at the epilayer/composite substrate interface contributing to the total channel charge. Proper surface preparation of the composite substrate (e.g., chemical and plasma treatment) and development of an insulating buffer schemes will be necessary to remove the parasitic charges at the epilayer/Ga<sub>2</sub>O<sub>3</sub> interface.

Device breakdown measurements were performed on the large  $L_{GD}$  devices with the wafer submerged in a dielectric liquid (Fluorinert FC-40). A large negative gate bias of  $-120$  V was applied during breakdown measurements to minimize bulk-related source-to-drain leakage. The breakdown voltages ( $V_{BR}$ ) increased from  $2.08$  to  $2.45$  kV as the  $L_{GD}$  was scaled

from  $16.2$  to  $23.2 \mu\text{m}$  as shown in Figure 3d. The average breakdown field was around  $\sim 1.3 \text{ MV/cm}$ , which is promising given that the devices did not employ any field plates to lower the peak electric field. The specific ON resistance ( $R_{on-sp}$ ; normalized with respect to the device area) values were  $14.5$ ,  $18.4$ , and  $24.8 \text{ m}\Omega \cdot \text{cm}^2$  for devices with  $L_{GD}$  values of  $16.2$ ,  $19.2$  and  $23.2 \mu\text{m}$ , respectively. The respective power figure of merit (PFOM;<sup>53</sup>  $V_{BR}^2/R_{on-sp}$ ) of the devices was  $295 \text{ MW/cm}^2$  ( $V_{BR} = 2.08 \text{ kV}$ ),  $303 \text{ MW/cm}^2$  ( $V_{BR} = 2.37 \text{ kV}$ ), and  $242 \text{ MW/cm}^2$  ( $V_{BR} = 2.45 \text{ kV}$ ). These are the highest  $V_{BR}$  and PFOM values ever reported for Ga<sub>2</sub>O<sub>3</sub> transistors fabricated on heterogeneously integrated substrates.<sup>50–52</sup> Figure 3e benchmarks the  $R_{on-sp}$ – $V_{BR}$  performance of the MOSFETs against values reported in the literature. With a PFOM of  $\sim 300 \text{ MW/cm}^2$ , these devices are better than most state-of-the-art homoepitaxial Ga<sub>2</sub>O<sub>3</sub> devices fabricated on native Ga<sub>2</sub>O<sub>3</sub> substrates and are significantly better than “transferred and non-epitaxial” Ga<sub>2</sub>O<sub>3</sub> transistors on SiC substrates.<sup>50–52</sup> The electrical performance is not compromised by fabricating devices on the composite substrate when using the low-temperature device-processing scheme. Even though this is the first demonstration of “epitaxially grown” Ga<sub>2</sub>O<sub>3</sub> MOSFETs fabricated on a composite substrate, the devices show promising OFF-state voltage-blocking capabilities up to  $2.45 \text{ kV}$  suitable for power electronics applications.

**2.4. Device Thermal Characterization.** Nanoparticle-assisted Raman thermometry<sup>54,55</sup> was used to perform the in situ channel temperature measurement of the MOSFET structures. Anatase TiO<sub>2</sub> nanoparticles of 99.98% purity were deposited on the devices to serve as surface temperature probes. The Stokes Raman peak shift of the  $E_g$  phonon mode was monitored during the device operation to estimate the

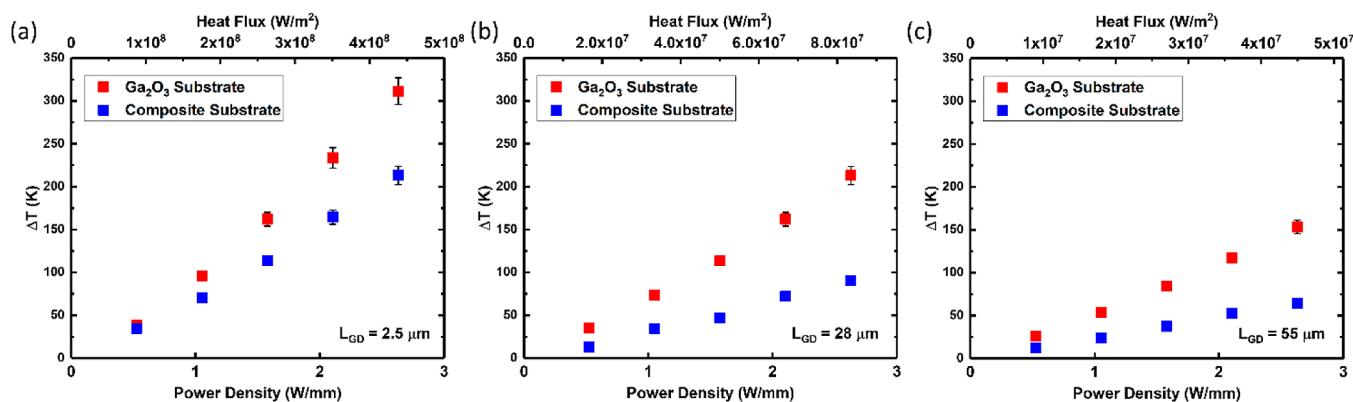

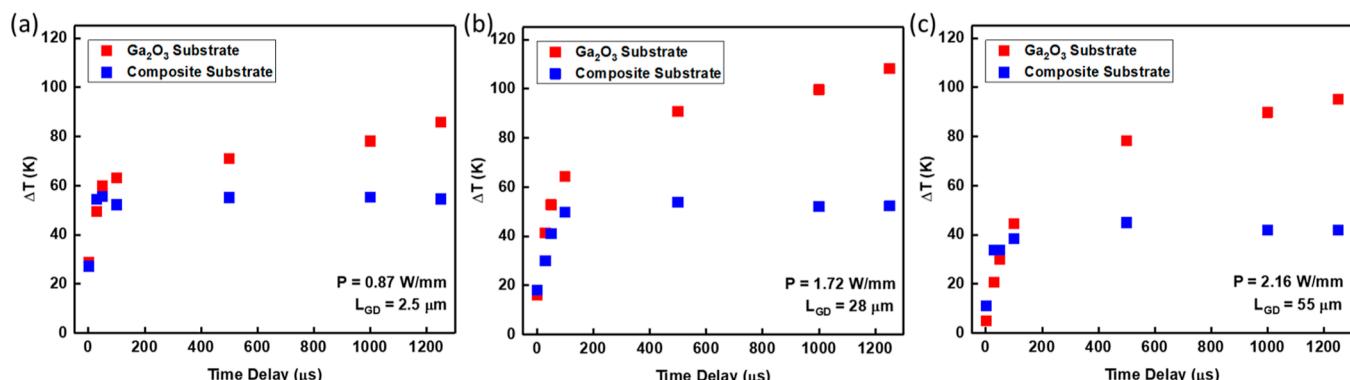

**Figure 4.** Steady-state channel temperature rise of the MOSFETs fabricated on the composite substrate and a bulk  $\text{Ga}_2\text{O}_3$  wafer. Devices with different  $L_{GD}$  values were tested. (a)  $L_{GD} = 2.5 \mu\text{m}$ , (b)  $L_{GD} = 28 \mu\text{m}$ , and (c)  $L_{GD} = 55 \mu\text{m}$ .

**Figure 5.** Transient channel temperature increase of MOSFETs fabricated on native ( $\text{Ga}_2\text{O}_3$ ) and composite substrates. Devices with different  $L_{GD}$  values were tested. (a)  $L_{GD} = 2.5 \mu\text{m}$ , (b)  $L_{GD} = 28 \mu\text{m}$ , and (c)  $L_{GD} = 55 \mu\text{m}$ .

channel temperature rise. Measurements were taken on nanoparticles close to the drain side edge of the gate, where the channel peak temperature is expected to occur due to electric field and Joule heat concentrations. Measurements were performed on devices with different dimensions ( $L_{GD}$  of  $\sim 2.2$ ,  $28$ , and  $55 \mu\text{m}$ ) fabricated on both the composite wafer and a native  $\text{Ga}_2\text{O}_3$  substrate. Figure 4 shows the steady-state temperature rise ( $\Delta T$ ) as a function of power density and the corresponding heat flux values. When comparing the temperature rise for devices with different  $L_{GD}$ , it is important to consider the heat flux since the area where Joule heating occurs is changing. Therefore, a device with a larger  $L_{GD}$  will experience a lower temperature rise for a given power density. It should be noted that the devices on the composite and native substrates exhibited similar power densities for particular drain voltages ( $V_{ds}$ ). Due to the enhanced heat transfer performance of the composite substrate, a significant reduction in channel temperature rise (up to a  $2.4\times$  reduction) was observed for devices (especially those with larger  $L_{GD}$ ) operating under a power density of  $2.63 \text{ W/mm}$ .

The transient channel temperature rise of the devices was characterized to understand the cooling effectiveness of the composite substrate under high-frequency switching operation. A transient Raman thermometry setup (details can be found in the Experimental Section) was used to monitor the channel temperature rise in response to a square electrical power pulse with a temporal resolution of  $25 \mu\text{s}$ .<sup>54,55</sup> As shown in Figure 5, the early-stage temperature increase ( $<100 \mu\text{s}$ ) is similar between the homoepitaxial and composite substrate; this is

because of the low thermal diffusivity (or slow transient thermal response) of  $\text{Ga}_2\text{O}_3$ , causing the heating to be restricted within the  $\sim 34 \mu\text{m}$  thick  $\text{Ga}_2\text{O}_3$  layer for both devices fabricated on the composite wafer and a native substrate. A lower temperature rise is observed for the devices on the composite wafer only after  $100 \mu\text{s}$ , from which the high thermal conductivity of 4H-SiC contributes to spreading the heat away from the device active region.<sup>3</sup> Data in Figure 5 indicate that the channel temperature of the devices on the composite substrate reaches steady state after  $200\text{--}300 \mu\text{s}$ , while the temperatures of the devices on a  $\text{Ga}_2\text{O}_3$  substrate continue to increase. In contrast to previously developed diamond integration methods for GaN HEMTs,<sup>18,56-59</sup> the low thermal diffusivity of  $\text{Ga}_2\text{O}_3$  renders a more in-depth thermal design process required for the development of  $\text{Ga}_2\text{O}_3$  devices on a composite wafer. For our current design, the thickness of the  $\text{Ga}_2\text{O}_3$  layer of the composite substrate is far larger than  $\sim 10 \mu\text{m}$  (recommended by Chatterjee et al.<sup>12</sup>), which is necessary to reduce the device thermal resistance less than that of a GaN-on-Si power switch. Therefore, 3D modeling was performed in the next section to further discuss the transient thermal response and its implications on design optimization.

**2.5. Modeling and Design Optimization.** In order to verify the results of the nanoparticle-assisted Raman thermometry measurements, a 3D transient electro-thermal model was constructed.<sup>12,19</sup> The (010)  $\text{Ga}_2\text{O}_3$  layer was modeled to be  $34.6 \mu\text{m}$  based on the SEM results, and a directional and temperature-dependent thermal conductivity

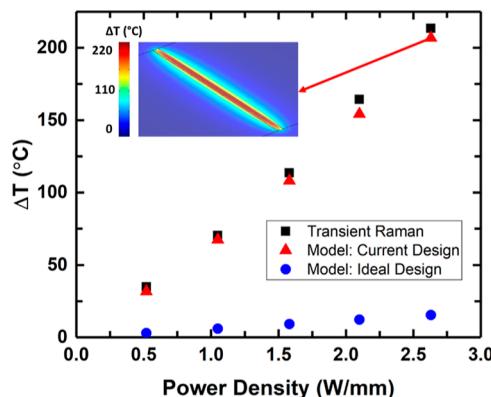

was employed from values published by Guo et al.<sup>6</sup> The 4H–SiC substrate layer was modeled to be 500  $\mu\text{m}$  thick, and a temperature-dependent thermal conductivity was adopted from Wei et al.<sup>10</sup> An effective TBR of 47.1  $\text{m}^2\text{K}/\text{GW}$ <sup>15</sup> was applied at the  $\text{Ga}_2\text{O}_3/\text{SiC}$  interface based on SSTR measurement results. First, the device detailed in Section 2.2 ( $L_{\text{GD}} \sim 2.5 \mu\text{m}$ ) was modeled under steady-state conditions matching the operating conditions used in the nanoparticle Raman experiments listed in Figure 4a. Figure 6 shows the modeling

**Figure 6.** Comparison of results (channel temperature rise) from the Raman experiments and simulation for the fabricated  $\text{Ga}_2\text{O}_3$ -on-SiC MOSFET and an “ideal” device.

results, which are in excellent agreement with the temperatures measured via the Raman thermometry experiments. The composite wafer is shown to reduce the device peak temperature during operation; however, the thermal performance can be further enhanced by reducing the  $\text{Ga}_2\text{O}_3$  layer thickness, improving phonon transport across the interface, and using a higher thermal conductivity substrate instead of 4H–SiC. Therefore, a second model was built to assess the theoretical performance limit by using such an “ideal” composite wafer. This ideal model assumes a reduced  $\text{Ga}_2\text{O}_3$  thickness of 1  $\mu\text{m}$  (which consists of 200 nm from ion-cutting,<sup>29</sup> 300 nm from a back barrier, and 500 nm for the channel) and a single-crystalline diamond substrate.<sup>60</sup> An effective TBR of 7.8  $\text{m}^2\text{K}/\text{GW}$  was assumed between the  $\text{Ga}_2\text{O}_3$  and the diamond substrate based on the TBC for using 10 nm  $\text{Al}_2\text{O}_3$  as the bonding interlayer.<sup>29</sup> This ideal case showed a significant reduction in channel temperature rise ( $\sim 10\times$ ) as compared to the current composite wafer design, suggesting the potential for further enhancement in the cooling performance with optimization.

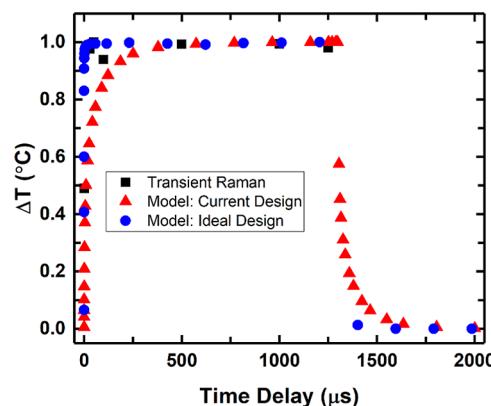

As previously mentioned, a composite wafer must be designed so that high cooling performance is offered under high-frequency switching operation. Transient thermal models for both the current design and the ideal case were constructed, with a device ON (power) square pulse of a 1.3 ms period and a 10% duty cycle (to match the transient Raman thermometry experiments). Figure 7 shows the normalized transient response for the measured and simulated responses for the current design and the ideal case. A power density of 0.87 W/mm was used in this study for both simulation and experiments. Due to the relatively large thickness ( $\sim 35 \mu\text{m}$ ) of the  $\text{Ga}_2\text{O}_3$  layer, the current design took  $\sim 300 \mu\text{s}$  to reach a quasi-steady-state temperature, while this took only  $\sim 4 \mu\text{s}$  for the ideal case. In other words, the current design only offers its full cooling performance for switching frequencies less than  $\sim 3$

**Figure 7.** Transient thermal response for the current  $\text{Ga}_2\text{O}_3$ -on-SiC device (measured via Raman thermometry and simulated) and an “ideal” device. The temperature is normalized based on their respective quasi steady-state temperatures ( $\sim 55^\circ\text{C}$  for the current design and  $\sim 6^\circ\text{C}$  for the ideal design).

kHz, while the ideal case is effective for frequencies up to  $\sim 250$  kHz. This switching frequency limit can be further increased by the implementation of top-side cooling solutions such as a diamond passivation overlayer<sup>61</sup> and flip-chipping.<sup>62</sup>

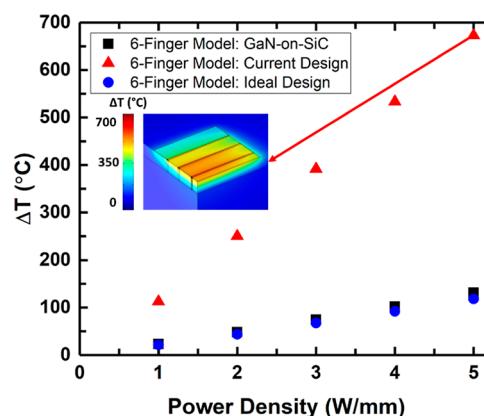

A recent computational study<sup>15</sup> has predicted that practical multi-finger devices would experience significantly aggravated self-heating (a  $4\times$  higher channel temperature than single-finger  $\text{Ga}_2\text{O}_3$  devices under identical power density conditions) due to the thermal cross-talk<sup>16</sup> among adjacent current channels. This trend has been experimentally confirmed by an experimental study<sup>17</sup> on multichannel  $\text{Ga}_2\text{O}_3$  FinFETs. Therefore, multi(6)-finger device structures were simulated for both the current  $\text{Ga}_2\text{O}_3/\text{SiC}$  composite wafer and an ideal case as detailed earlier. Further details of the electrically aware thermal model can be found in our previous work.<sup>62</sup> In Figure 8, the temperature results can be found for both aforemen-

**Figure 8.** Comparison of the temperature rise of the real and ideal 6-finger devices.

tioned single- and multi (6)-finger  $\text{Ga}_2\text{O}_3$  cases, in addition to that for a commercial multi-finger GaN-on-SiC device (details of the device geometry can be found in ref 62). Due to the thermal cross-talk between the channels, the temperature rise is greater than that of a single-channel device (by comparing with results in Figures 6 and 8). A significant reduction in the channel temperature of  $\sim 8\times$  is seen in the ideal multi-finger

case, giving promise to lower the device thermal resistance below that for today's commercial GaN-on-SiC transistors.<sup>62</sup>

### 3. CONCLUSIONS

This work reports the fabrication of UWBG  $\text{Ga}_2\text{O}_3$  power MOSFETs on a  $\text{Ga}_2\text{O}_3/4\text{H}-\text{SiC}$  composite wafer with simultaneous enhancement in the electrical and thermal performance. Low-temperature ( $\leq 600$  °C) epitaxy and device fabrication processes were developed to preserve the structural integrity of the composite substrate. This enabled the first realization of (010)-oriented "homoepitaxial"  $\text{Ga}_2\text{O}_3$  MOSFETs fabricated on a  $\text{Ga}_2\text{O}_3/4\text{H}-\text{SiC}$  composite substrate. The epitaxial  $\text{Ga}_2\text{O}_3$ -on-SiC MOSFETs exhibit a record high  $V_{\text{BR}}$  (of up to 2.45 kV) and PFOM ( $\sim 300$  MW/cm<sup>2</sup>), both of which are the highest among  $\text{Ga}_2\text{O}_3$  FETs constructed on a heterogeneously integrated substrate to date. Under DC operation, a significant reduction in the channel temperature was achieved for the MOSFETs fabricated on the composite wafer as compared to devices homoepitaxially grown on a native  $\text{Ga}_2\text{O}_3$  substrate. The experimentally measured temperature rise was validated by a 3D FEA electro-thermal model. Transient thermal analysis suggests that the cooling performance of an unoptimized composite wafer will be limited under high-frequency switching operation. The theoretical cooling limit of using a hypothetical  $\text{Ga}_2\text{O}_3$ /diamond composite substrate with ideal heat transfer performance was assessed by modeling. A 10× improvement in thermal performance can be achieved by reducing the  $\text{Ga}_2\text{O}_3$  layer thickness (to  $\sim 1$   $\mu\text{m}$ ) and lowering the TBR at the  $\text{Ga}_2\text{O}_3$ /diamond interface ( $\sim 7.8$  m<sup>2</sup>K/GW). This work provides key guidelines for the fabrication and realization of high-power UWBG devices on a composite wafer that will enable surpassing the thermal limit of next-generation  $\text{Ga}_2\text{O}_3$  power electronics.

**3.1. Methods.** *3.1.1. Focused Ion Beam/Scanning Electron Microscopy.* Plan view and cross-sectional SEM imaging was performed using a Helios NanoLab 650 Dual-Beam system with FIB milling capabilities with samples under vacuum. For plan view imaging, the samples were imaged with the electron beam perpendicular to the sample surface at low currents with acceleration voltages of 2–5 kV. For cross-sectional imaging, Ga ion current milling with a Pt protective capping layer was used to create craters up to 50  $\mu\text{m}$  deep. Ion current levels of up to 1 nA were used. For charge dissipation, an Omiprobe probing system was used to probe the metal contacts of the isolated  $\text{Ga}_2\text{O}_3$  MOSFETs.

*3.1.2. Scanning Transmission Electron Microscopy.* STEM samples were prepared via FIB milling using a ThermoFisher Helios dual-beam FIB system. To prepare a clean and thin specimen, the surface of the STEM foil was cleaned using low-energy ion milling (Fischione Nanomill) operated at 500 eV. High-angle annular dark field (HAADF) STEM imaging was performed using a ThermoFisher aberration-corrected Titan STEM microscope with probe convergence half angles of 10.03 mrad at an accelerating voltage of 300 kV. The microscope is also equipped with a ChemiSTEM EDX system, which allows for the characterization of the composition of the cross-sectional STEM sample. Five chemical species (Ga, Si, O, C, and N) at the interface were analyzed by the EDX elemental mapping. The bonding layer (including  $\text{SiN}_x$ ) total thickness of 40 nm was determined at the interface region. Due to the inhomogeneity of the lattice mismatch between the  $\text{Ga}_2\text{O}_3$  thin films and 4H-SiC substrate, the  $\text{SiN}_x$  bonding interface was marginally delaminated, resulting in the oxidation layer of 10

nm  $\text{SiO}_x$  within the  $\text{SiN}_x$  interfacial region. The elemental profile further demonstrated the distribution of O based on the cross-section STEM-EDX measurements.

**3.1.3. Raman Thermometry.** Raman thermometry is a temperature measurement technique that uses Raman spectroscopy, which employs monochromatic photonic excitation (typically in the visible wavelength regime) to interrogate the energy or frequency of crystal lattice vibration (i.e., phonons). The temperature effect on a phonon can be observed in the Raman spectra through peak position shifts, peak broadening (or linewidth), and changes in the ratio of anti-Stokes/Stokes Raman peak intensity.<sup>63,64</sup> Among these three ways, the peak position-based temperature measurement offers a higher measurement sensitivity with a low uncertainty and shorter measurement times. However, this method can lead to inaccuracies due to its sensitivity to both temperature and mechanical stress. Moreover, this measurement technique only provides the depth-averaged temperature information for UWBG semiconductors such as  $\text{Ga}_2\text{O}_3$ .

In this study, both steady-state and transient Raman thermometry were performed using a Horiba LabRAM HR Evolution spectrometer with a 532 nm excitation laser. A long working distance 50× objective (NA = 0.45) was used in a 180° backscattering configuration. A nanoparticle-assisted Raman thermometry technique<sup>65</sup> was used to measure the surface temperature of the channel region of the  $\text{Ga}_2\text{O}_3$  MOSFETs. Anatase titanium dioxide ( $\text{TiO}_2$ ) nanoparticles with 99.98% purity were deposited on the device surface.<sup>65</sup> As the nanoparticle remains in thermal equilibrium with the device surface, the temperature-dependent frequency shift of the  $E_g$  phonon mode was monitored to determine the device channel temperature. Since the nanoparticle can expand freely, the mechanical stress effect on the Raman peak position is negligible and does not affect the temperature measurement results. The spatial resolution is determined by the size of the  $\text{TiO}_2$  nanoparticles ( $\sim 200$  nm).

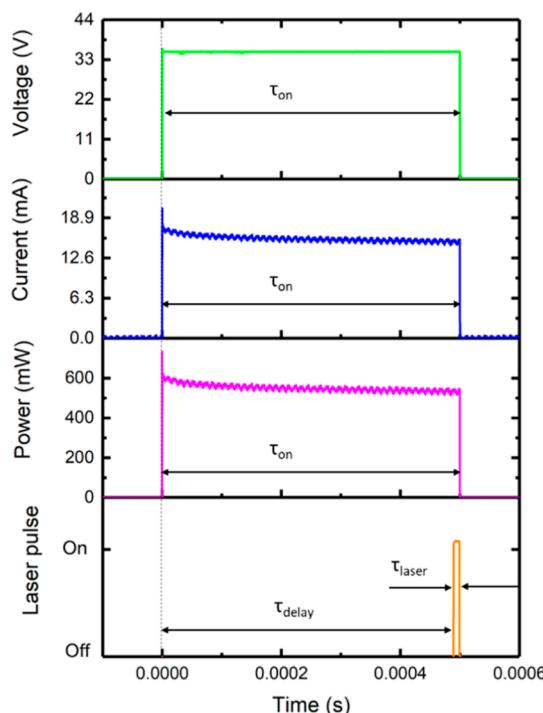

By augmenting the standard Raman microscope with a function generator, a delay generator, a trigger switch, and an oscilloscope, a setup for transient temperature measurement was constructed.<sup>66</sup> This transient setup uses a lock-in modulation scheme in which electrical and laser pulse trains are synchronized, and the Raman signal accumulates over many periods. A full transient thermal response is constructed by controlling/sweeping the laser pulse delay time ( $\tau_{\text{delay}}$ ) along the entire device electrical ( $V_{\text{DS}}$ ) pulse width ( $\tau_{\text{on}}$ ). An exemplary temporal schematic of the transient measurement is shown in Figure 9. In this example, a  $V_{\text{DS}}$  of  $\sim 35$  V (i.e., electric pulse) is applied to achieve a power dissipation level of  $\sim 0.5$  W while the device is ON. The laser pulse is active at the very end of the electrical pulse. A digital delay generator controls the time delay ( $\tau_{\text{delay}}$ ) between the electrical and laser pulses in order to monitor the transient self-heating behavior of the device in response to a square electrical pulse with a 10% duty cycle. Here, the device pulse width ( $\tau_{\text{on}}$ ) is 1.3 ms and the laser pulse width ( $\tau_{\text{laser}}$ ) is 25  $\mu\text{s}$ . A temporal resolution up to  $\sim 20$  ns can be achieved using our experimental setup. The synchronization and operation of the transient measurements were controlled using a LabVIEW program. To maximize the signal-to-noise ratio of the Raman signals, an electron-multiplying charge-coupled device (EMCCD) was used during the measurements.

**3.1.4. Thermophysical Property Measurement.** SSTR is a laser-based pump–probe technique, which is ideal to measure

**Figure 9.** Typical synchronized pulsing scheme used during transient Raman thermometry measurements.

the thermal conductivity of bulk materials.<sup>24</sup> Details of the SSTR setup used in this study are described in our previous work.<sup>15</sup> The pump and probe lasers were focused on the samples using the following microscope objectives: (i) a 2.5 $\times$  objective (NA = 0.08) with pump and probe laser radii of 19.4 and 12.4  $\mu\text{m}$ , respectively, and (ii) a 10 $\times$  objective (NA = 0.25) with pump and probe laser radii of 5 and 4.3  $\mu\text{m}$ , respectively. The thermal conductivity of the  $\text{Ga}_2\text{O}_3$  layer of the composite substrate was measured using a 10 $\times$  objective to confine the probing volume within the  $\text{Ga}_2\text{O}_3$  layer. The TBR at the interface was derived by performing measurement using a 2.5 $\times$  objective and fitting the data based on the measured thermal conductivity values of  $\text{Ga}_2\text{O}_3$  and 4H-SiC.

TDTR is an optical pump–probe technique that allows the extraction of thermal properties of thin films based on heat diffusion in response to ultrafast femtosecond laser pulses.<sup>25,26</sup> Details of the TDTR setup used in this study are described in our previous work.<sup>15</sup> The radii of the focused pump and probe beams were characterized using a scanning-slit optical beam profiler, and their radii were determined to be 8.4 and 6  $\mu\text{m}$ , respectively. TDTR (and FDTR) measurements were performed on a wedge-shaped thinned  $\text{Ga}_2\text{O}_3$  composite substrate to determine the TBR at the  $\text{Ga}_2\text{O}_3$ /4H-SiC interface. The thermal boundary conductance between the metal transducer and the  $\text{Ga}_2\text{O}_3$  film and between the cross-plane thermal conductivity of  $\text{Ga}_2\text{O}_3$  were simultaneously determined by TDTR measurements. To fit the acquired data, literature values for the thermal conductivity and volumetric heat capacity of Au<sup>67</sup> as well as the volumetric heat capacities of  $\text{Ga}_2\text{O}_3$ <sup>68</sup> and 4H-SiC<sup>69</sup> were assumed. The uncertainties in data were calculated based on 95% confidence bounds resulting from multiple measurements; error propagation associated with  $\pm 2$  nm uncertainty in the metal transducer thickness has also been accounted for.

FDTR is an optical pump–probe technique that measures material thermal properties based on fitting the phase of the thermal wave over a range of modulation frequencies.<sup>27,28</sup> Details of the FDTR setup used in this study are described in our previous work.<sup>15</sup> The radii of the focused pump and probe beams were 13.4 and 13.1  $\mu\text{m}$ , respectively. Material properties used to postprocess the FDTR raw data were identical to those used in the analytical model for TDTR experiments. The  $\text{Ga}_2\text{O}_3$  thermal conductivity (from TDTR measurements) and the 4H-SiC thermal conductivity (determined by SSTR) of the wedge-shaped thinned composite substrate were used as known parameters to extract the TBR between the  $\text{Ga}_2\text{O}_3$  layer and 4H-SiC substrate.

**3.1.5. Device Modeling.**  $\text{Ga}_2\text{O}_3$  device models were constructed using a 3D electro-thermal modeling scheme that has been demonstrated in our previous work.<sup>12,19</sup> A 2D electro-hydrodynamic model that adopts carrier mobility and Ohmic contact resistance determined from experiments is created so that it reproduces the device output/transfer characteristics. This electrical model calculates the internal heat generation profile as a function of electrical bias. The 2D Joule heat distribution is projected along the channel width so that a 3D volumetric heat generation profile is obtained. This 3D heat generation profile is imported into a 3D finite element transient thermal model. The  $\text{Ga}_2\text{O}_3$  and 4H-SiC thermal conductivities determined from experiments are employed in the thermal model. Interfacial phonon transport across the  $\text{Ga}_2\text{O}_3$ /4H-SiC interface is captured in the model by adopting the TBR values determined by experiments.

## ■ AUTHOR INFORMATION

### Corresponding Authors

**Sriram Krishnamoorthy** – Materials Department, University of California, Santa Barbara, California 93106, United States;  [orcid.org/0000-0002-4682-1002](https://orcid.org/0000-0002-4682-1002); Email: [sriramkrishnamoorthy@ucsb.edu](mailto:sriramkrishnamoorthy@ucsb.edu)

**Sukwon Choi** – Department of Mechanical Engineering, The Pennsylvania State University, University Park, Pennsylvania 16802, United States;  [orcid.org/0000-0002-3664-1542](https://orcid.org/0000-0002-3664-1542); Email: [sukwon.choi@psu.edu](mailto:sukwon.choi@psu.edu)

### Authors

**Yiwen Song** – Department of Mechanical Engineering, The Pennsylvania State University, University Park, Pennsylvania 16802, United States

**Arkka Bhattacharyya** – Department of Electrical and Computer Engineering, University of Utah, Salt Lake City, Utah 84112, United States

**Anwarul Karim** – Department of Mechanical Engineering, The Pennsylvania State University, University Park, Pennsylvania 16802, United States

**Daniel Shoemaker** – Department of Mechanical Engineering, The Pennsylvania State University, University Park, Pennsylvania 16802, United States

**Hsien-Lien Huang** – Department of Materials Science and Engineering, The Ohio State University, Columbus, Ohio 43210, United States

**Saurav Roy** – Materials Department, University of California, Santa Barbara, California 93106, United States

**Craig McGraw** – Modern Microsystems, Gaithersburg, Maryland 20878, United States;  [orcid.org/0000-0002-4613-1925](https://orcid.org/0000-0002-4613-1925)

Jacob H. Leach — Kyma Technologies, Inc., Raleigh, North Carolina 27617, United States

Jinwoo Hwang — Department of Materials Science and Engineering, The Ohio State University, Columbus, Ohio 43210, United States

Complete contact information is available at:

<https://pubs.acs.org/10.1021/acsami.2c21048>

### Author Contributions

Y.S. and A.B. have equally contributed to this work as co-first authors. S.C. and S.K. are co-corresponding authors of this work. Y.S. performed thermophysical property measurement and led the writing of the manuscript. A.B. and S.R. fabricated the  $\text{Ga}_2\text{O}_3$  MOSFET. A.B. contributed to writing the manuscript. A.K. performed optical thermometry. D.S. created the device thermal model and performed computational analysis. H-L.H. and J.H. performed electron microscopy studies. C.M. and J.H.L. fabricated the composite substrate. S.K. directed device fabrication and electrical characterization efforts in this work. S.C. managed the entire project, designed experiments and computational studies, and wrote the manuscript. All authors have given approval to the final version of the manuscript.

### Notes

The authors declare no competing financial interest.

### ACKNOWLEDGMENTS

Funding for efforts by Y.S. and S.C. was provided by NSF (CBET-1934482, Program Director: Dr. Ying Sun) and the Air Force Office of Scientific Research (AFOSR) Young Investigator Program (FA9550-17-1-0141, Program Officers: Dr. Brett Pokines and Dr. Michael Kendra, also monitored by Dr. Kenneth Goretta). A.B. and S.K. were supported by the II-VI Foundation's Block Gift Program and AFOSR (FA9550-21-0078, Program Officer: Dr. Ali Sayir). This work was performed in part at the Utah Nanofab sponsored by the College of Engineering and the Office of the Vice President for Research. A.B. and S.K. thank Dr. Randy Polson at the Electron Microscopy and Surface Analysis Lab (EMSAL), University of Utah for the FIB/SEM measurements and analysis used in this work. H.H. and J.H. acknowledge support by the AFOSR (FA9550-18-1-0479, Program Officer: Dr. Ali Sayir). Electron microscopy was performed in the Center for Electron Microscopy and Analysis (CEMAS) at The Ohio State university.

### REFERENCES

- (1) Higashiwaki, M.  $\beta$ -Gallium Oxide Devices: Progress and Outlook. *Phys. status solidi — Rapid Res. Lett.* **2021**, *15*, 2100357.

- (2) Green, A. J.; Speck, J.; Xing, G.; Moens, P.; Allerstam, F.; Gummelius, K.; Neyer, T.; Arias-Purdue, A.; Mehrotra, V.; Kuramata, A.; Sasaki, K.; Watanabe, S.; Koshi, K.; Blevins, J.; Bierwagen, O.; Krishnamoorthy, S.; Leedy, K.; Arehart, A. R.; Neal, A. T.; Mou, S.; Ringel, S. A.; Kumar, A.; Sharma, A.; Ghosh, K.; Singisetti, U.; Li, W.; Chabak, K.; Liddy, K.; Islam, A.; Rajan, S.; Graham, S.; Choi, S.; Cheng, Z.; Higashiwaki, M.  $\beta$ -Gallium oxide power electronics. *APL Mater.* **2022**, *10*, 029201.

- (3) Higashiwaki, M.; Jessen, G. H. Guest Editorial: The Dawn of Gallium Oxide Microelectronics. *Appl. Phys. Lett.* **2018**, *112*, 060401.

- (4) Tsao, J. Y.; Chowdhury, S.; Hollis, M. A.; Jena, D.; Johnson, N. M.; Jones, K. A.; Kaplar, R. J.; Rajan, S.; Van de Walle, C. G.; Bellotti, E.; Chua, C. L.; Collazo, R.; Coltrin, M. E.; Cooper, J. A.; Evans, K. R.; Graham, S.; Grotjohn, T. A.; Heller, E. R.; Higashiwaki, M.; Islam, M. S.; Juodawlkis, P. W.; Khan, M. A.; Koehler, A. D.; Leach, J. H.; Mishra, U. K.; Nemanich, R. J.; Pilawa-Podgurski, R. C. N.; Shealy, J. B.; Sitar, Z.; Tadjer, M. J.; Witulski, A. F.; Wraback, M.; Simmons, J. A. Ultrawide-Bandgap Semiconductors: Research Opportunities and Challenges. *Adv. Electron. Mater.* **2018**, *4*, 1600501.

- (5) Choi, S.; Graham, S.; Chowdhury, S.; Heller, E. R.; Tadjer, M. J.; Moreno, G.; Narumanchi, S. A Perspective on the Electro-Termal Co-Design of Ultra-Wide Bandgap Lateral Devices. *Appl. Phys. Lett.* **2021**, *119*, 170501.

- (6) Guo, Z.; Verma, A.; Wu, X.; Sun, F.; Hickman, A.; Masui, T.; Kuramata, A.; Higashiwaki, M.; Jena, D.; Luo, T. Anisotropic thermal conductivity in single crystal  $\beta$ -gallium oxide. *Appl. Phys. Lett.* **2015**, *106*, 111909.

- (7) Jiang, P.; Qian, X.; Li, X.; Yang, R. Three-dimensional anisotropic thermal conductivity tensor of single crystalline  $\beta$ - $\text{Ga}_2\text{O}_3$ . *Appl. Phys. Lett.* **2018**, *113*, 232105.

- (8) Beechem, T. E.; McDonald, A. E.; Fuller, E. J.; Talin, A. A.; Rost, C. M.; Maria, J.-P.; Gaskins, J. T.; Hopkins, P. E.; Allerman, A. A. Size Dictated Thermal Conductivity of GaN. *J. Appl. Phys.* **2016**, *120*, 095104.

- (9) Song, Y.; Lundh, J. S.; Wang, W.; Leach, J. H.; Eichfeld, D.; Krishnan, A.; Perez, C.; Ji, D.; Borman, T.; Ferri, K.; Maria, J.-P.; Chowdhury, S.; Ryou, J.-H.; Foley, B. M.; Choi, S. The Doping Dependence of the Thermal Conductivity of Bulk Gallium Nitride Substrates. *J. Electron. Packag.* **2020**, *142* (4), No. 041112.

- (10) Wei, R.; Song, S.; Yang, K.; Cui, Y.; Peng, Y.; Chen, X.; Hu, X.; Xu, X. Thermal Conductivity of 4H-SiC Single Crystals. *J. Appl. Phys.* **2013**, *113*, 053503.

- (11) Qian, X.; Jiang, P.; Yang, R. Anisotropic Thermal Conductivity of 4H and 6H Silicon Carbide Measured Using Time-Domain Thermoreflectance. *Mater. Today Phys.* **2017**, *3*, 70–75.

- (12) Chatterjee, B.; Zeng, K.; Nordquist, C. D.; Singisetti, U.; Choi, S. Device-Level Thermal Management of Gallium Oxide Field-Effect Transistors. *IEEE Trans. Components, Packag. Manuf. Technol.* **2019**, *9*, 2352–2365.

- (13) Chatterjee, B.; Song, Y.; Lundh, J. S. J. S.; Zhang, Y.; Xia, Z.; Islam, Z.; Leach, J.; McGraw, C.; Ranga, P.; Krishnamoorthy, S.; Haque, A.; Rajan, S.; Choi, S. Electro-thermal co-design of  $\beta$ -(Al<sub>x</sub>Ga<sub>1-x</sub>)<sub>2</sub>O<sub>3</sub>/Ga<sub>2</sub>O<sub>3</sub> modulation doped field effect transistors. *Appl. Phys. Lett.* **2020**, *117*, 153501.

- (14) Lundh, J. S.; Shoemaker, D.; Birdwell, A. G.; Weil, J. D.; De La Cruz, L. M.; Shah, P. B.; Crawford, K. G.; Ivanov, T. G.; Wong, H. Y.; Choi, S. Thermal Performance of Diamond Field-Effect Transistors. *Appl. Phys. Lett.* **2021**, *119*, 143502.

- (15) Song, Y.; Shoemaker, D.; Leach, J. H.; McGraw, C.; Huang, H.-L.; Bhattacharyya, A.; Zhang, Y.; Gonzalez-Valle, C. U.; Hess, T.; Zhukovsky, S.; Ferri, K.; Lavelle, R. M.; Perez, C.; Snyder, D. W.; Maria, J.-P.; Ramos-Alvarado, B.; Wang, X.; Krishnamoorthy, S.; Hwang, J.; Foley, B. M.; Choi, S. Ga<sub>2</sub>O<sub>3</sub>-on-SiC Composite Wafer for Thermal Management of Ultrawide Bandgap Electronics. *ACS Appl. Mater. Interfaces* **2021**, *13*, 40817–40829.

- (16) Manoi, A.; Pomeroy, J. W.; Lossy, R.; Pazirandeh, R.; Würfl, J.; Uren, M. J.; Martin, T.; Kuball, M. Time-Dependent Thermal Crosstalk in Multifinger AlGaN/GaN HEMTs and Implications on Their Electrical Performance. *Solid. State. Electron.* **2011**, *57*, 14–18.

- (17) Chatterjee, B.; Li, W.; Nomoto, K.; Xing, H. G.; Choi, S. Thermal Design of Multi-Fin Ga<sub>2</sub>O<sub>3</sub> Vertical Transistors. *Appl. Phys. Lett.* **2021**, *119*, 103502.

- (18) Bar-Cohen, A.; Maurer, J. J.; Altman, D. H. Embedded Cooling for Wide Bandgap Power Amplifiers: A Review. *J. Electron. Packag.* **2019**, *141* (4), No. 040803.

- (19) Kim, S. H.; Shoemaker, D.; Chatterjee, B.; Green, A. J.; Chabak, K. D.; Heller, E. R.; Liddy, K. J.; Jessen, G. H.; Graham, S.; Choi, S. Thermally-Aware Layout Design of  $\beta$ - $\text{Ga}_2\text{O}_3$  Lateral MOSFETs. *IEEE Trans. Electron Devices* **2022**, *69*, 1251–1257.

- (20) Bower, R. W.; Ismail, M. S.; Roberds, B. E. Low temperature Si<sub>3</sub>N<sub>4</sub>direct bonding. *Appl. Phys. Lett.* **1993**, *62*, 3485–3487.

- (21) Reck, K.; Østergaard, C.; Thomsen, E. V.; Hansen, O. Fusion Bonding of Silicon Nitride Surfaces. *J. Micromechanics Microengineering* **2011**, *21*, 5015.

(22) Nepal, N.; Katzer, D. S.; Downey, B. P.; Wheeler, V. D.; Nyakiti, L. O.; Storm, D. F.; Hardy, M. T.; Freitas, J. A.; Jin, E. N.; Vaca, D.; Yates, L.; Graham, S.; Kumar, S.; Meyer, D. J. Heteroepitaxial Growth of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> Films on SiC via Molecular Beam Epitaxy. *J. Vac. Sci. Technol. A* **2020**, *38*, 063406.

(23) Tong, Q.-Y.; Gosele, U. *SemiConductor Wafer Bonding: Science and Technology*. John Wiley Sons, Inc., 1999. 28, pp 215–241

(24) Braun, J. L.; Olson, D. H.; Gaskins, J. T.; Hopkins, P. E.; Olson, D. H.; Gaskins, J. T. A Steady-State Thermoreflectance Method to Measure Thermal Conductivity. *Rev. Sci. Instrum.* **2019**, *90*, 024905.

(25) Schmidt, A. J.; Chen, X.; Chen, G. Pulse Accumulation, Radial Heat Conduction, and Anisotropic Thermal Conductivity in Pump-Probe Transient Thermoreflectance. *Rev. Sci. Instrum.* **2008**, *79*, 114902.

(26) Cahill, D. G. Analysis of Heat Flow in Layered Structures for Time-Domain Thermoreflectance. *Rev. Sci. Instrum.* **2004**, *75*, 5119–5122.

(27) Schmidt, A. J.; Cheaito, R.; Chiesa, M. A Frequency-Domain Thermoreflectance Method for the Characterization of Thermal Properties. *Rev. Sci. Instrum.* **2009**, *80*, 094901.

(28) Yang, J.; Maragliano, C.; Schmidt, A. J. Thermal Property Microscopy with Frequency Domain Thermoreflectance. *Rev. Sci. Instrum.* **2013**, *84*, 4143.

(29) Cheng, Z.; Mu, F.; You, T.; Xu, W.; Shi, J.; Liao, M. E.; Wang, Y.; Huynh, K.; Suga, T.; Goorsky, M. S.; Ou, X.; Graham, S. Thermal Transport across Ion-Cut Monocrystalline  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> Thin Films and Bonded  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>–SiC Interfaces. *ACS Appl. Mater. Interfaces* **2020**, *12*, 44943–44951.

(30) Sun, H.; Simon, R. B.; Pomeroy, J. W.; Francis, D.; Faili, F.; Twitchen, D. J.; Kuball, M. Reducing GaN-on-Diamond Interfacial Thermal Resistance for High Power Transistor Applications. *Appl. Phys. Lett.* **2015**, *106*, 111906.

(31) Braun, J. L.; Baker, C. H.; Giri, A.; Elahi, M.; Artyushkova, K.; Beechem, T. E.; Norris, P. M.; Leseman, Z. C.; Gaskins, J. T.; Hopkins, P. E. Size Effects on the Thermal Conductivity of Amorphous Silicon Thin Films. *Phys. Rev. B* **2016**, *93*, 1–5.

(32) Reilly, C. E.; Hatui, N.; Mates, T. E.; Nakamura, S.; DenBaars, S. P.; Keller, S. 2DEGs Formed in AlN/GaN HEMT Structures with AlN Grown at Low Temperature. *Appl. Phys. Lett.* **2021**, *118*, 222103.

(33) Tsuchida, H.; Kamata, I.; Miyazawa, T.; Ito, M.; Zhang, X.; Nagano, M. Recent Advances in 4H-SiC Epitaxy for High-Voltage Power Devices. *Mater. Sci. Semicond. Process.* **2018**, *78*, 2–12.

(34) Kasu, M. Diamond Epitaxy: Basics and Applications. *Prog. Cryst. Growth Charact. Mater.* **2016**, *62*, 317–328.

(35) Bhattacharyya, A.; Ranga, P.; Roy, S.; Ogle, J.; Whittaker-Brooks, L.; Krishnamoorthy, S. Low Temperature Homoepitaxy of (010)  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> by Metalorganic Vapor Phase Epitaxy: Expanding the Growth Window. *Appl. Phys. Lett.* **2020**, *117*, 142102.

(36) Bhattacharyya, A.; Roy, S.; Ranga, P.; Shoemaker, D.; Song, Y.; Lundh, J. S.; Choi, S.; Krishnamoorthy, S. 130 MA Mm<sup>-1</sup>  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> Metal Semiconductor Field Effect Transistor with Low-Temperature Metalorganic Vapor Phase Epitaxy-Regrown Ohmic Contacts. *Appl. Phys. Express* **2021**, *14*, 076502.

(37) Bhattacharyya, A.; Sharma, S.; Alema, F.; Ranga, P.; Roy, S.; Peterson, C.; Seryogin, G.; Osinsky, A.; Singisetti, U.; Krishnamoorthy, S. 4.4 KV  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> MESFETs with Power Figure of Merit Exceeding 100 MW Cm<sup>-2</sup>. *Appl. Phys. Express* **2022**, *15*, 061001.

(38) Bhattacharyya, A.; Ranga, P.; Roy, S.; Peterson, C.; Alema, F.; Seryogin, G.; Osinsky, A.; Krishnamoorthy, S. Multi-kV Class  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> MESFETs With a Lateral Figure of Merit Up to 355 MW/cm<sup>2</sup>. *IEEE Electron Device Lett.* **2021**, *42*, 1272.

(39) Kalarickal, N. K.; Xia, Z.; Huang, H.-L.; Moore, W.; Liu, Y.; Brenner, M.; Hwang, J.; Rajan, S.  $\beta$ -(Al0.18Ga0.82)O<sub>3</sub>/Ga<sub>2</sub>O<sub>3</sub> Double Heterojunction Transistor With Average Field of 5.5 MV/cm. *IEEE Electron Device Lett.* **2021**, *42*, 899–902.

(40) Sharma, S.; Zeng, K.; Saha, S.; Singisetti, U. Field-Plated Lateral Ga<sub>2</sub>O<sub>3</sub> MOSFETs With Polymer Passivation and 8.03 KV Breakdown Voltage. *IEEE Electron Device Lett.* **2020**, *41*, 836–839.

(41) Chabak, K. D.; McCandless, J. P.; Moser, N. A.; Green, A. J.; Mahalingam, K.; Crespo, A.; Hendricks, N.; Howe, B. M.; Tetlak, S. E.; Leedy, K.; Fitch, R. C.; Wakimoto, D.; Sasaki, K.; Kuramata, A.; Jessen, G. H. Recessed-Gate Enhancement-Mode  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> MOSFETs. *IEEE Electron Device Lett.* **2018**, *39*, 67–70.

(42) Lv, Y.; Zhou, X.; Long, S.; Song, X.; Wang, Y.; Liang, S.; He, Z.; Han, T.; Tan, X.; Feng, Z.; Dong, H.; Zhou, X.; Yu, Y.; Cai, S.; Liu, M. Source-Field-Plated  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> MOSFET With Record Power Figure of Merit of 50.4 MW/Cm<sup>2</sup>. *IEEE Electron Device Lett.* **2018**, *40*, 1.

(43) Tetzner, K.; Egbo, K.; Klupsch, M.; Unger, R.-S.; Popp, A.; Chou, T.-S.; Anooz, S. B.; Galazka, Z.; Trampert, A.; Bierwagen, O.; Würfl, J. SnO/ $\beta$ -Ga<sub>2</sub>O<sub>3</sub> Heterojunction Field-Effect Transistors and Vertical p–n Diodes. *Appl. Phys. Lett.* **2022**, *120*, 112110.

(44) Kalarickal, N. K.; Feng, Z.; Anhar Uddin Bhuiyan, A. F. M. A. U.; Xia, Z.; Moore, W.; McGlone, J. F.; Arehart, A. R.; Ringel, S. A.; Zhao, H.; Rajan, S. Electrostatic Engineering Using Extreme Permittivity Materials for Ultra-Wide Bandgap Semiconductor Transistors. *IEEE Trans. Electron Devices* **2021**, *68*, 29–35.

(45) Wang, C.; Gong, H.; Lei, W.; Cai, Y.; Hu, Z.; Xu, S.; Liu, Z.; Feng, Q.; Zhou, H.; Ye, J.; Zhang, J.; Zhang, R.; Hao, Y. Demonstration of the P-NiOx/n-Ga<sub>2</sub>O<sub>3</sub> Heterojunction Gate FETs and Diodes With BV2/Ron,Sp Figures of Merit of 0.39 GW/Cm<sup>2</sup> and 1.38 GW/Cm<sup>2</sup>. *IEEE Electron Device Lett.* **2021**, *42*, 485–488.

(46) Tetzner, K.; Bahat Treidel, E. B.; Hilt, O.; Popp, A.; Bin Anooz, S. B.; Wagner, G.; Thies, A.; Ickert, K.; Gargouri, H.; Wurfl, J. Lateral 1.8 KV  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> MOSFET With 155 MW/Cm<sup>2</sup> Power Figure of Merit. *IEEE Electron Device Lett.* **2019**, *40*, 1503–1506.

(47) Wang, C.; Zhou, H.; Zhang, J.; Mu, W.; Wei, J.; Jia, Z.; Zheng, X.; Luo, X.; Tao, X.; Hao, Y. Hysteresis-Free and Ms-Switching of D/E-Modes Ga<sub>2</sub>O<sub>3</sub> Hetero-Junction FETs with the BV2/Ron,Sp of 0.74/0.28 GW/Cm<sup>2</sup>. *Appl. Phys. Lett.* **2022**, *120*, 112101.

(48) Lv, Y.; Liu, H.; Zhou, X.; Wang, Y.; Song, X.; Cai, Y.; Yan, Q.; Wang, C.; Liang, S.; Zhang, J.; Feng, Z.; Zhou, H.; Cai, S.; Hao, Y. Lateral  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> MOSFETs With High Power Figure of Merit of 277 MW/Cm<sup>2</sup>. *IEEE Electron Device Lett.* **2020**, *41*, 537–540.

(49) Joishi, C.; Zhang, Y.; Xia, Z.; Sun, W.; Arehart, A. R.; Ringel, S.; Lodha, S.; Rajan, S. Breakdown Characteristics of  $\beta$ -(Al0.22Ga0.78)-2O<sub>3</sub>/Ga<sub>2</sub>O<sub>3</sub> Field-Plated Modulation-Doped Field-Effect Transistors. *IEEE Electron Device Lett.* **2019**, *40*, 1241–1244.

(50) Wang, Y.; Xu, W.; You, T.; Mu, F.; Hu, H.; Liu, Y.; Huang, H.; Suga, T.; Han, G.; Ou, X.; Hao, Y.  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> MOSFETs on the Si Substrate Fabricated by the Ion-Cutting Process. *Sci. China Physics, Mech. Astron.* **2020**, *63*, 277311.

(51) Xu, W.; Wang, Y.; You, T.; Ou, X.; Han, G.; Hu, H.; Zhang, S.; Mu, F.; Suga, T.; Zhang, Y.; Hao, Y.; Wang, X. First Demonstration of Waferscale Heterogeneous Integration of Ga<sub>2</sub>O<sub>3</sub> MOSFETs on SiC and Si Substrates by Ion-Cutting Process; IEEE International Electron Devices Meeting (IEDM), 2019; pp 12.5.1–12.5.4.

(52) Wang, Y.; Han, G.; Xu, W.; You, T.; Hu, H.; Liu, Y.; Zhang, X.; Huang, H.; Ou, X.; Ma, X.; Hao, Y. Recessed-Gate Ga<sub>2</sub>O<sub>3</sub>-on-SiC MOSFETs Demonstrating a Stable Power Figure of Merit of 100 mW/cm<sup>2</sup> Up to 200 °C. *IEEE Trans. Electron Devices* **2022**, *69*, 1945–1949.

(53) Baliga, B. J. Power semiconductor device figure of merit for high-frequency applications. *IEEE Electron Device Lett.* **1989**, *10*, 455–457.

(54) Lundh, J. S.; Chatterjee, B.; Song, Y.; Baca, A. G.; Kaplar, R. J.; Beechem, T. E.; Allerman, A. A.; Armstrong, A. M.; Klein, B. A.; Bansal, A.; Talreja, D.; Pogrebnyakov, A.; Heller, E.; Gopalan, V.; Redwing, J. M.; Foley, B. M.; Choi, S. Multidimensional Thermal Analysis of an Ultrawide Bandgap AlGaN Channel High Electron Mobility Transistor. *Appl. Phys. Lett.* **2019**, *115*, 153503.

(55) Pomeroy, J. W.; Middleton, C.; Singh, M.; Dalcanale, S.; Uren, M. J.; Wong, M. H.; Sasaki, K.; Kuramata, A.; Yamakoshi, S.; Higashiwaki, M.; Kuball, M. Raman Thermography of Peak Channel Temperature in  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> MOSFETs. *IEEE Electron Device Lett.* **2019**, *40*, 189–192.

(56) Cheng, Z.; Mu, F.; Yates, L.; Suga, T.; Graham, S. Interfacial Thermal Conductance across Room-Temperature-Bonded GaN/Diamond Interfaces for GaN-on-Diamond Devices. *ACS Appl. Mater. Interfaces* **2020**, *12*, 8376–8384.

(57) Field, D. E.; Cuenca, J. A.; Smith, M.; Fairclough, S. M.; Massabuau, F. C.-P.; Pomeroy, J. W.; Williams, O.; Oliver, R. A.; Thayne, I.; Kuball, M. Crystalline Interlayers for Reducing the Effective Thermal Boundary Resistance in GaN-on-Diamond. *ACS Appl. Mater. Interfaces* **2020**, *12*, 54138–54145.

(58) Tadjer, M. J.; Anderson, T. J.; Ancona, M. G.; Raad, P. E.; Komarov, P.; Bai, T.; Gallagher, J. C.; Koehler, A. D.; Goorsky, M. S.; Francis, D. A.; Hobart, K. D.; Kub, F. J. GaN-On-Diamond HEMT Technology With TAVG = 176°C at PDC,Max = 56 W/Mm Measured by Transient Thermoreflectance Imaging. *IEEE Electron Device Lett.* **2019**, *40*, 881–884.

(59) Chao, P. C.; Chu, K.; Diaz, J.; Creamer, C.; Sweetland, S.; Kallaher, R.; McGraw, C.; Via, G. D.; Blevins, J.; Dumka, D. C.; Lee, C.; Tserng, H. Q.; Saunier, P.; Kumar, M. GaN-on-Diamond HEMTs with 11W/Mm Output Power at 10GHz. *MRS Adv* **2016**, *1*, 147–155.

(60) Inyushkin, A. V.; Taldenkov, A. N.; Ralchenko, V. G.; Bolshakov, A. P.; Koliadin, A. V.; Katrusha, A. N. Thermal Conductivity of High Purity Synthetic Single Crystal Diamonds. *Phys. Rev. B* **2018**, *97*, 144305.

(61) Malakoutian, M.; Song, Y.; Yuan, C.; Ren, C.; Lundh, J. S.; Lavelle, R. M.; Brown, J. E.; Snyder, D. W.; Graham, S.; Choi, S.; Chowdhury, S. Polycrystalline Diamond Growth on  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> for Thermal Management. *Appl. Phys. Express* **2021**, *14*, 055502.

(62) Shoemaker, D.; Malakoutian, M.; Chatterjee, B.; Song, Y.; Kim, S.; Foley, B. M.; Graham, S.; Nordquist, C. D.; Chowdhury, S.; Choi, S. Diamond-Incorporated Flip-Chip Integration for Thermal Management of GaN and Ultra-Wide Bandgap RF Power Amplifiers. *IEEE Trans. Components, Packag. Manuf. Technol.* **2021**, *11*, 1177–1186.

(63) Kuball, M.; Hayes, J. M.; Uren, M. J.; Martin, I.; Birbeck, J. C. H.; Balmer, R. S.; Hughes, B. T. Measurement of Temperature in Active High-Power AlGaN/GaN HFETs Using Raman Spectroscopy. *IEEE Electron Device Lett.* **2002**, *23*, 7–9.

(64) Choi, S.; Heller, E. R.; Dorsey, D.; Vetry, R.; Graham, S. Thermometry of AlGaN/GaN HEMTs Using Multispectral Raman Features. *IEEE Trans. Electron Devices* **2013**, *60*, 1898–1904.

(65) Dallas, J.; Pavlidis, G.; Chatterjee, B.; Lundh, J. S.; Ji, M.; Kim, J.; Kao, T.; Detchprohm, T.; Dupuis, R. D.; Shen, S.; Graham, S.; Choi, S. Thermal Characterization of Gallium Nitride P-i-n Diodes. *Appl. Phys. Lett.* **2018**, *112*, No. 073503.

(66) Lundh, J. S.; Song, Y.; Chatterjee, B.; Baca, A. G.; Kaplar, R. J.; Armstrong, A. M.; Allerman, A. A.; Klein, B. A.; Kendig, D.; Kim, H.; Choi, S. Device-Level Multidimensional Thermal Dynamics With Implications for Current and Future Wide Bandgap Electronics. *J. Electron. Packag.* **2020**, *142*, 47.

(67) Touloukian, Y. S.; Buyco, E. H. *Thermophysical Properties of Matter—the TPRC Data Series. Volume 4. Specific Heat - Metallic Elements and Alloys. (Reannouncement). Data Book*, 1971. 832.

(68) Adams, G. B.; Johnston, H. L. Low Temperature Heat Capacities of Inorganic Solids. XI. The Heat Capacity of  $\beta$ -Gallium Oxide from 15 to 300 °K. *J. Am. Chem. Soc.* **1952**, *74*, 4788–4789.

(69) Hitova, L.; Yakimova, R.; Trifonova, E. P.; Lenchev, A.; Janzen, E. Heat Capacity of 4H-SiC Determined by Differential Scanning Calorimetry. *J. Electrochem. Soc.* **2000**, *147*, 3546.

## Recommended by ACS

### Ga<sup>+</sup> Ion Irradiation-Induced Tuning of Artificial Pinning Sites to Control Domain Wall Motion

Domenico Giuliano, Fabrizio Riente, et al.

JANUARY 26, 2023

ACS APPLIED ELECTRONIC MATERIALS

READ

### Electron Transport Properties in High Electron Mobility Transistor Structures Improved by V-Pit Formation on the AlGaN/GaN Interface

Alice Hospodková, Tereza Košutová, et al.

APRIL 06, 2023

ACS APPLIED MATERIALS & INTERFACES

READ

### Transducer-Less Thermoreflectance Technique for Measuring Thermal Properties of the Buried Buffer Layer and Interface in GaN-based HEMTs

Chao Yuan, Yue Hao, et al.

DECEMBER 07, 2022

ACS APPLIED ELECTRONIC MATERIALS

READ

### Machine-Learned Fermi Level Prediction of Solution-Processed Ultrawide-Bandgap Amorphous Gallium Oxide (a-Ga<sub>2</sub>O<sub>3</sub>)

Diki Purnawati, Yukiharu Uraoka, et al.

NOVEMBER 25, 2022

ACS APPLIED ELECTRONIC MATERIALS

READ

Get More Suggestions >