# Transient Thermal Management of a $\beta$ -Ga<sub>2</sub>O<sub>3</sub> MOSFET Using a Double-Side Diamond Cooling Approach

Samuel H. Kim<sup>®</sup>, Daniel Shoemaker<sup>®</sup>, Andrew J. Green, Kelson D. Chabak<sup>®</sup>, *Senior Member, IEEE*, Kyle J. Liddy, Samuel Graham<sup>®</sup>, *Senior Member, IEEE*, and Sukwon Choi<sup>®</sup>, *Member, IEEE*

Abstract— $\beta$ -phase gallium oxide ( $\beta$ -Ga<sub>2</sub>O<sub>3</sub>) has drawn significant attention due to its large critical electric field strength and the availability of low-cost high-quality meltgrown substrates. Both aspects are advantages over gallium nitride (GaN) and silicon carbide (SiC) based power switching devices. However, because of the poor thermal conductivity of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>, device-level thermal management is critical to avoid performance degradation and component failure due to overheating. In addition, for highfrequency operation, the low thermal diffusivity of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> results in a long thermal time constant, which hinders the use of previously developed thermal solutions for devices based on relatively high thermal conductivity materials (e.g., GaN transistors). This work investigates a double-side diamond-cooled  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> device architecture and provides guidelines to maximize the device's thermal performance under both direct current (dc) and high-frequency switching operation. Under high-frequency operation, the use of a  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> composite substrate (bottom-side cooling) must be augmented by a diamond passivation overlayer (top-side cooling) because of the low thermal diffusivity of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>.

Index Terms— Gallium oxide ( $\beta$ -Ga<sub>2</sub>O<sub>3</sub>), MOSFET, Raman thermometry, thermal management, ultrawide bandgap (UWBG) semiconductor devices.

#### I. INTRODUCTION

The β-phase gallium oxide (β-Ga<sub>2</sub>O<sub>3</sub>) is an ultrawide bandgap (UWBG) semiconductor [1] that offers the potential to surpass wide bandgap power electronic devices

Manuscript received 21 November 2022; revised 13 January 2023; accepted 7 February 2023. Date of publication 22 February 2023; date of current version 24 March 2023. This work was supported in part by the National Science Foundation under Grant CBET-1934482 and in part by the Graduate Research Fellowship Program under Grant DGE1255832. The review of this article was arranged by Editor F. Bonani. (Corresponding author: Sukwon Choi.)

Samuel H. Kim and Samuel Graham are with the George W. Woodruff School of Mechanical Engineering, Georgia Institute of Technology, Atlanta, GA 30332 USA.

Daniel Shoemaker and Sukwon Choi are with the Department of Mechanical Engineering, The Pennsylvania State University, University Park, PA 16802 USA (e-mail: sukwon.choi@psu.edu).

Andrew J. Green, Kelson D. Chabak, and Kyle J. Liddy are with the Air Force Research Laboratory, Wright-Patterson AFB, Dayton, OH 45433 USA.

Color versions of one or more figures in this article are available at https://doi.org/10.1109/TED.2023.3244134.

Digital Object Identifier 10.1109/TED.2023.3244134

based on gallium nitride (GaN) and silicon carbide (SiC), owing to its outstanding electronic properties and potentially low manufacturing cost [2], [3]. The large bandgap energy (~4.8 eV) translates into a high breakdown electric field (~8 MV/cm) [4], [5], which renders the material ideal for high voltage and high power switching devices [6], [7]. In addition, melt-grown single crystal  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> substrates have become commercially available. While there has been significant progress in bulk material synthesis, epitaxial growth, doping, and the development of homoepitaxial device architectures [8], [9], [10], thermal management is still a considerable bottleneck to the commercialization of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> electronics.  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> possesses a poor thermal conductivity (11-27 W/m-K [11], [12]) as compared to GaN  $(\sim 150 \text{ W/m-K } [13], [14]) \text{ and SiC } (\sim 400 \text{ W/m-K } [15], [16]).$ Therefore,  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> devices suffer from device self-heating under nominal operating conditions [17]. To reduce the junction-to-package thermal resistance of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> devices under both direct current (dc) and high-frequency switching operation, this study builds upon recent reports on: 1) the fabrication of composite wafers that integrate  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> with high thermal conductivity substrates (e.g., 4H-SiC, diamond [18], [19], [20], [21]) and 2) the growth of polycrystalline diamond on  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> [22].

In this study, the cooling effectiveness of various diamond integration schemes applied to a β-Ga<sub>2</sub>O<sub>3</sub> MOSFET was evaluated, in order to minimize the device's thermal impedance under both dc and high-frequency switching operations. System-level thermal management solutions designed solely based on steady-state operation were shown to be often ineffective for applications that experience transient thermal loading and could result in an overdesigned cooling system [23]. Since the operation of a power electronic device involves high-frequency switching, the design of a thermally augmented device architecture will thus require the consideration of the device's transient thermal dynamics. The device thermal time constant  $(\tau)$  [24], [25], [26] (the rise time for a device to reach  $\sim$ 63% of its steady-state temperature in response to a power step input) [27] is inversely proportional to the thermal diffusivity  $(\alpha)$ , i.e.,  $\tau \propto (1/\alpha) = \rho c_p/\kappa$ , where  $\rho$  is the density,  $c_p$  is the specific heat, and  $\kappa$  is

0018-9383 © 2023 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See https://www.ieee.org/publications/rights/index.html for more information.

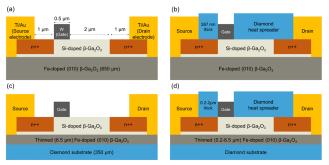

Fig. 1. Schematic of (a) baseline  $\beta$ -Ga $_2$ O $_3$  MOSFET, (b) top-side cooling scheme: 267 nm thick diamond heat spreader was grown on  $\beta$ -Ga $_2$ O $_3$ , (c) bottom-side cooling scheme: diamond heat spreader was bonded to thinned  $\beta$ -Ga $_2$ O $_3$ , and (d) double-side cooling scheme: various thickness options of top-side diamond and  $\beta$ -Ga $_2$ O $_3$  were considered.

the thermal conductivity. Since the thermal conductivity of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> is an order of magnitude lower than those for GaN and SiC, the thermal diffusivity is an order of magnitude lower as well. This renders  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> transistors to respond much slower to a power loss during switching as compared to GaN and SiC devices. Because of this relatively long thermal time constant, the heat diffusion length in  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> is limited under short transient thermal loading; therefore, device-level thermal management solutions established for GaN devices (i.e., use of a GaN-on-diamond composite wafer [28]) can be inappropriate for  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> devices, especially under highfrequency operating conditions. This study builds upon our recent reports on the fabrication of a β-Ga<sub>2</sub>O<sub>3</sub> composite substrate [29] and the growth of polycrystalline diamond on  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> [22]. This work identifies key considerations for the design of a double-side diamond-cooled β-Ga<sub>2</sub>O<sub>3</sub> device architecture using transient Raman thermometry and transient thermal modeling.

#### II. MODELING AND EXPERIMENTAL DETAILS

A comparative analysis of the steady-state and transient selfheating behavior of a  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> MOSFET and a GaN-on-Si high electron mobility transistor (HEMT) was performed. Fig. 1(a) shows a cross-sectional schematic of the  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> MOSFET tested in this work. A Si-doped  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> channel layer was grown on a Fe-doped (010)-oriented  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> commercial substrate using metal-organic vapor phase epitaxy (MOVPE). The channel length, gate length, gate-todrain spacing, and gate width are 2.5, 0.5, 2, and 100  $\mu$ m, respectively. More fabrication details of this device can be found in [17] and [30]. A GaN HEMT was fabricated on a commercial AlGaN/GaN/Si wafer, which consisted of a 10 nm in situ SiN<sub>x</sub> passivation layer, a 4 nm GaN cap layer, a 24 nm AlGaN barrier layer, a 514 nm GaN layer, and a 4.4  $\mu$ m GaN buffer layer. The GaN HEMT has a gate length, gate-to-source spacing, gate-to-drain spacing, and gate width of 2, 2, 15, and 100  $\mu$ m. More details of the device fabrication process can be found in [31]. An electro-thermal device model was constructed to conduct a design optimization study for device-level thermal management solutions. The simulated steady-state and transient self-heating behavior of these devices were validated against experimental results acquired via nanoparticle-assisted Raman thermometry.

A transient device thermal model was created based on the  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> MOSFET shown in Fig. 1(a). This model was then extended to investigate a hypothetical  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> device that employs a polycrystalline diamond passivation layer grown on top of the  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> channel [Fig. 1(b): top-side cooling scheme], a device fabricated on a  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>/diamond composite substrate [Fig. 1(c): bottom-side cooling scheme], and finally, a device that employs both a diamond heat spreader and a  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>/diamond composite substrate [Fig. 1(d): double-side cooling scheme]. For top-side cooling, it was assumed that a 267 nm thick polycrystalline diamond was grown on the  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> with a thermal conductivity of 110 W/m-K and a thermal boundary resistance (TBR) of 30.2 m<sup>2</sup>K/GW at the  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>/diamond interface, similar to our previous work [22]. For bottom-side cooling, the  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>/diamond composite wafer was assumed to be constructed by integrating a 6.5  $\mu$ m thick  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> layer with a 350  $\mu$ m-thick polycrystalline diamond substrate via fusion bonding [19]. Accordingly, the  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>/diamond TBR was assumed to be 47.1 m<sup>2</sup>-K/GW, similar to our previous work [19] on the fabrication of a β-Ga<sub>2</sub>O<sub>3</sub>/4H-SiC composite substrate via fusion bonding using a 30 nm thick SiN<sub>x</sub> bonding/interlayer. For the doubleside cooled structure in Fig. 1(d), simulation studies were performed as a function of the thicknesses of the diamond heat spreader and the  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> layer of the composite substrate as well as the interface TBRs in an effort to enhance the thermal performance beyond that of a GaN-on-SiC power switch. The device geometries (gate length and gate-to-drain distance) were kept identical to the baseline  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> MOSFET shown in Fig. 1(a). For all simulated device structures, the surface below the substrate (i.e., package temperature) was assumed to be 20 °C while other surfaces were subject to a natural convection boundary condition.

Room temperature thermal properties used to create the transient device thermal model are listed in Table I. Temperature- and thickness-dependent thermal conductivities were used, and a range TBRs at the β-Ga<sub>2</sub>O<sub>3</sub>/diamond interface was assumed based on published values shown in Table I. For example, the  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>/diamond TBR for a 267 nm polycrystalline diamond film grown on  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> was reported to be 30.2 m<sup>2</sup>-K/GW [22]. Another study where a 30 nm thick  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> layer was deposited on a single crystal diamond via atomic layer deposition reported a TBR of 7.3 m<sup>2</sup>-K/GW [29]. Previous work on the fabrication of a  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>/SiC composite substrate using a fusion bonding process reported a  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>/4H-SiC effective TBR of 47.1 m<sup>2</sup>-K/GW, where the thermal resistance of the  $SiN_x$  bonding layer was found to dominate the overall TBR [19]. For this study, a TBR of 47.1 m<sup>2</sup>-K/GW was selected as the upper limit, and 7.3 m<sup>2</sup>-K/GW was chosen as the lower limit. The thermal conductivity of a polycrystalline diamond thin film is a strong function of crystallographic direction and film thickness [32]. This is because these films undergo columnar growth, where the lateral grain size of the columns (which scatters phonons) increases with the film thickness. Accordingly, directionand thickness-dependent diamond thermal conductivity values from [33] (that are summarized in Table I) were adopted to model the polycrystalline diamond passivation overlayer.

| Material Property                                    | β-Ga <sub>2</sub> O <sub>3</sub> [11]        | <b>Diamond</b> [33], [37]–[39]                                                                     | <b>GaN</b> [13]     | 4H-SiC [22] |

|------------------------------------------------------|----------------------------------------------|----------------------------------------------------------------------------------------------------|---------------------|-------------|

| Density (g/m³)                                       | 6.44                                         | 3.5                                                                                                | 6.15                | 3.21        |

| Specific heat (J/kg-K)                               | 490                                          | 520 at 300 K, 620 at 323 K,<br>730 at 358 K, 1300 at 573 K                                         | 490                 | 670         |

| $k_x$ (W/m-K)                                        | $13.7 \times (300/T)^{1.12}$ [001] direction | Thin film: first 500 nm - 85,<br>second 500 nm - 175, third 1000 nm - 309<br>Bulk substrate: 2158  | 180<br>(4 μm thick) | 490         |

| k <sub>y</sub> (W/m-K)                               | $10.7 \times (300/T)^{1.21}$ [100] direction |                                                                                                    |                     |             |

| k <sub>z</sub> (W/m-K)                               | $23.4 \times (300/T)^{1.27}$ [010] direction | Thin film: first 500 nm - 142,<br>second 500 nm - 310, third 1000 nm - 510<br>Bulk substrate: 2158 |                     |             |

| Thermal Boundary<br>Resistance at 300 K<br>(m²-K/GW) | 7.3 [29], [40], 30.2 [22], 47.1 [19]         |                                                                                                    | 4.35 [41]           |             |

|                                                      | -                                            | 7.3 [40]                                                                                           |                     |             |

TABLE I THERMO-PHYSICAL PROPERTIES USED MODEL THE  $\beta$ -GA $_2$ O $_3$  AND GAN DEVICE STRUCTURES

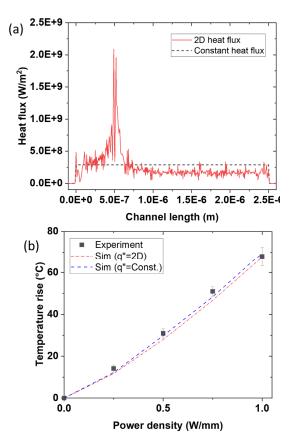

Previously, we developed a 3-D electro-thermal  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> device model by coupling a 2-D electrical model (using Synopsys Sentaurus TCAD [34], [35]) and a 3-D finite element thermal model with a detailed solid geometry that represents that of a real device (COMSOL Multiphysics) [17]. However, to reduce the computational load for the transient simulations, constant heat flux was applied from the source to drain to mimic a fully-open channel condition [36], instead of applying the heat flux profile (heretofore referred to as "2-D heat flux") obtained from the 2-D electrical model, as shown in Fig. 2(a). Fig. 2(b) shows the reasonable agreement between the experimental data and simulation results for simulation results based on the 2-D heat flux and constant heat flux. Therefore, a constant heat flux corresponding to a power density of 1 W/mm was selected for use in the 3-D transient thermal model throughout the remainder of this study.

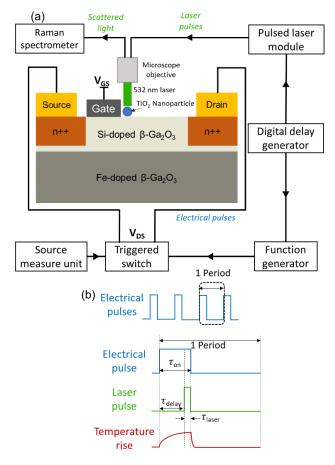

The steady-state and transient channel temperatures of the  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> MOSFET shown in Fig. 1(a) were measured using nanoparticle-assisted Raman thermometry. Experiments were performed using a Horiba LabRAM HR Evolution spectrometer with a 532 nm excitation source [31]. Measurements were performed in a 180° backscattering configuration with a long working distance  $50 \times$  objective (NA = 0.45). Anatase titanium dioxide (TiO<sub>2</sub>) nanoparticles (99.98% purity; ~250 nm in diameter), which served as surface temperature transducers, were deposited on the device surface. Since nanoparticle deposition (i.e., positioning individual particles) is not a fully controllable process, several deposition processes were performed until a device with a nanoparticle located at the drain side corner of the gate near the center of the gate width was identified. The Stokes Raman peak shift of the  $E_g$  phonon mode of TiO2 was used to estimate the channel temperature rise [27]. The spatial resolution of this technique is dictated by the size of the sub-micrometer nanoparticles. The experimental setup used for transient Raman thermometry experiments is illustrated in Fig. 3(a). This setup adopts a lock-in modulation scheme, in which the electrical and laser pulse trains are synchronized while the Raman signal accumulates over many periods. Using this experimental setup, a temporal resolution of 25 ns was achieved and used in this study. Fig. 3(b) shows

Fig. 2. (a) Heat flux obtained from a 2-D electrical model for 1 W/mm, and the constant heat flux (applied between the source and drained) assumed for simplicity. (b) Experimental results compared with modeling results based on 2-D heat flux and constant heat flux cases.

the synchronized pulsing scheme that allows control of the electrical pulsewidth  $(\tau_{on})$  of the applied drain–source voltage  $(V_{DS})$  and the laser pulsewidth  $(\tau_{laser})$  that produces a Raman signal, which is collected by an electron-multiplying charge-coupled device (EMCCD) of the Raman system. The time delay  $(\tau_{delay})$  between the electrical and laser pulses is controlled by a digital delay generator which allows to measure the full transient temperature rise of the device in response

Fig. 3. (a) Experimental setup used for transient Raman thermometry. (b) Synchronized electrical/laser pulsing scheme used to capture the transient thermal response of the  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> MOSFET.

to a square electrical pulse with a 10% duty cycle. Similar transient optical thermometry measurements were performed on the GaN-on-Si HEMT for comparison [31], [42].

## III. RESULTS AND DISCUSSION

# A. Transient Thermal Response of the Baseline Device Structure

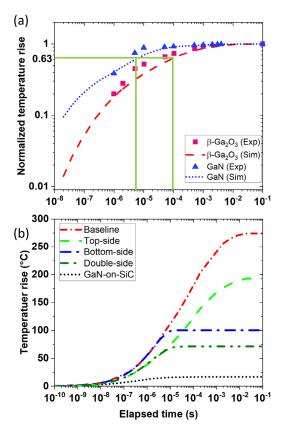

Fig. 4(a) Compares the transient temperature rise (with respect to a 20 °C ambient temperature condition under OFF-state) of the  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> MOSFET with that for a GaN-on-Si HEMT, normalized with respect to their steadystate temperature rise under 1 and 1.6 W/mm power dissipation levels, respectively. Under steady-state, the  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> MOSFET exhibits a 2.7× higher temperature rise than the GaN HEMT despite the  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> MOSFET operating under a  $\sim$ 38% lower power density. The corresponding junction-to-package thermal resistances of the β-Ga<sub>2</sub>O<sub>3</sub> MOSFET and the GaN HEMT under steady-state (or dc operation) are 65 and 15 K-mm/W, respectively. The  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> MOSFET device clearly exhibits a larger thermal time constant than the GaN-on-Si HEMT as indicated by the green lines in Fig. 4(a). This means its channel temperature reaches a steady-state value much slower than the GaN device.

To study the transient self-heating behavior of the four device architectures shown in Fig. 1, device simulations were performed under a realistic power dissipation level [28]

Fig. 4. (a) Normalized channel temperature rises of the  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> MOSFET and GaN-on-Si HEMT, with respect to their steady-state temperature rise. The steady-state temperature rise of the  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> MOSFET is 65 °C for a power dissipation level of 1 W/mm [17]. The steady-state temperature rise of the GaN-on-Si HEMT is 24 °C for a power dissipation level of 1.6 W/mm [42]. (b) Transient temperature rise under a power density of 4 W/mm for the baseline  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> MOSFET [Fig. 1(a): baseline], a  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> MOSFET passivated with a diamond layer [Fig. 1(b): top-side], a MOSFET fabricated on a  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>-diamond composite substrate [Fig. 1(c): bottom-side], a  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>-on-diamond MOSFET augmented by a diamond passivation layer [Fig. 1(d): double-side; 6.5  $\mu$ m-thick  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>], and a GaN-on-SiC HEMT.

of 4 W/mm, and results are plotted in Fig. 4(b). For comparison, simulation results for a GaN-on-SiC HEMT are also shown in Fig. 4(b). Without any cooling solution applied, the steady-state channel temperature rise of the baseline  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> MOSFET [see Fig. 1(a)] is 278 °C (i.e., the channel temperature is 298 °C while the base temperature is 20 °C), which far exceeds typical operational safety limits (e.g., 175 °C for GaN and 125 °C for Si devices [26]). Because of the low thermal conductivity of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>, replacing the  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> substrate with diamond [see Fig. 1(c)] reduces the steady-state temperature rise by  $\sim$ 64% (dropping from 278 °C to 100 °C). However, under high-frequency operation beyond the 10<sup>2</sup> kHz range [equivalent to the elapsed time less than  $\sim 10^{-5}$  s in Fig. 4(b)], the employment of a composite substrate alone does not improve the transient thermal response (i.e., self-heating) over the baseline case as shown in the red and blue curves in Fig. 4(b). The channel temperature rises for both device structures are identical up to  $\sim 3 \times 10^{-6}$  s, which corresponds to transient thermal loading under  $\sim$ 300 kHz. Therefore, solely relying on a bottom-side cooling strategy (i.e., employing a composite substrate similar to the case of GaN-on-diamond

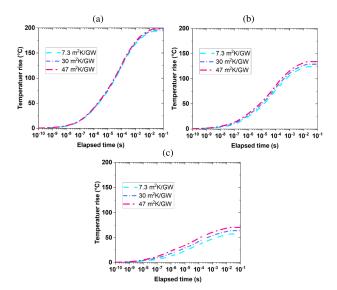

Fig. 5. Top-side cooling effectiveness as a function of diamond passivation layer thickness and diamond/ $\beta$ -Ga<sub>2</sub>O<sub>3</sub> TBR. Results for (a) 267 nm, (b) 1  $\mu$ m, and (c) 2  $\mu$ m thick diamond passivation layers. The operational power density for all simulation cases is 4 W/mm.

devices [28]) is insufficient for the thermal management of pulse-powered  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> MOSFETs. The addition of a topside heat spreader [i.e., diamond passivation, Fig. 1(b)] to the baseline device reduces the steady-state temperature rise by  $\sim 28\%$  (decreasing from 278 °C to 198 °C), which is less effective than the case of employing a bottom-side cooling solution [i.e.,  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>-on-diamond composite substrate; Fig. 1(c)]. However, it should be noted that the transient thermal response improves for elapsed times less than  $\sim 10^{-5}$ s. Therefore, a double-side cooling scheme shown in Fig. 1(d), might provide an opportunity to improve the device's thermal impedance under both steady-state and transient operating conditions. Accordingly, simulation results for the double-side cooled configuration (where the  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> layer thickness is 6.5  $\mu$ m) show a ~75% reduction in the steady-state temperature rise compared to the baseline  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> MOSFET, while also improving the transient thermal performance.

## B. Top-Side Cooling

The thermal conductivity of polycrystalline thin films synthesized via chemical vapor deposition is highly anisotropic and increases with the film thickness due to the evolution of columnar grain structures. For this parametric study, the thickness of the diamond was increased from 267 nm [22] to 2  $\mu$ m. The anisotropic thermal conductivity as a function of film thickness is summarized in Table I. Results in Fig. 5 can be compared with the baseline case (i.e.,  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> MOSFET fabricated on a native substrate) shown in Fig. 4(b). Fig. 5(a)-(c) shows the impact of the thickness of the topside diamond passivation layer on the operational channel temperature. Since the diamond passivation layer is directly located over the device channel, it effectively spreads heat away from the device's active region under both steady-state and transient operating conditions. Fig. 5(a)–(c) also includes the effect of TBR. The impact of TBR on the channel temperature rise is negligible for the 267 nm thick diamond

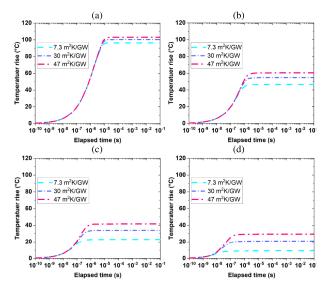

Fig. 6. Evaluation of the cooling effectiveness of the bottom-side cooling scheme as a function of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> thickness. Simulation results for a (a) 6.5, (b) 2.0, (c) 0.8, and (d) 0.2  $\mu$ m thick  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> layers. The operational power density for all simulation cases is 4 W/mm.

passivation layer. However, for 1 and 2  $\mu$ m thick diamond layers, an  $\sim$ 8% and  $\sim$ 18% respective difference in the steady-state temperature rise is observed between the lowest and the highest TBR values. For example, in Fig. 5(c), the channel temperature rise with a TBR of 47 m²-K/GW is 71 °C, while that for a TBR of 7.3 m²-K/GW is 58 °C. The transient temperature rise also reduces as the diamond film thickness increases; however, the thermal time constants for all three cases are identical ( $\sim$ 10<sup>-4</sup> s), which is almost identical to the thermal time constant of the base device shown in Fig. 4(a).

### C. Bottom-Side Cooling

The enhancement in the device's thermal performance by employing a β-Ga<sub>2</sub>O<sub>3</sub>/diamond composite wafer was evaluated via simulation. Key design parameters for reducing the thermal resistance of the composite substrate are the thickness of the  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> layer and the  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>/diamond TBR. Results for these case studies are summarized in Fig. 6 and can be compared to that for the baseline case (i.e.,  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> MOSFET fabricated on a native substrate) shown in Fig. 4(b). For a TBR of 47 m<sup>2</sup>-K/GW, as the  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> is thinned from 6.5 [19] to 0.2  $\mu$ m (relevant to the case of integration via ion-cutting [20], [21]), the steady-state channel temperature rise drops by  $\sim$ 77% from 103 °C to 23 °C. If the TBR of the bonded interface of the  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>/diamond composite substrate is reduced to 7.3 m<sup>2</sup>-K/GW, thinning the  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> film from 6.5 to 0.2  $\mu$ m results in a ~90% reduction in the steady-state temperature rise from 96 °C to 9.3 °C. Moreover, the thermal time constant as well as the transient channel temperature rise decrease as the thickness of the  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> reduces. For a TBR of 47 m<sup>2</sup>-K/GW, the thermal time constant of a  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>-on-diamond device with a 6.5  $\mu$ m thick  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> layer is  $\sim 1.5 \times 10^{-6}$  s, while that of a device with a 0.2  $\mu$ m thick  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> layer is  $\sim 4 \times 10^{-8}$  s. This corresponds to a decrease by two orders of magnitude. For a TBR of 7.3 m<sup>2</sup>-K/GW, as the  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> is thinned from 6.5 to 0.2  $\mu$ m,

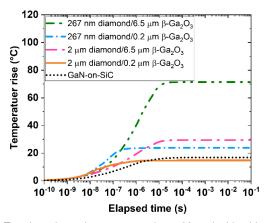

Fig. 7. Transient channel temperature rises of four double-side cooling schemes compared to that of a GaN-on-SiC HEMT.

the thermal time constant reduces from  $1.25 \times 10^{-6}$  to  $\sim 9.5 \times 10^{-9}$  s. To this end, the thermal time constant can be adjusted by reducing the thickness of the  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> layer of the composite substrate (bottom-side cooling), while the time constant is not affected by the thickness of the diamond passivation overlayer (top-side cooling). Additional modeling results (not shown) indicate that the diamond substrate thickness (within the simulated range of 100– $650~\mu m$ ) minimally (<5%) affects both the transient and steady-state thermal performance of the device.

#### D. Double-Side Cooling

Based on previous studies, the four different possible double-side cooling solutions were compared. The top-side diamond heat spreader was assumed to be 267 nm or 2  $\mu$ m thick. The  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> layer thickness was assumed to be either 6.5 or 0.2  $\mu$ m thick, as shown in Fig. 7. For the top-side diamond/β-Ga<sub>2</sub>O<sub>3</sub> interface, a TBR of 30 m<sup>2</sup>-K/GW was assumed. For the bottom-side  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>/diamond interface, a TBR of 47 m<sup>2</sup>-K/GW was used. Understandably, the combination that includes the thickest top-side diamond and the thinnest  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> shows the lowest temperature rise. This reduced steady-state temperature is comparable to that of a GaN-on-SiC device. By increasing the interface quality, it is possible to reduce the temperature even further. The diamond passivation layer with a moderately high thermal conductivity effectively reduces the device temperature not only under steady-state conditions, but also under the high-frequency operating regime, since it is located in proximity (i.e., less than several tens of nanometers) to the  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> device active region where the Joule heating occurs. Therefore, devicelevel thermal management of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> MOSFETs requires the combined use of a composite wafer and a top-side heat spreader in order to handle the thermal loading that occurs during both dc (steady-state) and pulsed (transient) operating conditions.

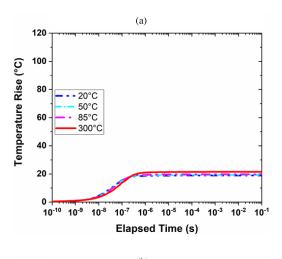

# E. Effect of Ambient Temperature

Previous case studies in this report were based on a base temperature of 20 °C. However, many real applications often result in elevated environmental temperatures. For example,

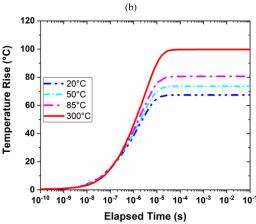

Fig. 8. Effect of base temperature on the channel temperature rise for double-side cooled devices with: (a) 2  $\mu$ m thick diamond passivation and 0.2  $\mu$ m thick  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> and (b) 267 nm thick diamond passivation and 6.5  $\mu$ m thick  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>.

a base temperature of 50 °C-85 °C is common for industrial applications, while a temperature of 300 °C can be expected for some space applications [1], [43]. Here, the best- and worst-case designs from Fig. 7 were compared for a double-side cooled device considering the temperaturedependent thermal properties of the diamond as shown in Table I. For both cases, the thermal time constant tends to increase with the ambient temperature since the specific heat of the diamond increases with temperature. For the best-case scenario, negligible effects on the channel temperature rise are observed as the base temperature increases from 20 °C to 85 °C, as shown in Fig. 8(a). However, as the ambient temperature further increases to 300 °C, the specific heat of the diamond increases more than twice as shown in Table I; therefore, the thermal time constant increases as well. With a lack of enough cooling power (and the  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> layer still notably contributing to the overall device thermal resistance), the steady-state temperature elevates by 50% (from 67 °C to 100 °C) if the base temperature increases from 20 °C to 300 °C, while the transient temperature rise between  $10^{-6}$  and  $10^{-5}$  s (1 MHz–100 kHz regime) elevates by 25% as shown in Fig. 8(b). However, due to the increased time constant for the base temperature of 300 °C, above the 10 MHz regime, the

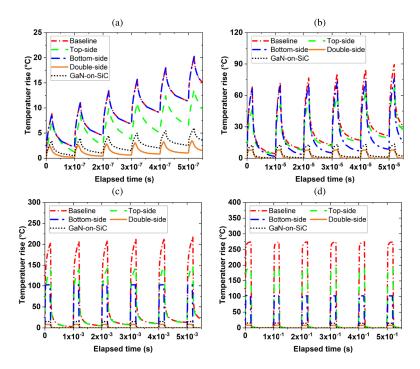

Fig. 9. (a)–(d) Effect of continuously pulsed operation for the baseline, top-side, bottom-side, and double-side cooled device architectures for various pulse periods (or frequencies).

transient channel temperature rise is lower than those under lower base temperature conditions.

# F. Heat Accumulation in Response to a Power Pulse Train

Finally, the effect of repeating pulse trains representing switching loss under device operation was investigated as shown in Fig. 9(a)–(d). Since the  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> system possesses a relatively long thermal time constant, the channel temperature may not be cooled down to the base temperature, resulting in progressively increasing channel temperatures in response to such a power pulse train. For this study, a 20% duty cycle was applied for four different power pulse periods, and the temperature rise for the first six pulses of each period was investigated. The four device architectures shown in Fig. 1 were compared. A 267 nm thick diamond passivation layer with a TBR of 30 m<sup>2</sup>-K/GW was assumed for the top-side cooled case [see Fig. 1(b)]. A 6.5  $\mu$ m thick  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> layer and a TBR of 47 m<sup>2</sup>-K/GW were assumed for the bottomside cooled device [see Fig. 1(c)]. A 2  $\mu$ m thick diamond passivation layer and a 0.2  $\mu$ m thick  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> layer for the composite substrate were assumed for the device adopting an ideal double-side cooling scheme [see Fig. 1(d)]. As discussed in the previous section, the thermal time constant of this double-side cooled device is  $\sim 4 \times 10^{-8}$  s. Therefore, the channel temperatures do not keep increasing when the pulse period is longer than  $10^{-7}$  s. Likewise, since the thermal time constant of the baseline  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> MOSFET is  $\sim 10^{-4}$ s, for a period of  $10^{-3}$  s, the peak temperature difference between the first peak and the sixth peak is only  $\sim 5\%$  as shown in Fig. 9(c). These results indicate that the thermal time constant is a key design parameter that provides guidelines for appropriate operational frequency ranges that prevent heat accumulation in the device.

### IV. CONCLUSION

In this study, the steady-state and transient self-heating behavior of a β-Ga<sub>2</sub>O<sub>3</sub> MOSFET fabricated on a native substrate was investigated. Based on this, a design optimization study was performed for a double-side diamondcooled MOSFET. The cooling effectiveness of a diamond passivation overlayer and a  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>/diamond composite substrate was evaluated via transient thermal modeling. Under high-frequency switching operation, the use of a  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> composite substrate (bottom-side cooling) must be augmented by a diamond heat spreader (top-side cooling) because of the low thermal diffusivity of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>. Replacing the native substrate with polycrystalline diamond (under a 6.5 µm-thick  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> layer) could reduce the steady-state temperature rise under dc operation by 64%. However, for high-frequency power switching beyond the  $\sim 10^2$  kHz regime, the use of a composite substrate alone fails to improve the transient thermal performance of the device. Adding a diamond passivation overlayer not only suppresses the steady-state temperature rise, but also drastically reduces the transient temperature rise under high-frequency operation. To maximize the thermal performance of a double-side diamond-cooled β-Ga<sub>2</sub>O<sub>3</sub> lateral transistor, the  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> layer thickness of the composite substrate and the TBRs at the  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>/diamond interfaces should be minimized. The heat-spreading performance of the diamond passivation layer should be maximized by increasing its thickness. The thermal time constant of the device structure should be considered to prevent heat accumulation in the device under high-frequency operation.

#### REFERENCES

J. Y. Tsao et al., "Ultrawide-bandgap semiconductors: Research opportunities and challenges," Adv. Electron. Mater., vol. 4, no. 1, pp. 1–49, 2018, doi: 10.1002/aelm.201600501.

- [2] S. B. Reese, T. Remo, J. Green, and A. Zakutayev, "How much will gallium oxide power electronics cost?" *Joule*, vol. 3, no. 4, pp. 903–907, 2019, doi: 10.1016/j.joule.2019.01.011.

- [3] K. O. Armstrong, S. Das, and J. Cresko, "Wide bandgap semiconductor opportunities in power electronics," in *Proc. IEEE 4th Workshop Wide Bandgap Power Devices Appl. (WiPDA)*, Nov. 2016, pp. 259–264, doi: 10.1109/WiPDA.2016.7799949.

- [4] M. Higashiwaki, K. Sasaki, A. Kuramata, T. Masui, and S. Yamakoshi, "Development of gallium oxide power devices," *Phys. Status Solidi A*, vol. 211, no. 1, pp. 21–26, Nov. 2014, doi: 10.1002/pssa.201330197.

- [5] S. J. Pearton, F. Ren, M. Tadjer, and J. Kim, "Perspective: Ga<sub>2</sub>O<sub>3</sub> for ultra-high power rectifiers and MOSFETs," *J. Appl. Phys.*, vol. 124, no. 22, Dec. 2018, Art. no. 220901, doi: 10.1063/1.5062841.

- [6] B. J. Baliga, "Power semiconductor device figure of merit for high-frequency applications," *IEEE Electron Device Lett.*, vol. 10, no. 10, pp. 455–457, Oct. 1989.

- [7] E. Johnson, "Physical limitations on frequency and power parameters of transistors," in *Proc. IRE Int. Conv. Rec.*, 1965, pp. 27–34, doi: 10.1109/IRECON.1965.1147520.

- [8] A. J. Green et al., "β-gallium oxide power electronics," APL Mater., vol. 10, no. 2, Feb. 2022, Art. no. 029201, doi: 10.1063/5.0060327.

- [9] M. Higashiwaki, "β-gallium oxide devices: Progress and outlook," Phys. Status Solidi (RRL) Rapid Res. Lett., vol. 15, no. 11, Nov. 2021, Art. no. 2100357, doi: 10.1002/pssr.202100357.

- [10] M. Higashiwaki and G. H. Jessen, "Guest editorial: The dawn of gallium oxide microelectronics," *Appl. Phys. Lett.*, vol. 112, no. 6, Feb. 2018, Art. no. 060401, doi: 10.1063/1.5017845.

- [11] Z. Guo et al., "Anisotropic thermal conductivity in single crystal β-gallium oxide," Appl. Phys. Lett., vol. 106, no. 11, Mar. 2015, Art. no. 111909, doi: 10.1063/1.4916078.

- [12] P. Jiang, X. Qian, X. Li, and R. Yang, "Three-dimensional anisotropic thermal conductivity tensor of single crystalline β-Ga<sub>2</sub>O<sub>3</sub>," Appl. Phys. Lett., vol. 113, no. 23, pp. 8–13, 2018, doi: 10.1063/1.5054573.

- [13] T. E. Beechem et al., "Size dictated thermal conductivity of GaN," J. Appl. Phys., vol. 120, no. 9, Sep. 2016, Art. no. 095104, doi: 10.1063/1.4962010.

- [14] Y. Song et al., "The doping dependence of the thermal conductivity of bulk gallium nitride substrates," *J. Electron. Packag.*, vol. 142, no. 4, pp. 1–10, Dec. 2020, doi: 10.1115/1.4047578.

- [15] R. Wei et al., "Thermal conductivity of 4H-SiC single crystals," J. Appl. Phys., vol. 113, no. 5, Feb. 2013, Art. no. 053503, doi: 10.1063/1.4790134.

- [16] X. Qian, P. Jiang, and R. Yang, "Anisotropic thermal conductivity of 4H and 6H silicon carbide measured using time-domain thermoreflectance," *Mater. Today Phys.*, vol. 3, pp. 70–75, Dec. 2017, doi: 10.1016/j.mtphys.2017.12.005.

- [17] S. H. Kim et al., "Thermally-aware layout design of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> lateral MOSFETs," *IEEE Trans. Electron Devices*, vol. 69, no. 3, pp. 1251–1257, Mar. 2022, doi: 10.1109/TED.2022.3143779.

- [18] T. Matsumae et al., "Low-temperature direct bonding of β-Ga<sub>2</sub>O<sub>3</sub> and diamond substrates under atmospheric conditions," Appl. Phys. Lett., vol. 116, no. 14, pp. 2–6, 2020, doi: 10.1063/5.0002068.

- [19] Y. Song et al., "Ga<sub>2</sub>O<sub>3</sub>-on-SiC composite wafer for thermal management of ultrawide bandgap electronics," ACS Appl. Mater. Interface, vol. 13, no. 34, pp. 40817–40829, Sep. 2021, doi: 10.1021/acsami.1c09736.

- [20] W. Xu et al., "First demonstration of waferscale heterogeneous integration of Ga<sub>2</sub>O<sub>3</sub> MOSFETs on SiC and Si substrates by ion-cutting process," in *IEDM Tech. Dig.*, Dec. 2019, p. 12, doi: 10.1109/IEDM19573.2019.8993501.

- [21] Z. Cheng et al., "Thermal transport across ion-cut monocrystalline β-Ga<sub>2</sub>O<sub>3</sub> thin films and bonded β-Ga<sub>2</sub>O<sub>3</sub>-SiC interfaces," ACS Appl. Mater. Interface, vol. 12, no. 40, pp. 44943–44951, Sep. 2020, doi: 10.1021/acsami.0c11672.

- [22] M. Malakoutian et al., "Polycrystalline diamond growth on  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> for thermal management," *Appl. Phys. Exp.*, vol. 14, no. 5, May 2021, Art. no. 055502, doi: 10.35848/1882-0786/abf4f1.

- [23] N. R. Jankowski and F. P. McCluskey, "Modeling transient thermal response of pulsed power electronic packages," in *Proc. IEEE Pulsed Power Conf.*, Jun. 2009, pp. 820–825, doi: 10.1109/PPC.2009.5386368.

- [24] K. R. Bagnall and E. N. Wang, "Theory of thermal time constants in GaN high-electron-mobility transistors," *IEEE Trans. Compon.*, *Packag., Manuf. Technol.*, vol. 8, no. 4, pp. 606–620, Apr. 2018, doi: 10.1109/TCPMT.2017.2773065.

- [25] K. R. Bagnall, O. I. Saadat, S. Joglekar, T. Palacios, and E. N. Wang, "Experimental characterization of the thermal time constants of GaN HEMTs via micro-Raman thermometry," *IEEE Trans. Electron Devices*, vol. 64, no. 5, pp. 2121–2128, May 2017, doi: 10.1109/TED.2017.2679978.

- [26] B. Chatterjee, K. Zeng, C. D. Nordquist, U. Singisetti, and S. Choi, "Device-level thermal management of gallium oxide field-effect transistors," *IEEE Trans. Compon., Packag., Manuf. Technol.*, vol. 9, no. 12, pp. 2352–2365, Dec. 2019.

- [27] J. Dallas et al., "Thermal characterization of gallium nitride p-i-n diodes," Appl. Phys. Lett., vol. 112, no. 7, Feb. 2018, Art. no. 073503, doi: 10.1063/1.5006796.

- [28] A. Bar-Cohen, J. J. Maurer, and D. H. Altman, "Embedded cooling for wide bandgap power amplifiers: A review," J. Electron. Packag., vol. 141, no. 4, pp. 1–14, Dec. 2019, doi: 10.1115/1.4043404.

- [29] Z. Cheng et al., "Integration of polycrystalline Ga<sub>2</sub>O<sub>3</sub> on diamond for thermal management," *Appl. Phys. Lett.*, vol. 116, no. 6, Feb. 2020, Art. no. 062105, doi: 10.1063/1.5125637.

- [30] K. J. Liddy et al., "Thin channel  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> MOSFETs with self-aligned refractory metal gates," *Appl. Phys. Exp.*, vol. 12, no. 12, 2019, Art. no. 126501, doi: 10.7567/1882-0786/ab4d1c.

- [31] J. S. Lundh et al., "Device-level multidimensional thermal dynamics with implications for current and future wide bandgap electronics," *J. Electron. Packag.*, vol. 142, no. 3, May 2020, Art. no. 031113, doi: 10.1115/1.4047100.

- [32] A. Sood et al., "Anisotropic and inhomogeneous thermal conduction in suspended thin-film polycrystalline diamond," *J. Appl. Phys.*, vol. 119, no. 17, May 2016, Art. no. 175103, doi: 10.1063/1.4948335.

- [33] D. Shoemaker et al., "Diamond-incorporated flip-chip integration for thermal management of GaN and ultra-wide bandgap RF power amplifiers," *IEEE Trans. Compon., Packag., Manuf. Technol.*, vol. 11, no. 8, pp. 1177–1186, Aug. 2021, doi: 10.1109/TCPMT.2021. 3091555.

- [34] B. Chatterjee et al., "Electro-thermal co-design of  $\beta$ -(Al $_x$ Ga $_{1-x}$ ) $_2$ O $_3$ /Ga $_2$ O $_3$  modulation doped field effect transistors," *Appl. Phys. Lett.*, vol. 117, no. 15, Oct. 2020, Art. no. 153501, doi: 10.1063/5.0021275.

- [35] B. Chatterjee, J. S. Lundh, J. Dallas, H. Kim, and S. Choi, "Electro-thermal reliability study of GaN high electron mobility transistors," in *Proc. 16th IEEE Intersociety Conf. Thermal Thermomechanical Phenomena Electron. Syst. (ITherm)*, May 2017, pp. 1247–1252, doi: 10.1109/ITHERM.2017.7992627.

- [36] E. Heller, S. Choi, D. Dorsey, R. Vetury, and S. Graham, "Electrical and structural dependence of operating temperature of AlGaN/GaN HEMTs," *Microelectron. Rel.*, vol. 53, no. 6, pp. 872–877, 2013, doi: 10.1016/j.microrel.2013.03.004.

- [37] A. C. Victor, "Heat capacity of diamond at high temperatures," J. Chem. Phys., vol. 36, no. 7, pp. 1903–1911, Apr. 1962, doi: 10.1063/1.1701288.

- [38] J. Anaya et al., "Simultaneous determination of the lattice thermal conductivity and grain/grain thermal resistance in polycrystalline diamond," *Acta Mater.*, vol. 139, pp. 215–225, Oct. 2017, doi: 10.1016/j.actamat.2017.08.007.

- [39] C. Song, J. Kim, and J. Cho, "The effect of GaN epilayer thickness on the near-junction thermal resistance of GaN-on-diamond devices," *Int. J. Heat Mass Transf.*, vol. 158, Sep. 2020, Art. no. 119992, doi: 10.1016/j.ijheatmasstransfer.2020.119992.

- [40] D. Shoemaker et al., "Diamond-incorporated flip-chip integration for thermal management of GaN and ultra-wide bandgap RF power amplifiers," *IEEE Trans. Compon., Packag., Manuf. Technol.*, vol. 11, no. 8, pp. 1177–1186, Aug. 2021, doi: 10.1109/TCPMT.2021. 3091555.

- [41] E. Ziade, J. Yang, G. Brummer, D. Nothern, T. Moustakas, and A. J. Schmidt, "Thermal transport through GaN–SiC interfaces from 300 to 600 k," *Appl. Phys. Lett.*, vol. 107, no. 9, Aug. 2015, Art. no. 091605, doi: 10.1063/1.4930104.

- [42] H. P. de Bock et al., "A system to package perspective on transient thermal management of electronics," *J. Electron. Packag.*, vol. 142, no. 4, pp. 1–11, Dec. 2020, doi: 10.1115/1.4047474.

- [43] X. Guo, Q. Xun, Z. Li, and S. Du, "Silicon carbide converters and MEMS devices for high-temperature power electronics: A critical review," *Micromachines*, vol. 10, no. 6, p. 406, Jun. 2019, doi: 10.3390/mi10060406.