# Simplified Two-Step Bidirectional Commutation Strategy for High Frequency Unity Power Factor Matrix Converter Supplying Inductive Power Transfer System

V. Oghafi <sup>a</sup>, A. Radan <sup>b</sup>, K. Abbaszadeh\* <sup>c</sup> and A. Shahirinia<sup>d</sup>

a. Department of Electrical and Computer Engineering, Khajeh Nasir University of Technology, Tehran, Iran.

b. Department of Electrical and Computer Engineering, Khajeh Nasir University of Technology, Tehran, Iran.

c. Department of Electrical and Computer Engineering, Khajeh Nasir University of Technology, Tehran, Iran.

d. Department of Electrical and Computer Engineering, University of District of Columbia, Washington DC, US.

## Abstract

The Commutation strategy of matrix converters for high-frequency unity power factor applications has been a challenge for years. The strategy should be simple, have a short duration, and possibly avoid current sensing. This paper proposes a new strategy for the bidirectional switch commutation of the three-phase to two-phase matrix converters supplying inductive power transfer (IPT) systems. This strategy's main merits are simplicity, the reduction of commutation time, and no need for detecting the load current sign, which is crucial for synthesizing the output voltage accurately. Pulse density modulation is used because of the high frequency output voltage and possibility of utilizing three phases in any particular output cycle leading sinusoidal shape of grid current. Presented simulation and experimental results verify the converter's appropriate function using the proposed strategy and a reduced switching state machine.

**keywords** Matrix converter ; Inductive power transfer ; Switch commutation ; Sinusoidal input current ; THD

## 1. Introduction

Some applications, such as contactless energy transmission systems, inductive heating, high power telecommunication, power supply, and electrical energy with high frequency, are required [1]-[3]. In the conventional systems, providing such energy needs a two-step power conversion (AC-DC-AC) that leads to higher power losses and causes to the bulky capacitor for DC-link. Besides these disadvantages, conventional converter load-side inverter such as H-Bridge naturally benefit from two-step commutation, which is crucial in high-frequency operation for accurately synthesizing the output voltage.

Inductive power transfer system is suitable for transporting power efficiently from a stationary part to the moving part over large air gap via magnetic coupling. Obviously mutual coupling within IPT is weak, therefore, to deliver the power and hence make sure that the electromagnetic equipment sizes maintain logical, it is important to operate at high frequency. Converters which are designed to high frequency application generally have two design considerations one of them is switching loss and the other is commutation time which is important to precisely synthesizing the output voltage in voltage source Inverter (VCI) or output current in current source Inverter (CSI). As mentioned in former paragraph Conventional two -step converter (AC-DC-AC) which is using H-Bridge in second part naturally use two-step commutation at the expense of high power losses due to two step conversion. To mitigate the conventional two-step converter drawbacks, an AC-AC matrix converter has emerged. It is preferred more advantages such as unity input power factor, bidirectional power flow, and low total harmonic distortion [4]. Matrix converters utilize bidirectional switches that can switch current in both directions and block the voltage. Bidirectional switches have two switches that can work in four quadrants [5]. However, four quadrants of bidirectional switches in matrix converter provide more switching states. The lack of a natural freewheeling path with the high number of active switches makes commutation more intrinsic than H-Bridge and resonant circuit. As a result, however, AC-AC matrix converter reduces power losses, its four steps commutation time still remain to alleviate.

There are many proposed methods for controlling the matrix converter. In [4], the authors propose a three-phase to two-phase matrix converter which controls the output voltage with unity input power factor using space vector modulation method with four steps commutation. In [6], the authors proposed a matrix converter to supply induction heating, which uses pulse pattern to decrease output voltage distortion and input current shaping. A four-step commutation that causes the converter's low-frequency operation has been used in [4] and [6]. In [7], the authors proposed a two-step commutation applicable for matrix converter with pulse pattern control. However, this idea suffers from low-frequency harmonics in the input current of the converter and output voltage variation because it uses two phases in any particular output cycle. Knowing that current direction commutation strategies are not applicable due to the delay of sensors in the high-frequency of the output current (up to 100KHz), the proposed method in [8],[9], and [10] are not applicable. Current should be transformed to voltage by a small series resistance or other sensors which has delay to transform current to voltage, therefore the amplitude of voltage is small enough to be perturbed by noise easily or has delay, which can cause false triggering and produce inaccurate results.

This new procedure creates a condition that any commutation between base main and normal main states of any particular region is possible, and base main states in critical and uncritical regions are the same. Thus, interval change can be easily implemented.

In this paper, the authors propose a new two-step commutation applicable to the matrix converter control method without needing voltage difference or current direction sign. This new procedure creates a condition that any commutation between base main and normal main states of any particular region is possible, and base main states in critical and uncritical regions are the same. Thus, interval change can be easily implemented. Since the proposed switching pattern have possibility of commutation between any phases in one particular output cycle the controlling procedure that has been proposed in [9] can be implemented which have the benefit of sinusoidal unity power factor of grid current. Therefore, this commutation strategy merits compared to proposed in [7] are sinusoidal grid current and controlled output voltage at the expense of complicated switching pattern.

## 2. Commutation Principles

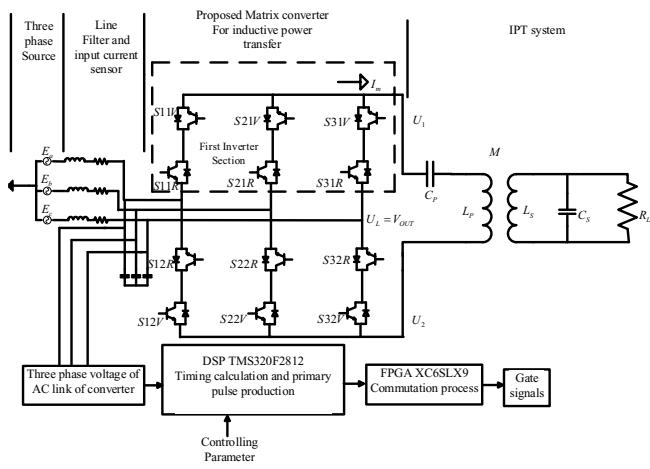

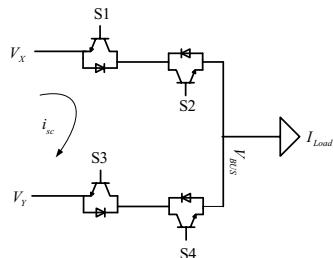

Overall schematic of the system which the proposed commutation procedure is applied is shown in Fig. 1. As it is clear a three phase LC filter and conventional topology for three phase to two phase matrix converter is used and parallel-series configuration for IPT utilized because this topology resonant frequency is not changed by varying the load. Inductive power transfer system design is thoroughly discussed in [11].

Three phase to two phase matrix converter.

In [7]-[8], the output voltages of the matrix converter are described as a function of the switching state of bidirectional switches  $c_{i,k}$  and input phase voltages:

$$\begin{aligned} U(t) &= \begin{bmatrix} u_1(t) \\ u_2(t) \end{bmatrix} \\ &= \begin{bmatrix} c_{1,1}(t) & c_{2,1}(t) & c_{3,1}(t) \\ c_{1,2}(t) & c_{2,2}(t) & c_{3,2}(t) \end{bmatrix} \\ &= C^T(t) \begin{bmatrix} u_{E_a}(t) \\ u_{E_b}(t) \\ u_{E_c}(t) \end{bmatrix} \end{aligned} \quad (1)$$

According to Fig. 1 and using (1), the output voltage can be written as bellow:

$$\begin{aligned} U_L &= U_1(t) - U_2(t) \\ &= (1 \ -1)U(t) \\ &= (1 \ -1)C^T(t) \begin{bmatrix} u_{E_a}(t) \\ u_{E_b}(t) \\ u_{E_c}(t) \end{bmatrix} \end{aligned} \quad (2)$$

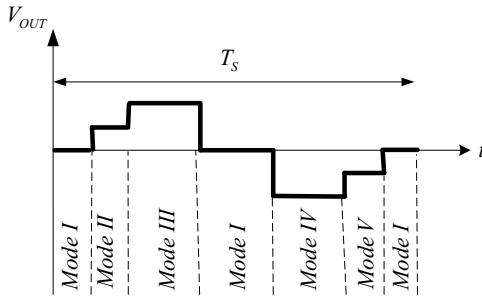

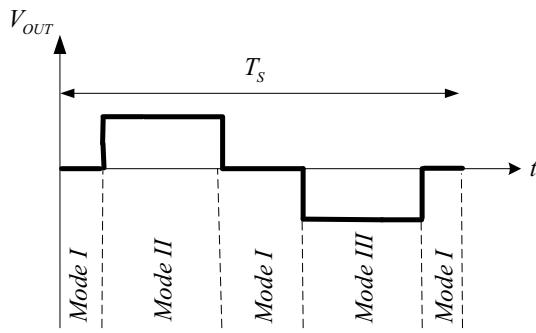

Fig. 2 and Fig. 3 show the output voltage of the converter in critical and uncritical regions (see Fig. 4). Their modes duration has been calculated in [9] to have constant output voltage and sinusoidal input current with unity power factor. Output voltage in the uncritical region.

Output voltage in the critical region.

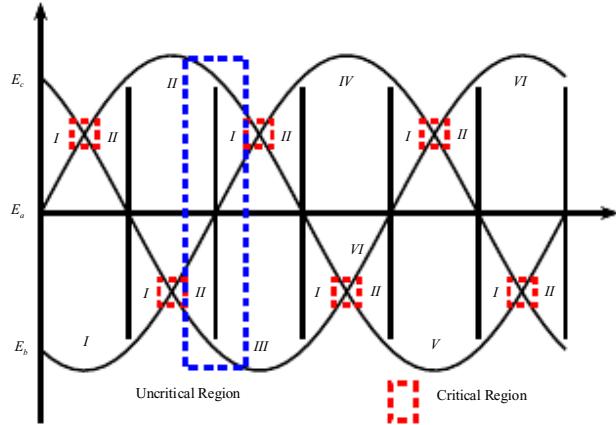

Twelve uncritical and six critical regions of one input three-phase voltage period. Each main interval has two subintervals that I and II distinguish.

According to [11] the rate of power transfer in IPT system is proportional to squared of applied voltage frequency, therefore converter should work in high frequency that leads to follow commutation procedure that needs the least commutation time. Although some commutation strategies have been proposed in recent years [12], In some converters, such as the proposed one, the conditions differ with three-phase matrix converters. Also, [13] uses a four-step commutation for a three-phase to two-phase matrix converter, which is not always applicable. Omitting two unusual commutation strategies called basic current commutation breaks the principles of switching laws, especially soft switching techniques [13]. There are two major strategies for bidirectional switch commutation 1) current-direction-based strategies [14]-[16] and 2) voltage-direction-based strategies [10] and [17]. The other commutation strategies are based on both current-direction and voltage-magnitude. In the current base method knowing the direction of the current makes a condition to switch unidirectional pass for commutation. The commutation sequence is arranged in the voltage base method so that no short circuit will happen, and the load current will not be interrupted. Due to delay in the current sensor, one of the predicaments is to accurately determine current signs, especially in zero-crossing time [18]. Thus, it is not practical to use the current sign in the commutation strategy. As a result, inevitably voltage-magnitude-base strategy is used in the high-frequency operation of the matrix converter.

### 2.1. Driving the Base Switching States of the Matrix Converter

In order to develop a switching state, it is necessary to remember that the synthesizing of the output voltage can be divided into two

sections of the converter ((1) first inverter section: three bidirectional switches on the upside, (2) second inverter section: three bidirectional switches in the downside). Depending on which voltage is produced, both sections should have switched to reach the goal. The switching state should be altered within one input period. The input three-phase voltage can be separated into twelve uncritical (six main intervals with two subintervals) and six critical regions following Fig. 4. In each main interval, one input line is the absolute maximum input voltage  $U_{E_{Max}}$  or absolute minimum input voltage  $U_{E_{Min}}$  and two non-peak voltage magnitudes determine two subintervals.

Knowing the basic rules of commutation, which is generally described in [19], and turning ON all of the switches that do not cause a short circuit in any switching states leads to abate the total commutation time. It also provides additional freewheeling paths for the load current in the case of any unpredicted happens. Due to the mentioned criteria, two types of switching states in two regions can be developed.

### 2.1.1. Critical Region

As shown in Fig. 5 in the critical region, an error-detection becomes critical at zero crossing phase-to-phase voltage between two non-peak voltage phases. An inaccurate selection of switching states will cause a short circuit two input non-peak voltage phases.

To clarify more, suppose that  $V_{YX} \geq 0$  then above arrangement of switches is reasonable. In case of error detection, short circuit current can flow when (3) is satisfied.

$$V_{YX_{cri}} < 2(V_{CE} + V_D) \quad (3)$$

Short circuit possibility in case of zero crossings of  $V_{YX}$ .

Where  $V_{YX_{cri}}$ ,  $V_{CE}$  and  $V_D$  are the boundary of critical voltage, collector-emitter voltage, and diode forward voltage, respectively. Depending on utilized power switches, the boundary of critical region voltage is between [19]-[22]:

$$V_{YX_{cri}} \approx 8.6V \text{ to } 10V \quad \text{IGBT + diode}$$

$$V_{YX_{cri}} \approx 5V \text{ to } 5.2V \quad \text{RBIGBT} \begin{cases} \text{reverse Blocking isolated} \\ \text{Gate Bipolar Transistor} \end{cases}$$

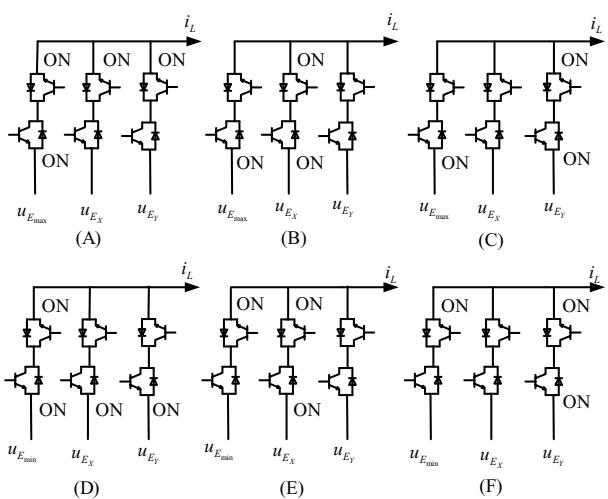

Equation (3) shows that, however supposing  $V_{YX} \geq 0$  is enough to avoid a short circuit, but in case that  $V_{YX}$  has a small boundary, a short circuit will happen. Therefore, none of the switches associated with the non-conducting non-peak phase have been turned ON in the critical region. Hence, only both switches of the conducting phases have been turned ON. For example, switch  $S_2$  in Fig. 5 should be turned OFF in the case of a critical region. As a result, in critical regions, to have a two-step commutation without any risk of a short circuit, the main switching states that are shown in Fig. 6 should be used. It is very similar to states reported in [7]. States A, D are the base main states, and B, C, E and F are normal main states.

### 2.1.2. Uncritical Region

Knowing that satisfying the basic conditions and considering the two basic switching laws, the main switching states can be derived (Fig. 7). These switching states demonstrate the possible maximum of unidirectional switches turned ON, without any input phase short circuit. States A and D with the bidirectional connection of  $U_{E_{Max}}$  or  $U_{E_{Min}}$  are called base main states (like critical region), while the other states H, I, J and K are normal main states of this region. Table I shows the switching states of the first inverter section for both regions.

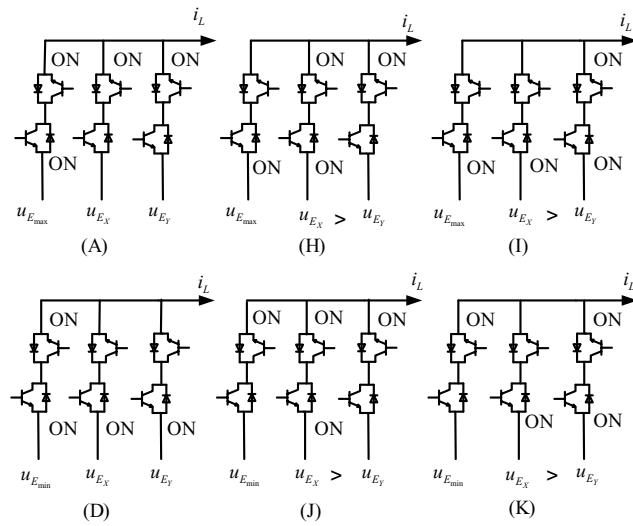

## 2.2. Two-Step Commutation

The switching table I, including the switching states in the first inverter section of the matrix converter, is available for all intervals. It confirms that a voltage-magnitude-based two-step commutation can be implemented since there are already turned unidirectional switches of the non-conducting input phase ON. Moreover, like phase shift control of H-bridge that diodes provide a freewheeling pass for load current, in this case, these non-conducting switches and diodes perform like H-Bridge diodes. Fig. 8 shows an examination of commutation of matrix converter, which more describes the two commutation steps:

- 1) Turning OFF the unidirectional switch, which will be OFF in the next main state.

- 2) Turning ON the unidirectional switches, which will be ON in the next main state.

Main switching states for matrix converter in a critical region for first section inverter in case of maximum  $U_{E_{Max}}$  or minimum  $U_{E_{Min}}$  of the input voltage.

7 Main switching states for matrix converter in the uncritical region for first section inverter in case of maximum  $U_{E_{Max}}$  or minimum  $U_{E_{Min}}$  of the input voltage.

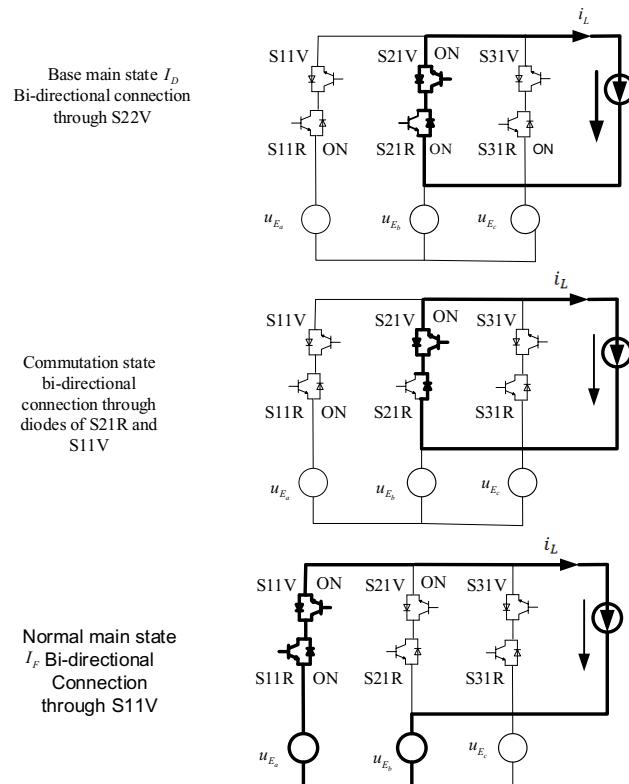

Current commutation at three-phase to two-phase matrix converter in the interval I:  $u_{E_b} < u_{E_a} < u_{E_c}$  with  $S22R$  and  $S22V$  is turned ON, and the load is modeled as a current source.

The commutation of two sections of matrix converter which are produced output voltage are similar and, in principle, are independent of each other. The only constrain is that both sections must provide a bidirectional connection for the load. This restriction is fulfilled by using a switching state for both sections of the matrix converter. As it is clear, commutation at both inverter sections must take place simultaneously. The number of unidirectional switches that must have turned on and OFF during a two-step commutation between main switching states generally depends on the beginning state and the final switching states, and the region. In total, the maximum number of switches that should be turned ON and OFF in the critical region equals three, and in the uncritical region equals two. Besides, soft commutation occurs depending on the magnitude of the incoming and outgoing phase voltage and load current sign.

### 3. Switching State Machine

A general view of the commutation is needed to synthesize output voltage and converter operation. The commutation requirement between the main states of one specific interval and between the main states of adjacent intervals gives possible commutations that satisfy the switching laws.

#### 3.1. Driving All Possible Commutations

In this section, all possible commutations during both regions are derived.

##### 3.1.1. Critical Region

In the critical region, a direct two-step commutation interval (for example  $I_E$  to  $I_F$ ) is not possible at any time due to a unidirectional connection of the load during the commutation. Therefore, an intermediate state such as the base main state for commutation can be used. Moreover, commutation between the base main state of the adjacent interval is needed when interval changes are relayed on the individual source ON switches and desired final state. For example, commutation  $III_F$  to  $IV_B$  is possible.

##### 3.1.2. Combination of Critical and Uncritical Region

Connecting commutation in critical and uncritical regions is a matter that should be solved. Although the two regions' normal main states differ, the base main states in any main interval are the same. Therefore, one solution is to use the base main state as an intermediate state, and the other one is to commutate between main states (for example  $I_{I_K}$  to  $I_F$ ). These two procedures can alleviate the problem. Analyzing of switching state table brought about to that there are many commutations possibility between states of the same and adjacent intervals. In [7], two conditions have been stated: if one of them becomes true, the commutation is not possible. These conditions are:

1) The next state (N) has no ON switch in the bi-directionally switched phase of the current state (C). For example,  $I_F^C$  to  $I_E^N$  or  $I_B^C$ .

2) The current state (C) has no ON switch in the bi-directionally switched phase of the next state (N). For example,  $II_B^C$  to  $II_C^N$  or  $IV_B^C$  to  $V_F^N$ .

Both conditions may be true only in critical regions since, in uncritical regions, there is always at least one ON switch in any phase.

A mathematical expression of the condition mentioned above is  $M$ , where  $M = 1$  means that two-step commutation is possible:

$$M = \left\{ \left( \left[ S_{11V}^C \& S_{11V}^N \right] \parallel \left[ S_{21V}^C \& S_{21V}^N \right] \parallel \left[ S_{31V}^C \& S_{31V}^N \right] \right) \right. \\ \left. \& \left( \left[ S_{11R}^C \& S_{11R}^N \right] \parallel \left[ S_{21R}^C \& S_{21R}^N \right] \parallel \left[ S_{31R}^C \& S_{31R}^N \right] \right) \right\} \quad (4)$$

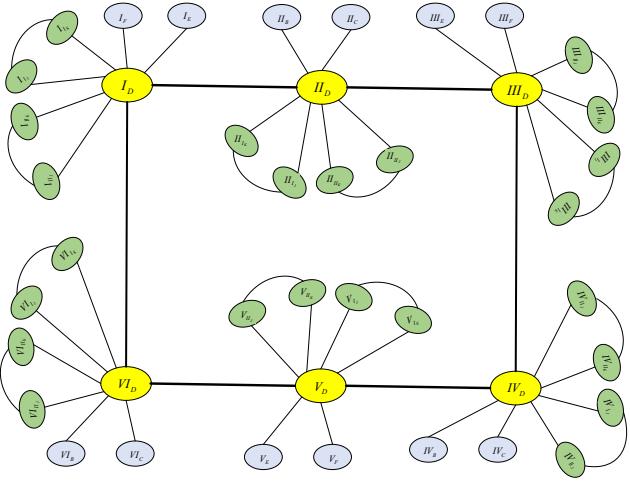

### 3.2. Reduced State Machine

The commutation's philosophy is the converter's safe operation and generating the output voltage according to the switching pattern, which is dictated by the converter's control procedure. Looking to table I, it is clear, all of the possible commutations between states don't need since some of them don't change the output voltage (for example  $II_A$  to  $III_{I_J}$ ) and the other more important reason to

eliminate some of the unused commutations is the nature of the controlling method of the converter, according to Fig. 2 and Fig. 3 in any output cycle, except commutation of two non-peak voltages in uncritical regions, there is always base main state between normal main states (for example commutation from  $I_F$  to  $II_B$  or  $I_{I_K}$  to  $I_F$  are possible but still are useless). Thus, a reduction in switching state machine is necessary because of a simple implementation. As a result, only commutation states in Fig. 9 remain to use.

Applied simplified switching state machine in the simulated and implemented circuit (yellow: base-main states; green: normal-main states in the uncritical region; and blue: normal-main states in the critical region; line shows commutation possibility and needs).

#### 4. Simulation Results

For confirming the appropriate function of the proposed two-step commutation matrix converter with the reduced state machine, simulations have been performed using the parameters of Table 2 in MATLAB Simulink/Simscape. It is worth noting that the parameters of power switches used in the implemented setup were chosen to achieve more accurate results from the simulation.

As mentioned earlier, the state machine of Fig. 9 gives only gating signals for the first inverter section. It is necessary to determine gate signals for the second inverter section. It is clear that both inverter sections work like each other with  $\left(\frac{1}{2f_s}\right)$  delay. Thus, having one inverter section can solve this dilemma ( $f_s$  is switching frequency of matrix converter). The most important points that should be zoomed are:

- 1) Interval change and uncritical region commutation.

- 2) Critical region commutation.

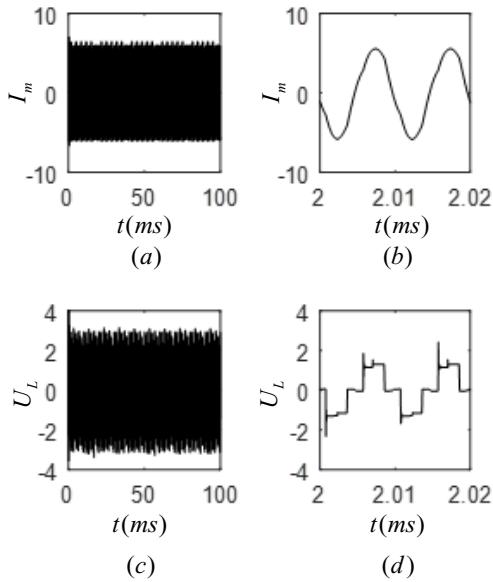

Fig. 10 illustrates the output voltage and current at the resonant frequency. The constant amplitude of current demonstrates that the voltage's fundamental component is constant either. The converter operates at a resonant frequency according to the controlling method. Therefore, frequencies below or above resonant frequency are not discussed.

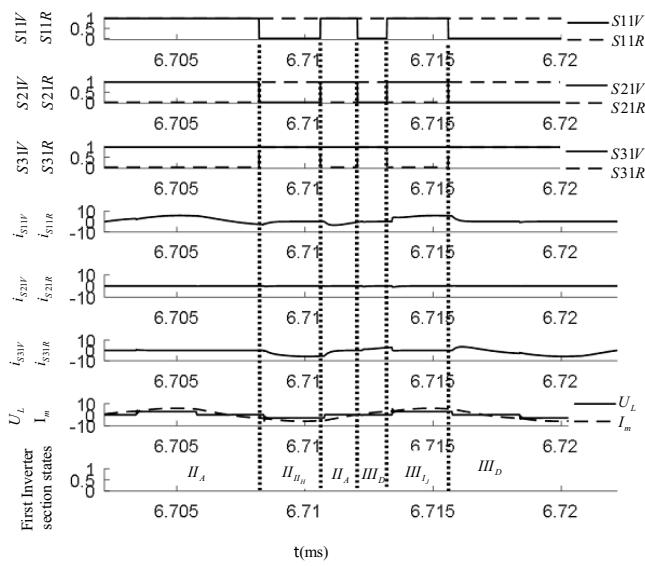

Fig. 11 depicts the interval change and uncritical region commutation. In an uncritical situation, where the interval changes from interval II to III at time 6.7121ms, since  $U_{E_b}$  is almost zero, and the control method time designation is proportional to the phase voltage magnitude. Thus, the time designated to phase b is zero. The gate signals that the interval changes without any load break and losing voltage fixed amplitude ( $(U_{E_a} = |U_{E_c}|)$ ) is in this figure.

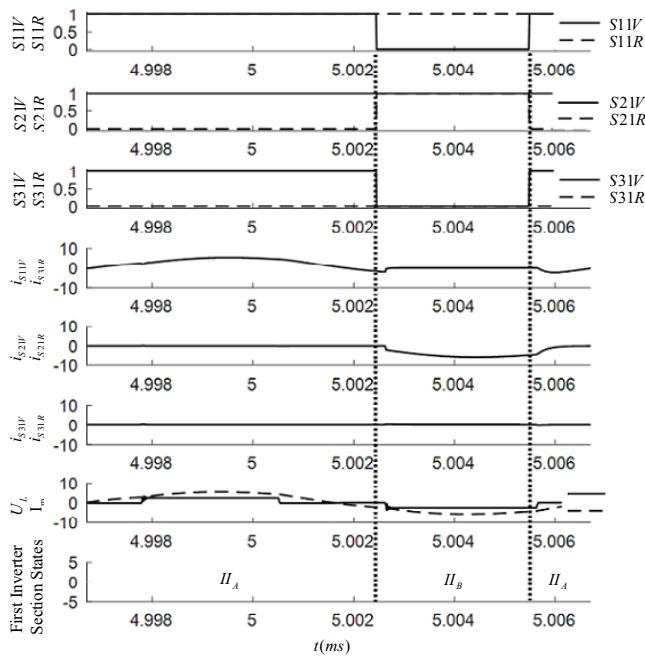

The first cycle of output voltage and current is in interval II and the second one is in interval III. Fig. 12. shows the gate signals and switch current in the critical region at any state, again it is clear no-load current break occurs at all.

The first cycle of output voltage and current is in interval II and the second one is in interval III. Fig. 12. shows the gate signals and switch current in the critical region at any state, again it is clear no-load current break occurs at all.

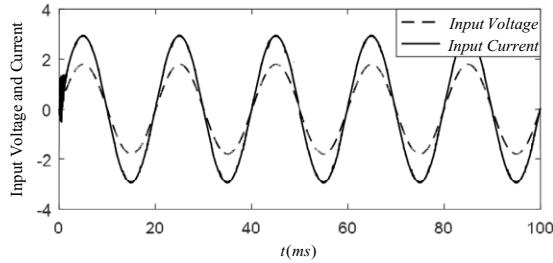

Fig. 13 proves that the proposed commutation method has appropriately worked, and as a result, grid voltage and current are approximately pure sinusoidal.

Simulated output current and the output voltage at resonant frequency  $f_r=100\text{KHz}$ . The constant amplitude of the output current proves that the converter output voltage is controlled(Volt/Div=100, A/Div=1).

Gate signals and currents of IGBTs and states of first inverter section and output voltage and current of the matrix converter are illustrated for uncritical region commutation and interval change from interval II to III.

Gate signals and currents of IGBTs, as well as states of the first inverter section and output voltage and current of the matrix converter, are illustrated for critical region commutation in interval II ( $U_{E_{a_{Max}}}$  and  $U_{E_b} \approx U_{E_c}$ ).

Grid input voltage and current (volt/Div=50 and A/Div=1).

#### 5. Experimental Results

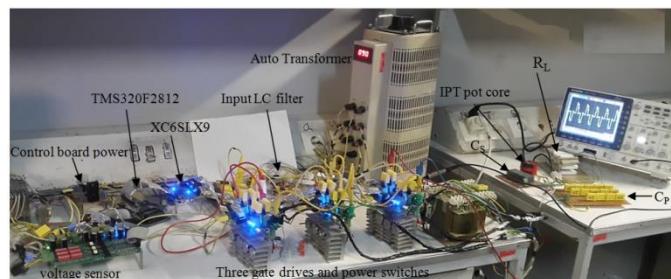

The proposed converter has been implemented for practical verification. The implemented setup includes a three-phase to two-phase matrix converter using IGBT switch IXGH48N60C3D1 as a power switch, using a digital signal processor (DSP) TMS320F2812 for the control application, and field-programmable gate array (FPGA) XC6SLX9 for the commutation process as shown in Fig. 14. The simulation and experimental parameters have been considered identical to validate the proposed bidirectional commutation method's functionality. For closer comparison, the implemented circuit parameters are set similar to the simulation one. The experimental results depict that there is neither a load break nor a short circuit. Fig. 15 shows ferrite pot cores that is used in IPT system.

Hardware implemented circuit.

. Ferrite pot cores for implemented IPT system.

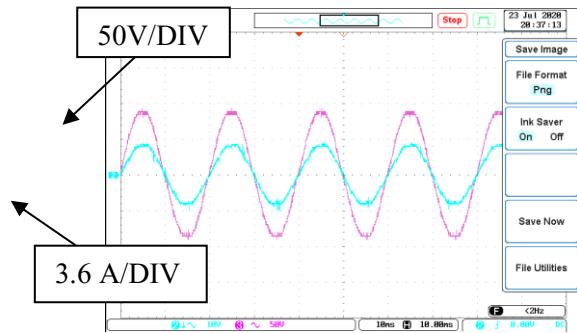

Fig. 16 clearly demonstrates that the grid's current is sinusoidal and has unity input power factor, therefore it proves that proposed commutation method works properly on entire input voltage period. In critical regions, there are a little disturbance in grid current. This is caused by same time designation to the two phases which are in critical region while their voltage amplitude are not exactly same as each other. Thus, input current shaping is not done proper to the phase voltage amplitude.

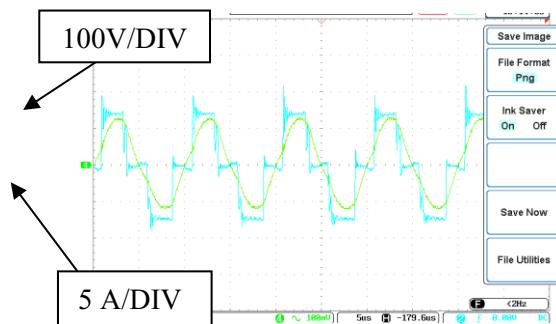

Fig. 17 illustrates the converter's output voltage and current (IPT input voltage and current) and demonstrates unity power factor condition of output for maximum power transfer. In some voltage transition there are oscillations which is produced by reverse recovery current of the conducting diode when turned off by reverse voltage applied by changing switching state which creates resonant with leakage inductance and snubber capacitance. The output current is not purely sinusoidal due to the low quality factor of equivalent resonant tank of IPT system.

Experimental results for the grid's input voltage and current.

Experimental results of the IPT input voltage and current.

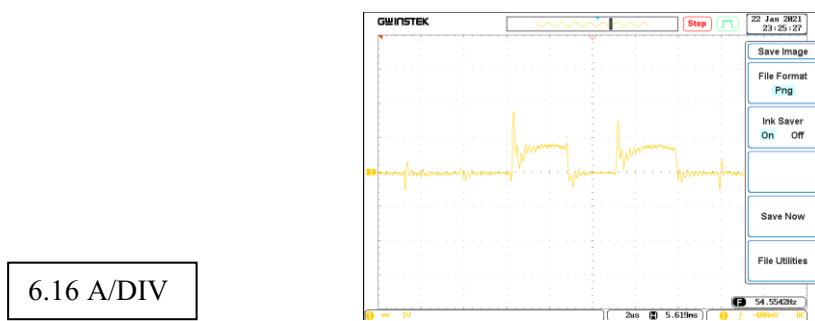

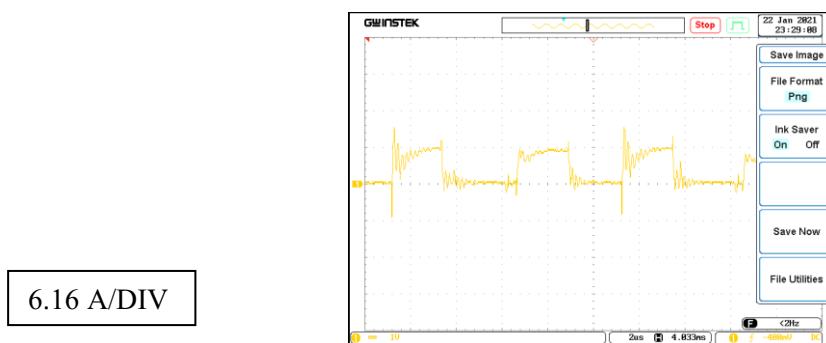

Fig.18 and 19 depict phase A current waveforms in the critical and uncritical regions, respectively. As it is apparent, phase A conducts the output current only in half cycle for the critical regions and in both half cycles for the uncritical regions. Current spikes are due to the resonant of reverse recovery current of the diodes with leakage inductance and snubber capacitance.

Experimental results for phase A current in the critical region.

Experimental results for phase A current in the uncritical region.

As a result, Table 3 shows a brief comparison between proposed switching pattern and proposed in [7].

## 6. Conclusion

This paper proposes a two-step commutation procedure for a three-phase to two-phase matrix converter that feeds an IPT circuit using a reduced state machine. The proposed two-step communication is based on the voltage-magnitudes and hence doesn't need current sensors. The sign of output current does not affect the switching pattern because of the existence of a bidirectional pass at any time and state. The strategy deals with both critical and uncritical well and reduces the commutation time using a reduced state machine. Experimental results verify the simulation results, and both demonstrate the appropriate function of commutation strategy with the reduced state machine. There is neither a load current break nor a short circuit because of a commutation failure at all. The results illustrate sinusoidal input currents and constant output voltage to satisfy an IPT matrix converter application's objective, however, converter input current in [7] is like three phase full bridge rectifier and there is no controllability on output voltage.

## References

1. Lee, T.S; Huang, SJ; Dai, SH; "Contactless power transfer for rail-guided vehicles with power equalization and efficiency improvement consideration", IEEE Transaction on Industrial electronics, Vol. 69, pp. 3566-3576, April 2022.

2. Kawashima, R; Mishima, T; Ide, C; "Three phase to single phase multi resonant direct AC-AC converter for metal hardening high frequency induction heating ", IEEE Transaction on power electronics, Vol. 36 , no. 1, pp. 639-653, Jan 2021.

3. Ratanapanachote, S ., Cha, H.J., Enjeti, P.N; : "A digitally controlled switch-mode power supply based on matrix converter", IEEE Trans Power Electron, Vol. 21, no. 1, PP. 124 - 130, Jan. 2006.

4. Safayatullah, M.D; Elaris, M.T; Ghosh, S; et al.; "A comprehensive review of power converter topologies and control methods for electric vehicle fast charging applications", IEEE Access, vol. 10, No.21686867 PP. 40753-40793, April 2022.

5. Ammar, A; Y.Kanaan, H; Moubayed, N; et al.: "A review on three phase AC/AC power converters derived from the conventional indirect matrix converter", IEEE international conference on Industrial technology, No.19532509, April. 2020.

6. Ngo-Phi, T; Nguyen-Quang, N; :"Variable pulse density modulation for induction heating", International symposium on electrical and electronics engineering, April 2021.

7. Ecklebe, A., Lindemann, A., Schulz, S; :"Bidirectional switch commutation for a matrix converter supplying a series resonant load", IEEE Trans. Power Electron, Vol. 24, NO. 5 PP, 1173 - 1181. May 2009.

8. Xie, J; Henneberg, D; Suberski, M; et al.: "Analysis and implementation of a novel four-step commutation method for direct matrix converters based on FPGA and DSP", European conference on power electrics and applications, No. 21259570, Oct 2021.

9. Oghafi, V., Radan, A.: "A bidirectional switch commutation for high-frequency UPF matrix converter supplying inductive power transfer system", Power Electronics, Drive Systems, and Technologies Conference (PEDSTC), 2014 5th, 5-6 Feb 2014.

10. Li, S; Cao, S; Liu, X; et al.: "A new four step commutation method for indirect matrix converter with active-voltage vectors being applied", IEEE journal of emerging and selected topics in power electronics, vol. 11 , No. 23514748, pp. 3949-3956, March 2023.

11. Wang, C,S; Stielau, O.H; Covics, G.A; "Design considerations for a contactless electric vehicle battery charger," IEEE Trans Ind. Electron,vol.52, no. 5, pp. 1308-1314, October 2005.

12. Ramalho, A.W.S; Vitorinio, M.A; Correa, M.B.D.R; et al.; "New Family of two-to-three phase AC-AC indirect matrix converters with open-end rectifier stage", Vol. 58, No. 1, pp. 517-530, Nov 2021.

13. Purgat, P; Bandyopadhyay, S; Qin, Z; et al.; "zero voltage switching criteria of triple active bridge converter", IEEE Transaction on power electronics, Vol. 36, No. 5 ,pp. 5425-5439, Sep 2020.

14. Ming, L; Ding, W; Chiang Loh, P; et al.; "An FPGA-Based Fault-Tolerant Method for reliable current commutation of direct matrix converter", IEEE International power electronics and motion control conference Nanjing China , no. 20547384, March 2021.

15. Empringham, L., Wheeler, P., Clare, J; "Bi-directional switch commutation for matrix converters", presented at the EPE conf, Lausanne, Switzerland, 1999 (on CD).

16. Casadei, D., Trentin, A., Matteini, M., et al.: "Matrix converter commutation strategy using both output current and input voltage sign measurement," presented at the EPE conf, Toulouse, France, 2003 (on CD).

17. Pipolo, S; Formentini, A; Trentin, A; et al.; Calvini, M; Venturini, M;"A novel matrix converter modulation with reduced number of commutations", IEEE Transactions on Industry applications, Vol. 57, No. 5, pp. 4991-5000, June 2021.

18. Dat Dao, N; Lee, D.C; "Modulation of bidirectional AC/DC Converters based on half-bridge direct-matrix structure", IEEE Trans Power Electronics, Vol. 35, No. 12 PP. 12657 - 12662, May 2020.

19. Mahlein, J., Igney, J., Weigold, J., et al.: "Matrix converter commutation strategies with and without Explicit input voltage sign measurement", IEEE Trans. Ind. Electron., Vol. 49, No. 2, PP. 407 - 414, Apr. 2002.

20. Power semiconductors, IGBT Modules, Siemens Data Book, Munich, Germany, 1996.

21. Power electronics, Semicron Data Book, Numberg, Germany, 1998.

22. IXYS Semiconductors Advanced technical information data sheet IXRH 50R80/60 IGBT with reverse blocking capability. [online]. Available: [www.ixys.net/1400.pdf](http://www.ixys.net/1400.pdf).

**Fig. 1** Three phase to two phase matrix converter.

**Fig. 2** Output voltage in the uncritical region.

**Fig. 3** Output voltage in the critical region.

**Fig. 4** Twelve uncritical and six critical regions of one input three-phase voltage period. Each main interval has two subintervals that I and II distinguish.

**Fig. 5** Short circuit possibility in case of zero crossings of  $V_{YX}$ .

**Fig. 6** Main switching states for matrix converter in a critical region for first section inverter in case of maximum  $U_{E_{Max}}$  or minimum  $U_{E_{Min}}$  of the input voltage.

**Fig. 7** Main switching states for matrix converter in the uncritical region for first section inverter in case of maximum  $U_{E_{Max}}$  or minimum  $U_{E_{Min}}$  of the input voltage.

**Fig. 8** Current commutation at three-phase to two-phase matrix converter in the interval I:  $u_{E_b} < u_{E_a} < u_{E_c}$  with S22R and S22V is turned ON, and the load is modeled as a current source.

**Fig. 9.** Applied simplified switching state machine in the simulated and implemented circuit (yellow: base-main states; green: normal-main states in the uncritical region; and blue: normal-main states in the critical region; line shows commutation possibility and needs).

**Fig. 10** Simulated output current and the output voltage at resonant frequency  $f_r = 100\text{KHz}$ . The constant amplitude of the output current proves that the converter output voltage is controlled (Volt/Div=100, A/Div=1).

**Fig. 11** Gate signals and currents of IGBTs and states of first inverter section and output voltage and current of the matrix converter are illustrated for uncritical region commutation and interval change from interval II to III.

**Fig. 12** Gate signals and currents of IGBTs, as well as states of the first inverter section and output voltage and current of the matrix converter, are illustrated for critical region commutation in interval II ( $U_{E_{aMax}}$  and  $U_{E_b} \approx U_{E_c}$ ).

**Fig. 13** Grid input voltage and current (volt/Div=50 and A/Div=1).

**Fig. 14** Hardware implemented circuit.

**Fig. 15.** Ferrite pot cores for implemented IPT system.

**Fig. 16** Experimental results for the grid's input voltage and current.

**Fig. 17** Experimental results of the IPT input voltage and current.

**Fig. 18** Experimental results for phase A current in the critical region.

**Fig. 19** Experimental results for phase A current in the uncritical region.

**TABLE 1**

SWITCHING STATES OF FIRST INVERTERSECTION FOR ALL INTERVALS

**TABLE 2**

SIMULATION PARAMETERS

**TABLE 3**

CAMPARISON BETWEEN PROPOSED SWITCHING PATTERN AND PROPOSED IN [7]

**Fig. 1**

**Fig. 2**

Fig. 3

Fig. 4

Fig. 5

Fig. 6

Fig. 7

Fig. 8

Fig. 9

Fig. 10

Fig. 11

Fig. 12

Fig. 13

Fig. 14

Fig. 15

Fig. 16

Fig. 17

Fig. 18

Fig. 19

**TABLE 1**

SWITCHING STATES OF FIRST INVERTERSECTION FOR ALL INTERVALS

| Interval | $U_{E_{max}}$ | $U_{E_{min}}$ | state | $S_{1I}V$ | $S_{1I}R$ | $S_{2I}V$ | $S_{2I}R$ | $S_{3I}V$ | $S_{3I}R$ |

|----------|---------------|---------------|-------|-----------|-----------|-----------|-----------|-----------|-----------|

| I        | $U_{E_b}$     | $I_D$         | 0     | 1         | 1         | 1         | 0         | 1         |           |

|          |               | $I_{IJ}$      | 1     | 0         | 1         | 0         | 1         | 1         |           |

|          |               | $I_{IK}$      | 1     | 1         | 1         | 0         | 0         | 1         |           |

|          |               | $I_E$         | 0     | 0         | 1         | 0         | 1         | 1         |           |

|          |               | $I_F$         | 1     | 1         | 1         | 0         | 0         | 0         |           |

|          |               | $I_{IIJ}$     | 0     | 1         | 1         | 0         | 1         | 1         |           |

|          |               | $I_{IJK}$     | 1     | 1         | 1         | 0         | 1         | 0         |           |

|          |               | $I_{IA}$      | 1     | 1         | 1         | 0         | 1         | 0         |           |

|          |               | $I_{IH}$      | 0     | 1         | 1         | 1         | 0         | 1         |           |

|          |               | $I_{II}$      | 0     | 1         | 1         | 0         | 1         | 1         |           |

| II       | $U_{E_a}$     | $II_B$        | 0     | 1         | 1         | 1         | 0         | 0         |           |

|          |               | $II_C$        | 0     | 1         | 0         | 0         | 1         | 1         |           |

|          |               | $II_{IIH}$    | 0     | 1         | 1         | 1         | 1         | 0         |           |

|          |               | $II_{II}$     | 0     | 1         | 0         | 1         | 1         | 1         |           |

|          |               | $III_D$       | 0     | 1         | 0         | 1         | 1         | 1         |           |

|          |               | $III_{IJ}$    | 1     | 1         | 1         | 0         | 1         | 0         |           |

|          |               | $III_{IK}$    | 0     | 1         | 1         | 1         | 1         | 0         |           |

|          |               | $III_{IE}$    | 1     | 1         | 0         | 0         | 1         | 0         |           |

| III      | $U_{E_c}$     | $III_F$       | 0     | 0         | 1         | 1         | 1         | 0         |           |

|          |               | $III_{IIJ}$   | 1     | 1         | 0         | 1         | 1         | 0         |           |

|          |               | $III_{IJK}$   | 1     | 0         | 1         | 1         | 1         | 0         |           |

|          |               | $IV_A$        | 1     | 0         | 1         | 1         | 1         | 0         |           |

|          |               | $IV_{IH}$     | 0     | 1         | 0         | 1         | 1         | 1         |           |

|          |               | $IV_{II}$     | 1     | 1         | 0         | 1         | 1         | 0         |           |

|          |               | $IV_B$        | 0     | 0         | 0         | 1         | 1         | 1         |           |

|          |               | $IV_C$        | 1     | 1         | 0         | 1         | 0         | 0         |           |

|          |               | $IV_{IIH}$    | 1     | 0         | 0         | 1         | 1         | 1         |           |

|          |               | $IV_{II}$     | 1     | 1         | 0         | 1         | 0         | 1         |           |

| IV       | $U_{E_b}$     | $V_D$         | 1     | 1         | 0         | 1         | 0         | 1         |           |

|          |               | $V_{IJ}$      | 1     | 0         | 1         | 1         | 1         | 0         |           |

|          |               | $V_{IK}$      | 1     | 0         | 0         | 1         | 1         | 1         |           |

|          |               | $V_E$         | 1     | 0         | 1         | 1         | 0         | 0         |           |

|          |               | $V_F$         | 1     | 0         | 0         | 0         | 1         | 1         |           |

|          |               | $V_{IIJ}$     | 1     | 0         | 1         | 1         | 0         | 1         |           |

|          |               | $V_{IJK}$     | 1     | 0         | 1         | 0         | 1         | 1         |           |

|          |               | $VI_A$        | 1     | 0         | 1         | 0         | 1         | 1         |           |

|          |               | $VI_{IH}$     | 1     | 1         | 0         | 1         | 0         | 1         |           |

|          |               | $VI_{II}$     | 1     | 0         | 1         | 1         | 0         | 1         |           |

| V        | $U_{E_a}$     | $VI_B$        | 1     | 1         | 0         | 0         | 0         | 1         |           |

|          |               | $VI_C$        | 0     | 0         | 1         | 1         | 0         | 1         |           |

|          |               | $VI_{IIH}$    | 1     | 1         | 1         | 0         | 0         | 1         |           |

|          |               | $VI_{II}$     | 0     | 1         | 1         | 1         | 0         | 1         |           |

|          |               | $VI_E$        | 1     | 0         | 1         | 1         | 0         | 0         |           |

| VI       | $U_{E_c}$     | $VI_F$        | 1     | 0         | 0         | 0         | 1         | 1         |           |

|          |               | $VI_{IIJ}$    | 1     | 0         | 1         | 1         | 0         | 1         |           |

|          |               | $VI_{IJK}$    | 1     | 0         | 1         | 0         | 0         | 1         |           |

|          |               | $VI_B$        | 1     | 1         | 0         | 0         | 0         | 1         |           |

|          |               | $VI_C$        | 0     | 0         | 1         | 1         | 0         | 1         |           |

**TABLE 2**

SIMULATION PARAMETERS

| Parameters                       | Symbol       | Value | Unit     |

|----------------------------------|--------------|-------|----------|

| Peak input phase voltage         | $V_m$        | 90    | $V$      |

| Input filter inductance          | $L_f$        | 65    | $\mu H$  |

| Input filter capacitance         | $C_f$        | 3.9   | $\mu F$  |

| Input current sensor             | $R_{sensor}$ | 1     | $\Omega$ |

| Primary inductance               | $L_p$        | 92    | $\mu H$  |

| Primary compensating capacitance | $C_p$        | 43    | $nF$     |

| Primary equivalent AC resistance | $R_p$        | 2.35  | $\Omega$ |

|                                    |                |      |          |

|------------------------------------|----------------|------|----------|

| Secondary inductance               | $L_s$          | 6.4  | $\mu H$  |

| Secondary compensating capacitance | $C_s$          | 390  | $nF$     |

| Secondary equivalent AC resistance | $R_s$          | .115 | $\Omega$ |

| Mutual inductance                  | $M$            | 14.8 | $\mu H$  |

| Pot cores air gap                  | $G$            | 7    | $mm$     |

| Load resistance                    | $R_L$          | 3.3  | $\Omega$ |

| Switching frequency                | $f_s$          | 100  | kHz      |

| Controlling parameter              | $\cos(\alpha)$ | 0.8  | ----     |

| Power switch                       | IXGH48N60C3D1  | ---- | ----     |

**TABLE 3**

CAMPARISON BETWEEN PROPOSED

SWITCHING PATTERN AND PROPOSED IN [7]

## Biographies

**Vahid. Oghafi** received the B.S.degree in electrical engineering from Zanjan University, Zanjan, Iran, in 2005, and the M.S. degree from Isfahan University Of Technology, Isfahan, Iran in 2007, he is currently working toward the PhD degree in KNTU. His research interests include inductive power transfer, motor drive, renewable energy, and power electronics.

| Switching Pattern | Input Current                          | Output Voltage Controllability |

|-------------------|----------------------------------------|--------------------------------|

| Proposed          | Sinusoidal                             | Yes                            |

| Proposed in [7]   | Like three phase full bridge rectifier | No                             |

electrical engineering. His research interests include high power converters and drives, modulation strategies, control of power electronics converters, wind and solar energy applications of power electronics and electric hybrid vehicles.

**Karim Abbaszadeh** received the B.S. degree in Communication Engineering from K. N. Toosi university of Technology, Tehran, Iran, in 1994, and the M.S. and Ph.D. degrees in Electrical Engineering from Amir Kabir University of Technology, Tehran, Iran, in 1997 and 2000, respectively. He joined from 2001 to 2003, as a visiting scholar at Texas A&M University, College Station. He is professor in Electrical Engineering Department, K.N.Toosi University, and Tehran, Iran. His main research interests and experience include power electronic such as Dc-Dc converter, multilevel inverter, motor control, and sensor less variable-speed drives, multiphase variable-speed drives for traction and propulsion applications fault diagnosis of electric machinery, analysis and design of electrical machines.

He has authored over 50 published journal papers in these fields. He is actively involved in presenting short courses and consulting in his area of expertise to various industries.

**Amir Shahirinia** (S'05–M'14) received B.S. and M.S. degrees from K.N.Toosi University of Tech., Tehran, Iran, and PhD from University of Wisconsin-Milwaukee in Electrical Engineering in 2003, 2005, and 2014, respectively. He also performed postdoctoral studies with the power electronics group at Rockwell Automation (Allen Bradley) from 2014 to 2016. He is currently an Assistant Professor of the Department of Electrical and Computer Engineering at the University of the District of Columbia, Washington D.C. He is also the director of Center of Excellence for Renewable Energy (CERE). His research background encompasses the areas of power systems and power electronics and ranges from optimal planning of renewable energy grid integration systems (REGIS), modeling and intelligent real-time control of REGIS, Bayesian statistical analysis and predictive modeling of REGIS, to power electronics and motor drives.