# Accurate Temperature Measurement of Active Area for Wide-Bandgap Power Semiconductors

Alireza Ramyar

Electrical Engineering

and Computer Science

University of Michigan

Ann Arbor, USA

aramyar@umich.edu

Yukun Lou

Electrical Engineering

and Computer Science

University of Michigan

Ann Arbor, USA

louyukun@umich.edu

Al-Thaddeus Avestruz

Electrical Engineering

and Computer Science

University of Michigan

Ann Arbor, USA

avestruz@umich.edu

Abstract—High breakdown voltage, low on-resistance, and high speed have made wide-bandgap power semiconductors suitable for many applications such as wireless power transfer, electric vehicles, hybrid and electric aircraft, and aerospace. However, the maximum power density of these devices is limited by the channel temperature rise. Thus, accurate temperature measurement of the active area is essential in research on wide-bandgap power semiconductors, which is often hampered by packaging and cooling methods. Employing temperature sensitive electrical parameters (TSEP) is a promising approach for the temperature measurement of power semiconductors. This paper uses a vector of three TSEPs, i.e., the gate-source voltage biased at weak, moderate, and strong inversion regions, to extract more information for accurate temperature measurement of the active area in GaN FETs.

Index Terms—GaN FETs, principal component analysis, temperature measurement, temperature sensitive electrical parameter, wide-bandgap power semiconductors.

#### I. Introduction

Due to high breakdown voltage, low on-resistance, and high speed [1], [2], wide-bandgap power semiconductors are being used in many applications such as wireless power transfer, electric vehicles, hybrid and electric aircraft, and aerospace [2]. However, the low thermal conductivity of the material and interfaces is typically one of the challenges in wide-bandgap semiconductors like GaN-based and  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>-based [2]–[5] devices. Power semiconductor devices have conduction and switching losses, which cause Joule heating within the device [5]. Low thermal conductivity hinders heat transfer from the device, which leads to channel temperature rise and limits the maximum power density of such devices [5]. Particularly, GaN FETs utilize a two-dimensional electron gas (2DEG) as their channel, and the conduction loss within this thin layer is a highly intensive heat source.

GaN FETs, particularly in power applications, are fabricated on foreign substrates such as Si due to the limitations of large-diameter freestanding GaN fabrication [6]. This may aggravate the thermal conduction problem, and using high thermal conductivity materials like SiC and diamond as the foreign substrate for GaN and  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> devices is one of

This work was supported by the National Science Foundation under Award No. 1937732.

the promising solutions to enhance the thermal characteristics of these devices [3]–[6]. Additionally, wide-bandgap power semiconductors with the highest power-density are chip-scale and do not have a package. Thus, conventional thermal management methods cannot be applied to these semiconductors. In addition to the aforementioned device-level approaches for improvement of the thermal characteristics of the high power-density wide-bandgap power semiconductors, various thermal management methods such as jumping-droplet hot-spot cooling [7], [8], liquid bridge confined boiling [9], and immersion cooling [10] have been proposed for chip-scale semiconductors. Note that accurate local temperature measurement of the active area is essential in all the aforementioned research activities on wide-bandgap power semiconductors.

A common method for temperature measurement of the semiconductors is to attach a thermo-sensitive device like a thermocouple to the device under test (DUT) [7], [8], [10], [11]. However, the thermal resistance of the contact between the thermo-sensitive device and the DUT, as well as lack of proximity to the actual heat source, adds error to the measurement [10], [12]. In other words, a thermo-sensitive device measures the temperature at the outer surface of the DUT and does not accurately detect the temperature within the active area. Another approach uses optical methods like Raman thermometry [3], [12], which usually require expensive equipment and requires clear optical access to the active area.

Employing temperature sensitive electrical parameters (TSEP) is a promising approach to measuring the temperature of power semiconductors, eliminating the need for thermo-sensitive devices and optical equipment. The basic idea of TSEP-based methods is to map a TSEP of the DUT to temperature. Different TSEP-based methods have been proposed for different power semiconductors like FETs and IGBTs. On-state resistance [9], [13], [14], threshold voltage [15], sub-threshold voltage [16], and drain current [17] are among the TSEPs used in the literature for temperature measurement of power semiconductors.

This paper uses a vector of three TSEPs, i.e., the gate-source voltage biased at weak, moderate, and strong inversion regions, to extract more information for accurate temperature measurement of the active area in GaN FETs. The DUT is

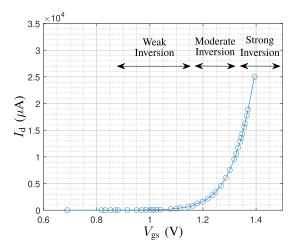

Fig. 1. Experimental example  $I_{\rm d}$  versus  $V_{\rm gs}$  of a diode-connected GaN FET illustrating different regions of operation.

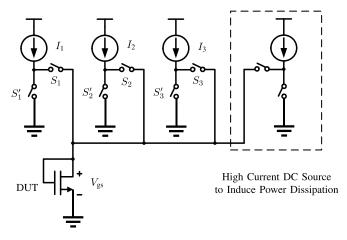

Fig. 2. Schematic of the electrical setup with a method to induce device power dissipation.

biased at three currents via precision current sources, and then corresponding voltages are synchronously detected [18] and measured. Finally, the vector of the TSEPs, which we term *temperature sensitive electrical vector* (TSEV), is mapped to temperature.

## II. TEMPERATURE MEASUREMENT METHOD

### A. Temperature Sensitive Electrical Vector

A particular categorization identifies FETs having three different regions of operation: weak, moderate, and strong inversion regions. Figure 1 illustrates the  $I_{\rm d}$ - $V_{\rm gs}$  curve of a diode-connected GaN FET with labeled regions of operation. In the strong inversion region  $V_{\rm gs} \gg V_{\rm th}$ , whereas in the weak inversion/sub-threshold region,  $V_{\rm gs} < V_{\rm th}$ . Additionally, the transition region between these two regions of operation is termed moderate inversion [19]. For a MOSFET,  $I_{\rm d}$  has a quadratic relationship with  $V_{\rm gs}$  in the strong inversion region

(in saturation mode  $V_{\rm ds} \ge V_{\rm gs} - V_{\rm th}$ ) [19],

$$I_{\rm d} \simeq \frac{\mu_{\rm n} C_{\rm ox} W}{2L} \left( V_{\rm gs} - V_{\rm th} \right)^2, \tag{1}$$

while it has an exponential relationship with  $V_{\rm gs}$  in the weak inversion region [19],

$$I_{\rm d} \simeq \frac{W I_{\rm d0}}{L} {\rm exp} \left( \frac{V_{\rm gs}}{n \left( kT/q \right)} \right),$$

(2)

where  $I_{\rm d}$  is the drain current,  $V_{\rm gs}$  is the gate-source voltage,  $V_{\rm th}$  is the threshold voltage, W is the channel width, L is the channel length,  $\mu_n$  is the mobility of electrons,  $C_{ox}$  is the oxide capacitance, n is the sub-threshold slope factor, k is the Boltzmann constant, T is the average temperature of the active area, q is the electron charge, and  $I_{d0}$  is a processed-dependent parameter that depends on  $V_{

m th}$  and source-bulk voltage  $V_{

m sb}$ [19]. Although the corresponding equations for different GaN FETs with different structures may differ from (1) and (2), the general temperature dependency remains the same [20]-[22]. From (1), and for a fixed  $I_d$ ,  $V_{gs}$  is temperature-dependent because  $V_{\mathrm{th}}$ ,  $\mu_{\mathrm{n}}$ , and  $C_{\mathrm{ox}}$  are temperature-dependent. Additionally, from (2) and for a fixed  $I_d$ ,  $V_{gs}$  is directly proportional to the temperature, while  $I_{\rm d0}$  is also temperature-dependent. This paper uses a vector of  $V_{\rm gs}$  at three biasing currents as a TSEV, i.e.,  $(V_{gs,wi}, V_{gs,mi}, V_{gs,si})$ .  $V_{gs,wi}, V_{gs,mi}$ , and  $V_{gs,si}$  are the gate-source voltage when the DUT is biased at weak, moderate, and strong inversion regions, respectively.

We configure the DUT as a diode-connected FET [23] by shorting the gate and drain, as shown in Fig. 2. Note that a diode-connected FET with  $V_{\rm gs} \geq V_{\rm th}$  is always in the saturation mode because  $V_{\rm ds} = V_{\rm gs} \geq V_{\rm gs} - V_{\rm th}$ . In order to bias the DUT at certain current values, three precision current sources (i.e.,  $I_1$ ,  $I_2$ , and  $I_3$ ) are connected to the DUT via switches  $S_1$ ,  $S_2$ , and  $S_3$ , respectively. This way, the current through the DUT alternates between these three current values. Note that switches  $S'_1$ ,  $S'_2$ , and  $S'_3$  are complementary of switches  $S_1$ ,  $S_2$ , and  $S_3$ , respectively, to short the corresponding current source to the ground while one of the other current sources is being pumped into the DUT.  $V_{\rm gs}$  is sent to the precision voltage measurement board via a Kelvin connection. On the voltage measurement board,  $V_{\rm gs}$  is then synchronously detected [18] and measured for each current source. It is worth noting that, DUT power dissipation can be induced by interleaving a high current dc source, which is also illustrated in Fig. 2.

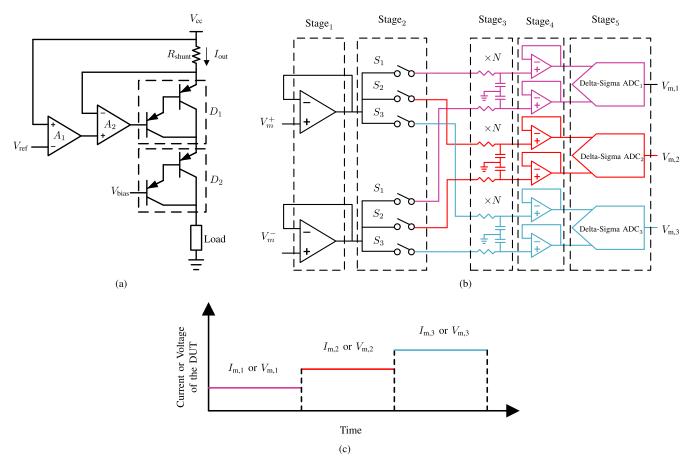

1) Precision Current Sources: The precision current sources in Fig. 2 are designed as shown in Fig. 3(a). PNP transistors, in a feedback loop closed by op-amp  $A_2$ , act as the voltage-controlled current source. Note that, in order to have a good common-mode rejection in the measurement board, the load (DUT) is grounded. Thus the current sources are floated, and we need to provide level shifting by an instrumentation amplifier  $(A_1)$ . The output current of the current sources is calculated as  $I_{\text{out}} = \frac{V_{\text{ref}}}{R_{\text{shunt}}}$ , where an accurate voltage reference provides  $V_{\text{ref}}$ . Having a high output resistance is essential for a precision current source, especially at low currents. So, PNP transistors are used because of their high output resistance. We

Fig. 3. (a) Schematic of the current sources. (b) Schematic of the measurement board. (c) Synchronous detection sequence.

cascoded [23] two Darlington [24] structures ( $D_1$  and  $D_2$ ) to further enhance the output resistance of the current sources.

The current sources are carefully designed and precision components are cautiously chosen. A precision voltage reference generates the reference voltage for the current sources. Low leakage diodes and logic-level MOSFETs are used as switches  $S_1$ - $S_3$  and  $S_1'$ - $S_3'$ , respectively. The control signals for logic-level MOSFETs come from a microcontroller (MCU) through digital isolators. The selected amplifiers have low offset voltage, low input bias current, low noise, and low-temperature drift. The shunt residences and all resistances of the voltage dividers are also precision resistances with ultra-low temperature drift coefficients.

2) Precision Voltage Measurement: Figure 3(b) shows the schematic of the measurement board.  $Stage_1$  is a buffer stage for the differential signals,  $V_{\rm m}^+$  and  $V_{\rm m}^-$ , which come from the DUT. In  $Stage_2$ , the phase of the measurement is selected via an analog switch. The control signals for the analog switch come from an MCU through digital isolators. After that, the signals are filtered by  $Stage_3$  containing N cascaded RC filters. In  $Stage_4$ , voltage-followers are used to drive the analog-to-digital converters (ADC) of  $Stage_5$ . This structure acts as a sample and hold circuit where the analog switch samples the signal and the capacitors hold the signal to be converted by an ADC [25]. Note that the outputs of  $Stage_3$

are dc signals, so we use delta-sigma ADCs, which are slow but highly accurate. A precision voltage reference generates the reference voltage for the ADCs. Finally, the ADCs send the measured values to the MCU through digital isolators using 3-wire serial peripheral interface (SPI) communication.

Note that switches  $S_1$ - $S_3$  in Fig. 3(b) are synchronous with switches  $S_1$ - $S_3$  in Fig. 2, respectively. As shown in Fig. 3(c), at each time interval, one of the current sources is pumping a certain amount of current into the DUT, which results in a specific voltage across the DUT. Using this circuitry and signal conditioning, the voltage across the DUT is synchronously detected for each current source [18]. Figure 4 shows photographs of the current source and the measurement boards.

## B. Principal Component Analysis and Polynomial Regression

Since the features, i.e.,  $V_{\rm gs,wi}$ ,  $V_{\rm gs,mi}$ , and  $V_{\rm gs,si}$ , are observed to be highly correlated, principal component analysis (PCA) is performed on the original data to reduce the multicollinearity while preserving as much information as possible. PCA is a method for dimensionality reduction that uses singular value decomposition to project the data onto a lower-dimensional space with uncorrelated variables known as principal components [26]. We then select the principal components we want to use based on their *explained variance ratio*. Explained

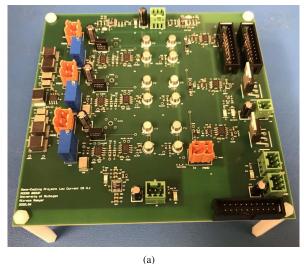

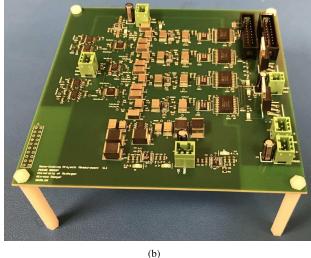

Fig. 4. Photographs of: (a) current source board, and (b) measurement board.

variance ratio is a metric for selecting principal components based on their contribution to explaining the variance in the data [26]. Here, we select the first two principal components (i.e.,  $PC_1$  and  $PC_2$ ) and find the projections of the original data onto them, i.e.,  $V_{\rm p,1}$  and  $V_{\rm p,2}$ ,

$$(V_{gs,wi}, V_{gs,mi}, V_{gs,si}) \longmapsto (V_{p,1}, V_{p,2}).$$

(3)

We then apply a  $2^{nd}$  order polynomial regression on  $(V_{p,1}, V_{p,2})$ , which results in the following equation for temperature

$$T(V_{p,1}, V_{p,2}) = C_1 + (C_2 \times V_{p,1}) + (C_3 \times V_{p,2}) + (C_4 \times V_{p,1}^2) + (C_5 \times V_{p,1} \times V_{p,2}) + (C_6 \times V_{p,2}^2),$$

(4)

where  $C_1$  is the intercept term and  $C_2$ - $C_6$  are the coefficients of the regression model.

# III. HARDWARE DEMONSTRATION

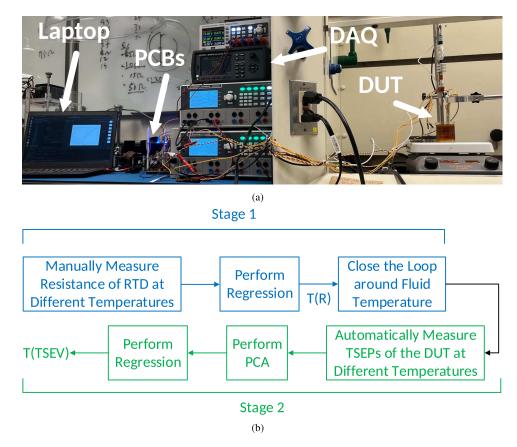

The hardware setup shown in Fig. 5(a) was used to demonstrate the measurement method. Current values of  $25\,\mu\text{A}$ , 2.5 mA, and 25 mA were selected as the biasing points of two DUTs (i.e., an EPC2019 GaN FET and an EPC2007C GaN FET) at weak, moderate, and strong inversion regions, respectively; it is worth noting that the choice of these currents needs to reflect the current density and hence depends on the device size.

#### A. Hardware Setup

The DUT, a 4-wire resistance temperature detector (RTD) probe, and an ultra-accurate digital thermometer were immersed in a beaker filled with mineral oil. The beaker was evenly surrounded with nichrome wires to symmetrically heat up the fluid and reduce the effects of thermal convection within the beaker. Additionally, a magnetic stirring bar was placed at the bottom of the beaker to rotate at 100 rpm using a magnetic stirrer. This way, we homogenize the fluid temperature, so the temperature of the GaN FET, including the temperature of the GaN FET's active area, equals the fluid temperature.

We employed a two-stage experimental procedure, as shown in Fig. 5(b). In Stage 1, the RTD probe was calibrated against an ultra-accurate digital thermometer at temperatures in the range of 300-420 K. Then, a linear regression was applied to the data to obtain T(R), which reflects temperature as a function of the resistance of the RTD probe. Finally, we closed the loop around the fluid temperature. In Stage 2, we set the fluid temperature to different values in the range of 300-420 K and automatically measured the TSEV of the DUT. After performing PCA, a polynomial regression was applied to the data to obtain T(TSEV), which is the map of the GaN FET's TSEV to the temperature of the GaN FET's active area.

# B. Hardware Results

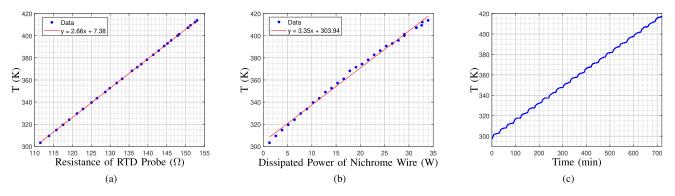

1) Stage 1: The results of Stage 1 are shown in Fig. 6. As shown in Fig. 6(a), the resistance of the RTD probe has a highly linear relationship with temperature, which is expected. Note that the slope of the plot shown in Fig. 6(b), i.e., 3.35, is the dc gain from the dissipated power of the nichrome wire to the fluid temperature. This information, together with the step response of the system (from the dissipated power of the nichrome wire to the fluid temperature), was used to model the plant and design a controller to track the fluid temperature at a reasonable speed. One of the challenges in designing the controller was the time delay due to the thermal diffusion, which was approximated by a pole and a non-minimum phase zero, i.e., first-order Padé approximation [27]. The open-loop transfer function from the dissipated power of the nichrome wire to the fluid temperature is

$$\frac{T(s)}{P(s)} = \frac{K\left(\frac{2}{T_{\rm d}} - s\right)}{\left(s + p\right)\left(\frac{2}{T_{\rm d}} + s\right)},\tag{5}$$

where p is the plant's pole,  $\frac{K}{p}$  is the dc gain, and  $T_d$  is the time delay. A PI controller was then designed and tuned to enable tracking of the fluid temperature and automation of Stage 2.

Fig. 5. (a) A photograph of the hardware setup. (b) Diagram of the experimental procedure.

Fig. 6. Hardware results of Stage 1: (a) fluid temperature versus resistance of RTD probe, (b) fluid temperature versus dissipated power of nichrome wire, and (c) example fluid temperature at different set points for closed-loop system.

Figure 6(c) shows the temperature of the fluid when we set the fluid temperature to values in the range of 300-420 K with a step size of 5 K and let it settle in 30 min. As illustrated, the controller works properly, and we are ready for Stage 2. Figures 7 and 8 show the results of Stage 2 for two different DUTs, i.e., an EPC2019 GaN FET and an EPC2007C GaN FET, respectively.

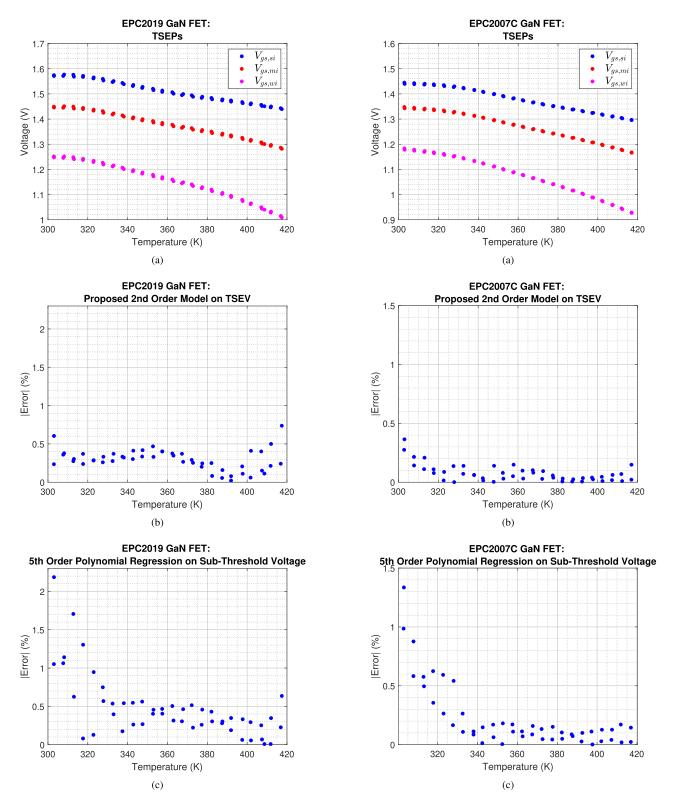

2) Stage 2: EPC2019 GaN FET: Figure 7(a) shows the measured  $V_{\rm gs,mi}$ ,  $V_{\rm gs,mi}$ , and  $V_{\rm gs,si}$  of the DUT at 49 data points. After performing PCA, we selected the first two principal components (i.e., PC<sub>1</sub> and PC<sub>2</sub>) with explained variance ratios

of 99.60% and 0.39%, respectively. We then applied a  $2^{\text{nd}}$  order polynomial regression on  $(V_{\text{p,1}}, V_{\text{p,2}})$ , which results in the following equation for temperature

$$T(V_{p,1}, V_{p,2}) = 372.86 + (38.81 \times V_{p,1}) + (10.33 \times V_{p,2}) - (14.08 \times V_{p,1}^{2}) - (2.50 \times V_{p,1} \times V_{p,2}) + (1.97 \times V_{p,2}^{2}).$$

(6)

The temperature measurement error is determined using leave-one-out cross-validation (LOOCV) [28]. For each data point, all the other data points form the training dataset of the

Fig. 7. Hardware results for Stage 2 (EPC2019 GaN FET): (a)  $V_{\rm gs, wi}$ ,  $V_{\rm gs, mi}$ , and  $V_{\rm gs, si}$  at different temperatures, (b) error at different temperatures for proposed 2<sup>nd</sup> order model on TSEV, i.e.,  $(V_{\rm gs, wi}, V_{\rm gs, mi}, V_{\rm gs, si})$ , and (c) error at different temperatures for 5<sup>th</sup> order polynomial regression on sub-threshold voltage, i.e.,  $V_{\rm gs, wi}$ .

Fig. 8. Hardware results for Stage 2 (EPC2007C GaN FET): (a)  $V_{\rm gs,wi}, V_{\rm gs,mi},$  and  $V_{\rm gs,si}$  at different temperatures, (b) error at different temperatures for proposed  $2^{\rm nd}$  order model on TSEV, i.e.,  $(V_{\rm gs,wi}, V_{\rm gs,mi}, V_{\rm gs,si})$ , and (c) error at different temperatures for  $5^{\rm th}$  order polynomial regression on sub-threshold voltage, i.e.,  $V_{\rm gs,wi}$ .

regression model, and the corresponding data point is used as the test data point. Figure 7(b) shows the values of the error, which were calculated from

$$|\text{Error}| = \left| \frac{T_{\text{actual}} - T_{\text{predicted}}}{T_{\text{actual}}} \right| \times 100,$$

(7)

where  $T_{\rm actual}$  is the measured temperature and  $T_{\rm predicted}$  is the predicted temperature by the model. As the results show, the measurement method has an accuracy of better than 99 %. For comparison, the results of a 5<sup>th</sup> order polynomial regression applied on the sub-threshold voltage (i.e.,  $V_{\rm gs,wi}$ ) is shown in Fig. 7(c). Note that both models have one intercept term and five coefficients and hence, have similar complexities. As illustrated, using three voltages at different operation regions results in a more accurate temperature measurement than the case in which we only use sub-threshold voltage.

3) Stage 2: EPC2007C GaN FET: Figure 8(a) shows the measured  $V_{\rm gs, mi}$ ,  $V_{\rm gs, mi}$ , and  $V_{\rm gs, si}$  of the DUT at 48 data points. Again, we selected the first two principal components (i.e., PC<sub>1</sub> and PC<sub>2</sub>) with explained variance ratios of 99.90% and 0.09%, respectively. We then applied a  $2^{\rm nd}$  order polynomial regression on  $(V_{\rm p,1}, V_{\rm p,2})$ , which results in the following equation for temperature

$$T(V_{p,1}, V_{p,2}) = 367.70 + (36.93 \times V_{p,1}) + (4.98 \times V_{p,2}) - (8.47 \times V_{p,1}^{2}) - (0.92 \times V_{p,1} \times V_{p,2}) + (0.67 \times V_{p,2}^{2}).$$

(8)

Figure 8(b) shows the values of the error at different data points. Similar to the case of the EPC2019 GaN FET, the measurement method has an accuracy of better than 99%. As shown, using three voltages at different operation regions results in a more accurate temperature measurement than the case in which we only use sub-threshold voltage, i.e., Fig. 8(c).

## IV. CONCLUSION

This paper investigates an accurate temperature measurement method for characterizing the thermal performance of practical wide-bandgap power devices in-situ. Through the hardware results, we showed that by (1) using a vector of three TSEPs, i.e., the gate-source voltage biased at weak, moderate, and strong inversion regions, (2) employing the principal component analysis on these three features, and finally (3) performing polynomial regression, the temperature of the active area can be measured with high accuracy.

## REFERENCES

- J. Millan, P. Godignon, X. Perpiñà, A. Pérez-Tomás, and J. Rebollo, "A survey of wide bandgap power semiconductor devices," *IEEE Transactions on Power Electronics*, vol. 29, no. 5, pp. 2155–2163, 2013.

- [2] H. A. Mantooth, K. Peng, E. Santi, and J. L. Hudgins, "Modeling of wide bandgap power semiconductor devices—Part I," *IEEE Transactions* on *Electron Devices*, vol. 62, no. 2, pp. 423–433, 2014.

- [3] Z. Cheng, S. Graham, H. Amano, and D. G. Cahill, "Perspective on thermal conductance across heterogeneously integrated interfaces for wide and ultrawide bandgap electronics," *Applied Physics Letters*, vol. 120, no. 3, p. 030501, 2022.

- [4] Z. Cheng, N. Tanen, C. Chang, J. Shi, J. McCandless, D. Muller, D. Jena, H. G. Xing, and S. Graham, "Significantly reduced thermal conductivity in β-(Al<sub>0.1</sub>Ga<sub>0.9</sub>)<sub>2</sub>O<sub>3</sub>/Ga<sub>2</sub>O<sub>3</sub> superlattices," *Applied Physics Letters*, vol. 115, no. 9, p. 092105, 2019.

- [5] Z. Cheng, M. Goorsky, F. Mu, T. Suga, and S. Graham, "Creating low thermal resistance interfaces in wide bandgap semiconductors through bonding," in 2021 IEEE CPMT Symposium Japan (ICSJ), 2021, pp. 135–137.

- [6] F. Medjdoub, Gallium Nitride (GaN): Physics, Devices, and Technology. CRC Press, 2017.

- [7] T. Foulkes, J. Oh, P. Birbarah, J. Neely, N. Miljkovic, and R. C. Pilawa-Podgurski, "Active hot spot cooling of GaN transistors with electric field enhanced jumping droplet condensation," in 2017 IEEE Applied Power Electronics Conference and Exposition (APEC), 2017, pp. 912–918.

- [8] J. Oh, P. Birbarah, T. Foulkes, S. L. Yin, M. Rentauskas, J. Neely, R. C. Pilawa-Podgurski, and N. Miljkovic, "Jumping-droplet electronics hot-spot cooling," *Applied Physics Letters*, vol. 110, no. 12, p. 123107, 2017.

- [9] T. Foulkes, J. Oh, R. Pilawa-Podgurski, and N. Miljkovic, "Self-assembled liquid bridge confined boiling on nanoengineered surfaces," *International Journal of Heat and Mass Transfer*, vol. 133, pp. 1154–1164, 2019.

- [10] P. Birbarah, T. Gebrael, T. Foulkes, A. Stillwell, A. Moore, R. Pilawa-Podgurski, and N. Miljkovic, "Water immersion cooling of high power density electronics," *International Journal of Heat and Mass Transfer*, vol. 147, p. 118918, 2020.

- [11] L. Zhu, R. F. Boehm, Y. Wang, C. Halford, and Y. Sun, "Water immersion cooling of PV cells in a high concentration system," *Solar Energy Materials and Solar Cells*, vol. 95, no. 2, pp. 538–545, 2011.

- [12] R. J. Simms, J. W. Pomeroy, M. J. Uren, T. Martin, and M. Kuball, "Channel temperature determination in high-power algan/gan hfets using electrical methods and raman spectroscopy," *IEEE Transactions on Electron Devices*, vol. 55, no. 2, pp. 478–482, 2008.

- [13] A. Koenig, T. Plum, P. Fidler, and R. W. De Doncker, "On-line junction temperature measurement of CoolMOS devices," in 2007 7th International Conference on Power Electronics and Drive Systems, 2007, pp. 90–95.

- [14] M. Wu, X.-H. Ma, L. Yang, Q. Zhu, M. Zhang, L.-A. Yang, and Y. Hao, "Accurate measurement of channel temperature for AlGaN/GaN HEMTs," *IEEE Transactions on Electron Devices*, vol. 65, no. 11, pp. 4792–4799, 2018.

- [15] H. Chen, V. Pickert, D. Atkinson, and L. Pritchard, "On-line monitoring of the MOSFET device junction temperature by computation of the threshold voltage," in 3rd IET International Conference on Power Electronics, Machines and Drives - PEMD, 2006, pp. 440–444.

- [16] R. Mandeya, C. Chen, V. Pickert, and R. Naayagi, "Prethreshold voltage as a low-component count temperature sensitive electrical parameter without self-heating," *IEEE Transactions on Power Electronics*, vol. 33, no. 4, pp. 2787–2791, 2017.

- [17] M. H. Wong, Y. Morikawa, K. Sasaki, A. Kuramata, S. Yamakoshi, and M. Higashiwaki, "Characterization of channel temperature in Ga2O3 metal-oxide-semiconductor field-effect transistors by electrical measurements and thermal modeling," *Applied Physics Letters*, vol. 109, no. 19, p. 193503, 2016.

- [18] P. Lindahl, A.-T. Avestruz, W. Thompson, E. George, B. R. Sennett, and S. B. Leeb, "A Transmitter—Receiver system for long-range capacitive sensing applications," *IEEE Transactions on Instrumentation and Measurement*, vol. 65, no. 10, pp. 2412–2423, 2016.

- [19] P. E. Allen and D. R. Holberg, CMOS Analog Circuit Design, 2nd ed. New York, NY: Oxford University Press, 2002.

- [20] B. Syamal, X. Zhou, S. B. Chiah, A. M. Jesudas, S. Arulkumaran, and G. I. Ng, "A comprehensive compact model for GaN HEMTs, including quasi-steady-state and transient trap-charge effects," *IEEE Transactions* on Electron Devices, vol. 63, no. 4, pp. 1478–1485, 2016.

- [21] S. Ghosh, S. A. Ahsan, A. Dasgupta, S. Khandelwal, and Y. S. Chauhan, "GaN HEMT modeling for power and RF applications using ASM-HEMT," in 2016 3rd International Conference on Emerging Electronics (ICEE), 2016, pp. 1–4.

- [22] K. Shah and K. Shenai, "Simple and accurate circuit simulation model for gallium nitride power transistors," *IEEE Transactions on Electron Devices*, vol. 59, no. 10, pp. 2735–2741, 2012.

- [23] A. S. Sedra and K. C. Smith, Microelectronic Circuits, 7th ed. New York, NY: Oxford University Press, 2015.

- [24] A. B. Grebene, *Bipolar and MOS Analog Integrated Circuit Design*. Hoboken NJ: Wiley, 1984.

- [25] S. A. Mahmoud and T. B. Nazzal, "Sample and hold circuits for low-frequency signals in analog-to-digital converter," in 2015 International conference on Information and Communication Technology Research (ICTRC), 2015, pp. 36–39.

- [26] F. Kherif and A. Latypova, "Principal component analysis," in *Machine Learning*. Elsevier, 2020, pp. 209–225.

- [27] J. K. Roberge, Operational Amplifiers: Theory and Practice. Wiley New York, 1975, vol. 197.

- [28] K. P. Murphy, Machine Learning: A Probabilistic Perspective. MIT press, 2012.