# Tuning Gate Potential Profiles and Current–Voltage Characteristics of Polymer Electrolyte-Gated Transistors by Capacitance Engineering

Kyung Gook Cho, Keun Hyung Lee,\* and C. Daniel Frisbie\*

Cite This: *ACS Appl. Mater. Interfaces* 2024, 16, 19309–19317

Read Online

ACCESS |

Metrics & More

Article Recommendations

Supporting Information

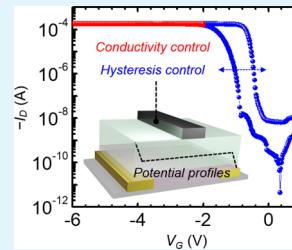

**ABSTRACT:** We demonstrate that the transfer characteristics of electrolyte-gated transistors (EGTs) with polythiophene semiconductor channels are a strong function of gate/electrolyte interfacial contact area, i.e., gate size. Polythiophene EGTs with gate/electrolyte areas much larger than the channel/electrolyte areas show a clear peak in the drain current vs gate voltage ( $I_D - V_G$ ) behavior, as well as peak voltage hysteresis between the forward and reverse  $V_G$  sweeps. Polythiophene EGTs with small gate/electrolyte areas, on the other hand, exhibit current plateaus in the  $I_D - V_G$  behavior and a gate-size-dependent hysteresis loop between turn on and off. The qualitatively different transport behaviors are attributed to the relative sizes of the gate/electrolyte and channel/electrolyte interface capacitances, which are proportional to interfacial area. These interfacial capacitances are in series with each other such that the total capacitance of the full gate/electrolyte/channel stack is dominated by the interface with the smallest capacitance or area. For EGTs with large gates, most of the applied  $V_G$  is dropped at the channel/electrolyte interface, leading to very high charge accumulations, up to ~0.3 holes per ring (hpr) in the case of polythiophene semiconductors. The large charge density results in sub-band-filling and a marked decrease in hole mobility, giving rise to the peak in  $I_D - V_G$ . For EGTs with small gates, hole accumulation saturates near 0.15 hpr, band-filling does not occur, and hole mobility is maintained at a fixed value, which leads to the  $I_D$  plateau. Potential drops at the interfaces are confirmed by *in situ* potential measurements inside a gate/electrolyte/polymer semiconductor stack. Hole accumulations are measured with gate current–gate voltage ( $I_G - V_G$ ) measurements acquired simultaneously with the  $I_D - V_G$  characteristics. Overall, our measurements demonstrate that remarkably different  $I_D$  behavior can be obtained for polythiophene EGTs by controlling the magnitude of the gate-electrolyte interfacial capacitance.

**KEYWORDS:** electrolyte-gated transistors, organic electrochemical transistors, capacitance engineering, interfacial potential drop, hysteresis

## 1. INTRODUCTION

Electrolyte-gated transistors (EGTs) have attracted great attention in the field of organic electronics due to their potential applications in artificial synapses, biosensors, and electrophysiology, for example, where interconversion of ionic and electronic currents is advantageous or essential.<sup>1–13</sup> For EGTs based on p-type polymer semiconductors, Figure 1, the electronic conductance switching mechanism is based on reversible electrochemical doping.<sup>1–5,14–16</sup> Application of a negative gate voltage  $V_G$  results in electron extraction from the polymer semiconductor through the source and drain electrodes and simultaneous insertion of anions from the electrolyte into the polymer to maintain charge neutrality. The result is a hole-doped polymer semiconductor with an electronic conductivity that depends sensitively on  $V_G$  in the ON state. Returning  $V_G$  below the threshold voltage reverses the electrochemical doping process and returns the polymer to an insulating OFF state. For EGTs based on hole conducting, chemically doped polymers such as poly(3,4-ethylenedioxythiophene):poly(styrenesulfonate) (PEDOT:PSS), the same basic operation applies but application of  $V_G$  is required to turn the devices OFF instead of ON.<sup>4,16–18</sup>

We note that EGT devices based on polymer semiconductors are also called organic electrochemical transistors (OECTs) in the literature.<sup>4,7,19–24</sup>

A variety of different gate electrode architectures are used for polymer EGTs.<sup>1–4,25–31</sup> In fact, one of attractive features of EGTs is that the gate electrode can be offset from the source-drain channel, which makes fabrication easier in some instances, albeit with a loss in switching speed.<sup>1–3,10,25–27,32</sup>

Gate electrode materials include metals such as Au, conducting polymers such as PEDOT:PSS as in Figure 1, and conducting porous carbon, for example.<sup>8,10,33–37</sup> Often times, not much attention is paid to the size of the contact area between the gate and the electrolyte, despite a few previous studies indicating that the gate electrode significantly influences

Received: January 2, 2024

Revised: February 23, 2024

Accepted: March 26, 2024

Published: April 9, 2024

**Figure 1.** (a) Scheme of a bottom-contact/top-gated polymer EGT with aerosol-jet-printed active layers. The semiconductor layer forms a 3D conductive channel with accumulated mobile hole carriers upon gate-induced electrochemical doping. Anions penetrate the layer to preserve the charge neutrality. Structures of (b) the polymer semiconductor PBTTT, (c) the [BMI][FAP] ionic liquid used to make the ionogel gate dielectric, and (d) the PEDOT:PSS conducting polymer gate electrode.

charge accumulation and EGT performance.<sup>38–40</sup> Here, we show that changing the gate–electrolyte contact area, which changes its interfacial capacitance, can have a profound impact on the measured current–voltage characteristics of EGTs. In fact, undersizing the gate electrode leads to large potential drops at the gate–electrolyte interface and produces drain current–gate voltage ( $I_D - V_G$ ) curves that saturate at large  $V_G$ ; it also causes large  $I_D - V_G$  hysteresis. Large gate–electrolyte contact areas and correspondingly large interfacial capacitances, on the other hand, ensure that all of the applied gate voltage appears at the polymer semiconductor–electrolyte interface, and this leads to the observation of a distinct conductivity peak in the transfer ( $I_D - V_G$ ) characteristics. Hysteresis is also observed, but the origin of the hysteresis for large gate devices is entirely different than for small gate devices. These two limiting gate size dependent  $I_D - V_G$  behaviors may be useful for distinct applications. However, for fundamental transport measurements, large gates, where the gate–electrolyte interfacial capacitance is at least an order of magnitude greater than the semiconductor–electrolyte capacitance, are necessary.<sup>33</sup> Previously, we have shown that managing gate capacitance is crucial to achieving 100 ns switching delays in EGTs<sup>41</sup>; here, we extend the capacitance engineering theme to show that the magnitude of the gate interfacial capacitance determines not just the magnitude but also the functional shape of the transfer characteristics.

## 2. EXPERIMENTAL SECTION

**Materials.** 1-Butyl-3-methylimidazolium tris(pentafluoroethyl)-trifluorophosphate ([BMI][FAP]) was obtained from Merck. Poly[2,5-bis(3-dodecylthiophen-2-yl)thieno[3,2-*b*]thiophene] (PBTTT), [BMI] hexafluorophosphate ([PF<sub>6</sub>]), 1-ethyl-3-methylimidazolium bis(trifluoromethylsulfonyl)imide ([EMI][TFSI]), terpineol, and ethylene glycol were purchased from Sigma-Aldrich. Regioregular poly(3-butylthiophene) (P3BT) and poly(3-hexylthiophene) (P3HT) were purchased from Rieke Metals. PEDOT:PSS (Clevios PH 1000) was obtained from Heraeus. Chloroform and ethyl acetate were purchased from Thermo Fisher.

**Device Fabrication.** To fabricate top-gated EGTs, 5 nm Cr as an adhesion layer and 45 nm Au as source (S) and drain (D) electrodes were patterned on a SiO<sub>2</sub> substrate, respectively, using thermal evaporation through a stencil mask (channel width/length = 1000  $\mu\text{m}$ /100  $\mu\text{m}$  = 10). For the side-gated EGTs, the source, drain, and gate Au electrodes were patterned onto a SiO<sub>2</sub>/Si wafer by photolithography (channel width/length = 100  $\mu\text{m}$ /20  $\mu\text{m}$  = 5). The polymer semiconductor, ionogel, and PEDOT:PSS layers were deposited sequentially with an AJ 200 benchtop aerosol jet printer (Optomec, Inc.) to prepare the bottom contact, top-gated EGTs. The carrier gas (N<sub>2</sub>) flow rates (sccm), sheath gas (N<sub>2</sub>) flow rates (sccm), and atomizer currents (A) for the semiconductor, ionogel, and PEDOT:PSS were kept at  $\sim$ 15 sccm/20 sccm/0.25 A,  $\sim$ 25 sccm/30 sccm/0.35 A, and  $\sim$ 30 sccm/40 sccm/0.45 A, respectively. The aerosol jet printing processes were conducted under ambient air conditions and a stage temperature of 60 °C. The polymer semiconductor and PEDOT:PSS gate layers were printed with a 150  $\mu\text{m}$  nozzle, and the ionogel layer was printed with a 200  $\mu\text{m}$  nozzle. We prepared semiconductor inks (PBTTT, P3BT, and P3HT) by dissolving a polymer semiconductor in chloroform at a concentration of 1 mg/mL, followed by the addition of terpineol solvent to reach 10% by volume of the ink prior to printing. To create the ionogel ink, we combined poly(styrene-*b*-ethyl acrylate-*b*-styrene) (SEAS) triblock polymer, ionic liquids (ILs), and ethyl acetate in a mass ratio of 1:9:90. The SEAS triblock copolymer used to create a gel-forming polymer network was synthesized using a previously established procedure.<sup>42</sup> In the case of the PEDOT:PSS solution, we mixed 5 wt % of ethylene glycol with an aqueous PEDOT:PSS solution to optimize ink viscosity and electronic conductivity of the gate film. All inks were stirred at a hot plate temperature of 50 °C for 2 h before use. For the PEDOT:PSS/ionogel/PBTTT capacitor, the bottom Au electrode was formed by thermally evaporating 5 nm of Cr followed by 45 nm of Au on a SiO<sub>2</sub> substrate ( $\sim$ 1  $\times$  1 cm). The PBTTT was spin-coated on the Au electrode. The solvent-cast ionogel and PEDOT:PSS were laminated sequentially on the PBTTT to form the gate/electrolyte/semiconductor stack. The Ag wire was inserted into the middle of the ionogel to make a quasi-reference electrode. To prevent electrical contact between the Ag electrode and PEDOT:PSS or PBTTT, the area of the ionogel was kept larger than those of the PEDOT:PSS and PBTTT films.

**Characterization.** The electrical characterization of EGTs was conducted under inert atmosphere using a probe station connected to Keithley 236 and 6517A source measure units. The accumulated charge carrier (hole) density ( $Q$ ) was calculated from gate current–gate voltage ( $I_G - V_G$ ) curves on the forward sweep using following equation<sup>33,43</sup>:

$$Q = \frac{\int I_G dV}{r_V} \quad (1)$$

where  $r_V$  is the  $V_G$  scan rate.  $I_G$  represents the accumulation of charge carriers, and leakage current was negligible as evident in the  $I_G - V_G$  traces. The volumetric hole density ( $p_{3D}$ ) was obtained based on the calculated  $Q$ .

$$p_{3D} = \frac{Q}{eAt_{\text{film}}} \quad (2)$$

where  $e$  is the elementary charge, and  $A$  and  $t_{\text{film}}$  are the area and thickness of the polymer semiconductor layers, respectively. The thicknesses of the films were measured by using a KLA P-7 surface profiler. The average hole mobility ( $\mu$ ) was estimated using the following equation:

$$\mu = \frac{L}{W} \frac{I_D}{ep_A V_D} \quad (3)$$

where  $p_A$  is the hole density normalized by area ( $Q/A$ ). Holes per thiophene ring (hpr) were estimated with the following equation:

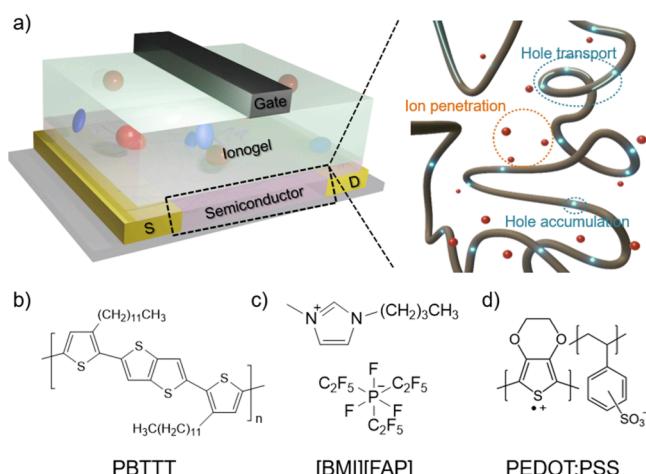

**Figure 2.** (a–c) Schemes of the PBTET EGT structures illustrating different gate sizes. (d–f)  $I_D$ – $V_G$  transfer curves corresponding to EGTs with high, middle, and low gate capacitances, respectively. (g–i) Corresponding  $I_G$ – $V_G$  traces. The thicknesses of the PBTET channels are  $\sim 50$  nm. Applied  $V_D = -0.1$  V and  $V_G$  scan rate is 50 mV/s. All transistor measurements were taken on the second  $V_G$  sweep cycle at room temperature under a nitrogen atmosphere. The ionogel was based on a [BMI][FAP] ionic liquid.

hole per thiophene ring(hpr)

$$= \frac{p_{3D} V_{\text{cell}}}{\text{number of thiophene ring/unit cell}} \quad (4)$$

where  $V_{\text{cell}}$  is the volume of the crystalline unit cell.<sup>44</sup> The thiophene ring number in each unit cell is four in all thiophene-based semiconductor polymers. We counted thieno[3,2-*b*]thiophene as two thiophene rings. Based on these equations,  $p_{3D}$  and hpr might be overestimated because the thickness expansion (e.g.,  $t_{\text{film}}$ ) of the semiconductor layers by penetrating ions is not accounted for. Additionally, eq 4 assumes 100% crystallinity, while we expect the electrochemically cycled films to be largely amorphous; the amorphous semiconductor material is estimated to be 10–15% less dense than crystalline films.<sup>45</sup> To some degree, these two systematic errors (i.e., neglect of ion-induced swelling in eq 2 vs the assumption of ideal packing in eq 4) are offsetting.

The gate interfacial capacitance of the PEDOT/ionogel/PEDOT capacitor was obtained by a Newtons PSM3750 multimeter equipped with an Impedance Analysis Interface 2. Cyclic voltammetry (CV) measurements and interfacial potential profiles of the PEDOT:PSS/ionogel/PBTET capacitor were performed with a Landt battery measurement system (WBCS3000K8, WonATech) in the Core-Facility Center for Sustainable Energy Materials at Inha University, simultaneously.

### 3. RESULTS AND DISCUSSION

Figure 1 displays the scheme of a bottom-contact/top-gate EGT fabricated using a precision aerosol-jet-printing process, which facilitates thorough studies of the device geometry. The semiconductor, dielectric layer, and gate electrode layers were printed sequentially, directly, and precisely on the thermally evaporated, microfabricated Au source and drain electrodes.

The channel length and width of the source and drain contacts were  $0.1 \text{ mm} \times 1 \text{ mm}$ , respectively. As the semiconductor channel material, the thiophene-based *p*-type polymer semiconductor PBTET, shown in Figure 1b, was utilized with thicknesses of 50 nm. For the dielectric layer, an ionogel electrolyte, composed of a [BMI][FAP] ionic liquid and a gelating SEAS triblock polymer, was employed, as shown in Figure 1c. In some cases, ionic liquids based on  $[\text{EMI}]^+$ ,  $[\text{PF}_6]^-$ , and  $[\text{TSFS}]^-$  ions were also employed, as noted. PEDOT:PSS, a high capacitance conducting polymer, was deposited as the top gate electrode with a thickness of  $\sim 3 \mu\text{m}$  and controlled gate-electrolyte areas in the range of 0.04–0.16  $\text{mm}^2$ , Figure 1d, to investigate the effects of gate capacitance. The PEDOT:PSS/ionogel interfacial capacitance increased linearly with the contact area from 60 to 260 nF at 10 Hz, but the areal specific capacitance values were maintained at  $\sim 0.15 \text{ mF/cm}^2$ , Figure S1.

The striking effect of varying the EGT gate electrode size is demonstrated in Figure 2. Panels a–c depict EGTs with high, medium, and low gate capacitances associated with systematically decreasing gate/electrolyte contact areas of 0.16, 0.08, and 0.04  $\text{mm}^2$ , respectively. Panels d–f and g–i show the corresponding  $I_D$ – $V_G$  transfer curves, and  $I_G$ – $V_G$  charging current characteristics, respectively. Importantly, inspection of 2d-f reveals that the  $I_D$ – $V_G$  curves are dramatically different as the gate area changes. For a large gate electrode area (high gate/electrolyte interfacial capacitance), the  $I_D$ – $V_G$  characteristic in Figure 2d has a pronounced peak on the forward scan and a smaller offset peak on the reverse sweep; conductivity is deeply suppressed in the high negative  $V_G$  ranges (light red

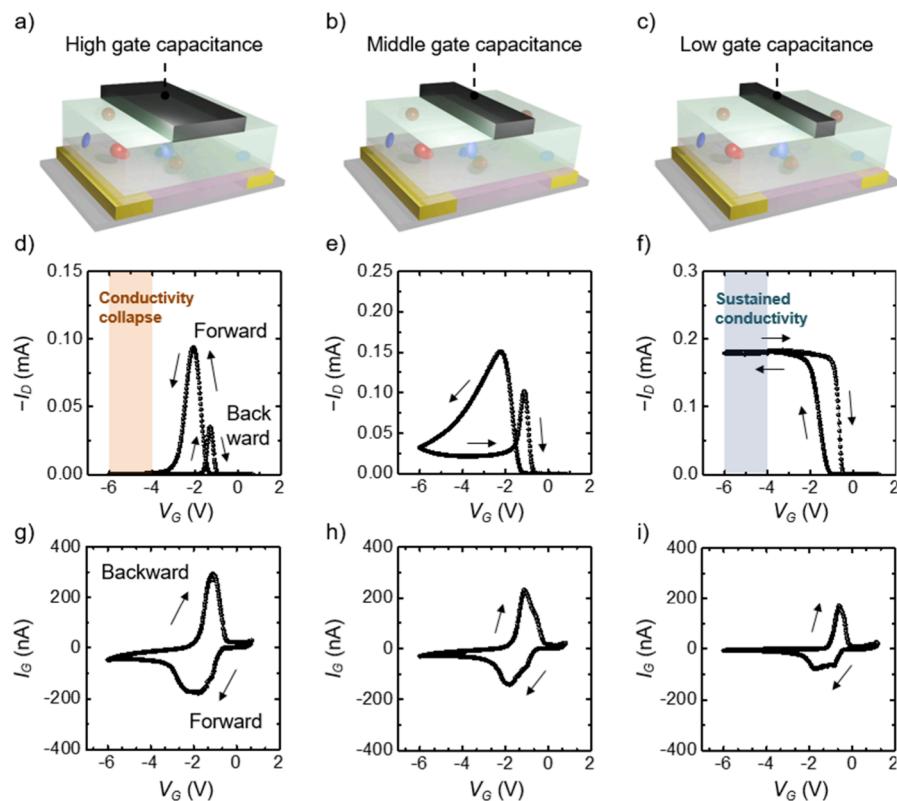

**Figure 3.** Holes-per-ring (hpr, in red) and average carrier mobility ( $\mu$ , in blue) as a function of  $V_G$  for PBTTT EGTs with (a) high, (b) middle, and (c) low gate capacitances, respectively.

shaded region in Figure 2d). This peaked behavior is repeatable (Figure S2a) and has been reported previously by the authors and others; the phenomenon is a consequence of a collapse in hole mobility at high hole densities, perhaps brought on by ion-carrier interactions and deep carrier trapping.<sup>7,33,43,46–50</sup> This is an extremely interesting effect, but it is not the main focus here. Rather, our key point is that this peaked behavior *completely disappears* as the gate electrode is made smaller. Figure 2f, corresponding to the smallest gate electrode, exhibits no peak. Instead, the channel current plateaus (light blue shaded region in Figure 2f), which is also an unusual behavior. In a typical p-type thin film transistor,  $I_D$  increases monotonically with increasingly negative  $V_G$ , albeit perhaps with a changing slope as the differential mobility varies. Here, we have the case that  $I_D$  completely flattens out for  $V_G < -2$  V on the forward sweep. The reverse sweep is similar but again exhibits some voltage hysteresis in the range of  $V_G > -2$  V. In addition, these peaked and plateaued conductivity behaviors were maintained at faster (100 mV/s) and slower (20 mV/s)  $V_G$  sweep rates, respectively, notwithstanding the  $I_D$  hysteresis variations, Figure S3. Figure 2e, corresponding to a device with an intermediate gate electrode area, shows an  $I_D$ – $V_G$  characteristic that is in some sense intermediate between the behaviors in Figure 2d,f; the  $I_D$  is peaked but not as sharply, and there is evidence of a current plateau on the reverse sweep.

As striking as the differences are in the  $I_D$ – $V_G$  characteristics, it is perhaps equally remarkable that the  $I_G$ – $V_G$  charging characteristics have similar shapes, except for the magnitudes of  $I_G$ . All three  $I_G$ – $V_G$  traces in Figures 2g–i show peaks on both the forward and reverse sweeps. For a given device, the integrated areas under the forward and reverse peaks are approximately the same, consistent with reversible hole accumulation and depletion on forward and reverse sweeps. However, it is clear by comparison that the total hole accumulation is largest for the device with the largest gate electrode, and the accumulation appears to scale with the gate electrode size.

We note that the  $I_D$ – $V_G$  and  $I_G$ – $V_G$  characteristics in Figure 2 were obtained during the second  $V_G$  sweep cycle. Figure S2 in Supporting Information shows the  $I_D$ – $V_G$  transfer and corresponding  $I_G$ – $V_G$  traces for repeated cycles of the EGTs with high and low gate capacitances, respectively. For the large gate EGT, maximum  $I_D$  in the first cycle is approximately  $-0.2$  mA, similar to the current for the small gate EGT. However, the maximum  $I_D$  decreases to approximately  $-0.1$  mA in the second cycle and then remains relatively consistent for subsequent cycles. The apparent cause of this “device breaking” behavior appears to be hole trapping, and while it is strongly evident in large gate devices, it is less evident for small

gate EGTs. We infer that deep traps are more accessible at higher carrier densities accessed in the large gate devices. A significant  $I_G$  decrease between the first cycle and subsequent cycles for the large gate EGT also is consistent with substantial hole trapping, Figure S2c. We note that a slight decrease in the channel conductivity occurs upon repeated cycling. This could be attributed to residual impurities present in the ionogel electrolyte, including water or halides, which can compromise the electrochemical stability of the ionic liquids.<sup>51–53</sup> In addition, other possible reasons are continued hole trapping or microstructural degradation in the electrochemically doped polymer semiconductor.

More quantitative comparison of hole accumulations in PBTTT EGTs are shown in Figure 3. Panels a–c exhibit the charge density in red, reported in units of “holes-per-ring”, or hpr, as we have done previously.<sup>33</sup> The hpr values in the PBTTT channel were estimated by integrating the forward sweep of the  $I_G$ – $V_G$  characteristics in Figure 2g–i to obtain the charge/volume ratio and dividing it by the estimated number of ring units per unit volume (see Experimental Section). One can clearly see by comparison of the data in Figure 3, that for all three EGTs with different gate electrode areas, the total hole density plateaus at large negative  $V_G$  values, consistent with the peaks seen in the  $I_G$ – $V_G$  plots in Figure 2. It is also evident that more charge accumulates for larger gate electrode area (larger gate electrode capacitance). The maximum hpr values are 0.32, 0.22, and 0.16 for the high, middle, and low gate capacitance EGTs, respectively.

Also shown in Figure 3 is the average hole mobility (blue) in PBTTT as a function of  $V_G$ . The average hole mobility was calculated by using eq 3 and the total hole density as a function of  $V_G$  (red trace). Figure 3a reveals the hole mobility “collapse” for the large gate device, i.e., the hole mobility increases as  $V_G$  (and hole density) increases, then peaks, and then sharply decreases. In contrast, Figure 3c indicates that the hole mobility has a gentle peak and plateaus for the small gate devices. The plateau in mobility is consistent with the plateaued  $I_D$ – $V_G$  and  $I_G$ – $V_G$  characteristics in Figure 2f,i. The EGT with the intermediate area again shows intermediate behavior for mobility vs  $V_G$ .

It is also evident in Figure 3 that the maximum mobility for each device follows the opposite trend of the charge density. That is, for the large gate EGT that achieves the largest charge density, the peak mobility is the smallest. The small gate EGT has the smallest charge density and the largest mobility (essentially a plateau). The midsized gate EGT has an intermediate peak mobility value. Importantly, Figure 3 also points out that the maximum mobility occurs at similar hole density of 0.12–0.15 hpr in all three cases. This is in agreement with our earlier finding that there is an optimum

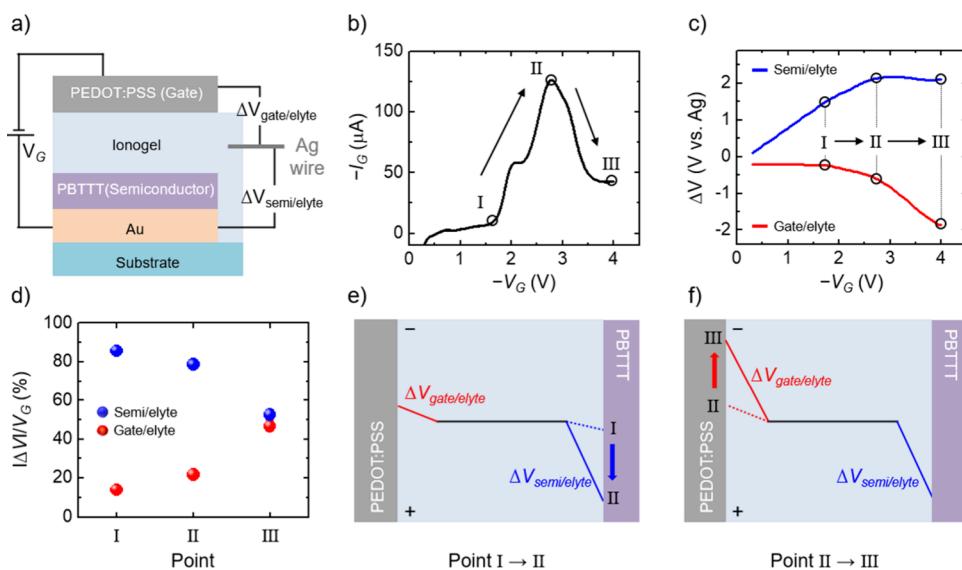

**Figure 4.** (a) Structure of a PEDOT:PSS/ionogel/PBTTT/Au capacitor with an inserted Ag wire quasi-reference electrode for investigating interfacial potential drops directly. Note  $\Delta V_{\text{gate/elyte}} = V_{\text{PEDOT}} - V_{\text{Ag}}$  and  $\Delta V_{\text{semi/elyte}} = V_{\text{PBTTT}} - V_{\text{Ag}}$ . (b)  $I_G - V_G$  curve of the capacitor, with points I, II, and III delineated in the forward direction (negative  $V_G$  sweep). (c) Voltage drops  $\Delta V_{\text{gate/elyte}}$  (red) and  $\Delta V_{\text{semi/elyte}}$  (blue) for gate/electrolyte and semiconductor/electrolyte interfaces, respectively. Note that the  $\Delta V_{\text{semi/elyte}}$  plateaus. (d) Fractional voltage dropped at the semiconductor/electrolyte and gate/electrolyte interfaces at points I, II, and III, based on the data in (c). (e, f) Schemes indicating the voltage drop profiles for  $V_G$  excursions I → II and II → III, respectively.

hole density for maximum average mobility.<sup>33</sup> The reason that the mobility plateaus at a high value for the small gate EGT is that the hole density levels out at 0.16 hpr, i.e., not much larger than the 0.12–0.15 hpr density for optimum mobility.<sup>33</sup> In contrast, the large gate EGT achieves a total hole density of 0.32 hpr, more than a factor of 2 greater than the optimum density, and so mobility collapses.<sup>33</sup>

We can make sense of the data in Figures 2 and 3 by understanding that the total capacitance,  $C_G$ , of the PEDOT:PSS gate/electrolyte/semiconductor stack is a strong function of the gate electrode area, as can be expected, and the applied voltage  $V_G$ .  $C_G$  is the summation of two capacitors in series, the gate/electrolyte interfacial capacitance,  $C_{\text{gate/elyte}}$ , and the semiconductor/electrolyte capacitance,  $C_{\text{semi/elyte}}$ . Using the rule for capacitors in series,  $1/C_G = 1/C_{\text{gate/elyte}} + 1/C_{\text{semi/elyte}}$ ; this means that  $C_G$  will be dominated by whichever interfacial capacitance is smaller. Furthermore,  $C_{\text{semi/elyte}}$  increases with voltage once electrochemical doping of the channel begins because the effective area of the 3D semiconductor–electrolyte interface increases dramatically as the semiconductor becomes conductive. This means that for EGTs with small gate electrodes  $C_G$  will evolve to be dominated by  $C_{\text{gate/elyte}}$  (the smaller of the two capacitances) as  $V_G$  becomes more negative. This in turn means that most of the applied  $V_G$  will drop at the gate-electrolyte interface, not at the semiconductor/electrolyte interface. Said another way, the gating power of the EGT with a small gate will decrease and it will become increasingly difficult to induce additional holes in the semiconductor. In fact, we see in Figure 3 that the hole density plateaus for all three devices at large  $V_G$  (for different reasons, *vide infra*), but it plateaus at a smaller density for the EGT with the smallest gate.

To check these ideas, we have carried out measurements of interfacial potential drops in a PEDOT/electrolyte/PBTTT capacitor structure using a Ag wire quasi-reference electrode inserted into the middle of the device, Figure 4a. Figure 4b displays the  $I_G - V_G$  characteristic of this device and highlights

three points, labeled I–III, where potential measurements were taken. The measured potential drops at the semiconductor/electrolyte ( $\Delta V_{\text{semi/elyte}}$ ) and gate/electrolyte ( $\Delta V_{\text{gate/elyte}}$ ) interfaces are shown in blue and red, respectively, versus  $V_G$  in Figure 4c. One can see that up through potential positions I and II,  $\Delta V_{\text{semi/elyte}}$  is increasing and  $\Delta V_{\text{gate/elyte}}$  is small in magnitude and relatively flat. However, as  $V_G$  continues to become more negative, moving toward position III,  $\Delta V_{\text{gate/elyte}}$  becomes more negative, and  $\Delta V_{\text{semi/elyte}}$  plateaus. In fact, one can observe that for  $V_G < -3$  V,  $\Delta V_{\text{semi/elyte}}$  is essentially pinned, and only the voltage drop at the gate is increasing. Figure 4d plots the fraction of applied  $V_G$  that is dropped at each of the interfaces. At low  $V_G$  biases, corresponding to position I in Figure 4b, over 80% of the voltage is dropped at the semiconductor/electrolyte interface. By position III, about half of the  $V_G$  potential is dropped at each interface. Figure 4e,f schematically illustrate the corresponding interfacial voltage drops in the  $V_G$  domains between points I and II and between points II and III, respectively. Figure S4 in the Supporting Information shows that the interfacial potential variations occur symmetrically in the reverse sweep.

The key point of Figure 4 is that uniform changes in  $V_G$  do not result in uniform changes in  $\Delta V_{\text{semi/elyte}}$ . Because  $\Delta V_{\text{semi/elyte}}$  determines the total charge induced in PBTTT ( $Q = C_{\text{semi/elyte}} \times \Delta V_{\text{semi/elyte}}$ ), we confirm that charge accumulation in PBTTT is not a steady function of  $V_G$ . In fact, at large negative  $V_G$  values, the accumulation of charge in PBTTT will cease, as  $\Delta V_{\text{semi/elyte}}$  becomes pinned.

The behavior observed in Figure 2 is now quite clear. For small gates, with low gate capacitance, e.g., in Figure 2c,f,i, as  $V_G$  becomes more negative and the PBTTT channel becomes conductive, the total potential drop becomes increasingly dominated by the gate/electrolyte interface and not the PBTTT/electrolyte interface, which means that charge accumulation in PBTTT slows and essentially stops. This leads to the decrease in  $I_G$  that is observed in Figure 2i and the plateau in the  $I_D - V_G$  plot, Figure 2f; no more carriers are

induced as  $V_G$  increases, so  $I_D$  remains fixed with  $V_G$ . Figure S5 in the Supporting Information shows that this same behavior is also visible in the  $I_D$ – $V_G$  characteristics. On the other hand, when the gate is large and has a high capacitance, Figure 2a,d,g, there is much larger charge accumulation in PBT TT, at least initially. However, the charge-triggered collapse in mobility at high charge (0.12–0.15 hpr) leads to a marked conductivity decrease of the semiconductor and thus a decrease in  $I_D$ , halting charge accumulation at large negative values of  $V_G$ , Figure 2g.

In light of this discussion, it is critical to observe that the shapes of the  $I_D$ – $V_G$  characteristics in Figure 2g,i, although similar, arise from very different mechanisms.  $I_D$  falls as  $V_G$  becomes more negative in Figure 2g because of band filling, as we have previously reported, which leads to a conductivity collapse.<sup>33,50</sup> In contrast, in Figure 2i,  $I_D$  falls as  $V_G$  becomes more negative because of an undersized gate capacitance, which stifles charge accumulation in the channel. If one is interested in the intrinsic conductance versus charge behavior of PBT TT, it is therefore critical to ensure that the gate/electrolyte capacitance is significantly larger than the PBT TT/electrolyte capacitance, noting that these interfacial capacitances depend on geometric gate contact area. Alternatively, if the “saturated” or plateaued  $I_D$ – $V_G$  behavior in Figure 2f is desirable, then engineering the gate/electrolyte capacitance to be comparable to, or smaller than, the semiconductor/electrolyte capacitance can ensure that this behavior is manifested.

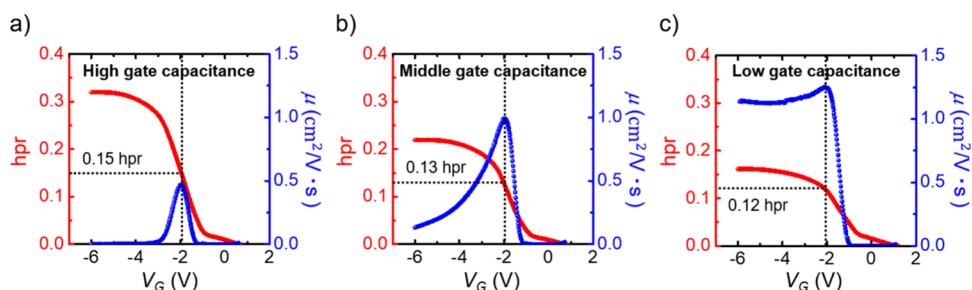

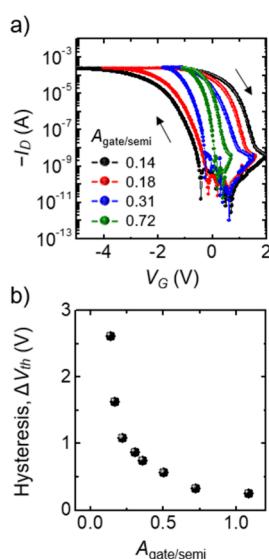

We also note that the relative sizes of the gate/electrolyte and semiconductor/electrolyte capacitances strongly impact hysteresis in the measured  $I_D$ – $V_G$  characteristics of EGTs. Figure 5a displays a semilog plot of  $I_D$  vs  $V_G$  for PBT TT EGTs with four different ratios of the PEDOT:PSS gate/electrolyte contact area to the PBT TT/electrolyte contact area ( $A_{\text{gate/semi}}$ ). In all four cases, the gate electrode is smaller than the semiconductor channel, and so  $I_D$  plateaus, as we have described above. However, the central observation is that the

**Figure 5.** (a)  $I_D$ – $V_G$  transfer curves of EGTs with varying  $A_{\text{gate/semi}}$  values (area ratio of PEDOT:PSS gate electrode to PBT TT semiconductor) of 0.14, 0.18, 0.31, and 0.72. (b) Calculated hysteresis  $\Delta V_{\text{th}}$  ( $|V_{\text{th, forward}} - V_{\text{th, backward}}|$ ) versus  $A_{\text{gate/semi}}$  from the  $I_D$ – $V_G$  transfer curves.  $V_D = -0.1$  V and the  $V_G$  scan rate is 50 mV/s.

hysteresis loop clearly broadens as the area ratio decreases, i.e., as the gate becomes smaller. The hysteresis loop width,  $\Delta V_{\text{th}}$ , is plotted vs the area ratio in Figure 5b. It is evident that there is a very sharp dependence. Figure S6 in the Supporting Information shows similar results for EGTs with gold side-gate electrodes, supporting the strong relationship between the gate capacitance and channel conductivity as well as hysteresis. In addition, when  $A_{\text{gate/semi}}$  is 0.5 for PEDOT:PSS and  $A_{\text{gate/semi}}$  is 38 for Au, both EGTs displayed a similar hysteresis value of  $\sim 0.55$  V. This suggests a higher areal specific capacitance of the PEDOT:PSS gate electrode.

The reason for this behavior is clear based on the discussion above. In all cases in Figure 5, the gate is undersized, and the more undersized it is, the more negative  $V_G$  must be on the forward sweep to induce a strong conductance change in the PBT TT. Once holes accumulate in PBT TT, the relative difference in the gate/electrolyte and PBT TT/electrolyte capacitances is even larger because the PBT TT has become conductive. Thus, on the reverse sweep, most of the applied  $V_G$  is dropped at the gate/electrolyte interface and larger, more positive  $V_G$  values are required to deplete holes from the PBT TT and turn the conductivity OFF. The critical conclusion here is that *strong hysteresis in the  $I_D$ – $V_G$  characteristics can simply reflect the relative capacitance of the gate compared to the semiconductor channel*. Specific ion-semiconductor effects (e.g., ion-polymer binding) are not required to explain the  $I_D$ – $V_G$  hysteresis when the gate electrode is undersized; device geometry alone can cause hysteresis in EGTs. In our view, this point is important for the community using EGTs for neuromorphic computing applications.<sup>10,29,54–58</sup>

There is an additional important point to make here regarding  $I_D$ – $V_G$  hysteresis. While we have made the case above that transfer curve hysteresis can be caused by gate geometry alone, there can also be an “intrinsic” dependence of the hysteresis based on the choice of electrolyte or polymer semiconductor. This does not refute the statement in italics in the paragraph above; it simply points out the underlying complexity. Figure S7 in the Supporting Information shows  $I_D$ – $V_G$  characteristics for four different EGTs based on two different polymer semiconductors and three different ionic liquid electrolytes. One sees that indeed the hysteresis varies even though the device geometry and the  $V_G$  sweep rate are the same in each case. Thus, the choice of materials in addition to device geometry affects hysteresis in the transfer curves, as the interfacial capacitances, and consequently, the carrier accumulation, depend on the chosen materials.

We note that for neuromorphic computing applications of EGTs, it is not just hysteresis that is important; current relaxation times and “memory” when  $V_G$  is initially pulsed and then set to zero are also critical. We have not investigated the dependence of these neuromorphic effects as a function of device geometry and composition, although that represents a potentially attractive direction for future research.

#### 4. CONCLUSIONS

In summary, we investigated the dependence of polymer EGT transfer characteristics as a function of the gate electrode area in contact with the electrolyte. We find that the  $I_D$ – $V_G$  behavior exhibits two remarkably different limits. For EGTs with very large gate/electrolyte areas and consequently large gate/electrolyte interfacial capacitances,  $I_D$  exhibits a well-defined peak vs  $V_G$ .  $I_D$  collapses at high  $V_G$  because of band

filling, which causes both charge accumulation to halt and mobility to drop. In contrast, for small gates with small gate/electrolyte capacitances,  $I_D$  exhibits a plateau vs  $V_G$ . The plateau occurs because charge accumulation in the semiconductor channel is halted, even as  $V_G$  continues to become more negative. The reason is that the small size of the gate/electrolyte capacitance compared to the semiconductor/electrolyte capacitance means that beyond some critical  $V_G$  value, effectively all the applied  $V_G$  is dropped at the gate/electrolyte interface; there is effectively no voltage drop at the semiconductor/electrolyte interface and thus no additional charge accumulation in the semiconductor. In the plateau regime, the HOMO band of the polymer is partially filled and mobility and charge accumulation are approximately constant. The  $I_G$ – $V_G$  characteristics acquired simultaneously with the  $I_D$ – $V_G$  characteristics support these conclusions, as do independent measurements of potential drops inside the electrolyte for capacitors that mimic the gate/electrolyte/semiconductor stack in an EGT.

We have also demonstrated that hysteresis in  $I_D$ – $V_G$  traces for EGTs can be a function of gate size with smaller gates leading to larger hysteresis. In practice, it seems that the  $I_D$ – $V_G$  hysteresis is a function of both device geometry and the selection of semiconductor and electrolyte materials. Overall, our results here demonstrate ample opportunities for designing the transconductance behavior of EGTs by tailoring the gate electrode geometry. When using EGTs to measure the fundamental transport properties of polymer semiconductors as a function of gate induced charge, care must be taken to ensure that the gate/electrolyte area is significantly larger than the polymer semiconductor/electrolyte area.

## ASSOCIATED CONTENT

### Supporting Information

The Supporting Information is available free of charge at <https://pubs.acs.org/doi/10.1021/acsami.4c00079>.

Experimental results including  $I_D$ – $V_G$ ,  $I_G$ – $V_G$ , and measured voltage profiles of EGTs, and extracted maximum  $I_D$  and hysteresis values ([PDF](#))

## AUTHOR INFORMATION

### Corresponding Authors

**Keun Hyung Lee** – Department of Chemistry and Chemical Engineering, Education and Research Center for Smart Energy and Materials Inha University, Incheon 22212, Republic of Korea; [orcid.org/0000-0003-4066-9991](#); Email: [kh.lee@inha.ac.kr](mailto:kh.lee@inha.ac.kr)

**C. Daniel Frisbie** – Department of Chemical Engineering and Materials Science, University of Minnesota–Twin Cities, Minneapolis, Minnesota 55455, United States; [orcid.org/0000-0002-4735-2228](#); Email: [frisbie@umn.edu](mailto:frisbie@umn.edu)

### Author

**Kyung Gook Cho** – Department of Chemical Engineering and Materials Science, University of Minnesota–Twin Cities, Minneapolis, Minnesota 55455, United States; [orcid.org/0000-0002-3992-3860](#)

Complete contact information is available at:

<https://pubs.acs.org/10.1021/acsami.4c00079>

### Notes

The authors declare no competing financial interest.

## ACKNOWLEDGMENTS

This work was supported by the MRSEC program of the U.S. National Science Foundation (NSF) under grant number DMR-2011401. Portions of this work were conducted in the Minnesota Nano Center, which was also supported by NSF through the NNCI Network under Award Number ECCS-2025124. This research was also partially supported by the National Research Foundation of Korea (NRF) grant funded by the Korean government (Ministry of Science and ICT, MSIT) (RS-2023-00247977 and 2021R1A2C1094911) and the Korea Institute for Advancement of Technology(KIAT) and the Ministry of Trade, Industry & Energy(MOTIE) of the Republic of Korea (no. P0017363).

## REFERENCES

- (1) Cho, J. H.; Lee, J.; Xia, Y.; Kim, B.; He, Y.; Renn, M. J.; Lodge, T. P.; Frisbie, C. D. Printable ion-gel gate dielectrics for low-voltage polymer thin-film transistors on plastic. *Nat. Mater.* **2008**, *7*, 900–906.

- (2) Kim, S. H.; Hong, K.; Xie, W.; Lee, K. H.; Zhang, S. P.; Lodge, T. P.; Frisbie, C. D. Electrolyte-Gated Transistors for Organic and Printed Electronics. *Adv. Mater.* **2013**, *25*, 1822–1846.

- (3) Torricelli, F.; Adrahtas, D. Z.; Bao, Z. N.; Berggren, M.; Biscarini, F.; Bonfiglio, A.; Bortolotti, C. A.; Daniel Frisbie, C.; Macchia, E.; Malliaras, G. G.; McCulloch, I.; Moser, M.; Nguyen, T.-Q.; Owens, R. M.; Salleo, A.; Spanu, A.; Torsi, L. Electrolyte-gated transistors for enhanced performance bioelectronics. *Nat. Rev. Method. Prim.* **2021**, *1*, 66.

- (4) Rivnay, J.; Inal, S.; Salleo, A.; Owens, R. M.; Berggren, M.; Malliaras, G. G. Organic electrochemical transistors. *Nat. Rev. Mater.* **2018**, *3*, 17086.

- (5) Gkoupidenis, P.; Koutsouras, D. A.; Malliaras, G. G. Neuromorphic device architectures with global connectivity through electrolyte gating. *Nat. Commun.* **2017**, *8*, 15448.

- (6) Keene, S. T.; Lubrano, C.; Kazemzadeh, S.; Melianas, A.; Tuchman, Y.; Polino, G.; Scognamiglio, P.; Cinà, L.; Salleo, A.; van de Burgt, Y.; Santoro, F. A biohybrid synapse with neurotransmitter-mediated plasticity. *Nat. Mater.* **2020**, *19*, 969–973.

- (7) Harikesh, P. C.; Yang, C. Y.; Wu, H. Y.; Zhang, S. L.; Donahue, M. J.; Caravaca, A. S.; Huang, J. D.; Olofsson, P. S.; Berggren, M.; Tu, D.; Fabiano, S. Ion-tunable antiambipolarity in mixed ion-electron conducting polymers enables biorealistic organic electrochemical neurons. *Nat. Mater.* **2023**, *22*, 242–248.

- (8) Sarkar, T.; Lieberth, K.; Pavlou, A.; Frank, T.; Mailaender, V.; McCulloch, I.; Blom, P. W. M.; Torricelli, F.; Gkoupidenis, P. An organic artificial spiking neuron for *in situ* neuromorphic sensing and biointerfacing. *Nat. Electron.* **2022**, *5*, 774–783.

- (9) Ho, D. H.; Roe, D. G.; Choi, Y. Y.; Kim, S.; Choi, Y. J.; Kim, D. H.; Jo, S. B.; Cho, J. H. Non–von Neumann multi-input spike signal processing enabled by an artificial synaptic multiplexer. *Sci. Adv.* **2022**, *8*, No. eabn1838.

- (10) Krauhhausen, I.; Koutsouras, D. A.; Melianas, A.; Keene, S. T.; Lieberth, K.; Ledanseur, H.; Sheelamathula, R.; Giovannitti, A.; Torricelli, F.; McCulloch, I.; Blom, P. W. M.; Salleo, A.; van de Burgt, Y.; Gkoupidenis, P. Organic neuromorphic electronics for sensor-imotor integration and learning in robotics. *Sci. Adv.* **2021**, *7*, No. eabl5068.

- (11) Seo, G.; Lee, G.; Kim, M. J.; Baek, S. H.; Choi, M.; Ku, K. B.; Lee, C. S.; Jun, S.; Park, D.; Kim, H. G.; Kim, S. J.; Lee, J. O.; Kim, B. T.; Park, E. C.; Kim, S. I. Rapid Detection of COVID-19 Causative Virus (SARS-CoV-2) in Human Nasopharyngeal Swab Specimens Using Field-Effect Transistor-Based Biosensor. *ACS Nano* **2020**, *14*, S135–S142.

- (12) Campos, R.; Borme, J.; Guerreiro, J. R.; Machado, G.; Cerqueira, M. F.; Petrovykh, D. Y.; Alpuim, P. Attomolar Label-Free Detection of DNA Hybridization with Electrolyte-Gated Graphene Field-Effect Transistors. *ACS Sens.* **2019**, *4*, 286–293.

(13) Masvidal-Codina, E.; Illa, X.; Dasilva, M.; Calia, A. B.; Dragojevic, T.; Vidal-Rosass, E. E.; Prats-Alfonso, E.; Martínez-Aguilar, J.; De la Cruz, J. M.; Garcia-Cortadella, R.; Godignon, P.; Rius, G.; Camassa, A.; Del Corro, E.; Bousquet, J.; Hébert, C.; Durduran, T.; Villa, R.; Sanchez-Vives, M. V.; Garrido, J. A.; Guimerà-Brunet, A. High-resolution mapping of infraslow cortical brain activity enabled by graphene microtransistors. *Nat. Mater.* **2019**, *18*, 280–288.

(14) Quill, T. J.; LeCroy, G.; Melianas, A.; Rawlings, D.; Thiburc, Q.; Sheelamathula, R.; Cheng, C.; Tuchman, Y.; Keene, S. T.; McCulloch, I.; Segalman, R. A.; Chabinyc, M. L.; Salleo, A. Ion Pair Uptake in Ion Gel Devices Based on Organic Mixed Ionic–Electronic Conductors. *Adv. Funct. Mater.* **2021**, *31*, No. 2104301.

(15) Neusser, D.; Malacrida, C.; Kern, M.; Gross, Y. M.; van Slageren, J.; Ludwigs, S. High conductivities of disordered P3HT films by an electrochemical doping strategy. *Chem. Mater.* **2020**, *32*, 6003–6013.

(16) Rivnay, J.; Leleux, P.; Ferro, M.; Sessolo, M.; Williamson, A.; Koutsouras, D. A.; Khodagholy, D.; Ramuz, M.; Strakosas, X.; Owens, R. M.; Benar, C.; Badier, J. M.; Bernard, C.; Malliaras, G. G. High-performance transistors for bioelectronics through tuning of channel thickness. *Sci. Adv.* **2015**, *1*, No. e1400251.

(17) Zhang, L.; Wang, L.; He, S.; Zhu, C.; Gong, Z.; Zhang, Y.; Wang, J.; Yu, L.; Gao, K.; Kang, X.; Song, Y.; Lu, G.; Yu, H.-D. High-Performance Organic Electrochemical Transistor Based on Photo-annealed Plasmonic Gold Nanoparticle-Doped PEDOT:PSS. *ACS Appl. Mater. Interfaces* **2023**, *15*, 3224–3234.

(18) Wu, X.; Stephen, M.; Hidalgo, T. C.; Salim, T.; Surgailis, J.; Surendran, A.; Su, X.; Li, T.; Inal, S.; Leong, W. L. Ionic-Liquid Induced Morphology Tuning of PEDOT:PSS for High-Performance Organic Electrochemical Transistors. *Adv. Funct. Mater.* **2022**, *32*, No. 2108510.

(19) Huang, W.; Chen, J.; Yao, Y.; Zheng, D.; Ji, X.; Feng, L.-W.; Moore, D.; Glavin, N. R.; Xie, M.; Chen, Y.; Pankow, R. M.; Surendran, A.; Wang, Z.; Xia, Y.; Bai, L.; Rivnay, J.; Ping, J.; Guo, X.; Cheng, Y.; Marks, T. J.; Facchetti, A. Vertical organic electrochemical transistors for complementary circuits. *Nature* **2023**, *613*, 496–502.

(20) Wang, Y.; Zhu, G.; Zeglio, E.; Castillo, T. C. H.; Haseena, S.; Ravva, M. K.; Cong, S.; Chen, J.; Lan, L.; Li, Z.; Herland, A.; McCulloch, I.; Inal, S.; Yue, W. n-Type Organic Electrochemical Transistors with High Transconductance and Stability. *Chem. Mater.* **2023**, *35*, 405–415.

(21) Deng, Y.; Qi, H.; Ma, Y.; Liu, S.; Zhao, M.; Guo, Z.; Jie, Y.; Zheng, R.; Jing, J.; Chen, K.; Ding, H.; Lv, G.; Zhang, K.; Li, R.; Cheng, H.; Zhao, L.; Sheng, X.; Zhang, M.; Yin, L. A flexible and highly sensitive organic electrochemical transistor-based biosensor for continuous and wireless nitric oxide detection. *Proc. Natl. Acad. Sci. U.S.A.* **2022**, *119*, No. e2208060119.

(22) Ohayon, D.; Savva, A.; Du, W.; Paulsen, B. D.; Uguz, I.; Ashraf, R. S.; Rivnay, J.; McCulloch, I.; Inal, S. Influence of side chains on the n-type organic electrochemical transistor performance. *ACS Appl. Mater. Interfaces* **2021**, *13*, 4253–4266.

(23) Flagg, L. Q.; Bischak, C. G.; Onorato, J. W.; Rashid, R. B.; Luscombe, C. K.; Ginger, D. S. Polymer crystallinity controls water uptake in glycol side-chain polymer organic electrochemical transistors. *J. Am. Chem. Soc.* **2019**, *141*, 4345–4354.

(24) Chen, L.; Fu, Y.; Wang, N.; Yang, A.; Li, Y.; Wu, J.; Ju, H.; Yan, F. Organic electrochemical transistors for the detection of cell surface glycans. *ACS Appl. Mater. Interfaces* **2018**, *10*, 18470–18477.

(25) Lee, K. H.; Kang, M. S.; Zhang, S. P.; Gu, Y. Y.; Lodge, T. P.; Frisbie, C. D. "Cut and Stick" Rubbery Ion Gels as High Capacitance Gate Dielectrics. *Adv. Mater.* **2012**, *24*, 4457–4462.

(26) Cho, K. G.; Kwon, Y. K.; Jang, S. S.; Seol, K. H.; Park, J. H.; Hong, K.; Lee, K. H. Printable carbon nanotube-based elastic conductors for fully-printed sub-1 V stretchable electrolyte-gated transistors and inverters. *J. Mater. Chem. C* **2020**, *8*, 3639–3645.

(27) Thomas, M. S.; Adrahtas, D. Z.; Frisbie, C. D.; Dorfman, K. D. Modeling of Quasi-Static Floating-Gate Transistor Biosensors. *ACS Sens.* **2021**, *6*, 1910–1917.

(28) White, S. P.; Frisbie, C. D.; Dorfman, K. D. Detection and sourcing of gluten in grain with multiple floating-gate transistor biosensors. *ACS Sens.* **2018**, *3*, 395–402.

(29) Kim, S. J.; Jeong, J.-S.; Jang, H. W.; Yi, H.; Yang, H.; Ju, H.; Lim, J. A. Dendritic network implementable organic neurofiber transistors with enhanced memory cyclic endurance for spatiotemporal iterative learning. *Adv. Mater.* **2021**, *33*, No. 2100475.

(30) Zhang, S.; Ding, P.; Ruoko, T.-P.; Wu, R.; Stoeckel, M.-A.; Masetti, M.; Liu, T.; Vagin, M.; Meli, D.; Kroon, R.; Rivnay, J.; Fabiano, S. Toward Stable p-Type Thiophene-Based Organic Electrochemical Transistors. *Adv. Funct. Mater.* **2023**, *33*, No. 2302249.

(31) Schmode, P.; Savva, A.; Kahl, R.; Ohayon, D.; Meichsner, F.; Dolynchuk, O.; Thurn-Albrecht, T.; Inal, S.; Thelakkat, M. The Key Role of Side Chain Linkage in Structure Formation and Mixed Conduction of Ethylene Glycol Substituted Polythiophenes. *ACS Appl. Mater. Interfaces* **2020**, *12*, 13029–13039.

(32) Sensi, M.; Berto, M.; Candini, A.; Liscio, A.; Cossarizza, A.; Beni, V.; Biscarini, F.; Bortolotti, C. A. Modulating the faradic operation of all-printed organic electrochemical transistors by facile in situ modification of the gate electrode. *ACS Omega* **2019**, *4*, 5374–5381.

(33) Cho, K. G.; Adrahtas, D. Z.; Lee, K. H.; Frisbie, C. D. Sub-Band Filling and Hole Transport in Polythiophene-Based Electrolyte-Gated Transistors: Effect of Side-Chain Length and Density. *Adv. Funct. Mater.* **2023**, *33*, No. 2303700.

(34) Hong, K.; Kim, S. H.; Mahajan, A.; Frisbie, C. D. Aerosol Jet Printed p- and n-type Electrolyte-Gated Transistors with a Variety of Electrode Materials: Exploring Practical Routes to Printed Electronics. *ACS Appl. Mater. Interfaces* **2014**, *6*, 18704–18711.

(35) Sayago, J.; Soavi, F.; Sivalingam, Y.; Cicoira, F.; Santato, C. Low voltage electrolyte-gated organic transistors making use of high surface area activated carbon gate electrodes. *J. Mater. Chem. C* **2014**, *2*, 5690–5694.

(36) Cho, K. G.; Cho, Y. K.; Kim, J. H.; Yoo, H. Y.; Hong, K.; Lee, K. H. Thermostable Ion Gels for High-Temperature Operation of Electrolyte-Gated Transistors. *ACS Appl. Mater. Interfaces* **2020**, *12*, 15464–15471.

(37) Cho, K. G.; Seol, K. H.; Kim, M. S.; Hong, K. H. Y.; Lee, K. H. Tuning Threshold Voltage of Electrolyte-Gated Transistors by Binary Ion Doping. *ACS Appl. Mater. Interfaces* **2022**, *14*, 50004–50012.

(38) Singh, M.; Mulla, M. Y.; Santacroce, M. V.; Magliulo, M.; Di Franco, C.; Manoli, K.; Altamura, D.; Giannini, C.; Cioffi, N.; Palazzo, G.; Scamarcio, G.; Torsi, L. Effect of the gate metal work function on water-gated ZnO thin-film transistor performance. *J. Phys. D: Appl. Phys.* **2016**, *49*, No. 275101.

(39) Awate, S. S.; Mostek, B.; Kumari, S.; Dong, C. Y.; Robinson, J. A.; Xu, K.; Fullerton-Shirey, S. K. Impact of Large Gate Voltages and Ultrathin Polymer Electrolytes on Carrier Density in Electric-Double-Layer-Gated Two-Dimensional Crystal Transistors. *ACS Appl. Mater. Interfaces* **2023**, *15*, 15785–15796.

(40) Koutsouras, D. A.; Torricelli, F.; Gkoupidenis, P.; Blom, P. W. M. Efficient Gating of Organic Electrochemical Transistors with In-Plane Gate Electrodes. *Adv. Mater. Technol.* **2021**, *6*, No. 2100732.

(41) Zare Bidoky, F.; Frisbie, C. D. Sub-3 V, MHz-Class Electrolyte-Gated Transistors and Inverters. *ACS Appl. Mater. Interfaces* **2022**, *14*, 21295–21300.

(42) Tang, B. X.; White, S. P.; Frisbie, C. D.; Lodge, T. P. Synergistic Increase in Ionic Conductivity and Modulus of Triblock Copolymer Ion Gels. *Macromolecules* **2015**, *48*, 4942–4950.

(43) Paulsen, B. D.; Frisbie, C. D. Dependence of Conductivity on Charge Density and Electrochemical Potential in Polymer Semiconductors Gated with Ionic Liquids. *J. Phys. Chem. C* **2012**, *116*, 3132–3141.

(44) McCulloch, I.; Heeney, M.; Bailey, C.; Genevicius, K.; MacDonald, I.; Shkunov, M.; Sparrowe, D.; Tierney, S.; Wagner, R.; Zhang, W.; Chabinyc, M. L.; Kline, R. J.; McGehee, M. D.; Toney, M. F. Liquid-crystalline semiconducting polymers with high charge-carrier mobility. *Nat. Mater.* **2006**, *5*, 328–333.

(45) Ehrenstein, G. W. *Polymeric materials: structure, properties, applications*; Carl Hanser Verlag GmbH Co KG: Munich, Germany, 2012.

(46) Ofer, D.; Wrighton, M. S. Potential dependence of the conductivity of poly (3-methylthiophene) in liquid sulfur dioxide/electrolyte: a finite potential window of high conductivity. *J. Am. Chem. Soc.* **1988**, *110*, 4467–4468.

(47) Wang, S.; Ha, M.; Manno, M.; Frisbie, C. D.; Leighton, C. Hopping transport and the Hall effect near the insulator–metal transition in electrochemically gated poly(3-hexylthiophene) transistors. *Nat. Commun.* **2012**, *3*, 1210.

(48) Xu, K.; Ruoko, T.-P.; Shokrani, M.; Scheunemann, D.; Abdalla, H.; Sun, H.; Yang, C.; Puttisong, Y.; Kolhe, N. B.; Figueroa, J. S. M.; Pedersen, J. O.; Ederth, T.; Chen, W. M.; Berggren, M.; Jenekhe, S. A.; Fazzi, D.; Kemerink, M.; Fabiano, S. On the origin of Seebeck coefficient inversion in highly doped conducting polymers. *Adv. Funct. Mater.* **2022**, *32*, No. 2112276.

(49) Panzer, M. J.; Frisbie, C. D. Polymer electrolyte gate dielectric reveals finite windows of high conductivity in organic thin film transistors at high charge carrier densities. *J. Am. Chem. Soc.* **2005**, *127*, 6960–6961.

(50) He, T.; Frisbie, C. D. Sub-band filling, Mott-like transitions, and ion size effects in C60 single crystal electric double layer transistors. *ACS Nano* **2022**, *16*, 4823–4830.

(51) De Vos, N.; Maton, C.; Stevens, C. V. Electrochemical Stability of Ionic Liquids: General Influences and Degradation Mechanisms. *ChemElectroChem.* **2014**, *1*, 1258–1270.

(52) O'Mahony, A. M.; Silvester, D. S.; Aldous, L.; Hardacre, C.; Compton, R. G. Effect of Water on the Electrochemical Window and Potential Limits of Room-Temperature Ionic Liquids. *J. Chem. Eng. Data* **2008**, *53*, 2884–2891.

(53) Galinski, M.; Lewandowski, A.; Stepniak, I. Ionic liquids as electrolytes. *Electrochim. Acta* **2006**, *51*, 5567–5580.

(54) Kim, N.; Go, G.-T.; Park, H.-L.; Ahn, Y.; Kim, J.; Lee, Y.; Seo, D.-G.; Lee, W.; Kim, Y.-H.; Yang, H.; Lee, T.-W. Molecular Tailoring to Achieve Long-Term Plasticity in Organic Synaptic Transistors for Neuromorphic Computing. *Adv. Intell. Syst.* **2023**, *5*, No. 2300016.

(55) Lee, Y.; Park, H. L.; Kim, Y.; Lee, T. W. Organic electronic synapses with low energy consumption. *Joule* **2021**, *5*, 794–810.

(56) Tuchman, Y.; Mangoma, T. N.; Gkoupidenis, P.; Van De Burgt, Y.; John, R. A.; Mathews, N.; Shaheen, S. E.; Daly, R.; Malliaras, G. G.; Salleo, A. Organic neuromorphic devices: Past, present, and future challenges. *MRS Bull.* **2020**, *45*, 619–630.

(57) Choi, Y.; Oh, S.; Qian, C.; Park, J.-H.; Cho, J. H. Vertical organic synapse expandable to 3D crossbar array. *Nat. Commun.* **2020**, *11*, 4595.

(58) Melianas, A.; Quill, T. J.; LeCroy, G.; Tuchman, Y.; Loo, H. v.; Keene, S. T.; Giovannitti, A.; Lee, H. R.; Maria, I. P.; McCulloch, I.; Salleo, A. Temperature-resilient solid-state organic artificial synapses for neuromorphic computing. *Sci. Adv.* **2020**, *6*, No. eabb2958.