# Reduction in density of interface traps determined by C-V analysis in III-nitride-based MOSHFET structure

Cite as: Appl. Phys. Lett. 124, 112103 (2024); doi: 10.1063/5.0193603 Submitted: 22 December 2023 - Accepted: 24 February 2024 -

Published Online: 11 March 2024

Samiul Hasan, 'n Mohi Uddin Jewel,' n Scott R. Crittenden,' n Md Ghulam Zakir,' n Nifat Jahan Nipa,' n Vitaliy Avrutin,' n 🖲 mit ၆ zg 🛭 n Hadis Morkoc , n and Iftikhar Ahmad 🗥 n

## **AFFILIATIONS**

- <sup>1</sup>Department of Electrical Engineering, University of South Carolina, Columbia, South Carolina 29208, USA

- $^2$ Department of Physics and Astronomy, University of South Carolina, Columbia, South Carolina 29208, USA

- <sup>3</sup>Department of Electrical and Computer Engineering, Virginia Commonwealth University, Richmond, Virginia 23284, USA

## **ABSTRACT**

An *in situ* metal-organic chemical vapor phase epitaxy is used to grow a complete AlGaN/GaN metal oxide semiconductor heterojunction field effect transistor (MOSHFET) structure, gated by a gallium oxide ( $Ga_2O_3$ ) layer; we observed reduction in the interfacial trap density compared to its version wherein the  $Ga_2O_3$  was grown *ex situ*, after breaking the vacuum, all else being the same. A remarkable decrease in the interfacial charge density for *in situ* MOSHFET structures in the range of 70%–88% for 10–30 nm oxide layer thickness and improvements in other electrical parameters required for high-performing devices were observed.

Published under an exclusive license by AIP Publishing. https://doi.org/10.1063/5.0193603

Gallium nitride (GaN)-based heterostructure field effect transistors (HFETs) continue to play a pivotal role in high-speed, highpower, and high-temperature RF/microwave applications in harsh environments. 1,2 The commercial and military applications of GaNbased electronics are numerous and diverse.<sup>2</sup> The fundamental problems that notably limit the performance of these devices, i.e., RF dispersion<sup>3</sup> current collapse4 and knee voltage walk-out,5 primarily can be attributed to the processes occurring near the gate edges. To overcome these problems, passivated HFETs or metal oxide semiconductor HFETs (MOSHFETs) have been used.<sup>6,7</sup> In addition to the gate leakage current reduction, MOSHFETs allow larger gate voltage swings and, thus, the ensuing higher channel currents paving the way to superior RF performance.8 The gate leakage current is reduced by the oxide layer, an insulator, which is in between the semiconductor and the metal. In the absence of the insulator layer, gate leakage current increases considerably with gate voltage, thus limiting the gate voltage swing. The oxide layer in the MOSHFET structure reduces the leakage current and allows a large gate voltage swing.

Mitigation of the aluminum gallium nitride (AlGaN) barrier layer surface states via passivation can play a significant positive role on the overall electrical performance of AlGaN/GaN-based devices. In a typical passivation process, the HFET structure and passivation layers are

not grown in the same reactor; thus, unavoidable air exposure and/or any other process-related steps would result in unwanted interface states, ultimately compromising the device performance.<sup>10</sup> Chemically and thermally stable dielectric materials with high dielectric constants and large bandgaps are coveted for gate passivation layers.<sup>11</sup> Previously, in situ SiNx deposition has been reported on AlGaN/GaNbased devices, demonstrating that the in situ dielectric deposition process improved the electrical performance of the device compared to the ex situ process. 12-14 Typically, SiN<sub>x</sub> dielectric constant (7.4) is low, with a moderate bandgap ranging from 2.9 to 5.1 eV based on the stoichiometric ratio. 12 In situ aluminum oxide-based GaN interlayer vertical trench GaN channel MOSHFET has been demonstrated, showing improvements in device electrical parameters, but no in-depth quantitative analysis was provided for interface trap densities. 15,16 It is noted that oxide-based dielectric material systems have a wide choice of dielectric constants and bandgaps.<sup>17</sup> As in the case of nitride-based dielectric systems, it follows that inclusion of oxide-based dielectrics, particularly in situ varieties, should improve the overall metal oxide semiconductor (MOS)-based device performance. However, integrating III-Nitride and III-oxide precursors in the same reactor brings about process-related challenges. The typical III-nitride-based growth processes use hydrogen as a carrier gas, where the inclusion of oxygen

a)Author to whom correspondence should be addressed: ahmad@cec.sc.edu

(O<sub>2</sub>) precursor may be catastrophic. <sup>18</sup> The commonly used nitrogen precursor ammonia (NH<sub>3</sub>) is highly reactive with oxygen precursors, which may lead to water formation inside the reactor. <sup>19</sup> Thus, the integration of nitride and oxide-based technology in the same reactor is challenging.

In this paper, we report on the in situ oxide dielectric, gallium oxide (Ga<sub>2</sub>O<sub>3</sub>), with a dielectric constant of 10.6 and a bandgap of 4.9 eV, by metal-organic chemical vapor deposition (MOCVD) on an AlGaN/GaN-based HFET structure to create a complete in situ MOSHFET structure in a single process step, starting from the sapphire substrate and without a breaking vacuum. Nitrogen was used as a carrier gas for III-nitride layers to avoid the reaction between highpurity oxygen instead of the typical hydrogen gas. For comparison, we created an ex situ MOSHFET structure where the Ga<sub>2</sub>O<sub>3</sub> layers were grown on the HFET structure albeit after its exposure to air. The thicknesses of the oxide and other layers for the in situ and ex situ structures were kept the same by separately measuring the growth rate of each layer, using UV-vis spectrometer, and then setting the calculated growth time for the required thickness in the device structure. The properties related to the oxide and AlGaN layers were studied, and a comparison was made based on different oxide charges and density of interface traps ( $D_{it}$ ) along with other electrical parameters, We also investigated the root cause for the threshold voltage ( $V_{th}$ ) shift using a thickness-dependent model,<sup>20,21</sup> correlating the theory and our experimental data.

The epilayer structures for this study were deposited on a c-plane sapphire substrate with 0.2° miscut toward m-plane in a custom-built vertical metal-organic chemical vapor deposition (MOCVD) system, with nitrogen ( $\stackrel{\frown}{N}$ ) as the carrier gas. Trimethylaluminum (TMAl), ammonia (NH3), and ultra-high purity oxygen (O2) were used as aluminum (Al), nitrogen, and oxygen precursors. The choice of triethylgallium (TEGa) as the gallium (Ga) precursor is motivated by previous reports, which infers that the use of TEGa can reduce GaN yellow band defects in the nitrogen carrier gas approach.<sup>22</sup> The epilayers of the MOSFET structure consist of a thin 150 nm aluminum nitride (AlN) layer<sup>23,24</sup> a 500 nm thick gallium nitride (GaN) layer grown using a V/III ratio of 8000 at a temperature of 960 °C, a 2 nm AlN spacer, and a 25 nm thick aluminum gallium nitride (Al<sub>0.3</sub>Ga<sub>0.7</sub>N) barrier layer grown using a V/III ratio of 5000 at a temperature of 1020 °C at 100 Torr chamber pressure, and finally, a set of 10, 20, and 30 nm thick **b**-Ga<sub>2</sub>O<sub>3</sub> layers as gate dielectrics were grown at 700 °C, 50 Torr chamber pressure, and a VI/III ratio of ~900.25 For the in situ growth process, the system was nitrogen purged for 30 min prior to growing Ga<sub>2</sub>O<sub>3</sub> in order to avoid an overlap of oxygen and hydrogen species at 50 Torr. In the case of ex situ process, the same growth recipe parameters were used as the in situ process, but the growth of nitride and oxide was accomplished in two steps, in the first steps, the nitride layers were grown and the sample was taken out of the growth chamber, and in the second step, the sample was placed back in the chamber and oxide growth was performed, mimicking the typical growth sequence of producing the MOSHFET structure. A Rigaku Miniflex II Desktop x-ray diffractometer with Cu-Ka1 x-ray source (k 1/4 1.5406 A°) operated at 30 mA current and 15 kV voltage was used to evaluate the structural properties of the epilayers. The capacitance-voltage (C-V) measurements were performed using a mercury probe controller (Materials Development Corporation, CA, USA) model 802B connected with an HP 4284A Precision LCR Meter capable of measuring

the impedance as a function of frequency. The gate diameter of the mercury probe was 797 lm with 0.1 pF stray capacitance.

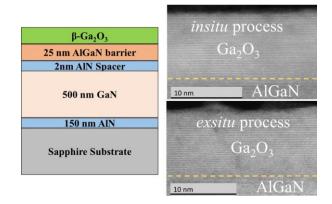

Figure 1 shows the device structures investigated, where Fig. 1(a) exhibits the schematic of the MOSHFET structure. Figures 1(b) and 1(c) show the high-resolution transmission electron microscopy (HR-TEM) images of the barrier AlGaN and Ga<sub>2</sub>O<sub>3</sub> interface for a 10 nm thick Ga<sub>2</sub>O<sub>3</sub> MOSHFET structure with oxide layer grown by *in situ* and *ex situ* processes, respectively. The interfaces are marked by dashed lines for clarity. We observe no apparent defects or imperfections, such as dislocations, stacking faults, or grain boundaries, present at the interface in both *in situ* and *ex situ* processes. From the atomic arrangement in the HR-TEM image, we can infer that the transition from AlGaN to Ga<sub>2</sub>O<sub>3</sub> did not create visible defects that can impact the electrical property; to confirm this, a detailed study will be needed, which is beyond the scope of this paper.

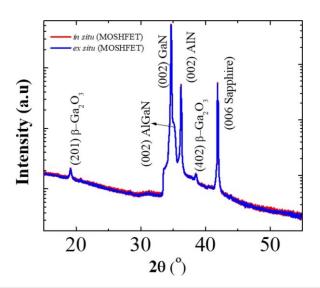

To understand the crystalline properties of the complete MOSHFET structure and to identify the presence of any other Ga<sub>2</sub>O<sub>3</sub> phase, XRD 2h scans were performed, as shown in Fig. 2. Due to the notably different lattice structures of AlGaN and b-Ga<sub>2</sub>O<sub>3</sub>, the stable phase monoclinic b-Ga<sub>2</sub>O<sub>3</sub> grows in the ½ 201] direction on (0001) oriented wurtzite AlGaN.<sup>26</sup> Here, we observed no change in peak positions of the *in situ* and *ex situ* MOSHFET structures. The peaks at 18.8° and 38.2° are related to the (201) and (402) Ga<sub>2</sub>O<sub>3</sub> of the b phase.<sup>27</sup> The peak at 34.5° and the adjacent higher angle shoulder are consistent with the (002) reflection from the GaN channel and AlGaN barrier layers, respectively.<sup>28</sup> Note that the GaN channel layer was grown on 0.15 lm thick AlN; thus, the peak at 36.1° is due to the (002) AlN reflection. The peaks at 20.4° and 41.6° correspond to the (003) and (006) sapphire reflections, respectively.<sup>27</sup> Guided by the XRD data and HR-TEM images, we can conclude that both the Ga<sub>2</sub>O<sub>3</sub> and

AlGaN were crystalline in both types of (in situ and ex situ) MOSHFET structures. Despite the change in orientation of  $Ga_2O_3$  to fit the lattice structure of AlGaN on which it is grown, there was no visible structural defect formation at the interface of these two materials.

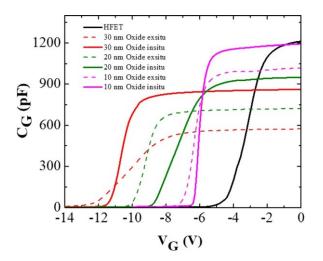

Figure 3 shows the capacitance-voltage (C-V) measurement for the MOSHFET structures investigated in this paper. The threshold voltage shifts, and capacitance in the accumulation region decreases when a b-Ga<sub>2</sub>O<sub>3</sub> is incorporated as a passivation layer on top of an

FIG. 1. (a) Schematic of the epilayer structure  $Ga_2O_3/Al_{0.3}Ga_{0.7}N/GaN$  MOSHFET and (b) HR-TEM image of  $Ga_2O_3/Al_{0.3}Ga_{0.7}N$  interface for *in situ* and (c) *ex situ* grown MOSHFET structures.

FIG. 2. XRD 2h scan of the MOSHFET structure showing crystalline  $Ga_2O_3$  (b phase), GaN, AlGaN, AlN, and sapphire substrate peaks.

Al<sub>0.3</sub>Ga<sub>0.7</sub>N/GaN HFET structure. Typically, with the increase in dielectric layer thickness, and decrease in dielectric constant, the threshold voltage shifts to a higher value.<sup>25</sup> The addition of an oxide layer adds a capacitance in series with the overall capacitance described as  $\frac{1}{C_G} = \frac{1}{C_b} + \frac{1}{C_o}$ , where  $C_b$  is the Al<sub>0.3</sub>Ga<sub>0.7</sub>N barrier layer capacitance,

$C_{ox}$  is the capacitance Ga<sub>2</sub>O<sub>3</sub> layer,  $C_{ox}$  is the total gate capacitance; thus, the capacitance in accumulation region of C-V curve decreases with the increase in the dielectric layer thickness. From Fig. 3, one can also discern that for similar oxide thickness, the threshold voltage shift is smaller associated with the  $in \ situ$  process as compared to the  $ex \ situ$  process. We also observe that the capacitance of the MOSHFET structure in the accumulation region grown by  $in \ situ$  process is higher than the MOSFET structure grown by the  $ex \ situ$  process, indicating

FIG. 3. C-V characteristics at 1 MHz frequency of MOSHFET structures with different oxide thicknesses. The *in situ* and the *ex situ* growths are indicated by the solid and dashed lines, respectively.

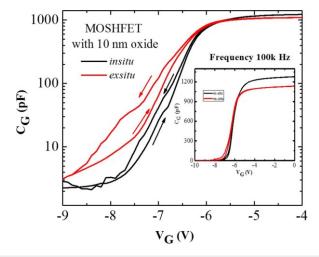

the reduction in extra charges at the oxide and AlGaN interface or reduction in the oxide thickness or increase in the dielectric constant. To confirm the cause of the difference in the capacitance of ex situ and in situ grown MOSHFET structures, C-V hysteresis measurements were performed at 10 k Hz. Figure 4 shows the results of C-V hysteresis measurements for both in situ and ex situ MOSHFET structures on the logarithmic scale; to observe the differences clearly, we plotted the vertical axis on the logarithmic scale, whereas inset of the graph depicted on linear scale; the C-V plots clearly show that MOSHFET growth by the ex situ process has more interfacial charges in its structure. Furthermore, the thickness is confirmed by TEM measurements, and material properties are confirmed by x-ray measurements; thus, we conclude that decrease in the capacitance is due to extra charges at the interface in the ex situ grown MOSHFET structure. The twodimensional electron gas (2DEG) carrier concentration (ns) for all three samples was measured by C-V, and the 2DEG carrier concentrations in ex situ and in situ processes were found to be in the range of  $1.18 \times 10^{13}$ – $1.42 \times 10^{13}$  cm<sup>-2</sup>, respectively, for different thickness samples. The origin of the shift in threshold voltage can be attributed to the gate-to-channel distance and to the bulk oxide charge density  $(n_{ox,bulk})$ , and the interface oxide charge density  $(n_{ox,int})$ , and can be visualized using the equation as follows: 20,25,29

$$V_{th} = u_b - u_f - DE_C - \frac{q_{ox}^t}{2e_{ox}} n_{ox;bulk} - \frac{q_{ox}^t}{e_{ox}} n_{ox;intf} - q \frac{t_{ox}}{e_{ox}} + \frac{t_b}{e_b};$$

(1)

where  $u_b$  is the metal-barrier height and taken as 4.5 eV as we are using a mercury probe as gate metal with a diameter of 798 lm, employing a resistance capacitor parallel equivalent model, with minimal effect of connect resistance. The term  $DE_C$  is the conduction band discontinuity at the oxide AlGaN interface.  $u_f$  is the energy difference between the conduction band and Fermi energy level in the GaN, and  $t_{ox}$  and  $t_{ox}$  are the oxide and barrier layer thicknesses. The impact of in situ passivation and the dependence of  $V_{th}$  on the ex situ and in situ process need an analytical model to decipher any correlation between the process and the electrostatic centric parameters associated with the

FIG. 4. Magnified *C-V* hysteresis characteristics of *in situ* and *ex situ* grown MOSHFET structure; inset shows the full range of data.

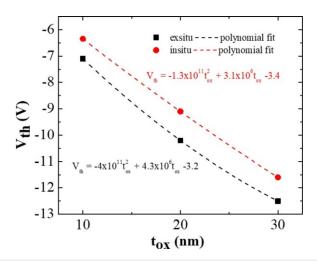

FIG. 5. MOSHFET threshold voltage dispersion for *in situ* and *ex situ* processes with  $Ga_2O_3$  thicknesses of 10, 20, and 30 nm. The points show experimental values, and dashed lines are polynomial fits.

two different processes. We used the oxide thickness-dependent C-V measurements to gauge the influence of different oxide charges on the Vth shift. Based on Eq. (1), Vth can be represented as second order polynomial function, as shown in Fig. 5. Through a polynomial fitting process of the thickness-dependent  $V_{th}$  dispersion,  $n_{ox,bulk}$  and  $n_{ox,intf}$ can be calculated. Note that these values are an average over the area of the capacitor, and there can be another term, such as  $N_{d,surf}$ , usually used to explain the formation of a 2DEG at the barrier and channel layer interface. The said charge ( $N_{d,surf}$ ) is formed during the growth process and follows the charge neutrality condition to minimize the free energy.<sup>20</sup> The interface charge depends on the oxide layer thickness and is usually compensated by the formation of 2DEG and can be excluded from the calculation.<sup>20</sup> From the fit, the value of  $n_{ox,bulk}$  for the ex situ MOSHFET samples was found to be  $+8.9 \times 10^{20}$  cm<sup>-3</sup>, whereas the value for the same for the in situ sample was  $+1.5 \times 10^{20}$  cm<sup>-3</sup>, which is smaller compared to the *ex situ* process. The value of noxint for the ex situ and in situ grown MOSHFET structures were found to be  $-2.5 \times 10^{15}$  cm<sup>-2</sup> and  $-1.8 \times 10^{15}$  cm<sup>-2</sup>, indicating a slightly lower value for the in situ grown MOSHFET structure. It is evident that both  $n_{ox,bulk}$  and  $n_{ox,intf}$  for the in situ MOSHFET structure are lower compared to the ex situ MOSHFET structure and can contribute

to the  $V_{th}$  shift. The correlation between Fig. 5 and constant term of Eq. (1) as a function oxide thickness give us the value of 1.1 eV for DEc.

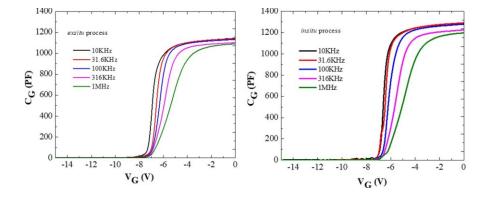

To further identify the dominating parameters responsible for the observed  $V_{th}$  shift, we calculated the density of interfacial trap states  $(D_{tt})$  at zero gate voltage. The frequency-dependent capacitances through Hi-Lo frequency method and the associated Eq. (2), was used to calculate the interfacial trap density  $(D_{tt})$  in both  $in \ situ$  and  $ex \ situ$  grown MOSHFET structures. The  $(D_{tt})$  in  $(D_{tt})$  in  $(D_{tt})$  is a low frequency and 1 M Hz was taken as a high frequency. At low frequencies, the trap states get sufficient time to respond to voltage modulation, leading to higher capacitance, whereas, at high frequencies, they cannot respond, leading to a low capacitance value. In this methodology, the interfacial trapped state density is given as follows:  $(D_{tt})$

$$D_{it}(V_G) = \frac{C_{ox}}{q} \frac{C_{LF}}{C_{ox} - C_{LF}} - \frac{C_{HF}}{C_{ox} - C_{HF}};$$

(2)

where  $C_{ox}$  is the capacitance of the dielectric oxide layer, which can be calculated using the parallel plate capacitor formula, q is the unit elementary charge,  $C_{LF}$  is the MOSHFET low-frequency capacitance value, and  $C_{HF}$  is the MOSHFET high-frequency capacitance value. Figure 6 shows the frequency-dependent capacitance data for both in situ and ex situ MOSHFET structures for a common 10 nm  $Ga_2O_3$  layer. The value of  $D_{it}$  for the ex situ MOSHFET structure is  $\sim 10^{12} \, \mathrm{cm}^{-2} \, \mathrm{eV}^{-1}$ , which is reduced to  $\sim 10^{11} \, \mathrm{cm}^{-2} \, \mathrm{eV}^{-1}$  for the in situ MOSFET structure (exact values are mentioned in Table I), which is remarkable. This reduction of  $\sim 80\%$  in the interfacial trap density is most likely the main contributing factor for  $V_{th}$  improvement as a result of the in situ process. Any improvement in  $V_{th}$  bodes very well in our quest to improve device performance.

In summary, we have demonstrated a process for *in situ* oxide dielectric deposition in the same reactor without breaking the vacuum, integrating III-Nitride and III-Oxide technology using N<sub>2</sub> as the carrier gas that results in a lower density of interface traps (charges). No significant crystal quality difference observed in comparing both processes by using TEM and XRD was notable. Compared to *ex situ* MOSHFET structures, the threshold voltage is improved by ~10% in the case of the *in situ* sample, which is a critical scaling factor for power efficiency, which results in higher transconductance and hence the improvement of the gain of the FET. Based on the analytical model, we found that all the key parameters, namely  $n_{ox,bulk}$ ,  $n_{ox,intf}$ , and  $D_{it}$ , reduced for the *in situ* MOSHFET variety. It should be stressed that

FIG. 6. Frequency-dependent C-V characteristic of a MOSHFET with 10 nm thick gate oxide at frequencies of 100 kHz, 316 kHz, and 1 MHz for the (a) *in situ* and (b) *ex situ* structure.

TABLE I. The summary of the key electrical parameters measured/calculated for HFET, in situ and ex situ MOSFET structures.

| Structure/process                                                       | HFET       | MOSHFET      |         | MOSHFET |              | MOSHFE'I |         |

|-------------------------------------------------------------------------|------------|--------------|---------|---------|--------------|----------|---------|

|                                                                         |            | Ex situ      | In situ | Ex situ | In situ      | Ex situ  | In situ |

| tox (nm)                                                                | 0          | 10           | 10      | 20      | 20           | 30       | 30      |

| $V_{th}$ (V)                                                            | <b>-</b> 5 | <b>—</b> 7.1 | -6.3    | -10.2   | <b>-</b> 9.1 | -12.5    | -11.6   |

| $n_{\rm s}$ (cm <sup>-2</sup> )× 10 <sup>13</sup>                       | 1.25       | 1.28         | 1.32    | 1.24    | 1.42         | 1.4      | 1.18    |

| $D_{it}$ (cm <sup>-2</sup> eV <sup>-1</sup> ) $\times$ 10 <sup>11</sup> | NA         | 22.3         | 5.52    | 75.7    | 8.52         | 49.8     | 8.05    |

reduction in  $D_{it}$  by an order of magnitude with the  $in \ situ$  approach is the main reason for threshold voltage improvement. The method developed here is applicable for incorporation of other oxide systems in electronic devices subject to the availability of MOCVD compatible precursors.

This work was supported by the National Science Foundation (NSF) Award No. 2124624, managed by Dr. Dominique Dagenais, and NSF Award No. 2329786, managed by Dr. Samir Iqbal.

# AUTHOR DECLARATIONS Conflict of Interest

The authors have no conflicts to disclose.

#### **Author Contributions**

Samiul Hasan: Conceptualization (equal); Data curation (equal); Formal analysis (equal); Investigation (equal); Writing - original draft (equal); Writing - review & editing (equal). Mohi Uddin Jewel: Data curation (equal); Writing - review & editing (equal). Scott R. Crittenden: Data curation (equal); Resources (equal); Writing - review & editing (equal). Md Ghulam Zakir: Data curation (equal); Resources (equal). Nifat Jahan Nipa: Data curation (equal); Resources (equal). Vitaliy Avrutin: Data curation (equal); Formal analysis (equal); Resources (equal); Writing - review & editing (equal). € mit Szgu€r: Data curation (equal); Resources (equal). Hadis Morkoc.: Conceptualization (equal); Formal analysis (equal); Methodology (equal); Resources (equal); Writing - review & editing (equal). Iftikhar Ahmad: Conceptualization (equal); Data curation (equal); Formal analysis (equal); Funding acquisition (equal); Investigation (equal); Methodology (equal); Project administration (equal); Resources (equal); Validation (equal); Writing - review & editing (equal).

# DATA AVAILABILITY

The data that support the findings of this study are available from the corresponding author upon reasonable request.

## **REFERENCES**

- <sup>1</sup>H. Morkoc, Handbook of Nitride Semiconductors and Devices, Materials Properties, Physics and Growth (John Wiley & Sons, 2009).

- <sup>2</sup>H. Morkoc, *Nitride Semiconductors and Devices* (Springer Science & Business Media, 2013), Vol. 32.

- <sup>3</sup>R. Trew, D. S. Green, and J. B. Shealy, IEEE Microwave 10(4), 116 (2009).

- <sup>4</sup>T. Hashizume, S. Ootomo, and H. Hasegawa, Appl. Phys. Lett. 83(14), 2952 (2003).

- <sup>5</sup>B. Ubochi, K. Ahmeda, and K. Kalna, ECS J. Solid State Sci. Technol. 6(11), S3005 (2017).

- <sup>6</sup>J. H. Leach and H. Morkoc, Proc. IEEE 98(7), 1127 (2010).

- <sup>7</sup>H. Zhou, X. Lou, K. Sutherlin, J. Summers, S. B. Kim, K. D. Chabak, R. G. Gordon, and P. D. Ye, IEEE Electron Device Lett. 38(10), 1409 (2017).

- <sup>8</sup>F. Husna, M. Lachab, M. Sultana, V. Adivarahan, Q. Fareed, and A. Khan, IEEE Trans. Electron Devices 59(9), 2424 (2012).

- <sup>9</sup>J. T. Asubar, Z. Yatabe, D. Gregusova, and T. Hashizume, J. Appl. Phys. 129(12), 121102 (2021).

- <sup>10</sup>J. Derluyn, S. Boeykens, K. Cheng, R. Vandersmissen, J. Das, W. Ruythooren, S. Degroote, M. R. Leys, M. Germain, and G. Borghs, J. Appl. Phys. 98(5), 054501 (2005).

- <sup>11</sup>B. Lee, L. Kang, R. Nieh, W. Qi, and J. Lee, Appl. Phys. Lett. 76(14), 1926 (2000).

- <sup>12</sup>A. Siddique, R. Ahmed, J. Anderson, M. Nazari, L. Yates, S. Graham, M. Holtz, and E. L. Piner, ACS Appl. Electron. Mater. 1, 1387 (2019).

- <sup>13</sup>H. Jiang, C. Liu, Y. Chen, X. Lu, C. W. Tang, and K. M. Lau, IEEE Trans. Electron Devices 64(3), 832 (2017).

- <sup>14</sup>M. Germain, K. Cheng, J. Derluyn, S. Degroote, J. Das, A. Lorenz, D. Marcon, M. Van Hove, M. Leys, and G. Borghs, Phys. Status Solidi C 5(6), 2010 (2008).

- <sup>15</sup>C. Gupta, S. H. Chan, Y. Enatsu, A. Agarwal, S. Keller, and U. K. Mish, IEEE Electron Device Lett. 37(12), 1601 (2016).

- <sup>16</sup>C. Gupta, C. Lund, S. H. Chan, A. Agarwal, J. Liu, Y. Enatsu, S. Keller, and U. K. Mishra, IEEE Electron Device Lett. 38(3), 353 (2017).

- <sup>17</sup>T. Hashizume, K. Nishiguchi, S. Kaneki, J. Kuzmik, and Z. Yatabe, Mater. Sci. Semicond. Process 78, 85 (2018).

- <sup>18</sup>M. A. A. Clyne and B. A. Thrush, Nature 189(4759), 135 (1961).

- <sup>19</sup>E. A. Albers, K. Hoyermann, H. G. Wagner, and J. Wolfrum, Symp. (Int.) Combust. 15(1), 765 (1975).

- <sup>20</sup>M. T apajna and J. Kuzmík, Appl. Phys. Lett. 100(11), 113509 (2012).

- <sup>21</sup>Y. Zhang, M. Sun, S. J. Joglekar, T. Fujishima, and T. Palacios, Appl. Phys. Lett. 103(3), 033524 (2013).

- <sup>22</sup>T. Hub´a´cek, A. Hospodkov´a, K. Kuldov´a, M. Slavick´a Zîkov´a, J. Pangr´ac, J. C´ı´zek, M. O. Liedke, M. Butterilng, A. Wagner, P. Hubík, and E. Hulicius, J. Cryst. Growth 531, 125383 (2020).

- <sup>23</sup>S. Hasan, A. Mamun, K. Hussain, M. Gaevski, I. Ahmad, and A. Khan, J. Mater. Res. 36(21), 4360 (2021).

- <sup>24</sup>S. Hasan, M. U. Jewel, S. G. Karakalos, M. Gaevski, and I. Ahmad, Coatings 12(7), 924 (2022).

- 25S. Hasan, M. U. Jewel, S. R. Crittenden, D. Lee, V. Avrutin, U€. O€ zgu€r, H. Morkoc, , and I. Ahmad, Crystals 13(2), 231 (2023).

- <sup>26</sup>M. U. Jewel, S. Hasan, S. R. Crittenden, V. Avrutin, U€. O€ zgu€r, H. Morkoc, and I. Ahmad, Phys. Status Solidi A 220(11), 2300036 (2023).

- <sup>27</sup>S. Ghose, S. Rahman, L. Hong, J. S. Rojas-Ramirez, H. Jin, K. Park, R. Klie, and R. Droopad, J. Appl. Phys. 122(9), 095302 (2017).

- <sup>28</sup>M. A. Moram and M. E. Vickers, Rep. Prog. Phys. 72(3), 036502 (2009).

- <sup>29</sup>S. Mollah, K. Hussain, A. Mamun, D. Alam, M. Chandrashekhar, G. Simin, and A. Khan, Appl. Phys. Express 15(10), 104001 (2022).

- <sup>30</sup>D. K. Schroder, Semiconductor Material and Device Characterization (John Wiley & Sons, Inc., 2005).