# 1 kV Self-Aligned Vertical GaN Superjunction Diode

Yunwei Ma, Student Member, IEEE, Matthew Porter, Yuan Qin, Joseph Spencer, Zhonghao Du, Ming Xiao, Yifan Wang, Ivan Kravchenko, Dayrl P Briggs, Dale K Hensley, Florin Udrea, Member, IEEE, Marko Tadjer, Senior Member, IEEE, Han Wang, Senior Member, IEEE, and Yuhao Zhang, Senior Member, IEEE

Abstract— This work demonstrates vertical GaN superjunction (SJ) diodes fabricated via a novel self-aligned process. The SJ comprises n-GaN pillars wrapped by the charge-balanced p-type nickel oxide (NiO). After the NiO sputtering around GaN pillars, the self-aligned process exposes the top pillar surfaces without the need for additional lithography or a patterned NiO etching which is usually difficult. The GaN SJ diode shows a breakdown voltage (BV) of 1100 V, a specific on-resistance ( $R_{\rm ON}$ ) of 0.4 mΩ·cm², and a SJ drift-region resistance ( $R_{\rm dr}$ ) of 0.13 mΩ·cm². The device also exhibits good thermal stability with BV retained over 1 kV and  $R_{\rm ON}$  dropped to 0.3 mΩ·cm² at 125 °C. The trade-off between BV and  $R_{\rm dr}$  is superior to the 1D GaN limit. These results show the promise of vertical GaN SJ power devices. The self-aligned process is applicable for fabricating the heterogeneous SJ based on various wide- and ultra-wide bandgap semiconductors. <sup>1</sup>

Index Terms— power electronics, gallium nitride, nickel oxide, superjunction, charge balance, self-align, high voltage

## I. INTRODUCTION

Superjunction (SJ) is arguably one of the most innovative device structures for power electronics [1]. It consists of alternative n- and p-type regions with the balanced charge, which engineer electric field (E-field) in an additional direction normal to the current conduction [2]. In a vertical SJ device, the charge balance allows for high doping concentration while retaining a uniform blocking E-field, enabling the specific onresistance ( $R_{\text{ON,SP}}$ ) to linearly increase with breakdown voltage (BV). In contrast, 1D devices are limited by a trade-off that  $R_{\text{ON,SP}}$  increases with the square of BV [1].

SJ has achieved a success in Si [3] and was recently reported in SiC [4]–[6]. It promises a superior limit in GaN. However, there still lacks experimental demonstration of a full GaN SJ due to fabrication challenges. Despite the recent progress on p-GaN regrowth [7] and ion implantation [8], the accurate charge control in the selective-area p-GaN is still difficult. Meanwhile, SJ concept has been leveraged in lateral GaN devices based on polarization charges [9]–[13]; but these devices are still limited by a  $R_{on,sp} \propto BV^2$  trade-off [2].

An alternative approach to make the SJ is pairing the n-type semiconductor with a distinct p-type material. Nickel oxide (NiO) is a candidate p-type material for GaN, as its bandgap (3.4~4 eV) and projected critical E-field (5 MV/cm [14]) are higher than GaN and it can form non-leaky junctions on GaN

This work is supported in part by Office of Naval Research monitored by Lynn Petersen (Grant N00014-21-1-2183), National Science Foundation (Grant ECCS-2036740), and CPES Power Management Industry Consortium. Device fabrication was conducted as part of a user project at the Center for Nanophase Materials Sciences, which is a DOE Office of Science User Facility at Oak Ridge National Laboratory. (Corresponding author: Yuhao Zhang).

Y. Ma, M. Porter, Y. Qin, J. Spencer, M. Xiao, Y. Wang, and Y. Zhang are with the Center of Power Electronics Systems, Virginia Polytechnic Institute and State University, Blacksburg, VA 24060 USA (e-mail: yhzhang@vt.edu).

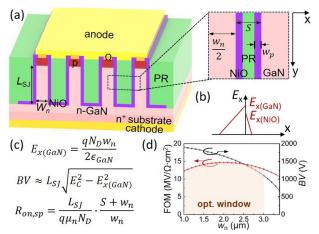

Fig. 1. (a) Schematic of the vertical GaN/NiO SJ diode and a SJ unit-cell. (b) Schematic of the lateral E-field distribution. (c) Major models of the BV and  $R_{\rm ON,SP}$  of the SJ region. (d) Modeled SJ FOM and BV as a function of  $w_{\rm n}$ .

[15]. Recently, a tunable acceptor concentration ( $N_A$ ) is realized in p-NiO, enabling fabrication of a vertical GaN heterojunction-based SJ [16].

However, the SJ fabrication in [16] is very complicated mainly due to the difficulty of NiO etch. It involves two steps of deep GaN etch and multiple alignments to the narrow n-GaN pillars. Besides, the outer sidewalls of periphery GaN pillars are not covered by NiO; the charge balance requires a halved pillar width and thus more demanding lithography. It is also unknown if the charge balance and high *BV* in such a hetero-SJ can be retained at high temperature.

This work addresses the above challenges via a novel self-aligned process, which allows for depositing the sidewall NiO and lifting off the cap NiO in a single, dry-etch-free step. This process obviates the need for the alignments to narrow pillars or adding the narrower pillars at device edge, and only a single GaN deep etch is needed. The fabricated GaN SJ diode shows a BV of 1.1 kV and a differential  $R_{\rm ON,SP}$  of 0.4 m $\Omega$ ·cm<sup>2</sup>. Both BV and  $R_{\rm ON,SP}$  show good thermal stability.

## II. DEVICE DESIGN

Fig. 1(a) shows the schematic of the vertical GaN SJ diode. A GaN p-n junction is designed to avoid the surface breakdown and probe the true BV of GaN SJ; it can be a building block of future GaN SJ transistors. The epi consists of 40 nm p<sup>++</sup>-GaN,

- J. Spencer and M. Tadjer are with the U. S. Naval Research Laboratory, Washington, DC 20375 USA.

- Z. Du is with Ming Hsieh Department of Electrical and Computer Engineering, University of Southern California, Los Angeles, CA 90089 USA.

- I. Kravchenko, D. P. Briggs, and D. K. Hensley are with the Oak Ridge National Laboratory, Oak Ridge, TN 37830 USA.

- F. Udrea is with the Department of Engineering, University of Cambridge, CB2 1TN Cambridge, UK.

- H. Wang is with the Department of Electrical and Electronic Engineering, University of Hong Kong, Hong Kong SAR, China.

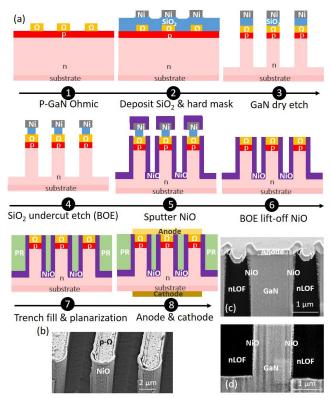

Fig. 2. (a) The main fabrication steps. (b) Top-view SEM images of the GaN pillars after the NiO cap lift-off. Cross-sectional SEM images of the final device with  $w_n = 1.5~\mu m$  in the (c) top SJ and (d) pillar bottom regions.

300 nm p-GaN ([Mg]:  $10^{19}$  cm<sup>-3</sup>), 8  $\mu$ m n-GaN ([Si]:  $9\times10^{16}$  cm<sup>-3</sup>), and 0.8  $\mu$ m n<sup>+</sup>-GaN, grown on 2-inch GaN substrates by Enkris Semiconductor Inc. Here n-GaN is doped  $\sim10$ X higher than 1D devices. The sidewall NiO width ( $w_p$ ) is designed based on  $w_pN_A = N_D w_n/2$  for charge balance, where  $w_n$  is the GaN pillar width and  $N_D$  is the donor concentration. The anode forms Ohmic contacts to both p-GaN and NiO.

The  $N_{\rm D}$  and  $N_{\rm A}$  are first characterized with two test structures. The  $N_{\rm D}$  is extracted to be  $8\times10^{16}$  cm<sup>-3</sup> from the C-V data of a vertical GaN p<sup>+</sup>-n diode. The  $N_{\rm A}$  of NiO can be tuned by the O<sub>2</sub> partial pressure in sputtering [16]. In this work, we use an Ar:O<sub>2</sub> flow rate of 20:1. The  $N_{\rm A}$  of NiO is extracted to be  $1.3\times10^{18}$  cm<sup>-3</sup> from the C-V data of a p-NiO/n<sup>+</sup>-Ga<sub>2</sub>O<sub>3</sub> diode similar to [17]. When temperature increases from 25 °C to 125 °C,  $N_{\rm A}$  shows an increase by 2.5%, while  $N_{\rm D}$  shows nearly no change.

With the determined  $N_D$  and  $N_A$ ,  $w_n$  is then optimized using the vertical SJ figure of merit ( $FOM_{SJ} = BV/R_{on,sp}$ ). Here we set the GaN pillar spacing (S) to be 1  $\mu$ m to avoid the NiO early coalescence issue in narrow trenches [16]. As shown in Fig. 1(b)-(c), the SJ's BV and  $R_{ON,SP}$  are modeled as a function of  $w_n$ . As  $w_n$  increases, the lateral E-field ( $E_x$ ) increases, reducing the vertical E-field ( $E_y$ ) and BV. Meanwhile,  $R_{ON,SP}$  decreases with the increased  $w_n$  due to a larger ratio ( $\beta$ ) between the GaN conduction area and the total device area ( $\beta$ =1+ $S/w_n$ ). Fig. 1(d) shows the modeled BV and  $FOM_{SJ}$  as a function of  $w_n$ , assuming that the SJ length ( $L_{SJ}$ ) and n-GaN mobility ( $\mu_n$ ) are 6  $\mu$ m and 600 cm²/Vs, respectively. A  $w_n$  window of 1~3  $\mu$ m is identified for the optimal  $FOM_{SJ}$ .

### III. DEVICE FABRICATION AND SIMULATION

Fig. 2(a) shows the main steps of device fabrication. Ni/Au (5/20 nm) Ohmic contact to p-GaN is first formed with 560 °C annealing in the air. 1  $\mu$ m thick SiO<sub>2</sub> is then deposited, followed by lifting off the Ti/Ni (10/340 nm) hard mask for GaN etching. The n-GaN pillar is etched with a ~6.5  $\mu$ m depth with the sidewall aligned to the m-plane, followed by a wet treatment to reduce the etch damage [18]. The sample is then dipped into 1:10 BOE for 40 s to produce an undercut on the SiO<sub>2</sub> sidewall. NiO is deposited by magnetron sputtering under the 60/3 sccm Ar/O<sub>2</sub> flow rate with other conditions identical to [17]. The undercut leaves the SiO<sub>2</sub> sidewall un-covered by NiO. A ~30 min rinse in 1:10 BOE follows to etch SiO<sub>2</sub> and naturally remove the NiO cap on GaN pillars.

A photoresist planarization process similar to [19] is then used to fill GaN trenches and connect all top contacts. The nLOF2020 is used, followed by a  $O_2$  etch to expose the Ohmic metals. Following a flood exposure and baking, a Ni/Au metal pad is deposited as the anode, which also forms Ohmic contact to the sidewall NiO. The cathode is formed at the backside of GaN substrate. Devices with  $w_n$  of  $1\sim3$   $\mu$ m are fabricated with S of 1  $\mu$ m and a target  $w_p$  of  $\sim45$  nm.

Fig. 2(b) shows the scanning electron microscopy (SEM) images of the device after the self-aligned process, revealing the complete lift-off of NiO caps and exposure of the p-GaN Ohmic metals. Fig. 2(c)-(d) shows the cross-sectional SEM images of the top and bottom SJ regions in the final device. The sidewall NiO thickness is found to decrease from ~100 nm to ~40 nm in the top 2  $\mu m$  of the SJ region, and remains nearly constant in the bottom 4  $\mu m$  SJ. This is due to the higher deposition rate of NiO near the planar surface. This higher planar deposition rate also leads to a thicker NiO at the trench bottom (~80 nm).

### IV. DEVICE CHARACTERISTICS

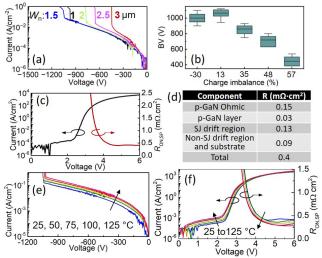

Current density is normalized to the entire anode area. Fig. 3(a) shows the reverse I-V characteristics of the GaN SJ diodes with various  $w_n$ . The BV first increases with  $w_n$ , reaching 1100 V at  $w_n$  of 1.5  $\mu$ m, and then decreases with  $w_n$ . The leakage current is below  $5\times10^{-2}$  A/cm² before BV. Fig. 3(b) shows the box plots of BV as a function of the charge imbalance percentage ( $\delta$ ) in the main SJ region as calculated by  $\delta = 1 - 2w_pN_A/w_nN_D$ . Here  $w_p$  of 40 nm is used. For each  $\delta$ , BV of six devices at different locations of the sample are measured. The result shows the strong impact of the SJ charge balance on BV, which is a key signature of SJ devices.

Fig. 3(c) shows the forward I-V characteristics of the device with  $w_n = 1.5 \mu m$ , revealing a differential  $R_{\rm ON,SP}$  of 0.4 mΩ·cm². Fig. 3(d) lists the  $R_{\rm ON,SP}$  components. The p-GaN contact resistance accounts for 40% of  $R_{\rm ON,SP}$ . It is calculated by scaling the contact resistance measured by the transfer length method by the ratio β. The resistances of the p-GaN layer and the SJ drift region are ~0.03 and 0.13 mΩ·cm², respectively, calculated using the respective layer thickness, β, and the carrier mobility and concentration.

Fig. 3(e) shows the reverse I-V characteristics at temperature (T) up to 125 °C. The non-destructive BV extracted at a 1A/cm<sup>2</sup> compliance is nearly constant at 25~75 °C and starts to decrease at higher T, remaining >1 kV at 125 °C. The leakage current at 1 kV increases by only 3 times from 25 to 125 °C.

Fig. 3(f) shows the forward I-V characteristics at T up to 125

Fig. 3. (a) Reverse I-V characteristics of the vertical GaN SJ diodes with  $w_n$  of 1~3  $\mu$ m and the identical S and  $w_p$ . (b) Box plot of the BV as a function of the SJ charge imbalance percentage. (c) Forward I-V characteristics and the extracted differential  $R_{\rm ON,SP}$  of the SJ diodes with  $w_n$ =1.5  $\mu$ m. (d) Component of the total device  $R_{\rm ON,SP}$ . Temperature-dependent (e) reverse I-V and (f) forward I-V and differential  $R_{\rm ON,SP}$  characteristics at 25 to 125 °C of the SJ diode with  $w_n$ =1.5  $\mu$ m.

°C, revealing a  $R_{\rm ON,SP}$  drop to 0.3 mΩ·cm². The  $R_{\rm ON,SP}$  reduction at high T could be due to two mechanisms: a) reduced p-GaN resistance and Ohmic contact resistance [20], and b) enhanced conduction via the p-NiO/n-GaN path due to the reduced NiO resistivity. The first mechanism is proved by the  $R_{\rm ON,SP}$  of 1D GaN p-n diodes fabricated on the same wafer, which decreases from 0.28 mΩ·cm² to 0.25 mΩ·cm² from 25 °C to 125 °C. The latter mechanism is supported by current increase with T in the SJ diode at the forward voltage below 2 V. In this bias range, minimal current increase is observed in the GaN p-n diode (the built-in potential of the NiO/GaN and GaN p-n junction is ~1.6 V and 3 V, respectively).

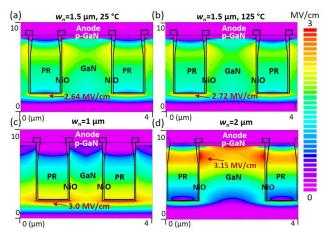

Simulation is used to understand the breakdown mechanism of the fabricated SJ device considering the non-uniform NiO thickness at the trench bottom and sidewall. In addition to the global SJ charge balance, the other determining factor of device BV is the local E-field crowding at the trench bottom formed by the thicker NiO. For  $w_n = 1.5 \mu m$ , the peak E-field is located at the trench bottom (Fig. 4(a)). As this E-field is induced by the locally excessive p-type charge, it is sensitive to  $N_A$ . At high T, the higher  $N_A$ , despite possibly improving the global SJ charge balance, leads to higher E-field stress at the trench bottom (Fig. 4(b)). This could explain the negative temperature coefficient of the experimental device BV.

This factor also impacts the  $w_n$  modulation of device BV. At  $w_n = 1 \mu m$ , the peak E-field is still located at the trench bottom (Fig. 4(c)), suggesting its dominant role on BV. At  $w_n = 2 \mu m$ , the excessive n-type charge moves the peak E-field to the NiO/GaN vertical sidewall at the top SJ region (Fig. 4(d)), as the impact of the global SJ charge imbalance becomes dominant. This can explain the BV's strong sensitivity on charge imbalance at  $w_n > 1.5 \mu m$  [see Fig. 3(b)].

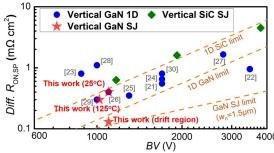

Fig. 5 compares the differential  $R_{\text{ON,SP}}$  versus BV trade-off of the vertical GaN SJ diode with the state-of-the-art vertical GaN 1D diodes [21]–[30] and SiC SJ devices [4]–[6], as well as the

Fig. 4. Simulated E-field contours in the SJ diodes with (a)  $w_n = 1.5 \mu m$ , (b) the same  $w_n$  and 2.5% higher  $N_A$ , (c)  $w_n = 1 \mu m$ , and (d)  $w_n = 2 \mu m$  at 1.1 kV.

Fig. 5. Differential  $R_{\rm ON,SP}$  versus BV trade-off of the vertical GaN SJ diode in comparison with vertical GaN diodes and SiC SJ devices. The high-temperature performance and drift-region resistance of our device are also marked. In the 1D limit, a critical E-field of 3 MV/cm and 2.5 MV/cm [31] and mobility of 1200 cm<sup>2</sup>/Vs and 800 cm<sup>2</sup>/Vs are used for GaN and SiC, respectively. The GaN SJ limit assumes a higher critical E-field of 3.3 MV/cm (due to higher doping) and a mobility of 600 cm<sup>2</sup>/Vs.

1D SiC/GaN limits and the GaN SJ limit  $[R_{on,sp} = 4w_nBV/(\varepsilon\mu_nE_c^2)]$ . The performance of our device is among the best in vertical GaN diodes with a similar BV. The device performance at 125 °C shows little degradation. The trade-off between BV and the drift region resistance is superior to the 1D GaN limit, fulfilling the theoretical promise of SJ devices in GaN. To fully exploit the SJ superiority, it is desirable to continue upscaling the BV as a) the SJ drift region will contribute an increasing percentage of device  $R_{\text{ON,SP}}$ , and b) the SJ theoretical limit will increasingly outperform the 1D limit.

### V. SUMMARY

We present the vertical GaN SJ diode fabricated by a novel self-aligned process to deposit NiO at the GaN pillar sidewalls. The device achieves a BV over 1 kV and  $R_{\rm ON,SP}$  of 0.4 m $\Omega$ ·cm², the trade-off of which is among the best in SJ devices. At 125 °C, BV maintains over 1 kV and  $R_{\rm ON,SP}$  drops to 0.3 m $\Omega$ ·cm². To date, such high temperature operation is reported in a hetero-SJ device for the first time. These results show the promise of GaN SJ power devices, and the self-signed process has the wide material and device applicability.

#### REFERENCES

- [1] F. Udrea, G. Deboy, and T. Fujihira, "Superjunction Power Devices, History, Development, and Future Prospects," *IEEE Trans. Electron Devices*, vol. 64, no. 3, pp. 713–727, Mar. 2017, doi: 10.1109/TED.2017.2658344.

- [2] Y. Zhang, F. Udrea, and H. Wang, "Multidimensional device architectures for efficient power electronics," *Nat. Electron.*, vol. 5, no. 11, Art. no. 11, Nov. 2022, doi: 10.1038/s41928-022-00860-5.

- [3] G. Deboy, N. Marz, J.-P. Stengl, H. Strack, J. Tihanyi, and H. Weber, "A new generation of high voltage MOSFETs breaks the limit line of silicon," in *International Electron Devices Meeting 1998. Technical Digest*, Dec. 1998, pp. 683–685. doi: 10.1109/IEDM.1998.746448.

- [4] X. Zhong, B. Wang, and K. Sheng, "Design and experimental demonstration of 1.35 kV SiC super junction Schottky diode," in 2016 28th International Symposium on Power Semiconductor Devices and ICs (ISPSD), Jun. 2016, pp. 231–234. doi: 10.1109/ISPSD.2016.7520820.

- [5] T. Masuda, Y. Saito, T. Kumazawa, T. Hatayama, and S. Harada, "0.63 mΩ·cm²/1170 V 4H-SiC Super Junction V-Groove Trench MOSFET," in 2018 IEEE International Electron Devices Meeting (IEDM), Dec. 2018, p. 8.1.1-8.1.4. doi: 10.1109/IEDM.2018.8614610.

- [6] R. Ghandi, C. Hitchcock, S. Kennerly, M. Torky, and T. P. Chow, "Scalable Ultrahigh Voltage SiC Superjunction Device Technologies for Power Electronics Applications," in 2022 International Electron Devices Meeting (IEDM), Dec. 2022, p. 9.1.1-9.1.4. doi: 10.1109/IEDM45625.2022.10019368.

- [7] J. Liu, M. Xiao, R. Zhang, S. Pidaparthi, H. Cui, A. Edwards, M. Craven, L. Baubutr, C. Drowley, and Y. Zhang, "1.2-kV Vertical GaN Fin-JFETs: High-Temperature Characteristics and Avalanche Capability," *IEEE Trans. Electron Devices*, vol. 68, no. 4, pp. 2025–2032, Apr. 2021, doi: 10.1109/TED.2021.3059192.

- [8] T. Kachi, T. Narita, H. Sakurai, M. Matys, K. Kataoka, K. Hirukawa, K. Sumida, M. Horita, N. Ikarashi, K. Sierakowski, M. Bockowski, and J. Suda, "Process engineering of GaN power devices via selective-area p-type doping with ion implantation and ultra-high-pressure annealing," *J. Appl. Phys.*, vol. 132, no. 13, p. 130901, Oct. 2022, doi: 10.1063/5.0107921.

- [9] H. Ishida, D. Shibata, M. Yanagihara, Y. Uemoto, H. Matsuo, T. Ueda, T. Tanaka, and D. Ueda, "Unlimited High Breakdown Voltage by Natural Super Junction of Polarized Semiconductor," *IEEE Electron Device Lett.*, vol. 29, no. 10, pp. 1087–1089, Oct. 2008, doi: 10.1109/LED.2008.2002753.

- [10] A. Nakajima, Y. Sumida, M. H. Dhyani, H. Kawai, and E. M. S. Narayanan, "GaN-Based Super Heterojunction Field Effect Transistors Using the Polarization Junction Concept," *IEEE Electron Device Lett.*, vol. 32, no. 4, pp. 542–544, Apr. 2011, doi: 10.1109/LED.2011.2105242.

- [11] M. Xiao, Y. Ma, K. Liu, K. Cheng, and Y. Zhang, "10 kV, 39 mΩ·cm2 Multi-Channel AlGaN/GaN Schottky Barrier Diodes," *IEEE Electron Device Lett.*, vol. 42, no. 6, pp. 808–811, Jun. 2021, doi: 10.1109/LED.2021.3076802.

- [12] M. Xiao, Y. Ma, Z. Du, V. Pathirana, K. Cheng, A. Xie, E. Beam, Y. Cao, F. Udrea, H. Wang, and Y. Zhang, "Multi-Channel Monolithic-Cascode HEMT (MC2-HEMT): A New GaN Power Switch up to 10 kV," in 2021 IEEE International Electron Devices Meeting (IEDM), Dec. 2021, p. 5.5.1-5.5.4. doi: 10.1109/IEDM19574.2021.9720714.

- [13] S.-W. Han, J. Song, M. Sadek, A. Molina, M. A. Ebrish, S. E. Mohney, T. J. Anderson, and R. Chu, "12.5 kV GaN Super-Heterojunction Schottky Barrier Diodes," *IEEE Trans. Electron Devices*, vol. 68, no. 11, pp. 5736–5741, Nov. 2021, doi: 10.1109/TED.2021.3111543.

- [14] J. A. Spencer, A. L. Mock, A. G. Jacobs, M. Schubert, Y. Zhang, and M. J. Tadjer, "A review of band structure and material properties of transparent conducting and semiconducting oxides: Ga2O3, Al2O3, In2O3, ZnO, SnO2, CdO, NiO, CuO, and Sc2O3," Appl. Phys. Rev., vol. 9, no. 1, p. 011315, Mar. 2022, doi: 10.1063/5.0078037.

- [15] M. Xiao, Y. Ma, Z. Du, X. Yan, R. Zhang, K. Cheng, K. Liu, A. Xie, E. Beam, Y. Cao, H. Wang, and Y. Zhang, "5 kV Multi-Channel AlGaN/GaN Power Schottky Barrier Diodes with Junction-Fin-Anode," in 2020 IEEE International Electron Devices Meeting (IEDM), Dec. 2020, p. 5.4.1-5.4.4. doi: 10.1109/IEDM13553.2020.9372025.

- [16] M. Xiao, Y. Ma, Z. Du, Y. Qin, K. Liu, K. Cheng, F. Udrea, A. Xie, E. Beam, B. Wang, J. Spencer, M. Tadjer, T. Anderson, H. Wang, and Y. Zhang, "First Demonstration of Vertical Superjunction Diode in GaN,"

- in 2022 International Electron Devices Meeting (IEDM), Dec. 2022, p. 35.6.1-35.6.4. doi: 10.1109/IEDM45625.2022.10019405.

- [17] Y. Qin, M. Xiao, M. Porter, Y. Ma, J. Spencer, Z. Du, A. G. Jacobs, K. Sasaki, H. Wang, M. Tadjer, and Y. Zhang, "10-kV Ga2O3 Charge-Balance Schottky Rectifier Operational at 200 °C," *IEEE Electron Device Lett.*, vol. 44, no. 8, pp. 1268–1271, Aug. 2023, doi: 10.1109/LED.2023.3287887.

- [18] Y. Zhang, M. Sun, Z. Liu, D. Piedra, J. Hu, X. Gao, and T. Palacios, "Trench formation and corner rounding in vertical GaN power devices," *Appl. Phys. Lett.*, vol. 110, no. 19, p. 193506, May 2017, doi: 10.1063/1.4983558.

- [19] Y. Zhang, M. Sun, D. Piedra, J. Hu, Z. Liu, Y. Lin, X. Gao, K. Shepard, and T. Palacios, "1200 V GaN vertical fin power field-effect transistors," in 2017 IEEE International Electron Devices Meeting (IEDM), Dec. 2017, p. 9.2.1-9.2.4. doi: 10.1109/IEDM.2017.8268357.

- [20] J. Liu, R. Zhang, M. Xiao, S. Pidaparthi, H. Cui, A. Edwards, L. Baubutr, C. Drowley, and Y. Zhang, "Surge Current and Avalanche Ruggedness of 1.2-kV Vertical GaN p-n Diodes," *IEEE Trans. Power Electron.*, vol. 36, no. 10, pp. 10959–10964, Oct. 2021, doi: 10.1109/TPEL.2021.3067019.

- [21] K. Nomoto, B. Song, Z. Hu, M. Zhu, M. Qi, N. Kaneda, T. Mishima, T. Nakamura, D. Jena, and H. G. Xing, "1.7-kV and 0.55- GaN p-n Diodes on Bulk GaN Substrates With Avalanche Capability," *IEEE Electron Device Lett.*, vol. 37, no. 2, pp. 161–164, Feb. 2016, doi: 10.1109/LED.2015.2506638.

- [22] K. Nomoto, Z. Hu, B. Song, M. Zhu, M. Qi, R. Yan, V. Protasenko, E. Imhoff, J. Kuo, N. Kaneda, T. Mishima, T. Nakamura, D. Jena, and H. G. Xing, "GaN-on-GaN p-n power diodes with 3.48 kV and 0.95 mΩ·cm2: A record high figure-of-merit of 12.8 GW/cm2," in 2015 IEEE International Electron Devices Meeting (IEDM), Dec. 2015, p. 9.7.1-9.7.4. doi: 10.1109/IEDM.2015.7409665.

- [23] H. Fukushima, S. Usami, M. Ogura, Y. Ando, A. Tanaka, M. Deki, M. Kushimoto, S. Nitta, Y. Honda, and H. Amano, "Vertical GaN p-n diode with deeply etched mesa and the capability of avalanche breakdown," *Appl. Phys. Express*, vol. 12, no. 2, p. 026502, Feb. 2019, doi: 10.7567/1882-0786/aafdb9.

- [24] H. Fu, K. Fu, S. R. Alugubelli, C.-Y. Cheng, X. Huang, H. Chen, T.-H. Yang, C. Yang, J. Zhou, J. Montes, X. Deng, X. Qi, S. M. Goodnick, F. A. Ponce, and Y. Zhao, "High Voltage Vertical GaN p-n Diodes With Hydrogen-Plasma Based Guard Rings," *IEEE Electron Device Lett.*, vol. 41, no. 1, pp. 127–130, Jan. 2020, doi: 10.1109/LED.2019.2954123.

- [25] J. Wang, R. McCarthy, C. Youtsey, R. Reddy, J. Xie, E. Beam, L. Guido, L. Cao, and P. Fay, "High-Voltage Vertical GaN p-n Diodes by Epitaxial Liftoff From Bulk GaN Substrates," *IEEE Electron Device Lett.*, vol. 39, no. 11, pp. 1716–1719, Nov. 2018, doi: 10.1109/LED.2018.2868560.

- [26] Y. Hatakeyama, K. Nomoto, N. Kaneda, T. Kawano, T. Mishima, and T. Nakamura, "Over 3.0 Figure-of-Merit GaN p-n Junction Diodes on Free-Standing GaN Substrates," *IEEE Electron Device Lett.*, vol. 32, no. 12, pp. 1674–1676, Dec. 2011, doi: 10.1109/LED.2011.2167125.

- [27] Z. Bian, K. Zeng, and S. Chowdhury, "2.8 kV Avalanche in Vertical GaN PN Diode Utilizing Field Plate on Hydrogen Passivated P-Layer," *IEEE Electron Device Lett.*, vol. 43, no. 4, pp. 596–599, Apr. 2022, doi: 10.1109/LED.2022.3149748.

- [28] Y. Qin, M. Xiao, R. Zhang, Q. Xie, T. Palacios, B. Wang, Y. Ma, I. Kravchenko, D. P. Briggs, D. K. Hensley, B. R. Srijanto, and Y. Zhang, "1 kV GaN-on-Si Quasi-Vertical Schottky Rectifier," *IEEE Electron Device Lett.*, vol. 44, no. 7, pp. 1052–1055, Jul. 2023, doi: 10.1109/LED.2023.3282025.

- [29] E. Farzana, J. Wang, M. Monavarian, T. Itoh, K. S. Qwah, Z. J. Biegler, K. F. Jorgensen, and J. S. Speck, "Over 1 kV Vertical GaN-on-GaN p-n Diodes With Low On-Resistance Using Ammonia Molecular Beam Epitaxy," *IEEE Electron Device Lett.*, vol. 41, no. 12, pp. 1806–1809, Dec. 2020, doi: 10.1109/LED.2020.3032387.

- [30] M. Xiao, Y. Wang, R. Zhang, Q. Song, M. Porter, E. Carlson, K. Cheng, K. Ngo, and Y. Zhang, "Robust Avalanche in 1.7 kV Vertical GaN Diodes with a Single-Implant Bevel Edge Termination," *IEEE Electron Device Lett.*, vol. 44, no. 10, pp. 1616–1619, Oct. 2023, doi: 10.1109/LED.2023.3302312.

- [31] J. A. Cooper, and D. T. Morisette, "Performance Limits of Vertical Unipolar Power Devices in GaN and 4H-SiC," *IEEE Electron Device Lett.*, vol. 41, no. 6, pp. 892-895, Jun. 2020, doi: 10.1109/LED.2020.2987282.