# Survey of Machine Learning for Software-assisted Hardware Design Verification: Past, Present, and Prospect

NAN WU, George Washington University, USA

YINGJIE LI, University of Maryland, USA

HANG YANG, Georgia Institute of Technology, USA

HANQIU CHEN, Georgia Institute of Technology, USA

STEVE DAI, NVIDIA Corporation, USA

CONG HAO, Georgia Institute of Technology, USA

CUNXI YU, University of Maryland, USA

YUAN XIE, Hong Kong University of Science and Technology, China

With the ever-increasing hardware design complexity comes the realization that efforts required for hardware verification increase at an even faster rate. Driven by the push from the desired verification productivity boost and the pull from leap-ahead capabilities of machine learning (ML), recent years have witnessed the emergence of exploiting ML-based techniques to improve the efficiency of hardware verification. In this paper, we present a panoramic view of how ML-based techniques are embraced in hardware design verification, from formal verification to simulation-based verification, from academia to industry, and from current progress to future prospects. We envision that the adoption of ML-based techniques will pave the road for more scalable, more intelligent, and more productive hardware verification.

Additional Key Words and Phrases: hardware verification, machine learning, formal verification, simulation-based verification

## ACM Reference Format:

Nan Wu, Yingjie Li, Hang Yang, Hanqiu Chen, Steve Dai, Cong Hao, Cunxi Yu, and Yuan Xie. 2024. Survey of Machine Learning for Software-assisted Hardware Design Verification: Past, Present, and Prospect. *ACM Trans. Des. Autom. Electron. Syst.* 1, 1 (July 2024), 42 pages. <https://doi.org/XXXXXX.XXXXXXX>

## 1 INTRODUCTION

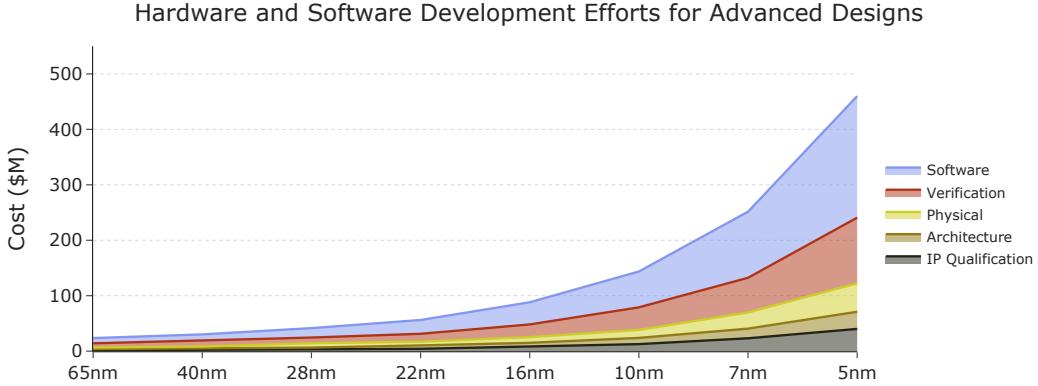

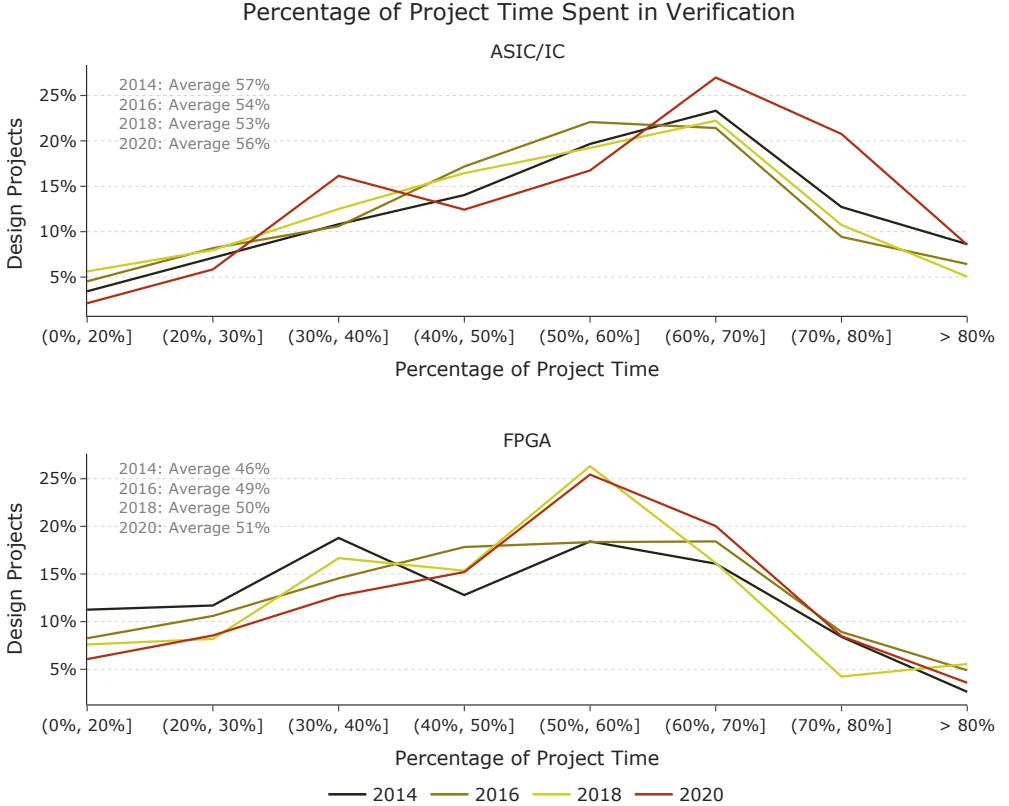

Hardware verification is at least comparably important with hardware design, if not more, in terms of labor, costs [191, 217], and project time [93] consumed in chip development cycles: the number of average engineers required for verification is commensurate with that of design [93]; Figure 1 shows the development efforts for advanced circuit designs, where verification roughly occupies half of the cost for hardware development; Figure 2 illustrates that verification obviously dominates the project time. With the growing complexity in design and verification, nearly 70% of application-specific integrated circuit (ASIC) or field-programmable gate array (FPGA) projects are completed behind schedule [93]. This indication is appealing for innovations in not only design but also verification.

Machine learning (ML) has demonstrated its versatility in hardware design optimization and evaluation [267]. This brings up one key question: **whether ML-based techniques can improve**

---

Authors' addresses: Nan Wu, Department of Electrical and Computer Engineering, George Washington University, Washington, District of Columbia, 20052, USA, nan.wu@gwu.edu; Yingjie Li, Department of Electrical and Computer Engineering, University of Maryland, College Park, Maryland, 20740, USA, yingjiel@umd.edu; Hang Yang, School of Electrical and Computer Engineering, Georgia Institute of Technology, Atlanta, Georgia, 30332, USA, hyang628@gatech.edu; Hanqiu Chen, School of Electrical and Computer Engineering, Georgia Institute of Technology, Atlanta, Georgia, 30332, USA, hchen799@gatech.edu; Steve Dai, 2701 San Tomas Expressway, NVIDIA Corporation, Santa Clara, California, 95050, USA, sdai@nvidia.com; Cong Hao, School of Electrical and Computer Engineering, Georgia Institute of Technology, Atlanta, Georgia, 30332, USA, callie.hao@ece.gatech.edu; Cunxi Yu, Department of Electrical and Computer Engineering, University of Maryland, College Park, Maryland, 20740, USA, cunxiyu@umd.edu; Yuan Xie, Department of Electrical and Computer Engineering, Hong Kong University of Science and Technology, Hong Kong, China, yuanxie@ust.hk.

Fig. 1. Development efforts for advanced designs under different technology nodes, which is redrawn based on data from Cadence [217].

**the quality and productivity of hardware design verification?** Hardware verification technologies can be roughly classified into two categories: hardware-assisted and software-assisted. The former includes emulation and prototyping, and the latter encompasses formal verification and oracle-based verification. Hardware-assisted verification has been gaining an expanding market share [141], especially advantageous for large-scale hardware designs. Despite its growth, the application of ML-based techniques in hardware-assisted verification is still in its early stages, with limited research studies available. For example, Siemens EDA employs ML to analyze the knowledge database built from previous compilations and emulation runs, making the hardware emulator smarter and more cost-effective over time [213]. To improve the compilation flow of multi-FPGA-based emulation systems, ML models can be applied to predict whether a netlist is easy or hard to compile, identify effective compilation strategies, estimate compilation time, and offer recommendations for modifying hard-to-compile netlist partitions into easier ones [6]; evaluation on a large-scale industry system-on-chip design demonstrates that the ML-based recommendation flow achieves an additional 15% reduction in compilation time. It is highly expected that more endeavors will be made in the future to leverage ML to enhance hardware-assisted verification. In light of the wealth of research integrating ML with software-assisted verification, our emphasis in this survey is on exploring how ML complements software-assisted design verification, specifically within the realms of formal and oracle-based verification.

**Formal verification** uses static analysis to mathematically prove or disprove the functional correctness of a system with respect to certain formal specifications or properties [220]. Several popular formal methods include the Boolean satisfiability (SAT) problem and equivalence checking. As the SAT problem is NP-complete [66] and equivalence checking is coNP-complete [113], they become computationally impractical with complex systems or hardware designs. **Oracle-based verification** exercises the designs with valid input stimulus to compare whether the outputs match the oracle provided by a golden reference model [40]. Different coverage metrics are defined to assess if the design-under-verification (DUV) or design-under-test (DUT) has been adequately examined. Though oracle-based verification has been the major technique for hardware verification, it still suffers from the scalability issue caused by the growing design size and more complex system-level integration; the tremendous amount of data generated during simulation further complicates the problem. These challenges all call for more productive verification by incorporating more intelligence. Driven by both the push from the desired verification productivity boost and the

Fig. 2. Percentage of ASIC/IC and FPGA project time spent in verification, which is redrawn based on data from the 2020 Wilson Research Group Functional Verification Study [93]. Similar trends are observed in the study in 2022 [93]. Note that verification time dominates project time on average.

pull from leap-ahead capabilities of ML-based techniques, **this question has a positive answer**, as follows.

- In formal verification:

- graph-based learning approaches are naturally suitable to improve the efficiency of SAT solvers, since Boolean formulas can be represented as graphs;

- the natural language processing (NLP)-based techniques largely benefit assertion generation across natural languages, verification languages, and hardware description languages;

- various types of classifiers enable efficient identification of equivalence across different levels of abstractions, facilitate fast generation and verification of properties, and aid in selecting the optimal premises and heuristics used in theorem proving as well as the most suitable formal engine for diverse verification problems.

- In oracle-based verification:

- fast and accurate ML-based predictive models can significantly reduce the long simulation time of DUTs and simplify exhaustive coverage analysis;

- ML-based optimizers are capable to eliminate the long search time for stressful and comprehensive test sets and accelerate coverage closure;

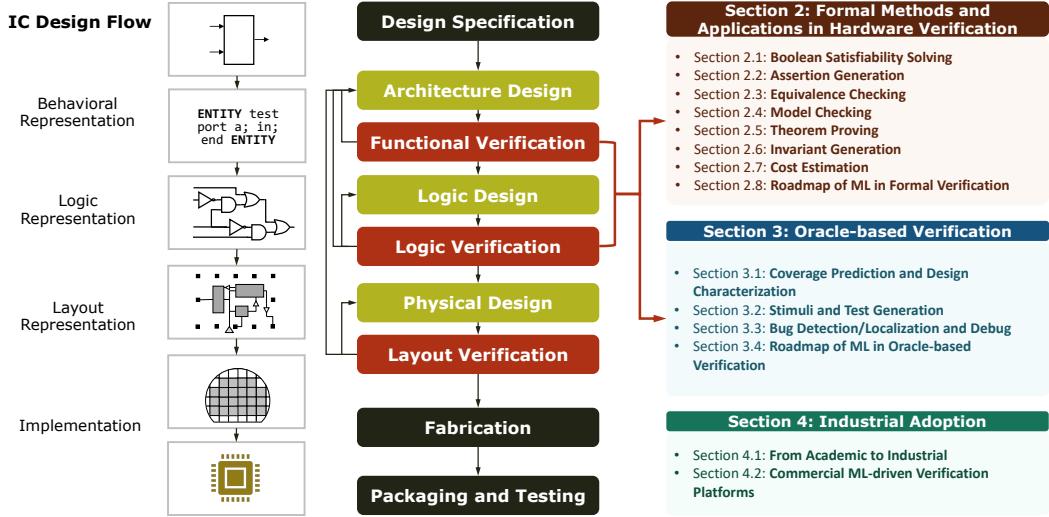

Fig. 3. Overall organization of this paper. Note that hardware verification is an indispensable step to guarantee desired functionalities.

- various clustering and classification methods enable the automation of bug detection, localization, and debug from a tremendous amount of failure information, which is nearly impossible for human engineers to well parse..

While there exist several short surveys about ML applications in hardware verification [70, 145, 251], they mostly focus on simulation-based verification, which is insufficient in practice, and provide detailed discussions on a few case studies, lacking a panorama of both static and dynamic verification, both academia and industry, and both current progress and future prospects. In this paper, we present a comprehensive overview of ML for hardware verification. From the static perspective (Section 2), we first briefly introduce the mainstream formal methods and their applications in hardware verification; then we summarize the problems in formal verification that can be solved by ML techniques, the common ML techniques adopted to resolve each of them, and the reason why ML techniques are powerful in these scenarios. From the dynamic perspective (Section 3), we review studies associated with three major steps in oracle-based verification: coverage analysis, test generation, and debug; we further discuss the role that ML techniques play, either a predictive model, an optimizer, or a combination of these two. We also provide a future vision of challenges, opportunities, and prospects of applying ML for hardware verification, aiming to pave the road for integrating more intelligence into next-generation verification (Section 2.8 and Section 3.4). In addition to attention to academic studies, we conduct sketchy discussions on how ML techniques are embraced in industrial productions or commercial verification tools (Section 4).

## 2 FORMAL METHODS AND APPLICATIONS IN HARDWARE VERIFICATION

The use of formal approaches in hardware verification is widespread. Contrary to testing-based verification approaches, formal verification makes use of rigorous formal methods and representations to formulate the specification and verification objectives of systems and to determine, without the need for extensive testing, whether the finalized design satisfies the specification at all properties [154]. To be more precise, formal approaches in hardware verification cover a wide range of specifications, from high-level specifications (such as SystemC, behavior HDL) to low-level

logic or physical representations (e.g., netlists). Depending on the nature of the design specification representation and its functionality, the requirements could be shown as block diagrams, look-up tables, or temporal logic. While there are a large variety of hardware formal verification problems, the fundamentals are to model the design properties and hardware implementation into rigorous mathematical representations and to obtain the verification objectives using desired verification techniques and solving mechanisms. In particular for hardware verification, the majority of the verification problems are formulated and solved with model checking [61], equivalence checking [159, 249], assertion-based formal verification [92, 97], and theorem proving [21, 74, 167]. To prove the mathematical models introduced by such verification techniques, solving mechanisms based on *canonical diagrams* [38, 39], *Boolean satisfiability* (SAT) [28, 175, 183], *Satisfiability Modulo Theories* (SMT) [22, 29, 75, 184], theorem proving, *computer algebra* [58, 59, 69, 173, 212, 273], etc., have been designed to prove or disprove with counterexamples. Even though formal verification can complement and eliminate extensive simulation or testing processes by rigorous mathematical reasoning, their scalability in practical verification problems has been the biggest challenge due to its runtime complexity and/or memory usage [96]. Hence, there have been increasing efforts in harnessing ML techniques to improve the scalability and reduce the runtime of different formal verification categories from various aspects. This section reviews the recent progress in SAT solving (Section 2.1), assertion-based formal verification (Section 2.2), equivalence checking (Section 2.3), model checking (Section 2.4), theorem proving (Section 2.5), invariant generation (Section 2.6), and runtime prediction and optimization (Section 2.7).

## 2.1 Boolean Satisfiability Solving

The SAT problem (i.e., Boolean satisfiability problem) is a decision problem: given a Boolean propositional formula, if there exists at least one valuation making the formula true, this formula is claimed to be satisfiable (SAT); otherwise, this formula is unsatisfiable (UNSAT). Boolean formulas are usually represented in the Conjunctive Normal Form (CNF): a formula is expressed as a conjunction ( $\wedge$ ) of clauses; a clause is expressed as a disjunction ( $\vee$ ) of literals that can be either a variable or its negation ( $\neg$ ).

Many practical problems can be reduced to the SAT problem, a proven NP-complete problem [66]. Given its broad applications, there has been consistent research attention on this hard combinatorial problem, and one promising direction is employing ML-based techniques to advance combinatorial optimization [24]. Targeting the SAT problem, ML-based techniques can be adopted to **1 build classifiers that provide fast SAT/UNSAT decisions based on input formulas** [15, 41, 81, 198, 222, 224], or **2 improve bottleneck components in existing SAT solvers** [163, 221, 265, 272, 276], such as Conflict-Driven Clause Learning (CDCL) solvers and Stochastic Local Search (SLS) solvers. For more reference, there is a comprehensive survey of ML for SAT solving [121].

**Classification for fast SAT/UNSAT decisions.** The SAT problem can be formulated as a binary classification based on input Boolean formulas. A Boolean formula in CNF can be represented as a bipartite graph, referred to as a literal-clause incidence graph (LIG), which contains nodes for each clause and each literal in the formula as well as edges connecting a clause node and a literal node if the clause contains this literal. When the literal nodes of the same variable in a LIG are connected, it is defined as  $\text{LIG}^+$ . The LIG-based representation makes it natural to exploit graph neural networks (GNNs) to classify satisfiability [41]. For example, NeuroSAT [222] consists of two parts: an encoder with a customized GNN that takes in the  $\text{LIG}^+$  representation of a formula and outputs an embedding for each literal, and an aggregator that maps each literal embedding to a scalar vote and aggregates them into the final prediction of satisfiability. NeuroSAT reaches an accuracy of 85% when evaluating on a synthetic random SAT generator with 40 variables per instance. Following NeuroSAT, Shi et al. [224] employs the transformer architecture to realize parallel speedup, which uses self-attention

Table 1. Formal verification with ML-based techniques. Both formal methods (SAT solving, assertion generation, equivalence checking, model checking, theorem proving, and invariant generation) and cost estimation can be improved by different ML-based techniques. S, U, and R stand for supervised, unsupervised, and reinforcement learning, respectively.

| Formal Method                                         | Problem Formulation                               | FWK              | ML Model/Technique                                                                            |

|-------------------------------------------------------|---------------------------------------------------|------------------|-----------------------------------------------------------------------------------------------|

| Boolean<br>Satisfiability<br>Solving<br>(Section 2.1) | Binary classification for satisfiability          | S<br>S<br>S      | GNN [222]<br>Transformer [224]<br>GNN + Contrast learning [81]                                |

|                                                       | Generating satisfiable assignments                | U<br>U           | Deep-gated recursive GNN [15]<br>Recurrent GNN [198]                                          |

|                                                       | Improving branching heuristics in CDCL            | S<br>R           | GNN [221]<br>DQN + GNN [163]                                                                  |

| Assertion<br>Generation<br>(Section 2.2)              | Improving variable initialization in CDCL         | S                | Logistic regression [265]                                                                     |

|                                                       | Improving variable selection in SLS               | R                | REINFORCE + GNN [272]                                                                         |

|                                                       | Improving variable initialization in SLS          | S                | GGCN [276]                                                                                    |

| Assertion<br>Generation<br>(Section 2.2)              | RTL + simulation trace $\rightarrow$ assertion    | S<br>S           | Binary decision tree [166, 223, 254]<br>Breadth-first decision tree [126]                     |

|                                                       | NL $\rightarrow$ SAL                              | U                | NLP [108]                                                                                     |

|                                                       | NL $\rightarrow$ SVA                              | U<br>S<br>S      | E-GRIDS [127], constituency tree [199]<br>Transformer [50]<br>GPT-3 [5]                       |

|                                                       | NL $\rightarrow$ RTL + UVM, SVA $\rightarrow$ NL  | S                | LSTM + machine translation [118]                                                              |

| Equivalence<br>Checking<br>(Section 2.3)              | System-level modeling & RTL equivalence           | S                | SVM [134, 135]                                                                                |

|                                                       | RTL & Gate-level signal correlation               | S                | Decision tree [13]                                                                            |

| Model Checking<br>(Section 2.4)                       | Boolean functions & hardware implementation       | U                | RNN [232]                                                                                     |

|                                                       | Generating properties                             | R                | GAN with RNN+CNN [102]                                                                        |

|                                                       | Directly verifying properties by classification   | S<br>S           | Boosted tree, random forest, decision tree,<br>and logistic regression [278]<br>GNN [185]     |

|                                                       | Finding counter-examples                          | R                | Q-learning [17, 23, 269]                                                                      |

| Theorem<br>Proving<br>(Section 2.5)                   | Refining abstraction based on counter-examples    | S                | Decision tree [60, 62]                                                                        |

|                                                       | Premise selection                                 | S<br>S<br>U<br>U | Naive Bayes/kernel-based learning [98, 151]<br>CNN, RNN [143]<br>Transformer [18]<br>GNN [91] |

|                                                       | Heuristic configuration adaptation                | S<br>S           | Gradient-based methods [98]<br>Gaussian-kernel-based regression [160]                         |

|                                                       | Heuristic selection                               | S                | Kernel-based learning [36, 37]                                                                |

| Invariant Generation<br>(Section 2.6)                 | Autoformalization                                 | S + R<br>S       | Imitation learning, REINFORCE, and GAN [263]<br>LLM [268]                                     |

|                                                       | Generating numerical and quantified invariants    | S                | Decision tree [103, 104]                                                                      |

|                                                       | Generating loop invariants                        | R                | GNN, LSTM, and policy gradient [228]                                                          |

| Cost Estimation<br>(Section 2.7)                      | Runtime estimation for formal verification        | S                | Linear regression [84]                                                                        |

|                                                       | Formal engine selection for verification problems | S                | Decision tree [85]                                                                            |

|                                                       | Time and memory usage                             | S                | MLP [247]                                                                                     |

and cross-attention to capture interactions among homogeneous and heterogeneous nodes in LIG-based representations, respectively. To relax the requirement of labeling a large number of SAT instances in supervised models, Duan *et al.* [81] combine label-preserving augmentations with contrast learning, which achieves comparable prediction accuracy to NeuroSAT with 100 $\times$  reduction in the number of required labels. Aiming to solve the SAT problem by directly generating a solution, Amizadeh *et al.* [15] propose a differentiable framework mimicking reinforcement learning (RL), which consists of a solver network and an evaluator network: the solver network, with the deep-gated recursive GNN structure, takes in Boolean circuits represented in directed acyclic graphs (DAGs) and directly generates an assignment of input variables; the evaluator

network evaluates whether the predicted assignment is SAT; the optimization goal is to push the solver network to generate an assignment that yields a higher satisfiability value in the evaluator network. QuerySAT [198] adopts recurrent GNNs with a query mechanism; for each query of a variable assignment, a differentiable unsupervised loss function is designed by relaxing input variables from discrete to continuous values, which can be directly optimized toward finding a satisfying assignment.

Even though ML-based techniques can make fast decisions of SAT/UNSAT, they are approximating the heuristics employed in conventional SAT solvers by stochastic NN models, without a theoretical guarantee of correctness. Thus, these ML-assisted SAT decisions are expected to quickly filter out obviously UNSAT solutions at early search stages instead of completely replacing conventional SAT solvers. In addition, several studies introduce unsupervised techniques to get rid of the efforts of labeling data, however, it requires high expertise to craft their differentiable loss functions [81, 198]. So, there is a trade-off between labeling efforts and required expertise in loss functions, suggesting the adoption of semi-supervised techniques in future work.

**Improving conventional SAT solvers.** For CDCL-based solvers, NeuroCore [221] incorporates a simplified NeuroSAT [222] into several high-performance SAT solvers that use the Exponential Variable State-Independent Decaying Sum (EVSIDS) as the branching heuristic [183], which maintains activity scores for every variable and branches on the free variable with the highest score. The goal is to complement the branching heuristics used in existing solvers by periodically querying NeuroSAT and resetting the variable activity scores according to NeuroSAT’s predictions of how likely the variables appear in an unsatisfiable core. Graph-Q-SAT [163] exploits deep Q-network (DQN) to improve the branching heuristic in CDCL-based solvers. The SAT formula is represented in a LIG, and the DQN agent equipped with a GNN decides whether to set each unassigned variable as true or false. Wu [265] focuses on finding the preferred initial value of each Boolean variable in a CDCL-based solver, where a logistic regression model is employed to predict SAT/UNSAT of Boolean formulas after fixing the values of certain variables.

For SLS-based solvers, Yolcu and Póczos [272] incorporate GNNs with REINFORCE to act as the variable selection heuristic. The GNN takes in LIG-based representations of Boolean formulas together with an assignment to all variables, and outputs a probability vector of flipping the value of each variable. NLocalSAT [276] uses a gated graph convolutional network (GGCN) to directly predict solutions to SAT instances based on LIG-represented formulas, providing guidance to the variable initialization heuristics.

Integrating ML-based techniques with conventional SAT solvers is a conservative yet more feasible way. Despite the performance boost in the solvers, one thing worth noting is the employment of ML models may introduce new sources of biases [180]. For instance, a common issue is the significant imbalance in data samples from SAT and UNSAT categories, potentially leading to sampling bias; even with representative data, human experts perform feature engineering and ML model selection, such as certain optimization objectives, regularizations, and constraints, based on their understanding of the nature of verification problems, which may include flawed or stale information that can bias the outcome of ML algorithms.

## 2.2 Assertion Generation

In formal verification, assertions are used to express desirable properties to be proven by formal methods and to define constraints in the verification environment for DUTs. The effectiveness and completeness of formal verification rely heavily on the generated assertions, however, assertion generation requires heavy manual efforts, such as multiple iterations and man-months, to achieve the minimal but effective assertions with high coverage [97]. This motivates automatic assertion generation using ML techniques. In general, assertions can be generated from two major sources: ①

**design-related information, such as RTL designs and simulation traces** [126, 166, 223, 254], and **2 design specification documents in natural languages** [5, 50, 108, 118, 127, 199].

**Generation from design-related information.** RTL designs and their simulation traces are good sources to generate hardware assertions using data mining techniques. GoldMine [254] is a methodology to automatically generate RTL assertions using data mining and static analysis. It consists of five major components: (1) data generator, which simulates RTL designs with random vectors to produce dynamic behavioral data; (2) lightweight static analyzer that extracts domain-specific information about the design; (3) A-miner that derives knowledge and information from simulation traces and design constraints, where a binary decision tree is employed to produce a set of ranked candidate assertions; (4) formal verifier, which verifies the candidate assertions produced by A-miner to filter out spurious assertions and retain system invariants; (5) A-Val, which compares the machine-generated assertions to those generated by a human and provides feedback to refine GoldMine accordingly. To achieve a higher coverage and generate more succinct assertions, Sheridan et al. [223] improve GoldMine by proposing a coverage-guided assertion miner with a combination of association rule learning and greedy set covering. Based on the GoldMine framework that generates bit-level assertions, Liu et al. [166] enhance the quality of assertion mining by generating word-level assertions that have higher expressiveness and readability than their counterparts in the bit-level. Hanafy et al. [126] extend the binary decision tree adopted in GoldMine to a breadth-first decision tree for assertion generation and refinement.

**Generation from design specification documents.** Hardware assertions can be directly extracted from design specification documents by translation from natural languages (NL) to assertion languages. ARSENAL [108] automatically translates NL requirements into a unified symbolic analysis laboratory (SAL) model with associated properties, through two stages: the NLP stage that extracts relations from texts using semantic parsing and interprets NL sentences to logical formulas, and the formal methods stage that converts the generated logical formulas to a SAL-based formal model. GLAst [127] transforms specification sentences in English to formal SystemVerilog assertions (SVA) by extending the E-GRIDS algorithm [204], which creates a custom formal grammar to capture the writing style and sentence structures of specifications to facilitate the automatic translation. With a similar goal, SpecToSVA [199] employs a random forest classifier to decide which sentence in specifications should be translated, an NLP package, spaCy [129], to detect name entity recognition, and a constituency tree with a self-attentive encoder [155] for final translation from design specifications in English to SVA. The evaluation shows an average precision of 64% on a dataset created from proprietary IC specification documents. Notably, SpecToSVA can only translate single and self-contained sentences to SVA, and cannot handle cases where multiple sentences need to be collectively considered and translated into a single SVA expression. Gulliya et al. [118] give attention to the conversion between English and SVA in register verification: from English to SVA, a long short-term memory (LSTM)-based model is trained to classify the type and functionality of different registers, and the prediction results are processed to generate proper RTL and universal verification methodology (UVM) code; from SVA to English, rule-based machine translation is employed. Recently, Transformer-based models, which are the state-of-the-art models of NLP, outperform conventional one-step attention RNNs in machine translation from English to SVA [50]. Though DAVE, a fine-tuned GPT-2 (the second generation Generative Pre-trained Transformer) model, majorly aims to automatically translate NL into Verilog snippets [202], it considers the assertion generation as the future work. Aditi et al. [5] propose a hybrid approach that utilizes GPT-3 to extract the entity information from specification sentences, after which a set of hand-crafted rules is applied for the final translation. This approach successfully generates SVAs for 1712 out of the 2000 statements (~85% success rate).

Automatic assertion generation enabled by ML-based techniques largely benefits verification productivity. The process of identifying assertions from either design itself or specification documents is analogous to neural machine translation, revealing numerous opportunities, especially in the era of large language models (LLMs). Though these ML-based models may not always generate non-trivial assertions, they can offer potential candidates that can be easily refined by human experts [5, 50].

### 2.3 Equivalence Checking

Equivalence checking guarantees design integrity by using mathematical modeling techniques to show that two representations from different design levels of the DUT exhibit the same behaviors. Practically, fast and accurate equivalence checking saves significant time and effort in engineering change order (ECO). With the help of ML-based techniques, the features and embeddings from one design level can be well captured and accurately mapped to another design level, greatly accelerating equivalence checking. For cross-design-level translations, we discuss the equivalence checking ① **from system-level to RTL** [134, 135], ② **from RTL to gate-level**, and ③ **from Boolean functions to hardware implementation** [232].

**System-level → RTL.** Modern hardware designs usually start with behavioral descriptions in high-level languages, such as C/C++ and SystemC, which are then compiled into RTL designs by synthesis tools or manual transformation. This translation step is time-consuming and error-prone. Thus, Hu et al. [135] employ support vector machine (SVM) to improve the efficiency of finite state machines with datapath (FSMD)-based equivalence checking between the system-level modeling (SLM) and its generated RTL design. Both SLM and RTL designs are converted into FSMD representations. The SVM model then learns from the SLM states to predict the corresponding RTL states, which helps identify the path pairs between SLM and RTL and drastically reduces the time complexity by avoiding arbitrary path selection. The selected path pairs will be further checked using symbolic simulation and the SMT solver. They also analyze multiple ML models to examine the trade-offs between effectiveness and efficiency [134].

**RTL → gate-level.** Designers usually optimize RTL designs for ECO, which can change the design hierarchy and transform signal names, making it hard to correlate RTL design signals with their counterparts in gate-level implementation [65]. Alhaddad et al. [13] explore seven ML models, including decision tree, random forest, K-nearest neighbors, linear support vector classification (SVC), linear regression, naive Bayes, and linear discriminant analysis, to identify each pair of signals from RTL and gate-level are equivalent or not, based on name features, structural features, signal proprieties, and functional similarity features. Evaluation on the OpenCores [195] benchmark shows that the decision tree outperforms other models, with the best accuracy of 89%.

**Boolean functions → hardware implementation.** Singireddy et al. [232] focus on the equivalence checking between flow-based computing systems in memristor crossbars and reference Boolean functions. The crossbar design is first recast into an RNN, which allows equivalence checking to be efficiently performed by NN inference, and then instances of Boolean variables are verified by passing input vectors to the RNN and checking the output against the reference Boolean function. Evaluation on circuits from the RevLib [264] and MCNC [271] suites show that the proposed method can verify the correctness of a design 166× faster than the state-of-the-art method based on graph reachability on average.

Despite the speedup achieved by ML-based techniques, there are several observations on existing approaches. First, feature engineering plays an important role in building effective ML models [13, 135]. However, this process can become cumbersome, particularly in scenarios involving large feature spaces. Second, the trained ML models seek to imitate the rules in equivalence checking,

aiming to provide rapid suggestions. Their full potential can be realized by integrating them with solvers that offer theoretical guarantees [13, 232].

## 2.4 Model Checking

Model checking involves abstracting the execution of a concrete system into a finite-state automaton and expressing the properties of interest by temporal logics. The procedure of model checking exhaustively explores the (abstract) state space, and either validates the properties or provides a counter-example. In practice, exhaustive exploration is challenging in face of the state explosion problem [63], which prompts the development of various techniques aiming at reducing the state space or enhancing its exploration through path exploration heuristics. We discuss how ML-based techniques contribute to **1 automatically generating properties** [102], **2 directly verifying properties** [185, 278], **3 finding counter-examples** [17, 23, 269], and **4 refining abstraction based on counter-examples** [60, 62].

**Generating properties.** To automate the laborious process of manually generating verification properties, Gao et al. [102] present a GAN-based property generation approach, which employs an LSTM-based model as the generator and a CNN-based classifier as the discriminator. Existing verification properties are represented as sequences of word vectors, serving as the initial inputs for the SeqGAN [274] algorithm to generate new verification properties. As this approach focuses on generating new verification properties using computational tree logic (CTL) formulas and/or Kripke structures, and given that hardware designs can be converted to Kripke structures and design specifications can be translated into CTL formulas, it is easily transferrable to hardware program property generation by adjusting the training data and corresponding labeling efforts.

**Directly verifying properties.** Linear temporal logic (LTL) model checking suffers from the state explosion problem and the exponentially growing compute complexity [63]. To alleviate these issues, several studies formulate LTL model checking as binary classification problems, in which 0/1 indicates the model (un)satisfies the specification. Zhu et al. [278] evaluate several ML algorithms (i.e., boosted tree, random forest, decision tree, and logistic regression) to predict whether an automaton satisfies a specification. While receiving comparable prediction accuracy to the classical LTL model checking tool, NuXmv [47], these algorithms exhibit limited generalization across different LTL formula lengths and automaton sizes. To achieve better generalization, GNN is adapted to encode the automaton with the target LTL formula expressed as node embeddings [185]. This graph classification method is capable of predicting results up to 17 $\times$  faster than the tool LTL3BA [19], especially when dealing with very large LTL formulas.

**Finding counter-examples.** Model checking tools should be geared towards efficient error detection [64]. Several studies improve the efficiency of finding counter-examples by using Q-learning to explicitly guide the exploration of paths in automaton that would violate properties of interest. For instance, Araragi and Mo Cho [17] give rewards to explorations leading to cycles or infinite paths between the premise and the response that invalidate the response property, which states that if a premise event occurs, a response event will be true thereafter. Behjati et al. [23] then extend the Q-learning algorithm to accommodate more LTLs. To enhance the search efficiency of Q-learning based approaches, neural Monte Carlo tree search (MCTS) is employed [269], which is capable to find counter-examples in less runtime. While Q-learning is effective in identifying counter-examples, it may face challenges due to high sensitivity in reward functions [239]. Hence, crafting meaningful rewards is crucial in these problems, especially in situations when it is challenging to build a clear relationship between the optimization goal and rewards.

**Refining abstraction based on counter-examples.** A counter-example can be spurious, if the last state of a path in the abstracted system model unites both deadend states (i.e. states without concrete transitions to failure states) and bad states (i.e., states with transitions to failure states) in

the actual system. This is because some system variables that are useful to prove the properties and distinguish these states are not considered in the system abstraction, suggesting a refinement in the abstracted system model by making these variables visible. To separate these states, Clarke et al. [60, 62] employ decision trees to classify whether system variables from the failure state should be visible.

## 2.5 Theorem Proving

In theorem proving, systems are described by appropriate mathematical logics, and important mathematical properties of the system are proved by theorem provers. Theorem provers check whether a conjecture, the target mathematical statement to be inferred, can be derived from a set of statements (e.g., axiom, hypothesis) and output the proof for the conjecture or a trace thereof. This is similar to computer algebra since both of them are used for symbolic computation, but with the advantages of more flexibility in logic expressiveness, clearer expression, and more rigor.

Theorem provers are essentially based on mathematical logics, and there is always a trade-off between automation and expressive power of logics [36]. For example, first-order logic (FOL) has high-level automation and is usually used to construct automated theorem provers (ATPs) [186]; higher-order logic (HOL) is more expressive and has the ability to prove complex problems, but requires more human guidance, which is often used to build interactive theorem provers (ITPs), e.g., Isabelle [30, 189], MIZAR [116], and Coq [26]. These theorem provers can be effectively applied for hardware design verification with light modifications. For example, Kami [55] is an extended library embedded in Coq, enabling expressive and modular reasoning for hardware designs, which has the capability to verify fairly realistic processors within Coq.

ML-based techniques have been successfully employed to aid theorem-proving systems in the following aspects: ① **the selection of facts (also known as premises)** that are most relevant for proving a new conjecture, which can be formulated as ML-based classification tasks [11, 18, 91, 143, 148, 151]; ② **automatic heuristic configuration and selection in ATPs**, where ML can help to model the relationship between input problems and the chosen heuristics [36, 37, 98, 160]; and ③ **autoformalization** [263, 268].

**Premise selection.** The premise selection task entails a conjecture and a set of facts/premises, with the objective of strategically choosing a subset of premises to be forwarded to an ATP. Alama et al. [11] employ naive Bayes and kernel-based learning methods to estimate which premises are likely to be useful for constructing a proof. To improve the scalability, Kaliszyk and Urban [151] adopt the sparse implementation of a multi-class naive Bayes classifier to rank available facts, where the top-ranked facts are selected to realize the proof. Irving et al. [143] simplify the subset selection of premises to computing pairwise relevance: two CNN/RNN sequence models are developed to compute the embeddings for a conjecture and a premise, respectively, which are then concatenated to produce the probability that this premise is useful for proving the conjecture.

Recent approaches convert logic statements into graphs and leverage graph representations to assist theorem provers. Aygun et al. [18] build a FOL prover by replacing all the clause-scoring heuristics of the state-of-the-art E prover [218, 219] with a Transformer-based clause scoring function. The Transformer-based model takes in clauses represented in graphs with spectral features and outputs the probability of a clause appearing in the proof, which is trained using hindsight experience replay in an incremental learning setting. The proposed approach can compete with the E prover in its best configuration. To further improve the transferability across domains using different vocabularies, NIAGRA [91] generates name invariant graph neural representations of clauses that provide more meaningful embeddings of non-logical symbols, such as predicates, functions, and constants. It also adopts the ensemble method that leverages different configurations

of the underlying ATP to learn proof guidance models. Evaluation shows that NIAGRA outperforms the method proposed by Aygun et al. [18] by 10%.

**Heuristic configuration adaptation and selection.** Heuristic configuration refers to a set of parameters in theorem provers that affect their preference on clause weighting and selection schemes, term orderings, and sets of inference and reduction rules used. Tuning such parameters is time-consuming and can be automated by different ML-based techniques. Fuchs [98] makes an early attempt to learn search-guiding heuristics from past experiences, where gradient-based methods are used to adapt coefficients in the heuristics to ensure application for a wider range of target problems. Kühlwein and Urban [160] propose an automatic framework to tune parameters inside ATPs. Given the parameter setting of an ATP and a target problem, a Gaussian-kernel-based method is adopted to predict its runtime, which enables more efficient adaptation of parameter settings for different problems. In addition to setting parameters in heuristics, Bridge et al. [36, 37] emphasize on selecting useful heuristics for proof search. Based on features of the conjecture to be proved and the associated axioms/facts, SVM and Gaussian-kernel-based methods are capable to select a beneficial set of heuristics. The developed ML-assisted system is also able to decline proof attempts, significantly reducing the time spent in proof with only a moderate reduction in the number of provable theorems.

ML-based techniques can greatly improve the scalability of premise selection and configuring heuristics, but a key consideration is the quality of these ML models often heavily depends on the available training data. Given the large search space of premises or configurations, it is highly probable that the collected training data implicitly incorporate the preference and domain knowledge from human experts. On the positive side, ML models can quickly imitate the behavior of human experts, while on the negative side, the learned solutions may be suboptimal and bounded by human perception. Possible solutions to address this concern involve combining techniques such as active learning, RL, or generative approaches with existing methods, which can generate new data points on-the-fly and potentially mitigate the limitations of relying solely on human-derived data.

**Autoformalization.** Autoformalization refers to the automatic translation from NL mathematics to formal specifications, theorems, and proofs. MetaGen [263] is a neural theorem generator, which synthesizes new theorems and their proofs expressed in the formalism in Metamath [179]. Two scenarios are considered: if both human-written theorem statements and their proofs are available, MetaGen is trained by imitation learning to provide human-like theorems; if only theorems are available, MetaGen uses the REINFORCE algorithm to find synthetic theorems similar to human-written theorems, where a discriminator, such as the one in generative adversarial networks (GAN) [114], is trained to measure the similarity. Wu et al. [268] observe that LLMs, such as OpenAI Codex [51, 193] and PaLM [57], can correctly translate a certain portion (25.3%) of mathematical competition problems in English to formal code used by the interactive proof assistant Isabelle [189]. The performance of a neural theorem prover, LISA [147], can be improved by training with these autoformalized theorems, reaching a new state-of-the-art proof rate from 29.6% to 35.2% on the MiniF2F [277] theorem proving benchmark. Though LLMs may not be able to generate perfect specifications or correct statements, they can produce slightly incorrect formal specifications and properties quickly, making it easier for hardware designers to iterate them efficiently.

## 2.6 Invariant Generation

Invariants, by capturing properties that remain unchanged during program execution, provide a foundation for reasoning about programs' behavior. Once appropriate inductive invariants are identified, the focus of program verification shifts to checking the validity of verification conditions

derived from finite loop-free paths extracted based on the invariants. This reduction in complexity is a key benefit of leveraging invariants in the verification process.

ML-based invariant generation excels in uncovering the implicit and intricate logic embedded within programs and target properties, with a moderate level of generalization to handle similar constraints and program structures. ICE-learning [103] (which stands for learning using implications, counter-examples, and examples) consists of two components in its framework: a teacher, which is a program verifier fully aware of the program and the property to be verified, and a learner, which is entirely agnostic of the program and property, aiming to generate invariants through interactions with the teacher. During each iteration, the teacher evaluates whether the current invariant is sufficient to prove a certain property and provides (counter-)examples accordingly; the learner refines the constructed invariant based on samples received from the teacher. In this abstraction, the learner can leverage any ML algorithm effective in generating Boolean functions. One example is to tailor a decision tree by developing new measures to determine the best attributes to branch current examples and implications [104]; the well-trained model will output a universal representation of Boolean functions composed of atomic formulas that are either inequalities bounding the numerical attributes by constants or Boolean attributes. To enhance the generalization capability across structurally similar programs, Code2Inv [228] utilizes a GNN to acquire neural representations of program structures. It frames the loop invariant generation as a deep RL problem: the learning agent, structured as an LSTM, accepts neural program representations as inputs and employs the policy gradient algorithm to execute a sequence of actions for generating a loop invariant. Remarkably, as invariants in hardware designs can be learned through the use of examples and counter-examples [236, 275] and hardware designs are naturally represented in graph formats, techniques developed in ICE-learning [103] (e.g., leveraging examples of properties) and Code2Inv [228] (e.g., generating invariants via neural program representations) can be applied in the hardware domain with insignificant modifications.

The decoupling of a comprehensive program verifier and an agnostic learner for invariant generation brings more flexibility, allowing the learner to apply various ML algorithms. Since this framework exhibits similarities to the general RL formulation, it can be seamlessly integrated with different RL algorithms as well as imitation learning to accelerate the learning process. Additional efforts are expected on multiple fronts, including designing new metrics for assessing the quality of generated invariants to effectively guide the ML-based learner, improving the capability of the teacher (i.e., the environment in the RL setting) to offer more representative (counter-)examples, and developing strategies for generalization, either across various invariant generation methods or diverse programs.

## 2.7 Cost Estimation

Estimating the complexity of formal methods in advance provides the possibility to applying more appropriate verification methods for target hardware designs and better formal results with the minimum efforts. The cost estimation and planning of formal verification can be conducted manually by systematically analyzing attributes of DUTs, property specifications, design constraints/assumptions, which requires sufficient domain expertise and long analysis time. By contrast, ML-based fast and accurate modeling improves the efficiency of automatic cost estimation.

Elmandouh and Wassal [84] employ multiple linear regression models, such as ridge regression and lasso regression, to predict the total CPU time of formal verification runs, based on features extracted from DUT attributes, design properties, formal netlists, and formal run initialization. Later, they give more attention on formal engine orchestration, the methodology to select the most appropriate formal engine for a specific verification problem [85]. The proposed framework includes a group of multi-class classifiers, each of which is trained to predict the capabilities of

one formal engine/algorithm to solve a verification problem in the form of categorical labels (i.e., easy, medium, hard, very hard, or not able to verify). These classifiers take in features distilled from RTL designs (written in VHDL, Verilog or SystemVerilog) and design properties (described in PSL, OVL, or SVA); several ML models are explored, among which the decision tree performs the best, reaching up to 59% of the maximum achievable time improvement. Twigg et al. [247] employ a multi-layer perceptron (MLP) to predict the time and memory usage of Synopsys Formality, a tool used for equivalence checking [241], by using features extracted from Verilog designs.

While cost estimation of formal verification is important, as a majority of failures stem from exceeding memory limits or time constraints, the process of fully automating this estimation still has a considerable journey ahead. First, data scarcity poses a significant obstacle. Each run of verification can consume a substantial amount of time, making it difficult to collect enough data to well train an ML model. Second, different formal methods may require different sets of features, and their behavior can vary largely on different platforms, presenting difficulties in developing generalizable ML models across diverse verification scenarios. There await innovative solutions and further advancements in data collection strategies, feature engineering techniques, and the development of robust ML algorithms tailored to the intricacies of formal verification processes.

## 2.8 Roadmap of ML in Formal Verification

To leverage current ML practices to improve and enhance formal verification tools, we often follow the pipeline for efficient integration: ① identify the formal verification problem, e.g., SAT solver, theorem proving, etc., and formulate it into an ML task, e.g., classification, regression, etc.; ② collect information or data from formal verification for the ML task, e.g., converting CNFs or Boolean networks to graphs for GNNs [15, 163, 221, 266, 272], extracting features of variables [108, 118] for NLP models; ③ figure out the best ML model, as well as parameters, for the formal verification problem.

However, formal verification and ML have opposite mathematical foundations and opposite use in real-life problems: formal verification usually relies on determinate mathematics and aims at ensuring correctness; ML often relies on probabilistic models and consists of learning patterns from training data. As a result, ML techniques cannot "replace" the conventional formal verification techniques or adequately "automatically solve" formal verification problems at present. Instead, ML techniques can "help" or "guide" the formal verification solving process. ML techniques have shown their great potential in improving/accelerating the formal verification process compared to human design. Specifically, ML techniques improve the runtime/efficiency of formal verification by providing a shortcut from data (input variables) to answer (if valuable in formal verification) to help formal verification experts to filter meaningless cases. Additionally, ML techniques can provide higher quality than manual designs by learning from the training data, which is confirmed especially in assertion generation tasks (Section 2.2).

While there have been exciting progresses, existing approaches in leveraging ML for formal verification have critical challenges to address. ① **Functional-aware ML.** For example, there are great needs in enforcing strong logic relations in ML features and the training process. Unfortunately, ML approaches in fundamental formal verification solving problems such as SAT solving only include soft logical constraints in the training and embedding, which greatly limits the generalizability in scaling to practical scaled SAT problems. Exploring hard logical constraints in developing domain-specific ML approaches for such problems is believed to generate broad impacts, e.g., developing computer algebra-based gradient descent mechanisms for training. ② **Heuristics mining and orchestration.** In addition to directly using ML to "solve" formal verification problems, there are substantial opportunities in leveraging the strength of decision-making to boost the solving capabilities of formal verification solvers and heuristics. For example, in SAT

solving, the major progress of runtime improvements for modern SAT solvers comes from the introduction of novel heuristics in the Davis-Putnam-Logemann-Loveland (DPLL) algorithm [1]. There is an increasing number of such heuristics on either cause/variable elimination or DPLL solving, each of which maintains its own strength in different SAT instances. Similar cases happen to other mathematical solving procedures such as solving Gröbner Basis [58, 59, 169, 172, 212] for arithmetic circuits verification problems. Leveraging the power of adaptive decision making in orchestrating existing heuristics and mining novel heuristics in formal solvers will be of great interest. **3 Parallelism in formal verification.** One of the greatest challenges in practical formal verification applications is the runtime cost. While most of the formal verification instances are NP-hard in nature, exploring high-performance computing capabilities offered by modern DL frameworks could significantly improve the scalability. Recently, we have seen lightweight neural network models or convex/non-convex formulation based approaches that solve combinatorial optimization problems with extensive parallelization on heterogeneous platforms. While formal verification solvers start leveraging GPU acceleration [73, 197], it is believed that exploring the tensor-level computation kernels of high-performance DL frameworks can further improve runtime performance of formal verification solvers. **4 Integratability.** While ML approaches are demonstrated to be effective in improving the verification process in various aspects, landing such approaches in end-to-end system integration is a non-trivial task. For example, the majority of the formal verification solvers and industrial verification toolchains are built with high-performance implementations in C/C++ and are mostly optimized for CPU computations. However, ML frameworks mostly involve multiple-level intermediate representations and require a GPU environment to efficiently perform the computations. Moreover, due to the nature of randomness in ML algorithms, lacking determinism could be a concern to land ML-based verification approaches in real-world products. One interesting and challenging direction will be exploring ML deployment in terms of system engineering challenges, e.g., considering the efficiency of heterogeneous computing platforms, programmability, etc.

Therefore, we can say employing ML in formal verification is promising but needs more efforts. We believe ML for formal verification can be further improved when more data is collected and more ML models are developed. ML for formal verification can get rid of human designs and abstractions, and may find a new aspect for problem-solving in formal verification, providing new understandings/interpretations in the formal verification domain.

### 3 ORACLE-BASED VERIFICATION

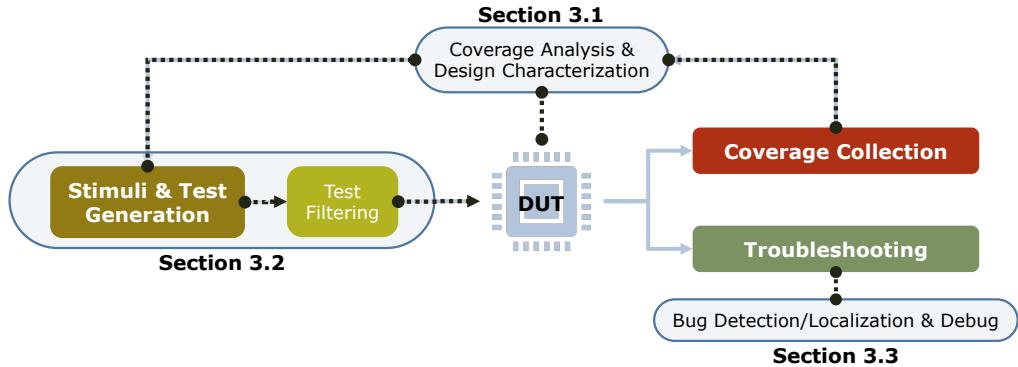

Oracle-based verification focuses on generating tests and achieving sufficient coverage [40]. The primary goal is to reveal failures by executing tests and comparing output results with the oracle provided by a golden reference model. Since the design under test (DUT) is exercised by input tests or stimulus, oracle-based verification is also acknowledged as simulation-based or dynamic verification. In general, simulation-based verification consists of three aspects: coverage measurement, test/stimulus generation, and response checking [205]. Specifically, coverage goals define the scope of a verification problem, and coverage measurement monitors the verification progress with respect to different types of coverage, such as code and functional coverage; test/stimulus generation intends to fully exercise a DUT, i.e., taking a DUT into all the possible behaviors, by constructing tests/stimulus required by the coverage goals; response checking is responsible for demonstrating how behaviors of the DUT conform with its specifications or the golden reference, which triggers the troubleshooting once the discrepancy is detected.

As mentioned by the Moore's law [171, 182], the principle powering the integrated-circuit revolution since the 1960s, the transistor density doubles every 18 months. Even if we are approaching the end of the Moore's law, the electronic industry continues to move to larger, more complex,

Fig. 4. An overview of the oracle-based functional verification. We identify the major ML-based components that could be inserted into the verification flow and how they change the classical verification flow.

and heterogeneous designs. Thus, simulation-based verification, which has been the major yet time-expensive technique for hardware verification, is encountering new challenges. The increasing design size is merely one aspect of the scalability challenge. It is the movement towards system-on-a-chip (SoC) integration and heterogeneous systems that drives simulation-based verification into a corner: nearly 70% of ASIC or FPGA designs contain multiple embedded processors, and around one-fifth to one-fourth of the designs incorporate RISC-V processors or AI processors/accelerators [93]. First, many of the techniques that work well for IP-block-level or sub-system-level verification (e.g., constrained-random and functional coverage) do not scale well to the entire SoC integration or system-level validation [93, 96]. Second, along with the increasing design complexity, simulation-based verification is producing so many data that it has become a big data problem [261, 262], begging for a new level of intelligence in verification, including but not limited to smarter test generation, coverage collection/analysis, and debug.

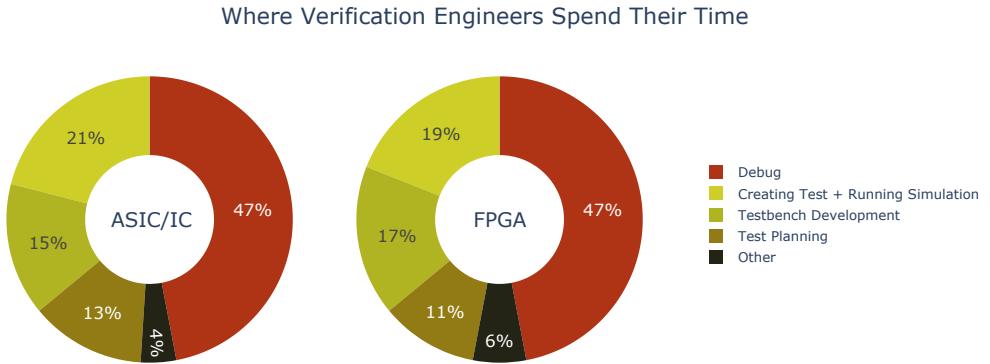

Reckoning on the growth in design and SoC complexity, system heterogeneity, and the amount of verification data, any endeavor enhancing the aforementioned three principal verification aspects (i.e., coverage measurement, test generation, and troubleshooting), either independently or integrally, will greatly promote the productivity and efficacy of simulation-based verification and hardware development. Figure 5 illustrates the breakdown of the time that verification engineers spend on different verification steps, also indicating that debug, test generation, and running simulation dominate the verification time. These all boost opportunities and prospects for incorporating ML-based techniques in verification.

In oracle-based verification, ML-based techniques usually serve as three roles. **① The predictive models for fast and accurate coverage predictions** (Section 3.1). ML has been widely adopted for predictive models [86], since many supervised learning algorithms can infer a general law from observations of particular instances. Such a law is generalizable from labeled examples to new instances under certain constraints. These ML-based predictive models, typically mining the relationships among design signals or from tests to coverage metrics, support eliminating the time-consuming simulation time of DUTs. **② The optimizer for test generation or selection** (Section 3.2). It has always been challenging to find the most stressful and comprehensive tests to stimulate DUTs, so that the coverage closure can be reached within time limits. Several ML-based optimization techniques, such as gradient-based methods [34, 235] or maximum a posteriori estimations [80], have the potentials to advance test generation. **③ The troubleshooting assistant** (Section 3.3). Debug is the bottleneck in verification. Clustering and classification algorithms [181]

Fig. 5. Breakdown of the average time spent on different verification steps by verification engineers in 2022, which is redrawn based on the data from the 2022 Wilson Research Group Functional Verification Study [94].

are flourishing in reasoning out root causes of failures and pinpointing the suspicious design signals/areas.

### 3.1 Coverage Prediction and Design Characterization

A satisfactory coverage level is necessary for verification sign-off. Commonly used coverage metrics include fault coverage, code coverage, and functional coverage [244]: fault coverage indicates the ability to handle faults in a DUT; code coverage measures the execution status of the actual code, which can be recognized as a quantitative measure; functional coverage attempts to measure whether the functionalities described in specifications and the implementation of the DUT have been adequately exercised, which can be considered as a qualitative measure.

Many studies adopt ML models to accelerate the verification cycle by fast and accurate coverage predictions, instead of resorting to the time-consuming simulation process. These learned ML models, which are surrogate models approximating the relation between tests or test templates and coverage metrics, can be either merely employed as predictive models, combined with conventional heuristic-based search algorithms to speed up the evaluation phase of test generation, or interpreted for rule learning of testing knowledge. We review the studies regarding **1 how ML-based surrogate models are embraced in fault** [157, 170, 238], **code** [99, 112, 146, 233], **and functional coverage analysis** [2, 82, 112, 161] in Section 3.1.1, and **2 ML-based design characterization** [77, 139, 215] **and rule learning** [53, 132, 133, 153] in Section 3.1.2.

**3.1.1 Coverage Prediction.** Fault coverage often refers to the percentage of detected faults in all potential faults. Test point insertion (TPI) is a commonly adopted approach to improving fault coverage, which modifies DUTs by inserting extra control points or observation points, but it may degrade the performance of a design in terms of area, power, and timing. The optimal TPI aims to achieve high fault coverage with as little performance degradation as possible, which is NP-complete [156]. Thus, ML techniques are employed to enhance the TPI process by providing accurate predictions on the testability. Given circuit netlists and node features (e.g., controllability, observability, logic depth from the furthest primary input), the impact on fault coverage after inserting a candidate test point can be accurately estimated by an ANN [238]. To better characterize the graph structure of circuits, Ma et al. [170] use graph convolutional networks (GCNs) to predict whether a node is easy or hard to observe, based on which new observation points are inserted.

Table 2. Coverage prediction and design characterization with ML models. S and U stand for supervised and unsupervised learning, respectively.

| Problem                                    | FWK   | ML Model                                              | Target HW                                                            |

|--------------------------------------------|-------|-------------------------------------------------------|----------------------------------------------------------------------|

| Testability prediction                     | S     | ANN [238]                                             | Industrial circuits                                                  |

|                                            | S     | GCN [170]                                             | Four industrial designs                                              |

|                                            | S     | SiFS [157]                                            | Combinational circuits                                               |

| Code coverage prediction                   | S     | Linear regression, decision tree, random forest [146] | An IP module                                                         |

| Toggle pair coverage analysis              | U     | K-means clustering [233]                              | Not mentioned                                                        |

| FSM coverage prediction                    | S     | Random forest [112]                                   | Quad-core cache (four private L1 caches and a shared L2 cache) [112] |

|                                            | S     | MLP, random forest [99]                               |                                                                      |

| Functional coverage analysis or prediction | U     | K-means clustering [82]                               | Industrial designs [82]                                              |

|                                            | S     | LSTM, random forest, SVM, DNN [112]                   | Quad-core cache [112]                                                |

|                                            | S     | Linear regression, SVR/C, KNN [161]                   | MESI cache coherence intersection controller [78]                    |

|                                            | S     | ANN, DNN, SVR, decision tree [2]                      | CORDIC core [79]                                                     |

|                                            | S     | MLP [76]                                              | GPU units [76]                                                       |

| Cross-design coverage prediction           | U + S | K-means clustering and DNNs [215]                     | Nvidia designs [215]                                                 |

| Design characterization                    | U     | K-means clustering [139]                              | Queue management block and serial line interface [139]               |

|                                            | S     | Random forest [77]                                    | UART custom protocol transceiver [111]                               |

| Rule learning                              | U     | ILP [133]                                             | Five-stage pipelined superscalar DLX processor [201]                 |

|                                            | S     | Decision tree [153]                                   | IBM Power7 Processor [152]                                           |

|                                            | U + S | CN2-SD [53]                                           | Load-store unit (LSU) in a processor                                 |

|                                            | S     | CART [132]                                            | Control unit in a commercial dual-core SoC                           |

Compared with classical ML models, such as logistic regression, random forest, SVM, and ANN, the classification accuracy is improved by at least 7.5%; compared with commercial testability analysis tools, this GCN-aided TPI flow achieved similar fault coverage with an 11% reduction in observation points and a 6% reduction in test pattern count. To better explain decisions made by the ML models, Krishnamurthy et al. [157] introduce an intrinsically interpretable and rule-based ML technique, namely Sentences in Feature Subsets (SiFS) [158], to classify whether a point is hard to test, reaching up to 95% accuracy with extra bonus of model interpretability.

Code coverage often refers to the percentage of the source code covered by tests, and typical code coverage analysis includes line, branch, condition, toggle, and finite state machine (FSM) coverage. Aiming to save manual efforts spent for general code coverage analysis, several ML techniques (i.e., linear regression, decision tree, and random forest) can be applied to predict per-test coverage percentage and simulation runtime based on input test parameters [146]. (1) Toggle coverage often refers to describing design activity in terms of changes in signal values, which monitors value changes on registers and nets and measures whether the value has changed from either 1 to 0 or 0 to 1. Stan Sokorac [233] introduces a new coverage metric, toggle pair coverage, which extracts all possible pairs of signals and measures their toggles, reaching a sweet point between the vanilla toggle coverage and the full state space regarding the number of coverage points; then K-means clustering is leveraged to group tests that cover similar areas of toggle pair coverage; after the clustering, genetic algorithm is applied individually within each group to generate tests that would exercise the rarely reached parts of DUTs as frequently as possible. (2) FSM coverage typically refers to how many states and transitions in an FSM have been visited during simulation. To recognize the correlation between instructions and FSM states, ML models, such as random forest [112] and MLP [99], can take the current state of the DUT and instructions to be executed as inputs to predict the next state. These learned models either help construct an augmented FSM upon which the shortest path algorithm (e.g., the Dijkstra [9] algorithm) is applied to direct generate sequences of

instructions as tests, or examine state transitions of current tests to prune out the ones unhelpful to improve transition coverage.

Functional coverage often refers to how many required design functionalities have been examined. These functionalities are converted to coverage points awaiting to be activated by the tests. Since different coverage points may share similarities, clustering algorithms are naturally suitable to group similar coverage points to provide guidance for new test generation. Mandouh et al. [82] take a two-step K-means clustering to prioritize coverage points with low coverage: the first step groups coverage points based on their functional similarities, and the second step assembles the identified clusters based on their coverage ratios. In terms of predicting functional coverage based on input tests, from the micro-architectural level, Gorgi et al. [112] notice that instruction-based predictions provide finer-grained feedback compared with test-template-based predictions, offering better guidance on generating test patterns towards coverage holes: specifically, the instruction-based predictor (LSTM or random forest) takes a sequence of instructions to forecast whether the interested events happen; the test-template-based predictor (DNN, random forest, or SVM) classifies whether an interested event is covered, uncovered, or uncertain. From the RTL, targeting a multi-processor cache controller, Kulkarni [161] studies various types of linear regression, SVR, SVC, and K-nearest neighbors to predict the FIFO queue depth based on test constraints; targeting arithmetic units, a case study [2] of the CORDIC core [79] performs comparative analysis among multiple ML models (MLP, DNN, SVR, and decision trees) and indicates that decision trees have the highest accuracy; targeting channel/datapath stalling to uncover corner-case timing critical bugs in GPU units, Dhadhi et al. [76] use an MLP to model the relation between stall parameters and the coverage metric, which is integrated with GA to efficiently tune the parameters for better coverage.

Among these ML-based coverage predictions, the more complex the hardware designs are, the larger ML models are employed. Though simple ML models are easy to train with moderate amount of data, their representation power is limited due to the number of parameters in the models. Currently, most of the discussed studies focus on single functional units instead of entire designs, and thus they tend to adopt conventional ML models. One issue that may arise is these ML models usually rely heavily on design-specific features, which is nearly impossible to migrate well-trained models to new hardware designs. Recent efforts tend to make analogy between ML models and target problems, such as using LSTM to handle sequences of instructions [112] and exploiting GNNs to represent circuit designs [170], so that domain-specific knowledge or contextual information can be integrated into ML models to enable better transferability.

**3.1.2 Design Characterization and Model Interpretation.** Several studies put more emphasis on design characterization with ML models. Ikram and Ellis [139] use K-means clustering to group modules based on code coverage metrics, and once there are changes in the DUT, the clustering information helps to find all the probably affected modules, providing guidance to test suite generation to cover the influence of the new changes. To reduce the mammoth simulation overhead of coverage collection, Roy et al. [215] use K-means clustering to select representative modules from the DUT, whose coverage metrics are collected and used to train a DNN that can predict the module-level coverage metrics (i.e. the reachability conditions in a module by a test during simulation) for the rest of modules given the same set of tests; experiment results indicate that collecting coverage for 3% of the modules enables predictions with less than 5% error averaged across various modules. Dinu et al. [77] use ML models to analyze the correlations among DUT signals, where a well-trained model can be recognized as a reference model to the DUT whose predictions help reduce the running time of DUT simulation; specifically, a wide range of ML techniques are evaluated to predict whether the data transmission by an UART [111] custom protocol transceiver is erroneous, among which the random forest shows the superior performance.