# A Visionary Look at the Security of Reconfigurable Cloud Computing

This article reviews the current scope of attacks on cloud field-programmable gate arrays and their remediation.

By Mirjana Stojilović<sup>®</sup>, Senior Member IEEE, Kasper Rasmussen<sup>®</sup>, Senior Member IEEE, Francesco Regazzoni<sup>®</sup>, Member IEEE, Mehdi B. Tahoori<sup>®</sup>, Fellow IEEE, and Russell Tessier<sup>®</sup>, Senior Member IEEE

**ABSTRACT** | Field-programmable gate arrays (FPGAs) have become critical components in many cloud computing platforms. These devices possess the fine-grained parallelism and specialization needed to accelerate applications ranging from machine learning to networking and signal processing, among many others. Unfortunately, fine-grained programmability also makes FPGAs a security risk. Here, we review the current scope of attacks on cloud FPGAs and their remediation. Many of the FPGA security limitations are enabled by the shared power distribution network in FPGA devices. The simultaneous sharing of FPGAs is a particular concern. Other attacks on the memory, host microprocessor, and input/output channels are also possible. After examining current attacks, we describe trends in cloud architecture and how they are likely to impact possible future attacks. FPGA integration into cloud hypervisors and system software will provide extensive computing

opportunities but invite new avenues of attack. We identify a series of system, software, and FPGA architectural changes that will facilitate improved security for cloud FPGAs and the overall systems in which they are located.

**KEYWORDS** | Cloud computing; denial-of-service (DoS) attack; fault injection; field-programmable gate array (FPGA); secure computing; side-channel attack.

## NOMENCLATURE

| AES | Advanced Encryption Standard.      |

|-----|------------------------------------|

| API | Application programming interface. |

AWS Amazon Web Services, a subsidiary of

Amazon.

AXI Advanced eXtensible Interface, microcon-

troller bus architecture.

BNN Binary neural network.

BRAM Block RAM, used for storing data inside an

FPGA.

BTI Bias temperature instability. CAD Computer-aided design.

CARRY8 Fast carry logic for a CLB (8 bit).

CGRA Coarse-grained reconfigurable array.

CLB Configurable logic block.

CPA Correlation power analysis.

CPU Central processing unit.

CSP Cloud service provider.

DMA Direct memory access.

DNN Deep neural network.

DoS Denial-of-Service.

DPA Differential power analysis.

DRAM Dynamic RAM.

DRL Dual rail logic.

Manuscript received 30 August 2022; revised 9 September 2023; accepted 26 October 2023. Date of publication 21 November 2023; date of current version 22 December 2023. The work of Mehdi B. Tahoori was supported in part by the German Research Foundation under Grant DFG TA 782/42-1. The work of Russell Tessier was supported in part by NSF under Grant CNS-1902532. (Corresponding author: Mirjana Stojilović.)

Mirjana Stojilović is with the School of Computer and Communication Sciences, École Polytechnique Fédérale de Lausanne (EPFL), 1015 Lausanne, Switzerland (e-mail: mirjana.stojilovic@epfl.ch).

Kasper Rasmussen is with the Department of Computer Science, University of Oxford, OX1 3QD Oxford, U.K. (e-mail: kasper.rasmussen@cs.ox.ac.uk).

**Francesco Regazzoni** is with the University of Amsterdam, 1098 XH Amsterdam, The Netherlands, and also with the Università della Svizzera italiana, 6900 Lugano, Switzerland (e-mail: f.regazzoni@uva.nl; francesco.regazzoni@usi.ch).

**Mehdi B. Tahoori** is with the Karlsruhe Institute of Technology, 76131 Karlsruhe, Germany (e-mail: mehdi.tahoori@kit.edu).

**Russell Tessier** is with the Department of Electrical and Computer Engineering, University of Massachusetts Amherst, Amherst, MA 01003 USA (e-mail: tessier@umass.edu).

Digital Object Identifier 10.1109/JPROC.2023.3330729

0018-9219 © 2023 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See https://www.ieee.org/publications/rights/index.html for more information.

DRM Digital rights management.

DSP Digital signal processing (chip).

FPGA Field-programmable gate array.

FPGAVirt Virtualization framework for FPGAs in the

cloud.

GPU Graphics processing unit.

HARP Hardware accelerator research program,

an Intel platform.

HDL Hardware description language.

HLS High-level synthesis. I/O Input/output. IP Intellectual property.

JTAG Joint Test Action Group, a standard for ver-

ifying and testing chips after manufacture.

LAB Logic array block. LUT Lookup table.

MAC Mandatory access control.

MLP Multilayer perceptron.

MMIO Memory-mapped I/O.

MPSoC Multiprocessor SoC.

NIC Network interface controller.

NN Neural network.NoC Network-on-Chip.PAX Postlayout parasitics.PCB Printed circuit board.

PCIe Peripheral Component Interconnect

Express, a high-speed serial computer expansion bus standard.

Power delivery network.

PID Proportional-integral-derivative, a widely

used control mechanism.

PLL Phase-locked loop.

PDN

RO

PUF Physically unclonable function.

RAM Random access memory.

RSA Rivest-Shamir-Adleman, a public-key

cryptosystem. Ring oscillator.

RTL Register-transfer level, a design abstrac-

tion for synchronous digital circuits.

S-box Substitution-box.

SAVI Smart applications on virtual infrastruc-

ture.

SCA Side-channel attack.

SLR Super logic region.

SoC System-on-Chip.

SPA Simple power analysis.

SQL Structured query language, a database

query language.

TDC Time-to-digital converter.

TEE Trusted execution environment.

TOR Top-of-rack, a switch that connects in-rack

switches to the rest of the data center.

TRNG True random number generator.

TTP Trusted third party.

VHDL Very high-speed integrated circuit hard-

ware description language.

VM Virtual machine.

XOR Exclusive OR.

#### I. INTRODUCTION

Traditionally, cloud platforms have been based on a single type of computing device: CPUs. This homogeneity of hardware resources reflected itself in cost efficiency; buying thousands of very similar types of servers allowed cloud providers to reap the benefits of the economies of scale. The homogeneity of servers had other advantages as well: easy management and scheduling of resources, and simple development and deployment of applications and tools for debugging and tracing.

In recent years, however, cloud servers have gone through a significant change. They have progressively shifted to become heterogeneous platforms in which CPUs join forces with special-purpose integrated circuits [e.g., Google's tensor processing units [1], GPUs, and reprogrammable devices (i.e., FPGAs)]. One of the driving forces behind this change originated from the end of Moore's law coupled with the breakdown of Dennard scaling. While transistor size can still be reduced (though at a slower pace than before), with small transistor sizes and high operating frequencies, the power density increases significantly. Consequently, modern applications' continuously growing hunger for computing power can no longer be satisfied with general-purpose hardware only. We have entered an era in which computational performance growth will be fueled by specialized and heterogeneous hardware [1].

Besides energy efficiency, another important advantage of heterogeneous platforms is more consistent and predictable performance. Cloud applications previously were large monolithic services, but they have evolved into fine-grained, modular designs (microservices or serverless computing), where end-to-end tail latency is several orders of magnitude smaller (in the order of microseconds). Since missing latency requirements lead to cascading performance issues, data center hardware must be able to meet them. Traditional, general-purpose servers were not designed to accommodate such constraints. Heterogeneity, on the other hand, implies tailoring the hardware (and software) to the needs of data center applications, however strict.

FPGAs have emerged as the platform of choice for both regular and irregular forms of application parallelism. Their unique features are low-level hardware access, finegrain programmability, and reconfiguration at runtime. Microsoft was among the first companies to recognize the potential of FPGAs for data center applications: their Catapult servers relied on FPGAs to accelerate the Bing search engine [2]. Since then, a number of commercial CSPs (Amazon AWS [3], Alibaba [4], Baidu, Microsoft Azure [5], and so on) have started offering users remote access to data center FPGAs to develop and deploy their hardware accelerators.

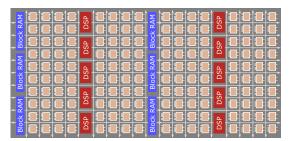

Fig. 1. Example FPGA architecture, showing a column-based layout of logic, memory, and DSP blocks.

Fine-grained control over the low-level FPGA hardware is, as it turns out, at the source of a number of electrical-level security issues. Today, we understand that FPGAs can empower a malicious user to execute a variety of remotely-controlled attacks: DoS, fault injection, power side-channel, and crosstalk side-channel attacks. In this article, in addition to describing the attacks in detail, we bring forward the multifaceted challenges of securely integrating FPGAs in the cloud, which are as relevant for FPGA vendors and developers as they are for cloud service providers and users. We discuss models for future cloud-level use of FPGAs and elaborate on security techniques adapted for virtualized FPGAs in the cloud. Our visionary viewpoints provide insights into how FPGAaccelerated, heterogeneous cloud platforms will likely be used in the future.

The remainder of this article is structured as follows. Section II describes the state of the art in cloud FPGA use. An overview of cloud FPGA threats is described in Section III. Existing cloud FPGA attacks (see Section IV) and remediation (see Section V) are then described. In Section VI, trends in cloud FPGA systems are discussed followed by likely threats to these systems (see Section VII). Suggested solutions to these challenges are described in Section VIII. We conclude this article by summarizing lessons learned (see Section IX) and offering closing thoughts (see Section X). A list of the acronyms used in this article is provided in the Nomenclature.

# II. FPGAs AS COMPUTE ACCELERATORS IN THE CLOUD

In this section, we introduce readers to FPGAs as compute accelerators in the cloud. We start by providing the basics of FPGA architecture (see Section II-A). Then, we describe common heterogeneous cloud architecture (see Section II-B) and the approaches that CSPs use to expose the FPGA fabric to remote users (see Section II-C).

### A. Field-Programmable Gate Arrays

Modern FPGAs consist of columns of logic blocks and heterogeneous hardened units, such as block memories (BRAMs), digital signal processing blocks, external memory interfaces, transceivers, PLLs, and even processor cores and GPU fabric [6].

Fig. 1 illustrates a small part of an FPGA die. The basic and most numerous building blocks of FPGAs are CLBs,

in AMD-Xilinx terminology, or LABs, in Intel terminology. Each of these logic blocks is a cluster of LUTs, flip-flops, and carry propagation logic, which further facilitates the implementation of fast arithmetic circuits. The connectivity between FPGA building blocks is provided by numerous wires, which are grouped in horizontal and vertical routing channels, and routing switches, which can be configured to make connections between wires.

## **B.** Heterogeneous Cloud Server Architecture

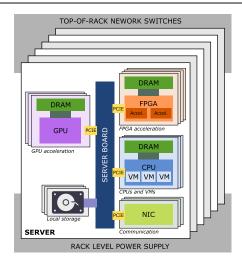

The main computational building block of a data center is a server. The computational performance of today's servers is no longer driven by the growth of the number of CPU cores but harvested from the heterogeneity of available computing units. In Fig. 2, we illustrate a heterogeneous server rack—a physical structure that holds tens of servers together, along with a rack-level power supply and TOR network switches. Owing to TOR switches, servers can access the data center level network and reach any other server or the Internet; in addition, the servers within one rack can communicate extremely efficiently with other servers in that same rack. A server itself can have a number of peripheral cards and local storage. A server configuration can be easily adapted by adding a suitable number of CPU, FPGA, GPU, or other accelerator cards via PCIe interfaces. NICs, which provide a networked connection between servers and TOR switches, are also integrated as PCIe peripherals. The configuration of servers across racks normally varies and is dictated by the targeted applications and desired performance.

The system illustrated in Fig. 2 corresponds to the *single-node accelerator* model, deployed by a number of cloud providers [7], such as AWS, Huawei, Baidu, Tencent, Nimbix, and Alibaba. However, there are other ways in which FPGAs can be or already are deployed in data centers. For instance, Microsoft uses FPGAs to intercept and accelerate network traffic to servers (a *bump-in-the-wire*

Fig. 2. Heterogeneous cloud server architecture.

configuration). In their Azure data centers, multiple FPGAs in a rack can directly communicate with each other, allowing for data center-wide scalability of FPGA workloads [2]. These thousands of FPGAs are not only used to accelerate packet processing but also for Bing search and machine learning inference [8]. Baidu uses FPGAs to accelerate storage, SQL queries, data security, search engines, and artificial intelligence workloads.

A single-node accelerator model is not the only way FPGAs could be exposed to users who wish to deploy their custom accelerator in the cloud. An alternative is a *coprocessor* model, in which an FPGA and a CPU coreside on the same server card (e.g., Intel's HARP platform, where the CPU and the FPGA are connected through a cache-coherent communication link) or even in the same package (e.g., as part of an SoC or an MPSoC). The deployment of MPSoC server cards in commercial clouds will allow for improved performance for applications that do not require an extreme amount of computing resources. It will also allow an FPGA to offload most network configuration tasks and simplify FPGA orchestration with the local CPU.

# C. FPGA Programming and Accelerator Deployment

Given their regular spatial architecture, FPGAs are perfectly tailored to implement highly parallel and deeply pipelined circuits. Furthermore, unlike on GPUs, hardware deployed on FPGAs can be of mixed granularity, ranging from single bit (e.g., control lines) up to hundreds of bits (e.g., for AXI interfaces and memories). Designing an FPGA circuit implies fully describing the functionality of the desired hardware circuit. Most commonly, the process uses HDLs, such as VHDL or Verilog, involving substantial work and competence. To bring FPGA programming closer to software developers, FPGA vendors have developed their own programming environments (e.g., supporting OpenCL [9]) and are also moving toward providing support for several languages and libraries for application spaces (e.g., Vitis from Xilinx and Intel's OneAPI toolkit).

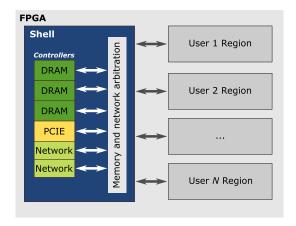

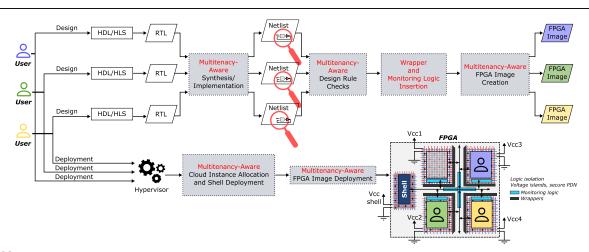

To decouple platform-specific FPGA hardware from user designs, CSPs employ a shell-role architecture [7], as illustrated in Fig. 3. The shell often is comprised of a PCIe interface, a DMA engine, a DRAM controller interface, virtual JTAG, and other health monitoring and image loading logic. The CSP develops the shell design and specifies the interface to user-controlled regions (also called *roles*), in which custom accelerators can be quickly deployed using partial reconfiguration. For example, on AWS FPGA instances, the shell occupies approximately 20% of the FPGA resources. The separation between the shell and user regions allows for different privilege levels within an FPGA design and improves the reuse of user applications [7]. In addition, the separation guarantees at least basic protection of the essential FPGA configuration and communication interfaces, which could otherwise be misconfigured or misused by customer applications.

Fig. 3. Accelerator deployment model for cloud FPGAs, illustrating the separation between the shell and the user regions (i.e., user roles).

The shell generally presents either a host-centric or a shared-memory programming model. In both cases, the shell exposes an MMIO control plane for software to manage the roles. The main difference between the host-centric and shared-memory models is whether the roles can issue their own DMAs. The host-centric model, in which the user accelerators are unaware of the system memory map, is the more widespread. It yields simpler FPGA hardware at the expense of increased communication latency between the CPU and the accelerator, in particular for applications that frequently perform pointer chasing (e.g., graph processing applications such as single source shortest path).

## III. THREATS TO CLOUD FPGAs

Since cloud FPGAs have been exposed to remote users, the attack surface on cloud infrastructures and cloud users has grown considerably. Some remote FPGA attacks aim to undermine the confidentiality of the cloud, e.g., by using side channels to extract secret information from other users. Others aim to break the integrity of the cloud by injecting faults into other users' applications. Last but not least, DoS FPGA attacks target the availability of cloud resources. These remote attacks, as we will soon see in detail, cover a wide landscape of security threats, including side-channel analysis attacks, IP reverse engineering, hardware Trojan insertion and triggering, new covert channels, and accelerated device aging. In this article, we will focus exclusively on successfully demonstrated remote FPGA attacks. Attacks that are impossible to demonstrate on a commercial cloud (e.g., because they require FPGA device tampering or substitution, modified software tools, and untrusted or corrupted FPGA shell) or which are unrelated to the cloud FPGA use case (e.g., FPGA bitstream reverse engineering) are out of scope.

Remote FPGA attacks can broadly be categorized as electrical- and system-level attacks. In the following, we describe the two categories of attacks and their corresponding threat models.

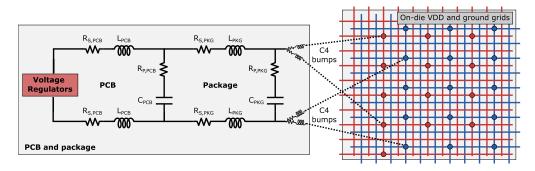

Fig. 4. High-level model of PDN sharing over a PCB (voltage regulators, power and ground planes, and onboard decoupling capacitors), device package (power and ground pins, and package capacitors), and FPGA programmable logic (C4 bumps, and power and ground distribution grid). Dashed lines illustrate the flow of current caused by the FPGA on-chip activity.

#### A. Electrical-Level Attacks

Electrical-level attacks leverage the electrical coupling between the adversary and the victim. An effective way to achieve such coupling in data center FPGAs is via the shared PDN. Figs. 4 and 5 illustrate PDN sharing across a PCB, FPGA package, and programmable logic. Due to the PDN's inductive, capacitive, and resistive components included by design or as parasitics, it is almost impossible to completely eliminate PDN side-channel leakage. Furthermore, maintaining an exact supply voltage level across the system, boards, chips, and individual transistors is generally impractical, if not impossible, irrespective of (data-dependent) transistor switching activities. PDN design usually maximizes reliability so that the amount of voltage drop is capped and limited to ensure proper chip timing at runtime. Several efforts have targeted reliable PDN design [10], [11], [12], [13].

The fine-grained hardware parallelism that makes FPGAs attractive for cloud applications also poses security risks. The bit- and wire-level hardware control provided by FPGAs gives malicious users the power to execute various electrical-level attacks [14]. For an electrical-level attack to be successful, an attacker must be able to either pick up the side-channel information generated by the target (i.e., the victim) or generate a signal (a disturbance) and inject it in the shared electrical medium, through which it propagates to the victim and causes either computational faults or the failure of the voltage regulator supplying the FPGA. The stronger the electrical coupling between the adversary and

the victim, the higher the risk of a successful attack. For this reason, the most common threat model targeting PDN sharing assumes *FPGA multitenancy*, where multiple user applications run simultaneously on the same FPGA.

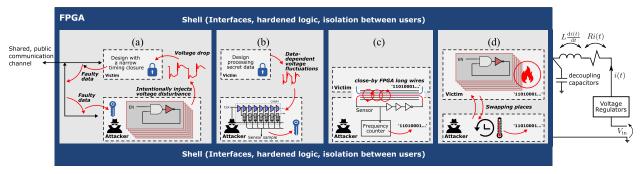

Fig. 6 summarizes the key features of the threat model of an electrical-level attack on a cloud FPGA. First, there is multitenancy. Second, the adversaries and the victims are physically and logically isolated (i.e., not reusing the same FPGA resources) although they share the same FPGA die and interfaces via the FPGA shell. Several attack variants are shown. In a fault-injection attack (scenario A in Fig. 6), the adversary uses specially designed FPGA circuits that draw high currents and, consequently, cause a significant disturbance in the shared supply voltage. Depending on the resulting voltage drop, the attack effects can range from injecting a fault in the victim's operation (and later exploiting it) to the reset or unresponsiveness of the entire cloud FPGA instance (a DoS attack). In the power SCA (scenario B in Fig. 6), the adversary deploys delay-sensing circuits to pick up the power side-channel leakage originating from the victims and uses it to extract their secrets (i.e., a cryptographic key, the images being classified by NN accelerators, and so on).

On FPGAs, the shared PDN is not the only electrical sidechannel medium: programmable interconnects (i.e., the routing wires) have also been shown to leak information. The threat model of such an attack (scenario C in Fig. 6), commonly referred to as a *crosstalk* SCA, considers that the victim is transmitting secret information over several

Fig. 5. Electrical model of the PDN illustrated in Fig. 4, emphasizing the serial and parallel parasitic resistance, capacitance, and inductance.

Fig. 6. Threat model of an electrical-level attack on a cloud FPGA.

cascaded long wires, spanning tens of columns or rows of FPGA logic elements; such long distances are not uncommon, especially for communication channels between the FPGA shell and the user partitions. In addition, it is assumed that the attacker has access to the neighboring wires and continuously measures and analyzes their propagation delay, knowing that it correlates with the secret being transmitted [15].

Thermal effects bring about another class of electrical-level threats (scenario D in Fig. 6), which do not require spatial multitenancy. Unlike voltage-based attacks that typically last for a few microseconds (which is why they concern spatially collocated tenants), temperature changes take several orders of magnitude longer time to dissipate. Consequently, temperature can be used as a covert communication channel [16], [17]. The sender can enable a heater (e.g., a free-running oscillator maximizing dynamic power) to raise the temperature, thus encoding and transmitting one bit of information; similarly, the sender can let the FPGA cool down to transmit the opposite value. As soon as the sender vacates the FPGA, the receiver may load their design with programmable sensors to read the on-chip temperature and infer the bit of information sent.

BTI effects are an example of an electrical-level phenomenon that leaves a trace for some time period. BTI effects physically deteriorate CMOS transistors, negatively impacting their switching speed [18]. They accumulate under voltage stress. Hence, FPGA resources holding a constant value (e.g., a secret key) for a long time are most affected. When the user vacates the FPGA and the voltage stress is removed, the transistors recover, slowly reverting to their previous faster state. An adversary residing on the same FPGA can monitor the BTI recovery process by measuring the propagation delay of the targeted FPGA resources over time [19]. Depending on how the propagation delay evolves over time, the adversary may infer the secret value previously imprinted by the BTI effects. Therefore, exploiting BTI effects is a form of an SCA. Given that the attack targets specific FPGA resources, the threat model requires the adversary to have knowledge of the exact placement and routing of the victim design.

BTI effects on FPGAs can be significantly accelerated with thermal aging. Cook et al. [20] have shown that PUFs

built from ROs are particularly sensitive to the frequency degradation caused by accelerated aging. By surrounding the FPGA ROs with short circuits (thus exposing them to extreme heat), their frequencies can be altered. Once the relative relationships of RO frequencies are adjusted, the overall PUF response can also be tuned. An adversary with the knowledge of the exact location of logic and wiring resources used by the RO PUF can use the targeted aging technique to imprint the desired PUF response, either for cloning the response of an authenticated device (an impersonation attack) or replacing it with an alternative of their choice. These results highlight the consequences of accelerated aging and warn against delay-based PUFs in cloud FPGAs.

## B. System-Level Attacks

In the threat model of a system-level FPGA-assisted attack, an adversary uses the FPGA to attack other parts of the cloud-based system. For example, the FPGA may be used to corrupt portions of memory shared with a CPU or overstress a communication bus shared with a CPU or other FPGAs. In these scenarios, an adversary requires access to the FPGA fabric and the ability to influence privileged CPU software (e.g., operating system, virtual memory manager, or device drivers). In the case that the adversary is able to control privileged FPGA logic, such as the shell, off-chip memory can be compromised (e.g., an adversary can intercept memory traffic via the shell). The host CPU, which is responsible for data transfer and for FPGA user region (role) configuration, may also be assumed to be untrusted and independent of any security mechanism provided by CPU TEEs. Hence, the vulnerability of the host CPU to TEE-targeted attacks is typically out of the scope of FPGA-assisted system-level attacks. Recent work has focused on creating a TEE specifically for cloud FPGAs [21]. These architectures allow for the security of data generated by the FPGAs.

# IV. SECURITY VULNERABILITIES OF CLOUD FPGAs

As introduced in Section III, cloud FPGAs are susceptible to a variety of electrical-level attacks. To implement SCAs, adversaries need one or more on-chip delay and

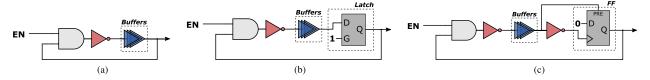

Fig. 7. Various RO designs, suitable for on-chip voltage sensing. Buffers serve to control the RO frequency; they are optional. (a) LUT-based RO. (b) LUT-latch RO. (c) LUT-FF RO.

voltage sensors. To inject a fault, force the FPGA to reset, or accelerate thermal aging, they need power-wasting circuits capable of drawing excessive current and causing a substantial drop in on-chip voltage. Given the low-level hardware control and bit-level programmability of FPGAs, many such circuits can be implemented. In this section, we introduce common FPGA malicious constructs (see Section IV-A) before addressing cloud FPGA attacks in detail (see Sections IV-B and IV-C).

### A. Malicious FPGA Constructs

1) Voltage Sensors: FPGA circuits specifically designed to be highly sensitive to FPGA logic and routing delay variations are key enablers of remote power and crosstalk SCAs. Examples of such circuits are ROs and TDCs.

An RO-based sensor is constructed by creating a loop whose frequency of oscillation is temperature- and voltage-dependent. An RO-sensor is typically enabled for some reference period (i.e., the measurement period), during which the corresponding number of pulses is counted. The measured frequency is then used to estimate the changes in voltage or temperature over time. When the temperature is approximately constant (as is the case for fast voltage transients), ROs sense local on-chip voltage variations. Such sensors have been used for power SCAs [22], crosstalk SCAs [23], [24], and thermal covert communication [25]. They have also been leveraged to receive covert communication, where the sender is a CPU, GPU, or FPGA, and the receiver is an FPGA sharing the same power supply unit in a data center setting [26].

Fig. 7 illustrates three ROs. The simplest design is comprised of an enable signal, a single inverting stage, and, optionally, one or more buffers for adjusting the oscillation frequency. This sensor, being a combinational loop, can easily be detected; indeed, the AWS CSP flags such designs

and does not allow them to be implemented, precisely because of the security risks they pose. However, it is not difficult to build alternative RO-based sensor designs. In Fig. 7(b) and (c) we see two similar constructs, both free of combinational loops, and thus, it more challenging to prohibit in a more general context.

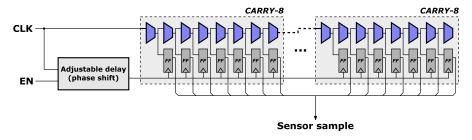

ROs need long measurement periods for precision and are, therefore, unsuitable for side channels that rely on fast transients. Alternatively, TDCs are often used to overcome the limitations of RO-based sensors [27] and have been shown to effectively obtain side-channel information on FPGAs [28]. In TDCs, each measurement reflects the delay of a circuit within a single clock cycle by observing how far through a tapped delay line a signal can travel during the cycle. This makes TDC sensors suitable for sensing short transient delay and voltage fluctuations on the order of a single clock cycle. For example, the TDC shown in Fig. 8 includes a chain of CARRY8 multiplexers used as delay stages. The adjustable delay blocks allow for delay path tuning. Delay-line sensors have even been used to demonstrate power SCAs on Amazon AWS F1 instances [29], recover the inputs to an NN deployed on the same instances [30], and recover the information imprinted via BTI effects [19]. They have also been used to mount attacks against other integrated circuits on the same board [31] and against a CPU sharing the same SoC [22].

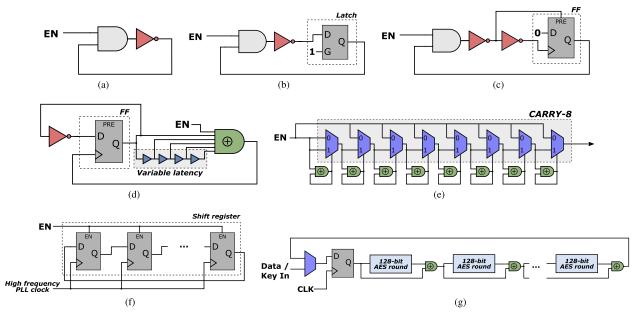

2) Power Wasters: ROs are not only suitable for voltage sensing but also for drawing power. They are particularly efficient power viruses (i.e., power wasters), thanks to their high oscillation frequency and small footprint, as well as the ease of instantiating many of them. Similar to RO-based sensors, several variants of RO-based power wasters can be built [see Fig. 9(a)–(c)]. One would be tempted to think that detecting and preventing combinational loops would be a solution; however, the problem

Fig. 8. FPGA implementation of a TDC, with carry propagation logic serving as a delay line.

Fig. 9. FPGA power wasting circuits that, when instantiated in large numbers, can cause fault injection or FPGA reset. (a) LUT-based RO power waster. (b) LUT-latch RO power waster. (c) LUT-FF RO power waster. (d) Glitch-based power waster. (e) CARRY8-based power waster. (f) Shift register-based power waster, initialized with alternating zeros and ones. (g) AES-based power waster.

is significantly more difficult: power wasters can be built in a variety of ways, and even benign-looking circuits can draw excessive current. In Fig. 9(d)–(g), we see examples of different power wasters—circuits' harnessing glitches, CARRY8 blocks, shift registers, and even AES encryption rounds [32], respectively. They have been successfully used for remote fault injection or DoS attacks. For even more aggressive attacks (e.g., targeted RO PUF aging in impersonation attacks), short circuits are required [20].

#### **B. Cloud FPGA Attacks**

1) Fault Injection and DoS: The use of on-FPGA power wasters to induce timing delay faults in victim circuits has been extensively studied. Characterizations of power waster voltage effects have been performed for localized attacks [48], dynamic and transient attacks [49], and attacks targeting the entire FPGA [36]. These characterizations show that voltage manipulations are possible chip-wide with an isolated power waster due to the FPGA's shared PDN. Recently, Alam et al. [44] showed that allowing a user to intentionally cause write collisions in FPGA dual-port BRAMs can also induce voltage and temperature fluctuations and result in circuit faults. Faults in victim circuits have also been induced using power wasters based on AES [40], [50] and glitch generators based on XOR gates [34], [45].

An assortment of victim circuits has been targeted for fault injection. Krautter et al. [39] examined the possibility of injecting faults into an AES core at a number of operating frequencies and circuit minimum slack values. In [37], a fault-inducing attack on TRNGs using ROs was described. The ROs were placed adjacent to TRNGs,

and TDCs were used to evaluate induced delay changes. In [42], RSA encryption was successfully attacked by enabling power wasters and inducing timing faults. The faulty output was analyzed to determine the secret RSA key [42]. Several attempts have been made to inject faults into machine learning circuits to cause mischaracterization [45], [46], [47]. Fault injection via voltage manipulation in machine learning is challenging due to model redundancy and the significant timing margins employed by FPGA physical design tools [45]. Other application attacks include stealthy FPGA Trojan triggering [41] and FPGA-to-CPU undervolting for injecting faults in CPU code execution [38].

If a sufficient supply of power wasters is simultaneously enabled, the regulators supplying power to the FPGA will be reset. Gnad et al. [33] showed that the sudden activation of thousands of ROs can drive Xilinx FPGAs into reset, requiring a bitstream reload. Although this attack results in a denial of service, it is not capable of stealthily extracting information from an unsuspecting circuit. Provelengios et al. [50] demonstrated that board failure for an Intel Stratix 10 FPGA can occur in as little as  $20 \ \mu s$ , necessitating an effective remediation approach.

Table 1 summarizes the research on PDN fault attacks. It compares the attack objectives, attack types (intra-FPGA or intra-SoC), victim applications, malicious designs deployed, and the FPGA platforms (including the public cloud) on which the attacks were demonstrated.

2) Side-Channel Attacks: In addition to fault injection, on-chip voltage fluctuation caused by victim circuit activity can be monitored to extract information. A variety of voltage fluctuation sensors have been crafted and

Table 1 Comparison of PDN Fault Attacks. Attacks Demonstrated on a Public Cloud Are Highlighted in Bold

| Attack objective   | Type          | Target circuit (the victim)  | Malicious circuits (the attacker)                    | Evaluation platform                                                  |  |  |  |

|--------------------|---------------|------------------------------|------------------------------------------------------|----------------------------------------------------------------------|--|--|--|

|                    |               |                              | Single-stage LUT-based RO [33]                       |                                                                      |  |  |  |

|                    | T.,           | Host                         | Glitch generator and long wires [34]                 | Kintex 7 (KC705) [33]                                                |  |  |  |

| Denial of service  | Intra<br>FPGA | FPGA                         | ROs with transparent latch [35]<br>ROs with FFs [35] | Zynq 7020 (Zedboard) [33]                                            |  |  |  |

|                    | FPGA          | [33], [34], [35]             | ROs with FFS [35] ROs through carry chain logic [35] | Zynq UltraScale+ (Ultra96) [34] Virtex UltraScale+ (Amazon AWS) [35] |  |  |  |

|                    |               |                              | Glitch amplification [35]                            | Virtex UltraScale+ (Alveo U200) [35]                                 |  |  |  |

|                    |               |                              | 1                                                    | viitex Ultrascale+ (Alveo U200) [55]                                 |  |  |  |

|                    | Intra         | A ddon [26] [22]             | 19-stage ROs as voltage sensors [36]                 | Cyclone V (Terasic DE1-SoC) [36], [32]                               |  |  |  |

| Fault injection    | FPGA          | Adder [36], [32]<br>RNG [37] | Single-stage ROs [36], [37]<br>ROs with FFs [32]     | Aria 10 GX (Terasic DE5a-Net) [32]                                   |  |  |  |

|                    | FFGA          | KNG [37]                     | Shift registers[32]                                  | Virtex-7 (VC707) [37]                                                |  |  |  |

|                    |               | Software routines:           | Shift registers[32]                                  |                                                                      |  |  |  |

| Fault injection    | Intra         | multiplication [38]          | Single-stage ROs [38]                                | Zyng UltraScale+ (Genesys-ZU) [38]                                   |  |  |  |

| raun injection     | SoC           | AES [38]                     | Single-stage ROS [56]                                | Zyriq Oltrascale+ (Geliesys-ZU) [58]                                 |  |  |  |

|                    |               | 7125 [30]                    |                                                      | Cyclone V SoC                                                        |  |  |  |

|                    |               | DFA on AES [39], [40]        | Single-stage LUT-based RO                            | (Terasic DE1-SoC [39], [41], [42], [40],                             |  |  |  |

|                    |               | HW Trojan infected AES [41]  | [39], [41], [42], [40], [43]                         | Terasic DE0-Nano-SoC [39])                                           |  |  |  |

| Recover the key    | Intra         | Adder [42]                   | 19-stage ROs as voltage sensors [42]                 | Aria 10 GX (Terasic DE5a-Net) [42]                                   |  |  |  |

|                    | FPGA          | RSA [42]                     | AES [40]                                             | Lattice Semiconductor iCE40HX8K [40]                                 |  |  |  |

|                    |               | DFIA on AES [43]             | ISCAS'89 s1238 benchmark [40]                        | Stratix 10 SX SoC (DE10-Pro) [40]                                    |  |  |  |

|                    |               | . ,                          | . ,                                                  | Spartan-7 (Arty S7) [43]                                             |  |  |  |

|                    |               | CNN [44]                     | Dual-port RAM memory collisions [44]                 |                                                                      |  |  |  |

|                    |               | MobileNet-V1 [45]            | TDC for timing the attack [46], [47]                 | Artix-7 (Nexys 4 DDR) [44]                                           |  |  |  |

| Degrade network    | Intra         | DNN LeNet-5 [46]             | Single-stage ROs [45]                                | Stratix 10 (Terasic DE10-Pro) [45]                                   |  |  |  |

| inference accuracy | FPGA          | ResNet-20 [47]               | ROs with transparent latches [46], [47]              | Pynq-Z1 [46]                                                         |  |  |  |

|                    |               | VGG-11 [47],                 | Clock-gated garbled XORs [45]                        | Zynq UltraScale+ (ZCU104) [47]                                       |  |  |  |

|                    |               | MobileNetV2 [47]             | Clock-gated hybrid toggling logic [45]               |                                                                      |  |  |  |

demonstrated to work (as shown in Figs. 7 and 8) [27], [28], [36], [56], [57]. For example, Zhao and Suh [22] demonstrated that RSA encryption activity on a microprocessor could be detected using ROs in the FPGA fabric when both devices share the same power source. More common attacks on encryption occur when both the victim circuit and sensors are located in the FPGA fabric. AES key information was extracted on a stand-alone FPGA board [28] and AWS EC2 F1 [29] using a TDC. A TDC was used to extract a black-and-white image input to a BNN circuit [30], where tiny voltage fluctuations were used to differentiate between black and white pixels. In [54], a TDC is used to identify the operational phases and parameters of a versatile tensor accelerator.

SCAs that use voltage and electromagnetic effects have been demonstrated using one or more FPGAs. In [58], ROs are periodically enabled to reduce on-FPGA voltage. A collection of TDCs is used to measure small voltage changes as a changed logic value. A similar approach was used to communicate information across multiple dies (SLRs) in an FPGA [59]; in this work, multiple ROs are used to detect communicated values. Finally, when a power supply is shared, it was shown that communication via on-FPGA voltage manipulation can be made across FPGA chips [26] and even across boards that contain FPGAs [26]. It was found that cross-device communication is more effective when the on-chip voltage of the receiver is stressed using RO power wasters.

SCAs in FPGAs can also be carried out using adjacent long FPGA wires. It has previously been shown [23], [24], [60] that the delay of a wire differs slightly if the adjacent

wire carries a logic "0" or a logic "1." This difference can be exploited to extract an AES encryption key [23] from an unsuspecting victim.

Finally, Drewes et al. [19] analyzed the side-channel created by BTI effects. On an AWS EC2 F1 instance, they deployed TDC sensors to track the recovery behavior of the FPGA routing wires and multiplexers previously exposed to accelerated BTI effects. They observed a difference in the recovery behavior, which correlates with the type of BTI effect (positive or negative) to which the wires and multiplexers were exposed.

Table 2 summarizes and compares the FPGA voltage and the long-wire-coupling SCAs.

#### C. System-Level Attacks

Attacks using cloud FPGAs can have impacts beyond the FPGA fabric. These devices can be manipulated to disclose information or generate faulty results from attached memory, caches, CPUs, and adjacent FPGAs. For example, cloud FPGAs can be programmed to fingerprint specific devices to disclose configurations of computing resources in the data center. Tian et al. [25] used a cloud FPGA to access PUFs implemented in DRAM. Distinctive DRAM decay patterns help distinguish specific FPGAs in the cloud. A similar goal was achieved using on-FPGA RO power wasters to create an identifiable per-FPGA voltage response [35]. Tian et al. [61] showed that PCIe contention could also be used to map the locations of cloud nodes. If one FPGA overuses the attached PCIe bus, an adjacent resource on the same bus suffers from excessive bus latency, which

Table 2 Comparison of Power Side-Channel and Long-Wire Coupling Attacks, Together With Thermal and BTI Side Channels. Scenarios Demonstrated on a Public Cloud Are Highlighted in Bold

| Attack Objective                                                                                      | Туре          | Target circuit (the victim)                                                                                                                                             | Malicious circuits (the attacker)                                  | Evaluation platform                                                                                                                                                                  |

|-------------------------------------------------------------------------------------------------------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Recover the key                                                                                       | Intra<br>FPGA | RSA (SPA attack [22]) AES (CPA attack [28], [51])                                                                                                                       | ROs as voltage sensors [22]<br>TDC [28], [51]                      | Zynq-7020 (Zedboard) [22]<br>Spartan-6 (Sakura-G) [28]<br>Virtex UltraScale+ (Amazon AWS) [51]                                                                                       |

| Recover the key                                                                                       | Inter<br>FPGA | AES (CPA attack [31])                                                                                                                                                   | TDC [31]                                                           | Spartan-6 (Sakura-G) [31]                                                                                                                                                            |

| Recover the key                                                                                       | Intra<br>SoC  | OpenSSL AES (CPA attack [52])<br>Tiny AES (CPA attack [52])                                                                                                             | TDC [52]                                                           | Zynq-7000 [52]                                                                                                                                                                       |

| Recover: DNN model [53], the architecture of NN layers [54], BNN inputs [30], folding parameters [55] | Intra<br>FPGA | MLP [53], AlexNet [53],<br>VGG16 [53]<br>Versatile Tensor Accelerator<br>(ResNet-18, MobileNet v1) [54]<br>Convolution unit of a BNN [30]<br>FINN-MLP with folding [55] | Three-stage ROs as voltage sensors [53] TDC [54], [30], [55]       | Zynq-7000 SoC (Zedboard) [53]<br>Zynq-7000 SoC (ZC706) [54]<br>Artix-7 (ChipWhisperer) [30]<br>Zynq UltraScale+ (ZCU1-4) [30]<br>Virtex UltraScale+ [30]<br>Pynq-Z1 (Z-7020 SoC)[55] |

| Recover the key                                                                                       | Intra<br>FPGA | Long wire at the AES S-box input [23]<br>Long wire carrying AES key [24]                                                                                                | Long wire<br>side-channel leakage<br>sensed with ROs<br>[23], [24] | Cyclone IV E [23] Cyclone IV GX [23] Virtex 6 (ML605s) [24] Artix 7 (Digilent Nexys 4 DDR) [24] Artix 7(Digilent Basys 3) [24] Spartan 7 (ArtyS7) [24]                               |

| Covert communication                                                                                  | Thermal       | Temperature sensors:<br>RO sensors [16], [17]                                                                                                                           | Heaters:<br>Power wasters [16], [17]                               | Stratix V [16] SmartSSD (with an FPGA) [17]                                                                                                                                          |

| Recover previous user data                                                                            | ВТІ           | Long wires [19]                                                                                                                                                         | TDC [19]                                                           | ZCU102 Ultrascale+ [19] Virtex UltraScale+ (Amazon AWS) [19]                                                                                                                         |

is easily identifiable. Contention can, thus, effectively be used to map out the locations of the interconnected components (CPUs, memory, and FPGAs) in AWS EC2 F1 nodes. PCIe bus contention can also be used as a covert channel. Giechaskiel et al. [62] showed that a low-bandwidth channel can be established between two VMs that use cloud FPGAs via PCIe bus contention. A VM can transfer a logic "1" value to another VM that shares the bus by programming its FPGA to overuse the bus. The lack of contention indicates a logic "0" transfer.

Cloud FPGAs have also been used to induce faults in attached DRAM and caches. Weissman et al. [63] showed that RowHammer [64] attacks could be efficiently executed on DRAM from an FPGA. Bit flips caused by the attack led to the exposure of an RSA encryption key. It was also shown in this article that a cloud FPGA could attack the last level (LL) cache used by an attached CPU creating a covert side channel.

Table 3 summarizes and compares the research works on cloud system-level FPGA attacks.

# V. REMEDIATION FOR ELECTRICAL-LEVEL ATTACKS

A body of research investigated remediations against electrical-level cloud FPGA attacks. In this section, we introduce and discuss the proposed countermeasures, highlighting their key features. The strategies against system-level attacks are discussed in Sections VII and VIII.

# A. Protection Against Fault-Injection and DoS Attacks

Approaches to address voltage-based fault injection and DoS attacks in multitenant FPGAs can be broken into two broad classes: bitstream scanning and runtime remediation. Scanning FPGA bitstreams or intermediate designs used to generate bitstreams can help identify potentially malicious logic structures, such as ROs. For example, Krautter et al. [65] and La et al. [66] have developed bitstream scanners that attempt to locate malicious circuits instantiated in a library. These circuits include ROs, selfclocked logic, high fan-out circuits, and glitch amplifiers. Both tools regenerate a netlist from a partial bitstream and use graph-based algorithms to locate potentially malicious circuits. Although this approach can locate many types of circuits, it is, unfortunately, straightforward to build power wasters that have the same logical profile as legitimate circuits [see Fig. 9(a)] [32]. Benign-looking constructs can be used to inject faults [40] or perform SCAs [40]. This makes the job of such FPGA antivirus tools much harder. Another issue is the balance between false positives (benign designs that are red-flagged) and false negatives (malicious designs that escape detection).

During deployment, the software of the CSP should monitor the activities of various tenants and closely watch for electrical-level issues [78]. For instance, by identifying suspicious tenants and reacting to voltage surges, a malicious tenant can be disabled and evicted from the FPGA fabric before causing harm and impacting other FPGA tenants [67]. However, the efficiency of such approaches can be greatly improved by providing proper support in the technology and toolchain of cloud FPGAs, allowing for quick deconfiguration of malicious tenants. Runtime approaches for voltage attack detection typically involve the use of distributed voltage sensors [27]. Both Provelengios et al. [36] and Mirzargar et al. [79] use an array of low-overhead RO-based voltage sensors that can

Table 3 Comparison of System-Level Attacks. Attacks Demonstrated on a Public Cloud Are Highlighted in Bold

| Attack Objective                                                                                               | Type                                                                                                                                                     | Target (the victim)              | Malicious circuits (the attacker)                                                       | Evaluation platform                                                                                  |

|----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|-----------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|

| Fingerprinting cloud<br>FPGA instances [25]                                                                    | FPGA-to-DRAM                                                                                                                                             | Cloud infrastructure [25]        | Decay-based<br>DRAM PUF [25]                                                            | Virtex UltraScale+<br>(Amazon AWS) [25]                                                              |

| Retrieve cloud configuration; Reverse engineer the FPGA instance allocation algorithm                          | PCIe contention                                                                                                                                          | Cloud<br>infrastructure [61]     | Remote user<br>transferring data between<br>CPU and FPGA,<br>creating PCIe traffic [61] | Virtex UltraScale+<br>(Amazon AWS) [61]                                                              |

| Use PCIe traffic signatures for covert communication; Deduce cloud resource usage by monitoring PCIe bandwidth | Covert communication<br>between virtual machines<br>on FPGA-accelerated<br>cloud instances;<br>Side-channel leak<br>of PCIe signatures<br>of cloud users | Cloud infrastructure [62]        | Remote user causing intensive PCIe traffic [62]                                         | Virtex UltraScale+<br>(Amazon AWS) [62]                                                              |

| Covert communication<br>between components<br>powered by the same<br>power supply unit                         | FPGA-to-FPGA<br>CPU-to-FPGA<br>GPU-to-FPGA                                                                                                               | Cloud infrastructure [26]        | Four-stage ROs<br>(one inverter and<br>three buffers) [26]                              | Kintex 7 (KC705)<br>Artix 7 (AC701)<br>Xeon E5645 CPU<br>Xeon E5-2609 CPU<br>Nvidia GeForce GPU [26] |

| Fault attack on RSA, leaking the private factors                                                               | FPGA-to-DRAM<br>RowHammer                                                                                                                                | Shared DRAM [63]                 | RowHammer attacker from the FPGA [63]                                                   | Arria 10 GX PAC [63]                                                                                 |

| Cache-based covert communication                                                                               | Cache attack<br>FPGA-to-FPGA<br>CPU-to-FPGA<br>FPGA-to-CPU                                                                                               | CPU LL-cache,<br>FPGA cache [63] | Software or hardware<br>accessing the cache<br>to evict, time,<br>prime, or reload [63] | Arria 10 GX PAC [63]                                                                                 |

identify voltage droops. This information can be used for remediation. More recent work has shown that TDCs can identify droops more quickly, allowing for a faster response time [82].

Since voltage attacks can lead to fault injection (in a few microseconds) or board reset (in tens of microseconds), attack remediation techniques must be able to be rapidly deployed. Luo and Xu [81] built a framework that controls the frequency of the target FPGA applications to avoid timing faults. Provelengios et al. [50] demonstrated a processor-based approach to suppress synchronous power wasters. Information from voltage sensors is transferred to an ARM core via a dedicated network. If an attack is detected, it is localized to a clock region, and the associated clock is deactivated, stopping the attack. The remediation approach was shown to suppress voltage attacks on a Stratix 10 FPGA within 20  $\mu$ s, sufficiently fast to prevent board reset. In [67], partial FPGA reconfiguration is used to disrupt the operation of loop-based ROs. The authors determined a configuration sequence that was able to rapidly deactivate interconnect in a clock region of an UltraScale+ FPGA, effectively stopping a voltage attack. Partial reconfiguration was sufficiently fast enough to suppress a board crash and some timing faults.

#### **B. SCA Remediation**

Power SCAs can be defeated if preventive actions are deployed. FPGA SCA countermeasures can be classified into two categories: hiding and masking [83]. The goal of

hiding is to reduce the signal-to-noise ratio of side-channel information by increasing noise in the side channel or equalizing power consumption across computation [74]. Masking requires the processing of randomized data while ensuring computation correctness [73]. Unfortunately, both approaches lead to area increases and the possibility of higher order attacks [83]. For multitenant FPGAs, remediation approaches against power SCAs have been developed by Le Masle et al. [75] and Krautter et al. [76]. These approaches use a closed-loop control system to stabilize the steady-state power consumption of an FPGA circuit. In the former case, an on-chip RO network is used to monitor on-FPGA voltage [75]. A PID controller, whose PID constants are set so that the voltage measured by the sensors is kept approximately constant, is used as a control circuit. The latter approach uses a fence composed of ROs between two neighboring FPGA tenants [76] to increase the signal-to-noise ratio. The number of active ROs is controlled by a voltage sensor. The total size of the fence can be adjusted by the designer of the circuit to be protected. For an even more effective fence per unit of area, ROs can be combined with the abundant FPGA routing resources [77].

Effective remediation approaches against long-wire coupling prevent security-sensitive signals from being routed in the vicinity of other tenants' signals. Both CAD and architectural techniques have been developed to address the potential risks of crosstalk. Huffmire et al. [68] isolated risky applications and their signals via moats and drawbridges. Yazdanshenas and Betz [69] proposed wrapping

Table 4 Comparison of the Proposed Protections Against Electrical-Level Attacks on Shared FPGAs

|                            | Applicability |              |              | Use of FPGA resources |         | Who should deploy them |         |         |         |         |              |            |          |

|----------------------------|---------------|--------------|--------------|-----------------------|---------|------------------------|---------|---------|---------|---------|--------------|------------|----------|

| Protections                | crs           | pwr          | dos          | flt                   | logic   | wire                   | clk     | Туре    | usr     | vnd     | csp          | Disclosure | Portable |

| Krautter et al. [65]       | •             | •            | 0            | •                     | 0       | 0                      | 0       | Passive | 0       | 0       | •            | O*         | N/A      |

| La et al. [66]             |               | $lackbox{0}$ | $lackbox{0}$ | $lackbox{0}$          | $\circ$ | $\circ$                | $\circ$ | Passive | $\circ$ | $\circ$ |              | <b>O</b> * | N/A      |

| Nassar et al. [67]         | $\circ$       | $\circ$      |              | $lackbox{0}$          | •       | •                      |         | Active  | $\circ$ | $\circ$ |              | $\circ$    | •        |

| Huffmire et al. [68]       | $lackbox{0}$  | 0            | 0            | $\circ$               | •       | •                      | 0       | Passive |         | $\circ$ | 0            | $\circ$    | $\circ$  |

| Yazdanshenas and Betz [69] | •             | $\circ$      | $\circ$      | $\circ$               | •       | •                      |         | Passive | 0       | •       |              | •          | •        |

| Luo et al. [70]            |               | $\circ$      | $\circ$      | $\circ$               | $\circ$ | •                      | $\circ$ | Passive | $\circ$ |         | $\circ$      | $\circ$    | •        |

| Seifoori et al. [71]       |               | 0            | $\circ$      | $\circ$               | $\circ$ |                        | $\circ$ | Passive | $\circ$ |         | $\circ$      | 0          | •        |

| Luo et al. [72]            |               | $\circ$      | $\circ$      | $\circ$               | $\circ$ | •                      | $\circ$ | Passive | 0       |         | $\circ$      | •          | •        |

| Regazzoni et al. [73]      | 0             | •            | $\circ$      | $\circ$               | •       | •                      | $\circ$ | Passive |         | $\circ$ | $\circ$      | $\circ$    | •        |

| Tiri et al. [74]           | $\circ$       | $lackbox{}$  | $\circ$      | $\circ$               |         |                        | $\circ$ | Passive |         | $\circ$ | $\circ$      | 0          |          |

| Le Masle et al. [75]       | 0             | •            | 0            | $\circ$               | •       | •                      |         | Active  |         | $\circ$ | 0            | $\circ$    | $\circ$  |

| Krautter et al. [76]       | 0             | •            | $\circ$      | $\circ$               | •       | •                      |         | Active  |         | $\circ$ | $lackbox{0}$ | $\circ$    | $\circ$  |

| Glamočanin et al. [77]     | $\circ$       | •            | $\circ$      | $\circ$               | •       |                        |         | Active  |         | $\circ$ | $lackbox{0}$ | $\circ$    | $\circ$  |

| Shen et al. [78]           | $\circ$       | $\circ$      | $\circ$      |                       |         |                        |         | Active  |         | $\circ$ | $\circ$      | 0          | $\circ$  |

| Provelengios et al. [36]   | 0             | $\circ$      | •            |                       | •       | •                      |         | Active  |         | $\circ$ |              | •          | $\circ$  |

| Mirzargar et al. [79]      | $\circ$       | $\circ$      | $lackbox{0}$ |                       | •       | •                      |         | Active  | $\circ$ | $\circ$ |              | •          | •*       |

| Stott et al. [80]          | $\circ$       | $\circ$      | $\circ$      |                       | •       | •                      |         | Active  |         | $\circ$ | $\circ$      | 0          | $\circ$  |

| Mahmoud et al. [41]        | $\circ$       | $\circ$      | $\circ$      | •                     | •       | •                      | $\circ$ | Active  |         | $\circ$ | $\circ$      | $\circ$    | $\circ$  |

| Luo and Xu [81]            | $\circ$       | $\circ$      | $\circ$      |                       | •       | •                      | •       | Active  | •       | 0       | 0            | $\circ$    | $\circ$  |

**Legend:** *crs*) Crosstalk side-channel attack; *pwr*) Power side-channel attack; *dos*) Denial-of-service attack; *flt*) Fault attack; *logic*) FPGA logic; *wire*) FPGA routing; *clk*) Clocking resources; *usr*) Users; *vnd*) FPGA vendors; *csp*) Cloud service providers; ● Yes; ● Partially; ○ No; \* Conditionally; N/A Not applicable.

roles with wrappers made from FPGA logic. All data transported to or from a role are encrypted. The approach leads to an 80% data transport latency increase and a 20% role area increase. A hardware isolation framework [70], [72] was developed, which prevents security-critical nets from using long routing wires. The nets are isolated from other users' nets by routing them first and keeping subsequently routed signals away from them. For long wires that cannot fit within the design boundaries, wires surrounding sensitive signals are left unassigned. Seifoori et al. [71] modified PathFinder, an FPGA routing algorithm, to prevent potential crosstalk. Their approach requires the users to specify security-critical nets at design time and set parameters to control the use of wires adjacent to these nets.

Side channels based on temperature and BTI effects are best addressed, first, by not allowing aggressive heating (a strategy effective also against targeted aging attacks aiming at FPGA impersonation [20]) and, second, by allowing sufficient recovery time between two subsequent FPGA tenants [16], [17], [19].

## C. Discussion

Table 4 summarizes and compares proposed countermeasures using the following criteria:

- 1) applicability, if a countermeasure is effective against more than a single attack type;

- 2) use of logic, wiring, and clock resources;

- 3) real-time (i.e., active) application or not real time (i.e., passive);

- 4) deployed by users, FPGA vendors, or CSPs;

- 5) whether design disclosure to the CSP is a requirement for protection implementation;

- 6) amount of effort required to port the countermeasure to an FPGA of another family or another vendor.

We can observe that countermeasures seldom target more than a single type of attack. Furthermore, they often require additional FPGA resources. Some are easily portable between different FPGA families, but many are not. It is clear that combined efforts by researchers, end users, FPGA vendors, and CSPs are required to reach a more general solution or at least a suitable combination of the existing ideas.

# VI. TRENDS IN CLOUD SYSTEM USE OF FPGAs

Currently, the most widespread model of cloud-level use of FPGAs is the single-node accelerator model, as discussed in Section II and illustrated in Fig. 2. In such a model, an FPGA accelerator node acts as a PCIe-attached coprocessor, which remote users can access and program with designs via a host CPU. From the point of view of CSPs, this model is convenient for a number of reasons. First, CSPs can quickly and efficiently deploy an FPGA-accelerated cloud by using off-the-shelf boards, an approach used by Nimbix and Tencent [7]. Other CSPs, e.g., Amazon AWS, Baidu, Huawei, and Alibaba, have designed custom boards and tailored their hardware not only to specific user requirements but also to their specific data center-level architecture requirements and upgrades. While custom board design implies higher startup and maintenance costs, it provides the freedom of feature selection (e.g., FPGA family, size, I/O port count, and off-chip memory size and type). Another advantage of the distributed single-node accelerator model is simplicity. FPGA instances are easier to orchestrate, and the risk of their failure affecting a large amount of data center resources is reduced. In addition, in a single-node accelerator model, it is straightforward to offer FPGAs as bare-metal resources using standard FPGA-design tools.

Despite the aforementioned advantages, the single-node accelerator model is not here to stay. Future models for cloud system-level use of FPGAs will need to provide higher scalability, minimum communication and data transfer latency, virtualization, and sharing of FPGA resources while addressing the accompanied security risks. In this section, we first discuss trends in FPGA-accelerator architectures that address the challenge of scalability and latency. Then, we give a detailed overview of research on FPGA resource virtualization.

#### A. Trends in Cloud FPGA Architectures

Unlike production systems, research architectures are built with less concern regarding total implementation cost or security constraints but rather focus on performance and latency. For instance, to achieve fast FPGA-to-FPGA communication, a number of research architectures deploy a secondary network that connects FPGAs across servers. Examples of such architectures include Microsoft's Catapult v1 [84], Novo-G# [85], Albireo nodes of the Cygnus supercomputer system at the University of Tsukuba, and the Noctua system at the Paderborn Center for Parallel Computing [86]. None of today's production systems uses a secondary network, likely because of the cost and complexity of wiring and additional networking hardware and the resources needed to secure the system. However, designers of some production systems are considering providing fast FPGA-to-FPGA links; specifically, Amazon AWS is advertising its plans to enable FPGA cards to send or receive data from an adjacent card at 200 Gb/s, over a generic raw streaming interface [87].

Another important trend among research architectures is to directly connect FPGAs to the data center network. Consequently, FPGAs could be accessed by a CPU or by another FPGA, leading to good scalability. Some examples of such architectures include CloudFPGA by IBM Zurich Research Lab [88], the University of Toronto SAVI testbed [89] (where a cluster of FPGAs is connected to the data center network), Enzian at ETH Zürich [90] (where an FPGA is connected to the network on one side and coherently attached to a server-class SoC on another side), and Microsoft Azure. It is obvious that the security and reliability concerns inherent to direct network connectivity of FPGAs limit user FPGA access.

## B. FPGA Resource Management and Virtualization

Users of cloud FPGA environments ideally want access to one or more dedicated FPGA boards without having

to worry about resource sharing. However, cloud FPGA providers can sell FPGA services to more users if they can virtualize the environment and allow users who do not take up all FPGA and connected peripheral resources to share the underlying physical infrastructure. Sharing can be performed either by giving each user a specific time period in which to use the cloud environment, also called slot-based allocation, e.g., [91], or by allowing multiple users to use the environment at the same time (multitenancy). A virtualized view of peripherals can be provided to make it seem like each user has unique access, e.g., [92], [93], and [94]. Multitenancy allows for increased flexibility and control.

The goal of a virtualized environment is to make it seem like a user has sole resource access while physically serving several users at the same time. This approach for FPGAs is conceptually similar to traditional CPU virtualization, which is widely deployed and understood. However, FPGA virtualization differs in several important ways that make existing virtualization solutions for CPUs unsuitable. One important difference is that FPGAs do not execute sequential programs one instruction at a time but rather implement parallel circuits, so circuits from different users run simultaneously. Furthermore, FPGA circuits can contain asynchronous elements that are not directly controlled by an external clock, so stopping and restarting an FPGA are not feasible with the current technology. Since FPGAs are often used for time-sensitive processes, even if there was a way to interrupt an FPGA and restart it in the same internal state, it would likely interfere with application semantics.

To achieve a virtualized environment, external memory must be remapped to different physical addresses, and access to the FPGA must be carefully controlled to make sure that each user cannot interfere with other users on the same hardware. The same is true for other external resources, such as the network or storage systems. Together a shell and the virtualized peripherals should create a good logical separation between different users, even if several users use the hardware at the same time. However, multiple problems have been presented in the last few years, which cast doubt on the effectiveness of this separation technique [15], [24], [39], [59], [60], [91], [95].

The challenge of data center resource provisioning has motivated the development of platforms that allow data center managers to monitor the network and modify, in real time, the amount and type of compute resources given to each application. Examples of such platforms are OpenStack [96] (a free and open standard for cloud computing platforms) and Kubernetes [97]. While these platforms orchestrate the entire data center, they require individual components on each server to provision its resources. Furthermore, these platforms are currently limited to provisioning CPUs. For heterogeneous servers, extending and redesigning the existing orchestration platforms to include other types of computing components are

Table 5 Trends in FPGA Virtualization Architectures

|                          | Access<br>method | FPGA<br>regions | Spatial sharing | On-chip<br>comm. |

|--------------------------|------------------|-----------------|-----------------|------------------|

| Byma et al. [105]        | 10 GbE           | Х               | /               | Х                |

| Chen et al. [103]        | PCIe             | 4               | /               | Х                |

| Fahmy et al. [106]       | PCIe             | 4               | /               | Х                |

| Weerasinghe et al. [107] | 10 GbE           | 1               | ×               | Х                |

| Asiatici et al. [108]    | PCIe             | 3               | /               | Х                |

| Vesper et al. [109]      | PCIe             | 4               | /               | ✓                |

| Tarafdar et al. [110]    | 10 GbE           | 1               | ×               | Х                |

| Zhang et al. [111]       | PCIe             | ×               | /               | Х                |

| Mbongue et al. [104]     | PCIe             | 4               | /               | ✓                |

| Mbongue et al. [92]      | PCIe, Ethernet   | 6               | ✓               | ✓                |

necessities. In particular, provisioning and sharing FPGA resources require an entirely new solution for resource virtualization [98], operating system support, and FPGA programming (i.e., bitstream file creation and partial reconfiguration). Processor virtualization relies either on instruction set translation or hardware support with technologies such as Intel Virtualization Technology (Intel VT) [99]. Alternative approaches are needed for FPGAs. Two common approaches for FPGA resource management are slot-based allocation and FPGA overlays.

In slot-based FPGA resource management [7], [100], [101], [102], an FPGA is divided into several reconfigurable regions, in which user FPGA circuits can be mapped at runtime via reconfiguration. These regions may or may not be symmetric, i.e., use similar or identically sized slots. In an example of slot-based FPGA virtualization [103], an FPGA is divided into four regions, while the architecture multiplexes FPGAs by dynamically assigning resources. The main limitation of the architecture is the lack of on-chip communication between regions, resulting in a considerable data-copy overhead when such a transfer is required. To address the above issue and reduce data movement overhead, Mbongue et al. [94], [104] and Yazdanshenas and Betz [69] make use of the FPGA on-chip interconnect. A number of research proposals for FPGA virtualization architectures are listed in Table 5. In addition to the solutions listed in the table, commercial solutions from VMAccell and InAccel offer complete frameworks. The VMAccel software is based on OpenStack, Docker, and Kubernetes, while InAccel software contains high-level APIs in C/C++, Java, and Python and a unified engine to support a heterogeneous multiaccelerator platform.

FPGA overlays, also called intermediate architectures or fabrics [112], offer an alternative to FPGA partitioning. Overlays abstract away the low-level FPGA hardware components (e.g., LUTs, flip-flops, and DSPs). Higher level coarse-grained processing elements, also called CGRAs, are implemented and can be programmed at runtime through software-level function calls. These elements are connected using interconnect topologies that allow both parallel processing and easy data exchange [7], [113], [114], [115], [116]. CGRAs are often supported by compilers that can map popular software programming languages. By abstracting away the low-level hardware

details, overlays also allow faster FPGA development cycles.