# CuTi as potential liner- and barrier-free interconnect conductor

Minghua Zhang and Daniel Gall

Abstract— CuTi layers are co-sputter deposited on 20nm-SiO<sub>2</sub>/Si(001) wafers at 350 °C to quantify their stability in direct contact with a dielectric and to explore the potential of CuTi as barrier- and liner-free interconnect metal. X-ray diffraction pole figures indicate a preferred 001 out-of-plane crystalline orientation and Rutherford backscattering confirms stoichiometric composition. Vacuum annealing tests at 450 °C of CuTi layers indicate considerably higher thermal stability than for pure Cu layers, including negligible dewetting observed by scanning electron microscopy and negligible intermixing with the oxide substrate quantified by photoelectron spectroscopy. Fourpoint bend tests show a 25% higher interfacial toughness for CuTi/SiO2 than Cu/SiO2 interfaces. CuTi/SiO2 samples also exhibit a 300-times longer failure time than Cu/SiO<sub>2</sub> during timedependent dielectric breakdown tests using an externally applied 3 MV/cm electric field. The higher stability of CuTi in comparison to Cu is attributed to a higher cohesive energy in combination with an atomically thin self-limiting Ti oxide layer at the CuTi/SiO2 interface.

Index Terms—CuTi layers, interconnects, stability, barrier-free

### I. INTRODUCTION

u interconnect technology including dual-damascene processing and Ta/TaN liner/barrier layers have dominated back-end-of-line integrated circuit manufacturing for over two decades [1, 2]. However, the decreasing pitch size for each technology node causes an increasing resistance and associated signal delay and power consumption [3, 4]. The resistance increase is due to both a reduced interconnect cross-sectional area and an increased Cu resistivity caused by electron scattering at surfaces [5-8] and grain boundaries [9-13]. As a result, considerable research effort has focused on exploring alternative materials to replace Cu metallization [14-17], considering both elemental metals like Ru [18], Co [19], Ir [20], Rh [21], W [22] and Mo [23], or compound conductors including CuAl<sub>2</sub> [24], NiAl [25, 26], Al<sub>3</sub>Sc [27], Cu<sub>2</sub>Mg [28], VNi<sub>2</sub> [5], and Ti<sub>4</sub>SiC<sub>3</sub> [29] as conductive material. These alternative conductors have the potential to outperform the Cu line conductance at small dimensions based on either a suppressed resistivity size effect due to a small electron mean free path and/or a liner/barrier free metallization scheme [14]. Liner/barrier layers are required for Cu lines to facilitate adhesion and suppress electromigration and Cu diffusion into the dielectric [30, 31]. However, they occupy a considerable fraction of the space within the trench, effectively increasing the resistance of Cu lines. Conversely, a conductive material which does not require liner/barrier layers has a conductance advantage over Cu at small dimensions. We have recently

quantified the intrinsic resistivity scaling of CuTi and CuAl<sub>2</sub> using a combination of transport measurements on epitaxial layers. We found that CuAl<sub>2</sub> [24] has a comparable resistivity scaling with W [22, 32] and Co [19, 33, 34] while CuTi has a worse resistivity scaling and only provides a conductance advantage if its large cohesive energy facilitates liner/barrierfree metallization [35]. Thus, in this letter, we present a study on the stability of the CuTi/SiO<sub>2</sub> interface, representing the first step towards a potential liner/barrier-free CuTi metallization. Direct comparison of CuTi/SiO<sub>2</sub> with Cu/SiO<sub>2</sub> layers indicates a range of CuTi advantages including a higher thermal stability, better wetting and less intermixing with the oxide, a higher interface toughness, and a higher stability against timedependent dielectric breakdown. The CuTi electromigration (EM) performance is also expected to be superior, although it is not directly measured in this study. More specifically, based on previous studies on other metals including Cu and Co [36, 37], the EM activation energy is proportional to the melting point  $T_{\rm m}$ [36, 38], while  $T_{\rm m}$  is proportional to the cohesive energy [39]. The cohesive energy of 4.33 eV/atom for CuTi [35] is 24% larger than that for Cu (3.49 eV/atom) [40], resulting in a substantially larger expected electromigration performance for CuTi.

## II. PROCEDURE

CuTi and Cu films were deposited onto 20-nm-thick thermal  $SiO_2/Si(001)$  substrates in a ultrahigh vacuum DC magnetron sputtering system with a base pressure of  $10^{-7}$  Pa [41, 42]. The multistep substrate preparation and layer deposition processes are described in more detail in our previous publication [35] and include co-sputtering of 51-mm-diameter Cu (99.999%) and Ti (99.995%) targets in 3 mTorr 99.999% pure Ar using constant powers of 60 and 50 W to achieve stoichiometric CuTi deposition onto substrates which are kept at 350 °C.

X-ray diffraction (XRD) polefigures were acquired with a PANalytical X'pert PRO MPD system using a point source with a polycapillary x-ray lens that provides a quasi-parallel Cu K $\alpha$  beam with a divergence <0.3°. The diffraction angle was kept constant at  $2\theta = 42.13^{\circ}$  to detect the CuTi 012 reflection. Rutherford back scattering (RBS) spectra were obtained in a  $10^{-7}$  Torr chamber using a 2 × 2 mm<sup>2</sup> 2 MeV alpha-particle beam. The backscattered intensity was measured at a scattering angle of 166° and data analysis was done using the SIMNRA simulation software [43].

The scanning electron micrographs were obtained in a VERSA scanning electron microscope (SEM) with a 10 keV primary electron beam and a 6 mm working distance. X-ray

The authors acknowledge funding from the Semiconductor Research Corporation (SRC) and DARPA under task Nos. 3137.19 and 3137.21, the National Science Foundation (NSF) under grant No. 2328906 through the Future of Semiconductors program supported by NSF and industry partners, and from the NY State Empire State Development's Division of

Science, Technology and Innovation (NYSTAR) through Focus Center-NY-RPI Contract C180117.

The authors are with the Department of Materials Science and Engineering, Rensselaer Polytechnic Institute, 110 8th St, Troy, NY 12180, USA. Corresponding author: Daniel Gall; email: galld@rpi.edu

photoelectron spectroscopy (XPS) depth profile plots from the same annealed Cu and CuTi layers were obtained with a PHI 5000 Versaprobe system with a hemispherical analyzer and an 8-channel detector using Al Kα radiation (1486.6 eV) and a 3 keV 2 mA Ar<sup>+</sup> beam incident at 45° relative to the surface normal over a 1 mm<sup>2</sup> area for sputter etching.

Four-point-bend mechanical tests were done on dummy-Si/epoxy/Ti/metal/SiO<sub>2</sub>/Si test structures. More specifically, 50-nm-thick Cu or CuTi metal layers were deposited on 20-nmthick thermal SiO<sub>2</sub>/p-type Si substrates, followed by deposition of 200-nm-thick Ti adhesion layers in the same sputtering system. The Ti/metal/SiO<sub>2</sub>/Si(001) stacks were bonded to dummy Si wafers with epoxy T88 and diced into  $6 \times 30 \text{ mm}$ beams. A 400-um-deep notch was machined into the host Si wafer to initiate the delamination during mechanical testing [44, 45]. Room-temperature time-dependent dielectric breakdown (TDDB) experiments were done on Cu/SiO<sub>2</sub>/Si and CuTi/SiO<sub>2</sub>/Si samples. The top electrodes were 100-µmdiameter 100-nm-thick Cu or CuTi layers that are formed using a lift-off process [26] while the bottom electrodes are 300-nmthick Al layers deposited on the backside of the Si substrate to form ohmic contacts.

# III. RESULTS

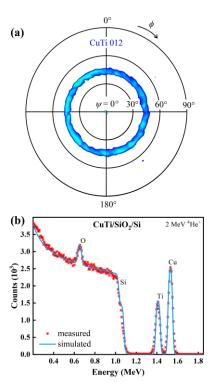

Figure 1 shows representative XRD and RBS results from a 44.3-nm-thick CuTi layer. The XRD polefigure in Fig. 1(a) shows the CuTi 012 reflection as a circularly symmetric ring at a  $\chi = 45 \pm 3^{\circ}$  sample tilt with negligible intensity at other  $\chi$ values. The expected angle between CuTi 012 and 001 planes is 45°. Thus, the polefigure indicates a 001 out-of-plane growth direction with a random in-plane orientation and negligible misoriented grains, consistent with our previous work which indicates a 001 texture for CuTi/SiO<sub>2</sub> growth with a 1.7° rocking curve width [35]. This polycrystalline structure is as expected for the thin film growth on amorphous SiO2, while the crystalline orientation of the underlying Si(001) substate is expected to have no effect on the CuTi growth. The RBS spectrum in Fig. 1(b) shows the measured reflected intensity vs particle energy as red data points and the result from data analysis as blue line. The peaks at 1.41 and 1.53 MeV are due to He reflections at Ti and Cu nuclei in the CuTi layer, the Opeak at 0.65 MeV is from the SiO<sub>2</sub> thermal oxide, and the Si shoulder below 1.1 MeV from the SiO2 layer and the Si substrate. The O-peak shape indicates negligible oxygen impurity in the CuTi layer, as expected for deposition in a system with a 10<sup>-7</sup> Pa base pressure which is estimated to lead to a maximum 0.1% impurity concentration. Quantitative analysis yields 49% Cu and 51% Ti atoms in the layer, confirming a stoichiometric CuTi composition within the  $\pm 2\%$ experimental uncertainty.

Fig. 1. (a) X-ray diffraction pole figure for the CuTi 012 reflection and (b) RBS spectrum from a 44.3-nm-thick CuTi/SiO<sub>2</sub> layer.

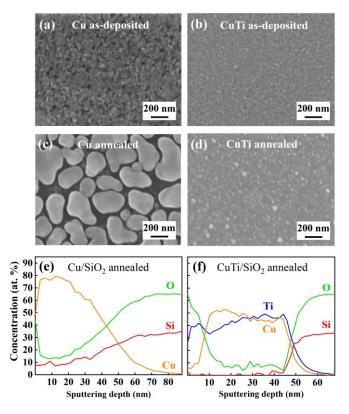

Figures 2(a) and (b) show secondary electron micrographs from as-deposited Cu and CuTi layers with a 40 nm (nominal) and a 44.3 nm (measured) thickness, respectively. Both Cu and CuTi show good surface coverage on the amorphous SiO<sub>2</sub> substrate, with 30-100 nm and 10-30 nm wide surface mounds, respectively. The micrograph from the Cu layer in Fig. 2(a) also shows dark contrast features which may indicate 10-50 nm wide pinholes caused by the poor wettability of Cu on dielectric SiO<sub>2</sub> [30], as previously reported for bare Cu films grown on SiO<sub>2</sub> without liner [46]. In contrast, no evidence for pinholes can be detected in Fig. 2(b) from the CuTi film. Figures 2(c) and (d) are SEM micrographs from the same Cu and CuTi layers but after vacuum (10<sup>-9</sup> torr) annealing at 450 °C for 15 min. The Cu layer exhibits a discontinuous microstructure with large 100-300 nm wide islands, suggesting dewetting of the Cu on SiO<sub>2</sub> during annealing. The corresponding micrograph for CuTi in Fig. 2(d) shows a continuous film with 10-50 nm wide circular surface mounds and no pinholes or cavities, indicating only minor surface morphological changes during annealing of the CuTi layers. Thus, in summary, the SEM micrographs reveal quite dramatic microstructural changes during annealing of the Cu layer but relatively modest changes for CuTi, indicating a considerably higher thermal stability of the CuTi compound. We note that resistivity measurements show an infinite resistance for the annealed Cu layer, confirming the discontinuous microstructure. The CuTi sheet resistance is 14% higher after annealing than for the as-deposited layer, which may be attributed to increased surface roughness, surface oxidation during annealing and/or precipitation of Ti or Cu rich impurity phases. Figures 2(e) and (f) are XPS depth profile plots from the same annealed Cu and CuTi layers, respectively. The profile in (e) shows a Cu signal which decreases nearly linearly from 80 to 0 at.% over a sputter depth of 20 to 70 nm while the O and Si signals simultaneously increase, exhibiting a 2:1 ratio

as expected for SiO<sub>2</sub>. The Si-signal is non-zero prior to sputter etching and remains approximately constant at 8±2 at.% for the first 20 nm of depth. This indicates that the Cu surface coverage is incomplete (80±5 %) for this annealed layer so that the SiO<sub>2</sub> substrate can be detected, consistent with the micrograph in Fig. 2(c). In contrast, the profile in Fig. 2(f) shows no detectable Si signal until a sputter depth of 43 nm is reached, indicating complete coverage of the SiO<sub>2</sub> by the CuTi layer. Further sputtering leads to a fast transition from Cu and Ti to Si and O within 3 sputter cycles, indicating a sharp interface between the CuTi film and the SiO<sub>2</sub> substrate with negligible intermixing and/or Cu diffusion into the SiO2. The stark differences in the two depth profiles confirm the much better wetting of SiO<sub>2</sub> by CuTi than by Cu. Thus, CuTi is stable against dewetting in direct contact with the dielectric during typical BEOL thermal treatment processes, which is promising when considering its promise as a barrier-free interconnect metal.

Fig. 2. SEM micrograph of as-deposited (a) Cu/SiO<sub>2</sub> and (b) CuTi/SiO<sub>2</sub> thin films. (c) and (d) show the corresponding Cu and CuTi micrographs after vacuum annealing at 450 °C for 15 min, and (e) and (f) are compositional XPS depths profiles of the annealed films.

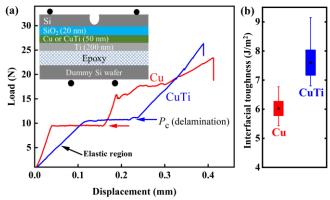

Figure 3 shows the results from four-point-bend mechanical tests which are used to quantify the Cu-SiO<sub>2</sub> and CuTi-SiO<sub>2</sub> interface toughness G, also referred to as the interface debonding energy [47]. The plot in Fig. 3(a) shows typical load-displacement curves from a Cu and a CuTi sample, obtained using a slow strain rate of 0.01  $\mu$ m/s. A steady-state interfacial delamination occurs in the dummy-Si/epoxy/Ti/metal/SiO<sub>2</sub>/Si test structures [illustrated in Fig. 3(a)] when the crack from the notch tip reaches the weakest interface and spreads along the interface, forming a plateau in the load-displacement curve at a critical load  $P_c$  [44, 48]. The higher  $P_c$  for CuTi indicates a higher critical load for debonding of CuTi from SiO<sub>2</sub> than for the Cu-SiO<sub>2</sub> interface. The corresponding interface debonding

energy is obtained using  $G = K(1-v^2)P_c^2/E$ , where E = 190 GPa and v = 0.28 are the elastic modulus and Poisson's ratio of the Si substrate, and  $K = 21L^2/16b^2h^3$  is a geometric factor where L is the spacing between inner and outer loading line, b is the beam width and h is the half thickness [49-51]. Fig. 3(b) shows the resulting interfacial toughness for the Cu-SiO<sub>2</sub> and CuTi-SiO<sub>2</sub> interfaces. The plotted solid black squares indicate the average values from five delamination experiments, the boxes denote the standard deviation and the whiskers indicate the minimum and maximum from the five measurements. The CuTi-SiO<sub>2</sub> interfacial debonding energy of 7.5 J/m<sup>2</sup> is 25% higher than the measured 6.0 J/m<sup>2</sup> for the Cu-SiO<sub>2</sub> interface. The better interfacial adhesion is expected to correspond to a higher electromigration (EM) performance [52]. Thus, the higher interfacial toughness of CuTi-SiO2 suggests good EM resistance of possible liner-free CuTi interconnects.

Fig. 3. (a) Representative load-displacement curves and (b)  $\text{Cu-SiO}_2$  and  $\text{CuTi-SiO}_2$  interfacial toughness determined from critical load  $P_c$  delamination plateaus during 4-point bend tests on test structures shown in the inset of (a).

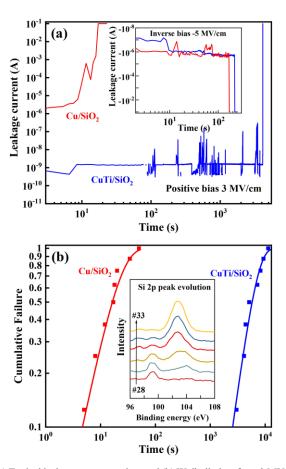

Figure 4 shows the results from room-temperature TDDB experiments. Typical leakage current curves are plotted in Fig. 4(a) as a function of time for a Cu/SiO<sub>2</sub>/Si and a CuTi/SiO<sub>2</sub>/Si sample, using a positive bias of 6 V. Nearly the entire potential drop occurs across the 20-nm-thick SiO2, corresponding to 3 MV/cm within the SiO<sub>2</sub> with negligible potential drop in the Cu or CuTi. The Cu/SiO<sub>2</sub> sample fails after ~10 s, while the failure for CuTi/SiO<sub>2</sub> occurs after 4000 s. This suggests that the ion drift into the SiO<sub>2</sub> is 400 times slower for the CuTi than the Cu layer, indicating a strong advantage of CuTi over Cu with regards to TDDB performance. The inset in Fig. 4(a) shows the leakage current for an inverse bias of -5 MV/cm. Inverse bias involves no ion drift into the oxide such that these experiments reveal the intrinsic breakdown of SiO<sub>2</sub>, independent of if the top electrode is Cu or CuTi. Both samples exhibit a similar time to failure of ~200 s, confirming that the breakdown is independent of the metal layer composition, as expected for an inverse bias, and also indicating a consistent dielectric quality. We note that positive-bias experiments with this higher 5 MV/cm field lead to fast failure within a few seconds as metal ions quickly penetrate into and through the oxide and accumulate to reach a threshold level that causes nearly immediate dielectric breakdown [53]. Correspondingly, we use a smaller positive bias of 3 MV/cm for our statistical TDDB measurements and analyses and consider breakdown if the measured current reaches 10<sup>-1</sup> A. This value is relatively high in comparison to other studies [53, 54] and is chosen because of our relatively large electrode area of  $7.9 \times 10^3 \, \mu m^2$ .

Figure 4(b) is a Weibull distribution plot showing the cumulative failure time from eight Cu and CuTi electrodes during 3 MV/cm TDDB tests. This quantitative analysis follows the most common approach to evaluate TDDB tests [53, 55-57]. The fitted scale parameters yield statistical failure times of 21 s for Cu and 6800 s for CuTi. The failure time for CuTi is over 300-times longer, indicating a superior interdiffusion reliability on bare SiO<sub>2</sub> dielectric for CuTi in comparison to Cu. The data fitting also yields the shape parameter  $\beta$  in the Weibull distributions of 1.5 and 2.3 for Cu and CuTi, respectively, suggesting a higher defect concentration in the SiO<sub>2</sub> in contact with Cu. It is generally believed that Cu ions that diffuse into SiO<sub>2</sub> bond to two-coordinated bridging oxygen atoms to form a shallow energy level in the SiO<sub>2</sub> band gap, allowing Poole-Frenkel type conduction [58]. Thus, the SiO<sub>2</sub> in direct contact with Cu (in comparison to CuTi) exhibits a higher localized defect concentration which is due to the interaction between migrated Cu ions and SiO<sub>2</sub>. The resulting higher interdiffusion reliability of CuTi on SiO<sub>2</sub> is attributed to the higher cohesive energy which facilitates superior stability of the interconnect material. Specifically, a high cohesive energy has been related to a high stability under thermoelectric stress [59] and a high formation energy for vacancies, resulting in slow self-diffusion kinetics [16]. Therefore, the rate for Cu atoms leaving the CuTi layers is expected to be considerably lower than for pure Cu, yielding the observed improved TDDB stability.

The inset in Fig. 4(b) provides some additional information about the physical reasons for the CuTi-SiO<sub>2</sub> interdiffusion reliability. It is a plot of the XPS Si 2p peak evolution at the CuTi-SiO<sub>2</sub> interface region corresponding to sputter cycles #28 - 33. The peak for cycles #31-33 is at a binding energy of 102.9 eV, close to the expected 103.3 eV for SiO<sub>2</sub>. However, it shifts left to lower binding energies near the CuTi layer for cycles #28-30, indicating a reduction of SiO<sub>2</sub>. This indicates the formation of an interfacial Ti oxide layer at the SiO2-CuTi interface. This interfacial oxide is expected to act as an intrinsic diffusion barrier layer to kinetically retard the diffusion between interconnect and dielectric, resulting in the measured enhanced interdiffusion reliability. The interfacial Ti oxide may also enhance interfacial adhesion [26], but we note that the plotted binding energy is simply a measure of the bond ionicity and cannot directly quantify the strength of the atomic bonds at the interface. We also note that XPS depth profiles after annealing exhibit similar characteristics, indicating that the interfacial oxide is self-limiting and is therefore expected to form a continuous layer with a uniform thickness, facilitating the stability of the CuTi-SiO<sub>2</sub> interface. Thus, the reliability of CuTi compensates for its larger resistivity scaling [35] and yields possible benefits for the future interconnects.

Fig. 4. (a) Typical leakage current vs time and (b) Weibull plots from 3 MV/cm TDDB tests of 20-nm-SiO<sub>2</sub> with Cu and CuTi top electrodes. The inset in (a) shows results from tests with -5 MV/cm inverse bias. The inset in (b) shows the XPS Si 2p peak near the CuTi-SiO<sub>2</sub> interface during a depth profile experiment for sputter cycles #28-33.

#### IV. CONCLUSIONS

CuTi layers on SiO<sub>2</sub> exhibit higher thermal stability against dewetting than Cu layers during vacuum annealing at 450 °C. They also exhibit negligible intermixing with SiO<sub>2</sub> and a 25% higher interfacial toughness, suggesting higher resistance against electromigration than Cu. CuTi-SiO<sub>2</sub> exhibits a 300-times higher failure time than Cu-SiO<sub>2</sub> during TDDB tests with 3 MV/cm. The higher stability of the CuTi-SiO<sub>2</sub> interface is attributed to a self-limiting interfacial Ti-oxide layer and indicates the potential for barrier-free CuTi metallization.

### References

- S. Salahuddin, K. Ni, and S. Datta, "The era of hyper-scaling in electronics," *Nat. Electron.*, vol. 1, no. 8, pp. 442-450, Aug. 2018, doi: 10.1038/s41928-018-0117-x.

- [2] D. K. Ferry, "Nanowires in Nanoelectronics," *Science*, vol. 319, no. 5863, pp. 579-580, Feb. 2008, doi: 10.1126/science.1154446.

- [3] D. E. Shim, V. Huang, X. Chen, S. K. Gupta, and A. Naeemi, "A Comprehensive Modeling Platform for Interconnect Technologies," *IEEE Trans. Electron Devices*, vol. 70, no. 5, pp. 2594-2599, May 2023, doi: 10.1109/TED.2023.3261828.

- [4] T. Zhou and D. Gall, "Resistivity scaling due to electron surface scattering in thin metal layers," *Phys. Rev. B*, vol. 97, no. 16, p. 165406, Apr. 2018, doi: 10.1103/PhysRevB.97.165406.

- [5] M. Zhang and D. Gall, "Resistivity size effect in epitaxial VNi2 layers," J. Appl. Phys., vol. 134, no. 10, p. 105302, Sep. 2023, doi: 10.1063/5.0160462.

- [6] E. Milosevic, P. Zheng, and D. Gall, "Electron scattering at epitaxial Ni (001) surfaces," *IEEE Trans. Electron Devices*, vol. 66, no. 10, pp. 4326-4330, Aug. 2019, doi: 10.1109/TED.2019.2934636.

- [7] E. Milosevic and D. Gall, "Copper Interconnects: Surface State Engineering to Facilitate Specular Electron Scattering," *IEEE Trans. Electron Devices*, vol. 66, no. 6, p. 2692, Jun. 2019, doi: 10.1109/TED.2019.2910500.

- [8] E. Milosevic, S. Kerdsongpanya, M. E. McGahay, B. Wang, and D. Gall, "The Resistivity Size Effect in Epitaxial Nb (001) and Nb (011) Layers," *IEEE Trans. Electron Devices*, vol. 66, no. 8, pp. 3473-3478, Jul. 2019, doi: 10.1109/TED.2019.2924312.

- [9] K. Fuchs, "The conductivity of thin metallic films according to the electron theory of metals," in *Mathematical Proceedings of the Cambridge Philosophical Society*, vol. 34, no. 1 1938, pp. 100-108, doi: 10.1017/S0305004100019952.

- [10] A. Mayadas and M. Shatzkes, "Electrical-resistivity model for polycrystalline films: the case of arbitrary reflection at external surfaces," *Phys. Rev. B*, vol. 1, no. 4, p. 1382, Feb. 1970, doi: 10.1103/PhysRevB.1.1382.

- [11] E. H. Sondheimer, "The mean free path of electrons in metals," Adv. Phys., vol. 1, no. 1, pp. 1-42, 1952, doi: 10.1080/00018730110102187.

- [12] M. César, D. Gall, and H. Guo, "Reducing Grain-Boundary Resistivity of Copper Nanowires by Doping," *Phys. Rev. Appl.*, vol. 5, no. 5, p. 054018, May 2016, doi: 10.1103/PhysRevApplied.5.054018.

- [13] T. Zhou, A. Jog, and D. Gall, "First-principles prediction of electron grain boundary scattering in fcc metals," *Appl. Phys. Lett.*, vol. 120, no. 24, p. 241603, Jun. 2022, doi: 10.1063/5.0098822.

- [14] D. Gall, J. J. Cha, Z. Chen, H.-J. Han, C. Hinkle, J. A. Robinson, R. Sundararaman, and R. Torsi, "Materials for interconnects," MRS Bulletin, vol. 46, no. 10, pp. 959-966, Oct. 2021, doi: 10.1557/s43577-021-00192-3

- [15] D. Gall, "The search for the most conductive metal for narrow interconnect lines," J. Appl. Phys., vol. 127, no. 5, p. 050901, Feb. 2020, doi: 10.1063/1.5133671.

- [16] C. Adelmann, L. G. Wen, A. P. Peter, Y. K. Siew, K. Croes, J. Swerts, M. Popovici, K. Sankaran, G. Pourtois, and S. Van Elshocht, "Alternative metals for advanced interconnects," in 2014 IEEE International Interconnect Technology Conference (IITC), Jun. 2014, pp. 173-176, doi: 10.1109/IITC.2014.6831863.

- [17] O. V. Pedreira, K. Croes, A. Leśniewska, C. Wu, M. Van Der Veen, J. De Messemaeker, K. Vandersmissen, N. Jourdan, L. Wen, and C. Adelmann, "Reliability study on cobalt and ruthenium as alternative metals for advanced interconnects," in 2017 IEEE International Reliability Physics Symposium (IRPS), Jun. 2017, pp. 6B-2.1-6B-2.8, doi: 10.1109/IRPS.2017.7936340.

- [18] E. Milosevic, S. Kerdsongpanya, A. Zangiabadi, K. Barmak, K. R. Coffey, and D. Gall, "Resistivity size effect in epitaxial Ru (0001) layers," J. Appl. Phys., vol. 124, no. 16, p. 165105, Oct. 2018, doi: 10.1063/1.5046430.

- [19] E. Milosevic, S. Kerdsongpanya, M. E. McGahay, A. Zangiabadi, K. Barmak, and D. Gall, "Resistivity scaling and electron surface scattering in epitaxial Co (0001) layers," *J. Appl. Phys.*, vol. 125, no. 24, p. 245105, Jun. 2019, doi: 10.1063/1.5086458.

- [20] A. Jog and D. Gall, "Resistivity size effect in epitaxial iridium layers," J. Appl. Phys., vol. 130, no. 11, p. 115103, Sep. 2021, doi: 10.1063/5.0060845.

- [21] A. Jog, T. Zhou, and D. Gall, "Resistivity Size Effect in Epitaxial Rh (001) and Rh (111) Layers," *IEEE Trans. Electron Devices*, vol. 68, no. 1, pp. 257-263, Jan. 2021, doi: 10.1109/TED.2020.3040202.

- [22] P. Zheng and D. Gall, "The anisotropic size effect of the electrical resistivity of metal thin films: Tungsten," *J. Appl. Phys.*, vol. 122, no. 13, p. 135301, Oct. 2017, doi: 10.1063/1.5004118.

- [23] A. Jog, P. Zheng, T. Zhou, and D. Gall, "Anisotropic Resistivity Size Effect in Epitaxial Mo(001) and Mo(011) Layers," *Nanomaterials*, vol. 13, no. 6, p. 957, Mar. 2023, doi: 10.3390/nano13060957.

- [24] M. Zhang and D. Gall, "Resistivity Scaling in Epitaxial CuAl 2 (001) Layers," *IEEE Trans. Electron Devices*, vol. 69, no. 9, pp. 5110-5115, Sep. 2022, doi: 10.1109/TED.2022.3188952.

- [25] J.-P. Soulié, Z. Tőkei, J. Swerts, and C. Adelmann, "Improved resistivity of NiAl thin films at low temperature for advanced interconnect metallization," in 2022 IEEE International Interconnect Technology Conference (IITC), Jun. 2022, pp. 73-75, doi: 10.1109/IITC52079.2022.9881310.

- [26] L. Chen, D. Ando, Y. Sutou, D. Gall, and J. Koike, "NiAl as a potential material for liner-and barrier-free interconnect in ultrasmall technology

- node," Appl. Phys. Lett., vol. 113, no. 18, p. 183503, Oct. 2018, doi: 10.1063/1.5049620.

- [27] J.-P. Soulié, Z. Tőkei, J. Swerts, and C. Adelmann, "Aluminide intermetallics for advanced interconnect metallization: thin film studies," in 2021 IEEE International Interconnect Technology Conference (IITC), Jul. 2021, pp. 1-3, doi: 10.1109/IITC51362.2021.9537441.

- [28] L. Chen, Q. Chen, D. Ando, Y. Sutou, M. Kubo, and J. Koike, "Potential of low-resistivity Cu2Mg for highly scaled interconnects and its challenges," *Appl. Surf. Sci.*, vol. 537, p. 148035, Jan. 2021, doi: 10.1016/j.apsusc.2020.148035.

- [29] M. Zhang, S. Kumar, R. Sundararaman, and D. Gall, "Resistivity scaling in epitaxial MAX-phase Ti4SiC3(0001) layers," *J. Appl. Phys.*, vol. 130, no. 3, p. 034302, Jul. 2021, doi: 10.1063/5.0054542.

- [30] H. Kim, T. Koseki, T. Ohba, T. Ohta, Y. Kojima, H. Sato, and Y. Shimogaki, "Cu Wettability and Diffusion Barrier Property of Ru Thin Film for Cu Metallization," *J. Electrochem. Soc.*, vol. 152, no. 8, p. G594, Jun. 2005, doi: 10.1149/1.1939353.

- [31] H. Kim, C. Detavenier, O. van der Straten, S. M. Rossnagel, A. J. Kellock, and D. G. Park, "Robust TaNx diffusion barrier for Cu-interconnect technology with subnanometer thickness by metal-organic plasma-enhanced atomic layer deposition," *J. Appl. Phys.*, vol. 98, no. 1, p. 014308, Jul. 2005, doi: 10.1063/1.1935761.

- [32] P. Zheng, B. D. Ozsdolay, and D. Gall, "Epitaxial growth of tungsten layers on MgO (001)," J. Vac. Sci. Technol. A, vol. 33, no. 6, p. 061505, 2015, doi: 10.1116/1.4928409.

- [33] E. Milosevic and D. Gall, "Electron scattering at Co (0001) surfaces: Effects of Ti and TiN capping layers," AIP Adv., vol. 10, no. 5, p. 055213, 2020, doi: 10.1063/1.5145327.

- [34] E. Milosevic, S. Kerdsongpanya, and D. Gall, "The Resistivity Size Effect in Epitaxial Ru (0001) and Co (0001) Layers," in 2018 IEEE Nanotechnology Symposium (ANTS) 2018, pp. 1-5, doi: 10.1109/NANOTECH.2018.8653560.

- [35] M. Zhang, S. Kumar, R. Sundararaman, and D. Gall, "Resistivity scaling in CuTi determined from transport measurements and first-principles simulations," *J. Appl. Phys.*, vol. 133, no. 4, p. 045102, Jan. 2023, doi: 10.1063/5.0135132.

- [36] C. K. Hu, J. Kelly, H. Huang, K. Motoyama, H. Shobha, Y. Ostrovski, J. H. C. Chen, R. Patlolla, B. Peethala, P. Adusumilli, T. Spooner, R. Quon, L. M. Gignac, C. Breslin, G. Lian, M. Ali, J. Benedict, X. S. Lin, S. Smith, V. Kamineni, X. Zhang, F. Mont, S. Siddiqui, and F. Baumann, "Future on-chip interconnect metallization and electromigration," in 2018 IEEE International Reliability Physics Symposium (IRPS) 2018, pp. 4F.1-1-4F.1-6, doi: 10.1109/IRPS.2018.8353597.

- [37] C.-K. Hu, J. Kelly, J. H. Chen, H. Huang, Y. Ostrovski, R. Patlolla, B. Peethala, P. Adusumilli, T. Spooner, and L. Gignac, "Electromigration and resistivity in on-chip Cu, Co and Ru damascene nanowires," in 2017 IEEE International Interconnect Technology Conference (IITC) 2017, pp. 1-3, doi: 10.1109/IITC-AMC.2017.7968977.

- [38] A. J. V. I. LeClaire, Progress in Metal Physics. 1949, p. 306.

- [39] K. Sankaran, K. Moors, Z. Tőkei, C. Adelmann, and G. Pourtois, "Ab initio screening of metallic MAX ceramics for advanced interconnect applications," *Phys. Rev. Mater.*, vol. 5, no. 5, p. 056002, 2021, doi: 10.1103/PhysRevMaterials.5.056002.

- [40] K. Sankaran, S. Clima, M. Mees, and G. Pourtois, "Exploring Alternative Metals to Cu and W for Interconnects Applications Using Automated First-Principles Simulations," ECS Journal of Solid State Science and Technology, vol. 4, no. 1, p. N3127, 2015, doi: 10.1149/2.0181501jss.

- [41] B. Wang, M. Zhang, V. Adhikari, P. Fang, S. V. Khare, and D. Gall, "Bandgap and strain engineering in epitaxial rocksalt structure (Ti0.5Mg0.5)1-xAlxN(001) semiconductors," *J. Mater. Chem. C*, 10.1039/D0TC03598J vol. 8, no. 36, pp. 12677-12688, Aug. 2020, doi: 10.1039/D0TC03598J.

- [42] P. Fang, B. Wang, and D. Gall, "Epitaxial MoCx: Competition between cubic δ-MoCy(111) and hexagonal β-Mo2C(0001)," Surf. Coat. Technol., vol. 420, p. 127333, Aug. 2021, doi: 10.1016/j.surfcoat.2021.127333.

- [43] M. Mayer, "Improved physics in SIMNRA 7," *Nucl. Instrum. Methods Phys. Res. B*, vol. 332, pp. 176-180, Aug. 2014, doi: 10.1016/j.nimb.2014.02.056.

- [44] P. K. Chow, Y. Cardona Quintero, P. O'Brien, P. Hubert Mutin, M. Lane, R. Ramprasad, and G. Ramanath, "Gold-titania interface toughening and thermal conductance enhancement using an organophosphonate nanolayer," *Appl. Phys. Lett.*, vol. 102, no. 20, p. 201605, May 2013, doi: 10.1063/1.4807436.

- [45] D. D. Gandhi, M. Lane, Y. Zhou, A. P. Singh, S. Nayak, U. Tisch, M. Eizenberg, and G. Ramanath, "Annealing-induced interfacial toughening

- using a molecular nanolayer," *Nature*, vol. 447, no. 7142, pp. 299-302, May 2007, doi: 10.1038/nature05826.

- [46] E. Liniger, L. Gignac, C. K. Hu, and S. Kaldor, "In situ study of void growth kinetics in electroplated Cu lines," *J. Appl. Phys.*, vol. 92, no. 4, pp. 1803-1810, Jul. 2002, doi: 10.1063/1.1492871.

- [47] A. Jain, B. Singh, S. Garg, N. Ravishankar, M. Lane, and G. Ramanath, "Atomistic fracture energy partitioning at a metal-ceramic interface using a nanomolecular monolayer," *Phys. Rev. B*, vol. 83, no. 3, p. 035412, Jan. 2011, doi: 10.1103/PhysRevB.83.035412.

- [48] M. Kwan, M. Braccini, M. W. Lane, and G. Ramanath, "Frequency-tunable toughening in a polymer-metal-ceramic stack using an interfacial molecular nanolayer," *Nat. Commun.*, vol. 9, no. 1, p. 5249, Dec. 2018, doi: 10.1038/s41467-018-07614-y.

- [49] R. H. Dauskardt, M. Lane, Q. Ma, and N. Krishna, "Adhesion and debonding of multi-layer thin film structures," *Eng. Fract. Mech.*, vol. 61, no. 1, pp. 141-162, Aug. 1998, doi: 10.1016/S0013-7944(98)00052-6.

- [50] G. Ramanath, G. Cui, P. G. Ganesan, X. Guo, A. V. Ellis, M. Stukowski, K. Vijayamohanan, P. Doppelt, and M. Lane, "Self-assembled subnanolayers as interfacial adhesion enhancers and diffusion barriers for integrated circuits," *Appl. Phys. Lett.*, vol. 83, no. 2, pp. 383-385, Jul. 2003, doi: 10.1063/1.1591232.

- [51] M. A. Hopcroft, W. D. Nix, and T. W. Kenny, "What is the Young's Modulus of Silicon?," *J. Microelectromechanical Syst.*, vol. 19, no. 2, pp. 229-238, Apr. 2010, doi: 10.1109/JMEMS.2009.2039697.

- [52] M. W. Lane, E. G. Liniger, and J. R. Lloyd, "Relationship between interfacial adhesion and electromigration in Cu metallization," *J. Appl. Phys.*, vol. 93, no. 3, pp. 1417-1421, Feb. 2003, doi: 10.1063/1.1532942.

- [53] L. Chen, D. Ando, Y. Sutou, S. Yokogawa, and J. Koike, "Liner- and barrier-free NiAl metallization: A perspective from TDDB reliability and interface status," *Appl. Surf. Sci.*, vol. 497, p. 143810, Dec. 2019, doi: 10.1016/j.apsusc.2019.143810.

- [54] L. Zhao, M. Lofrano, K. Croes, E. Van Besien, Z. Tőkei, C. J. Wilson, R. Degraeve, T. Kauerauf, G. P. Beyer, and C. Claeys, "Evaluations of intrinsic time dependent dielectric breakdown of dielectric copper diffusion barriers," *Thin Solid Films*, vol. 520, no. 1, pp. 662-666, Oct. 2011, doi: 10.1016/j.tsf.2011.08.073.

- [55] K. Park, K. Park, S. Im, S. Hong, K. Son, and J. Jeon, "Development of an Advanced TDDB Analysis Model for Temperature Dependency," *Electronics*, vol. 8, no. 9. doi: 10.3390/electronics8090942

- [56] M. N. Chang, Y. H. Lee, S. Y. Lee, K. Joshi, C. C. Ko, C. C. Chiu, and K. Wu, "A new insight into BEOL TDDB lifetime model for advanced technology scaling," in 2015 IEEE International Electron Devices Meeting (IEDM) 2015, pp. 7.4.1-7.4.4, doi: 10.1109/IEDM.2015.7409647.

- [57] P. J. Roussel, A. Chasin, S. Demuynck, N. Horiguchi, D. Linten, and A. Mocuta, "New methodology for modelling MOL TDDB coping with variability," in 2018 IEEE International Reliability Physics Symposium (IRPS) 2018, pp. 3A.5-1-3A.5-6, doi: 10.1109/IRPS.2018.8353555.

- [58] H. Miyazaki, D. Kodama, and N. Suzumura, "Phenomenological classification of stress-induced leakage current and time-dependent dielectric breakdown mechanism," *J. Appl. Phys.*, vol. 106, no. 10, p. 104103, Nov. 2009, doi: 10.1063/1.3259386.

- [59] S. Dutta, S. Beyne, A. Gupta, S. Kundu, S. Van Elshocht, H. Bender, G. Jamieson, W. Vandervorst, J. Bömmels, and C. J. Wilson, "Sub-100 nm 2 cobalt interconnects," *IEEE Electron Device Lett.*, vol. 39, no. 5, pp. 731-734, 2018, doi: 10.1109/LED.2018.2821923.