#### **PAPER • OPEN ACCESS**

# Power efficient MoS<sub>2</sub> synaptic devices based on Maxwell–Wagner interfacial charging in binary oxides

To cite this article: Jingyi Zou et al 2024 2D Mater. 11 015009

View the article online for updates and enhancements.

# You may also like

- Emerging memory technologies for neuromorphic computing Chul-Heung Kim, Suhwan Lim, Sung Yun Woo et al.

- Synaptic electronics: materials, devices and applications Duygu Kuzum, Shimeng Yu and H-S Philip Wong

- Two-dimensional materials for artificial synapses: toward a practical application I-Ting Wang, Chih-Cheng Chang, Yen-Yu Chen et al.

# **2D** Materials

#### **OPEN ACCESS**

#### RECEIVED

15 June 2023

#### REVISED

14 September 2023

## ACCEPTED FOR PUBLICATION

9 October 2023

#### PUBLISHED

3 November 2023

Original content from this work may be used under the terms of the Creative Commons Attribution 4.0 licence.

Any further distribution of this work must maintain attribution to the author(s) and the title of the work, journal citation and DOI.

#### **PAPER**

# Power efficient MoS<sub>2</sub> synaptic devices based on Maxwell–Wagner interfacial charging in binary oxides

Jingyi Zou<sup>1</sup>, Sen Lin<sup>1</sup>, Tianyi Huang<sup>2</sup>, Hefei Liu<sup>3</sup>, Yushuang Liu<sup>1</sup>, Yibai Zhong<sup>2</sup>, Yuxuan Cosmi Lin<sup>3</sup>, Han Wang<sup>4</sup>, Sheng Shen<sup>2</sup>, Min Xu<sup>5</sup> and Xu Zhang<sup>1,\*</sup>

- Department of Electrical and Computer Engineering, Carnegie Mellon University, Pittsburgh, PA, United States of America

- Department of Mechanical Engineering, Carnegie Mellon University, Pittsburgh, PA, United States of America

- <sup>3</sup> Department of Materials Science and Engineering, Texas A&M University, College Station, TX, United States of America

- <sup>4</sup> Ming Hsieh Department of Electrical and Computer Engineering, University of Southern California, Los Angeles, United States of America

- Computational Biology Department, Carnegie Mellon University, Pittsburgh, PA, United States of America

- \* Author to whom any correspondence should be addressed.

E-mail: xuzh@cmu.edu

**Keywords:** 2D materials, neuromorphic computing, interfacial charge, synaptic devices, low power consumption Supplementary material for this article is available online

#### Abstract

Synaptic devices with tunable weight hold great promise in enabling non-von Neumann architecture for energy efficient computing. However, conventional metal-insulator-metal based two-terminal memristors share the same physical channel for both programming and reading, therefore the programming power consumption is dependent on the synaptic resistance states and can be particularly high when the memristor is in the low resistance states. Three terminal synaptic transistors, on the other hand, allow synchronous programming and reading and have been shown to possess excellent reliability. Here we present a binary oxide based three-terminal MoS<sub>2</sub> synaptic device, in which the channel conductance can be modulated by interfacial charges generated at the oxide interface driven by Maxwell-Wagner instability. The binary oxide stack serves both as an interfacial charge host and gate dielectrics. Both excitatory and inhibitory behaviors are experimentally realized, and the presynaptic potential polarity can be effectively controlled by engineering the oxide stacking sequence, which is a unique feature compared with existing charge-trap based synaptic devices and provides a new tuning knob for controlling synaptic device characteristics. By adopting a three-terminal transistor structure, the programming channel and reading channel are physically separated and the programming power consumption can be kept constantly low ( $\sim$ 50 pW) across a wide dynamic range of 10<sup>5</sup>. This work demonstrates a complementary metal oxide semiconductor compatible approach to build power efficient synaptic devices for artificial intelligence applications.

#### 1. Introduction

Conventional von Neumann computing paradigm is becoming increasingly inefficient in terms of speed and energy for data-intensive artificial intelligence applications, due to the physical separation of logic units and memory units [1–3]. Biological neural networks with an extreme-parallel architecture have constantly inspired new computing hardware, such as artificial neuron network (ANN), for in-memory computing [4–9]. Electrical signals in biological neurons originate from the exchange of charges across

the plasma membrane through ion channels [10, 11]. The neuron membrane potentials can be effectively modulated by a transmembrane influx of ionic charges [12, 13], such as Na<sup>+</sup> and K<sup>+</sup>. The powerful computational capabilities of neurons are achieved through controllable movement of these transmembrane charges. On the other hand, the most prevalent device structure to implement ANN is a two-terminal filament based memristor, typically made of metal-insulator-metal (MIM) structures [6, 14–23]. Anodic oxides [22, 24–33], (e.g. HfO<sub>2</sub>, TiO<sub>2</sub>, Ta<sub>2</sub>O<sub>5</sub>, MoO, WO, NiO, etc) have been widely exploited as

resistive switching media due to their good stability, retention and endurance performance. As atomically precise materials, a wealth of 2D materials have also been extensively studied as resistive switching medium to build memristors [34-47], including hexagonal boron nitride [35, 45], transition metal dichalcogenides [37, 48, 49], MXenes [39, 40], transition metal carbides [41, 50], and nitrides [51], among many others. These MIM memristors operate in different mechanisms than their biological counterparts, i.e. creation and rupture of conductive filaments [22]. Their synaptic weight is associated with the conductivity of two-terminal MIM channels, which can be continuously modulated by controlling the number of conductive filaments. The two-terminal design allows a crossbar array structure with compact footprint and cost-effectiveness [52]. However, the filament based memristor design is also embodied with limitations. Due to their two-terminal design, the programming and reading processes cannot be done simultaneously. This fails to faithfully emulate a natural synaptic response and adds to the complexity in the peripheral circuitry to control and coordinate learning and readout [30, 52]. In addition, in a two-terminal memristor, its writing power strongly depends on the channel conductance and can be quite high when the MIM channel is in the low resistance state (LRS) [6, 52]. To address these challenges, three-terminal synaptic transistors have been proposed and investigated. For instance, electrochemical 'iontronic' transistors use movable alkali metal ions to transport through a gel electrolyte for channel gating and to emulate biological synapses [53–55]. However, this approach is not complementary metal oxide semiconductor (CMOS) compatible due to the use of alkali metal ions. Being atomically thin, 2D semiconductors provide an excellent solidstate platform to develop synaptic transistors for neuromorphic applications [47, 56]. So far, researchers have mainly relied on the charge traps near 2D material surface or bulk trap states inside dielectric insulators to modulate the 2D channel conductivity [29, 57–60]. However, these charge traps are essentially random and difficult to control in terms of their location and polarity, which in turn limit critical device characteristics such as dynamic range of synaptic weight change and power consumption, etc.

Here we exploit the interfacial charges in a binary oxide ( $AlO_x/SiO_x$ ) structure driven by Maxwell-Wagner instability to demonstrate an interfacial charge gated synaptic (ICGS) device, which adopts a three-terminal structure and uses  $MoS_2$  as the channel material. Maxwell-Wagner instability is a well-studied mechanism of interfacial charge trapping in silicon CMOS devices with binary oxides as dielectrics [61–63]. Unlike the filament-based two terminal structure, we adopt a three terminal structure to decouple the writing channel from the resistive switching channel (figure 1(a)), which allows a

constantly low writing power ( $\sim$ 50 pW) as the MoS<sub>2</sub> channel conductance. The channel conductance represents the synaptic weight of the artificial synapse and varies across five orders of magnitude. The binary oxide stack serves both as an interfacial charge host and gate dielectric. Gate voltage pulses, playing a similar role as the pre-synaptic action potentials, can effectively control the polarity and number of interfacial charges. Since the MoS<sub>2</sub> channel is atomically thin, the induced interfacial charges hold tight electrostatic control over the MoS<sub>2</sub> surface potential and result in synaptic weight adjustment over a wide dynamic range of 10<sup>5</sup>. Control experiments confirm that the large tunability contributes from the interfacial trap states between binary oxides, instead of bulk trap states inside individual oxide layers. Importantly, we experimentally demonstrate that the excitatory and inhibitory polarity can be effectively switched by changing the binary oxide stacking sequence, which is a key feature of Maxwell-Wagner instability driven interfacial charging effect [61, 62, 64]. By controlling the amount and polarity of interfacial charges, the surface potential of the MoS<sub>2</sub> channel respond sensitively and results in synaptic weight adjustment, emulating the change of post-synaptic membrane potential through the bonding of neurotransmitters [13, 65]. Our approach presents a CMOS compatible method to build biorealistic memristors with ultralow power consumption.

## 2. Results and discussion

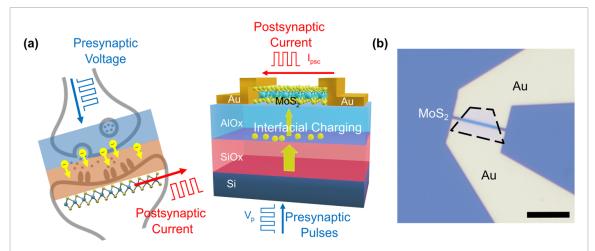

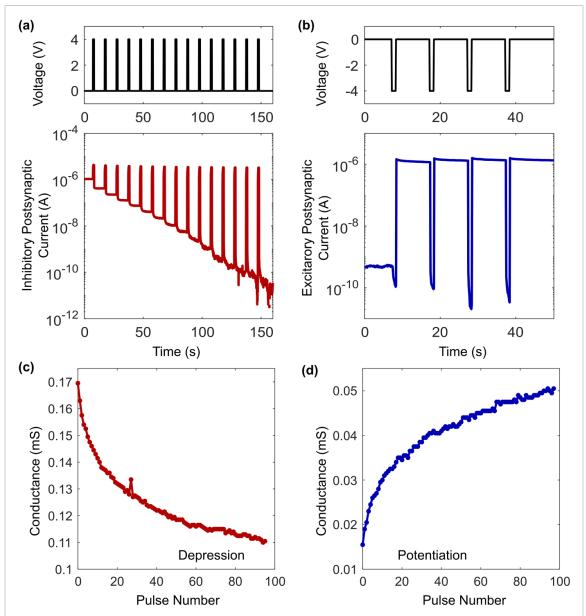

A binary oxide stack (10 nm  $AlO_x/10$  nm  $SiO_x$ ) was sequentially deposited on top of a doped Si substrate by atomic layer deposition (ALD) (figure 1(a)). The channel areas of the synaptic device were defined by electron beam lithography (EBL) using few-layer MoS<sub>2</sub> as the channel material (figure 1(b)). Details can be found in the section 4. We fabricated a dozen of ICGS devices with a channel length of 0.5  $\mu$ m and channel width ranging from 5 to 10  $\mu$ m. The optical microscopy image of a typical MoS<sub>2</sub> ICGS device is shown in figure 1(b). A train of pre-synaptic voltage pulses with an amplitude of 4 V and duration of 1 s is applied to the backgate. The post-synaptic current flowing through the MoS<sub>2</sub> channel is monitored during the process with a 10 mV drain bias (figure 1(a)). The experimental results show that positive pulses lead to effective depression (figure 2(a)). MoS<sub>2</sub> ICGS devices are selected with an initial channel current of  $\sim 1 \mu A$  under zero gate bias. When a positive pulse (amplitude: +4 V; duration: 1 s) is applied to the backgate terminal, the channel current decreases during the pulse period. The inhibitory postsynaptic current is shown in figure 2(a). After the pulse is removed, the channel current drops to a lower value under zero gate bias than its initial current, exhibiting memory effects. Subsequent positive pulses cause

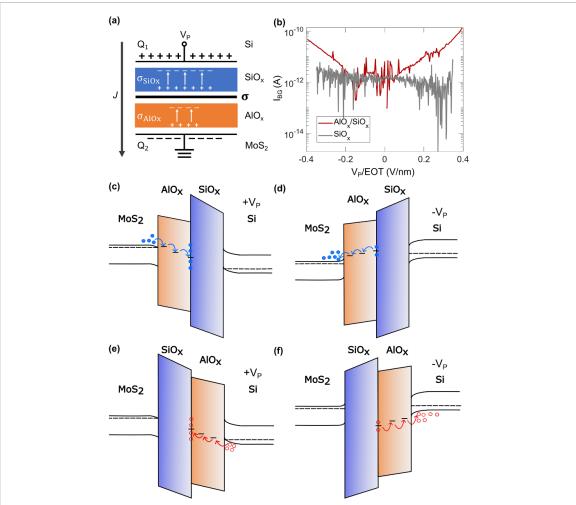

**Figure 1.** (a) Left: analogy with biological synapses. Right: schematic illustration of a three-terminal synaptic device with few-layer  $MoS_2$  as the channel material on top of a stack of binary oxides (10 nm  $AlO_x/10$  nm  $SiO_x$ ). The substrate is heavily doped silicon. Pre-synaptic pulses are applied to the backgate Si substrate. The post-synaptic current flowing through the  $MoS_2$  channel is measured. (b) An optical image of a typical  $MoS_2$  synaptic device. Scale bar:  $10 \ \mu m$ .

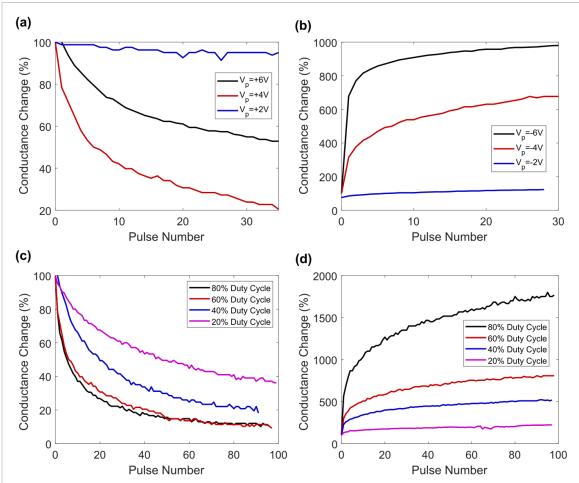

similar depression effects. The MoS<sub>2</sub> channel current under zero gate voltage decreases from  $\sim$ 1  $\mu$ A to  $\sim$ 10 pA after 15 consecutive positive pulses applied to the backgate, achieving a dynamic resistive switching range of  $\sim 10^5$ . As shown in figure 2(b), negative pulses lead to effective potentiation in the MoS<sub>2</sub> ICGS device. The MoS<sub>2</sub> channel current is initialized to be about 500 pA and a train of negative pulses (amplitude: -4 V; duration: 1 s) is subsequently applied to the backgate. During the negative pulse, the MoS<sub>2</sub> channel current is reduced due to the N-type characteristics of MoS<sub>2</sub>. However, after the negative pulse is removed, the channel current increases to about 1 μA under zero backgate bias. Subsequent negative pulses will lead to saturation in the channel current. The excitatory postsynaptic current is shown in figure 2(b). By reducing the duration of voltage pulses, the channel conductance of the MoS<sub>2</sub> ICGS device can be adjusted continuously both for potentiation and depression. As shown in figures 2(c) and (d), gradual decrease/increase of channel conductance is observed when a series of voltage pulses with a duration of 80 ms and an amplitude of +4 V/-4 Vis applied. The synaptic weight, i.e. the channel conductance, can be further modulated by tuning pulse amplitude and duty cycle. As we increase the pulse amplitude from 2 V to 6 V, both inhibitory and excitatory synaptic weight tuning can be enhanced (figures 3(a) and (b), duty cycle is fixed at 60%). Similarly, as we increase the duty cycle from 20% to 80%, both inhibitory and excitatory synaptic weight tuning can be enhanced (figures 3(c) and (d), pulse amplitude is fixed at 4 V). For depression, the synaptic weight change saturates when the duty cycle exceeds 60%.

To better understand the resistive switching mechanism of the binary oxide based ICGS device, we also fabricate two groups of MoS<sub>2</sub> devices with

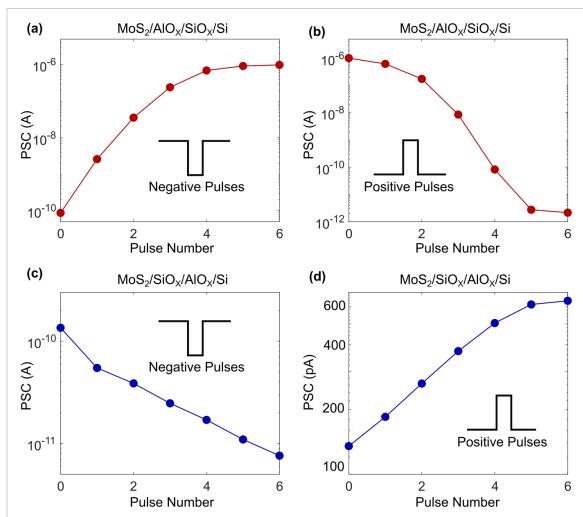

10 nm AlO<sub>x</sub> only and with 10 nm SiO<sub>x</sub> only as dielectric layers, respectively, for control experiments. The single oxide layer of  $AlO_x$  and  $SiO_x$  is deposited using the same ALD parameters as for the binary  $AlO_x/SiO_x$ dielectric layers. As shown in figures S1(a) and (b), the resistive switching behaviors in the  $AlO_x$  only and the SiO<sub>x</sub> only device are negligible compared with binary oxide counterpart devices under the same pulse schemes. During the comparison test, the pulse duration is kept the same for all devices under test and the pulse amplitudes are adjusted to guarantee the same electric field strength generated for AlOx, SiOx and  $AlO_x/SiO_x$  dielectric layers. These results indicate the impact of bulk trap states inside the individual AlO<sub>x</sub> and  $SiO_x$  dielectric layers is negligible. We attribute the strong excitatory and inhibitory effects to the interfacial charges generated near the binary oxide interface when the voltage pulses are applied, and the interfacial charges can electrostatically gate the MoS<sub>2</sub> channel and modulate its channel conductance over a wide dynamic range. Another important feature of the binary oxide ICGS devices is that the excitatory and inhibitory polarity can be switched by changing the oxide stacking sequence. As shown in figure 4, we experimentally found that, in the MoS<sub>2</sub>/SiO<sub>x</sub>/AlO<sub>x</sub>/Si ICGS device, positive pulses result in potentiation and negative pulses lead to depression, which is opposite as the MoS<sub>2</sub>/AlO<sub>x</sub>/SiO<sub>x</sub>/Si counterpart devices.

The generation of interfacial charging at the binary oxide interface can be explained by the Maxwell-Wagner instability theory. The Maxwell-Wagner instability is a widely found phenomenon in almost all binary dielectric systems with different compositions, such as silicon metal-oxide-semiconductor (MOS) and metal-nitride-oxide-silicon structures [61–63]. It was first discovered by Maxwell [66] in the 19th century and later investigated by Wagner [67]. Two layers of oxides with different compositions

Figure 2. (a), (b) Transient current response in the  $MoS_2$  channel when a train of pulses with amplitude of +4 V (a) and -4 V (b) is applied to the backgate terminal. The pulse duration for (a) and (b) is 1 s. The dwell time between two consecutive pulses is 9 s. Pulse frequency: 0.1 Hz. (c), (d)  $MoS_2$  channel conductance as a function of pulse number. Pulse duration: 80 ms. Pulse frequency: 10 Hz. Pulse amplitude: +4 V (c) and -4 V (d). Both potentiation and depression can be achieved by controlling the pulse voltage polarity.

generally have different conductivities. Under a bias across a stack of binary oxides, there can be a discontinuity in current density across the interface between the two oxide layers, causing interfacial charges to accumulate. Figure 5(a) illustrates the charge distribution across the  $MoS_2/AlO_x/SiO_x/Si$  gate stack under a positive presynaptic pulse  $V_p$ . The  $\sigma_{SiO_x}$  and  $\sigma_{AlO_x}$  represent the surface charge density of the  $SiO_x$  and  $AlO_x$  layers due to dielectric polarization, respectively. The  $\sigma$  represents the interfacial charge density accumulated at the  $SiO_x/AlO_x$  interface. The  $Q_1$  and  $Q_2$  are the charges accumulated at the two terminals of the gate capacitor. In steady state, the system should reach charge neutrality, so

that  $Q_1 + \sigma A - Q_2 = 0$ , where A denotes the device area. Based on Gauss's law, the electric fields in the two dielectrics are given by

$$E_{\text{SiO}_x} = \frac{\frac{Q_1}{A} - \sigma_{\text{SiO}_x}}{\epsilon_0} \tag{1}$$

$$E_{\text{AlO}_x} = \frac{\frac{Q_2}{A} - \sigma_{\text{AlO}_x}}{\epsilon_0} \tag{2}$$

respectively, where  $\epsilon_0$  is the vacuum permittivity. The pulse voltage  $V_{\rm p}$  can be calculated as  $V_{\rm p} = d_{\rm AlO_x} E_{\rm AlO_x} + d_{\rm SiO_x} E_{\rm SiO_x}$ , where the  $d_{\rm AlO_x}$  and  $d_{\rm SiO_x}$  are the thickness of AlO<sub>x</sub> and SiO<sub>x</sub> layers, respectively.

Figure 3. Dependency of synaptic weight update on voltage pulse amplitude and duty cycle. (a) Synaptic weight change as a function of inhibitory pulse number with different pulse amplitudes (blue: +2 V; red: +4 V; black: +6 V). Pulse frequency: 10 Hz. Pulse width: 60 ms. The gap between two adjacent pulses is 40 ms, i.e. the duty cycle is 60%. (b) Synaptic weight change as a function of excitatory pulse number with different pulse amplitudes (blue: -2 V; red: -4 V; black: -6 V). Pulse frequency: 10 Hz. Duty cycle: 60%. (c)-(d) Synaptic weight update as a function of inhibitory (c) and excitatory (d) pulse number with different duty cycles. Pulse amplitude: +4 V (c) and -4 V (d). Pulse frequency is 10 Hz for both (c) and (d).

Assuming that the dielectric polarization is linearly proportional to the electrical field, the surface charge density can be expressed as  $\sigma_{\rm SiOx} = \epsilon_0 \chi_{\rm SiO_x} E_{\rm SiO_x}$  and  $\sigma_{\rm AlOx} = \epsilon_0 \chi_{\rm AlO_x} E_{\rm AlO_x}$ , where  $\chi$  represents the corresponding dielectric susceptibilities. From the above equations, we can obtain the number of interfacial charges per unit area as

$$\sigma = \epsilon_0 (1 + \chi_{AIO_x}) E_{AIO_x} - \epsilon_0 (1 + \chi_{SiO_x}) E_{SiO_x}$$

= \epsilon\_0 (\epsilon\_{AIO\_x} E\_{AIO\_x} - \epsilon\_{SiO\_x} E\_{SiO\_x}) (3)

where  $\epsilon_{AlO_x}$  and  $\epsilon_{SiO_x}$  being the relative permittivity of  $SiO_x$  and  $AlO_x$ , respectively. As a result, the polarity and quantity of the Maxwell-Wagner instability induced interfacial trapped charge depend on the permittivity and the strength of electrical fields in the two dielectric layers. This makes the interfacial charge density to be controllable by engineering the oxide materials and tuning external pulses. Therefore, we

can engineer the interfacial trap charges to be significantly larger than bulk trap states inside individual oxides.

With positive pulses applied, the MoS<sub>2</sub> channel conductance decreases (figure 2(b)). Given the N-type characteristics of MoS<sub>2</sub>, it indicates that negative interfacial charges are generated under positive pulses. We can therefore deduce that the interfacial charge density  $\sigma = \epsilon_0 \left( \epsilon_{AlO_x} E_{AlO_x} - \epsilon_{SiO_x} E_{SiO_x} \right) < 0$ (when  $V_{\rm p}>0$ ). Considering that the relative permittivity of ALD deposited AlO<sub>x</sub>( $\sim$ 8–9) [68] is larger than that of ALD deposited  $SiO_x$  (~3.9) [68], the electric field in the AlO<sub>x</sub> layer must be smaller than that in the SiO<sub>x</sub> layer. This holds true when the pulse polarity switches to negative. According to the model, the polarization of the interfacial charge is inversed under negative gate voltage, i.e.  $\sigma = \epsilon_0 \left( \epsilon_{AlO_x} E_{AlO_x} - \epsilon_{SiO_x} E_{SiO_x} \right) > 0 \text{ (when } V_p < 0),$ leading to positive charge accumulation under negative pulses. Thus, we should expect an increase in the channel conductance for N-type MoS2, which agrees

**Figure 4.** Performance comparison between MoS<sub>2</sub> ICGS devices with different oxide stacking orders. To reach the maximum dynamic range, six voltage pulses with 10 s duration and incremental pulse amplitudes are applied to the back gate terminal of each device. The amplitudes of the six voltage pulses start with 1 V with a step of 1 V. (a) (b) The MoS<sub>2</sub> channel current of a  $MoS_2/10$  nm  $AlO_x/10$  nm  $SiO_x/Si$  ICGS device as a function of gate pulse number during depression under negative pulses (a) and potentiation under positive pulses (b). (c), (d) The  $MoS_2$  channel current of a  $MoS_2/10$  nm  $SiO_x/10$  nm  $AlO_x/Si$  ICGS device as a function of gate pulse number during depression under negative pulses (c) and potentiation under positive pulses (d). Different growth conditions of the dielectrics (e.g. substrate, surface roughness and composition) affect the deposition quality and thus the conductance of the dielectrics layers, which is believed to cause the difference in the dynamic range of the two devices.

well with our experimental data (figure 2(a)). Based on the model, if we reverse the stacking sequence of the binary oxide, the interfacial charge generated would become

$$\sigma^* = \epsilon_0 \left( \epsilon_{\text{SiO}_x} E_{\text{SiO}_x} - \epsilon_{\text{AlO}_x} E_{\text{AlO}_x} \right) \tag{4}$$

Consequently, positive  $\sigma^*$  would be generated under positive pulses, which should lead to increased channel conductivity. Negative  $\sigma^*$  would be generated under negative pulses, which should lead to decreased channel conductivity. That means the pulse polarity corresponding to potentiation and depression is expected to be reversed.

To experimentally verify this, we fabricate  $MoS_2$  ICGS devices with a binary oxide stack of 10 nm  $SiO_x/10$  nm  $AlO_x$  using the same ALD deposition parameters (i.e.  $AlO_x$  is deposited first and closer to the back gate). We found that these devices

with reversed oxide sequence indeed exhibit opposite polarity in potentiation and depression processes compared to the original devices (figure 4). It further validates the Maxwell-Wagner instability model presented here. We also measured the programming current (i.e. dielectric leakage current) of the binary oxide based MoS<sub>2</sub> ICGS device and compared it with single oxide counterparts. As shown in figure 5(b), the dielectric leakage current remains constant (on the order of few pA) as the pulse gate bias increases in the single oxide devices. In the binary oxide device, however, the dielectric leakage current increases as the pulse gate bias increases, which indicates that a significant number of charges migrate in and out of the binary oxide stack and part of these charges can be trapped near the interface, as described by the Maxwell-Wagner model. This aligns well with both our model and the experimental data. The volatility of the ICGS device further supports the Maxwell-Wagner instability model. Maxwell-Wagner

Figure 5. Net charge transport across the binary oxide stack. (a) Illustration of Maxwell-Wagner instability induced dielectric leakage current and interfacial charging in the  $MoS_2/AlO_x/SiO_x/Si$  gate stack. (b) Dielectric leakage current measured in the  $MoS_2/AlO_x/SiO_x/Si$  and  $MoS_2/SiO_x/Si$  stacks under backgate bias. Positive value means current flowing from the Si gate to the  $MoS_2$  channel, and vice versa. (c), (d) Band diagram of the  $MoS_2/AlO_x/SiO_x/Si$  gate stack under positive (c) and negative (d) gate bias. The blue arrows indicate the electron transport direction. (e), (f) Band diagram of the  $MoS_2/SiO_x/AlO_x/Si$  gate stack under positive (e) and negative (f) gate bias. The red arrows indicate the hole transport direction.

instability induced interfacial charges is supposed to exhibit time-dependent dynamics. The reason is that, at steady state with zero pulse bias applied, the dielectrics are no longer polarized and the electric fields inside oxides  $E_{\rm SiO_x}$ ,  $E_{\rm AlO_x}$  will be zero. As a result, the interfacial charge  $\sigma = \epsilon_0 \left( \epsilon_{\rm AlO_x} E_{\rm AlO_x} - \epsilon_{\rm SiO_x} E_{\rm SiO_x} \right)$  will eventually relax to zero. Figures S2(a) and (b) confirm the time-dependent response of MoS2 channel current after a negative and positive gate pulses are removed, respectively. To extract the time constant of this relaxation process, we measure the channel current in a 40 min period (supplementary information, figure S3) and the time constant is estimated to be 43.6 s.

The band diagrams in figures 5(c)–(f) can provide physical insights behind the excitatory and inhibitory effects of the binary oxide based MoS<sub>2</sub> ICGS devices. For the MoS<sub>2</sub>/AlO<sub>x</sub>/SiO<sub>x</sub>/Si stack under positive backgate pulses, a decrease in the channel conductivity indicates that there is negative charge accumulation at the interface that electrostatically gates the MoS<sub>2</sub>

channel, contributed by electron injection from the MoS<sub>2</sub> channel to the oxide interface through trapassisted tunneling. The trap-assisted tunneling process happens mainly through the  $AlO_x$  layer, probably because the trap states inside  $AlO_x$  are more than that in the SiO<sub>x</sub> layer. A higher quality of ALD deposited  $SiO_x$  might originate from a better seeding on top of the silicon substrate. Given the thickness of oxide layers (10 nm  $AlO_x + 10$  nm  $SiO_x$ ) and the amplitude of pulses (i.e. 4 V), the direct tunneling current will be negligible. The net charge migration is illustrated in figure 5(c). Similarly, for the  $MoS_2/AlO_x/SiO_x/Si$ stack under negative pulses, the band bending is in favor of electrons escaping from the interface traps to the MoS<sub>2</sub> channel through trap assisted tunneling (figure 5(d)). Therefore, the interfacial charge gating will enhance the channel conductivity. When the oxide stacking sequence is reversed, the charge transport is illustrated in figures 5(e)–(f). For the MoS<sub>2</sub>/SiO<sub>x</sub>/AlO<sub>x</sub>/Si stack under positive pulses, an increase in conductivity indicates that the dominating

J Zou et al

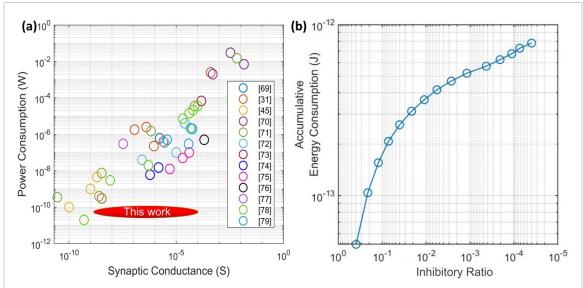

**Figure 6.** (a) Benchmark this work with state-of-the-art two-terminal memristive devices (open circles) in terms of programming power consumption at different synaptic conductance states. The literature data are from [31, 45, 69-79]. Each color represents a different reference. (b) The energy consumption of our synaptic device as a function of the inhibitory synaptic weight tuning ratio. The energy consumption is below 1 pJ as the synaptic weight is adjusted across  $\sim$ 5 orders of magnitude.

charge transport is holes injected from the p-doped silicon substrate to the oxide interface due to trapassisted tunneling through  $AlO_x$  (figure 5(e)). For the same stack order under negative pulses, the band bending is in favor of holes escaping from the oxide interface to the substrate and results in a reduced channel conductivity (figure 5(f)). We note that only the net charge accumulation paths are illustrated in figures 5(c)–(f).

Due to the separation of the programming channel (i.e. binary oxides) and the reading channel (i.e. MoS<sub>2</sub>), our device can achieve an ultralow programming power consumption. Unlike the conventional two terminal memristors, the programming power consumption  $P_p$  is independent of resistive states of the synaptic device presented here. The programming power consumption  $P_p$  is kept around 50 pW while the synaptic conductance varies from ∼1 nS to  $\sim$ 100  $\mu$ S. We also benchmark the performance of our device with state-of-the-art synaptic memristors [35, 45, 69–79]. As shown in figure 6(a), our device has a clear advantage in terms of low programming power, especially when the synaptic device operates in the LRSs. For example, Chen et al demonstrated a Ag/h-BN/Ag threshold resistive switching memristor with compliance-current-controlled on/off ratio ranging up to  $10^{11}$ . The device exhibited ultra-low  $P_p$  $(\sim 40-80 \text{ fW})$  when the synaptic conductance is on the order of 100 fS. However, the  $P_{\rm p}$  can rise to  $\sim$ 0.4– 0.7  $\mu$ W when the synaptic conductance in about 2  $\mu$ S [35]. Our device consumes about  $10^7$  lower  $P_p$  than the state of the art at the same synaptic conductance. It allows more precise control on the synaptic weight update at a given pulse width. This is the key advantage of the binary oxide based MoS2 ICGS device with a three-terminal design, in which the programming

and reading channels are separated. The reading power usually depends on the minimum measurable voltage and current resolution of instruments and does not fully reflect the inherent properties of synaptic devices. Therefore, the reading power consumption is not benchmarked here. Figure 6(b) shows the accumulative energy consumption as a function of the synaptic conductance change ratio during depression (normalized by initial conductance of 108  $\mu$ S). It consumes less than 1 pJ of total energy to adjust the synaptic conductance across about five orders of magnitude.

It is worth noting that our MoS<sub>2</sub> ICGS devices differ from the conventional silicon charge-trap flash memory based synaptic devices in three folds. (1) In conventional charge-trap flash memory, the programming/erasing voltage polarity only depends on the doping type of channel semiconductor [80, 81], not on the stacking sequence of dielectrics. In this work, the depression and potentiation pulse polarity can be reversed by changing the stacking sequence of dielectrics, which provides new tuning knobs for synaptic weight modulation. (2) In charge-trap flash memory, the bulk defect/trap states play a dominating role in hosting injected carriers through Fowler-Nordheim tunneling or hot carrier effects [82, 83]. In our device, the interfacial defect/trap states near the binary oxide interface play a more important role than the bulk traps inside individual oxide layers. (3) The atomic thickness of the MoS<sub>2</sub> channel allows a tight electrostatic control by the interfacial charges induced by the Maxwell-Wagner instability. The atomically thin 2D channel and a tight electrostatic gate control translate to a wider dynamic range of resistive switching of the synaptic channel at a given amount of injected interfacial charges near the

binary oxide interface, compared to 3D bulk semiconductor channels made from silicon.

#### 3. Conclusion

We have fabricated binary oxide based MoS2 ICGS devices with ultralow programming power consumption ( $\sim$ 50 pW), which is independent of the synaptic conductance. This benefits from the physical separation of the programming channel and the reading channel. Induced by Maxwell-Wagner instability, interfacial charges near the binary oxide interface can be generated and modulated by pulses applied to the substrate. Through the electrostatic gating of the induced interfacial charges, the MoS<sub>2</sub> synaptic channel conductance can be tuned. Both potentiation and depression have been experimentally demonstrated. By reversing the oxide stacking sequence, the excitatory/inhibitory pulse polarity will also be reversed, which further validates the Maxwell-Wagner instability model. Due to the atomic thickness MoS<sub>2</sub> channel, the interfacial charge holds tight electrostatic control over the channel and leads to a wide resistive switching dynamic range of 105. Our method is also CMOS compatible and can be easily scaled up for system-level in-memory computing.

#### 4. Methods

#### 4.1. Fabrication of IGCS devices

We started with a 500  $\mu$ m thick heavily doped silicon substrate, which also performs as the backgate electrode. The binary oxide layers (10 nm AlO<sub>x</sub>/10 nm  $SiO_x$ ) were deposited sequentially using ALD method at a temperature of 250 °C. Few-layered MoS<sub>2</sub> flakes were mechanically exfoliated on top of the binary oxide layers, from commercially available ntype molybdenum disulfide crystal (supplied by 2D Semiconductors) using Scotch tape. The source and drain contacts were patterned by a standard EBL process. Au was used as the contact metal with a thickness of 50 nm, using electron beam evaporation. To mitigate the damage of the evaporated Au to the MOS<sub>2</sub> surface, the first 5 nm Au was deposited at a rate of  $0.5 \, \text{Å s}^{-1}$ , and the rest of Au was deposited at a rate of  $5 \text{ Å s}^{-1}$ .

#### 4.2. Electrical characterization

The transient electrical measurements were conducted using a Keysight B1500A semiconductor parameter analyzer and a probe station. The waveform generator was connected to the Si back gate of the device under test to generate pulses using Keysight 33600 waveform generator. The MoS<sub>2</sub> channel current was measured by Keysight B1500, with a sampling rate of 100  $\mu$ s. During the measurement, a reading voltage of 10 mV was constantly applied to the drain terminal.

# Data availability statement

All data that support the findings of this study are included within the article (and any supplementary files).

# Acknowledgments

This work was financed in part by a Grant (contract C000080565) from the Commonwealth of Pennsylvania, Department of Community and Economic Development, National Science Foundation (Grant No.: NSF ECCS-2239822). National Science Foundation (Grant No.: NSF DBI-1949629), and support from Carnegie Mellon University. J Z, S L, T H, Y Z, S S and X Z also acknowledge the support from the CMU Claire & John Bertucci Nanotechnology Laboratory.

#### **ORCID** iDs

Jingyi Zou https://orcid.org/0000-0002-5135-

Hefei Liu https://orcid.org/0000-0001-6533-7112 Yuxuan Cosmi Lin https://orcid.org/0000-0003-0638-2620

Sheng Shen **b** https://orcid.org/0000-0002-4759-2010

Xu Zhang https://orcid.org/0000-0003-0474-5846

#### References

- [1] von Neumann J 1993 First draft of a report on the EDVAC *IEEE Ann. Hist. Comput.* **15** 27–75

- [2] Aly M M S and Chattopadhyay A (Ed) 2022 Emerging Computing: From Devices to Systems: Looking beyond Moore and Von Neumann 1st edn (Springer)

- [3] Nguyen H A D, Yu J, Xie L, Taouil M, Hamdioui S and Fey D 2017 Memristive devices for computing: beyond CMOS and beyond von Neumann 2017 IFIP/IEEE Int. Conf. on Very Large Scale Integration (VLSI-SoC) pp 1–10

- [4] Kandel E R 2001 The molecular biology of memory storage: a dialogue between genes and synapses *Science* **294** 1030–8

- [5] Schuman C D, Kulkarni S R, Parsa M, Mitchell J P, Date P and Kay B 2022 Opportunities for neuromorphic computing algorithms and applications *Nat. Comput. Sci.* 2 10–19

- [6] Jo S H, Chang T, Ebong I, Bhadviya B B, Mazumder P and Lu W 2010 Nanoscale memristor device as synapse in neuromorphic systems Nano Lett. 10 1297–301

- [7] Wan W et al 2022 A compute-in-memory chip based on resistive random-access memory Nature 608 504–12

- [8] Im I H, Kim S J and Jang H W 2020 Memristive devices for new computing paradigms Adv. Intell. Syst. 2 2000105

- [9] Kim S J, Kim S and Jang H W 2021 Competing memristors for brain-inspired computing iScience 24 101889

- [10] Hodgkin A L and Huxley A F 1952 A quantitative description of membrane current and its application to conduction and excitation in nerve J. Physiol. 117 500–44

- [11] Gerstner W, Kistler W M, Naud R and Paninski L 2014 Neuronal Dynamics: From Single Neurons to Networks and Models of Cognition 1st edn (Cambridge University Press)

- [12] Alberts B, Johnson A, Lewis J, Raff M, Roberts K and Walter P 2002 Ion channels and the electrical properties of membranes Molecular Biology of the Cell 4th edn (Garland Science) (available at: www.ncbi.nlm.nih.gov/books/ NBK26910/)

- [13] Alarcón G 2012 Cellular electrophysiology: membrane, synaptic and action potentials *Introduction to Epilepsy* ed A Valentín and G Alarcón (Cambridge University Press) pp 22–30

- [14] Kuzum D, Yu S and Wong H-S P 2013 Synaptic electronics: materials, devices and applications *Nanotechnology* 24 382001

- [15] Chua L 1971 Memristor-the missing circuit element IEEE Trans. Circuit Theory 18 507–19

- [16] Strukov D B, Snider G S, Stewart D R and Williams R S 2008 The missing memristor found Nature 453 80–83

- [17] Midya R, Wang Z, Rao M, Upadhyay N K and Yang J J 2019 14—RRAM/memristor for computing Advances in Non-Volatile Memory and Storage Technology (Woodhead Publishing Series in Electronic and Optical Materials) 2<sup>nd</sup> edn, ed B Magyari-Köpe and Y Nishi (Woodhead Publishing) pp 539–83

- [18] Zidan M A, Strachan J P and Lu W D 2018 The future of electronics based on memristive systems *Nat. Electron*. 1 22–29

- [19] Yang J J, Strukov D B and Stewart D R 2013 Memristive devices for computing Nat. Nanotechnol. 8 13–24

- [20] Borghetti J, Snider G S, Kuekes P J, Yang J J, Stewart D R and Williams R S 2010 'Memristive' switches enable 'stateful' logic operations via material implication *Nature* 464 873–6

- [21] Wang Z et al 2017 Memristors with diffusive dynamics as synaptic emulators for neuromorphic computing Nat. Mater. 16 101–8

- [22] Yang J J, Pickett M D, Li X, Ohlberg D A A, Stewart D R and Williams R S 2008 Memristive switching mechanism for metal/oxide/metal nanodevices Nat. Nanotechnol. 3 429–33

- [23] Liu H et al 2023 Artificial neuronal devices based on emerging materials: neuronal dynamics and applications Adv. Mater. 35 2205047

- [24] Zhang Y et al 2021 Evolution of the conductive filament system in HfO<sub>2</sub>-based memristors observed by direct atomic-scale imaging Nat. Commun. 12 7232

- [25] González M B et al 2021 synaptic devices based on HfO<sub>2</sub> memristors Mem-elements for Neuromorphic Circuits with Artificial Intelligence Applications (Advances in Nonlinear Dynamics and Chaos (ANDC)) ed C Volos and V-T Pham (Academic) ch 19, pp 383–426

- [26] Illarionov G A, Morozova S M, Chrishtop V V, Einarsrud M-A and Morozov M I 2020 Memristive TiO<sub>2</sub>: synthesis, technologies, and applications Front. Chem. 8 724

- [27] Torrezan A C, Strachan J P, Medeiros-Ribeiro G and Williams R S 2011 Sub-nanosecond switching of a tantalum oxide memristor *Nanotechnology* 22 485203

- [28] Kim S, Choi S, Lee J and Lu W D 2014 Tuning resistive switching characteristics of tantalum oxide memristors through Si doping ACS Nano 8 10262–9

- [29] Qu B, Younis A and Chu D 2016 Recent progress in tungsten oxides based memristors and their neuromorphological applications *Electron. Mater. Lett.* 12 715–31

- [30] Sheridan P and Lu W 2014 Memristors and memristive devices for neuromorphic computing Memristor Networks ed A Adamatzky and L Chua (Springer) pp 129–49

- [31] Li Y, Fang P, Fan X and Pei Y 2020 NiO-based memristor with three resistive switching modes Semicond. Sci. Technol. 35 055004

- [32] Li Y, Chu J, Duan W, Cai G, Fan X, Wang X, Wang G and Pei Y 2018 Analog and digital bipolar resistive switching in solution-combustion-processed NiO memristor ACS Appl. Mater. Interfaces 10 24598–606

- [33] Mohammad B, Jaoude M A, Kumar V, Al Homouz D M, Nahla H A, Al-Qutayri M and Christoforou N 2016 State of the art of metal oxide memristor devices *Nanotechnol. Rev.* 5 311–29

- [34] Duan H, Cheng S, Qin L, Zhang X, Xie B, Zhang Y and Jie W 2022 Low-power memristor based on two-dimensional materials J. Phys. Chem. Lett. 13 7130–8

- [35] Chen S et al 2020 Wafer-scale integration of two-dimensional materials in high-density memristive crossbar arrays for artificial neural networks Nat. Electron. 3 638–45

- [36] Zhou Z, Yang F, Wang S, Wang L, Wang X, Wang C, Xie Y and Liu Q 2021 Emerging of two-dimensional materials in novel memristor Front. Phys. 17 23204

- [37] Tang B et al 2022 Wafer-scale solution-processed 2D material analog resistive memory array for memory-based computing Nat. Commun. 13 3037

- [38] Xie J, Afshari S and Sanchez Esqueda I 2022 Hexagonal boron nitride (h-BN) memristor arrays for analog-based machine learning hardware npj 2D Mater. Appl. 6 50

- [39] Ling S, Zhang C, Ma C, Li Y and Zhang Q 2023 Emerging MXene-based memristors for in-memory, neuromorphic computing, and logic operation Adv. Funct. Mater. 33 2208320

- [40] Patel M, Hemanth N R, Gosai J, Mohili R, Solanki A, Roy M, Fang B and Chaudhari N K 2022 MXenes: promising 2D memristor materials for neuromorphic computing components *Trends Chem.* 4 835–49

- [41] Yan X et al 2019 A new memristor with 2D  $Ti_3C_2T_x$  MXene flakes as an artificial bio-synapse Small 15 1900107

- [42] Rahmani M K, Kim M-H, Hussain F, Abbas Y, Ismail M, Hong K, Mahata C, Choi C, Park B-G and Kim S 2020 Memristive and synaptic characteristics of nitride-based heterostructures on Si substrate *Nanomaterials* 10 994

- [43] Kwon K C, Baek J H, Hong K, Kim S Y and Jang H W 2022 Memristive devices based on two-dimensional transition metal chalcogenides for neuromorphic computing *Nano-Micro Lett.* 14 58

- [44] Marinella M J, Stevens J E, Longoria E M and Kotula P G 2012 Resistive switching in aluminum nitride 70th Device Research Conf. pp 89–90

- [45] Zhao H et al 2017 Atomically thin femtojoule memristive device Adv. Mater. 29 1703232

- [46] Ma J, Liu H, Yang N, Zou J, Lin S, Zhang Y, Zhang X, Guo J and Wang H 2022 Circuit-level memory technologies and applications based on 2D materials Adv. Mater. 34 2202371

- [47] Hsu A et al 2013 Large-area 2D electronics: materials, technology, and devices Proc. IEEE 101 1638–52

- [48] Ge R, Wu X, Kim M, Shi J, Sonde S, Tao L, Zhang Y, Lee J C and Akinwande D 2018 Atomristor: nonvolatile resistance switching in atomic sheets of transition metal dichalcogenides *Nano Lett.* 18 434–41

- [49] Hus S M, Ge R, Chen P-A, Liang L, Donnelly G E, Ko W, Huang F, Chiang M-H, Li A-P and Akinwande D 2021 Observation of single-defect memristor in an MoS<sub>2</sub> atomic sheet Nat. Nanotechnol. 16 58–62

- [50] He N et al 2021 V<sub>2</sub>C-based memristor for applications of low power electronic synapse IEEE Electron Device Lett. 42 319–22

- [51] Choi B J, Yang J J, Zhang M-X, Norris K J, Ohlberg D A A, Kobayashi N P, Medeiros-Ribeiro G and Williams R S 2012 Nitride memristors Appl. Phys. A 109 1–4

- [52] Tetzlaff R (ed) 2013 Memristors and Memristive Systems 2014th edn (Springer)

- [53] Zhu J et al 2018 Ion gated synaptic transistors based on 2D van der Waals crystals with tunable diffusive dynamics Adv. Mater. 30 1800195

- [54] Zhu L Q, Wan C J, Guo L Q, Shi Y and Wan Q 2014 Artificial synapse network on inorganic proton conductor for neuromorphic systems *Nat. Commun.* 5 3158

- [55] Yang C S, Shang D S, Liu N, Shi G, Shen X, Yu R C, Li Y Q and Sun Y 2017 A synaptic transistor based on quasi-2D molybdenum oxide Adv. Mater. 29 1700906

- [56] Cao G, Meng P, Chen J, Liu H, Bian R, Zhu C, Liu F and Liu Z 2021 2D material based synaptic devices for neuromorphic computing Adv. Funct. Mater. 31 2005443

- [57] Yang F-S et al 2020 Oxidation-boosted charge trapping in ultra-sensitive van der Waals materials for artificial synaptic features Nat. Commun. 11 2972

[58] Wang B et al 2021 Monolayer MoS<sub>2</sub> synaptic transistors for high-temperature neuromorphic applications Nano Lett. 21 10400–8

- [59] Tian H, Guo Q, Xie Y, Zhao H, Li C, Cha J J, Xia F and Wang H 2016 Anisotropic black phosphorus synaptic device for neuromorphic applications Adv. Mater. 28 4991–7

- [60] Zhang F, Li C, Li Z, Dong L and Zhao J 2023 Recent progress in three-terminal artificial synapses based on 2D materials: from mechanisms to applications *Microsyst. Nanoeng.* 9 16

- [61] Jinesh K B, Lamy Y, Klootwijk J H and Besling W F A 2009 Maxwell–Wagner instability in bilayer dielectric stacks Appl. Phys. Lett. 95 122903

- [62] Jameson J R, Griffin P B, Plummer J D and Nishi Y 2006 Charge trapping in high-kGate stacks due to the bilayer structure itself *IEEE Trans. Electron Devices* 53 1858–67

- [63] Frohman-Bentchkowsky D and Lenzlinger M 2003 Charge transport and storage in metal-nitride-oxide-silicon (MNOS) structures J. Appl. Phys. 40 3307–19

- [64] Karthik R and Tummala V 2017 Voltage dependent Maxwell-Wagner polarization in dielectric heterostructures Mater. Today 4 8751–7

- [65] Iversen L, Iversen S, Bloom F E and Roth R H 2008 Introduction to Neuropsychopharmacology 1st edn (Oxford University Press)

- [66] Maxwell J C 1892 A Treatise on Electricity and Magnetism (Oxford University Press)

- [67] Schering H et al 1924 Die isolierstoffe der elektrotechnik. Vortragsreihe, veranstaltet von dem Elektrotechnischen verein e. v. und der Technischen hochschule, Berlin (Springer) (available at: http://archive.org/details/ bibliotecadeleg01corogoog)

- [68] Nalwa H S 1999 Handbook of low and high dielectric constant materials and their applications Volume 1: Materials and Processing. Volume 2: Phenomena, Properties and Applications 1st edn (Academic)

- [69] Li Y et al 2022 Low-voltage ultrafast nonvolatile memory via direct charge injection through a threshold resistive-switching layer Nat Commun. 13 4591

- [70] Wu X et al 2019 Thinnest nonvolatile memory based on monolayer h-BN Adv. Mater. 31 1806790

- [71] Shi Y et al 2018 Electronic synapses made of layered two-dimensional materials Nat. Electron. 1 458–65

- [72] Feng X et al 2019 A fully printed flexible MoS<sub>2</sub> memristive artificial synapse with femtojoule switching energy Adv. Electron. Mater. 5 1900740

- [73] Wang Y, Yang J, Wang Z, Chen J, Yang Q, Lv Z, Zhou Y, Zhai Y, Li Z and Han S-T 2019 Near-infrared annihilation of conductive filaments in quasiplane MoSe<sub>2</sub>/Bi<sub>2</sub>Se<sub>3</sub> nanosheets for mimicking heterosynaptic plasticity Small 15 1805431

- [74] Ranganathan K, Fiegenbaum-Raz M and Ismach A 2020 Large-scale and robust multifunctional vertically aligned MoS<sub>2</sub> photo-memristors Adv. Funct. Mater. 30 2005718

- [75] Roy S et al 2020 Toward a reliable synaptic simulation using Al-doped HfO<sub>2</sub> RRAM ACS Appl. Mater. Interfaces 12 10648–56

- [76] Lei P, Duan H, Qin L, Wei X, Tao R, Wang Z, Guo F, Song M, Jie W and Hao J 2022 High-performance memristor based on 2D layered BiOI nanosheet for low-power artificial optoelectronic synapses Adv. Funct. Mater. 32 2201276

- [77] Wang X et al 2020 Solution-processable 2D polymer/graphene oxide heterostructure for intrinsic low-current memory device ACS Appl. Mater. Interfaces 12 51729–35

- [78] Lu X F et al 2021 Exploring low power and ultrafast memristor on p-type van der Waals SnS Nano Lett. 21 8800–7

- [79] Kim H, Mahmoodi M R, Nili H and Strukov D B 2021 4K-memristor analog-grade passive crossbar circuit *Nat. Commun.* 12 5198

- [80] Lorenzi P, Rao R, Ghidini G, Palma F and Irrera F 2009 Charge trapping non volatile memory ECS Trans. 25 269

- [81] Micheloni R, Crippa L and Marelli A 2010 Inside NAND Flash Memories (Springer)

- [82] Aritome S 2015 NAND Flash Memory Technologies 1st edn (Wiley-IEEE Press)

- [83] Hasnat K, Yeap C-F, Jallepalli S, Hareland S A, Shih W-K, Agostinelli V M, Tasch A F and Maziar C M 1997 Thermionic emission model of electron gate current in submicron NMOSFETs IEEE Trans. Electron Devices 44 129–38