# Comparison of Voltage Balance and State Estimation Dynamics for Hybrid Switched-Capacitor Converter Topologies

Kishalay Datta and Jason T. Stauth

Thayer School of Engineering at Dartmouth College

Hanover, NH USA

Kishalay.Datta.TH@dartmouth.edu, Jason.T.Stauth@dartmouth.edu

Abstract—This work develops a general analytical framework to understand and quantify state estimation and flying capacitor voltage balance dynamics in hybrid switched-capacitor converter topologies. We expand a state-space modelling framework previously only applied to flying-capacitor multilevel (FCML) converters to treat other topology classes including Dickson-based, series-parallel (SP), Fibonacci, and exponential (doubler) converters. In the generalized treatment, it is shown that many topologies undergo order-reduction which provides significant simplification compared to the FCML case. To compare the relative difficulty of estimating or balancing flying capacitor voltages, we introduce the concept of condition number to better quantify observability and controllability. A hardware prototype consisting of Series-Parallel and FCML topologies is used to verify the model and illustrate topology differences.

# I. INTRODUCTION

Control and regulation are important in power conversion to ensure reliable operation while rejecting disturbances and achieving regulation or tracking objectives. Hybrid switched-capacitor (SC) converters are attractive as they can reduce energy storage (volume) of passive components [1]–[3], however, they have higher-order control dynamics due to the additional energy storage modalities of flying capacitors [4]–[10]. This work develops a generalized modern control framework to analyze these high-order dynamics, including details of flying capacitor voltage balance and state estimation such as can inform broader control and regulation strategies.

Recent literature has developed state-space models for flying-capacitor multilevel (FCML) converters which are known to have challenges in terms of flying capacitor voltage balance [7]–[9], [11], [12]. State-space (SS) modelling serves a powerful method of capturing the converter dynamics where the flying capacitor voltage(s) are treated as state variables. This further enables perspectives on modern control metrics: controllability and observability [13] which have provided insights into natural balance [9] and feasibility of estimating flying capacitor voltages [8]. However, such models have not been extended to other topology classes and give only a limited (true/false) indication regarding the feasibility of achieving voltage balance and state estimation.

This work extends and generalizes the state-space model such that it can be applied to a wider range of hybrid SC topologies including Dickson-based, series-parallel (SP),

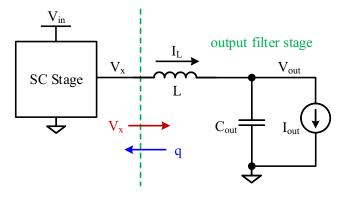

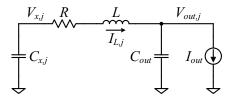

Fig. 1. Direct-conversion hybrid SC converter treated as two subsystems: switched capacitor (SC) and output filter stages.

Fibonacci, and exponential (doubler) architectures. The main focus of this work is on the *direct-conversion* version of these architectures [2], [14]–[16] where the SC stage is soft-charged by a single inductor connected to the switching node  $V_x$ , conceptually illustrated in Fig. 1. This work builds on prior work by providing an analog quantification of controllability and observability using the numerical linear algebra concept called 'condition number'. Condition number is a robust and well-established concept derived from the *Singular Value Decomposition* (SVD) theory for matrices [13], [17], [18]. Condition number is relatively easy to calculate based on the configuration of flying capacitors across a converter's switching states, and can provide insight or rapid assessment of hybrid SC balancing or control performance with little effort prior to simulation or hardware development.

The rest of the paper is organized as follows. Section II describes construction of the discrete-time (DT) SS model for direct-conversion hybrid SC converters. Section III provides perspectives on controllability and observability based on the condition number concept and compares voltage balance and state estimation for the Series Parallel (SP), Dickson-based, Exponential, and FCML converters. Section IV explains the correlation of the condition number concept to the special case of natural balancing. Section V describes the experimental validation using a hardware prototype using exemplary SP and FCML converters. Section VI concludes the paper.

1

#### II. DISCRETE-TIME (DT) STATE SPACE (SS) MODEL

Illustrated in Fig. 1, direct conversion hybrid SC topologies typically operate with a single inductor connected to switching node  $V_x$  which can soft-charge the SC stage, either operating in a resonant mode [15], or a pulse-width modulated (inductive) mode [19]. In [8], the general model in Fig. 1 was used to decompose the flying-capacitor multilevel (FCML) topology into two stages, namely, the SC stage and the output filter stage. This abstraction allows the development of a DT state-space model for the SC stage, where the output of the model is switching node voltage  $V_{x,j}$  and input is the charge  $q_i$  transferred through the inductor in switching phase, j. The state variables of the model are the flying capacitor voltages  $V_C$ , which are affected by charge flow across relevant switching phases in converter switching period k. For FCML converters with  $N_c$  flying capacitors (i.e. N-cell or N+1 Level converters, where  $N = N_c + 1$ ), we have  $N_c$  state variables.

As detailed in [8], [9], the DT SS model is formulated by identifying the state and output equations for the SC stage. The state equation parametrizes capacitor voltages  $V_C$  across converter period k using a state-connection matrix B based on the configurations and charge flow through capacitors in relevant switching phases. The output equation parametrizes the switching node voltages  $V_x$  in period k using output connection matrix C based on flying capacitor voltages and their configurations in relevant switching phases. As the process of formulating these matrices and models for FCML converters is well detailed in [20], here we focus on illustrating the process using other topologies, which leads to some interesting differences and simplifications compared to the more complicated FCML formulation.

## A. DT SS model formulation and order reduction

To illustrate the DT SS model formulation, we will start with the series-parallel (SP) converter with  $N_c=2$  flying capacitors. A slight deviation in the notations from [8], [9] is made for this example by incorporating an additional '\*' subscript to some vectors and matrices. Its importance will become clear soon. We denote the state-vector to be  $\mathbf{V}_{C*}(k) = \begin{bmatrix} V_{C1}(k) & V_{C2}(k) \end{bmatrix}^T$ , which is of order  $2 \times 1$ . The input vector consisting of charge flow through the inductor in the two switching phases is defined as  $\mathbf{q}(k) = \begin{bmatrix} q_1(k) & q_2(k) \end{bmatrix}^T$ , which is of order  $2 \times 1$ . The output vector is  $\mathbf{V}_{x}(k) = \begin{bmatrix} V_{x,1}(k) & V_{x,2}(k) \end{bmatrix}^T$  of order  $2 \times 1$ . We assume the outputs are sampled at the end of each switching phase. Applying KVL, we get the state equation as,

$$\boldsymbol{V_{C*}}(k+1) = \begin{bmatrix} 1 & 0 \\ 0 & 1 \end{bmatrix} \cdot \boldsymbol{V_{C*}}(k) + (\frac{1}{C_f}) \begin{bmatrix} -1/2 & 1 \\ -1/2 & 1 \end{bmatrix} \cdot \boldsymbol{q}(k), (1)$$

and the output equation is given by,

$$\mathbf{V}_{\mathbf{x}}(k) = \begin{bmatrix} \frac{1}{2} & \frac{1}{2} \\ -1 & -1 \end{bmatrix} \cdot \mathbf{V}_{C*}(k) + (\frac{1}{C_f}) \begin{bmatrix} -\frac{1}{2} & 0 \\ 1 & -2 \end{bmatrix} \cdot \mathbf{q}(k) + \begin{bmatrix} 0 \\ 1 \end{bmatrix} \cdot V_{in}.$$

(2)

Assuming that in the parallel phase, the two capacitor voltages are forced to be equal, the two equations represented

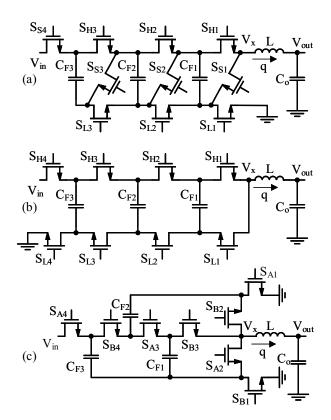

Fig. 2. Hybrid SC converters with 4:1 ratio using (a) Modified Series-Parallel, (b) FCML and (c) Dickson topologies.

in (1) are identical. Thus, we can manipulate (1) by dropping one of the state variables to get,

$$V_C(k+1) = V_C(k) + (\frac{1}{C_f}) \begin{bmatrix} -1/2 & 1 \end{bmatrix} \cdot \mathbf{q}(k),$$

(3)

where,  $V_C(k) = V_{C1} = V_{C2}$ . The output equation can be manipulated by using this equality to obtain simplification,

$$\mathbf{V}_{\mathbf{x}}(k) = \begin{bmatrix} 1 \\ -2 \end{bmatrix} \cdot V_C(k) + \left(\frac{1}{C_f}\right) \begin{bmatrix} -\frac{1}{2} & 0 \\ 1 & -2 \end{bmatrix} \cdot \mathbf{q}(k) + \begin{bmatrix} 0 \\ 1 \end{bmatrix} \cdot V_{in}. \tag{4}$$

Unlike (3), in (4) we only change the coefficient matrix of  $V_{C*}(k)$  and the rest remain unchanged.

This exercise reveals an interesting property of this topology. To fully explain its dynamics only a single state variable (capacitor voltage) is sufficient. This is because with the SP topology, assuming slow-switching limit (SSL) operation, i.e. that there is sufficient time in the parallel phase that flying capacitor voltages are forced to be equal, the flying capacitor voltages become dependent and thus the SC stage can be represented by a single state variable (capacitor voltage).

We can execute the same exercise to show that DT SS model of any arbitrary SP converter with  $N_c$  flying capacitors reduces to a single state variable model. This gives valuable insight and a key differentiation from prior FCML models that, depending on the topology, the order of the DT SS model of an SC stage may be reduced to a lower number of states, p, where

$$1 \le p \le N_c. \tag{5}$$

For a generic SC stage with  $N_c$  flying capacitors and J switching phases, treating all  $N_c$  flying capacitor voltages as

state variables, we can use KVL to form a preliminary DT SS model:

$$V_{C*}(k+1) = A_* \cdot V_{C*}(k) + B_* \cdot q(k) + W_{i*} \cdot V_{in}, \quad (6)$$

$$V_{x}(k) = C_{*} \cdot V_{C*}(k) + D \cdot q(k) + W_{o} \cdot V_{in}, \qquad (7)$$

where,  $V_{C*}(k) = \begin{bmatrix} V_{C1}(k) & \dots & V_{CNc}(k) \end{bmatrix}^T$  is the state vector of order  $N_c \times 1$ , consisting of all the possible states;  $A_*$  of order  $N_c \times N_c$ , gives the inherent state-transition behavior of the SC stage;  $B_*$  is the input matrix of order  $N_c \times J$ , to represent capacitor connection and amount of charge flow based on the input charge vector  $q(k) = \begin{bmatrix} q_1(k) & \dots & q_J(k) \end{bmatrix}^T$  of order  $J \times 1$ .  $V_x(k) = \begin{bmatrix} V_{x,1}(k) & \dots & V_{x,J}(k) \end{bmatrix}^T$  is the output vector of order  $J \times 1$ , consisting of samples taken at the end of each phase;  $C_*$  of order  $J \times N_c$ , represents the connection of the flying capacitors to the output;  $D_*$  of order  $J \times J$ , contains the contributions of q(k) to the output; finally,  $W_{i*}$  of order  $N_c \times 1$  and  $W_o$  of order  $J \times 1$ , represents influence of the input,  $V_{in}$ , on the states and outputs respectively.

The next step is to identify the p independent state variables satisfying (5). This may involve algebraic manipulations based on circuit knowledge to identify the p linearly independent equations in (6), like the one demonstrated for SP topology. The concept of generating a controllability matrix which is described later in this paper can be used as a possible technique to eliminate dependent states. Once we obtain p, we can form the *reduced order* DT SS model of the SC stage, such that the state equation is,

$$V_C(k+1) = A \cdot V_C(k) + B \cdot q(k) + W_i \cdot V_{in}, \quad (8)$$

where, A is the system matrix of order  $p \times p$ ; B of order  $p \times J$ , is termed as the *weighted state connection matrix*. B defines which capacitors are connected, the polarity, and the quantity of charge flow for individual switching phases.  $W_i$  conveys the weight of the input,  $V_{in}$ , if at all, to the state variables. Similarly, the output equation of the reduced order system is,

$$V_{x}(k) = C \cdot V_{C}(k) + D \cdot q(k) + W_{O} \cdot V_{in}, \tag{9}$$

where, C is the *reduced-order output connection matrix* of order  $J \times p$ . A key point to clarify is that unlike FCML models where A is always the identity matrix, in (8), this need not be true for other SC topologies<sup>1</sup>.

# B. SC Topologies Encountering Order Reduction

Several converter families like SP, Dickson and Fibonacci [21], [22] form rigid capacitor loops. The interesting characteristic of such converters is that they may not have  $N_c$  independent states to explain their dynamics and can undergo order reduction. Here, we will briefly outline the DT SS models for some of the known SC topologies<sup>2</sup> such that they have  $N_c$  flying capacitors but undergo order reduction due to

the presence of rigid capacitor loops. Due to a lack of space, the derivations are omitted. The appropriate values of  $\boldsymbol{B}$  and  $\boldsymbol{C}$  are listed in Table I. The converters listed always have  $\boldsymbol{A}$  as an identity matrix of order p=1 since they reduce only a single independent state variable. Except for Dickson with even  $N_c$  [23], [24], we assume all flying capacitances have identical value,  $C_f$ .

TABLE I

REDUCED DT SS MODELS FOR DIFFERENT SC FAMILIES.

| Topology              | $C_f \cdot \boldsymbol{B}$                                       | C                                                                  |

|-----------------------|------------------------------------------------------------------|--------------------------------------------------------------------|

| Series-Parallel       | $\begin{bmatrix} -\frac{1}{N_c} & 1 \end{bmatrix}$               | $\begin{bmatrix} 1 & -N_c \end{bmatrix}^T$                         |

| Fibonacci             | $\begin{bmatrix} -\frac{F_k(N_c)}{F_k(N_c+1)} & 1 \end{bmatrix}$ | $\begin{bmatrix} 1 & -\frac{F_k(N_c+1)}{F_k(N_c)} \end{bmatrix}^T$ |

| Dickson (even $N_c$ ) | $\left[ -\frac{2}{N_c + 2}  \frac{2}{N_c} \right]$               | $\begin{bmatrix} 1 & -\frac{N_c + 2}{N_c} \end{bmatrix}^T$         |

An interesting observation for the three reduced-order cases in Table I, is the relationship between  $\boldsymbol{B}$  and  $\boldsymbol{C}$  matrices. We can conclude that for these cases,  $\boldsymbol{B} = -(b_{11}/C_f) \cdot \boldsymbol{C}^T$ , where,  $(b_{11}/C_f)$  is first element of  $\boldsymbol{B}$ . This aligns with DT SS models for FCML [8] such that,  $\boldsymbol{C}$  has a negatively scaled transpose relationship with  $\boldsymbol{B}$ . Hence, we can generically state that for any converter topology,

$$\boldsymbol{B} = -(\frac{1}{C_f}) \cdot \boldsymbol{M_{scale}} \cdot \boldsymbol{C}^T, \tag{10}$$

where  $M_{scale}$  is some full-rank scaling matrix of order  $p \times p$ . The intuition behind (10) is that both (8) and (9) are derived from the same KVL loops, thus B and C provide essentially the same information.

Converter families like FCML and Exponential [21], [25], which do not form rigid capacitive loops, have all the  $p=N_c$  states to be independent. This implies that controlling any one flying capacitor does not influence the control action on the others entirely. This provides opportunities to control each independently which has been demonstrated for FCML converters [10], [11], [26] and exponential converters [27].

The main conclusion of this section is that the true order of the DT SS model for an SC stage could be lower than  $N_c$ . This implies that many seemingly complex topologies like those in Table I could actually have very simple and lower-order dynamics. The presence of charge-sharing loops tries to reduce any relative imbalances among the flying capacitors. Thus, simpler control and estimation may come at the cost of charge-sharing losses if the converter becomes imbalanced.

# III. OBSERVABILITY AND CONTROLLABILITY OF FLYING CAPACITOR VOLTAGES

Given the systematic framework to construct DT SS models for the SC stages, the next objective is to understand the observability and controllability of various topologies. As discussed in [8], [9], in this context, observability quantifies whether samples of the switching node voltage  $V_{x,j}$  across switching phases  $(j = 1 \cdots J)$  have sufficient information

$<sup>^1</sup>$ The Dickson topology with odd  $N_c$  under split-phase is a notable example with non-identity  ${m A}$  matrix.

$<sup>^2</sup>$ In Table I,  $\overset{\checkmark}{F}_k(i)$  refers to the  $i^{th}$  term of the Fibonacci sequence [22]. For Dickson with even  $N_c$ , the convention from [23], [24] has been used. Due to space constraints, Dickson with odd  $N_c$  under split phase has not been shown.

to determine (estimate) flying capacitor voltages  $V_{C,i}$ ,  $(i = 1 \cdots N_c)$ . Controllability quantifies whether flying capacitor voltages can be independently regulated (or ballanced) through a control effort applied to the inductor current (i.e. charge quantities flowing through the inductor,  $q_i$ ).

#### A. Rank-based criterion

Adopting the modern control theory concepts which have also been used for FCML converter models [8], the controllability matrix is formulated as<sup>3</sup>,

$$C = \begin{bmatrix} B & AB & \cdots & A^{p-1}B \end{bmatrix}. \tag{11}$$

In the generalized treatment given (5), for the system to be controllable, C is required to be full-rank, which means,

$$rank(\mathcal{C}) = p. \tag{12}$$

Similarly, to check for state estimation we need to create the observability matrix,

$$\mathcal{O} = \begin{bmatrix} C & CA & \dots & CA^{p-1} \end{bmatrix}^T. \tag{13}$$

Likewise,  $\mathcal{O}$  also needs to full-rank for the system to be observable, and hence,

$$rank(\mathcal{O}) = p. \tag{14}$$

The criteria (11) - (14) is more generic than results previously derived for FCML converters [8]. This is because we cannot assume A to be an identity matrix and the order of the system may not be linearly related to the conversion ratio, N but rather p. This is particularly applicable for reduced order models as well as converters with highly nonlinear conversion ratios like the Exponential  $(N=2^{N_c})$  and Fibonacci  $(N=F_k(N_c+1))$  topologies.

# B. Relative Controllability and Observability based on Condition Number

The binary nature (*true* or *false*) of controllability (12), unfortunately, provides little insight into the degree of controllability of a converter. This is particularly needed for practical scenarios like the FCML converter while operating over the full range of duty cycles ( $0 \le D \le 1$ ); or Pulse Width Modulated (PWM) operation<sup>4</sup> for Dickson topologies like the Double Step-Down (DSD) variants [24], [28]; and so on.

Importantly, even though  $\mathcal{C}$  may be full-rank when the converters operate close to the uncontrollable cases, intuitively we would expect the converter to be harder to control. Thus, a more analog or quantitative measure of controllability is needed. An excellent sensitivity function-based approach in [29] analyzes open-loop converters near uncontrollable scenarios. However, as of now, only certain case-by-case transient analyses have been provided.

In this work, we use a robust and well-established concept developed for numerical computation used in linear algebra known as the *condition number* [13], [17], [18],  $\kappa(\alpha)$ , which measures *how full-rank is a matrix*,  $\alpha$ , such that,

$$1 \le \kappa(\alpha) = \frac{\sigma_{max}}{\sigma_{min}} < \infty. \tag{15}$$

$\sigma_{min}$  and  $\sigma_{max}$  are the minimum and maximum singular values of  $\alpha$ , which can be computed using its *Singular Value Decomposition* (SVD)<sup>5</sup> [17], [18].

Let us get some intuition about  $\kappa(\alpha)$  in the context of solving a two-variable linear equation. The equation is,

$$\boldsymbol{\alpha} \cdot \mathbf{x} = \begin{bmatrix} \alpha_{11} & \alpha_{12} \\ \alpha_{21} & \alpha_{22} \end{bmatrix} \begin{bmatrix} x_1 \\ x_2 \end{bmatrix} = \begin{bmatrix} b_1 \\ b_2 \end{bmatrix}.$$

Consider two different scenarios:

- If  $\alpha$  is a  $2^{nd}$  order identity matrix and  $b_1 = 1$ ,  $b_2 = 2$ . Then we get,  $x_1 = 1$ ,  $x_2 = 2$  and  $\kappa(\alpha) = 1$ .

- For  $\alpha_{11}=1, \alpha_{12}=0.99, \alpha_{21}=1.01,$  and  $\alpha_{22}=1$  with  $b_1=1, b_2=2,$  we get,  $x_1=-9.8\times 10^3, x_2=9.9\times 10^3$  and  $\kappa(\alpha)=4\times 10^4.$

The above cases show how relative solution magnitudes diverge and the sensitivity to slight parameter differences (or systematic errors) grow with increasing condition number. So, even though both versions of  $\alpha$  are full-rank, the appropriate value of x starts to become unbounded with a  $\kappa(\alpha)$  much greater than unity indicating how unsolvable the system is.

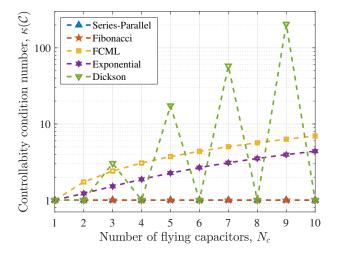

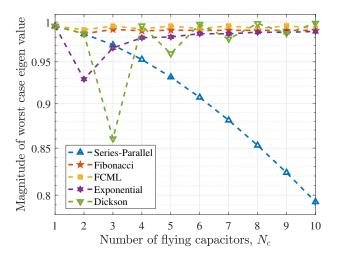

Fig. 3. Condition number of the controllability matrix C versus Number of flying capacitors,  $N_c$ , for different converters (lower is more controllable).

This can now be applied to hybrid SC converters to quantify the relative difficulty of achieving flying capacitor balance. Fig. 3 shows the condition number of the controllability matrix,  $\kappa(\mathcal{C})$ , for several converter topologies when operating at their nominal conversion ratio. The closer  $\kappa(\mathcal{C})$  is to unity, the easier it is to externally adjust any flying capacitor imbalances using a controller. It is evident from Fig. 3 that the topologies undergoing order reduction to p=1, i.e., SP, Fibonacci and Dickson with even  $N_c$ , are extremely well-conditioned. The Dickson with odd  $N_c$  under split-phase operation however, rapidly becomes difficult to control with increasing  $N_c$  even

$^5$ SVD is a well-known concept in linear algebra and hence is not discussed here. In MATLAB, it can be computed using the svd() function.

$<sup>^3</sup>$ If the  $\mathcal{C}$  matrix is formed using (6), then it can also be effectively used to identify linearly dependent rows which represent the dependent states and enable order reduction.

<sup>&</sup>lt;sup>4</sup>Due to space constraints, analysis for PWM scenario using condition number is not covered in this paper.

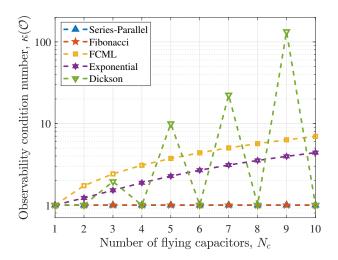

Fig. 4. Condition number of the observability matrix  $\mathcal{O}$  versus Number of flying capacitors,  $N_c$ , for different converters (lower is more observable).

though it undergoes order reduction to  $p=(N_c+1)/2$ . The FCML and Exponential topologies, which do not undergo any order reduction, under nominal conversion mode become less controllable with increasing  $N_c$  because the order is progressively increasing. A point to highlight is that condition number  $\kappa(\mathcal{C})$  is only a proxy for the degree of controllability, i.e. it describes the relative control effort needed in an ideal state-feedback control system. However, the actual closed-loop system performance will depend also on the nature and dynamics of the associated controller. For example in a natural balance scenario, the dynamics of the output filter need to be taken into account to determine actual natural balance strength and settling time as will be seen in the next section.

We can apply the same concept to the observability matrix to calculate its condition number,  $\kappa(\mathcal{O})$ . Similar to Fig. 3,  $\kappa(\mathcal{O})$  for different converters are shown in Fig. 4. As controllability and observability are closely linked due to their dependence on similar KVL relationships in the SC network,  $\kappa(\mathcal{O})$  and  $\kappa(\mathcal{C})$  are qualitatively similar, however different interpretations of these metrics may arise in the practical implementation of state observers and feedback controllers.

#### IV. CLOSED-LOOP BEHAVIOR UNDER NATURAL BALANCE

Natural Balance is the special control case where passive feedback like the LC output filter for the hybrid SC converter can drive the flying capacitors towards a balanced condition [30], [31]. To understand the closed-loop behavior we need to combine the SC stage and the output filter in order to derive the overall closed-loop DT SS model.

#### A. Overall Closed-loop model for Natural Balance

The output filter stage can be represented with its own DT SS model, based on the per-phase Thevenin equivalent circuit model for the hybrid SC converter as shown in Fig. 5 [15]. Using the initial conditions of equivalent capacitance  $C_{x,j}$ , inductor L, and output voltage  $V_{out}$ , the differential equations

Fig. 5. Equivalent circuit of a generic direct-conversion hybrid SC converter in the  $j^{th}$  switching phase [15].

of the model are solved to find the final values of  $V_{x,j}$  and  $I_{L,j}$  using a state-transition model [20], [29], [32]–[34].

In the state transition model, initial values of the inductor current and output voltage at the beginning of  $k^{th}$  switching period are denoted as,  $\boldsymbol{x}(k) = \begin{bmatrix} I_{L,0}(k) & V_{out,0}(k) \end{bmatrix}^T$ . The input of the output filter is  $\boldsymbol{V_x}(k)$  and its output being  $\boldsymbol{q}(k)$ . The DT SS model state equation is then written as,

$$x(k+1) = P \cdot x(k) + Q \cdot V_x(k) + W_1 \cdot I_{out}, \quad (16)$$

where, P, Q and  $W_1$  are the system matrix, input matrix, and weight matrix to quantify the impact of the load current,  $I_{out}$  on x(k) respectively. Similarly, the output equation may be written as,

$$q(k) = \mathbf{R} \cdot \mathbf{x}(k) + \mathbf{S} \cdot \mathbf{V}_{\mathbf{x}}(k) + \mathbf{W}_{\mathbf{2}}I_{out}, \tag{17}$$

where, R, S and  $W_2$  are the output matrix, feed-forward matrix, and weight matrix to quantify the impact of  $I_{out}$  on q(k) respectively. Detailed derivations of these matrices for a 4-cell FCML are available in [20].

Given that we have the individual DT SS models for both the SC stage, (8) - (9), and the output filter, (16) - (17), we can derive the overall closed-loop DT SS model of the hybrid SC converter [13], [20] such that,

$$\begin{bmatrix} V_{C}(k+1) \\ x(k+1) \end{bmatrix}$$

$$= \begin{bmatrix} A + BTSC & BTR \\ QC + QDTSC & P + QDTR \end{bmatrix} \begin{bmatrix} V_{C}(k) \\ x(k) \end{bmatrix}$$

$$+ \begin{bmatrix} W_{i} + BTSW_{o} & BTW_{2} \\ QW_{o} + QDTSW_{o} & W_{1} + QDTW_{2} \end{bmatrix} \begin{bmatrix} V_{in} \\ I_{out} \end{bmatrix}, (18)$$

where  $T = (I - SD)^{-1}$ ; I is the identity matrix.

Thus, the closed-loop passive feedback model where the dynamics are determined by its own characteristics (circuit parameters and phase duration) and external excitation (input voltage and load current), can be simply expressed as

$$x_{cl}(k+1) = A_{cl} \cdot x_{cl}(k) + E \cdot e, \tag{19}$$

where  $x_{cl} = [V_C, I_{L,0}, V_{out,0}]^T$  stands for the discrete-time state variables of both subsystems: the initial values in a given converter period k of flying capacitor voltages, the inductor current, and output voltage;  $A_{cl}$  is the state matrix of the closed loop passive feedback system; e represents the external excitation via input voltage or output current and E is its coefficient matrix.

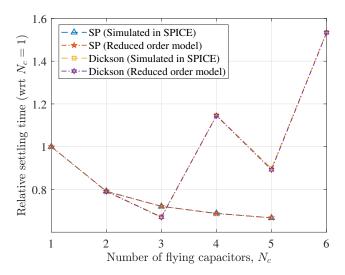

Fig. 6. Worst case eigenvalue magnitude versus  $N_c$  under natural balancing with identical  $C_f=1\mu F$  and  $L/R=1\mu s$ .

### B. Balancing Strength using Closed-loop Eigenvalues

The closed-loop eigenvalues,  $\lambda$ , of naturally balanced hybrid SC converters can serve as a good indicator of their balancing strength. Importantly for the DT SS model in (19), due to the passive nature of the converter, the eigenvalue will always lie inside or on the unit circle ( $|\lambda| \leq 1$ ). The lower the magnitude of maximum eigenvalue,  $|\lambda_{max}|$ , the better is the natural balancing strength.

In Fig. 6,  $|\lambda_{max}|$  is plotted for multiple converter families across  $N_c$ . In all such cases, the inductor ESR is dominant such that  $L/R = 1\mu s$  and the switching phase with minimum time duration for all cases is the same at  $(\pi/10) \mu s$ . This plot has several interesting observations. Notably for the SP converter unlike all others,  $|\lambda_{max}|$  monotonically decreases with  $N_c$ , indicating that SP converters with higher conversion ratios have stronger balancing strength. A possible explanation comes from the large asymmetry in equivalent capacitance  $C_{x,j}$  and imbalance voltage in the respective series and parallel phases, which leads to a larger magnitude of disturbance injected in the series phase and a longer time to correct imbalance in the parallel phase. Next, for the Dickson topologies, odd  $N_c$ with split-phasing outperforms even  $N_c$  cases. When odd  $N_c$ converters are imbalanced, it can be shown they will have resulting charge sharing losses, which add damping on top of the natural balance mechanism on top of the output filter action. Thus, the enhanced balancing performance.

To validate the reduced order model with circuit simulations as well as exhibit the actual settling performance, comparisons are made for SP and Dickson topologies as shown in Fig. 7. Firstly, the reduced order models computed analytically in MATLAB match closely with SPICE simulated results. More importantly, the intuition gained from Fig. 6, is also verified from the settling time performance.

### C. Relation with Controllability Condition Number

Another key concept to be clarified is the correlation of condition number with the actual closed-loop performance. For

Fig. 7. Settling time normalized with respect  $N_c = 1$  compared between SPICE simulation versus reduced order model for SP and Dickson topologies.

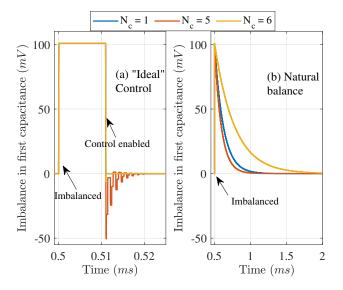

Fig. 8. Comparison of (a) Ideal control action versus (b) Natural balancing for Dickson topologies with  $N_c=1,5$  (split-phase) and 6.

the case of natural balancing, let us approach this in two ways.

The first is to check the correlation among the same topology but different  $N_c$ . If we compare Fig. 3 and Fig. 6, we observe for the cases where the condition number is increasing with  $N_c$  (Dickson with odd  $N_c$ , FCML and Exponential),  $|\lambda_{max}|$  is also increasing. However, for the well-conditioned cases ( $\kappa(\mathcal{C})=1$ ), the correlation is not strong. This aligns with our discussion in the previous section that  $\kappa(\mathcal{C})$  does not provide an exact correlation if the system is well-controlled. However, it gives a good indication of the poor closed-loop performance for ill-conditioned cases.

A similar correlation is observed when comparing two different converters with the same  $N_c$ . The well-conditioned cases of SP clearly outperform any other converters. Similarly, comparing the FCML and Exponential converters, we see a clear correlation. The relatively well-conditioned Exponential

converter has superior natural balancing dynamics to FCML. An exception to this is the Dickson with odd  $N_c$  with respect to other topologies. Because the odd  $N_c$  Dickson topology has charge sharing when imbalanced, it is less receptive to external control efforts to balance it.

To further justify this intuition, in Fig. 8, we plot the SPICE simulated transient response of Dickson with  $N_c=1,5,6$ , to the same imbalance when controlled by an ideal controller versus natural balance. With ideal control, the well-conditioned cases of  $N_c=1,6$  settle almost immediately but the poorly conditioned  $N_c=5$  case has oscillatory settling behavior. The conclusion is the opposite of the natural balance scenario. We should also observe the relative settling time of the two cases. The ideal control is almost two orders of magnitude faster than the natural balance. The above discussion shows that for stronger controllers, the condition number gives a better correlation of the closed-loop performance than weaker cases.

#### V. EXPERIMENTAL VALIDATION

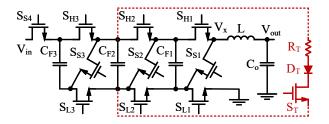

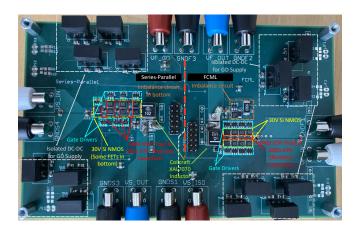

Experimental validation of the concepts presented above has been performed for the SP and FCML converter both having  $N_c=3$ . Under steady-state, an imbalance can be inserted by shorting the second flying capacitor,  $C_{F2}$ , to a forward-biased diode,  $D_T$ , using the switch,  $S_T$ , as shown in Fig. 9 for the SP converter. The same is true for the FCML converter case. The actual validation PCB is shown in Fig. 10. It is ensured that both cases have identical LC output filters with an inductance of  $1\mu H$ , and all the flying capacitances are nominally at  $1\mu F$ .

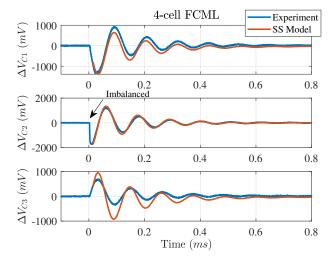

Fig. 11 shows the natural balance settling behavior of the flying capacitors after the imbalance has been inserted for the FCML case. The theoretical closed-loop DT SS model response is also compared and we observe good agreement for  $C_{F1}$  and  $C_{F2}$ . Because  $C_{F3}$  is exposed to higher voltage and is subject to voltage de-rating, the experimental model (which is based on equal capacitance) matches less well, but the overall settling behavior matches with good agreement.

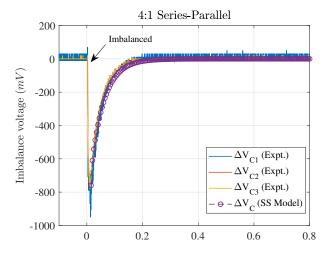

Fig. 12 shows the results and comparison for SP converter. The experimental result and the reduced order DT SS model seem to have good agreement. Comparing the two cases, we observe that, SP has a first-order settling and the settling time is almost 4 times faster than the oscillatory settling of the FCML. This validates both the intuition from condition number as well overall closed-loop behavior under natural balance as seen in Fig. 3 and 6 respectively.

Fig. 9. Test schematic for series-parallel converter.

Fig. 10. Annotated experimental PCB.

Fig. 11. Experimental data versus analytical calculation of the capacitor voltage settling measured after injected imbalance for 4-cell FCML.

Fig. 12. Experimental data versus analytical calculation of the capacitor voltage settling measured after injected imbalance for 4:1 SP.

#### VI. CONCLUSION

This work presents a general analysis of hybrid SC converters based on the DT SS framework to obtain models for any converter topology. The concept of order reduction for apparently complex topologies is presented. Modern control concept of condition number is used to obtain a better quantitative metric to understand the ability to control and estimate flying capacitor voltages for different families. A detailed analysis of the natural balancing of hybrid SC converters is presented. Finally, the theoretical analyses are validated using several simulations and actual PCB-based experiments.

# VII. ACKNOWLEDGEMENT

This work was supported in part by the National Science Foundation under award number NSF IIP 1822140 and by the Power Management Integration Center PMIC at Dartmouth under award PMIC-52. Thanks to Minh Phan and Ziyu Xia for their invaluable discussions.

#### REFERENCES

- [1] Z. Ye, S. R. Sanders, and R. C. N. Pilawa-Podgurski, "Modeling and comparison of passive component volume of hybrid resonant switchedcapacitor converters," *IEEE Transactions on Power Electronics*, vol. 37, no. 9, pp. 10 903–10 919, 2022.

- [2] P. H. McLaughlin, J. S. Rentmeister, M. H. Kiani, and J. T. Stauth, "Analysis and comparison of hybrid-resonant switched-capacitor dc-dc converters with passive component size constraints," *IEEE Transactions* on *Power Electronics*, vol. 36, no. 3, pp. 3111–3125, 2021.

- [3] A. Stupar, T. McRae, N. Vukadinović, A. Prodić, and J. A. Taylor, "Multi-objective optimization of multi-level dc-dc converters using geometric programming," *IEEE Transactions on Power Electronics*, vol. 34, no. 12, pp. 11912–11939, 2019.

- [4] R. H. Wilkinson, T. A. Meynard, and H. du Toit Mouton, "Natural balance of multicell converters: The general case," *IEEE Transactions* on Power Electronics, vol. 21, no. 6, pp. 1658–1666, 2006.

- [5] S. Thielemans, A. Ruderman, B. Reznikov, and J. Melkebeek, "Improved natural balancing with modified phase-shifted pwm for single-leg fivelevel flying-capacitor converters," *IEEE Transactions on Power Electronics*, vol. 27, no. 4, pp. 1658–1667, 2012.

- [6] J. Celikovic, R. Das, H.-P. Le, and D. Maksimovic, "Modeling of capacitor voltage imbalance in flying capacitor multilevel dc-dc converters," in 2019 20th Workshop on Control and Modeling for Power Electronics (COMPEL), 2019, pp. 1–8.

- [7] I. Z. Petric, R. K. Iyer, N. C. Brooks, and R. C. N. Pilawa-Podgurski, "A real-time estimator for capacitor voltages in the flying capacitor multilevel converter," in 2022 IEEE 23rd Workshop on Control and Modeling for Power Electronics (COMPEL), 2022, pp. 1–8.

- [8] Z. Xia, B. L. Dobbins, J. S. Rentmeister, and J. T. Stauth, "State space analysis of flying capacitor multilevel dc-dc converters for capacitor voltage estimation," in 2019 IEEE Applied Power Electronics Conference and Exposition (APEC), 2019, pp. 50–57.

- [9] Z. Xia, B. L. Dobbins, and J. T. Stauth, "Natural balancing of flying capacitor multilevel converters at nominal conversion ratios," in 2019 20th Workshop on Control and Modeling for Power Electronics (COMPEL), 2019, pp. 1–8.

- [10] R. K. Iyer, I. Z. Petric, R. S. Bayliss, N. C. Brooks, and R. C. N. Pilawa-Podgurski, "A high-bandwidth parallel active balancing controller for current-controlled flying capacitor multilevel converters," in 2023 IEEE Applied Power Electronics Conference and Exposition (APEC), 2023, pp. 775–781.

- [11] N. Vukadinović, A. Prodić, B. A. Miwa, C. B. Arnold, and M. W. Baker, "Extended wide-load range model for multi-level dc-dc converters and a practical dual-mode digital controller," in 2016 IEEE Applied Power Electronics Conference and Exposition (APEC), 2016, pp. 1597–1602.

- [12] J. S. Rentmeister and J. T. Stauth, "Modeling the dynamic behavior of hybrid-switched-capacitor converters in state space," in 2018 IEEE 19th Workshop on Control and Modeling for Power Electronics (COMPEL), 2018, pp. 1–7.

- [13] J.-N. Juang, *Identification and control of mechanical systems*. Cambridge :: Cambridge University Press, 2001.

- [14] Y. Lei and R. C. N. Pilawa-Podgurski, "A general method for analyzing resonant and soft-charging operation of switched-capacitor converters," *IEEE Transactions on Power Electronics*, vol. 30, no. 10, pp. 5650–5664, 2015.

- [15] S. R. Pasternak, M. H. Kiani, J. S. Rentmeister, and J. T. Stauth, "Modeling and performance limits of switched-capacitor dc-dc converters capable of resonant operation with a single inductor," *IEEE Journal of Emerging and Selected Topics in Power Electronics*, vol. 5, no. 4, pp. 1746–1760, 2017.

- [16] K. Kesarwani and J. T. Stauth, "Resonant and multi-mode operation of flying capacitor multi-level dc-dc converters," in 2015 IEEE 16th Workshop on Control and Modeling for Power Electronics (COMPEL), 2015, pp. 1–8.

- [17] G. H. Golub and C. F. Van Loan, *Matrix Computations*, 3rd ed. The Johns Hopkins University Press, 1996.

- [18] V. Klema and A. Laub, "The singular value decomposition: Its computation and some applications," *IEEE Transactions on Automatic Control*, vol. 25, no. 2, pp. 164–176, 1980.

- [19] C. Schaef, J. Rentmeister, and J. T. Stauth, "Multimode operation of resonant and hybrid switched-capacitor topologies," *IEEE Transactions* on *Power Electronics*, vol. 33, no. 12, pp. 10512–10523, 2018.

- [20] Z. Xia, "Modeling and control of direct-conversion hybrid switched-capacitor dc-dc converters," Ph.D. dissertation, 2022. [Online]. Available: https://digitalcommons.dartmouth.edu/dissertations/92

- [21] M. D. Seeman and S. R. Sanders, "Analysis and optimization of switched-capacitor dc-dc converters," *IEEE Transactions on Power Electronics*, vol. 23, no. 2, pp. 841–851, 2008.

- [22] M. Makowski and D. Maksimovic, "Performance limits of switched-capacitor dc-dc converters," in *Proceedings of PESC '95 Power Electronics Specialist Conference*, vol. 2, 1995, pp. 1215–1221 vol.2.

- [23] N. M. Ellis and R. Amirtharajah, "Large signal analysis on variations of the hybridized dickson switched-capacitor converter," *IEEE Transactions* on *Power Electronics*, vol. 37, no. 12, pp. 15005–15019, 2022.

- [24] R. Das, G.-S. Seo, and H.-P. Le, "Analysis of dual-inductor hybrid converters for extreme conversion ratios," *IEEE Journal of Emerging* and Selected Topics in Power Electronics, vol. 9, no. 5, pp. 5249–5260, 2021.

- [25] D. Li, G. Roberts, and A. Prodić, "Exponential flying capacitor converter," in 2022 IEEE 23rd Workshop on Control and Modeling for Power Electronics (COMPEL), 2022, pp. 1–6.

- [26] J. S. Rentmeister and J. T. Stauth, "A 48v:2v flying capacitor multi-level converter using current-limit control for flying capacitor balance," in 2017 IEEE Applied Power Electronics Conference and Exposition (APEC), 2017, pp. 367–372.

- [27] Z. Xia and J. T. Stauth, "A cascaded hybrid switched-capacitor dc-dc converter capable of fast self startup for usb power delivery," *IEEE Journal of Solid-State Circuits*, vol. 57, no. 6, pp. 1854–1864, 2022.

- [28] G.-S. Seo, R. Das, and H.-P. Le, "Dual inductor hybrid converter for point-of-load voltage regulator modules," *IEEE Transactions on Industry Applications*, vol. 56, no. 1, pp. 367–377, 2020.

- [29] L. Corradini and D. Maksimović, "Steady-state indeterminacy in lossless switched-mode power converters," *IEEE Transactions on Power Elec*tronics, vol. 38, no. 3, pp. 3001–3013, 2023.

- [30] R. Wilkinson, H. Mouton, and T. Meynard, "Stability analysis of multicell converters," in 2004 IEEE Africon. 7th Africon Conference in Africa (IEEE Cat. No.04CH37590), vol. 2, 2004, pp. 1131–1136.

- [31] T. Meynard, M. Fadel, and N. Aouda, "Modeling of multilevel converters," *IEEE Transactions on Industrial Electronics*, vol. 44, no. 3, pp. 356–364, 1997.

- [32] A. R. Brown and R. Middlebrook, "Sampled-data modeling of switching regulators," in 1981 IEEE Power Electronics Specialists Conference, 1981, pp. 349–369.

- [33] R. D. Middlebrook and S. Cuk, "A general unified approach to modelling switching-converter power stages," in 1976 IEEE Power Electronics Specialists Conference, 1976, pp. 18–34.

- [34] N. C. Brooks, R. K. Iyer, R. S. Bayliss, and R. C. N. Pilawa-Podgurski, "Fundamental state-space modeling methodology for the flying capacitor multilevel converter," in 2022 IEEE 23rd Workshop on Control and Modeling for Power Electronics (COMPEL), 2022, pp. 1–7.