# 1 Indigo3: A Parallel Graph Analytics Benchmark Suite for 2 Exploring Implementation Styles and Common Bugs 3

4 YIQIAN LIU, Texas State University, USA

5

6 NOUSHIN AZAMI, Texas State University, USA

7

8 Avery R VANAUSDAL, Texas State University, USA

9

10 MARTIN BURTSCHER, Texas State University, USA

11

12 Graph analytics codes are widely used and tend to exhibit input-dependent behavior, making them particularly

13 interesting for software verification and validation. This paper presents Indigo3, a labeled benchmark suite

14 based on 7 graph algorithms that are implemented in different styles, including versions with deliberately

15 planted bugs. We systematically combine 13 sets of implementation styles and 15 common bug types to create

16 the 41,790 CUDA, OpenMP, and parallel C programs in the suite. Each code is labeled with the styles and bugs

17 it incorporates. We used 4 subsets of Indigo3 to test 5 program-verification tools. Our results show that the

18 tools perform quite differently across the bug types and implementation styles, have distinct strengths and

19 weaknesses, and generally struggle with graph codes. We discuss the styles and bugs that tend to be the most

20 challenging as well as the programming patterns that yield false positives.

21

22 **CCS Concepts:** • Software and its engineering → Software verification and validation; • Computing

23 methodologies → Parallel computing methodologies; Parallel algorithms.

24

25 Additional Key Words and Phrases: Benchmark-suite design, bug insertion, software verification, graph

26 analytics, parallel computing

27

## 28 ACM Reference Format: 29

30 Yiqian Liu, Noushin Azami, Avery R VanAusdal, and Martin Burtscher. 2024. Indigo3: A Parallel Graph

31 Analytics Benchmark Suite for Exploring Implementation Styles and Common Bugs. *ACM Trans. Parallel

32 Comput.* 1, 1 (May 2024), 30 pages. <https://doi.org/10.1145/3665251>

33

## 34 1 INTRODUCTION 35

36 With the rise of social networks, recommender systems, GPS navigators, and data science, graph

37 algorithms for computing communities, centrality, shortest paths, frequent motifs, and so on have

38 become an important workload. Many of these algorithms exhibit irregular behavior, meaning

39 their control flow and memory-access patterns are data dependent and tend to change during

40 program execution [22]. Control-flow irregularity typically stems from *variable-iteration* loops, and

41 memory-access irregularity usually comes from *pointer-chasing* operations.

42

43 Such behavior makes it challenging for verification tools to check program correctness, especially

44 since the observed behavior for one input or time slice may not be representative of the behavior

45 of the same code for a different input or time slice [21]. Parallelism often exacerbates the problem

46 as the relative timing of the threads can change from run to run.

47

---

48 Authors' addresses: Yiqian Liu, y\_l120@txstate.edu, Texas State University, 601 University Drive, San Marcos, TX, USA,

49 78666; Noushin Azami, Texas State University, 601 University Drive, San Marcos, USA, noushin.azami@txstate.edu; Avery

R VanAusdal, Texas State University, 601 University Drive, San Marcos, USA, arv107@txstate.edu; Martin Burtscher, Texas

State University, 601 University Drive, San Marcos, USA, burtscher@txstate.edu.

50

51 Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee

52 provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the

53 full citation on the first page. Copyrights for components of this work owned by others than the author(s) must be honored.

54 Abstracting with credit is permitted. To copy otherwise, or republish, to post on servers or to redistribute to lists, requires

55 prior specific permission and/or a fee. Request permissions from permissions@acm.org.

56

57 © 2024 Copyright held by the owner/author(s). Publication rights licensed to ACM.

58

59 2329-4949/2024/5-ART \$15.00

60

61 <https://doi.org/10.1145/3665251>

62

50 To make things worse, irregularity creates opportunities for implementing the same algorithm in

51 many different ways. For example, we have written a connected-components (CC) algorithm using

52 hundreds of different combinations of parallelization and implementation styles (168 CUDA versions,

53 36 OpenMP versions, and 36 C-threading versions) [45]. The large number of implementation

54 styles adds yet another dimension of complexity to the program verification problem. In fact, the

55 community possesses little understanding of how the many possible ways of implementing an

56 irregular algorithm affect program verification.

57 Several widely-used benchmark suites with parallel implementations of irregular graph algo-

58 rithms exist, including Lonestar [38] with 14 parallel implementations of 11 graph algorithms and

59 Gardenia [69], an extended version of GAP [13], with 126 parallel implementations of 14 graph

60 algorithms. These and similar suites include a range of interesting algorithms and inputs to study.

61 However, none of them are designed to provide a large variety of each algorithm, nor do they

62 include enough inputs to elicit the many different irregular behaviors needed to thoroughly evaluate

63 the effectiveness of verification tools.

64 Moreover, since these suites were designed for performance measurements, they do not include

65 bugs to help with designing and testing program verification tools. Only a few suites contain

66 defective codes, such as DataRaceBench [43]. Hence, verification developers typically run their

67 tools on existing open-source code bases [36]. This approach presents several challenges. First, it

68 requires manual code inspection to verify any reported bugs. Second, it does not help with true or

69 false negatives. Third, selecting a suitable set of open-source codes and installing them tends to

70 be time consuming. Fourth, such codes naturally lack documentation of the bugs they contain. In

71 some cases, tool designers have scanned commit histories to identify older versions of a code base

72 with known bugs to test their tools [68]. However, this approach is even more time consuming, the

73 “unfinished” code is even harder to install and run, and true and false negatives remain a problem.

74 Clearly, the community could benefit from a “calibrated” suite that includes many code samples

75 with *labeled* bugs to evaluate and improve their verification tools.

76 In response to this need, we introduced Indigo [47], a microbenchmark suite capable of automati-

77 cally generating thousands of bug-free and buggy irregular parallel code patterns. While valuable,

78 these microbenchmarks are simple in nature and do not compute meaningful results. To address

79 this limitation, we expanded our efforts with the introduction of Indigo2 [45], which is based on 6

80 important graph algorithms and includes hundreds of bug-free CUDA, OpenMP, and parallel C++

81 implementations of each algorithm.

82 Building upon this foundation, we now present Indigo3, a fusion of the strengths of Indigo and

83 Indigo2. Indigo3 extends Indigo2 by incorporating additional programs and versions, including a

84 minimum spanning tree algorithm and hybrid parallelization of all codes, while also introducing a

85 broad range of bugs akin to those found in Indigo. The incorporated software defects include data

86 races, other synchronization issues, livelocks, deadlocks, and memory errors. Indigo3 methodically

87 and automatically inserts these bugs as well as all possible combinations thereof to generate the

88 codes in the suite. Since we manually select the applicable styles and bugs for each algorithm, all of

89 the generated codes can be compiled. The bug-free codes generate identical results to the serial

90 implementation of a validated algorithm. The file name of each code indicates which bugs, if any,

91 are present. In total, Indigo3 includes 2516 bug-free codes and 39,274 buggy codes. In this paper,

92 we use a subset of these codes to evaluate the effectiveness of current program verification tools

93 and highlight important avenues for future work in the program verification domain.

94 The paper makes the following main contributions.

95 • It introduces Indigo3, the first *labeled* verification benchmark suite that includes a wide

96 range of full-fledged buggy and bug-free irregular CUDA, OpenMP, and parallel C codes.

97

- It presents 13 largely orthogonal parallelization and implementation styles for CPUs and GPUs, yielding the 2516 bug-free versions of 7 key graph algorithms in Indigo3.

- It describes 15 types of common bugs and how they are systematically inserted into the bug-free base codes to create the 39,274 buggy programs in Indigo3.

- It evaluates 2 GPU and 3 CPU program verification tools on Indigo3 codes to explore how different implementation styles and bug types affect the tools' effectiveness.

The Indigo3 benchmark suite is publicly available in open source on Github [46].

The rest of the paper is organized as follows. Section 2 reviews relevant background information. Section 3 summarizes related work. Section 4 describes the design of the Indigo3 suite in detail. Section 5 discusses the experimental methodology. Section 6 evaluates several CPU and GPU program verification tools on buggy and bug-free codes from Indigo3. Section 7 summarizes the paper and draws conclusions.

## 2 BACKGROUND

This section provides background information on the main types of verification tools and the graph format used by the Indigo3 codes. It also presents an example of an irregular program.

### 2.1 Program verification

As outlined in the introduction, irregularity in programs is caused by input-dependent memory accesses and control flow. Such behavior makes codes harder to debug because even buggy codes will execute correctly for inputs that happen to yield (1) control flow that avoids the problematic code sections or (2) memory-access patterns that exclude the problematic data dependencies. In other words, only certain inputs may trigger the software defects present in the code. Moreover, the thread timing in parallel programs similarly only triggers software defects in some but not all executions of a program, even when using the same input. Together, this makes detecting bugs in irregular parallel programs particularly challenging.

Verification tools mainly consider the correctness of a program and are not concerned with performance. There are two main types of tools: static and dynamic. A dynamic tool observes runtime events while the program is executing [28]. Such tools tend to be relatively fast but only catch problems that actually occur during the observed run. For example, if the used input does not result in the code block containing a data race being executed, a dynamic tool will not detect the race. Hence, dynamic tools cannot prove the absence of data races even if they have not found any [43]. In other words, they typically produce no false positives but do produce false negatives.

Static verification tools, in contrast, examine the code before the program is run, for instance by analyzing the dependency graph, control flow, and data flow. Importantly, they consider all possible program behaviors and, in cases where they cannot prove that certain combinations of memory accesses or program paths never occur together, also include impossible behaviors. Hence, they typically produce no false negatives (if the bug lies in their search space) but do produce false positives. The generally large number and high complexity of code paths and memory-access patterns in irregular programs can quickly lead to a combinatorial explosion of possibilities to consider, making static tools potentially very slow on such codes.

In summary, irregular programs tend to be more challenging to verify than regular codes. This is true for both static and dynamic verification approaches.

### 2.2 Parallelization and implementation styles

There are numerous ways to parallelize irregular programs. We differentiate code optimizations from parallelization/implementation styles as follows. Parallelization and implementation styles

148 are broadly applicable to many graph algorithms. In contrast, code optimizations tend to be specific

149 to individual programs or a particular implementation of an algorithm. Due to this difference,

150 programmers are more likely to be able to apply a given parallelization or implementation style

151 when writing an irregular program than they are to apply a given code optimization. An example

152 of a parallelization style is using thread, warp, or block granularity in GPU codes [73], as described

153 in Section 4.1.8. An example of an implementation style is push versus pull (i.e., pushing data to

154 neighboring vertices or pulling data from neighbors), which is common in both CPU and GPU

155 graph codes [12], as described in Section 4.1.4.

156 Indigo3 employs numerous parallelization and implementation styles to create thousands of

157 irregular programs. This multitude of combinations yields a wide range of irregular codes and

158 behaviors for use in program verification and other domains. The styles present in Indigo3 are

159 described in Section 4.1.

### 160 2.3 Irregular code example

161 Breadth-First Search (BFS) is an important graph traversal algorithm that is used in many applica-

162 tions, such as finding the shortest path in networks, identifying connected communities, and

163 web crawling [51]. It labels all vertices with the shortest distance (in number of edges) from a

164 given source vertex. Section 4 uses BFS as an example to describe different parallelization and

165 implementation styles.

166 As shown in Algorithm 1, BFS starts by setting the distance of the source vertex to 0 and all other

167 distances to  $\infty$ . For each  $edge(v, n)$ , a new distance is calculated (i.e.,  $dist[v] + 1$ ) in each iteration.

168 Vertex  $n$ 's distance is updated if the new distance is shorter. These edge relaxation operations repeat

169 until the algorithm reaches a fixed point. The three *for all* loops are parallel assuming *dist* and

170 *updated* are accessed with atomic loads and stores. Whereas more work-efficient BFS algorithms

171 exist, this version generally yields more parallelism and is often used, especially in GPU codes.

172 Using the graph from Figure 1 as input and vertex 0 as the source, Table 1 shows the BFS

173 computation step by step. It initializes the distance of the source to 0 and all other distances to  $\infty$ .

174 In the first iteration, every active vertex  $v$  (i.e., whose distance is not  $\infty$ ) calculates a new distance

175 (i.e.,  $dist[v] + 1$ ) to its neighbors. The new distance for vertices 1 and 2 is 1, which is smaller than

176 their current distances, so they are updated to 1, as shown in the *Iter1* column of the table. Similarly,

177 in the second iteration, vertices 0, 1, and 2 calculate new distances to their neighbors and find

178 shorter distances for vertices 3 and 4. The next iteration is the final iteration because no new shorter

179 distances are found.

181 182 Table 1. Distance values computed in each step of the BFS algorithm on the example graph

| 183 Vertex | 184 Init     | 185 Iter1    | 186 Iter2 | 187 Iter3 |

|------------|--------------|--------------|-----------|-----------|

| 188 0      | 189 0        | 190 0        | 191 0     | 192 0     |

| 193 1      | 194 $\infty$ | 195 1        | 196 1     | 197 1     |

| 198 2      | 199 $\infty$ | 200 1        | 201 1     | 202 1     |

| 203 3      | 204 $\infty$ | 205 $\infty$ | 206 2     | 207 2     |

| 208 4      | 209 $\infty$ | 210 $\infty$ | 211 2     | 212 2     |

193 Note that this algorithm is input dependent and has both control-flow (e.g., line 12) and memory-

194 access (e.g., line 14) irregularity. It is impossible to statically predict the iteration count of the inner

195 *for-all* loop without knowing the input graph. Similarly, it is impossible to statically predict the

196 order in which the elements of the *dist* array will be written unless we know the input graph and

197 the order of the elements in the adjacency lists.

---

197 **Algorithm 1** Parallel breadth-first search

---

```

198 Require: Graph  $G = (V, E)$  and source vertex  $s$

199 1: for all vertices  $v \in V$  do

200 2:   if  $v = s$  then

201 3:      $dist[v] \leftarrow 0$

202 4:   else

203 5:      $dist[v] \leftarrow \infty$

204 6:   end if

205 7: end for

206 8:  $updated \leftarrow true$

207 9: while  $updated$  do

208 10:    $updated \leftarrow false$

209 11:   for all vertices  $v \in V$  do

210 12:     for all neighbors  $n \in adj[v]$  do

211 13:       if  $dist[n] > dist[v] + 1$  then

212 14:          $dist[n] \leftarrow dist[v] + 1$

213 15:          $updated \leftarrow true$

214 16:       end if

215 17:     end for

216 18:   end for

217 19: end while

```

218 **Ensure:** Each vertex is labeled with the shortest distance from  $s$

---

223 Implementing the loop over a vertex's neighbors (line 12) using the CSR format (see below)

224 provides the opportunity for out-of-bounds accesses, especially in the presence of vertices with no

225 neighbors. Moreover, the writes to the  $dist$  array as well as to  $updated$  are likely to yield data races

226 in a parallel implementation unless proper synchronization primitives are utilized. For example,

227 assume two threads are processing the graph from Figure 1. Since vertex 4 is a neighbor of vertices

228 2 and 3, a data race is possible if the two threads processing vertices 2 and 3, respectively, are

229 allowed to push their updated distance to vertex 4 in an unsynchronized manner. Depending on

230 internal timing, the distance of vertex 4 may end up as the distance from vertex 2, vertex 3, or some

231 other value, even a seemingly impossible arbitrary value [18].

232

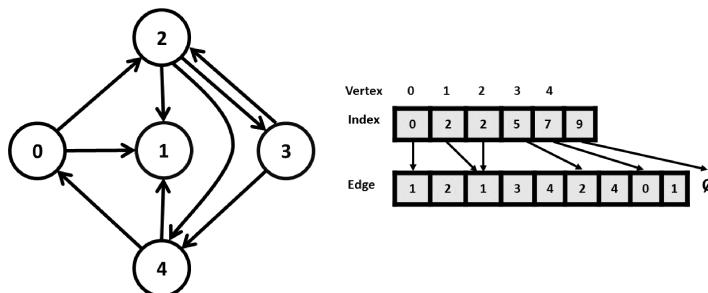

## 233 2.4 CSR graph format

234 The Compressed Sparse Row (CSR) format is one of the most widely used graph representations [27].

235 It is based on two dense arrays: an array of indices and an array of edges. The edge array holds the

236 concatenated adjacency lists of all vertices. The index array holds the starting position (index) of

237 each adjacency list. It has an extra element at the end specifying the size of the edge array. Figure 1

238 shows an example graph and its CSR representation.

239 For example, Pannotia [23] and Lonestar [38] use CSR inputs. All Indigo2 and, by extension,

240 Indigo3 input graph generators produce graphs in this format, meaning that every generated graph

241 can be used as an input for any code in our suites. Moreover, basing Indigo3 on the CSR format

242 makes it easy for users to use their own graphs. For this purpose, we provide converters from

243 several common formats (e.g., MatrixMarket, SNAP, and DIMACS) to our CSR format [20].

Fig. 1. Example graph (left) and corresponding CSR representation (right)

### 3 RELATED WORK

This section reviews prior benchmark suites of parallel programs (designed for either performance evaluation or verification), automatic code generation, and verification tools for parallel codes.

#### 3.1 Parallel benchmark suites

Many benchmark suites with parallel codes exist. They target a plethora of program behaviors, application domains, programming languages, and so on. The early suites that focus on parallel programs mainly comprise *regular* high-performance computing (HPC) applications. One of the first suites not focusing on HPC is PARSEC [16], released in 2008, which contains 12 regular parallel codes. With accelerators becoming popular, quite a few suites now include GPU code. The Rodinia [24] suite targets heterogeneous systems. It exhibits different types of parallelization, memory-access and data-communication patterns, synchronization, and power consumption through 23 regular parallel codes written in CUDA, OpenMP, and OpenCL. The SHOC [25] suite is designed to test the performance and stability of heterogeneous systems. It contains 25 regular parallel codes. Parboil [61] is a suite for evaluating the throughput of a range of applications, which can be used by programmers as a baseline to improve upon and/or for task-parallel programs. It includes 11 parallel codes. The Chai [32] suite includes 14 parallel codes to evaluate the shared virtual memory, memory coherence, and system-wide atomics of heterogeneous systems as well as data- and task-based workload partitioning between the CPU and GPU. Lonestar [38] contains 22 C++ and CUDA implementations of iterative graph algorithms. Pannotta [23] is an OpenCL suite of 8 applications for studying graph algorithms on GPUs. GraphBIG [50] contains implementations of representative data structures, workloads, and data sets from 21 real-world use cases of multiple application domains. GAPBS [13] not only specifies graph kernels, input graphs, and evaluation methodologies but also provides optimized reference implementations for 6 mostly irregular parallel codes written in OpenMP. GARDENIA [69] is a suite for studying irregular graph algorithms on accelerators. It includes 9 workloads from graph analytics, sparse linear algebra, and machine learning. GBBS [26] is a C++ suite of scalable, provably-efficient implementations of 20 graph problems for shared-memory multicore machines. It extends the Ligra interface with additional primitives and clearly defined cost bounds. Our Indigo3 suite, which is based on irregular graph algorithms, is much larger than these prior suites. It contains 2516 bug-free and 39,274 buggy codes.

295 There are also parallel benchmark suites in other domains. For instance, the NAS Parallel

296 Benchmarks for GPUs (NPB-GPU) [10] contain larger CFD applications with more complex routines

297 offloaded to the GPU. SPar [33] is a Domain-Specific Language (DSL) for developing parallel stream

298 applications. It uses standard C++ attributes to introduce annotations for tagging components

299 such as the stream sources and processing stages. Stream processing introduces a unique set of

300 challenges, including ensuring the correct order (e.g., video applications need to keep the order of

301 the frames). SPBench [30] is a framework for benchmarking such stream processing applications.

302 Many prior publications present ways to parallelize and optimize irregular graph codes. Several

303 of them discuss and evaluate at least some implementation styles, but no systematic study of

304 a large number of styles exists. Becchi et al. propose workload consolidation schemes [67] and

305 different parallelization templates [41] to increase the GPU utilization of programs with nested

306 parallelism. Wang et al. characterize dynamically formed parallelism and evaluate codes designed

307 to exploit them [66]. Nasre et al. present morph algorithms and provide insights into how other

308 morph algorithms can be efficiently implemented for GPUs [56]. In contrast, Indigo3 systematically

309 applies 13 general parallelization and implementation styles to a set of 7 key graph algorithms.

310 Indigo3 not only includes orders of magnitude more codes than other benchmark suites but also

311 a much larger number of inputs (which is important for data-dependent codes) and supports the

312 creation of user-defined subsets through configurable code and graph generators. Between the

313 thousands of codes and the unbounded number of inputs, Indigo3 allows users to run millions of

314 distinct tests and to create subsets for many different usage scenarios. Furthermore, as described

315 below, Indigo3 includes versions of its codes with deliberately planted bugs, giving users the ability

316 to methodically test and analyze program verification tools.

### 317 3.2 Benchmark suites for data-race detection

318 DataRaceBench [43] is a relatively recent suite of regular programs designed to evaluate CPU

319 data-race detection tools. It includes a set of kernels, some of which contain bugs. It comes with a

320 script to evaluate verifiers such as Helgrind, Archer, ThreadSanitizer, Intel Inspector, and Coderrect

321 Scanner. Verma et al. enhanced the suite by adding kernels that represent additional patterns

322 and include FORTRAN code [64]. RMRaceBench [59] is a microbenchmark suite to evaluate the

323 capabilities of RMA (Remote Memory Access) race detection tools for MPI RMA, OpenSHMEM,

324 and GASPI. It consists of about 100 synthetic race test cases for each programming model, aiming

325 to cover all possible race scenarios. In our prior work [48], we introduced the Indigo benchmark

326 suite, which contains common irregular code patterns. We systematically built variations of these

327 patterns to alter the control-flow and memory-access behavior and/or to introduce bugs, yielding

328 the thousands of OpenMP and CUDA microbenchmarks in the suite. In contrast, Indigo3 includes

329 full-fledged graph algorithms instead of only short parallel code patterns. This enabled us to

330 introduce additional parallelization bugs, yielding over 41,000 codes for verification-tool evaluation.

331 There are also benchmark suites for other parallel programming languages such as Go. Tu et

332 al. analyzed the causes, detection, and fixes of 171 concurrency bugs from 6 popular Go software

333 applications [62]. GoBench [71], the first suite for Go concurrency bugs, was introduced in 2021. It

334 contains 82 real bugs from 9 open source applications and 103 bug kernels. It covers traditional

335 and Go-specific concurrency issues. It uses configuration files in json format that record the type

336 of bugs and describe how to generate the corresponding Docker files. Indigo3's configuration file

337 similarly defines the types of codes and inputs to be included in the generated suite.

### 338 3.3 Automatic code generation

339 The source code annotation and variation in CREST [63] and DLBENCH [58] inspired the code

340 generation process in the Indigo suites. DLBENCH consists of a kernel generator, a profiler, and a

341 342 343

344 performance analyzer to generate parameterized variants of a synthetic microbenchmark. CREST is

345 a software framework that analyzes dependencies among GPU threads and performs source-level

346 restructuring. It uses source-code annotations in the code restructurer to control optimizations. In

347 our prior work on parallelization and implementation styles for graph algorithms, we took 6 key

348 graph algorithms, generated hundreds of CUDA, OpenMP, and parallel C++ versions of each of

349 them, and published them in the Indigo2 suite [45]. To determine which styles work well and under

350 what circumstances, we evaluated 1106 of the Indigo2 programs on various systems and inputs.

351 Most if not all of these styles have separately been described before. For example, Hong et al. [35]

352 propose a warp-centric programming method to improve the performance of applications with

353 heavily imbalanced workloads. Nasre et al. study data-driven and topology-driven implementations

354 to understand the tradeoffs [54] and investigate high-level methods to eliminate atomics in irregular

355 programs [52]. Pingali et al. discuss different styles to process nodes (e.g., topology-driven and

356 data-driven) and operators that modify the graph (e.g., morphs and local computations) [57]. Indigo2

357 combines these styles in hundreds of different ways, most of which have never been studied before.

358 Indigo3 goes a step further by introducing bugs into the codes of Indigo2 to enable the evaluation

359 of verification tools. Moreover, we ported the C++ codes from Indigo2 to C code in Indigo3 because

360 many program verification tools do not yet support C++.

### 362 3.4 Program verifiers

363 GKLEE [42] searches for correctness and performance bugs in GPU codes. It includes 40 benchmarks

364 that cover many CUDA program behaviors and problems such as thread divergence, bank conflicts,

365 deadlock, and data races. GPUVerify [15] comes with a suite of 163 CUDA and OpenCL kernels

366 drawn from public and commercial resources. Barracuda [29] is a concurrency bug detector for

367 CUDA programs. It handles a wide range of parallelism constructs including branch operations,

368 low-level atomics, and memory fences. It includes a concurrency bug suite with 53 programs, 12 of

369 which have data races. Since essentially no third-party verification suites with buggy GPU codes

370 exist, all of these tools include their own. ThreadSanitizer [8] is a dynamic data-race detector for

371 C/C++ programs and is part of Clang 3.2 and gcc 4.8. Archer [1] is a data-race detector for OpenMP

372 codes that combines static and dynamic techniques. CIVL [60] is a verification platform for parallel

373 C programs. Its intermediate language, CIVL-C, employs a general model of concurrency that can

374 represent OpenMP, CUDA, MPI, and Pthreads programs. CIVL includes front-ends to translate code

375 to CIVL-C and a back-end that uses symbolic execution and model-checking techniques to verify

376 CIVL-C programs. Compute-sanitizer (formerly cuda-memcheck) is a correctness-checking suite

377 for CUDA. It includes the memory access error and leak detection tool Memcheck [5], the shared

378 memory data access hazard detection tool Racecheck [6], the uninitialized global memory access

379 detection tool Initcheck [4], and the thread synchronization hazard detection tool Synccheck [7].

380 We evaluate several of these CPU and GPU program verification tools in the result section.

## 381 4 INDIGO3 DESIGN

383 The following subsections describe the various parallelization and implementation styles included in

384 the Indigo3 programs. We illustrate each style on the example of the breadth-first-search algorithm

385 described in Section 2.3. Note that, throughout this paper, we assume the shared data values (e.g.,

386 the distances) to be scalars and assume load and store instructions to atomically read and write

387 these values [19].

388 We wrote our graph codes using three parallel programming models: CUDA, OpenMP, and C

389 threads. CUDA programs operate at multiple levels of parallelism. 32 contiguous threads form

390 a warp and execute the same instruction in the same cycle (or are disabled). Sets of up to 32

391 warps (up to 1024 threads) form a block, and the blocks are grouped into a grid. CUDA provides

392

393 built-in variables for the thread and block indices as well as the block and grid dimensions. These

394 values are often combined by computing  $threadIdx.x + blockIdx.x * blockDim.x$  to form a global

395 index for assigning work to each thread, which we call  $gidx$  in our codes. OpenMP is based on

396 *pragma* compiler directives. Each such directive consists of a name followed by optional clauses.

397 For example, a clause can specify the scheduling to be used or a reduction operation. In Listing 11b

398 below, it selects dynamic scheduling. Since C11, C supports multithreading in the standard library.

399 It includes built-in types and functions for threads, atomics, mutual exclusion, and more.

## 400 4.1 Parallelization and implementation styles

401 This section describes the parallelization and implementation styles available in Indigo3.

### 402 4.1.1 Vertex-based vs. edge-based.

403 Graphs can be processed by iterating across either their vertices or their edges [72]. Listing 1a

404 shows vertex-based code, where every thread processes a different vertex  $v$  based on the unique

405 global thread index ( $gidx$ ) and iterates over all neighbors  $n$  of  $v$ . Listing 1b shows edge-based code

406 that assigns a different edge  $e = (v, n)$  to each thread.

407 The algorithm to be implemented and the graph representation (e.g., CSR format [31]) typically

408 determine which style is preferable. For instance, if the graph is represented by a set of adjacency

409 lists, it is often more natural to employ the vertex-based style. To streamline the discussion, we use

410 this style in the following subsections.

411 (a) Vertex-based

```

412

413

414

415     v = gidx;

416     if (v < nodes) {

417         beg = nbr_idx[v];

418         end = nbr_idx[v + 1];

419         for (i = beg; i < end; i++) {

420             n = nbr_list[i];

421             ...

422         }

423     }

424

425

426

427

428

429

430

431

432

433

434

```

415 (b) Edge-based

```

416     e = gidx;

417     if (e < edges) {

418         v = src_list[e];

419         n = dst_list[e];

420         ...

421     }

422

423

424

425

426

427

428

429

430

431

432

433

434

```

435 Listing 1. Vertex- and edge-based computations

### 436 4.1.2 Topology-driven vs. data-driven.

437 This style describes two ways to determine which data-structure elements to process [57]. The

438 topology-driven approach in Listing 2a simply processes all elements. In contrast, the data-driven

439 approach in Listing 2b only processes the elements that likely need to be updated, which are stored

440 in a worklist ( $wl$ ). For example, topology-driven BFS applies the relaxation function to all vertices of

441 the graph in each iteration. Data-driven BFS only applies the relaxation function to the vertices in

442 the worklist. Those vertices are in the worklist because their distance changed in the prior iteration.

443 The topology-driven style tends to yield more parallelism and is easier to implement. The data-

444 driven style is more work efficient and, therefore, often results in better performance, especially

445 for iterative algorithms that operate on high-diameter graphs.

### 446 4.1.3 Duplicates in worklist vs. no duplicates in worklist.

447 This style, which only applies to data-driven implementations, specifies whether or not duplicate

448 items are allowed on the worklist [55]. In codes that allow duplicates, as shown in Listing 3a, each

449 thread can push a vertex onto the worklist regardless of whether the worklist already contains that

450 vertex. In programs that do not allow duplicates, as shown in Listing 3b (where  $itr$  denotes the

451 current iteration), the threads may only add a vertex to the worklist if it is not already there.

```

442          (a) Topology-driven

443

444      v = gidx;

445      if (v < nodes) {

446          ...

447      }

448

449          (b) Data-driven

450

451      idx = gidx;

452      if (idx < worklist_size) {

453          v = worklist[idx]

454          ...

455      }

```

Listing 2. Topology- and data-driven computations

Disallowing duplicates eliminates redundant work in the next iteration. Moreover, it caps the size of the worklist. However, it incurs additional synchronization overhead and requires extra state tracking (*stat*) to determine whether a vertex is already on the worklist.

```

456          (a) Duplicates in worklist

457

458      idx = atomicAdd(&worklist_size, 1);

459      worklist[idx] = v;

460

461          (b) No duplicates in worklist

462

463      if (atomicMax(&stat[v], itr) != itr) {

464          idx = atomicAdd(&worklist_size, 1);

465          worklist[idx] = v;

466      }

```

Listing 3. Duplicates and no duplicates in worklist

**4.1.4 Push vs. pull.**

The data flow in programs that update vertex data can be either push-based, where data is pushed from a vertex to its neighbors, or pull-based, where data is pulled from the neighbors to the vertex [14]. For example, in push-style BFS, shown in Listing 4a, a thread reads the vertex distance, adds 1, and updates the neighbor if the new distance is shorter. In pull-style BFS, shown in Listing 4b, the thread reads the neighbor's distance, adds 1, and updates the vertex distance if it is shorter.

Using the push style, different threads may update the same neighboring vertex. In contrast, the pull style guarantees that there is only a single writer per vertex. Moreover, it allows the update to be factored out of the loop (not done in Listing 4b), thus reducing memory accesses. Having said that, push is sometimes a more natural fit for the underlying algorithm and preferred in combination with a data-driven approach because only the neighbors that were actually updated need to be placed on the worklist.

```

476          (a) Push

477

478      for (i = beg; i < end; i++) {

479          n = nbr_list[i];

480          new_dist = dist[v] + 1;

481          atomicMin(&dist[n], new_dist);

482      }

483

484          (b) Pull

485

486      for (i = beg; i < end; i++) {

487          n = nbr_list[i];

488          new_dist = dist[n] + 1;

489          atomicMin(&dist[v], new_dist);

490      }

```

Listing 4. Push and pull data flow

**4.1.5 Read-write vs. read-modify-write.**

Many graph algorithms conditionally update vertex data, where a thread reads the current value, performs a computation with it, and writes the new value if it meets a certain condition. For example, in BFS, the vertex distance is only updated if the new distance is shorter. This read-write approach works in certain situations, such as in Listing 5a, because the updates are monotonic

and the algorithm is resilient to temporary priority inversions [53]. The read-modify-write style shown in Listing 5b is more general as it does not suffer from this problem, but it requires an atomic read-modify-write operation, which tends to be slower and hampers parallelism.

```

491

492

493

494

495           (a) Read-write

496

497           old_dist = dist[v];

498           if (new_dist < old_dist)

499               dist[v] = new_dist;

500

501

502           (b) Read-modify-write

503

504           atomicMin(&dist[v], new_dist);

505

506

507

508

509

510

```

Listing 5. Read and write operations

#### 4.1.6 Non-deterministic vs. deterministic.

The unpredictable timing of threads can introduce internal non-determinism in some parallel codes [17]. In Listing 6a, multiple threads may write an element of the *dist* array that is read by another thread. Depending on which thread performed the last write before the read, a different value may be read, leading to the computation of a different new distance. Any non-final distance value will be overwritten in subsequent iterations, meaning the ultimate result is deterministic, but the number of iterations may differ from run to run. Note that we only study programs in this paper where the final result is deterministic.

To make the code internally deterministic, Listing 6b uses two arrays, one that is only read (*dist1*) and another that is updated (*dist2*). However, in this approach, the computation can no longer take advantage of results generated in the same iteration, which may slow down the execution. On the upside, the deterministic code will always require the same number of iterations for a given input, which can simplify debugging [11].

```

516

517           (a) Non-deterministic

518

519           new_dist = dist[v] + edge_weight;

520           atomicMin(&dist[n], new_dist);

521

522

523           (b) Deterministic

524

525           new_dist = dist1[v] + edge_weight;

526           atomicMin(&dist2[n], new_dist);

527

528

529

530

531

532

```

Listing 6. Non-deterministic and deterministic updates

#### 4.1.7 Persistent vs. non-persistent.

This style only applies to GPU codes. The persistent style, shown in Listing 7a, uses as many threads as the GPU can concurrently schedule on its SMs [34], meaning a thread may need to process multiple vertices (as is done in CPU codes). In contrast, the non-persistent style in Listing 7b launches at least as many threads as the input has vertices and assigns no more than one vertex to each thread. For graphs where the number of vertices exceeds the number of threads that can concurrently run on the SMs, the GPU will automatically schedule batches of threads until all threads have executed. The persistent style is a little more complex to implement but may improve performance in cases where common subexpressions can be precomputed or common data preloaded and then reused.

#### 4.1.8 Thread vs. warp vs. block.

This variation only applies to GPU codes. It refers to the granularity at which the program processes the vertices. Threads, warps, and blocks are the three hardware-supported granularities. In thread-based BFS, each thread processes all neighbors of a vertex as shown in Listing 8a. In warp- or block-based BFS, the entire warp or block processes the neighbors of a single vertex, respectively, as

```

540

541         (a) Persistent

542         threads = blockDim.x * gridDim.x;

543         for (v = gidx; v < nodes; v += threads)

544             ...

545

546         (b) Non-persistent

547         v = gidx;

548         if (v < nodes)

549             ...

550

551

552

```

Listing 7. Persistent and non-persistent threads

546

547 shown in Listings 8b and 8c. Both warp- and block-based processing yields a two-level parallelization

548 scheme: the vertices are distributed across the warps or blocks while the neighbors are distributed

549 across the threads within the warp or block. This approach is useful for reducing load imbalance

550 when processing high-degree vertices in power-law graphs [9]. However, it is typically not useful

551 for low-degree graphs such as road networks.

552

553

```

554         (a) Thread

555

556         beg = nbr_idx[v];

557         end = nbr_idx[v + 1];

558         for (i = beg; i < end; i++)

559             ...

560

561         (b) Warp

562

563         lane = threadIdx.x % warpSize;

564         beg = nbr_idx[v];

565         end = nbr_idx[v + 1];

566         for (i = beg + lane; i < end; i += warpSize)

567             ...

568

569

570         (c) Block

571

572         beg = nbr_idx[v];

573         end = nbr_idx[v + 1];

574         for (i = beg + threadIdx.x; i < end; i += blockDim.x)

575             ...

576

577

578

579

```

Listing 8. Thread, warp, and block parallelization

576

577

578

579

580

581

582

583

584

585

586

587

588

589

590

591

592

593

594

595

596

597

598

599

600

#### 4.1.9 Global-add vs. block-add vs. reduction-add.

601 Reductions are widely used in parallel computing to combine multiple independently computed

602 partial results into a single global result using a binary associative operator [44]. For example,

603 multiple threads may need to add the partial sums they computed to a global sum.

604 We employ three reduction styles in our GPU codes. The first approach directly updates a shared

605 global variable using atomic operations, as shown in Listing 9a. The second approach makes use

606 of faster block-level atomics. All threads of a block first compute a block-local solution in the

607 GPU’s “shared memory”, and only one thread updates the global solution as shown in Listing 9b.

608 This minimizes the number of slower global atomics. The third approach utilizes not only shared-

609 memory buffers for local results but also warp-level primitives to quickly perform warp and block

610 reductions as outlined in Listing 9c. This implementation is more complex but tends to be faster as

611 it avoids most memory accesses.

612

613

614

615

616

617

618

619

620

621

622

623

624

625

626

627

628

629

630

631

632

633

634

635

636

637

638

639

640

641

642

643

644

645

646

647

648

649

650

651

652

653

654

655

656

657

658

659

660

661

662

663

664

665

666

667

668

669

670

671

672

673

674

675

676

677

678

679

680

681

682

683

684

685

686

687

688

689

690

691

692

693

694

695

696

697

698

699

700

701

702

703

704

705

706

707

708

709

710

711

712

713

714

715

716

717

718

719

720

721

722

723

724

725

726

727

728

729

730

731

732

733

734

735

736

737

738

739

740

741

742

743

744

745

746

747

748

749

750

751

752

753

754

755

756

757

758

759

760

761

762

763

764

765

766

767

768

769

770

771

772

773

774

775

776

777

778

779

780

781

782

783

784

785

786

787

788

789

790

791

792

793

794

795

796

797

798

799

800

801

802

803

804

805

806

807

808

809

810

811

812

813

814

815

816

817

818

819

820

821

822

823

824

825

826

827

828

829

830

831

832

833

834

835

836

837

838

839

840

841

842

843

844

845

846

847

848

849

850

851

852

853

854

855

856

857

858

859

860

861

862

863

864

865

866

867

868

869

870

871

872

873

874

875

876

877

878

879

880

881

882

883

884

885

886

887

888

889

890

891

892

893

894

895

896

897

898

899

900

901

902

903

904

905

906

907

908

909

910

911

912

913

914

915

916

917

918

919

920

921

922

923

924

925

926

927

928

929

930

931

932

933

934

935

936

937

938

939

Listing 9. Different reductions in CUDA

```

601                                (a) Atomic reduction

602

603      #pragma omp parallel for

604      for (i = beg; i < end; i++) {

605          ...

606          #pragma omp atomic

607          sum += val;

608      }

609

610                                (b) Critical reduction

611

612      #pragma omp parallel for

613      for (i = beg; i < end; i++) {

614          ...

615          #pragma omp critical

616          sum += val;

617      }

618

619                                (c) Clause reduction

620

621      #pragma omp parallel for reduction(+: sum)

622      for (i = beg; i < end; i++) {

623          ...

624          sum += val;

625      }

```

Listing 10. Different reductions in OpenMP

#### 4.1.11 Default scheduling vs. dynamic scheduling.

OpenMP provides a convenient way to parallelize certain *for* loops using a *parallel for* directive. By default, as shown in Listing 11a, this directive statically assigns each thread a contiguous chunk of loop iterations. In contrast, the dynamic schedule in Listing 11b assigns iterations at runtime whenever a thread is ready to execute another iteration. This improves the load balance but incurs overhead.

```

622

623             (a) Default scheduling

624

625             #pragma omp parallel for

626             for (v = 0; v < nodes; v++) {

627                 ...

628             }

629

630             (b) Dynamic scheduling

631

632             #pragma omp parallel for schedule(dynamic)

633             for (v = 0; v < nodes; v++) {

634                 ...

635             }

```

Listing 11. Default and dynamic loop scheduling

#### 4.1.12 Blocked vs. cyclic.

When parallelizing the iterations of a *for* loop, a blocked schedule assigns a contiguous chunk of iterations to each thread, as shown in Listing 12a. If the iterations' running times correlate with their loop index, a block distribution can lead to load imbalance. The cyclic schedule in Listing 12b assigns the iterations in a round-robin fashion to the threads, which improves the load balance in this scenario. A blocked schedule usually has better data locality in CPUs because each thread

638 accesses contiguous memory locations. However, a cyclic schedule yields better data locality in

639 GPUs because of coalesced memory accesses, i.e., combining multiple memory accesses into a

640 single memory transaction.

(a) Blocked scheduling

```

642

643

644 beg = tid * nodes / threads;

645 end = (tid + 1) * nodes / threads;

646 for (v = beg; v < end; v++) {

647   ...

648 }

```

(b) Cyclic scheduling

```

649 for (v = tid; v < nodes; v += threads) {

650   ...

651 }

```

Listing 12. Blocked and cyclic scheduling

## 4.2 Common bugs

652 As discussed in the background section, the input-dependent behavior makes bug detection partic-

653 ularly challenging in irregular codes. Additionally, certain parallelization bugs, such as data

654 races, can be difficult to find because they are thread-timing dependent and may not manifest every

655 time the code is executed. To help the community develop better tools and techniques to identify

656 such bugs, Indigo3 contains versions of all its codes with intentionally planted software defects,

657 including parallelism bugs (e.g., data races, missing barriers, livelock, and deadlock), memory bugs,

658 and other serial bugs. Table 2 lists the parallelism-related bug types, Table 3 the memory bug types,

659 and Table 4 the remaining bug types available in Indigo3.

Table 2. Parallelism bug types

| Name        | Description                   | Bug-free example                                   | Buggy example                                    |

|-------------|-------------------------------|----------------------------------------------------|--------------------------------------------------|

| RaceBug     | Missing atomic operation      | atomicAdd(val, 1);                                 | val++;                                           |

| SyncBug     | Missing barrier               | syncthreads();                                     | //no barrier                                     |

| MixSyncBug  | Mixing synchronization        | critical(dist[src], s);<br>critical(dist[dst], d); | critical(dist[src], s);<br>atomic(dist[dst], d); |

| LivelockBug | Actively running w/o progress | if (newd < d)<br>then d = newd;                    | if (newd <= d)<br>then d = newd;                 |

| DeadlockBug | Some threads wait forever     | if (v < nodes)<br>then ...;<br>syncthreads();      | if (v < nodes)<br>then syncthreads();            |

| GuardBug    | Non-atomic check              | atomicMax(d, m);                                   | if (d < m)<br>then atomicMax(d, m);              |

677 Most of these bug types are well known. The GuardBug is a data race where a variable is accessed

678 both atomically and non-atomically (e.g., in an attempt to avoid the slower atomic operation when

679 it is not needed). Unlike the BoundsBug, the NbrBoundsBug often does not result in accesses past

680 the end of an array but only past the end of one of the concatenated adjacency lists in the CSR's

681 edge array (see Figure 1), making it harder to detect. The WorkloadBug occurs when the problem

682 size is not evenly divisible by the number of threads. It ends up not processing all of the workload.

683 Each bug is independent in the sense that it causes a software defect no matter if there are

684 any other bugs in the code. However, one bug may interact with another and yield more complex

685 program behavior. For example, the memory bug "BoundsBug" can lead to out-of-bounds accesses,

Table 3. Memory bug types

| Name             | Description                               | Bug-free example                            | Buggy example                           |

|------------------|-------------------------------------------|---------------------------------------------|-----------------------------------------|

| NameBug          | Wrong variable                            | for (...; v < nodes; ...)                   | for (...; v < edges; ...)               |

| ExcessThreadsBug | Too many threads                          | if (gidx < nodes)                           | //no check                              |

| BoundsBug        | Out-of-bounds access                      | type buffer[size];<br>a = buffer[size - 1]; | type buffer[size];<br>a = buffer[size]; |

| NbrBoundsBug     | Exceeding adjacency list                  | for (...; nbr < end; ...)                   | for (...; nbr <= end; ...)              |

| UninitializedBug | Data not fully initialized                | data[v] = init;                             | //no initialization                     |

| ShadowBug        | Re-declaring a variable in an inner scope | int i;<br>for (i = v; ...);                 | int i;<br>for (int i = v; ...);         |

Table 4. Other bug types

| Name        | Description               | Bug-free example                                        | Buggy example                                    |

|-------------|---------------------------|---------------------------------------------------------|--------------------------------------------------|

| OverflowBug | Range overflow            | val = INT_MAX;<br>if (val != INT_MAX)<br>then val += d; | val = INT_MAX;<br>val += d;                      |

| WorkloadBug | Incorrect work assignment | gidx * size / threads;                                  | chunksize = size / threads;<br>gidx * chunksize; |

which may trigger race conditions if multiple threads access the same out-of-bounds memory address. Hence, combining “BoundsBug” with “RaceBug” may increase the chance of data races.

Note that combining bugs increases the number of codes exponentially. For example, 3 bugs yield 7 buggy combinations (3 versions with 1 bug, 3 versions with 2 bugs, and 1 version with 3 bugs). Hence, adding just 3 bugs results in 7 times more codes than there are bug-free codes. Since at least 3 of the 14 bugs listed in Tables 2, 3, and 4 are applicable to each of our bug-free codes, we end up with nearly 40,000 buggy codes in Indigo3.

### 4.3 Annotation tags

Combining the implementation styles and bugs yields thousands of codes for each algorithm, making it nearly impossible and not maintainable to produce them by hand. Hence, we wrote just a few source files per algorithm and expressed all variations using annotation tags. These tags are similar to the annotation comments in the Java Modeling Language (JML) [40]. Indigo3 automatically generates the codes from the annotated source files. This code generation framework enables us and others to easily introduce additional implementation styles and bugs in the future by adding more tags.

Listing 13 provides an excerpt of annotated CUDA code. We use the syntax “`/*@tag@*/`” (without the quotes) to label alternative statements on a line of code. Each tag is associated with the code that follows it. The associated code will be generated when the tag is activated. Only one tag per line can be active at a time. Tags with different names on different lines are *independent* and all combinations can be generated. However, tags on different lines with the same name are *dependent*, meaning the same alternative will be used on all lines with the same tag names. Furthermore, matching tags affixed with “+” and “-”, such as Lines 3 and 5 in Listing 13, extend the activation idea to a block of code and enable the nesting of tags. This provides more flexibility and allows

736 us to express complex interactions between tags. Listing 14 shows the generated codes for the

737 persistent and non-persistent style that have no name bug and no bounds bug.

738

```

739 1 /*@NoNameBug@*/ const int gsize = nodes; /*@NameBug@*/ const int gsize = edges;

740 2

741 3 /*@+NonPersist@*/

742 4 /*@NoBoundsBug@*/ if (v < gsize) { /*@BoundsBug@*/ if (v <= gsize) {

743 5 /*@-NonPersist@*/

744 6

745 7 /*@+Persist@*/

746 8 /*@NoBoundsBug@*/ for (idx = v; idx < gsize; idx += threads) { /*@BoundsBug@*/ for

747 9 (idx = v; idx <= gsize; idx += threads) {

748 10 /*@-Persist@*/

749 11 }

750

751

752

753

754 1 const int gsize = nodes;

755 2 if (v < gsize) {

756 3 ...

757 4 }

```

Listing 13. Tag-based annotations to generate code variations

(a) Non-persistent code example

(b) Persistent code example

```

758 1 const int gsize = nodes;

759 2 for (idx = v; idx < gsize; idx += threads) {

760 3 ...

761 4 }

```

758 Listing 14. Examples of generated code

759

760 We believe it is important for the generated codes to be human readable so they can be manually

761 inspected and understood. Thus, Indigo3 does not use synthetic variable names. It automatically

762 indents the code, which is necessary when variations introduce or remove *if* statements, and it

763 eliminates blank lines due to empty tags. The file name of each generated program specifies the

764 algorithm followed by all activated tags to make it easy to identify which file contains which code

765 and what bugs are present, if any.

#### 766 4.4 Subset selection

767 Combining the various implementation styles with all meaningful bug combinations yields 41,790

768 codes. Running them through a reasonable set of inputs results in millions of tests, which may take

769 too long to run. To control the execution time, the suite supports the generation of user-defined

770 subsets of the codes.

771 The code filtering is accomplished through a configuration file. We adopted this approach from

772 Indigo [49] and chose it to simplify the subset creation. The configuration file lists the desired code

773 versions and filters out the rest. For example, the user can elect to only generate bug-free codes.

774 TACO [37] similarly creates tensor algebra kernels based on user-defined constraints. With this

775 approach, an Indigo3 user can, for instance, generate a small subset for testing and later a more

776 extensive subset to perform a detailed study.

777 The configuration file comprises 4 rules to manage the code generation as shown in Listing 15.

778 The user can select the target graph algorithms, bug types, implementation styles, and data types.

779 The example in Listing 15 generates every possible implementation style for all 7 graph algorithms,

780 does not insert any bugs, and only uses the integer data type. The supported algorithms are

781 breadth-first search (bfs), single-source shortest paths (sssp), connected components (cc), maximal

782 independent set (mis), minimum spanning tree (mst), triangle counting (tc), and page rank (pr).

785 Table 5 lists the available choices for the code filters. As a shorthand, Indigo3 also supports the

786 keywords “all” and “only”. The former turns off any filtering, and the latter means only code that

787 includes the required tag will be generated. For example, putting “only RaceBug” in the bug option

788 rule generates only the codes that have a race bug but do not include any other bugs.

```

789 1 CODE:

790 2   algorithm: {all}

791 3   bug_option: {nobug}

792 4   style_option: {all}

793 5   dataType: {IntType}

```

Listing 15. Sample configuration file

Table 5. Choices for managing the code generation

| Rule         | Choices                                       |

|--------------|-----------------------------------------------|

| Algorithm    | all, bfs, sssp, cc, mis, mst, tc, pr          |

| Bug option   | all, nobug, bug names from Tables 2, 3, and 4 |

| Style option | all, style names from Section 4.1             |

| Data type    | all, IntType, FloatType, LongType, DoubleType |

## 5 EXPERIMENTAL METHODOLOGY

### 5.1 Hardware and software

806 The system we used for running the parallel C and OpenMP codes has two Intel Xeon Gold 6226R

807 CPUs with 16 cores each. Hyperthreading is enabled, meaning the 32 cores can run 64 simultaneous

808 threads. The main memory has a capacity of 128 GB. The operating system is Fedora 37. We

809 ran the CUDA codes on an RTX 4090 GPU with 16,384 processing elements distributed over 128

810 multiprocessors. We compiled the CPU codes with *clang* 14.0.5 using the “-O3 -march=native”

811 optimization flags, including “-fopenmp” for the OpenMP and “-pthread -std=c11” for the parallel C

812 codes. We used *nvcc* 12.0.140 with the “-O3 -arch=sm\_89” flags to compile the CUDA codes. We ran

813 the CPU codes with 64 threads. For the CUDA experiments, we launched 512 threads per block.

### 5.2 Codes and inputs

814 Our test codes are based on 7 graph algorithms, namely Breadth-First Search, Connected Components,

815 Single Source Shortest Path, Maximal Independent Set, Triangle Counting, PageRank, and

816 Minimum Spanning Tree. We selected these algorithms because they are also frequently included

817 in other benchmark suites. Since many existing program-analysis tools do not support the complex

818 feature set of C++, we ported the Indigo2 C++ codes to C before including them in Indigo3. We

819 generated the 2516 bug-free codes in the Indigo3 suite from these algorithms by applying the

820 implementation and parallelization styles listed in Section 4. Since several of the code-verification

821 tools we evaluated do not support the libcu++ library and parallel C, we removed the parallel C

822 and CUDA codes that use this library from our tests, leaving 1924 bug-free codes. Half of them

823 operate on 32-bit data types and the other half on 64-bit data types. To keep the running times

824 manageable, we only evaluate the 32-bit data types in this paper.

825 To ensure compatibility with the iGuard [36] tool, we introduced the optional use of *atomicAdd(0)*

826 and *atomicExch* for implementing atomic load and store operations in CUDA. Whereas these

827 alternatives incur some performance overhead, they do broaden the range of tools to which our

828

Table 6. Graph information

| Name             | Type      | Origin | Vertices  | Edges      | Size (MB) | $d_{avg}$ | $d_{max}$ | $d \geq 32$ | $d \geq 512$ | Diameter |

|------------------|-----------|--------|-----------|------------|-----------|-----------|-----------|-------------|--------------|----------|

| soc-LiveJournal1 | community | SNAP   | 4,847,571 | 85,702,474 | 362.2     | 17.7      | 20,333    | 14.0%       | 0.125%       | 21       |

| rmat22.sym       | RMAT      | Galois | 4,194,304 | 65,660,814 | 542.1     | 15.7      | 3,687     | 12.4%       | 0.045%       | 19       |

| USA-road-d.NY    | road map  | Dimacs | 264,346   | 730,100    | 6.9       | 2.8       | 8         | 0.0%        | 0.000%       | 721      |

codes can be applied. In summary, Indigo3 includes parallel C, OpenMP, and CUDA codes as well as alternative atomic load and store implementations for the CUDA tools that need it.

To thoroughly test the programs, we ran each of them on 67 input graphs, including one social network, one random graph, and one road map. Table 6 provides information on the type, size, and degree distribution of the three graphs. The remaining 64 inputs are all possible undirected graphs with four vertices. They are generated by enumerating all possible symmetric adjacency matrices.

### 5.3 Verification tools

We evaluate the effectiveness of 5 program-verification tools. Table 7 presents the type (static or dynamic), version, and the targeted programming model of each tool. Archer [1] is a data-race detector for OpenMP codes that combines static and dynamic techniques. ThreadSanitizer [8] is a dynamic data-race detector for C/C++ programs and is part of Clang 3.2 and gcc 4.8. We also tested CIVL [60], but being a static analyzer, it ended up being too slow to be included in our study.

iGUARD [36] instruments GPU programs to detect races in them. It is based on NVIDIA’s NVBit binary instrumentation framework [65]. Compute Sanitizer [3] is a correctness-checking suite included in the CUDA toolkit. It contains multiple tools to perform different types of checks. The *memcheck* [5] tool detects out-of-bounds and misaligned memory accesses. It also reports hardware exceptions. The *racecheck* [6] tool flags shared memory data access hazards that can cause data races. The *initcheck* [4] tool checks for accesses to uninitialized data in global memory. The *synccheck* [7] tool reports cases where the application attempts invalid uses of synchronization primitives.

To accommodate the unique requirements of Archer and iGuard, which demand specific earlier versions of libraries and CUDA drivers, we implemented distinct setups to make them work. For Archer, we leveraged a Docker container environment, whereas iGuard is tested on a separate system with a Titan V GPU, CUDA driver version 418.39, and nvcc 10.1.

Table 7. Tested Verification Tools

| Tool                      | Type           | Version  | C/OpenMP | CUDA |

|---------------------------|----------------|----------|----------|------|

| Clang Static Analyzer [2] | Static         | 18.0.0   | Yes      | No   |

| Archer [1]                | Dynamic/Static | 2.0.0    | Yes      | No   |

| ThreadSanitizer [8]       | Dynamic        | 9.3.1    | Yes      | No   |

| iGuard [36]               | Dynamic        | 1.0      | No       | Yes  |

| Compute Sanitizer [3]     | Dynamic        | 2023.2.2 | No       | Yes  |

### 5.4 Metrics

To evaluate each tool, we measured the four counts shown in Table 8 to produce a confusion matrix. A tool generates a false positive (FP) if it reports a non-existing bug. If it correctly detects an existing bug, it is a true positive (TP). It is a true negative (TN) if the tool does not detect any bug in a bug-free program. If it fails to detect an existing bug, it is a false negative (FN). Note that,

883 for a bug-free program, a tool can only generate either an FP or TN result. Similarly, it can only

884 generate either a TP or FN result for a buggy program.

886 Table 8. Confusion Matrix

|                        | <b>Bug-free code</b> | <b>Buggy code</b>   |

|------------------------|----------------------|---------------------|

| <b>Positive report</b> | False positive (FP)  | True positive (TP)  |

| <b>Negative report</b> | True negative (TN)   | False negative (FN) |

892 To make the results easier to understand, it is common to convert them into the three higher-is-

893 better metrics *accuracy* ( $A$ ), *precision* ( $P$ ), and *recall* ( $R$ ), which are defined as follows:

$$894 A = (TP + TN) / (TP + FP + TN + FN),$$

$$895 P = TP / (TP + FP), \text{ and}$$

$$896 R = TP / (TP + FN).$$

897 The accuracy reflects the probability that the tool produces a correct report, the precision denotes

898 the probability of correctly detecting a bug out of all positive reports, and the recall measures the

899 probability of detecting a bug within all buggy codes.

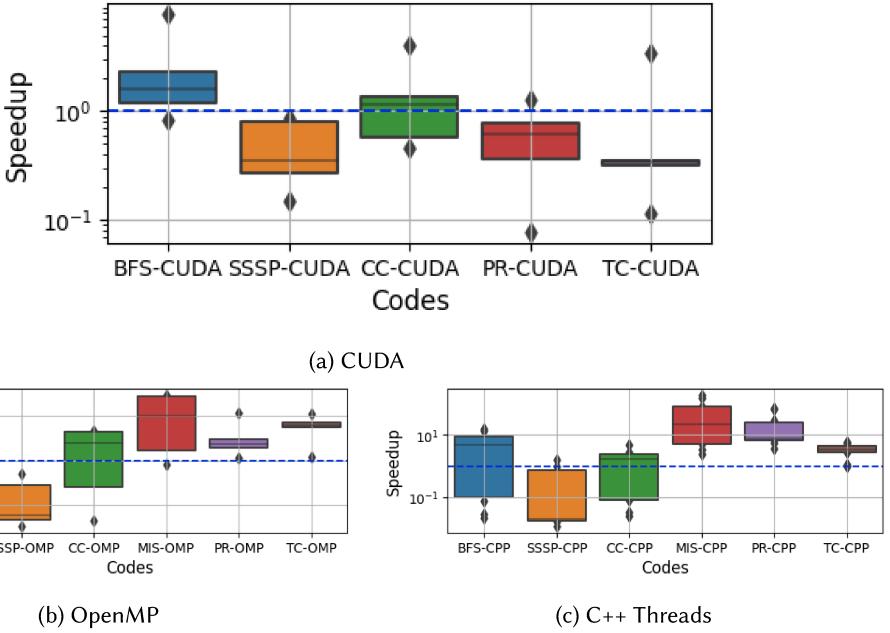

## 900 6 RESULTS

901 Applying all possible combinations of the 15 supported bug types to the 962 bug-free codes would

902 result in hundreds of thousands of codes, and evaluating them on our 67 inputs would take many

903 months. To make the running time manageable, we select four sets of codes for our experiments:

904 (1) bug-free codes, (2) codes that have one parallelism bug, (3) codes that have one memory bug,

905 and (4) codes that combine one parallelism bug. Additionally, we compare the generated bug-free

906 codes with optimized third-party codes (i.e., Lonestar and Gardenia).

### 907 6.1 Bug-free codes

908 For the bug-free codes, if a tool reports a data race or memory bug, we count it as a false positive.

909 Tables 9 and 10 list the tool, programming language, the number of evaluated codes, the number of

910 these codes yielding a false positive for at least one input, the number of runs (i.e., codes  $\times$  inputs),

911 and the number of runs yielding a false positive. For example, ThreadSanitizer reports data races

912 for 145 out of 12,596 runs, and these 145 runs stem from 4 bug-free codes.

913 Table 9 shows that Clang does not find any bugs in the bug-free CPU codes. Since it is a static

914 analyzer that runs at compile time, it does not use any inputs. ThreadSanitizer reports non-existent

915 data races in 4 codes, 2 of which use an OpenMP clause reduction and the other 2 swap two

916 pointers to arrays after each iteration. Archer reports non-existent data races in 10 codes, all of

917 which use an OpenMP clause reduction. Evidently, the internal implementation of the OpenMP

918 reduction confuses both ThreadSanitizer and Archer. Additionally, ThreadSanitizer appears to

919 not understand the implicit barrier at the end of a parallel code section, which is why swapping

920 pointers between 2 such code sections yields false positives.

921 We made sure that the reported bugs are not actual bugs as follows. For the reduction problem,

922 we changed the clause reduction to a critical section. With this change, ThreadSanitizer and Archer

923 no longer output any data race warnings. For the swap problem, we duplicated the parallel code

924 section and switched the array names in the second copy to eliminate the need for swapping the

925 pointers. The modified code uses one copy in every odd iteration and the other copy in every even

926 iteration. With this change, ThreadSanitizer no longer gives any data race warnings.

927 Table 10 shows that iGuard reports non-existent data races in 36 of the bug-free GPU codes, and

928 Compute Sanitizer does not report any bugs. The false positives for iGuard stem from three scenarios:

932 codes that launch kernels at different granularities (e.g., thread-based and warp-based), codes that

933 swap array pointers between kernels, and codes that access memory at different granularity (e.g.,

934 integer and Boolean arrays).

935 We modified the codes as follows to explore the reasons for the false positives and make sure

936 they are not true positives. For the first scenario, we changed the kernels so that we could launch

937 all of them at the same granularity. For the second condition, we first tried the idea outlined above

938 to remove the swap. Since this did not help, we resorted to only launching 1 kernel at at time on the

939 GPU and running the rest of the code on the CPU. For the third scenario, we converted the Boolean

940 array into an integer array. These changes removed all iGuard data race reports. We believe the

941 first two types of false positives arise because iGuard ignores the implicit barrier between kernel

942 launches. The third type arises because we used iGuard’s default memory-access granularity of 4

943 bytes, which is too coarse for Boolean arrays.

944

945 Table 9. Results for bug-free CPU codes

946

| Tool                  | Language | Codes | FP Codes  | Runs   | FP Runs    |

|-----------------------|----------|-------|-----------|--------|------------|

| Clang Static Analyzer | OpenMP   | 188   | 0 (0.0%)  | n/a    | n/a        |

| ThreadSanitizer       | OpenMP   | 188   | 4 (2.1%)  | 12,596 | 145 (1.2%) |

| Archer                | OpenMP   | 188   | 10 (5.3%) | 12,596 | 592 (4.7%) |

951

952 Table 10. Results for bug-free GPU codes

953

| Tool              | Language | Codes | FP Codes  | Runs   | FP Runs      |

|-------------------|----------|-------|-----------|--------|--------------|

| iGuard            | CUDA     | 774   | 36 (4.6%) | 51,858 | 1,974 (3.8%) |

| Compute Sanitizer | CUDA     | 774   | 0 (0.0%)  | 51,858 | 0 (0.0%)     |

## 954 6.2 Parallelism bug detection

955 Tables 11 and 12 show the results for the Indigo3 codes with exactly one parallelism bug. If a tool

956 reports a data race or a missing barrier, we count it as a true positive result.

957 As Table 11 shows, the Clang Static Analyzer does not detect any of the bugs, presumably

958 because it statically analyzes the program without considering inputs or runtime behavior. Both

959 ThreadSanitizer and Archer detect some of the bugs, with ThreadSanitizer performing a little better.

960 The GPU results in Table 12 show that both iGuard and Compute Sanitizer find a few of the bugs.

961 iGuard performs better because Compute Sanitizer does not check for races in global memory.

962 The LivelockBug (see Table 2) is particularly challenging for ThreadSanitizer, Archer, and iGuard

963 as evidenced by the increase in the percentages when removing the livelock codes. ThreadSaniti-

964 zzer correctly flags 118 (74.7%) and Archer 113 (71.5%) of 158 non-livelock buggy codes. iGuard

965 correctly flags 201 (47.4%) of 424 non-livelock buggy codes. While iGuard has a timeout option,

966 ThreadSanitizer and Archer potentially run forever if the program contains a livelock bug.

## 967 6.3 Memory bug detection

968 Since some memory bugs (e.g., out of bounds accesses) may cause data races, we count such reports

969 as true positives. Tables 13 and 14 show the results for the codes with exactly one memory bug.

970 Even though the Clang Static Analyzer is not able to detect parallelism bugs, it does correctly

971 report memory warnings for 19.1% of our codes. Archer detects more memory bugs and ThreadSaniti-

972 zzer even more, but both of them perform better on parallelism bugs than on memory bugs. This is

981 Table 11. Results for CPU codes with one parallelism bug

982

| 983 <b>Tool</b>       | 984 <b>Language</b> | 985 <b>Codes</b> | 986 <b>TP Codes</b> | 987 <b>Runs</b> | 988 <b>TP Runs</b> |

|-----------------------|---------------------|------------------|---------------------|-----------------|--------------------|

| Clang Static Analyzer | OpenMP              | 212              | 0 (0.0%)            | n/a             | n/a                |

| ThreadSanitizer       | OpenMP              | 212              | 136 (64.2%)         | 14,204          | 7,840 (55.2%)      |

| Archer                | OpenMP              | 212              | 115 (59.9%)         | 14,204          | 4,140 (31.9%)      |

989 Table 12. Results for GPU codes with one parallelism bug