# Design of an ultra-compact, energy-efficient non-volatile photonic switch based on phase change materials

Khoi Phuong Dao<sup>a,\*</sup>, Juejun Hu,<sup>a</sup> and Richard Soref<sup>b</sup>

<sup>a</sup>Massachusetts Institute of Technology, Department of Materials Science and Engineering, Cambridge, Massachusetts, United States

<sup>b</sup>University of Massachusetts Boston, Department of Engineering, Boston, Massachusetts, United States

**ABSTRACT.** The on-chip photonic switch is a critical building block for photonic integrated circuits and the integration of phase change materials (PCMs) enables non-volatile switch designs that are compact, low-loss, and energy-efficient. Existing switch designs based on these materials typically rely on weak evanescent field interactions, resulting in devices with a large footprint and high energy consumption. Here, we present a compact non-volatile  $2 \times 2$  switch design leveraging optical concentration in slot waveguide modes to significantly enhance interactions of light with PCM, thereby realizing a compact, efficient photonic switch. To further improve the device's energy efficiency, we introduce an integrated single-layer graphene heater for ultrafast electrothermal switching of the PCM. Computational simulations demonstrate a  $2 \times 2$  switch crosstalk (CT) down to  $-24$  dB at  $1550$  nm wavelength and more than  $55$  nm  $0.3$  dB insertion loss (IL) bandwidth. The proposed photonic switch architecture can constitute the cornerstone for next-generation high-performance reconfigurable photonic circuits.

© The Authors. Published by SPIE under a Creative Commons Attribution 4.0 International License. Distribution or reproduction of this work in whole or in part requires full attribution of the original publication, including its DOI. [DOI: [10.1117/1.JOM.4.3.031204](https://doi.org/10.1117/1.JOM.4.3.031204)]

**Keywords:** phase change materials; reconfigurable photonics; optical switch; graphene heater

Paper 23042SS received Dec. 30, 2023; revised Apr. 3, 2024; accepted Apr. 4, 2024; published May 25, 2024.

## 1 Introduction

In the past few decades, the rapid development of photonic integrated circuits (PICs) has demonstrated their potential in telecommunication and data communications. Moreover, the von Neumann bottleneck in electronics<sup>1</sup> suggests that scalable programmable PICs could be an alternative solution for energy-efficient classical and/or quantum information storage and processing.<sup>2,3</sup> Programmable PIC reported to date predominantly rely on thermo-optic effects,<sup>4</sup> free-carrier effects,<sup>5</sup> or electro-optic effects<sup>6</sup> of materials. The small change in refractive index afforded by these effects, however, limits the tunability and scalability of these methods, leading to a large device footprint and excessive energy consumption. Although plasmonic light confinement can mitigate the issue that results in lossy devices,<sup>7</sup> making the approach unsuitable for large-scale PICs. Moreover, these effects are volatile and demand a constant power supply ( $\sim 10$  mW). This disqualifies them for applications where only sporadic re-programming or reconfiguration is needed, such as optical switching and routing in data centers,<sup>8</sup> optical neural networks,<sup>9</sup> and photonic memories.<sup>10,11</sup>

\*Address all correspondence to Khoi Phuong Dao, [khoiдаo@mit.edu](mailto:khoiдаo@mit.edu).

Chalcogenide-based phase change materials (PCMs) emerge as promising candidates to enable ultra-compact and energy-efficient reconfigurable photonics. They can reversibly switch between two stable states (amorphous and crystalline) in a non-volatile fashion and with exceptionally high refractive index contrast ( $\Delta n \sim 1$ ).<sup>11–14</sup> Phase transition in PCMs can be triggered by ultrashort optical or electrical pulses,<sup>15</sup> and a multitude of intermediate states (between fully amorphous and crystalline) can be accessed by changing the pulse parameters.<sup>16</sup> In addition, PCMs offer compatibility with large-scale integration, as they can be conveniently prepared using various large-area deposition methods<sup>11,12,17,18</sup> onto different photonic integrated circuit (PIC) platforms in a CMOS backend-compatible manner.<sup>12,19</sup> Despite these advantages, conventional PCMs, such as  $\text{Ge}_2\text{Se}_2\text{Te}_5$  (GST) and GeTe, display significant absorption in both phases at optical communication wavelengths, limiting their effectiveness in photonic phase shifters—a crucial component of programmable PICs. Recently, interest has been growing in wide-bandgap PCMs, such as GeSbSeTe (GSST),<sup>20,21</sup> antimony selenide ( $\text{Sb}_2\text{Se}_3$ ),<sup>22</sup> and antimony sulfide ( $\text{Sb}_2\text{S}_3$ ).<sup>22,23</sup> For example,  $\text{Sb}_2\text{Se}_3$  exhibits minimal losses at 1550 nm and a substantial index contrast ( $\Delta n \approx 0.77$ ).<sup>22</sup> These characteristics position  $\text{Sb}_2\text{Se}_3$  as a promising phase-change material for applications in programmable photonics within the telecommunication bands.

One essential design element in PCM-based configurable devices is the heating mechanism. Electro-thermal heating using resistive micro-heaters facilitating scalable on-chip integration have been investigated in numerous recent studies. Various heater materials have been employed, including metals,<sup>24,25</sup> transparent conducting oxides (TCOs),<sup>26</sup> and doped Si.<sup>27–29</sup> While metals prove effective for free-space reflective devices, they introduce notable optical losses in transmissive or waveguide components. Doped silicon stands out as an excellent choice for integrating PCMs into the silicon-on-insulator (SOI) platform. However, applying it to  $\text{Si}_3\text{N}_4$ -based devices, another widely used photonic platform, or to other non-silicon waveguide platforms poses challenges. TCO heaters, while suitable for devices operating in the visible spectrum, encounter exacerbated optical losses in the infrared due to free carrier absorption. To address these challenges, graphene has emerged as a promising heating material due to its exceptional thermal and electrical conductivity, versatile integration compatibilities, and remarkable stability.<sup>30,31</sup> In addition, the infrared optical losses associated with graphene can be minimized by leveraging the doping-induced Pauli blocking effect. Recent theoretical analysis and experimental reports<sup>32–34</sup> indicate that graphene heaters exhibit two orders-of-magnitude higher figures of merit for overall performance (heating efficiency and induced loss) than that of doped Si or TCO heaters when applied to PCM switching.

Here, we present the design of a compact non-volatile photonic  $2 \times 2$  switch on the SOI platform utilizing  $\text{Sb}_2\text{Se}_3$  and a single-layer graphene heater. The design exploits a configuration involving a slotted waveguide filled with PCM. Compared to traditional layouts where the PCM typically interacts only with evanescent fields, the design leverages strong field concentration in the slot region to boost light-PCM interactions,<sup>35</sup> thus simultaneously achieving low insertion loss, a compact form factor, high extinction ratio, and zero-static power consumption.

## 2 Structure and Design

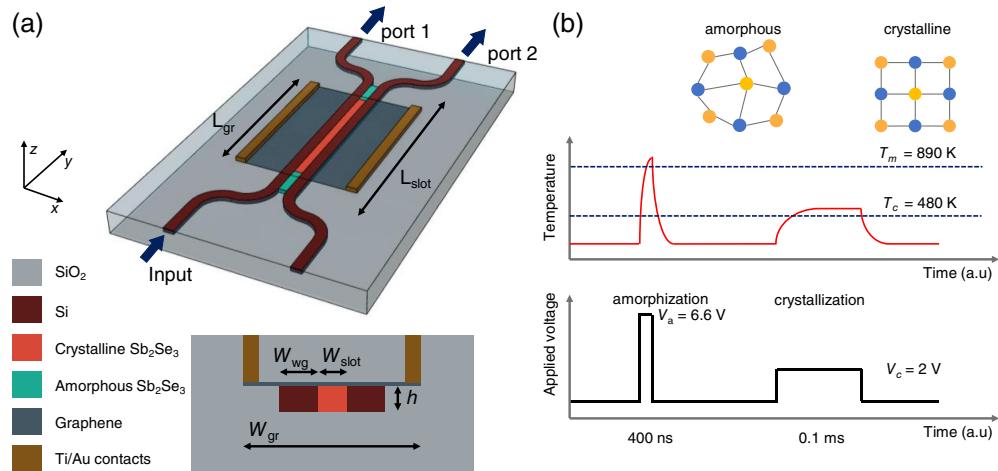

Figure 1 shows the proposed  $2 \times 2$  photonics directional-coupler switch design in a semi-standard SOI platform. The switch consists of a multimode slotted waveguide (the two-waveguide coupling zone) attached to four single-mode waveguides serving as input and output ports, on either side of the multimode section. The height and width of the single-mode waveguides are  $h = 240$  nm and  $W_{\text{wg}} = 450$  nm, respectively. The slot waveguide has a length  $L_{\text{slot}} = 10 \mu\text{m}$  and a centrally located slot with a width  $W_{\text{slot}} = 100$  nm, which is completely filled with  $\text{Sb}_2\text{Se}_3$ . In the telecommunication C-band, the refractive indices of  $\text{Sb}_2\text{Se}_3$  are taken from Ref. 22 as 3.825 and 4.050 at 1550 nm wavelength for the amorphous  $\text{Sb}_2\text{Se}_3$  and crystalline  $\text{Sb}_2\text{Se}_3$ , respectively. The loss of crystalline  $\text{Sb}_2\text{Se}_3$  was also reported in the same paper to be as low as  $0.01 \text{ dB } \mu\text{m}^{-1}$ . The whole device is cladded all around by  $\text{SiO}_2$  with a thickness of  $2 \mu\text{m}$ . Directly on top of the multimode slot waveguide, there is a single-layer graphene heater. The dimensions of the graphene layer are  $L_{\text{gr}} = 9 \mu\text{m}$  and  $W_{\text{gr}} = 3 \mu\text{m}$ , and it is symmetrically positioned on the slot waveguide. Ti/Au contact pads are placed on both sides of the graphene heating layer to minimize contact resistance. Figure 1(b) demonstrates the working principle of

**Fig. 1** (a) Schematic of the  $2 \times 2$  photonic switch based on Sb<sub>2</sub>Se<sub>3</sub>. (b) Schematic of switching operation utilizing amorphization/crystallization voltage pulses to induce Joule heating.

the switch as the PCM is switched reversibly by a sequence of voltage pulses applied to the graphene heater. Short pulses (several hundreds of nanoseconds) with high voltage will reset the PCM back to the amorphous state while long pulses (several milliseconds) with moderate voltage are used to crystallize the material. Sb<sub>2</sub>Se<sub>3</sub> was reported to be successfully amorphized at  $T_a = 620^\circ\text{C}$  for 400 ns and crystallized at  $T_c = 200^\circ\text{C}$  for minimally 0.1 ms.<sup>12</sup> In this study, the fundamental transverse electric (TE) mode at the telecommunication wavelength of 1550 nm was targeted. Yet, the design principle is not wavelength-sensitive and can be applied to a broadband device, as we will show later. The whole design could be realized by standard lithography and dry etching processes. Sb<sub>2</sub>Se<sub>3</sub> be deposited in the slot by conformal coating methods, such as atomic layer deposition<sup>36</sup> and solution processing.<sup>37</sup> Alternatively, thermal reflow has been demonstrated as an effective means for filling thin slots with chalcogenide materials.<sup>38</sup> The graphene heater can be fabricated by transferring chemical-vapor-deposition (CVD) grown single-layer graphene via the standard wet transfer technique,<sup>39</sup> followed by lithographic patterning and metallization.

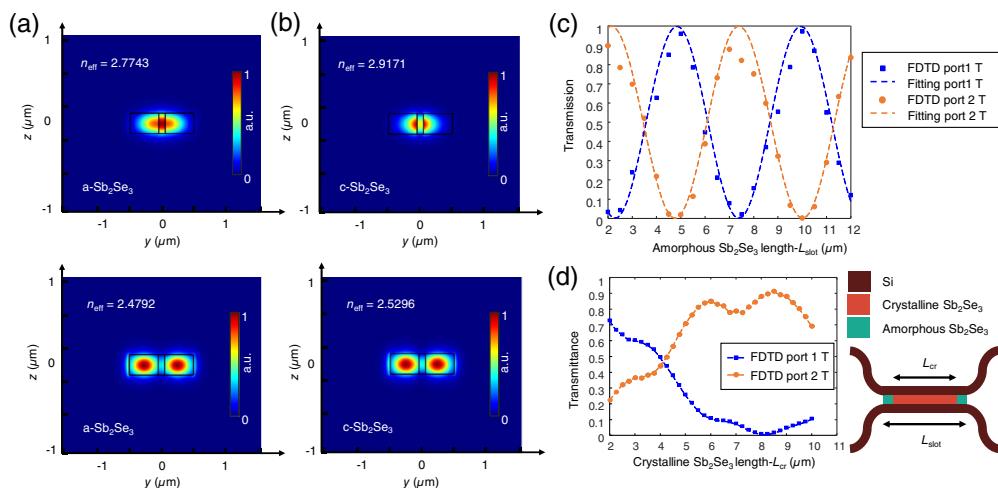

The substantial refractive index contrast provided by Sb<sub>2</sub>Se<sub>3</sub> facilitates the generation of even and odd TE modes within the multimode slot waveguide region, characterized by significant shifts in effective indices upon transitioning the phase of the slot material [as shown in Figs. 2(a) and 2(b)]. Exploiting the disparities in the confinement and effective indices of these supermodes at amorphous and crystalline states, the photonic switch can be dynamically shifted

**Fig. 2** (a), (b) The cross-sectional electric field distribution for even and odd TE modes of the multimode slot waveguide. (c) Transmission through the two ports as functions of PCM length. (d) Transmission through the two ports as function of crystallized PCM section's length.

from a bar state to a cross state. Due to the difference in propagating constants, the interference between odd mode and even mode results in the oscillation between bar state and cross state when we increase the slot length. The ultralow loss exhibited by  $\text{Sb}_2\text{Se}_3$  allows the PCM to have a strong overlap with the supermodes in the slot region without incurring excessive losses, thereby enhancing the phase modulation effect. The effective index differences between the even mode and the odd mode are 0.2951 and 0.3875 for amorphous and crystalline  $\text{Sb}_2\text{Se}_3$  states, respectively, corresponding to different beating lengths in the two states.

Figure 2(c) plots transmission through the ports 1 and 2 in the amorphous  $\text{Sb}_2\text{Se}_3$  state with different PCM-filled slot length  $L_{\text{slot}}$ , simulated using 3D finite-difference time-domain (FDTD) and fitted to sine curves. Following the result, we take the slot length to be  $10 \mu\text{m}$ , which yields the maximum transmission in the amorphous (bar) state. To realize switching with maximum contrast, we selectively crystallize the center section of the PCM as shown in Fig. 2(d). In practice, this can be implemented by controlling the temperature profile along the  $y$ -axis, as the center portion of the PCM slot experiences the highest temperature and hence preferentially crystallizes first (refer to Fig. 4 and discussions for more details). Figure 2(d) shows the simulated transmission through the output ports as a function of crystallized  $\text{Sb}_2\text{Se}_3$  slot length. The plot implies that an optical crystallization section length of  $8.5 \mu\text{m}$  (i.e., leaving  $0.75 \mu\text{m}$  of amorphous region on either side) would result in maximal switching contrast. This leads to an overall device (including the four single-mode waveguide ports) footprint of  $5.5 \mu\text{m} \times 24 \mu\text{m}$ . We note that partial crystallization of PCMs has been discussed in a number of literature reports showing good reproducibility.<sup>40–42</sup> The main difference between our assumption here and the actual experiment implementation is that there is no abrupt interface between the amorphous and crystalline  $\text{Sb}_2\text{Se}_3$  sections. Instead, a gradual transition region with varying crystalline fraction is likely present. This contributes to lowering reflection and scattering from the abrupt interface and can lead to even lower insertion losses than the simulations presented here.

### 3 Results

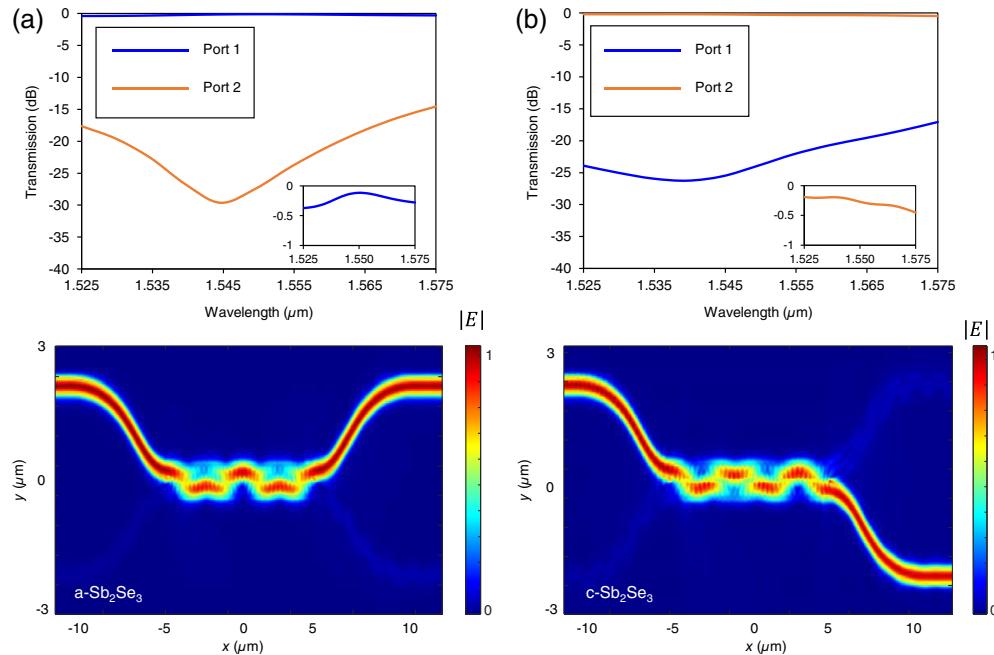

We conducted 3D FDTD simulations to validate the switching efficiency of our proposed design. Figures 3(a) and 3(b) show the transmission spectra of our  $2 \times 2$  photonic switch and the

**Fig. 3** Transmission spectra at two output port and the normalized electric field intensity distribution of the  $2 \times 2$  switch at 1550 nm with (a) amorphous  $\text{Sb}_2\text{Se}_3$  (bar state) and (b) crystalline  $\text{Sb}_2\text{Se}_3$  (cross state).

**Table 1** Comparison of PCM-based optical switches.

| Design           | Ref.      | PCM                      | IL (dB)              | CT (dB) | Footprint ( $\mu\text{m}^2$ ) | Optical BW (nm) | Switching energy               |

|------------------|-----------|--------------------------|----------------------|---------|-------------------------------|-----------------|--------------------------------|

| DC <sup>d</sup>  | 14        | GST                      | 2                    | -10     | 5 $\times$ 45                 | 30              | —                              |

| DC <sup>d</sup>  | 18        | GST                      | 2                    | -10     | 5 $\times$ 50                 | 30              | 380 nJ (6.8 $\mu\text{J}$ )    |

| MZI <sup>d</sup> | 12        | $\text{Sb}_2\text{Se}_3$ | 0.3 <sup>a</sup>     | 6.5/15  | 100 $\times$ 100              | 15              | 176 nJ (3.8 $\mu\text{J}$ )    |

| MZI <sup>d</sup> | 43        | $\text{Sb}_2\text{Se}_3$ | 3                    | -12     | 100 $\times$ 100              | 20              | —                              |

| MRR              | 44        | GST                      | 2                    | -20     | 15 $\times$ 15                | <1              | —                              |

| MRR <sup>d</sup> | 45        | GST                      | 3                    | 14      | 25 $\times$ 25                | <1              | 0.25 nJ (11 nJ) <sup>c</sup>   |

| MRR <sup>d</sup> | 46        | GST                      | 5.1/4.3 <sup>b</sup> | 5       | 60 $\times$ 60                | <1              | 0.19 nJ (17.1 nJ) <sup>c</sup> |

| MMI <sup>d</sup> | 47        | $\text{Sb}_2\text{Se}_3$ | 0.5 <sup>a</sup>     | 8       | 6 $\times$ 33                 | —               | 14 nJ (0.95 mJ) <sup>c</sup>   |

| DC               | 48        | $\text{Sb}_2\text{Se}_3$ | 0.26                 | -31.3   | 4.9 $\times$ 25.4             | 35              | 9.59 nJ (—)                    |

| DC               | This work | $\text{Sb}_2\text{Se}_3$ | 0.3                  | -23.9   | 5.5 $\times$ 24               | 55              | 21 nJ (1.13 $\mu\text{J}$ )    |

DC, directional coupler; MZI, Mach–Zehnder interferometer; MRR, micro-ring resonator; MMI, multimode interferometer; IL, insertion loss; CT, crosstalk; Optical BW, optical bandwidth for the corresponding IL; switching energy, energy per switching event for amorphization/crystallization.

<sup>a</sup>Additional loss due to PCMs to the total device IL.

<sup>b</sup>Through/drop port IL.

<sup>c</sup>Optical pulse energy.

<sup>d</sup>Experimental results.

corresponding in-plane electric field distributions corresponding to amorphous and crystalline  $\text{Sb}_2\text{Se}_3$  states. The overall insertion loss (IL) is  $-0.27$  dB (cross state) and  $-0.11$  dB (bar state) at 1550 nm and is consistently  $<0.5$  dB across 1525 to 1575 nm wavelengths. The 0.3 dB IL bandwidth is no  $<55$  nm. The crosstalk (CT), defined as the contrast ratio between the on/off states at the output ports, reaches  $-23.9$  dB (cross state) and  $-27.4$  dB (bar state) at 1550 nm and stays better than  $-15$  dB throughout the 1525 to 1575 nm band. These performance metrics compare favorably to state-of-the-art PCM switches as summarized in Table 1.

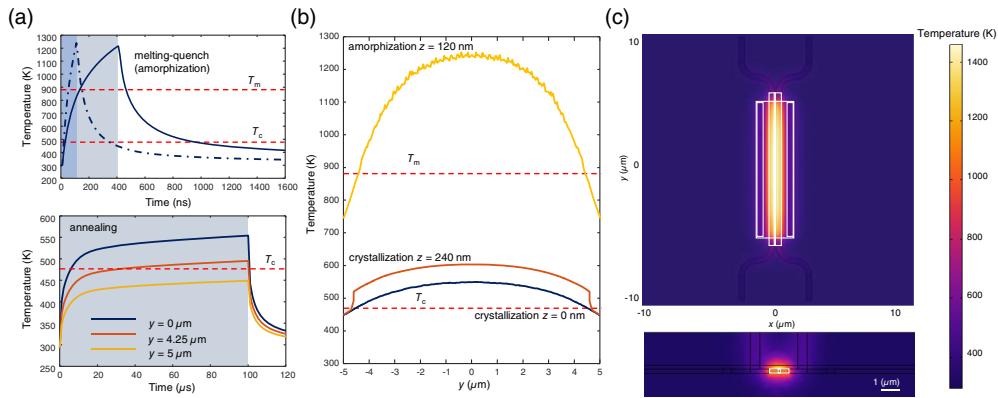

Next, we discuss the thermal performance of the single-layer graphene heater. The graphene heater has been reported to have outstanding performance as a heating element for integrated photonic devices incorporating PCMs, offering exceptional energy efficiency and high operational speed,<sup>31,32</sup> owing to its ultralow heat capacity and high in-plane thermal and electrical conductivity. Compared to doped Si, which is another popular choice of heater material, graphene heaters claim significantly lower induced loss and higher heating efficiency.<sup>32,33</sup> Joule heating employing the graphene heater follows similar phase change dynamics demonstrated in Refs. 12 and 29. The pulse width and voltage are contingent on the microheater’s properties. With our specific proposed graphene heater, pulses of 2 V, which induces a current of 5.67 mA, with a duration of 100  $\mu\text{s}$  are applied to partially crystallize the  $\text{Sb}_2\text{Se}_3$  slot, heating its 8.5  $\mu\text{m}$  long center section to above the crystallization temperature  $T_c$  (here set as 200°C). It is reported that pulses (as short as 5  $\mu\text{s}$ ) can crystallize  $\text{Sb}_2\text{Se}_3$  but result in spatially non-uniform crystallization. Longer pulses lasting 100  $\mu\text{s}$  or more are necessary to crystallize the PCM uniformly,<sup>12</sup> which justifies our pulse parameter choice here. To induce amorphization, we investigated two types of pulses, a single 8.6 V (22.4 mA), 100 ns pulse<sup>12,22</sup> or a 6.6 V (18.7 mA), 400 ns pulse. Both can elevate the temperature of the entire PCM-filled slot above the melting point,  $T_m = 620^\circ\text{C}$  (893 K). The total energy consumption for crystallization is 1.13  $\mu\text{J}$  and 21/49.4 nJ (100/400 ns pulse) for amorphization. Clearly, a trade-off between pulse voltage and switch energy exists for the amorphization process. Figure 4(a) demonstrates the temperature evolution over amorphization and crystallization cycles from finite-element method (FEM) simulations using COMSOL Multiphysics. For crystallization, the temperature remains stably higher than  $T_c$  across the target section. Figure 4(b) plots the temperature across the  $\text{Sb}_2\text{Se}_3$  slot at the end of the crystallization and amorphization (100 ns) pulses. The coordinate  $z = 0$  nm refers to the boundary between the silicon waveguide layer and the buried oxide

**Fig 4** (a) FEM simulated transient temperature during and after the amorphization and crystallization pulses. The shaded areas represent pulse-on times. (b) Simulated temperature across the slot at the end of the amorphization and crystallization pulses. (c) Simulated three-dimension temperature profiles at the end of the amorphization pulse.

(BOX). The yellow line shows that the entire  $\text{Sb}_2\text{Se}_3$  middle section (from  $y = -4.25 \mu\text{m}$  to  $y = 4.25 \mu\text{m}$ ) was elevated to be above its melting point, which guarantees complete amorphization. The 3D temperature profile predicted by thermal FEM simulation at the end of the 100 ns amorphization pulse was shown in Fig. 4(c), suggesting that the heat is effectively confined within the target section of  $\text{Sb}_2\text{Se}_3$ .

The out-of-plane temperature variation is particularly relevant for graphene heaters, given that graphene exhibits varying out-of-plane thermal resistance due to the surface polar phonons (SPoPh) scattering effect.<sup>49</sup> Consequently, a temperature gradient is established along the out-of-plane direction, as heat transfer occurs more efficiently toward the substrate than toward the top cladding. In order to ensure complete amorphization of  $\text{Sb}_2\text{Se}_3$  following the melt-quenching pulse, a series of dynamic simulations was conducted with varying amorphization pulse power. Thermal FEM simulations [Fig. 4(b)] suggest that the crystallization length within the slot barely changes at  $z = 0$  and  $z = 240 \text{ nm}$ , implying that the crystallization is uniform along the  $z$ -direction. The kinks near the two ends of the orange curve in Fig. 4(b) are attributed to the ends of the graphene sheet.

The quenching rate after the amorphization pulse, which is critical in gauging whether crystallization can be bypassed, is predominantly governed by thermal conductance through cladding material and BOX. As shown in Fig. 4(a), the quenching rate is  $\sim 1 \text{ K/ns}$ , which is sufficient to prohibit re-crystallization of  $\text{Sb}_2\text{Se}_3$ .

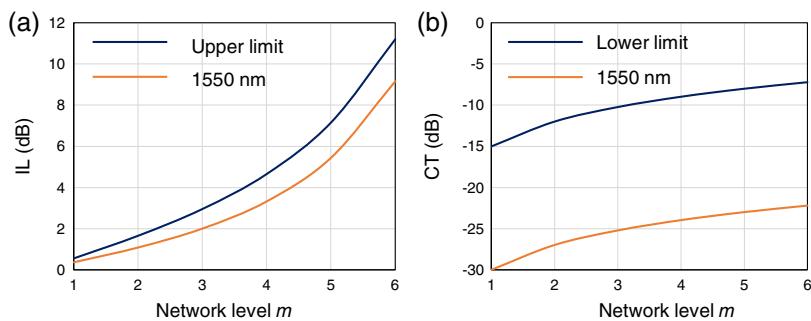

Finally, we assess the scalability of our design to large switch matrices.  $2^m \times 2^m$  switches built from  $2 \times 2$  building blocks using the Benes network can be used to estimate the performance of our proposed design.<sup>20</sup> Using the values presented in Table 1, we can estimate the total insertion loss and the lower and maximum CT of an  $m$ -order switch matrix (assuming that the IL of a waveguide crossing in the C-band as 0.1 dB<sup>50</sup>):

$$\text{IL}_m = (2^m - 2) \times 0.1 \text{ dB} + (2m - 1) \times 0.45 \text{ dB}, \quad (1)$$

$$\text{CT}_m = -(15 \text{ dB} - 10\log_{10} m \text{ dB}). \quad (2)$$

Scaling from our  $2 \times 2$  switch's performance, a  $16 \times 16$  switch is anticipated to exhibit maximal 3.2 dB insertion loss and  $-24 \text{ dB}$  CT at 1550 nm, representing highly promising performance metrics, compared to the state-of-the-art (volatile) on-chip  $16 \times 16$  switch reported by Lu et al.<sup>51</sup> The devices can also be put to good use in creating large-scale, programmable, rectangular and triangular and hexagonal meshes<sup>52</sup> (Fig. 5).

## 4 Conclusion

In conclusion, the non-volatile  $2 \times 2$  photonic switch design takes advantage of a PCM-slot configuration to achieve an ultra-compact footprint ( $5.5 \times 24 \mu\text{m}^2$ ) with minimal CT ( $-23.9 \text{ dB}$ ), and the low-loss PCM  $\text{Sb}_2\text{Se}_3$  enables a low insertion loss of 0.27 dB, and a single-layer

**Fig. 5** (a) Insertion loss and (b) maximum CT as functions of the switch matrix of order  $m$ .

graphene heater achieves low switching energies of  $1.13 \mu\text{J}$  for crystallization and  $21 \text{nJ}$  for amorphization. The design further demonstrates its scalability toward large-scale non-blocking switch matrices. Our proposed design, therefore, holds the potential for the development of future large-scale PCM-based programmable PICs.

## Disclosure

The authors declare no conflict of interests

## Code and Data Availability

The data that support the findings of this study are available from the corresponding author, KPD, upon reasonable request.

## Acknowledgments

Funding support was provided by NSF (Grant No. 2132929) and the Air Force Office of Scientific Research AFOSR (Grant Nos. FA9550-21-1-0347 and FA9550-22-1-0532). We acknowledge the insightful discussions and technical assistance from Professor Francesco De Leonardi.

## References

1. A. H. Atabaki et al., "Integrating photonics with silicon nanoelectronics for the next generation of systems on a chip," *Nature* **556**(7701), 349–354 (2018).

2. J. Wang et al., "Multidimensional quantum entanglement with large-scale integrated optics," *Science (1979)* **360**(6386), 285–291 (2018).

3. J. Feldmann et al., "Parallel convolutional processing using an integrated photonic tensor core," *Nature* **589**(7840), 52–58 (2021).

4. D. Pérez et al., "Multipurpose silicon photonics signal processor core," *Nat. Commun.* **8**(1), 636 (2017).

5. G. T. Reed et al., "Silicon optical modulators," *Nat. Photonics* **4**(8), 518–526 (2010).

6. C. Wang et al., "Integrated lithium niobate electro-optic modulators operating at CMOS-compatible voltages," *Nature* **562**(7725), 101–104 (2018).

7. C. Haffner et al., "All-plasmonic Mach–Zehnder modulator enabling optical high-speed communication at the microscale," *Nat. Photonics* **9**(8), 525–528 (2015).

8. Q. Cheng et al., "Photonic switching in high performance datacenters [Invited]," *Opt. Express* **26**(12), 16022–16043 (2018).

9. Y. Shen et al., "Deep learning with coherent nanophotonic circuits," *Nat. Photonics* **11**(7), 441–446 (2017).

10. S. R. Kari et al., "Optical and electrical memories for analog optical computing," *IEEE J. Sel. Top. Quantum Electron.* **29**(2: Optical Computing), 1–12 (2023).

11. C. Ríos et al., "Integrated all-photonic non-volatile multi-level memory," *Nat. Photonics* **9**(11), 725–732 (2015).

12. C. Ríos et al., "Ultra-compact nonvolatile phase shifter based on electrically reprogrammable transparent phase change materials," *PhotoniX* **3**(1), 26 (2022).

13. M. Wuttig, H. Bhaskaran, and T. Taubner, "Phase-change materials for non-volatile photonic applications," *Nat. Photonics* **11**(8), 465–476 (2017).

14. P. Xu et al., "Low-loss and broadband nonvolatile phase-change directional coupler switches," *ACS Photonics* **6**(2), 553–557 (2019).

15. F. Rao et al., “Reducing the stochasticity of crystal nucleation to enable subnanosecond memory writing,” *Science (1979)* **358**(6369), 1423–1427 (2017).

16. C. D. Wright et al., “Fast and reliable storage using a 5 bit, nonvolatile photonic memory cell,” *Optica* **6**(1), 1–6 (2019).

17. J. Zheng et al., “GST-on-silicon hybrid nanophotonic integrated circuits: a non-volatile quasi-continuously reprogrammable platform,” *Opt. Mater. Express* **8**(6), 1551–1561 (2018).

18. R. Chen et al., “Broadband nonvolatile electrically controlled programmable units in silicon photonics,” *ACS Photonics* **9**(6), 2142–2150 (2022).

19. R. Chen et al., “Deterministic quasi-continuous tuning of phase-change material integrated on a high-volume 300-mm silicon photonics platform,” Research Square (Preprint), (2023).

20. Q. Zhang et al., “Broadband nonvolatile photonic switching based on optical phase change materials: beyond the classical figure-of-merit,” *Opt. Lett.* **43**(1), 94–97 (2018).

21. Y. Zhang et al., “Broadband transparent optical phase change materials for high-performance nonvolatile photonics,” *Nat. Commun.* **10**(1), 4279 (2019).

22. M. Delaney et al., “A new family of ultralow loss reversible phase-change materials for photonic integrated circuits:  $\text{Sb}_2\text{S}_3$  and  $\text{Sb}_2\text{Se}_3$ ,” *Adv. Funct. Mater.* **30**(36), 2002447 (2020).

23. W. Dong et al., “Wide bandgap phase change material tuned visible photonics,” *Adv. Funct. Mater.* **29**(6), 1806181 (2019).

24. S. Abdollahramezani et al., “Electrically driven reprogrammable phase-change metasurface reaching 80% efficiency,” *Nat. Commun.* **13**(1), 1696 (2022).

25. Y. Wang et al., “Electrical tuning of phase-change antennas and metasurfaces,” *Nat. Nanotechnol.* **16**(6), 667–672 (2021).

26. H. Taghinejad et al., “ITO-based microheaters for reversible multi-stage switching of phase-change materials: towards miniaturized beyond-binary reconfigurable integrated photonics,” *Opt. Express* **29**(13), 20449–20462 (2021).

27. H. Zhang et al., “Nonvolatile waveguide transmission tuning with electrically-driven ultra-small GST phase-change material,” *Sci. Bull.* **64**(11), 782–789 (2019).

28. H. Zhang et al., “Miniature multilevel optical memristive switch using phase change material,” *ACS Photonics* **6**(9), 2205–2212 (2019).

29. J. Zheng et al., “Nonvolatile electrically reconfigurable integrated photonic switch enabled by a silicon PIN diode heater,” *Adv. Mater.* **32**(31), 2001218 (2020).

30. J. Li et al., “High-performance graphene-integrated thermo-optic switch: design and experimental validation [Invited],” *Opt. Mater. Express* **10**(2), 387–396 (2020).

31. M. Romagnoli et al., “Graphene-based integrated photonics for next-generation datacom and telecom,” *Nat. Rev. Mater.* **3**(10), 392–414 (2018).

32. J. Zheng et al., “Modeling electrical switching of nonvolatile phase-change integrated nanophotonic structures with graphene heaters,” *ACS Appl. Mater. Interfaces* **12**(19), 21827–21836 (2020).

33. C. Ríos et al., “Multi-level electro-thermal switching of optical phase-change materials using graphene,” *Adv. Photonics Res.* **2**(1), 2000034 (2021).

34. Z. Fang et al., “Ultra-low-energy programmable non-volatile silicon photonics based on phase-change materials with graphene heaters,” *Nat. Nanotechnol.* **17**(8), 842–848 (2022).

35. J. Zhang et al., “Ultra-low-power nonvolatile integrated photonic switches and modulators based on nano-gap-enhanced phase-change waveguides,” *Opt. Express* **28**(25), 37265–37275 (2020).

36. Y. K. Lee et al., “Atomic layer deposition of chalcogenides for next-generation phase change memory,” *J. Mater. Chem. C Mater.* **9**(11), 3708–3725 (2021).

37. R. Sharma et al., “Solution-based  $\text{Sb}_2\text{Se}_3$  thin films for microphttonics,” *J. Opt. Microsyst.* **4**(3), 031203 (2024).

38. S. Serna et al., “Engineering third-order optical nonlinearities in hybrid chalcogenide-on-silicon platform,” *Opt. Lett.* **44**(20), 5009–5012 (2019).

39. J.-Y. Hong et al., “A rational strategy for graphene transfer on substrates with rough features,” *Adv. Mater.* **28**(12), 2382–2392 (2016).

40. C. Ríos et al., “Controlled switching of phase-change materials by evanescent-field coupling in integrated photonics [Invited],” *Opt. Mater. Express* **8**(9), 2455–2470 (2018).

41. C. Wu et al., “Programmable phase-change metasurfaces on waveguides for multimode photonic convolutional neural network,” *Nat. Commun.* **12**(1), 96 (2021).

42. Y. Zhang et al., “Electrically reconfigurable non-volatile metasurface using low-loss optical phase-change material,” *Nat. Nanotechnol.* **16**(6), 661–666 (2021).

43. X. Yang et al., “Phase change material enabled  $2 \times 2$  silicon nonvolatile optical switch,” *Opt. Lett.* **46**(17), 4224–4227 (2021).

44. C. Zhang et al., “Wavelength-selective  $2 \times 2$  optical switch based on a  $\text{Ge}_2\text{Sb}_2\text{Te}_5$ -assisted microring,” *Photonics Res.* **8**(7), 1171–1176 (2020).

45. C. Wu et al., "Low-loss integrated photonic switch using subwavelength patterned phase change material," *ACS Photonics* **6**(1), 87–92 (2019).

46. M. Stegmaier et al., "Nonvolatile all-optical  $1 \times 2$  switch for chipscale photonic networks," *Adv. Opt. Mater.* **5**(1), 1600346 (2017).

47. M. Delaney et al., "Nonvolatile programmable silicon photonics using an ultralow-loss  $\text{Sb}_2\text{Se}_3$  phase change material," *Sci. Adv.* **7**(25), eabg3500 (2023).

48. C. Song et al., "Compact nonvolatile  $2 \times 2$  photonic switch based on two-mode interference," *Opt. Express* **30**(17), 30430–30440 (2022).

49. X. Tang et al., "Five orders of magnitude reduction in energy coupling across corrugated graphene/substrate interfaces," *ACS Appl. Mater. Interfaces* **6**(4), 2809–2818 (2014).

50. L. Qiao, W. Tang, and T. Chu, "32  $\times$  32 silicon electro-optic switch with built-in monitors and balanced-status units," *Sci. Rep.* **7**(1), 42306 (2017).

51. L. Lu et al., "16  $\times$  16 non-blocking silicon optical switch based on electro-optic Mach-Zehnder interferometers," *Opt. Express* **24**(9), 9295–9307 (2016).

52. E. Sánchez, A. López, and D. Pérez-López, "Simulation of highly coupled programmable photonic circuits," *J. Lightwave Technol.* **40**(19), 6423–6434 (2022).

**Khoi Phuong Dao** is a doctoral candidate in the Department of Materials Science and Engineering at the Massachusetts Institute of Technology (MIT). He received his BS degree with a double major in physics and materials science in 2020 from the Korean Advanced Institute of Science and Technology. His research interests include on-chip photonic isolators, on-chip in-situ material thermal treatment, and applications of phase change materials in integrated optics and photonics.

**Juejun Hu** is the John F. Elliott professor of materials science and engineering at MIT. His research primarily focuses on integrated optics and photonics. He has authored and coauthored more than 150 refereed journal publications, and he has been recognized with the SPIE Early Career Achievement Award, the Robert L. Coble Award from the American Ceramic Society, the Vittorio Gottardi Prize from the International Commission on Glass, the NSF CAREER award, and the DARPA Young Faculty Award, among others. He is a fellow of Optica, SPIE, and the American Ceramic Society.

**Richard Soref** is currently a research professor of engineering at the University of Massachusetts at Boston. After attaining a Ph.D.E.E. from Stanford University in 1964, he embarked upon a 59-year research career that continues to the present day. He is known as the father of silicon photonics, and he co-founded the IEEE Group IV Photonics Conference. He holds 54 U.S. patents and is recognized at Google Scholar with 32,460 citations, a Hirsch index of 87, and an i10 index of 336.