IMAGE LICENSED BY INGRAM PUBLISHING

I AM HONORED TO RECEIVE THIS year's IEEE Pioneer Award in Nanotechnology. I would like to use this opportunity to share three nanotechnology approaches we have developed and our vision on how these could contribute to the continued scaling of semiconductor technologies in 3D and by heterogeneous integration, with plenty of room all-around.

#### **2022 IEEE NANOTECHNOLOGY PIONEER AWARD RECIPIENT**

It is widely accepted that the Feynman Lecture delivered on Dec. 29<sup>th</sup>, 1959 at the annual American Physical Society meeting, "There is plenty of room at the

# There Is Plenty of Room All-Around

Highlight of Semiconductor Nanotechnology Research in My Lab

*Digital Object Identifier 10.1109/MNANO.2022.3228096*

*Date of current version: 6 March 2023*

**XIULING LI**

bottom," spurred the beginning of the nanotechnology field. In that lecture, Feynman brilliantly articulated that size matters – "When we get to the very, very small world—say circuits of seven atoms—we have a lot of new things that would happen that represent completely new opportunities for design. Atoms on a small scale behave like nothing on a large scale, for they satisfy the laws of quantum mechanics. So, as we go down and fiddle around with the atoms down there, we are working with different laws, and we can expect to do different things. We can manufacture in different ways. We can use, not just circuits, but some system involving the quantized energy levels, or the interactions of quantized spins, etc." His vision on how physics and engineering could move in the direction of shrinking in size eventually created nanotechnology – "an invitation to enter a new field of physics," as the subtitle of that famous lecture rightly noted.

For semiconductor nanotechnology, we must start with the discovery of transistors and how the transistors scaled in dimension and performance over the past half a century. In 1947, John Bardeen (1908–1991) and Walter Brattain (1902–1987) produced a semiconductor amplifier, named a "transistor," which was further developed by William Shockley (1910–1989); and the three of them were awarded the Nobel Prize in Physics in 1956. That first transistor was essentially made by hand, one at a time. The concept of the integrated circuit was not conceived until Jack Kilby (1923–2005) and Robert Noyce (1927–1990) independently came up with the conception of integration. In July 1958, Jack Kilby proposed a novel miniaturized electronic circuit with all components completely integrated into the body of the semiconductor (US Patent No. 3,138,743). Almost at the same time (Jan. 1959), Robert Noyce, from the then Fairchild Semiconductor (the precursor of Intel), also filed his patent (U.S. Patent 2,981,877) on the concept of multiple devices on a single piece of silicon (Si): the integrated circuit. Compared with Kilby's drawing, Noyce's planar transistor clearly depicted metal interconnect without flying wires. There is no doubt that it is these two giants who set the field of semiconductors onto the road of "reducing size,

weight, etc. as well as cost per active element." In 2000, the Nobel Physics Prize was awarded to Jack Kilby "for his part in the invention of the integrated circuit." With this integration scheme, Kilby envisioned that "there is no limit upon the complexity or configuration of circuits which can be made in this manner." Indeed, no other industry has advanced, and continues to reinvent itself, at the amazing rate of transistor technology predicted by Gordon Moore. The number of transistors per die doubles every two years approximately. The continuation of Moore's law has been enabled by many disruptive transformations at the materials, structures, and circuit levels, including strained Si at 90 nm node, high-k metal gate at 45 nm node, FinFET at 22 nm node; and continued aggressive scaling for integration is 3D in nature and heterogeneous by definition. At the same time, tremendous progress in optoelectronic, high-speed, and high-power electronic devices, have been enabled by compound semiconductor heterojunction growth and nanofabrication.

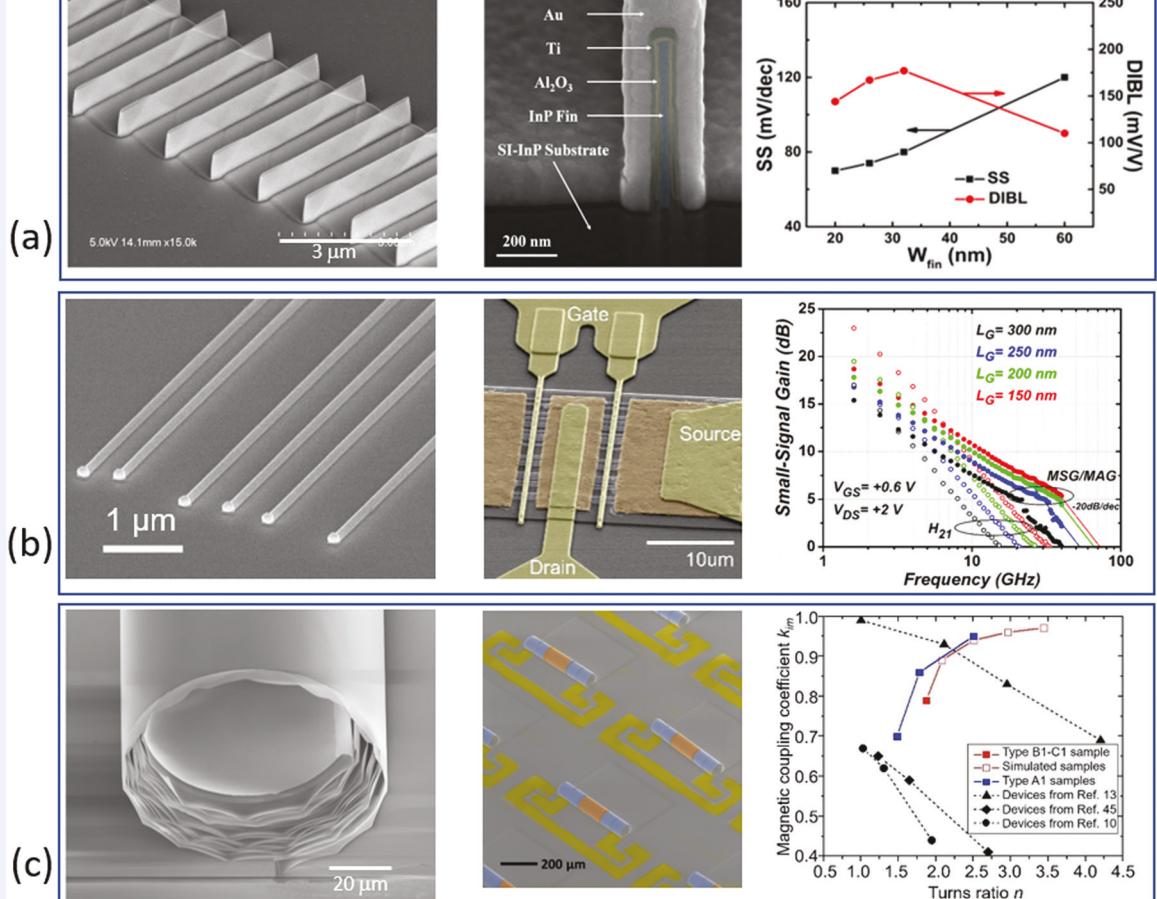

Inspired by the transformative impact so many pioneers in the field, my research lab, which started at University of Illinois about 16 years ago and recently relocated to the University of Texas, has been striving, in our own way, to address the ever-present need to reduce the size, weight, power, and cost (SWaP-C) of semiconductor devices. Our research objective is to create semiconductor nanostructures that enable new device concepts and new science discoveries, in a compatible and scalable fashion. Below, I highlight three nanotechnology platforms we have been developing and a few examples of the unique nanostructures enabled are shown in Figure 1.

### **MACETCH-NOT YOUR ORDINARY ETCHING**

From transistors to lasers, semiconductor wafers go through many levels of lithography, deposition, and etching. In the fabrication of modern optoelectronic and electronic devices such as FinFETs, anisotropic etching is indispensable. Wet etch is inherently isotropic in most cases, and plasma-based dry etch, such as

reactive ion etching, is therefore required. Defying the isotropic nature of conventional wet etch, metal assisted chemical etching (MacEtch or MACE) is a near-room temperature, plasma-free, yet highly anisotropic etching method. MacEtch relies on a local catalysis and electron transfer effect to enable site-controlled semiconductor nanostructure fabrication. Unpresented aspect ratio (as high as 10,000:1) and an etch rate  $> 3\mu\text{m}/\text{min}$  have been reported. [1], [2], [3], [4], [5], [6], [7] This innovative etching method has profound impact on semiconductor fabrication, not only because of the readily achievable extraordinary aspect ratio, but also the inherent absence of ion-induced damage. The latter becomes increasingly critical as devices are aggressively scaled down, especially for compound semiconductors where high energy ion induced etching damage cannot be easily repaired without causing collateral loss.

We first reported MacEtch as a method to generate porous Si using a discontinuous layer of noble metal catalyst metal film under open circuit in 2000 in a solution of hydrofluoric acid (HF) and peroxide ( $\text{H}_2\text{O}_2$ ). [8] The first related patent was filed in 2000 and granted in 2004 (U.S. Patent 6,790,785). Note that the acronym MacEtch or MACE was not used in the community until much later. Highly anisotropic etching was then achieved by patterning the metal catalyst film, using the self-assembled dendritic Ag network from the  $\text{AgNO}_3$  solution and various conventional lithographic methods. [9] The frontier of this technology continues to advance from investigating the fundamental mechanism, process parameters, properties, and applications, to extending its applicability to other semiconductors. Beyond Si, we have demonstrated MacEtch of Ge, [10] III-As, [11] III-P, [12], [13] III-N, [14] SiC, [15] and  $\text{Ga}_2\text{O}_3$ , [4], [16], [17], [18], as well as heterostructures. Metal catalysts, including the well-known noble metals such as Au, Ag, Pt, and CMOS-compatible Ru [19] and TiN [20], as well as metal stacks, have been proven to be effective for different structural or device requirements. Depending on the semiconductor doping type and level, metal catalyst-semiconductor barrier height,

[21] catalyst pattern (size, pitch, shape, and border), [22], [23] and etching solution composition and concentration, MacEtch can lead to different etching rates, topography, porosity, and morphology.

Apart from the competition with conventional chemical etch, there are mainly two rate-determining steps, [22] carrier generation (oxidation) and mass transport (dissolution of oxide). Self-anchored catalyst (*SAC-MacEtch*) overcomes the mass-transport limitation of large feature sizes and made it possible to etch over large areas and through deep trenches vertically, all the way through the entire wafer ( $> 500 \mu\text{m}$ ) without detouring [24]. When either one of these two critical rate-determining steps cannot proceed where

the metal-catalyst is, inverse-MacEtch (*i-MacEtch*) occurs, i.e., etching starts in the location where metal catalyst is absent. [12], [13] For wide and ultra-wide bandgap semiconductors, because of the limited carrier mobilities in these materials, it is necessary to use above bandgap photons ( $\hbar\nu$ ) to generate free electron-hole pairs and enhance MacEtch rate. [4], [14], [15], [16], [17], [18] *hν-MacEtch* is inherently *i-MacEtch*, because the UV light does not penetrate metal catalyst film; it is essentially an open-circuit photo-enhanced etching, but spatially defined by the metal catalyst. *I-MacEtch* enabled the demonstration of high performance, ultra-smooth and damage-free sidewalls in InP (see Figure 1(a)) and Ga<sub>2</sub>O<sub>3</sub> finFETs. [12],

[25] The additional degree of freedom,  $\hbar\nu$  energy, allows selective etching based on the bandgap energy of the semiconductor. By adding ferromagnetic metal in the catalyst, magnetic-field guided MacEtch (*b-MacEtch*) [26], [27], [28] can enable better control of the etching direction, including arbitrary trajectories. Efforts to take MacEtch to vapor-phase have led to better control of the metal-Si interface and etching morphology and overcome stiction issues. [29], [30] We believe that programmable vapor-phase MacEtch (*VP-MacEtch*, U.S. Patent 10,748,781), where the flow of etchants can be independently controlled, will ultimately position the MacEtch technology towards true scalability and manufacturability.

**FIGURE 1** (a) From left to right: SEM image of a 50:1 aspect ratio InP fin array produced by MacEtch, the cross-section of a single fully fabricated FinFET, and the plot of subthreshold slope (SS) and drain-induced barrier lowering (DIBL) as a function of fin width [12]. (b) From left to right: SEM images of a planar GaAs nanowire array grown by Au-assisted VLS selective lateral epitaxy, a fully fabricated GaAs/AlGaAs planar nanowire double gate finger RF testing configuration, and the small signal gain as a function of frequency for various gate length ( $L_G$ ) [32], [33]. (c) From left to right: SEM images of a single self-rolled-up nanomembrane (S-RuM) tubular inductor, an array of fully fabricated S-RuM L-C network, and the magnetic coupling coefficient of S-RuM transformers as a function of turns ratio. [41], [42], [43]. Adapted from [12], [32], [33], [41], [42], [43] with permission.

The simplicity, versatility, manufacturability, and the plasma-free, damage-free, and highly-anisotropic nature of the MacEtch process make it highly promising to supplement and enhance the well-known reactive ion etching methods for deep trenches or pillars with high aspect ratios, periodic or random arrays of ordered or random patterns, as well as shallow surface texturing. This technology is positioned to have disruptive lasting impact to various electronics, photonics, energy, quantum and bio-sensing applications.

### **MOCVD NANOEPITAXY FOR 3D HETEROGENEOUS INTEGRATION**

For semiconductor technologies, advancement in epitaxial growth is one of the major factors responsible for the technology development momentum. Metal-organic chemical vapor deposition (**MOCVD**) represents the main-stream approach for the production of compound semiconductor lasers, high speed and high power transistors, LEDs, photodetectors, and high efficiency solar cells. Nanowire has long been regarded as a promising architecture for beyond Si finFET logic and high frequency III-V electronics, as well as next generation optoelectronic applications. The challenges have been the controllability and manufacturability. My lab's discovery of selective lateral epitaxy of planar III-V nanowire arrays via the metal-assisted vapor-liquid-solid (VLS) mechanism [31], [32] has transformed the long-standing perception of uncontrollability of self-assembled nanowires. On the fundamental side, this work opens up a new paradigm of crystal growth and consequently in situ lateral junction formation. Technologically, in-plane nanowire configuration is perfectly compatible with existing planar processing technology for industry. We have demonstrated chip-scale GaAs/AlGaAs nanowire high electron mobility transistors (HEMTs) with record DC and RF performance (Figure 1(b)), and a clear path to reach THz for high speed applications [33]. As transistor scaling continues, the FinFET inevitably evolves to the Gate-All-Around (GAA) configuration for even better static control and allows stacking transistors

vertically. Our innovation in this space includes vertically stacked NWs with tunable size and doping levels for each level in the stack (U.S. Patent 20,140,353,574; licensed) as the high mobility GAA channel for low power and high linearity on-chip applications.

On the other hand, the holy grail of compound semiconductor technology is to integrate onto the mature Si platform, and the quintessential challenge of heterogeneous integration of III-V on Si and other foreign substrates is the lattice matching restriction. Through unconventional epitaxial growth modes including selective area, direct and van der Waals epitaxy, my lab has achieved site-controlled MOCVD growth of device quality III-V (GaAs, InAs, InGaAs, GaP, InAsP, GaAsP) nanowire arrays on Si [34], [35] and graphene [36], [37], as well as MoS<sub>2</sub> on GaN, [38], and uncovered new understanding of selective area nanoepitaxy and quasi-van der Waals epitaxy. These results could bring translational impact on nanoelectronics and nanophotonics, including III-V gate-all-around transistors and multi-junction tandem solar cells.

### **S-RuM NANOTECHNOLOGY FOR EXTREME MINIATURIZATION AND INTEGRATION**

Combining bottom-up and top-down approaches, my group has established a 3D self-rolled-up membrane (**S-RuM**) nanotechnology platform for extreme miniaturization of passive electronic devices for radio frequency integrated circuits (RFICs) and beyond. The overarching physical principle of S-RuM nanotech is strain-driven spontaneous deformation of 2D membranes into 3D architectures [39]. Complex 3D structures formed by S-RuM enable advanced functionalities that are otherwise out of reach. S-RuM RF inductors have been demonstrated with a footprint that is 10 – 100 times smaller than the 2D counterpart [40]. By virtue of the small size and 3D confinement, energy loss to substrate and free space is minimized, leading to high frequency operation. Monolithic mTesla level magnetic induction was achieved at 10 MHz by geometric transformation of centimeter-long

2D nanomembranes into 140  $\mu\text{m}$  diameter air-core microtubes (see Figure 3(c)), followed by post-rolling ferrofluid core-filling [41]. By stacking two S-RuM inductors in-plane or vertically to form transformers, near unity coupling coefficients and unconventional advantageous scaling trend with turns ratio have been achieved (Figure 3(c)) [42]. By combining multiple inductors and capacitors, all in one single lithography step monolithically before rolling, various L-C network (see Figure 3(c)) can be configured with unprecedented integration density and configurability [43]. To paraphrase Kilby on active device integrated circuits, there is practically no limit upon the complexity or configuration of L-C circuits, which can be made in the manner of S-RuM, and all with one single lithography step. Through global and local strain engineering, transmission lines (U.S. Patent 9,018,050) and antennas (U.S. Patent 9,224,809) with ultra-high frequency (RF, mm Wave, and THz) and bandwidth can also be enabled. S-RuM technology promises to break the constraints of size, weight, and performance (SWAP) of RFICs. The miniaturized form factor can also bring transformative impact to on-chip integration of passive components to power circuits, wearable and flexible IoT devices, microfluidics, and biomedical applications, including the demonstrated guiding and accelerating neuron cell growth for neural regeneration and DNA-based data storage [44], [45].

It is impossible to imagine a world without semiconductors. Through both bottom-up and top-down approaches, we have discovered or developed several portfolios of semiconductor nanotechnology for potential lasting impact to electronics, photonics, energy, and quantum systems, as well as human health. With continued innovation including heterogeneous integration and system-driven codesign approaches, there is plenty of room all-around to further scale semiconductor devices smaller, lighter, faster, more efficient, and less expensive. Our path to profoundly advance nanotechnology, inherently 3D, will continue, from epitaxial growth, fabrication, to devices, circuits, and systems.

## ACKNOWLEDGMENTS

The author is deeply indebted to her current and past students and postdocs, as well as many long-term collaborators. Financial support provided by NSF (including NSF ECCS #2200651), DARPA, ONR, AFOSR, ARO (including MURI #W911NF2110337), DOE, Intel, Lam Research, Western Digital etc. are greatly appreciated.

## ABOUT THE AUTHORS

**Xiuling Li** (xiuling.li@utexas.edu) is with the Department of Electrical and Computer Engineering, The University of Texas at Austin, Austin, TX, 78758, USA.

## REFERENCES

- [1] X. Li, "Metal assisted chemical etching for high aspect ratio nanostructures: A review of characteristics and applications in photovoltaics," *Curr. Opin. Solid State Mater. Sci.*, vol. 16, pp. 71–81, 2012.

- [2] Z. Huang, N. Geyer, P. Werner, J. De Boor, and U. Gösele, "Metal-assisted chemical etching of silicon: A review," *Adv. Mater.*, vol. 23, pp. 285–308, 2011.

- [3] L. Romano and M. Stampaoni, "Microfabrication of X-ray optics by metal assisted chemical etching: A review," *Micromachines*, vol. 11, 2020, Art. no. 589.

- [4] H.-C. Huang, Z. Ren, C. Chan, and X. Li, "Wet etch, dry etch, and MacEtch of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>: A review of characteristics and mechanism," *J. Mater. Res.*, vol. 36, pp. 4756–4770, 2021.

- [5] W. McSweeney, H. Geaney, and C. O'Dwyer, "Metal-assisted chemical etching of silicon and the behavior of nanoscale silicon materials as li-ion battery anodes," *Nano Res.*, vol. 8, pp. 1395–1442, 2015.

- [6] M. Y. Arafat et al., "Fabrication of black silicon via metal-assisted chemical etching—A review," *Sustainability*, vol. 13, 2021, Art. no. 10766.

- [7] K. Balasundaram et al., "Porosity control in metal-assisted chemical etching of degenerately doped silicon nanowires," *Nanotechnology*, vol. 23, 2012, Art. no. 305304.

- [8] X. Li and P. W. Bohn, "Metal-assisted chemical etching in HF/H<sub>2</sub>O<sub>2</sub> produces porous silicon," *Appl. Phys. Lett.*, vol. 77, pp. 2572–2574, 2000.

- [9] K. Peng et al., "Metal-particle-induced, highly localized site-specific etching of Si and formation of single-crystalline Si nanowires in aqueous fluoride solution," *Chem.—A Eur. J.*, vol. 12, pp. 7942–7947, 2006.

- [10] M. Kim et al., "Enhanced performance of Ge photodiodes via monolithic antireflection texturing and  $\alpha$ -Ge self-passivation by inverse metal-assisted chemical etching," *ACS Nano*, vol. 12, pp. 6748–6755, 2018.

- [11] P. K. Mohseni et al., "GaAs pillar array-based light emitting diodes fabricated by metal-assisted chemical etching," *J. Appl. Phys.*, vol. 114, 2013, Art. no. 064909.

- [12] Y. Song et al., "Ultra-high aspect ratio InP junctionless FinFETs by a novel wet etching method," *IEEE Electron Device Lett.*, vol. 37, no. 8, pp. 970–973, Aug. 2016.

- [13] S. H. Kim, P. K. Mohseni, Y. Song, T. Ishihara, and X. Li, "Inverse metal-assisted chemical etching produces smooth high aspect ratio InP nanostructures," *Nano Lett.*, vol. 15, pp. 641–648, 2014.

- [14] C. Y. Chan, S. Namiki, J. K. Hite, M. A. Mastro, S. B. Qadri, and X. Li, "Homoepitaxial GaN micropillar array by plasma-free photo-enhanced metal-assisted chemical etching," *J. Vac. Sci. Technol. A*, vol. 39, 2021, Art. no. 053212.

- [15] J. A. Michaels et al., "Producing silicon carbide micro and nanostructures by plasma-free metal-assisted chemical etching," *Adv. Funct. Mater.*, vol. 31, 2021, Art. no. 2103298.

- [16] M. Kim et al., "Nanoscale groove textured  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> by room temperature inverse metal-assisted chemical etching and photodiodes with enhanced responsivity," *Appl. Phys. Lett.*, vol. 113, 2018, Art. no. 222104.

- [17] H.-C. Huang et al., "High aspect ratio  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> fin arrays with low interface charge density by inverse metal-assisted chemical etching," *ACS Nano*, vol. 13, pp. 8784–8792, 2019.

- [18] H.-C. Huang et al., " $\beta$ -Ga<sub>2</sub>O<sub>3</sub> FinFETs with ultra-low hysteresis by plasma-free metal-assisted chemical etching," *Appl. Phys. Lett.*, vol. 121, 2022, Art. no. 052102.

- [19] A. Mallavarapu, P. Ajay, C. Barrera, and S. V. Sreenivasan, "Ruthenium-assisted chemical etching of silicon: Enabling CMOS-compatible 3D semiconductor device nanofabrication," *ACS Appl. Mater. Interfaces*, vol. 13, pp. 1169–1177, 2021.

- [20] J. D. Kim, M. Kim, C. Chan, N. Draeger, J. J. Coleman, and X. Li, "CMOS-compatible catalyst for MacEtch: Titanium nitride-assisted chemical etching in vapor phase for high aspect ratio silicon nanostructures," *ACS Appl. Mater. Interfaces*, vol. 11, pp. 27371–27377, 2019.

- [21] R. A. Lai, T. M. Hymel, V. K. Narasimhan, and Y. Cui, "Schottky barrier catalysis mechanism in metal-assisted chemical etching of silicon," *ACS Appl. Mater. Interfaces*, vol. 8, pp. 8875–8879, 2016.

- [22] J. D. Kim et al., "Scaling the aspect ratio of nanoscale closely packed silicon vias by MacEtch: Kinetics of carrier generation and mass transport," *Adv. Funct. Mater.*, vol. 27, 2017, Art. no. 1605614.

- [23] O. J. Hildreth, A. G. Fedorov, and C. P. Wong, "3D spirals with controlled chirality fabricated using metal-assisted chemical etching of silicon," *ACS Nano*, vol. 6, pp. 10004–10012, 2012.

- [24] J. D. Kim et al., "Self-anchored catalyst interface enables ordered via array formation from submicrometer to millimeter scale for polycrystalline and single-crystalline silicon," *ACS Appl. Mater. Interfaces*, vol. 10, pp. 9116–9122, 2018.

- [25] H.-C. Huang et al., " $\beta$ -Ga<sub>2</sub>O<sub>3</sub> FinFETs with ultra-low hysteresis by plasma-free metal-assisted chemical etching," *Appl. Phys. Lett.*, vol. 121, 2022, Art. no. 052102.

- [26] K. Balasundaram, P. K. Mohseni, Y.-C. Shuai, D. Zhao, W. Zhou, and X. Li, "Photonic crystal membrane reflectors by magnetic field-guided metal-assisted chemical etching," *Appl. Phys. Lett.*, vol. 103, 2013, Art. no. 214103.

- [27] X. Li, W. Zhou, and W. Huang, "Apparatus and method for magnetic-field guided metal-assisted chemical etching," U.S. Patent 9704951B2, Jul. 11, 2017.

- [28] T. K. Kim, J.-H. Bae, J. Kim, Y.-C. Kim, S. Jin, and D. W. Chun, "Bulk micromachining of Si by annealing-driven magnetically guided metal-assisted chemical etching," *ACS Appl. Electron. Mater.*, vol. 2, pp. 260–267, 2020.

- [29] O. J. Hildreth and D. R. Schmidt, "Vapor phase metal-assisted chemical etching of silicon," *Adv. Funct. Mater.*, vol. 24, pp. 3827–3833, 2014.

- [30] L. Romano et al., "Metal assisted chemical etching of silicon in the gas phase: A nanofabrication platform for X-ray optics," *Nanoscale Horiz.*, vol. 5, pp. 869–879, 2020.

- [31] S. A. Fortuna, J. Wen, I. S. Chun, and X. Li, "Planar GaAs nanowires on GaAs (100) substrates: Self-aligned, nearly twin-defect free, and transfer-printable," *Nano Lett.*, vol. 8, pp. 4421–4427, 2008.

- [32] C. Zhang, X. Miao, K. D. Chabak, and X. Li, "A review of III-V planar nanowire arrays: Selective lateral VLS epitaxy and 3D transistors," *J. Phys. D: Appl. Phys.*, vol. 50, 2017, Art. no. 393001.

- [33] X. Miao, K. Chabak, C. Zhang, P. K. Mohseni, D. Walker, and X. Li, "High-speed planar GaAs nanowire arrays with fmax >75 GHz by wafer-scale bottom-up growth," *Nano Lett.*, vol. 15, pp. 2780–2786, 2015.

- [34] W. Choi, H.-C. Huang, S. Fan, P. Mohseni, M. L. Lee, and X. Li, "Selective area heteroepitaxy of p-i-n junction GaP nanopillar arrays on Si (111) by MOCVD," *IEEE J. Quantum Electron.*, vol. 58, no. 4, Aug. 2022, Art. no. 3200106.

- [35] J. C. Shin et al., "In<sub>x</sub> Ga<sub>1-x</sub> as nanowires on silicon: One-dimensional heterogeneous epitaxy, bandgap engineering, and photovoltaics," *Nano Lett.*, vol. 11, pp. 4831–4838, 2011.

- [36] P. K. Mohseni et al., "Monolithic III-V nanowire solar cells on graphene via direct van der Waals epitaxy," *Adv. Mater.*, vol. 26, pp. 3755–3760, 2014.

- [37] P. K. Mohseni et al., "In<sub>x</sub> Ga<sub>1-x</sub> as nanowire growth on graphene: Van der Waals epitaxy induced phase segregation," *Nano Lett.*, vol. 13, pp. 1153–1161, 2013.

- [38] C.-Y. Liu et al., "Hybrid integration of n-MoS<sub>2</sub>/p-GaN diodes by Quasi-van der Waals epitaxy," *ACS Appl. Electron. Mater.*, vol. 2, pp. 419–425, 2020.

- [39] X. Li, "Strain induced semiconductor nanotubes: From formation process to device applications," *J. Phys. D: Appl. Phys.*, vol. 41, 2008, Art. no. 193001.

- [40] X. Yu et al., "Ultra-small, high-frequency, and substrate-immune microtube inductors transformed from 2D to 3D," *Sci. Rep.*, vol. 5, 2015, Art. no. 9661.

- [41] W. Huang et al., "Monolithic metasla-level magnetic induction by self-rolled-up membrane technology," *Sci. Adv.*, vol. 6, 2020, Art. no. eaay4508.

- [42] W. Huang et al., "Three-dimensional radio-frequency transformers based on a self-rolled-up membrane platform," *Nature Electron.*, vol. 1, pp. 305–313, 2018.

- [43] Z. Yang et al., "Monolithic heterogeneous integration of 3D radio frequency L-C elements by self-rolled-up membrane nanotechnology," *Adv. Funct. Mater.*, vol. 30, 2020, Art. no. 2004034.

- [44] P. Froeter, Y. Huang, O. V. Cangellaris, M. U. Gillette, J. C. Williams, and X. Li, "Toward intelligent synthetic neural circuits: Directing and accelerating neuron cell growth by self-rolled-up silicon nitride microtube array," *ACS Nano*, vol. 8, pp. 11108–11117, 2014.

- [45] A. Khandelwal et al., "Self-assembled microtubular electrodes for on-chip low-voltage electro-phoretic manipulation of charged particles and macromolecules," *Microsyst. Nanoeng.*, vol. 8, pp. 1–12, 2022.