# Class AB Amplifier With Noise Reduction, Speed Boost, Gain Enhancement, and Ultra Low Power

Ali Far

ali.t.far@ieee.org

**Abstract** — This paper presents an approach that improves the cost-performance of an amplifier whose output noise ( $V_{ONOISE}$ ) is lowered by narrow-banding filtering it, while slew rate (SR) and settling time ( $\tau_s$ ) are enhanced, when an imbalance is detected at the amplifier's input ( $V_{IN}$ ) via a rail-to-rail (RR) minimum-current-selector (MCS). The contributions of the proposed circuit are (1) increasing the amplifier's gain without impeding its dynamic response by implementing a boot-strapped gain stage in a folded cascode transconductance amplifier, or FCTA (2) lowering  $V_{ONOISE}$  and enhancing the amplifier's dynamic response, with a smaller size suppression capacitor, or  $C_s$ , which lowers die cost and reduces the boost current consumption, or  $I_{DD}$  (3) enhancing the amplifier's SR and  $\tau_s$ , lowering the dynamic  $I_{DD}$ , and improving the amplifier's power supply rejection, during the boost cycles, by utilizing a complementary MCS and a floating current summation, or FCS, circuits. Worst case simulations (WC), and Monte Carlo simulations (MC) simulations demonstrate the following: gain ( $A_V$ )  $\sim 120$ dB,  $\tau_s \sim 7\mu s$  to  $\sim 10\mu s$  with a rail-to-rail (RR) 1.5V step at  $V_{IN}$ ,  $V_{ONOISE}$  at 1kHz  $\sim 9\mu V/\sqrt{Hz}$ , unity gain band-width ( $f_u$ )  $\sim 5$ kHz, phase margin (PM)  $\sim 80$  degrees, current consumption ( $I_{DD}$ )  $\sim 180$ nA, minimum operating  $V_{DD} \sim 1.2$ V, power supply rejection ratio (PSRR)  $\sim 94$ dB, common mode rejection ratio (CMRR)  $\sim 125$ dB. Approximate amplifier area is  $\sim 70$   $\mu m$ /side in 0.18 $\mu m$  digital CMOS.

**Keywords** — low noise, dynamic biasing, ultra low power, class AB, high speed, rail to rail, buffer amplifier, batteryless, slew rate boost, energy harvesting, smart dust, self powered, IoT.

## I. INTRODUCTION

All else equal, operating an amplifier in the subthreshold region at ultra low  $I_{DD}$ , generally increases  $V_{ONOISE}$ , slows the dynamic response (SR and  $\tau_s$ ), and reduces  $A_V$  [4-6]. The proposed embodiment of the (patent pending) method disclosed in [1-3], lowers the  $V_{ONOISE}$  of an amplifier by band passing it with an oversized suppression capacitor ( $C_s$ ), while speeding up its  $\tau_s$  by dynamically boosting the amplifier's bias current, when its  $V_{IN}$  is subjected to a large signal. Trading-off for higher operating  $V_{DD}$  requirement, the advantages of the proposed circuit over those proposed in [1-2] are: achieving nearly the same  $V_{ONOISE}$  and  $\tau_s$  at  $\sim 1/3$   $I_{DD}$ , with  $\sim 50$ x more  $A_V$ , at  $\sim 1/60$  of peak boost-on (transient)  $I_{DD}$ , with  $\sim 1/6$ th the die size (due in part to smaller  $C_s$ ).

## II. NOISE REDUCTION & DYNAMIC RESPONSE (BOTH SLEW RATE AND SETTLING TIME) BOOSTING

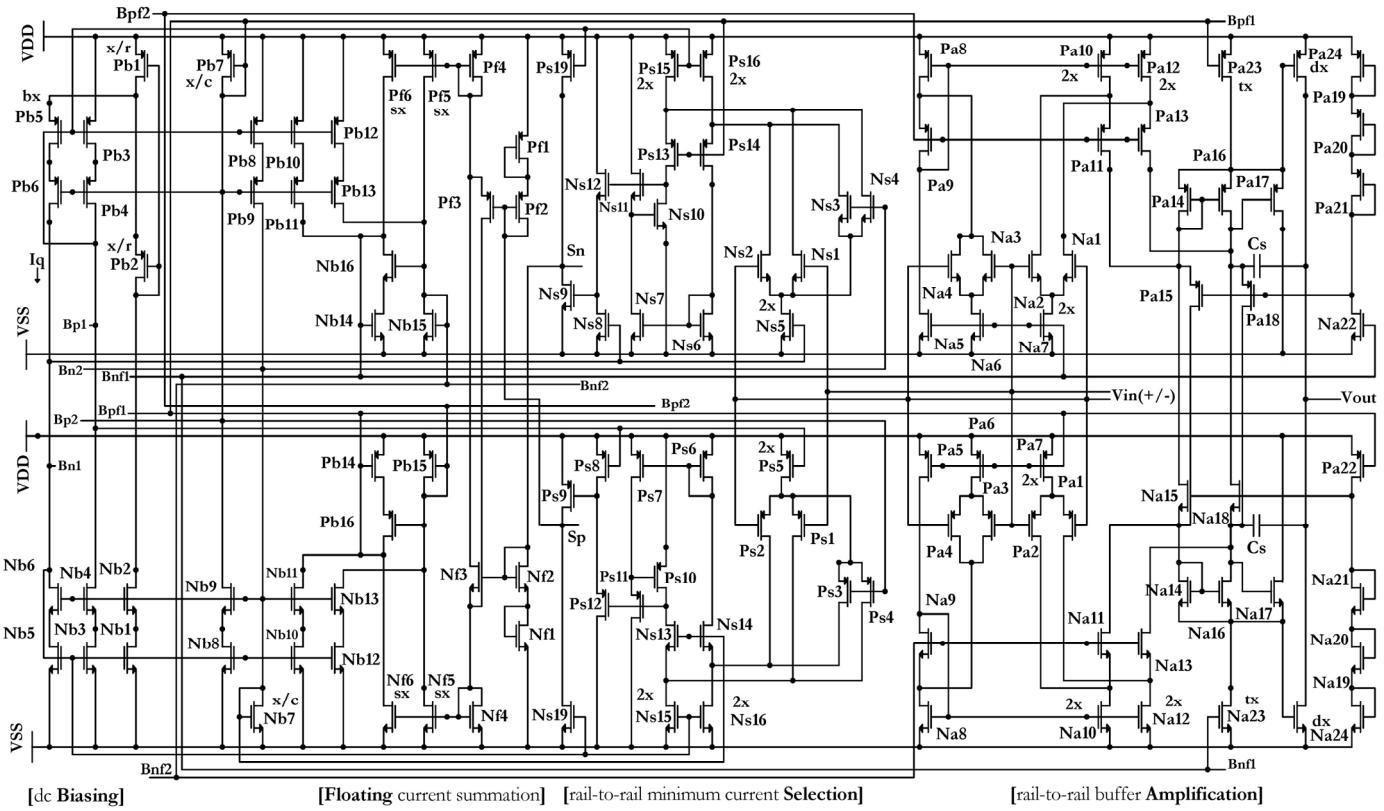

The proposed circuit is depicted in Fig. 1. For brevity, only the lower half of Fig. 1 is described here, given the symmetrical complementary nature of the upper and lower

TABLE I: SPECIFICATION COMPARISON

| Typical Specs                                     | [1][2]       | This work   | Figures   |

|---------------------------------------------------|--------------|-------------|-----------|

| Area ( $\mu m^2$ )                                | $\sim 180^2$ | $\sim 70^2$ | 21        |

| $V_{ONOISE}$ @1kHz( $\mu V/\sqrt{Hz}$ )           | 10           | 9           | 8         |

| $V_{DD}$ min (V) : with boost-on                  | 0.9          | 1.2         | 16        |

| $V_{DD}$ min (V) : with boost-off                 | 0.6          | 0.8         |           |

| $I_{DD}$ (nA)                                     | 500          | 175         | 18,19     |

| Peak Boost-on $I_{DD}$ ( $\mu A$ )                | 520          | 8.5         | 2,3,4,5   |

| Minimum $R_L$ ( $\Omega$ )                        | 2K           | 10K         | 10, 15    |

| Maximum $C_L$ (pF)                                | 1000         | 800         | 7         |

| $A_V$ (dB)                                        | 85           | 120         | 9,10      |

| $f_u$ (KHz)                                       | 20           | 5           | 9,10      |

| $\varphi_M$ (°)                                   | 75           | 85          | 9,10      |

| $ PSRR $ (dB)                                     | 85/80        | 92          | 13,14     |

| $ CMRR $ (dB)                                     | 125          | 94          | 11,12     |

| $V_{IN-pp}$ 1.5V pulse, $\tau_{S+/-}$ ( $\mu s$ ) | 5            | 6/7         | 2,3,4,5,6 |

halves of the circuit.

This first section describes the RR buffer amplifier stage, containing a boot-strapped FCTA that increases the amplifier's gain. In the RR common source amplifier (CSA) section of the FCTA, the  $I_{Pa1}$  and  $I_{Pa2}$  differential currents (in concert with  $I_{Na10}$  and  $I_{Na12}$ ) are steered onto  $N_{a11}$  and  $N_{a13}$ . Then,  $I_{Na11}$  and  $I_{Na13}$  are fed onto the FCTA high impedance high gain stage containing  $N_{a14}$  and  $N_{a16}$ , where  $VDS_{Na16}$  is boot-strapped through  $VGS_{Na17}$ . Qualitatively speaking, gain is enhanced here since  $VDS_{Na16}$  is held fairly constant (by  $VGS_{Na17}$ ), irrespective of variations in the FCTA's gain stage output voltage ( $VD_{Na16}$ ). Note that the boot-strapped topology, increases the minimum operating  $V_{DD}$  by an extra  $V_{GS}$ . Two floating constant current sources, containing  $N_{a15}$ ,  $P_{a15}$  and  $N_{a18}$ ,  $P_{a18}$ , provide the proper biasing for the boot-strapped gain stage (containing  $N_{a14}$ ,  $N_{a16}$ ,  $N_{a17}$ ). The output FETs ( $N_{a24}$ ,  $P_{a24}$ ) and the boot-strapped gain stage quiescent currents ( $I_{qc}$ ) are established by  $I_{Na23}$  and  $I_{Pa22}$ , which also bias  $VGS_{Na19} + VGS_{Na20} + VGS_{Na21} = VGS_{Na18} + VGS_{Na17} + VGS_{Na24}$ , in concert with their complementary symmetric counterparts,  $I_{Pa23}$  and  $I_{Na22}$  which bias  $VGS_{Pa19} + VGS_{Pa20} + VGS_{Pa21} = VGS_{Pa18} + VGS_{Pa17} + VGS_{Pa24}$ . A qualitative description of the transient signal flow of the boot-strapped gain stage is provided next.

During the transient rise of  $V_{OUT}$ ,  $N_{a14}$  is fed the extra transient differential current that is steered through  $I_{Na11}$  and  $I_{Na13}$  causing  $I_{Na14} \gg I_Q$  (for clarity, let's assume  $I_Q = I_{qc}$ , or equal quiescent currents in each of the FETs in the buffer amplifier stage, excluding  $N_{a24}$  and  $P_{a24}$ ). Hence, during this transitory phase,  $I_{Na14}$ 's mirror  $I_{Na16} \gg I_Q$  causes the decline in  $VDS_{Na16}$  and  $VGS_{Na17}$  (i.e.,  $N_{a16}$  enters triode, and  $N_{a17}$  shuts off). As such, during the transient rising of  $V_{OUT}$ , the

transient current through  $C_S$  is sourced by  $P_{a24}$  on one end and sunk on the other end (through  $N_{a16}$  in triode) and onto  $N_{a23}$  (scaled at 't.x') where  $I_{Na23} = t \times I_Q$ . The portion of  $I_{Na23}$  current, that was allocated to bias  $N_{a17}$  in steady state, is used here to speed up the transient response, given that  $N_{a17}$  is shut off. Note that during  $V_{OUT}$  transient rise, the capacitance at the output ( $N_{a24}$ 's gate) node is dominated by the roughly the Miller equivalent of  $C_{g_{Na24}}$ . When the  $N_{a15}$  and  $N_{a18}$  clamps kick in, the impedance at  $N_{a24}$ 's gate  $\sim \propto f(1/g_m)$  of  $N_{a14} - N_{a18}$  which are lowered by the extra available transient current ( $g_m \propto 1/I$ ) with the rising  $V_{OUT}$  (and falling  $V_{G_{Na24}}$ ).

Conversely, during the transient falling of  $V_{OUT}$ ,  $N_{a14}$  (and  $N_{a16}$ ) are starved from current and are nearly off. Here, the floating current source ( $P_{a18}$ ,  $N_{a18}$ ) dominated by  $P_{a18}$  pulls up the gate of  $N_{a17}$  source follower. When  $I_{Na14} = I_{Na16} \approx 0$ , then  $I_{Na17}$  gets all of  $\approx t \times I_Q$  that drives  $N_{a24}$  which speeds up the rise time for  $V_{G_{Na24}}$ . Moreover, note  $N_{a17}$  and  $P_{a17}$  source followers decouple the impact of large sized output FET's  $C_{g_{Na24}}$  and  $C_{g_{Pa24}}$ , providing more independence for the amplifier's AC response to be dominated by  $C_S$ . Note also that increasing the gain and the output impedance of FCTA via the boot-strap stage, reduces the size of (oversized noise suppressing)  $C_S$ , which speeds up the SR ( $C_S \propto 1/SR$ ). To accommodate RR span,  $P_{a3}$ ,  $P_{a4}$  track  $P_{a1}$ ,  $P_{a2}$  and turn off when  $V_{IN}$  is at or near  $V_{DD}$ . In order to avoid an  $I_{qc}$  imbalance in the FCTA boot-strap stage with  $V_{IN}$  near the rails, when  $P_{a7}$  is cut off from feeding  $N_{a10}$ ,  $N_{a12}$  (through  $P_{a1}$ ,  $P_{a2}$ ), then  $P_{a6}$  is also cut off from adding current (through  $P_{a3}$ ,  $P_{a4}$ ) to  $N_{a8}$  which is mirrored onto  $N_{a10}$ ,  $N_{a12}$ . Note also that in part,

Figure 1. Buffer Amplifier Circuit Schematic Simplified (patents pending)

because the amplifier's speed is boosted rail-to-rail (RR), making its input stage's  $g_m$  constant RR does not justify the added cost and overhead.

This second section describes the RR MCS<sub>P</sub>, which detects if  $V_{IN}$  is subjected to a large signal imbalance [5]. Un-equalized  $V_{IN}$  causes either of the drain currents  $I_{Ns13} = I_{Ps10} = I_{Ps1}$  or  $I_{Ns14} = I_{Ps6} = I_{Ps7} = I_{Ps11} = I_{Ps2}$  to be starved from current, which results in either of  $V_{GS_{Ps10}}$  or  $V_{GS_{Ps11}}$  to decline. Note that for MCS<sub>P</sub>, the  $V_{GS_{Ps11}} + V_{GS_{Ps10}} = V_{GS_{Ps9}} + V_{GS_{Ps12}}$ . Thus, when  $V_{GS_{Ps9}} + V_{GS_{Ps12}}$  declines enough, it causes  $P_{s9}$  to shut off. As such,  $I_{Ns19}$  pulls down on node  $S_p$  which initiates the 'boost-on' signal. The signal at  $S_p$ , via  $I_{Ns19}$ , drives the floating current summation (FCS<sub>P</sub>) section, where  $I_{Ns19} = I_{Pf1} = I_{Pf2}$ . Similarly, on the complementary side of (FCS<sub>N</sub>) when  $N_{s9}$  is off, then  $I_{Ps19}$  pulls up on  $S_n$ , which initiates a symmetric and complementary 'boost-on' signal as well (feeding  $I_{Nf1} = I_{Nf2}$ ).

In steady state, when  $V_{IN}$  is equalized then  $I_{Ps1} = I_{Ps2} = I_{Ps10} = I_{Ps11} = I_{Ps12} = I_{Ps8} = I_Q = I_{Ps9}$ . By setting  $I_{Ps9} > I_{Ns19}$ , then a 'boost-off' signal is initiated at node  $V_{Sp} \rightarrow V_{DD}$  that shuts off both  $P_{f1}$  and  $P_{f2}$ . Similarly, on the flip side (FCS<sub>N</sub>) by setting  $I_{Ns9} > I_{Ps19}$ , it causes  $V_{Sn} \rightarrow V_{SS}$ , which initiates a symmetric 'boost-off' signal, and shuts off both  $N_{f1}$  and  $N_{f2}$ . Also, for FCS<sub>N</sub> to span RR,  $P_{s3}$  and  $P_{s4}$  steer  $P_{s5}$  current away from  $P_{s1}$  and  $P_{s2}$  when  $V_{IN}$  gets near  $V_{DD}$ , causing  $V_{Sp} \rightarrow V_{DD}$  and thus disabling FCS<sub>N</sub> from falsely initiating a 'boost-on' signal. However, note that when  $V_{IN}$  is near  $V_{DD}$ , the complementary FCS<sub>P</sub> containing  $P_{s3}$  and  $P_{s4}$  continues tracking large signal imbalances at  $V_{IN}$ , and remains equipped to initiate the 'boost on and off' signals.

### SIMULATION RESULTS AND FIGURES

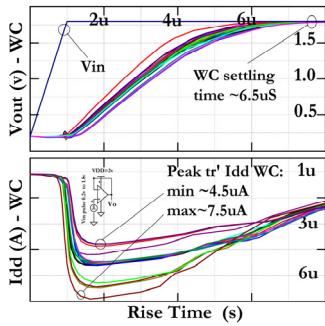

Fig. 2. Rising  $\tau_s$  of  $V_{OUT}$  &  $I_{DD}$  (WC)

Fig. 3. Falling  $\tau_s$  of  $V_{OUT}$  &  $I_{DD}$  (WC)

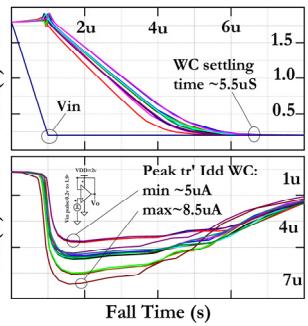

Fig. 4. Rising  $\tau_s$  of  $V_{OUT}$  &  $I_{DD}$  (MC)

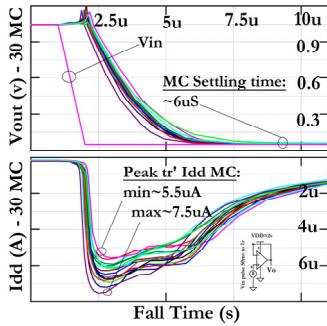

Fig. 5 Falling  $\tau_s$  of  $V_{OUT}$  &  $I_{DD}$  (MC)

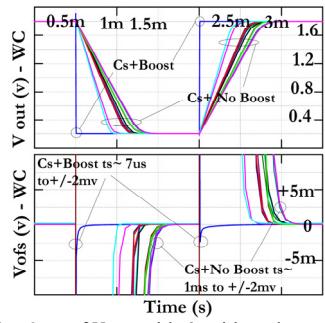

Fig. 6.  $\tau_s$  of  $V_{OUT}$  with & without boost (WC)

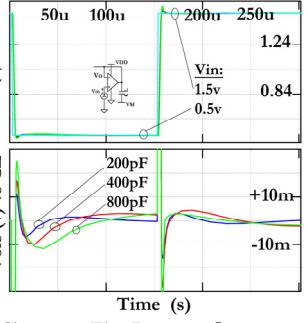

Fig. 7.  $\tau_s$  vs.  $C_L$

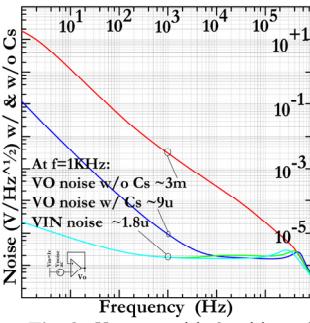

Fig. 8.  $V_{ONOISE}$  with & without  $C_s$

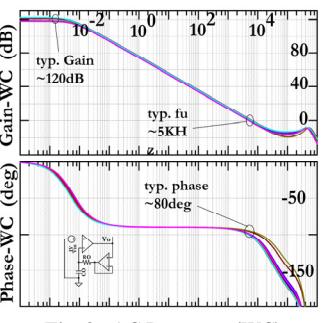

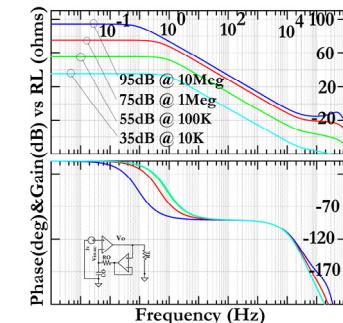

Fig. 9. AC Response (WC)

Fig. 10. AC response vs.  $R_L$

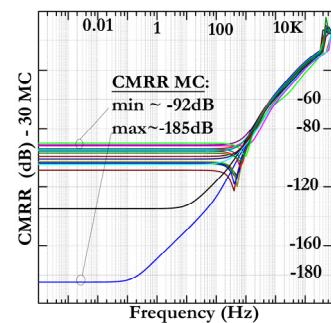

Fig. 11. CMRR (MC)

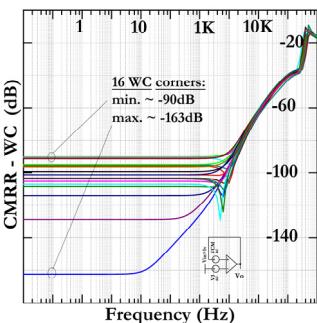

Fig. 12. CMRR (WC)

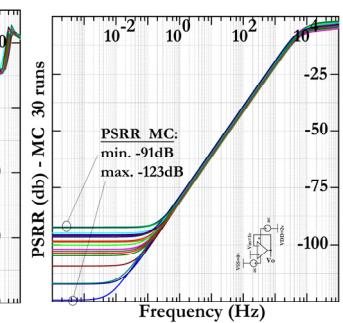

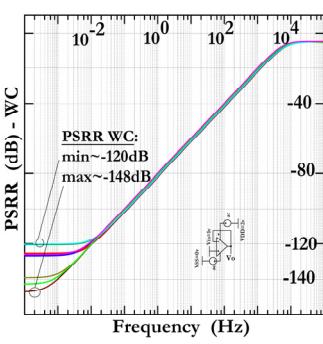

Fig. 13. PSRR  $V_{DD}$  (MC)

Fig. 14. PSRR  $V_{DD}$  (WC)

Fig. 15.  $I_{SINK}/I_{SOURCE}$  vs.  $R_L$

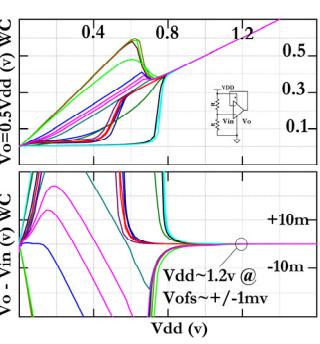

Fig. 16.  $V_{DD}$  vs.  $V_{OFFSET}$  (WC)

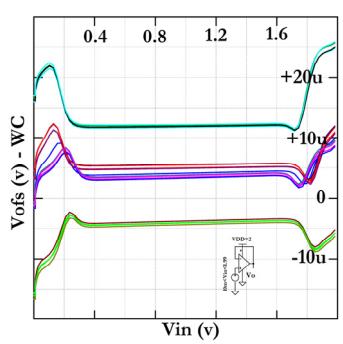

Fig. 17.  $V_{IN}$  vs.  $V_{OFFSET}$  (WC)

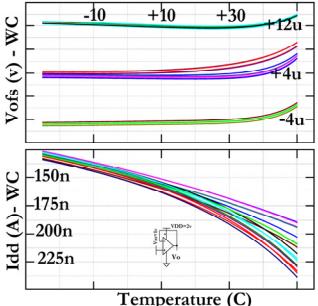

Fig. 18.  $V_{IN}$  vs.  $V_{OSF}$  vs. Temp (WC)

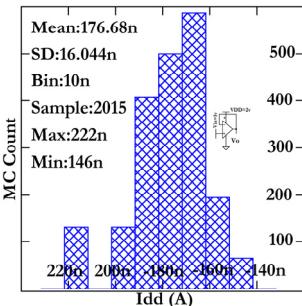

Fig. 19.  $I_{DD}$  (MC)

Fig. 20.  $V_{OFFSET}$  (MC)

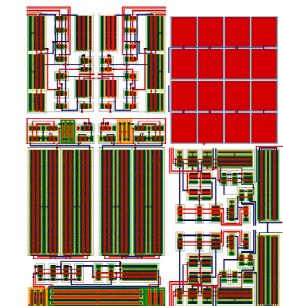

Fig. 21. Amplifier size  $\sim(70\mu\text{m})^2$

This third section describes the FCS. In 'boost-on' phase, FCS generates a fast current spike for the main amplifier's bias network ( $N_{b14-16}$  and  $P_{b14-16}$ ) to boost its SR. In 'boost-off' phase when  $V_{IN}$  starts nearing equalization, then FCS provides a slow decaying current for the amplifier's bias network (starting at the peak of 'boost-on' dynamic current level), to enhance the amplifier's  $\tau_s$ . With  $V_{GS_{Pf1}} + V_{GS_{Pf2}} = V_{GS_{Pf3}} + V_{GS_{Pf4}}$ , and  $V_{GS_{Nf1}} + V_{GS_{Nf2}} = V_{GS_{Nf3}} + V_{GS_{Nf4}}$ , then  $I_{Pf3} + I_{Nf3} = I_{FCS}$  (floating current source) where  $I_{FCS}$  feeds each of  $P_{f4}$  and  $N_{f4}$  concurrently. Note that  $I_{FCS}$  is mirrored (onto  $N_{f5}$ ,  $N_{f6}$ , and  $P_{f5}$ ,  $P_{f6}$ ) and scaled up by factor of 's' onto the central bias current network. In summary, when  $V_{IN}$  is imbalanced after it receives a large signal ('boost-on' phase), on the  $FCS_p$  side,  $N_{s19}$  turns on  $P_{f1}$ ,  $P_{f2}$  which turn  $P_{f3}$ ,  $P_{f4}$ ,  $N_{f4}$  on while (symmetrically and ) concurrently at the  $FCS_n$  side,  $P_{s19}$  turns on  $N_{f1}$ ,  $N_{f2}$  which turn on  $N_{f3}$ ,  $N_{f4}$ ,  $P_{f4}$ . As such,  $FCS_n$  and  $FCS_p$ , collectively and symmetrically, feed the amplifier's bias network with a fast current spike to speed up SR. Conversely, when the 'boost-off' signal is initiated,  $P_{f4}$ ,  $N_{f4}$  are cut off from current. As such, a decaying current (that continues feeding the amplifier's bias network) enhances  $\tau_s$ , which is initiated by cutting off  $P_{f4}$ ,  $N_{f4}$  where the current decay time constant is set by the impedance ( $g_m \propto 1/I$ ) and the equivalent  $C_{eqiv} \propto C_{g_{Pf5}} + C_{g_{Pf6}}$  and  $C_{g_{Nf5}} + C_{g_{Nf6}}$ .

### III. MONTE CARLO & WORST CASE SIMULATIONS SUMMARY

MOSIS equivalent models for BSIM3v3.1 for  $0.18\mu\text{m}$  CMOS are applied for WC and MC simulations. Table I provides a specification comparison summary. Figure 2 is WC  $\tau_{s+} \approx 6.5 \mu\text{s}$  to  $\pm 10\text{mV}$  with  $V_{in} \uparrow 1.6\text{V}$  step, transient  $5\mu\text{A} > I_{DD_{t+}} > 7.5\mu\text{A}$ . Figure 3 is WC  $\tau_{s-} \approx 5.5 \mu\text{s}$  to  $\pm 10\text{mV}$  with a  $V_{in} \downarrow 1.6\text{V}$  step, transient  $5\mu\text{A} > I_{DD_{t-}} > 8.5\mu\text{A}$ . Figure 4 is MC  $\tau_{s+} \approx 6 \mu\text{s}$  to  $\pm 10\text{mV}$  with a  $V_{in} \uparrow 0.95\text{V}$  step, transient  $5.5\mu\text{A} > I_{DD_{t+}} > 7.5\mu\text{A}$ . Figure 5 is MC  $\tau_{s-} \approx 6 \mu\text{s}$  to  $\pm 10\text{mV}$  with a  $V_{in} \downarrow 0.95\text{V}$  step, transient  $5.5\mu\text{A} > I_{DD_{t-}} > 7.5\mu\text{A}$ . Figure 6 is WC  $\tau_s$  ( $V_{in} \uparrow \downarrow 1.6\text{V}$  pulse) with the boost circuit on and without it. This indicates WC  $\tau_s < 7\mu\text{s}$  to  $\pm 2\text{mV}$  with the boost enabled, or more than 60X improvement in  $\tau_s$ , compared to WC  $\tau_s < 1\text{mS}$  to  $\pm 2\text{mV}$  with the boost disabled. Figure 7 is  $\tau_{s+}$  ( $< 25 \mu\text{s} \pm 10\text{mV}$  to with  $V_{in} \downarrow 1\text{V}$  step) vs.  $C_L$  (200pF, 400pF, and 800pF). Note here that  $\tau_{s-}$  is faster ( $V_{IN} \uparrow 1\text{V}$  step), but that is due to the tail-end of 'boost-off' current still decaying in the amplifier's bias network. Figure 8 is the noise response, indicating  $V_{ONOISE} \approx 9\mu\text{V}/\sqrt{\text{Hz}}$  at 1kHz with the noise reduction (band-pass) capacitor  $C_S$  vs.  $V_{ONOISE} \approx 3\text{mV}/\sqrt{\text{Hz}}$  at 1kHz without  $C_S$ , which indicates more than 300X improvement in  $V_{ONOISE}$ . Figure 9 is WC AC response with  $A_v \approx 120\text{dB}$ ,  $f_u \approx 5\text{kHz}$ ,  $\phi \approx 80^\circ$ . Figure 10 is typical AC response (gain at  $\sim 95\text{dB}$ ,  $\sim 75\text{dB}$ ,  $\sim 55\text{dB}$ ,  $35\text{dB}$ ) vs.  $R_L$  ( $10\text{M}\Omega$ ,  $1\text{M}\Omega$ ,  $100\text{k}\Omega$ , and  $10\text{k}\Omega$ , respectively). Figure 11 is MC  $-185\text{dB} < CMRR < -92\text{dB}$ . Figure 12 is WC  $-163\text{dB} < CMRR < -90\text{dB}$  for  $V_{DD}$ . Figure 13 is MC  $-123\text{dB} < PSRR < -91\text{dB}$  for  $V_{DD}$ . Figure 14 is WC  $-148\text{dB} < PSRR < -120\text{dB}$  for  $V_{DD}$ . Figure 15 is the output  $I_{sink \& source}$  vs.  $R_L$ :  $10\text{M}\Omega$ ,  $1\text{M}\Omega$ , and  $100\text{k}\Omega$  vs.

spanning  $10\text{mV} > V_{IN} > 1.99\text{V}$ . Fig. 16 is WC  $\min. V_{DD} > 1.2\text{V}$  by reading  $V_{OFFSET}$  (bias amplifier for  $I_{DD} = 8\mu\text{A}$  to emulate transient current during 'boost-on') and ramping up  $V_{DD}$  with  $V_{IN} = 1/2V_{DD}$ . Note that in boost-off phase, WC  $I_{DD} \min.$  is  $\sim 0.8\text{V}$ . Figure 17 is WC  $-10\mu\text{V} < V_{OFFSET} < +30\mu\text{V}$  spanning  $10\text{mV} < V_{IN} < +1.99\text{V}$ . Figure 18 is WC  $V_{OFFSET}$  and  $I_{DD}$  vs. temperature ( $T$ ) from  $-25^\circ\text{C}$  to  $+50^\circ\text{C}$ . Figure 19 and 20 are MC  $I_{dd}$  (avg.  $177\text{nA}$ ), and MC  $V_{OFFSET}$  (avg.  $160\mu\text{V}$ ). Figure 21 is rough layout size  $\sim (70\mu\text{m})^2$

### ACKNOWLEDGMENT

My gratitude to Professor Shahriar Mirabbasi at University of British Columbia for his review and comments.

### IV. CONCLUSION

Output noise of a rail-to-rail high-gain amplifier is lowered by band-pass filtering it with an oversized  $C_S$ , and when  $V_{IN}$  is imbalanced, the amplifier's speed is boosted. Accordingly, a dynamic current is injected into its bias during 'boost-on' to accelerate SR, as well as  $\tau_s$  during 'boost-off' by slowly decaying its bias current back to steady state levels. FCTA gain is enhanced by a boot-strapped topology that leaves the dynamic response generally unimpeded. A MCS initiates the boost on-off signals, via feeding a FCS circuit that supplies the amplifier's dynamic operating current, symmetrically and RR.

### REFERENCES

- [1] A. T. Far, "Ultra low power high-performance amplifier", U.S. patent pending Ser. No. 15/451,334

- [2] A. Far, "Low Noise Rail-To-Rail Amplifier Runs Fast at Ultra Low Currents And Targets Energy Harvesting," *2017 IEEE International Autumn Meeting on Power, Electronics and Computing (ROPEC)*, Ixtapa, 2017,

- [3] A. T. Far, "Sub-1 Volt Class AB Amplifier With Low Noise, Ultra Low Power, High-Speed, Using Winner-Take-All," *2018 IEEE 9th Latin American Symposium on Circuits & Systems (LASCAS)*, Puerto Vallarta, 2018,

- [4] Seevinck, E. et al., "Universal Adaptive Biasing Principle for Micropower Amplifiers," in Solid-State Circuits Conference, 1984. ESSCIRC '84. Tenth European, vol. no., pp.59-62

- [5] Y. Tsuruya et al., "A nano-watt power CMOS amplifier with adaptive biasing for power-aware analog LSIs," ESSCIRC (ESSCIRC), 2012 Proceedings of the, Bordeaux, 2012, pp. 69-72.

- [6] Allen P.E. , "Analog integrated circuit design", 1st. Ed., John Wiley & Sons, New York, 1997.

Ali Far received his B.S. in EECS from UC Berkeley; and MSEE, MBA, Juris Doctor in Law, and M.A. in Psychology, all from Santa Clara University. He is working on his M.A. in Philosophy at SFSU. He has more than 20 years of analog IC design experience in Silicon valley where he worked at Plantronics, PMI (ADI), MPS (MaxLinear), MVT (Creative Labs), and TelCom (Microchip) where he was Vice President of Design. He has 10 years of technology investment banking experience in Wall Street, where he worked at Prudential Securities, Galleon, and Spherix where he served as Technology Analyst. Ali has published a dozen papers in IEEE, has 14 patents and some pending in the area of analog ICs, and is currently researching ultra low power analog for energy harvesting.