1 **Ultrathin High-Mobility SWCNT Transistors with Electrodes Printed by Nanoporous

2 Stamp Flexography**

3 Dhanushkodi D. Mariappan<sup>1</sup>, Sanha Kim<sup>1,2</sup>, Junjie Zhao<sup>3</sup>, Hangbo Zhao<sup>1</sup>, Ulrich Muecke<sup>1</sup>, Karen

4 Gleason<sup>3</sup>, Akintunde Ibitayo Akinwande<sup>4</sup>, A. John Hart<sup>1\*</sup>

5 <sup>1</sup>Department of Mechanical Engineering, Massachusetts Institute of Technology, Cambridge, MA 02139,

6 USA.

7 <sup>2</sup>Department of Mechanical Engineering, Korea Advanced Institute of Science and Technology, Daejeon

8 34141, South Korea.,

9 <sup>3</sup>Department of Chemical Engineering, Massachusetts Institute of Technology, Cambridge, MA 02139, USA.

10 <sup>4</sup>Department of Electrical Engineering and Computer Science, Massachusetts Institute of Technology,

11 Cambridge, MA 02139, USA.

12

13 \*Corresponding author: [ajhart@mit.edu](mailto:ajhart@mit.edu)

14

15 **Abstract**

16 To achieve high-performance printed electronic devices, scalable and cost-effective printing of high-

17 quality metallic electrodes with narrow gaps, such for transistors with short channel lengths, is desirable.

18 Here, we demonstrate short channel (<10 $\mu$ m) transistors, using thin (< 100-200 nm) electrodes fabricated

19 by flexographic printing with nanoporous stamps, with single-wall carbon nanotubes (SWCNTs) as the

20 network semiconductor. The nanoporous stamps comprise polymer-coated vertically aligned carbon

21 nanotubes (CNTs) and facilitate control of the printed ink thickness in the 50-200 nm range. The

22 measured on-off ratio and mobility meet or exceed those of previously reported SWCNT network

23 transistors fabricated by alternative printing methods.

24

25 **Keywords:** printed electrodes, transistors, flexography, nanoporous stamps, SWCNT networks

26

27

1    **Main Text**

2    High-throughput, cost-effective manufacturing of electronics including radio frequency identification

3    (RFID) tags<sup>1</sup>, gas sensors, and light emitting diodes (LEDs) is essential to broader availability of

4    technologies such as smart packages, wearable displays, and skin-conforming medical devices<sup>2-6</sup>. To

5    expand the use of electronics in such daily-life products, silicon microfabrication processes are limited in

6    terms of cost, throughput and substrate flexibility. Printed electronics utilizing scalable printing

7    technologies, such as inkjet, screen printing, gravure and flexography are promising alternatives.

8    Therefore, a massive number of research, development and production of printed electronic devices has

9    been reported in the last two decades<sup>7-10</sup>.

10   Transistors are a basic building block of printed electronics, and the transistor quality and performance

11   are driven by the choice of materials, degree of miniaturization, and dimensional precision. For example,

12   the performance of the printed displays<sup>11,12</sup> is driven by the thickness and the switching speed of the

13   constituent thin-film transistors<sup>13,14</sup>. The speed of a thin-film transistor depends mainly on the

14   semiconductor carrier mobility and the channel length, measured by the distance between the source and

15   drain electrodes. Thick and non-uniform dielectric and electrode layers in transistors lead to lower

16   breakdown voltages due to large localized electric fields<sup>13</sup>. Therefore, the performance of transistors

17   manufactured by printing technologies are correlated with lateral resolution and minimum thickness of

18   extant methods<sup>9</sup>.

19   Most of printing technologies for electronics use liquid or polymeric inks, often containing colloidal

20   nanoparticles that are annealed to form films after evaporation of the carrier solvent. As such, limitations

21   to the feature size and thickness are attributed to the coupled, time-dependent fluid and solid mechanics of

22   the printing process. Recently, flexographic printing with significantly finer printed feature dimensions

23   was achieved using nanoporous stamps instead of traditional non-porous polymer stamps.<sup>9</sup> The

24   nanoporous stamps can retain the ink within their volume<sup>9,15</sup>, enabling the printed pattern to precisely

25   replicate the shape of stamp features without suffering the squeeze-out and dewetting instabilities that are

26   common in traditional flexography with non-porous elastomeric stamps. Nanoporous flexography, which

27   is capable of printing conductive, dielectric, and semiconducting nanoparticle inks into features having ~3

28    $\mu\text{m}$  minimum width and ~30-50 nm thickness at high speed (0.1 m/s)<sup>9,16</sup>, is therefore attractive for

29   printing high performance transistors as elements of future integrated devices.

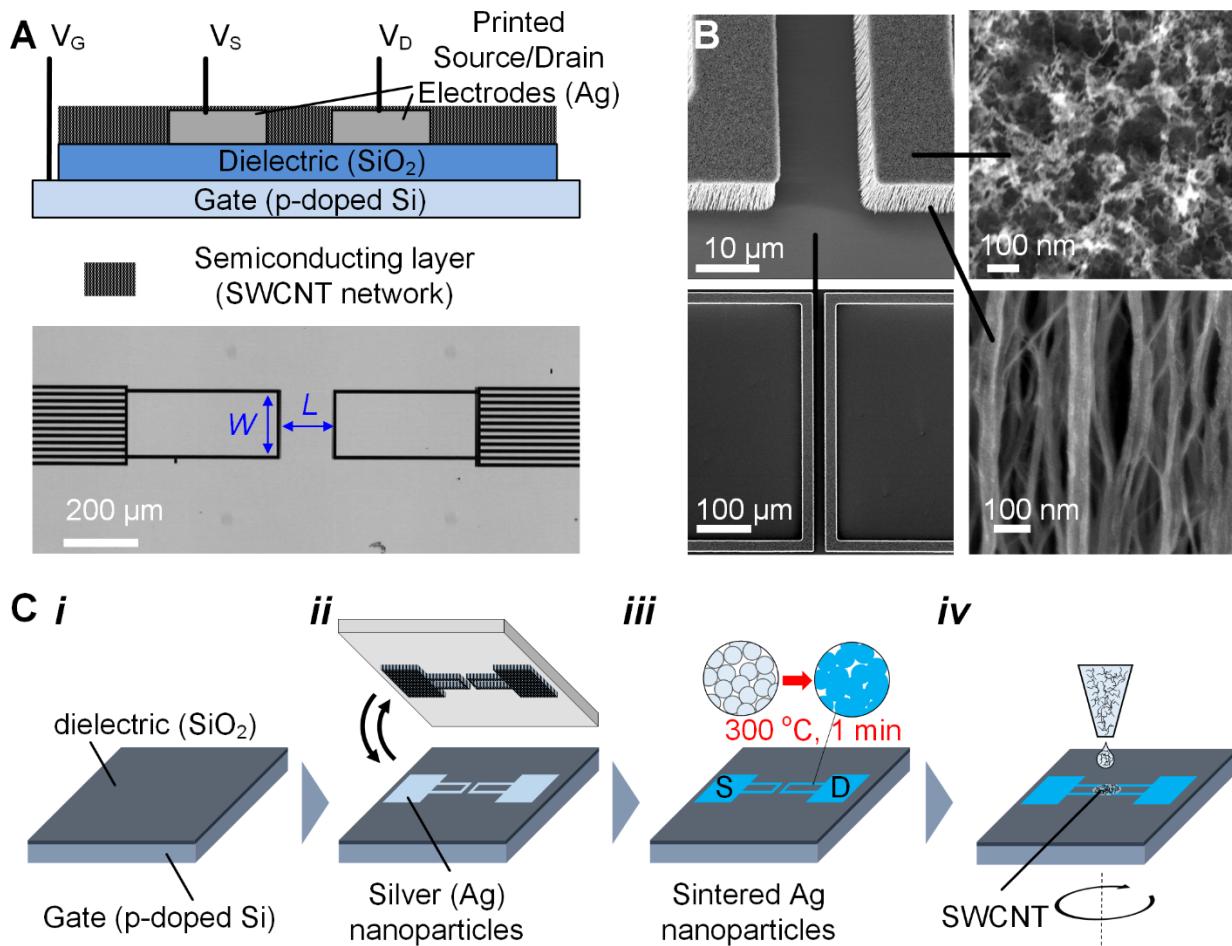

30   Here, we demonstrate thin (< 100-500 nm), short channel (<10  $\mu\text{m}$ ) transistors, using electrodes fabricated

31   by flexographic printing with nanoporous stamps, with single-wall carbon nanotubes (SWCNTs) as the

32   network semiconductor. We designed and fabricated a bottom gate, top-contact transistor as shown in

33   [Fig.1A](#). The device consists of a p-doped silicon gate electrode (resistance = 0.001-0.005  $\Omega\text{-cm}$ , thickness

34   = 500  $\mu\text{m}$ ), thermally grown silicon dioxide (thickness = 300 nm, University Wafer Product No. 1583)

35   dielectric layer, silver source and drain electrodes (thickness ~100-200 nm), and SWCNT network

36   semiconducting layer.

37   Flexographic printing of silver electrodes was achieved with nanoporous stamps comprising vertically

38   aligned carbon nanotubes (CNTs) which are conformally coated with polymer via initiated chemical

39   vapor deposition (iCVD, [Fig.1B](#)). We inked the stamp via spin-coating, and the high porosity (~90%) of

40   the prepared stamp allows to retain the liquid ink within their volume. Using the inked stamp designed

41   according to the device, the source and drain electrode pattern ([Fig. 1C](#)) was printed directly onto the

42   oxide-coated silicon wafer. For successful printing, control of contact pressure was essential, and must lie

1 within a range determined by the stiffness of the CNTs, CNT-CNT spacing, and the standard deviation of

2 the lengths of CNTs.<sup>9,15</sup> In a prior work, we estimate the pressure range where the area ratio (ratio of area

3 of stamp pattern to printed pattern) is ~ 1 using experiments and analytical modeling. The thickness of the

4 printed layer can be controlled via the speed at which the stamp is retracted away from the substrate after

5 contact. During printing, in a custom-built plate-to-plate printing apparatus<sup>9</sup>, we brought the stamp into

6 contact with the wafer and apply a contact pressure of ~50 to 100 kPa using a weight. After maintaining

7 contact for ~15 s, we retracted the stamp quasi-statically (~1 mm/s) enabling printing of layers with

8 thickness > 200nm after solvent evaporation.

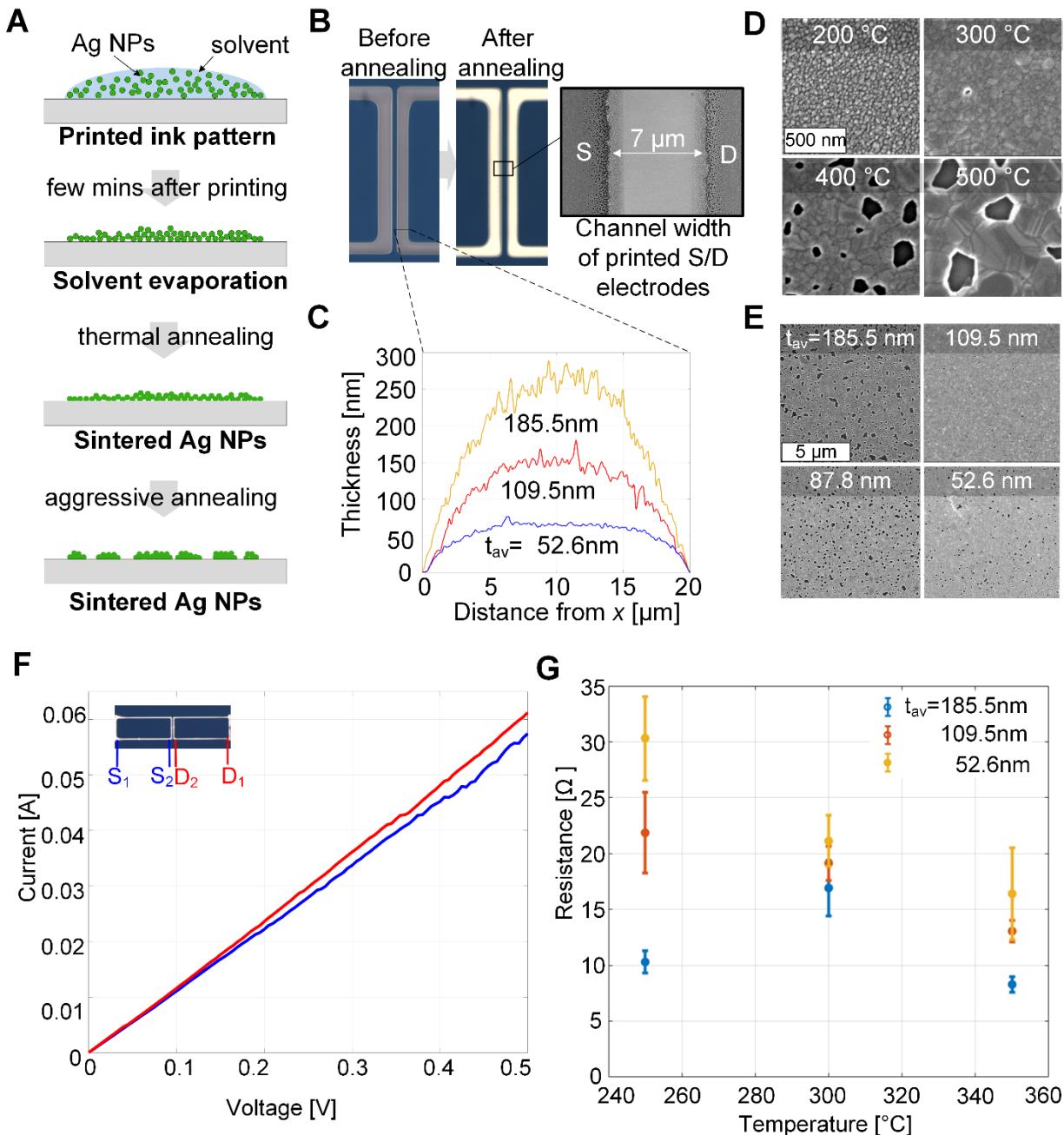

9 The liquid ink (736511, Sigma Aldrich) contained <10 nm silver nanoparticles dispersed in tetradecane

10 with ~50-60% weight concentration. After drying for 2 mins in ambient conditions, the substrate with the

11 printed ink pattern was annealed to retain the electrical conductivity by sintering the metal particles into a

12 continuous film (Fig. 2A-C). Here, the annealing condition needs to be appropriately controlled

13 considering the printed thickness, as excessive temperature and/or annealing time can cause dewetting

14 and breakup of the Ag film. Annealing was performed in ambient conditions on a hot plate with a set

15 temperature of 200-500 °C<sup>17</sup>. Higher annealing temperature and longer annealing time results in greater

16 grain size therefore can enhance the electrical conductivity, yet voids may form once the local metal grain

17 size exceed the layer thickness and therefore the conductivity reduces. At sintering temperatures below

18 300 °C coarsening and densification is insufficient and at temperatures above 300 °C, though continuous

19 films with large grains form locally, several voids form and this can lead to large variations in the

20 measured conductivity of the sintered films (Fig. 2D). At sintering temperature of 300 °C, it is possible to

21 form continuous layers with few voids for printed layers of thicknesses varying from 50 to 250 nm (Fig.

22 2E). With appropriate annealing, the measured conductivity (Fig. 2F, 2G) of the annealed source and

23 drain electrodes was  $4.25 \times 10^7$  S/m, which is 70% of that of bulk silver.

24 The annealing condition should be adjusted according to the printing thickness. For experimental

25 investigation, we printed electrodes with different thickness of ~50 nm, 110 nm, and 185 nm (Fig. 2C).

26 We observed the SEM images of the annealed samples to assess the continuity of films qualitatively (Fig.

27 2E). For the thinnest layers (~50nm), dewetting leads to discontinuities in the sintered layers. The

28 resistance of the sintered layers was measured by printing lines of length ~850 μm and width ~10 μm

29 (Fig. 2G). The resistance decreases with increasing sintering temperature for lines of thicknesses >100nm.

30 (Fig. 2G). At 250 °C sintering temperature, resistance is high and has the largest variation with thickness.

31 At 350 °C sintering temperature, resistance is the lowest for all thicknesses but there is large variation

32 with thickness. But, at 300 °C sintering temperature, for printed films of  $t_{av}$  ~50- 250nm, resistance has

33 minimum variation with thickness. Therefore, 300 °C was determined to be the optimal sintering

34 temperature, and good quality features with conductivity of  $4.4 \times 10^7$  S/m (~70% of bulk silver) and the

35 minimum sintering time is ~ 1 min.

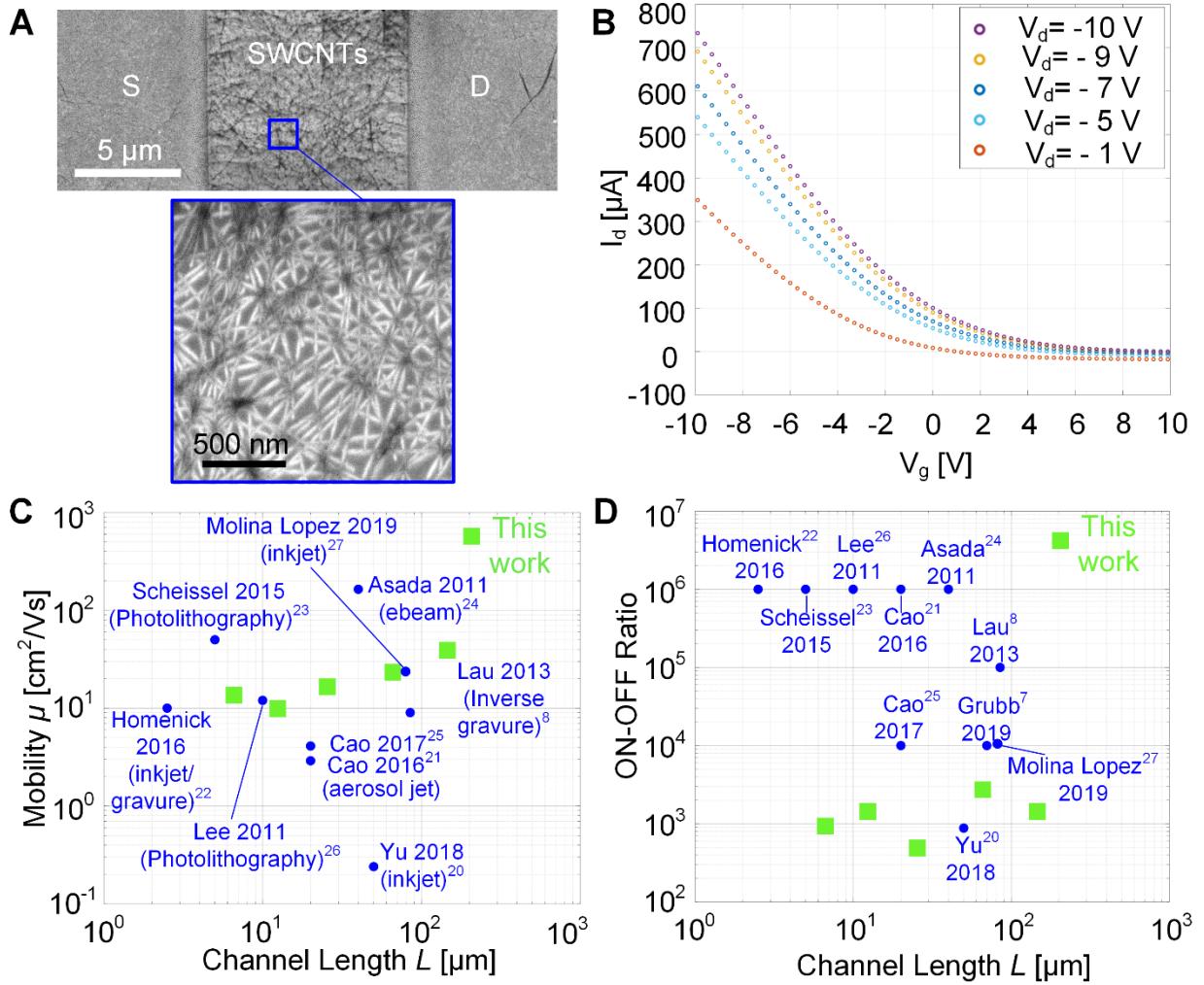

36 We selected SWCNTs as the semiconducting layer, owing to the compatibility of solution-based SWCNT

37 deposition with non-lithographic fabrication. The performance of CNT network transistors strongly

38 depends not only on the quality of individual CNTs but also the CNT density. We deposited the

39 semiconducting layer on top of our printed S/D electrodes via spincoating, and the density was tunable by

40 the droplet volume, spincoating speed and duration. Here, a 300 μl droplet of ink (NanoIntegris, IsoSol-

41 S100, 99.9% purity) was pipetted onto the wafer and then the wafer was spun to 1500 rpm for 15 seconds

42 in a spincoater (Specialty Coating Systems, G3P SPINCOAT). No surface pretreatment was used before

43 deposition. The measured density of the network of SWNCTs is ~100 SWCNTs/μm<sup>2</sup> (Fig. 3A, Fig.S1)

44 which is above the percolation threshold<sup>18,19</sup> (> 40 SWCNTs/μm<sup>2</sup>) resulting in high on-conductance and

45 mobility.

1 The transfer characteristics of the fabricated transistors were measured by varying  $V_g$  from -10V to +10V

2 and measuring  $I_d$  for  $V_d = 1V, 5V, 7V, 9V, 10V$ . [Fig. 3B](#), [Fig. S2](#) shows the transfer characteristics for the

3 transistor with a channel length of 7  $\mu m$ . The on-off ratio of the transistors exceeded  $10^3$  and the threshold

4 voltage varied from 1 V to 8 V. The mobility is calculated based on the slope of the plot of  $\sqrt{I_d}$  against

5  $V_g$  using the following equation (see Supporting Information)

6

$$\sqrt{I_d} = \sqrt{\frac{\mu C_{ox} W}{2L}} (V_g - V_T)$$

7 where  $\mu$ ,  $C_{ox}$ , and  $V_T$  are the mobility, oxide capacitance and threshold voltage respectively. [Fig. S3](#)

8 compares the transfer characteristics at  $V_d = 1V$  for three transistors with channel lengths of 6.6, 12.4, and

9 146  $\mu m$ . The mobility increases from  $13.8 \text{ cm}^2/\text{Vs}$  for  $L = 12.4 \mu m$  to  $39.5 \text{ cm}^2/\text{Vs}$  for  $L = 146 \mu m$  ([Table S1](#)). The mobility variation with channel length is likely due to the variation in the SWCNT network

10 density between the devices of different channel lengths. The extracted mobility is also likely affected by

11 the contact resistance and its variations. The low on-off ratio is likely due to high contact resistance. The

12 output resistance calculated from the output characteristics ([Fig. S4](#)) does not vary significantly with the

13 gate voltage, which is one of the indicators of high contact resistance in the device.

14 The on-off ratio and the mobility of our transistors were determined in the range of  $10^3$ - $10^4$  and  $\sim 13$ - $39$ ,

15 respectively, which are comparable to other printed transistors ([Fig. 3C and 3D](#)).<sup>7,8,20-27</sup> The total thickness

16 of the device excluding the gate (p-doped Si) layer is  $\sim 400$ - $600$  nm which is thinner than other printed

17 transistors reported in literature.<sup>13,28</sup> With nanoporous stamps, ultra-thin layers can be printed as the ink

18 transfer volume per unit length is the lowest as compared to other printing processes<sup>9</sup>. Notably, nanoporous

19 stamps can be adopted to continuous manufacturing by fabricating CNTs on a roller and using a continuous

20 inking system. In prior work, we have shown also compatibility with continuous printing in a plate to roll

21 format, and the combination of speed ( $>200$  mm/s) and resolution ( $\sim 3 \mu m$ ) surpasses published process

22 capabilities for flexography, gravure, inkjet and screen printing processes<sup>9</sup>.

23 We have demonstrated a TFT with good performance characteristics. To demonstrate a fully printed

24 device on flexible substrates, printing of gate and dielectrics and optimization of sintering conditions are

25 required and we expect these can be achieved. The printing of SWCNT networks can also be studied. By

26 using layer to layer registration and achieving a designed overlap between the S/D electrodes and

27 dielectric layer, leakage currents can be reduced to achieve even higher on-off ratios ( $>10^4$ ) than what has

28 been achieved in this work.

29

30

1    **Supporting Information**

2    Fabrication of transistor by printing silver nanoparticles and forming a continuous layer by sintering and

3    deposition of SWCNT networks with organic solvent based ink, Transfer characteristics of the transistor

4    (channel length 7  $\mu\text{m}$ ) for drain voltages varying from 1-10V, Transfer Characteristics of the transistors

5    with channel lengths varying from 6.6 to 146  $\mu\text{m}$  plotted as  $\sqrt{I_d}$  against  $V_g$  for calculation of mobility and

6    on-off ratio, Output characteristics of the transistor (channel length 7  $\mu\text{m}$ ) for gate voltages varying from -

7    3V to -0.5V, On-off ratio and mobility values for the transistors calculated from the transfer characteristics,

8    Mobility calculation using model for linear region.

9

10    **Acknowledgements**

11    Financial support was provided by the National Science Foundation (CMMI-1463344, CMMI-1826216),

12    the MIT Energy Initiative Seed Fund, the MIT-Skoltech Next Generation Program (First Round, 2016-

13    2019), and BAE Systems. We thank Ahmad Zubair, Elaine McVay, and Marek Hempel for assistance in

14    measurements of transfer characteristics. CNT catalyst deposition and patterning were performed at the

15    MIT Microsystems Technology Laboratory (MTL). Electron microscopy and profilometry were performed

16    at the shared experimental facilities at the MIT Center for Materials Science and Engineering (CMSE)

17    supported in part by the MRSEC Program of the National Science Foundation under award number DMR-

18    1419807.

19

20    **Methods**

21    **Stamp Fabrication** The stamp consists of source and drain electrodes with different channel lengths ( $L=5$ -

22     $150\mu\text{m}$ ) and fixed width ( $W=200\mu\text{m}$ ). An exemplary stamp is shown in [Fig. 1B](#). To fabricate the stamps<sup>9</sup>,

23    first vertically aligned CNT arrays (CNT ‘forests’) are grown on lithographically patterned silicon

24    substrates by atmospheric pressure chemical vapor deposition (CVD). Then, the top entangled ‘crust’ layer

25    ( $<1\mu\text{m}$  thickness) is removed by a brief oxygen plasma etching (Diener, Femto Plasma System) and coated

26    with a thin layer ( $\sim 20\text{ nm}$ ) of poly-perfluorodecylacrylate (pPFDA) using initiated CVD (iCVD).<sup>9,29,30</sup> The

27    plasma etching is critical to remove the stiff and rough crust which is not desirable for high-resolution

28    printing because it results in non-uniform contact against the target substrate. The pPFDA coating followed

29    by second plasma treatment allow liquid infiltration and solvent evaporation without shrinkage or collapse

30    of the CNT forest by elastocapillary densification. The final plasma-treated pPFDA-CNT microstructures

31    are highly porous ( $>90\%$  porosity) with nanometer pore size ( $\sim 100-200\text{ nm}$ ), allow liquid infiltration

32    without deformation due to capillary forces, and are mechanically compliant, enabling uniform contact with

33    the target substrates.

34    **Inking** The ink used in this study is composed of silver nanoparticles dispersed in tetradecane (Sigma-

35    Aldrich, 736511). The surface tension and viscosity of the ink are 27 mN/m and 10 mPa-s, respectively,

36    and the ink exhibits good conductivity (30-60% of bulk silver) after annealing.<sup>9</sup> The particle concentration

37    is 50-60 wt% with particle sizes less than 10 nm. A 100  $\mu\text{l}$  droplet of ink is pipetted onto the stamp and

38    then the stamp is spun to 1500 rpm for 1-3 minutes in a spincoater.

1    **Annealing** A hot plate was used to do rapid annealing of the silver nanoparticles after printing the silver

2    ink. The hot plate was set to the 300 °C and the stamps were placed on the hotplate after it reached the

3    setpoint. The stamps were left on the hot plate for 1 minute for annealing.

4    **Device Characterization** A DC probe station and semiconductor parameter analyzer (Agilent 4155C,

5    Easy Expert software) were used for the measurement of conductivity of the annealed electrodes, and the

6    transfer characteristics of the TFTs.

7

8

1      **References**

2      (1) Want, R. A Key to Automating Everything Already Common in Security Systems. *Sci Am*

3      **2004**, *290* (1), 56–65.

4      (2) Vena, A.; Perret, E.; Tedjini, S.; Tourtollet, G. E. P.; Delattre, A.; Garet, F.; Boutant, Y.

5      Design of Chipless RFID Tags Printed on Paper by Flexography. *IEEE Trans Antennas

6      Propag* **2013**, *61* (12), 5868–5877. <https://doi.org/10.1109/TAP.2013.2281742>.

7      (3) Ostfeld, A. E.; Deckman, I.; Gaikwad, A. M.; Lochner, C. M.; Arias, A. C. Screen Printed

8      Passive Components for Flexible Power Electronics. *Sci Rep* **2015**, *5*, 1–11.

9      <https://doi.org/10.1038/srep15959>.

10     (4) Wang, X.; Zhang, Y.; Guo, R.; Wang, H.; Yuan, B.; Liu, J. Conformable Liquid Metal

11     Printed Epidermal Electronics for Smart Physiological Monitoring and Simulation

12     Treatment. *Journal of Micromechanics and Microengineering*. Institute of Physics

13     Publishing February 5, 2018. <https://doi.org/10.1088/1361-6439/aaa80f>.

14     (5) Kuberský, P.; Syrový, T.; Hamacek, A.; Nešpůrek, S.; Stejskal, J. Printed Flexible Gas

15     Sensors Based on Organic Materials. In *Procedia Engineering*; Elsevier Ltd, 2015; Vol.

16     120, pp 614–617. <https://doi.org/10.1016/j.proeng.2015.08.746>.

17     (6) Gao, W.; Ota, H.; Kiriya, D.; Takei, K.; Javey, A. Flexible Electronics toward Wearable

18     Sensing. *Acc Chem Res* **2019**, *52* (3), 523–533.

19     <https://doi.org/10.1021/acs.accounts.8b00500>.

20     (7) Grubb, P. M.; Mokhtari Koushyar, F.; Lenz, T.; Asghari, A.; Gan, G.; Xia, W.; Dalir, H.;

21     Subbaraman, H.; Chen, R. T. High Speed Roll-to-Roll Printable Transistor Enabled by a

22     Pulsed Light Curable CNT Ink. *Journal of Manufacturing and Materials Processing* **2019**,

23     *3* (2), 33. <https://doi.org/10.3390/jmmp3020033>.

24     (8) Lau, P. H.; Takei, K.; Wang, C.; Ju, Y.; Kim, J.; Yu, Z.; Takahashi, T.; Cho, G.; Javey, A.

25     Fully Printed, High Performance Carbon Nanotube Thin-Film Transistors on Flexible

26     Substrates. **2013**. <https://doi.org/10.1021/nl401934a>.

27     (9) Kim, S.; Sojoudi, H.; Zhao, H.; Mariappan, D.; McKinley, G. H.; Gleason, K. K.; Hart, A.

28     J. Ultrathin High-Resolution Flexographic Printing Using Nanoporous Stamps. *Sci Adv*

29     **2016**, *2* (12), e1601660. <https://doi.org/10.1126/sciadv.1601660>.

30     (10) Reddy, A. S. G.; Narakathu, B. B.; Eshkeiti, A.; Bazuin, B. J.; Joyce, M.; Atashbar, M. Z.

31     Fully Printed Organic Thin Film Transistors (OTFT) Based Flexible Humidity Sensors. In

32     *Proceedings of IEEE Sensors*; IEEE Computer Society, 2013.

33     <https://doi.org/10.1109/ICSENS.2013.6688309>.

34     (11) Wang, C.; Zhang, J.; Ryu, K.; Badmaev, A.; Arco, L. G. De; Zhou, C. Wafer-Scale

35     Fabrication of Separated Carbon Nanotube Thin-Film Transistors for Display Applications.

36     **2009**. <https://doi.org/10.1021/nl902522f>.

37     (12) Suzuki, K.; Yutani, K.; Nakashima, M.; Onodera, A.; Mizukami, S.; Kato, M.; Tano, T.;

38     Tomono, H.; Yanagisawa, M.; Kameyama, K. All-Printed Organic TFT Backplanes for

39     Flexible Electronic Paper. **2010**, 1–6.

1 (13) Fukuda, K.; Someya, T. Recent Progress in the Development of Printed Thin-Film

2 Transistors and Circuits with High-Resolution Printing Technology. *Advanced Materials*

3 **2017**, *29* (25). <https://doi.org/10.1002/adma.201602736>.

4 (14) Khan, S.; Lorenzelli, L.; Dahiya, R. S. Technologies for Printing Sensors and Electronics

5 over Large Flexible Substrates: A Review. *IEEE Sens J* **2015**, *15* (6), 3164–3185.

6 <https://doi.org/10.1109/JSEN.2014.2375203>.

7 (15) Mariappan, D. D.; Kim, S.; Boutilier, M. S. H.; Zhao, J.; Zhao, H.; Beroz, J.; Muecke, U.;

8 Sojoudi, H.; Gleason, K.; Brun, P. T.; Hart, A. J. Dynamics of Liquid Transfer from

9 Nanoporous Stamps in High-Resolution Flexographic Printing. *Langmuir* **2019**, *35* (24),

10 7659–7671. <https://doi.org/10.1021/acs.langmuir.9b00460>.

11 (16) Mariappan, D. D.; Kim, S.; Hart, A. J. A Precision Desktop Plate-to-Roll Apparatus for

12 Development of Advanced Flexographic Printing Processes. *Precis Eng* **2020**, *66*

13 (January), 392–400. <https://doi.org/10.1016/j.precisioneng.2020.07.012>.

14 (17) Kim, J.; Oh, J.; Jung, K.-M.; Park, K.; Kim, Y.-S.; Jeon, J.-H. Ultrathin Flexible Thin Film

15 Transistors with CYTOP Encapsulation by Debonding Process. *Semicond Sci Technol*

16 **2019**. <https://doi.org/10.1088/1361-6641/ab2201>.

17 (18) Kocabas, C.; Pimparkar, N.; Yesilyurt, O.; Kang, S. J.; Alam, M. A.; Rogers, J. A.

18 Experimental and Theoretical Studies of Transport through Large Scale, Partially Aligned

19 Arrays of Single-Walled Carbon Nanotubes in Thin Film Type Transistors. *Nano Lett*

20 **2007**, *7* (5), 1195–1202. <https://doi.org/10.1021/nl062907m>.

21 (19) Zhou, Y.; Gaur, A.; Hur, S.-H.; Kocabas, C.; Meitl, M. a; Shim, M.; Rogers, J. a. P-

22 Channel, n-Channel Thin Film Transistors and P–n Diodes Based on Single Wall Carbon

23 Nanotube Networks. *Nano Lett* **2004**, *4* (10), 2031–2035.

24 <https://doi.org/10.1021/nl048905o>.

25 (20) Yu, M.; Wan, H.; Cai, L.; Miao, J.; Zhang, S.; Wang, C. Fully Printed Flexible Dual-Gate

26 Carbon Nanotube Thin-Film Transistors with Tunable Ambipolar Characteristics for

27 Complementary Logic Circuits. *ACS Nano* **2018**, *12* (11), 11572–11578.

28 <https://doi.org/10.1021/acsnano.8b06748>.

29 (21) Cao, C.; Andrews, J. B.; Kumar, A.; Franklin, A. D. Improving Contact Interfaces in Fully

30 Printed Carbon Nanotube Thin-Film Transistors. *ACS Nano* **2016**, *10* (5), 5221–5229.

31 <https://doi.org/10.1021/acsnano.6b00877>.

32 (22) Homenick, C. M.; James, R.; Lopinski, G. P.; Dunford, J.; Sun, J.; Park, H.; Jung, Y.; Cho,

33 G.; Malenfant, P. R. L. Fully Printed and Encapsulated SWCNT-Based Thin Film

34 Transistors via a Combination of R2R Gravure and Inkjet Printing. *ACS Appl Mater

35 Interfaces* **2016**, *8* (41), 27900–27910. <https://doi.org/10.1021/acsami.6b06838>.

36 (23) Schießl, S. P.; Fröhlich, N.; Held, M.; Gannott, F.; Schweiger, M.; Forster, M.; Scherf, U.;

37 Zaumseil, J. Polymer-Sorted Semiconducting Carbon Nanotube Networks for High-

38 Performance Ambipolar Field-Effect Transistors. *ACS Appl Mater Interfaces* **2015**, *7* (1),

39 682–689. <https://doi.org/10.1021/am506971b>.

1 (24) Miyata, Y.; Shiozawa, K.; Asada, Y.; Ohno, Y.; Kitaura, R.; Mizutani, T.; Shinohara, H.

2 Length-Sorted Semiconducting Carbon Nanotubes for High-Mobility Thin Film

3 Transistors. *Nano Res* **2011**, *4* (10), 963–970. <https://doi.org/10.1007/s12274-011-0152-7>.

4 (25) Cao, C.; Andrews, J. B.; Franklin, A. D. Completely Printed, Flexible, Stable, and

5 Hysteresis-Free Carbon Nanotube Thin-Film Transistors via Aerosol Jet Printing. *Adv

6 Electron Mater* **2017**, *3* (5), 1–10. <https://doi.org/10.1002/aelm.201700057>.

7 (26) Lee, H. W.; Yoon, Y.; Park, S.; Oh, J. H.; Hong, S.; Liyanage, L. S.; Wang, H.; Morishita,

8 S.; Patil, N.; Park, Y. J.; Park, J. J.; Spakowitz, A.; Galli, G.; Gygi, F.; Wong, P. H. S.;

9 Tok, J. B. H.; Kim, J. M.; Bao, Z. Selective Dispersion of High Purity Semiconducting

10 Single-Walled Carbon Nanotubes with Regioregular Poly(3-Alkylthiophene)s. *Nat

11 Commun* **2011**, *2* (1). <https://doi.org/10.1038/ncomms1545>.

12 (27) Molina-Lopez, F.; Gao, T. Z.; Kraft, U.; Zhu, C.; Öhlund, T.; Pfattner, R.; Feig, V. R.;

13 Kim, Y.; Wang, S.; Yun, Y.; Bao, Z. Inkjet-Printed Stretchable and Low Voltage Synaptic

14 Transistor Array. *Nat Commun* **2019**, *10* (1). <https://doi.org/10.1038/s41467-019-10569-3>.

15 (28) White, M. S.; Kaltenbrunner, M.; Głowacki, E. D.; Gutnichenko, K.; Kettlgruber, G.; Graz,

16 I.; Aazou, S.; Ulbricht, C.; Egbe, D. A. M.; Miron, M. C.; Major, Z.; Scharber, M. C.;

17 Sekitani, T.; Someya, T.; Bauer, S.; Sariciftci, N. S. Ultrathin, Highly Flexible and

18 Stretchable PLEDs. *Nat Photonics* **2013**, *7* (10), 811–816.

19 <https://doi.org/10.1038/nphoton.2013.188>.

20 (29) Gupta, M.; Gleason, K. K. Initiated Chemical Vapor Deposition of Poly(1H,1H,2H,2H-

21 Perfluorodecyl Acrylate) Thin Films. *Langmuir* **2006**, *22* (24), 10047–10052.

22 <https://doi.org/10.1021/la061904m>.

23 (30) Sojoudi, H.; Kim, S.; Zhao, H.; Annavarapu, R. K.; Mariappan, D.; Hart, A. J.; McKinley,

24 G. H.; Gleason, K. K. Stable Wettability Control of Nanoporous Microstructures by ICVD

25 Coating of Carbon Nanotubes. *ACS Appl Mater Interfaces* **2017**, *9* (49).

26 <https://doi.org/10.1021/acsami.7b13713>.

27

**Figure 1. SWCNT transistors with electrodes printed using nanoporous stamps. A)** Schematic of the device and top-view microscope image of the CNT-based printing stamp showing the channel geometry defined by the source and drain electrodes. B) SEM images of the stamp, showing the top and sidewall surfaces; channel has 10  $\mu\text{m}$  length, defined by gap between stamp islands. C) Device fabrication steps showing i) p-doped silicon gate electrode with thermally grown silicon dioxide ii) printing of Ag nanoparticle ink to define source and drain electrodes, followed by iii) annealing to sinter the nanoparticles, and then iv) deposition of the semiconducting CNT solution which forms a thin film by spin-coating.

**Figure 2. Analysis of sintering of printed Ag nanoparticle inks to conductive electrodes.** (A) Schematic of transformation of thin ink film to continuous conductive layer after solvent evaporation and sintering. (B) Optical microscope and SEM images of printed source and drain electrodes. (C) Cross-sectional profiles of printed Ag ink lines before annealing having thicknesses 185.5 nm, 109.5 nm, and 52.6 nm. (D) Comparison of Ag film morphology after annealing at 200, 300, 400, 500 °C for 10 minutes. (E) Comparison of Ag film morphology after annealing at 300 °C for 10 minutes, for corresponding as-printed ink thicknesses. (F) IV characteristics of the source and drain electrodes exhibiting conductivity of ~70% of bulk silver after appropriate annealing. (G) Resistance of printed electrodes according to printed layer thickness and annealing temperature (times fixed to 10 minutes).

**Figure 3. Characteristics of SWCNT transistors fabricated using sintered Ag electrodes.**

(A) SEM images of spincoated SWCNT film on top of Ag electrodes. (B) transfer characteristics of the transistor (channel length 7 μm) for drain voltages varying from -10V to -1V. (C) Mobility and (D) on-off ratio according to the channel length of the transistors reported in this work, and comparison with other previous SWCNT-based transistors.