pubs.acs.org/NanoLett Letter

# Graphene-Based Artificial Dendrites for Bio-Inspired Learning in Spiking Neuromorphic Systems

Samuel Liu, Deji Akinwande, Dmitry Kireev, and Jean Anne C. Incorvia\*

Cite This: https://doi.org/10.1021/acs.nanolett.4c00739

**Read Online**

ACCESS I

III Metrics & More

SI Supporting Information

ABSTRACT: Analog neuromorphic computing systems emulate the parallelism and connectivity of the human brain, promising greater expressivity and energy efficiency compared to those of digital systems. Though many devices have emerged as candidates for artificial neurons and artificial synapses, there have been few device candidates for artificial dendrites. In this work, we report on biocompatible graphene-based artificial dendrites (GrADs) that can implement dendritic processing. By using a dual side-gate configuration, current applied through a Nafion membrane can be used to control device conductance across a trilayer graphene channel, showing spatiotemporal responses of leaky recurrent, alpha, and Gaussian dendritic potentials. The devices can be variably connected to enable higher-order neuronal responses, and we show through data-driven spiking neural network simulations that spiking activity is reduced by ≤15% without accuracy loss while low-frequency operation is stabilized. This positions the GrADs as strong candidates for energy efficient bio-interfaced spiking neural networks.

KEYWORDS: transistor, 2D materials, graphene, biohybrid, neuromorphic computing, spiking neural network

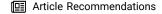

rtificial neural networks (ANNs) are rapidly proliferating A retificial neural networks (22,212), many first of data that as a useful tool for processing large amounts of data that cannot easily be analyzed with other methods. 1,2 However, due to the separation of computing and memory in von Neumann architecture, the speed and energy demands of state-of-the-art ANNs require new devices and architectures for further development.<sup>3,4</sup> Neuromorphic computing draws inspiration from the brain, combining artificial neurons and synapses to implement ANNs in hardware.<sup>5-8</sup> Spiking neural networks (SNNs) process information in time- and location-dependent spikes for biomimetic computation.6 The requirements for ANN and SNN devices depend on their intended use, e.g., CMOS-compatible devices for state-of-the-art electronics and biocompatible devices for use in health. Many devices have been proposed for building these systems; 9-25 however, only a subset meets the performance requirements, 26-29 few are biocompatible,<sup>30–33<sup>1</sup></sup> and fewer leverage advanced biological behavior such as that of dendrites.<sup>34–36</sup> In biological systems, dendrites branch out from the neuronal body and process incoming spikes into nonspiking spatiotemporal signals. For example, the leaky integrate-and-fire model of neuronal behavior is composed of one leaky recurrent dendrite and a soma for an activation threshold. Each neuron can have multiple sets of dendrites independently processing incoming spikes, allowing neuronal configurations such as the multipolar neuron shown in the left panel of Figure 1a.<sup>37</sup> Figure 1b shows leaky recurrent, alpha, and Gaussian waveform responses that are commonly observed in biological dendrites as stated in ref 34. These dendritic responses are useful in implementing spiking systems if the dendrites are processing spike

information that occurs near the order of magnitude of the time constant of the waveform.<sup>38</sup> We can use these waveform responses as a baseline to model dendritic behavior, while noting that the actual response of an artificial dendrite does not need to match exactly. Previous work on analog neuromorphic devices for artificial dendrites has focused on using CMOS, requiring circuit overhead when designing a neuronal configuration with multiple dendrites. 36,39 Other works have proposed the use of emerging memories as artificial dendrites. For example, PEDOT has been shown to electropolymerize and form synaptic connections between dendritic branches that can be controlled through unsupervised learning methods, though the potentiation of the dendritic branches was not characterized. 40 Silicon nanowire, 41 ionic nanomemristor, 42 and starch-based transistor<sup>43</sup> artificial synapses have been shown to benefit from the dendrite-like physical dynamics of the ion-gated devices. Another work has proposed a volatile memristor with simulation results showing that dendrite-like behavior provides performance enhancement in nonspiking neural networks.<sup>44</sup> The same group showed a combination of two different memristors to represent both dendrite and soma functionality.<sup>45</sup> See Table S1 for a comparison of our work to

Received: February 28, 2024 Revised: May 27, 2024 Accepted: May 28, 2024

Figure 1. GrAD design and single-gate operation. (a) Diagram of a neuron depicting three dendritic branches (purple), each of which is implemented by a GrAD (left). Picture of a mGrAD along with a diagram of the GrAD structure (middle), where the dynamics are controlled using the input gate and tuning gate and readout is through the voltage applied across the graphene channel (purple) through terminals D and S. The Nafion-117 gating material is colored light blue, and Au contacts are colored gold. Circuit schematic symbol of the GrAD (right). (b) Leaky recurrent, alpha, and Gaussian dendritic kernel waveforms commonly recorded in biological dendrites. (c) Transfer characteristics of a  $\mu$ GrAD with two forward and backward sweeps of -1 to 1 V. The D–S current is colored blue, and the InG–S current is colored red. (d) Single-gate current operation of a  $\mu$ GrAD showing synaptic characteristics.

previous works. These works indicate that an artificial dendrite device candidate tailored for SNNs could greatly enhance the functionality of analog neuromorphic systems.

In this work, we emulate dendrite dynamics by designing and measuring a graphene-based artificial dendrite (GrAD) for use in biocompatible neuromorphic computing, and we show the device can aid in processing low-spiking activity data. We have previously shown that transistors formed using biocompatible materials, i.e., graphene as the channel material and Nafion-117 as an ionic gate, can be operated as artificial synapses for online learning. 46 In contrast with previous work, we have described the characteristics of GrADs with dendritic behaviors described by computational neuroscience. By designing dual-gate operation, we determine that fabricated macroscale GrADs (mGrADs) and microscale GrADs (µGrADs) can transform incoming spiking signals from the previous layer of neurons into three different dendritic spatiotemporal signals: leaky recurrent, alpha, and Gaussian. Using data-driven simulations, we show that dendrites can enhance SNNs by increasing stability when training at low energy and that they reduce energy dissipation by lowering overall spiking activity by 15% without accuracy loss.

The goal of this work is to emulate dendritic behavior in a single dendritic branch, as shown by the dashed-line box in Figure 1a. A diagram of the GrAD is shown in the middle panel of Figure 1a. Trilayer graphene functions as a channel material between the source (S) and drain (D) contacts, and Nafion-117 is used as a gate insulator. Trilayer graphene was chosen to maximize the yield of the fabricated devices. Two gates denoted as the input gate (IG) and tuning gate (TG) are placed to the sides of the channel underneath the Nafion, on the same layer as the S/D contacts to provide side gating. Current signals  $I_{\rm IG}$  and  $I_{\rm TG}$  control the conductance of the channel, which is read by applying a read voltage  $V_{\rm read}$  between

the D and grounded S terminals. For this work, two types of GrAD devices were fabricated: macroscale (mGrAD, ~50 mm<sup>2</sup>) and microscale ( $\mu$ GrAD, 40  $\mu$ m × 40  $\mu$ m). The  $\mu$ GrADs are fabricated using a wafer-scale method that results in an ~25% yield with large device-to-device variation, most likely due to the processing of the Nafion membrane. The same fabrication method without the incorporation of Nafion has been shown to result in yields of >90%,<sup>47</sup> indicating that a further optimization of the processing of Nafion can help realize large-scale integration. Figure 1c shows the transfer curve of a  $\mu$ GrAD operated as an electrolytic transistor, where the gate voltage is swept twice between -1 and 1 V at a ramp rate of 50 mV/s across the input gate and source, with a fixed drain voltage of 0.1 V. The transfer hysteresis indicates that there is a memory effect on the time scale of the ramp rate. Due to the size of the device and Nafion gating material, a high leakage current is observed, reaching 10 nA at an applied voltage of 1.0 V. When the GrAD is operated using current operation through the input gate with a floating tuning gate, the device shows artificial synapse characteristics (Figure 1d), where positive and negative pulse trains are applied for several cycles showing distinct synaptic weight levels, indicated by the stable conductance values after a pulse is applied. This longterm potentiation was analyzed in our previous work, facilitated by the shifting of the ionic distribution within the dry Nafion-117 membrane.46 Because the artificial dendrite presented in this work is fabricated using the same material system, the biocompatible artificial synapse shown in our previous work and the presented artificial dendrites can be combined as a monolithic analog system.

This material system and larger device sizing were chosen due to the possibility of application in bio-interfaces. The fabrication of the mGrADs detailed in Methods follows the tattoo-based fabrication of graphene electrodes in ref 48, where

Nano Letters pubs.acs.org/NanoLett Letter

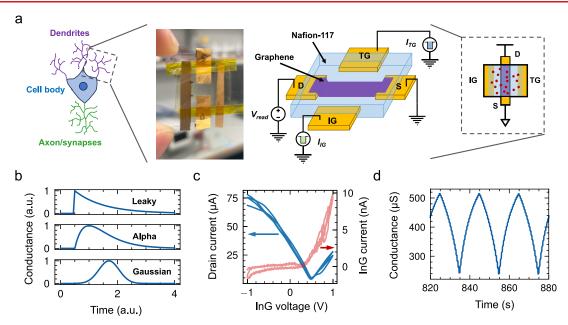

Figure 2. mGrAD time-dependent response. (a) Square current pulse applied to the input gate and constant current applied at the tuning gate that generate the leaky recurrent response. (b) Leaky recurrent mGrAD device response to the input pulse trains of varying frequency (blue for 1 Hz, green for 2 Hz, and orange for 5 Hz). The time taken to reach the threshold is denoted with the red dashed line. (c) Activation function of a leaky recurrent dendrite with a varying dc current applied to the tuning gate (blue triangles for 0 nA, green squares for 100 nA, and orange circles for 200 nA). (d) Triangular input current pulse applied with a constant current applied at the tuning gate that generates the alpha response. (e) Alpha mGrAD device response for varying  $I_{\rm IG}$  amplitudes (solid lines) compared to an ideal alpha kernel response (dotted lines). (f) Alpha and Gaussian waveform generation at varying  $I_{\rm IG}$  values (blue for 100 nA, green for 200 nA, orange for 300 nA, red for 400 nA, and purple for 500 nA).

the tattoos were used to monitor blood pressure in humans<sup>49</sup> and applied on heart tissue to diagnose and monitor cardiac arrhythmia.<sup>50</sup> Nafion has also been established as a biocompatible substrate and used for in vivo sensing coatings.<sup>51,52</sup> As shown in the middle panel of Figure 1a, the GrADs are transparent and flexible. The biocompatibility of the material system is a motivating factor for operating the devices in frequency ranges of biological neural systems, between 0.1 and 100 Hz.

First, three time-dependent waveforms, the leaky recurrent, alpha, and Gaussian kernels, are chosen from a set identified in ref 34 as target dendrite behaviors. To introduce conductance inhibition, a constant bias current,  $I_{TG}$ , is applied to the tuning gate, shown in Figure 2a. The spiking signals entering the dendrite are represented as square wave current pulses applied to the input gate to stimulate a leaky recurrent response. In Figure 2b,  $I_{\rm TG}$  is 100 nA and  $I_{\rm IG}$  is 1 ms long, with a -10  $\mu$ A amplitude, applied to a mGrAD at input frequencies of 1, 2, and 5 Hz. A threshold conductance is set at 1 mS to emulate the effect of a soma. A simple circuit implementation of the soma as well as a simulation demonstration is shown in Figure S1. We observed that the GrAD conductance integrates when  $I_{\rm IG}$  is on and leaks back to a lower conductance when  $I_{\rm IG}$  is off. By taking the inverse of thresholding times  $t_1-t_3$ , we can infer the output spiking frequency. The frequency-based activation function of the leaky recurrent model is in the form of a rectified linear unit (ReLU), where the slope of the ReLU function is mediated by the leak strength. This is reflected in mGrAD, where the output spiking frequency is further inhibited by an increase in  $I_{TG}$ , shown in Figure 2c. This

shows that GrADs can have LIF artificial neuron function and the response can be controlled using the tuning gate.

To emulate the other two dendrite responses, alpha and Gaussian, the input spikes are represented as triangular wave current pulses and  $I_{TG}$  is applied as in the previous case (depicted in Figure 2d). Figure 2e shows the resulting waveform for  $I_{IG}$  amplitudes of -1 to  $-4 \mu A$  with a halfmaximum pulse duration of 500 ms and an  $I_{\rm TG}$  of 200 nA. The GrAD response is qualitatively similar to the alpha function. There is an additional delay of 0.3 s between the start of the triangular pulse applied to the input gate and the beginning of the alpha waveform resulting from the device, which is the point at which the potentiating signal from the input gate overcomes the depressive signal at the tuning gate. We observed that as  $I_{IG}$  becomes larger, the deviation from an ideal alpha function also becomes larger. In particular, the locations of the conductance peak and a hump during the decay are the places with the largest deviation. However, when they are limited to small values, the waveforms match the alpha

The mGrAD can be tuned to show a Gaussian response by applying different  $I_{\rm TG}$  values. Figure 2f shows a series of five triangular pulses at the input gate applied with an amplitude of  $-1~\mu{\rm A}$  and a half-maximum duration of 500 ms (colored black).  $I_{\rm TG}$  values from 100 to 500 nA were applied, and the conductance of the channel was tracked. As  $I_{\rm TG}$  is increased, both time constant and conductance change decrease. Between 300 and 500 nA of bias, the output of the GrAD was measured to be symmetric, matching the shape of a Gaussian function over that of an alpha function. An analysis of the fit to

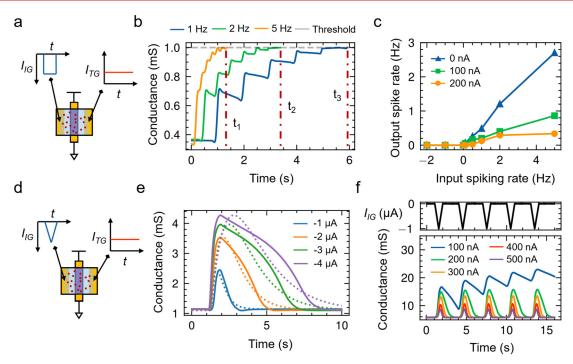

Figure 3. Multiple GrAD and  $\mu$ GrAD time-dependent responses. (a) Symbolic representation of a dendritic unit. (b) Circuit diagram of the dendritic unit. (c) Experimental output (blue) of a dendritic unit consisting of two dendrites with separate inputs (purple and red). (d) Optical microscope image of  $\mu$ GrAD dual side-gate device layout. (e) Alpha waveform generation at varying  $I_{\rm IG}$  values. (f) Alpha and Gaussian waveform generation at varying  $I_{\rm TG}$  values.

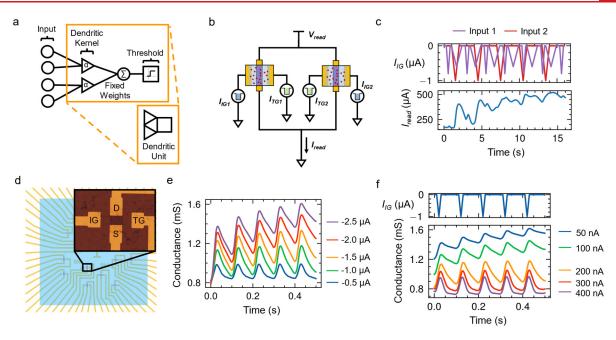

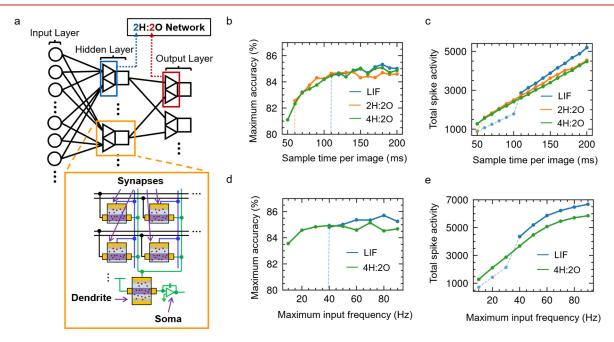

Figure 4. Dendritic spiking neural network simulations. (a) Symbolic representation of a dendritic multilayer perceptron. The circuit representation of the analog crossbar is shown in the inset. (b) Maximum accuracy after training for 20 epochs as a function of sample time per image. The drop-off settles at an accuracy of 10% below the indicated point. (c) Total spike activity of the network as a function of sample time per image. Faded coloring indicates accuracy of 10% for the corresponding sample time per image. (d) Maximum accuracy after training for 20 epochs as a function of the maximum input frequency. (e) Total spike activity of the network as a function of maximum input frequency.

characteristic equations of alpha and Gaussian responses is presented in section S.3 of the Supporting Information.

While mGrAD shows an emulation of dendritic kernels, the ability to combine separate branches of dendritic signals is necessary for implementation of bio-inspired neuron structure (shown in Figure 1a). Figure 3a depicts how GrADs can be connected to form a full dendritic unit, where the dendrite branch potentials are summed to describe the overall neuronal

potential. A demonstration of this dendritic unit was implemented using two parallel connected GrADs as shown in Figure 3b. Two different signals are applied to the input gates, while an  $I_{\rm TG}$  of 200 nA was applied to both tuning gates. Figure 3c shows the two input signals in purple and red in the top panel. The input signals consist of triangular wave inputs of varying amplitude and duration, where each triangular wave peak can be considered as a spike from the previous layer of

Nano Letters pubs.acs.org/NanoLett Letter

neurons. As shown, the alpha response can be generalized to triangular wave inputs. The resulting waveform shown in the bottom panel is the combined output current of the two mGrADs that represents the effective membrane potential of the dendritic unit. The results demonstrate that multiple GrADs can be flexibly connected to implement the desired dendritic unit configuration.

To demonstrate the potential for large-scale implementation of dendritic devices,  $\mu$ GrADs, shown in Figure 3d, were fabricated. The same dendrite characterization performed previously for the mGrADs was applied to the  $\mu$ GrADs. Figure 3e shows the output waveform for repeated triangular pulses applied to the input gate with varying amplitudes between -0.5 and -2.5  $\mu A$  with a half-maximum pulse duration of 10 ms, with an  $I_{TG}$  of 200 nA. A low pass filter with a cutoff frequency of 25 Hz was used to eliminate noise introduced by the measurement setup. The unfiltered data can be found in Figure S3. The measured data from the  $\mu$ GrADs show behavior similar to that of the mGrAD device, where the change in conductance increased as the pulse amplitude increased. Additionally, smaller amplitude and shorter pulses were required to change the conductance of the device, indicating favorable scaling. Figure 3f shows that  $I_{TG}$  can tune the time constant of the dendritic response. While the  $I_{TG}$  for the  $\mu$ GrAD is similar in magnitude to that applied to the mGrAD, the results indicate that 50-fold faster operation of the device is enabled due to microscaling, along with a similar improvement in energy. A description of the energy calculation is provided in section S.5. The resulting 6.2  $\mu$ W of peak power dissipation for the  $\mu$ GrADs is ~1/58 compared to the peak power dissipation of a previous memristor-based device.

After the mGrADs and µGrADs were characterized, the experimental conductance response was used to simulate a SNN by representing the behavior using a model described in section S.6. Supervised learning was chosen as the application because it is the nearest-term application for analog accelerators due to high accuracy compared to that of training using unsupervised methods. It is important to note that dendritic behavior has been shown to have benefits when applied to bio-inspired learning algorithms shown in refs 35, 36, 39, and 40 and it is an important building block for biological systems. The Fashion-MNIST clothing article classification task was chosen as the benchmark. Training is simulated using custom modules in the Norse framework<sup>53</sup> based in PyTorch.<sup>54</sup> The network architecture used for this simulation is a multilayer perceptron with one 200-unit hidden layer, as shown in Figure 4a. The neurons in the hidden layer and output layer are replaced with dendritic units. Additionally, inspiration is drawn from an architecture devised in ref 44 that is explained as follows. For the X dendrites per unit in the hidden layer, the neurons of the input layer are split into X groups. Each group is then connected to their corresponding dendrite; e.g., neurons of the first group are connected to the first dendrite in each unit. The notation XH:YO describes the network configuration, where X and Y are the numbers of dendrites per dendritic unit in the hidden and output layers, respectively. The inset of Figure 4a shows the analog implementation of the network, where the synapses are represented using graphene/Nafion transistor devices. 46 The summed currents along the columns (green) then feed into the input gate of a GrAD. To evaluate the impact of the introduction of dendrites into an SNN, a baseline network consisting of ideal LIF neurons described in section S.6 was

evaluated alongside the dendritic networks. An additional baseline of a nonspiking network with the same parameters can be found in section S.7.

To characterize the learning performance, the sampling time per image and maximum input frequency are swept. Panels b and c of Figure 4 show the maximum accuracy after 20 epochs of two configurations of dendritic networks, 2H:2O and 4H:2O, respectively, compared to the LIF network for varying sampling times per image. The maximum input spiking frequency is fixed at 50 Hz. The maximum accuracy of the network is consistent among the different configurations. However, the LIF network and the 2H:2O network both have a point at which the network does not train and decreases to 10% accuracy, the equivalent of a random guess. This occurs at 100 ms for the LIF network and 50 ms for the 2H:2O network. The 4H:2O network can be trained for the full range of sampling time per image, indicating that performance for an optimal configuration of dendritic network can have enhanced stability with a shorter sampling time. Additionally, in Figure 4c, the spike number characterizes energy efficiency because the spiking activity within the network is directly correlated to energy dissipation. For the sampling time per image where the networks are successfully trained, the 4H:2O and 2H:2O networks have 15% and 9% average reduced spiking activity, respectively, compared to the LIF network, indicating that increased energy efficiency is another benefit of a dendritic network. A sweep of the maximum input frequency in panels d and e of Figure 4 yields similar observations. The LIF network fails to train when the maximum input frequency decreases below 40 Hz in contrast to the dendritic network, which successfully trained for all of the input frequencies that were evaluated. The accuracy drop occurs when the spikes of the previous layer of neurons no longer stimulate the last layer of neurons sufficiently to allow for accurate application of the error gradient. The failure of the LIF network to train at a lower input frequency and sampling time for the same time constant indicates that more careful design of the time constant is necessary for LIF neurons than for the alpha dendrites due to the more sustained tail that alpha dendrites have at the same time constant. A comparison of the two waveforms for the same input is shown in Figure S5. For the dendritic network, the spiking activity for frequencies that resulted in successful training was again 15% lower than the spiking activity for the LIF network, corroborating the previous result. Though this result is promising, each neuron had more than one dendrite, adding an area overhead to spike the activity reduction. The result of 15% lower spiking activity is also likely not optimized, and many other hyperparameters of the network can be adjusted to enhance the results, such as network size, connectivity, and spike encoding method.

In conclusion, we have demonstrated dendritic behavior in graphene/Nafion devices with a dual-gate structure at time scales compatible with biological signals. The device is biocompatible and heavily informed by dendritic behavior modeled in computational neuroscience, contrasting it with previous works. We have shown that there is a high degree of tunability of the time-dependent conductance signal, which can be used to represent how a dendrite responds in time to a train of spiking input signals. We show that microdevice scaling can increase the speed of operation and reduce the current requirements. Through neural network simulations driven by this experimental behavior, we show that SNNs can benefit greatly from a dendritic configuration, showing significantly

Nano Letters pubs.acs.org/NanoLett Letter

higher training stability at low power operation and lower spiking activity. Though the current devices operate independently, a possibility for integrating competitive behaviors between dendrites is to engineer devices with multiple side gates and channels underneath the same Nafion membrane. These characteristics make the GrAD a promising building block for networks bridging bioelectronics and neuromorphic computing.

# **■** METHODS

mGrAD Device Fabrication. The graphene was prepared by first mounting it on a piece of tattoo paper for transfer. Monolayer CVD grown on large-scale graphene on copper (Grolltex) was taped onto a silicon wafer and spin-coated with PMMA at a rate of 2500 rpm for 60 s, resulting in an ~200 nm thick layer. The sample was then hard-baked at 200 °C for 15-20 min. The copper was then etched away by placing the sample in 0.1 M ammonium persulfate. The PMMA/graphene film was then wet transferred onto temporary tattoo paper. The gate contacts were prepared by evaporating gold onto an EVA/PET film. The two gates were then placed in contact with a Nafion-117 preprocessed film and heated at 150 °C to adhere. Adhesive gold contacts were then attached to the Nafion-117 film to form the source and drain contacts and prepare for graphene transfer. The graphene tattoo paper was then soaked in deionized water and transferred once the edges began to delaminate, forming a channel across the Nafion.

$\mu$ GrAD Device Fabrication. CVD-grown graphene was prepared by spin-coating PMMA and etching away copper using the method described in the previous section. The graphene was then transferred onto Au/Cr (90 nm/10 nm thick) contacts patterned on a Si/SiO<sub>2</sub> wafer. The graphene channel was then patterned, and excess graphene was etched away using oxygen plasma. Photostructurable polyimide HD8820 was used in the last step to form the passivation. The devices were diced from the wafer, drop coated with a Nafion-117 solution (Sigma-Aldrich), and hard-baked at 150 °C.

**Device Measurement Setup.** The devices were measured using two high-precision source/measure units (Agilent 2902B). One of the SMUs was used to apply 0.1 V of the drain—source potential, while the gate was used in the current-pulsing mode with various pulse shapes to induce conductance changes. A third SMU was used to apply a small constant positive current to tune the dendritic behavior.

## ASSOCIATED CONTENT

# **Data Availability Statement**

The data that support the findings of this study are available from the corresponding author upon reasonable request. The code repository for the neural network simulations is available at https://github.com/liukts/graphene-dendrites/tree/main.

## **Solution** Supporting Information

The Supporting Information is available free of charge at https://pubs.acs.org/doi/10.1021/acs.nanolett.4c00739.

Comparison of ours to other proposed artificial dendrites, circuit implementation and demonstration of a soma, equations of alpha and Gaussian dendrites, plots of raw data, energy dissipation calculation, dendritic response simulated in Norse details, leaky integrate-and-fire network configuration, and training performance of a nonspiking deep neural network (PDF)

#### AUTHOR INFORMATION

#### **Corresponding Author**

Jean Anne C. Incorvia — Chandra Family Department of Electrical and Computer Engineering, The University of Texas at Austin, Austin, Texas 78712, United States; Microelectronics Research Center, The University of Texas at Austin, Austin, Texas 78758, United States; orcid.org/0000-0002-4805-2112; Email: incorvia@austin.utexas.edu

#### **Authors**

Samuel Liu — Chandra Family Department of Electrical and Computer Engineering, The University of Texas at Austin, Austin, Texas 78712, United States; Microelectronics Research Center, The University of Texas at Austin, Austin, Texas 78758, United States; orcid.org/0000-0002-1864-5734

Deji Akinwande — Chandra Family Department of Electrical and Computer Engineering, The University of Texas at Austin, Austin, Texas 78712, United States; Microelectronics Research Center, The University of Texas at Austin, Austin, Texas 78758, United States; ⊚ orcid.org/0000-0001-7133-5586

Dmitry Kireev — Chandra Family Department of Electrical and Computer Engineering, The University of Texas at Austin, Austin, Texas 78712, United States; Microelectronics Research Center, The University of Texas at Austin, Austin, Texas 78758, United States; Department of Biomedical Engineering, University of Massachusetts Amherst, Amherst, Massachusetts 01003, United States; Orcid.org/0000-0003-1499-5435

Complete contact information is available at: https://pubs.acs.org/10.1021/acs.nanolett.4c00739

#### **Author Contributions**

S.L. and D.K. designed the experiments. S.L. and D.K. fabricated the devices. S.L. performed the data analysis and simulations. S.L. and J.A.C.I. wrote the manuscript. D.A. supervised the research. J.A.C.I. led the project. All authors proofed and approved the final version of the manuscript.

#### Notes

The authors declare no competing financial interest.

#### ACKNOWLEDGMENTS

This research is partially supported by the National Science Foundation Graduate Research Fellowship under Grant 2021311125 and partially supported by the National Science Foundation under CCF award 2246855. The fabrication work was done at the Texas Nanofabrication Facility supported by NSF Grant No. NNCI-1542159.

#### REFERENCES

- (1) Hopfield, J. J. Artificial Neural Networks. *IEEE Circuits and Devices Magazine* **1988**, *4* (5), 3–10.

- (2) Krogh, A. What Are Artificial Neural Networks? *Nat. Biotechnol.* **2008**, 26 (2), 195–197.

- (3) Wulf, Wm. A.; McKee, S. A. Hitting the Memory Wall. ACM SIGARCH Computer Architecture News 1995, 23 (1), 20–24.

- (4) Angizi, S.; He, Z.; Reis, D.; Hu, X. S.; Tsai, W.; Lin, S. J.; Fan, D. Accelerating Deep Neural Networks in Processing-in-Memory Platforms: Analog or Digital Approach? In 2019 IEEE Computer Society Annual Symposium on VLSI (ISVLSI); IEEE, 2019; pp 197–202. DOI: 10.1109/ISVLSI.2019.00044

- (5) Schuman, C. D.; Kulkarni, S. R.; Parsa, M.; Mitchell, J. P.; Date, P.; Kay, B. Opportunities for Neuromorphic Computing Algorithms and Applications. *Nat. Comput. Sci.* **2022**, *2* (1), 10–19.

- (6) Roy, K.; Jaiswal, A.; Panda, P. Towards Spike-Based Machine Intelligence with Neuromorphic Computing. *Nature* **2019**, *575* (7784), 607–617.

- (7) Marković, D.; Mizrahi, A.; Querlioz, D.; Grollier, J. Physics for Neuromorphic Computing. *Nat. Rev. Phys.* **2020**, 2 (9), 499–510.

- (8) Burr, G. W.; Shelby, R. M.; Sebastian, A.; Kim, S.; Kim, S.; Sidler, S.; Virwani, K.; Ishii, M.; Narayanan, P.; Fumarola, A.; Sanches, L. L.; Boybat, I.; Le Gallo, M.; Moon, K.; Woo, J.; Hwang, H.; Leblebici, Y. Neuromorphic Computing Using Non-Volatile Memory. *Adv. Phys. X* **2017**, *2* (1), 89–124.

- (9) La Barbera, S.; Ly, D. R. B.; Navarro, G.; Castellani, N.; Cueto, O.; Bourgeois, G.; De Salvo, B.; Nowak, E.; Querlioz, D.; Vianello, E. Narrow Heater Bottom Electrode-Based Phase Change Memory as a Bidirectional Artificial Synapse. *Adv. Electron. Mater.* **2018**, 4 (9), 1800223.

- (10) Wong, H. S. P.; Raoux, S.; Kim, S.; Liang, J.; Reifenberg, J. P.; Rajendran, B.; Asheghi, M.; Goodson, K. E. Phase Change Memory. *Proc. IEEE* **2010**, 98 (12), 2201–2227.

- (11) Kumar, S.; Wang, X.; Strachan, J. P.; Yang, Y.; Lu, W. D. Dynamical Memristors for Higher-Complexity Neuromorphic Computing. *Nat. Rev. Mater.* **2022**, *7* (7), 575–591.

- (12) Wang, M.; Cai, S.; Pan, C.; Wang, C.; Lian, X.; Zhuo, Y.; Xu, K.; Cao, T.; Pan, X.; Wang, B.; Liang, S.-J.; Yang, J. J.; Wang, P.; Miao, F. Robust Memristors Based on Layered Two-Dimensional Materials. *Nat. Electron.* **2018**, *1* (2), 130–136.

- (13) Milo, V.; Malavena, G.; Monzio Compagnoni, C.; Ielmini, D. Memristive and CMOS Devices for Neuromorphic Computing. *Materials* **2020**, *13* (1), 166.

- (14) Zhou, G.; Wang, Z.; Sun, B.; Zhou, F.; Sun, L.; Zhao, H.; Hu, X.; Peng, X.; Yan, J.; Wang, H.; Wang, W.; Li, J.; Yan, B.; Kuang, D.; Wang, Y.; Wang, L.; Duan, S. Volatile and Nonvolatile Memristive Devices for Neuromorphic Computing. *Adv. Electron. Mater.* **2022**, *8*, No. 2101127.

- (15) Siddiqui, S. A.; Dutta, S.; Tang, A.; Liu, L.; Ross, C. A.; Baldo, M. A. Magnetic Domain Wall Based Synaptic and Activation Function Generator for Neuromorphic Accelerators. *Nano Lett.* **2020**, *20* (2), 1033–1040.

- (16) Grollier, J.; Querlioz, D.; Camsari, K. Y.; Everschor-Sitte, K.; Fukami, S.; Stiles, M. D. Neuromorphic Spintronics. *Nat. Electron.* **2020**, 3 (7), 360–370.

- (17) Jung, S.; Lee, H.; Myung, S.; Kim, H.; Yoon, S. K.; Kwon, S.-W.; Ju, Y.; Kim, M.; Yi, W.; Han, S.; Kwon, B.; Seo, B.; Lee, K.; Koh, G.-H.; Lee, K.; Song, Y.; Choi, C.; Ham, D.; Kim, S. J. A Crossbar Array of Magnetoresistive Memory Devices for In-Memory Computing. *Nature* **2022**, 601 (7892), 211–216.

- (18) Leonard, T.; Liu, S.; Jin, H.; Incorvia, J. A. C. Stochastic Domain Wall-Magnetic Tunnel Junction Artificial Neurons for Noise-Resilient Spiking Neural Networks. *Appl. Phys. Lett.* **2023**, *122* (26), 262406.

- (19) Liu, S.; Xiao, T. P.; Kwon, J.; Debusschere, B. J.; Agarwal, S.; Incorvia, J. A. C.; Bennett, C. H. Bayesian Neural Networks Using Magnetic Tunnel Junction-Based Probabilistic in-Memory Computing. *Front. Nanotechnol.* **2022**, *4*, 1021943.

- (20) Leonard, T.; Liu, S.; Alamdar, M.; Jin, H.; Cui, C.; Akinola, O. G.; Xue, L.; Xiao, T. P.; Friedman, J. S.; Marinella, M. J.; Bennett, C. H.; Incorvia, J. A. C. Shape-Dependent Multi-Weight Magnetic Artificial Synapses for Neuromorphic Computing. *Adv. Electron. Mater.* **2022**, 8 (12), No. 2200563.

- (21) Hu, X.; Cui, C.; Liu, S.; Garcia-Sanchez, F.; Brigner, W. H.; Walker, B. W.; Edwards, A. J.; Xiao, T. P.; Bennett, C.; Hassan, N.; Frank, M. P.; Incorvia, J. A. C.; Friedman, J. Magnetic Skyrmions and Domain Walls for Logical and Neuromorphic Computing. *Neuromorphic Computing and Engineering* **2023**, *3*, 022003.

- (22) Gkoupidenis, P.; Schaefer, N.; Garlan, B.; Malliaras, G. G. Neuromorphic Functions in PEDOT:PSS Organic Electrochemical Transistors. *Adv. Mater.* **2015**, *27* (44), 7176–7180.

- (23) Melianas, A.; Quill, T. J.; LeCroy, G.; Tuchman, Y.; Loo, H. v.; Keene, S. T.; Giovannitti, A.; Lee, H. R.; Maria, I. P.; McCulloch, I.; Salleo, A. Temperature-Resilient Solid-State Organic Artificial Synapses for Neuromorphic Computing. *Sci. Adv.* **2020**, *6* (27), eabb2958.

- (24) van de Burgt, Y.; Lubberman, E.; Fuller, E. J.; Keene, S. T.; Faria, G. C.; Agarwal, S.; Marinella, M. J.; Alec Talin, A.; Salleo, A. A Non-Volatile Organic Electrochemical Device as a Low-Voltage Artificial Synapse for Neuromorphic Computing. *Nat. Mater.* **2017**, *16* (4), 414–418.

- (25) Huang, H.; Yang, R.; Tan, Z.; He, H.; Zhou, W.; Xiong, J.; Guo, X. Quasi-Hodgkin—Huxley Neurons with Leaky Integrate-and-Fire Functions Physically Realized with Memristive Devices. *Adv. Mater.* **2019**, *31* (3), No. 1803849.

- (26) Sun, X.; Yu, S. Impact of Non-Ideal Characteristics of Resistive Synaptic Devices on Implementing Convolutional Neural Networks. *IEEE Journal of Emerging Select Top Circuits and Systems* **2019**, 9 (3), 570–579.

- (27) Agarwal, S.; Plimpton, S. J.; Hughart, D. R.; Hsia, A. H.; Richter, I.; Cox, J. A.; James, C. D.; Marinella, M. J. Resistive Memory Device Requirements for a Neural Algorithm Accelerator. In 2016 International Joint Conference on Neural Networks (IJCNN); IEEE, 2016; pp 929–938. DOI: 10.1109/IJCNN.2016.7727298

- (28) Xiao, T. P.; Bennett, C. H.; Feinberg, B.; Agarwal, S.; Marinella, M. J. Analog Architectures for Neural Network Acceleration Based on Non-Volatile Memory. *Appl. Phys. Rev.* **2020**, *7* (3), 031301.

- (29) Xiao, T. P.; Feinberg, B.; Bennett, C. H.; Prabhakar, V.; Saxena, P.; Agrawal, V.; Agarwal, S.; Marinella, M. J. On the Accuracy of Analog Neural Network Inference Accelerators. *IEEE Circuits and Systems Magazine* **2022**, *22* (4), 26–48.

- (30) Keene, S. T.; Lubrano, C.; Kazemzadeh, S.; Melianas, A.; Tuchman, Y.; Polino, G.; Scognamiglio, P.; Cinà, L.; Salleo, A.; van de Burgt, Y.; Santoro, F. A Biohybrid Synapse with Neurotransmitter-Mediated Plasticity. *Nat. Mater.* **2020**, *19* (9), 969–973.

- (31) Kim, Y.; Park, C. H.; An, J. S.; Choi, S.-H.; Kim, T. W. Biocompatible Artificial Synapses Based on a Zein Active Layer Obtained from Maize for Neuromorphic Computing. *Sci. Rep.* **2021**, *11* (1), No. 20633.

- (32) Park, H.; Lee, Y.; Kim, N.; Seo, D.; Go, G.; Lee, T. Flexible Neuromorphic Electronics for Computing, Soft Robotics, and Neuroprosthetics. *Adv. Mater.* **2020**, 32 (15), e1903558.

- (33) Robinson, D. A.; Foster, M. E.; Bennett, C. H.; Bhandarkar, A.; Webster, E. R.; Celebi, A.; Celebi, N.; Fuller, E. J.; Stavila, V.; Spataru, C. D.; Ashby, D. S.; Marinella, M. J.; Krishnakumar, R.; Allendorf, M. D.; Talin, A. A. Tunable Intervalence Charge Transfer in Ruthenium Prussian Blue Analog Enables Stable and Efficient Biocompatible Artificial Synapses. *Adv. Mater.* **2023**, *35* (37), e2207595.

- (34) Tapson, J. C.; Cohen, G. K.; Afshar, S.; Stiefel, K. M.; Buskila, Y.; Wang, R. M.; Hamilton, T. J.; van Schaik, A. Synthesis of Neural Networks for Spatio-Temporal Spike Pattern Recognition and Processing. *Front. Neurosci.* **2013**, *7*, 153.

- (35) Yang, S.; Gao, T.; Wang, J.; Deng, B.; Lansdell, B.; Linares-Barranco, B. Efficient Spike-Driven Learning With Dendritic Event-Based Processing. *Front. Neurosci.* **2021**, *15*, 601109.

- (36) Kaiser, J.; Billaudelle, S.; Müller, E.; Tetzlaff, C.; Schemmel, J.; Schmitt, S. Emulating Dendritic Computing Paradigms on Analog Neuromorphic Hardware. *Neuroscience* **2022**, 489, 290–300.

- (37) Stuart, G.; Spruston, N.; Häusser, M. Dendrites, 3rd ed.; Oxford University Press, 2016.

- (38) Maass, W.; Sontag, E. D. Neural Systems as Nonlinear Filters. *Neural Computing* **2000**, *12* (8), 1743–1772.

- (39) Cardwell, S. G.; Chance, F. S. Dendritic Computation for Neuromorphic Applications. In *Proceedings of the 2023 International Conference on Neuromorphic Systems*; ACM: New York, 2023; pp 1–5. (40) Janzakova, K.; Balafrej, I.; Kumar, A.; Garg, N.; Scholaert, C.; Rouat, J.; Drouin, D.; Coffinier, Y.; Pecqueur, S.; Alibart, F. Structural Plasticity for Neuromorphic Networks with Electropolymerized

Dendritic PEDOT Connections. Nat. Commun. 2023, 14 (1), 8143.

- (41) Li, X.; Yu, B.; Wang, B.; Bao, L.; Zhang, B.; Li, H.; Yu, Z.; Zhang, T.; Yang, Y.; Huang, R.; Wu, Y.; Li, M. Multi-Terminal Ionic-Gated Low-Power Silicon Nanowire Synaptic Transistors with Dendritic Functions for Neuromorphic Systems. *Nanoscale* **2020**, *12* (30), 16348–16358.

- (42) Meng, J.; Song, J.; Fang, Y.; Wang, T.; Zhu, H.; Ji, L.; Sun, Q.-Q.; Zhang, D. W.; Chen, L. Ionic Diffusive Nanomemristors with Dendritic Competition and Cooperation Functions for Ultralow Voltage Neuromorphic Computing. *ACS Nano* **2024**, *18* (12), 9150–9159.

- (43) Gao, W. T.; Zhu, L. Q.; Tao, J.; Wan, D. Y.; Xiao, H.; Yu, F. Dendrite Integration Mimicked on Starch-Based Electrolyte-Gated Oxide Dendrite Transistors. ACS Appl. Mater. Interfaces 2018, 10 (46), 40008–40013.

- (44) Li, X.; Tang, J.; Zhang, Q.; Gao, B.; Yang, J. J.; Song, S.; Wu, W.; Zhang, W.; Yao, P.; Deng, N.; Deng, L.; Xie, Y.; Qian, H.; Wu, H. Power-Efficient Neural Network with Artificial Dendrites. *Nat. Nanotechnol.* **2020**, *15* (9), 776–782.

- (45) Li, X.; Zhong, Y.; Chen, H.; Tang, J.; Zheng, X.; Sun, W.; Li, Y.; Wu, D.; Gao, B.; Hu, X.; Qian, H.; Wu, H. A Memristors-Based Dendritic Neuron for High-Efficiency Spatial-Temporal Information Processing. *Adv. Mater.* **2023**, *35* (37), e2203684.

- (46) Kireev, D.; Liu, S.; Jin, H.; Patrick Xiao, T.; Bennett, C. H.; Akinwande, D.; Incorvia, J. A. C. Metaplastic and Energy-Efficient Biocompatible Graphene Artificial Synaptic Transistors for Enhanced Accuracy Neuromorphic Computing. *Nat. Commun.* **2022**, *13* (1), 4386.

- (47) Kireev, D.; Brambach, M.; Seyock, S.; Maybeck, V.; Fu, W.; Wolfrum, B.; Offenhäusser, A. Graphene Transistors for Interfacing with Cells: Towards a Deeper Understanding of Liquid Gating and Sensitivity. *Sci. Rep.* **2017**, *7* (1), 6658.

- (48) Kireev, D.; Ameri, S. K.; Nederveld, A.; Kampfe, J.; Jang, H.; Lu, N.; Akinwande, D. Fabrication, Characterization and Applications of Graphene Electronic Tattoos. *Nat. Protoc.* **2021**, *16* (5), 2395–2417.

- (49) Kireev, D.; Sel, K.; Ibrahim, B.; Kumar, N.; Akbari, A.; Jafari, R.; Akinwande, D. Continuous Cuffless Monitoring of Arterial Blood Pressure via Graphene Bioimpedance Tattoos. *Nat. Nanotechnol.* **2022**, *17* (8), 864–870.

- (50) Lin, Z.; Kireev, D.; Liu, N.; Gupta, S.; LaPiano, J.; Obaid, S. N.; Chen, Z.; Akinwande, D.; Efimov, I. R. Graphene Biointerface for Cardiac Arrhythmia Diagnosis and Treatment. *Adv. Mater.* **2023**, 35 (22), e2212190.

- (51) Kim, G.; Kim, H.; Kim, I. J.; Kim, J. R.; Lee, J. I.; Ree, M. Bacterial Adhesion, Cell Adhesion and Biocompatibility of Nafion Films. *J. Biomater. Sci., Polym. Ed.* **2009**, 20 (12), 1687–1707.

- (52) Liu, B.-J.; Ma, L.-N.; Su, J.; Jing, W.-W.; Wei, M.-J.; Sha, X.-Z. Biocompatibility Assessment of Porous Chitosan-Nafion and Chitosan-PTFE Composites in Vivo. J. Biomed. Mater. Res., Part A 2014, 102 (6), 2055–2060.

- (53) Pehle, C.; Pedersen, J. E. Norse A Deep Learning Library for Spiking Neural Networks. Zenodo, January 2021. DOI: 10.5281/zenodo.4422025

- (54) Paszke, A.; Gross, S.; Massa, F.; Lerer, A.; Bradbury, J.; Chanan, G.; Killeen, T.; Lin, Z.; Gimelshein, N.; Antiga, L.; Desmaison, A.; Kopf, A.; Yang, E.; DeVito, Z.; Raison, M.; Tejani, A.; Chilamkurthy, S.; Steiner, B.; Fang, L.; Bai, J.; Chintala, S. PyTorch: An Imperative Style, High-Performance Deep Learning Library. In *Advances in Neural Information Processing Systems*; Wallach, H., Larochelle, H., Beygelzimer, A., d Alché-Buc, F., Fox, E., Garnett, R., Eds.; Curran Associates, Inc., 2019; Vol. 32.