# Programmable Retention Characteristics in MoS<sub>2</sub>-Based Atomristors for Neuromorphic and Reservoir Computing Systems

Yoonseok Lee, Yifu Huang, Yao-Feng Chang, Sung Jin Yang, Nicholas D. Ignacio, Shanmukh Kutagulla, Sivasakthya Mohan, Sunghun Kim, Jungwoo Lee, Deji Akinwande,\* and Sungjun Kim\*

Cite This: *ACS Nano* 2024, 18, 14327–14338

Read Online

ACCESS |

Metrics & More

Article Recommendations

Supporting Information

**ABSTRACT:** In this study, we investigate the coexistence of short- and long-term memory effects owing to the programmable retention characteristics of a two-dimensional Au/MoS<sub>2</sub>/Au atomristor device and determine the impact of these effects on synaptic properties. This device is constructed using bilayer MoS<sub>2</sub> in a crossbar structure. The presence of both short- and long-term memory characteristics is proposed by using a filament model within the bilayer transition-metal dichalcogenide. Short- and long-term properties are validated based on programmable multilevel retention tests. Moreover, we confirm various synaptic characteristics of the device, demonstrating its potential use as a synaptic device in a neuromorphic system. Excitatory postsynaptic current, paired-pulse facilitation, spike-rate-dependent plasticity, and spike-number-dependent plasticity synaptic applications are implemented by operating the device at a low-conductance level. Furthermore, long-term potentiation and depression exhibit symmetrical properties at high-conductance levels. Synaptic learning and forgetting characteristics are emulated using programmable retention properties and composite synaptic plasticity. The learning process of artificial neural networks is used to achieve high pattern recognition accuracy, thereby demonstrating the suitability of the use of the device in a neuromorphic system. Finally, the device is used as a physical reservoir with time-dependent inputs to realize reservoir computing by using short-term memory properties. Our study reveals that the proposed device can be applied in artificial intelligence-based computing applications by utilizing its programmable retention properties.

**KEYWORDS:** programmable retention, atomristor, molybdenum disulfide, neuromorphic system, reservoir computing, resistive switching

## INTRODUCTION

Present artificial intelligence and big data applications require substantial computational power, thus leading to the need for high efficiencies and high-performance processing abilities.<sup>1–4</sup> The traditional complementary metal-oxide semiconductor (CMOS)-based von Neumann architecture has reached the limit of data-processing speed between the central processing unit and the memory; further advances are required to improve the fundamental computing structure to overcome this challenge. Neuromorphic computing, which emulates neuronal and synaptic functions in the brain, is currently gaining attention owing to its efficient data-processing capabilities and mechanisms. Resistive random access memory (RRAM) and ferroelectric, phase-change, and spin-transfer torque magnetic random access memories are examples of memristors with resistive switching, high parallel-processing performance, and

energy-efficient characteristics suitable for neuromorphic computing.<sup>5–14</sup>

Among them, RRAM is one of the most promising candidates for application in neuromorphic computing owing to its high scalability, low-power consumption, increased switching speed, and high-switching versatility. Various materials such as metal-oxide, organic, and two-dimensional (2D) are being investigated for applications in neuromorphic systems to emulate synaptic functions.<sup>15–21</sup> In particular, the conductive bridge random access memory (CBRAM), a type

Received: January 9, 2024

Revised: May 1, 2024

Accepted: May 8, 2024

Published: May 20, 2024

**Table 1. Comparison between 2D Memristors as Synaptic Devices**

| 2D layer                              | electrode pair    | operation voltage (V) | on/off ratio     | memory type | degradation issue <sup>a</sup> | synaptic property                                  | application <sup>b</sup>                                                     | refs      |

|---------------------------------------|-------------------|-----------------------|------------------|-------------|--------------------------------|----------------------------------------------------|------------------------------------------------------------------------------|-----------|

| h-BN                                  | Au/Au             | ±3                    | 10 <sup>7</sup>  | LTM         | X                              | potentiation                                       | neuromorphic with ANN                                                        | 21        |

| h-BN                                  | Ag/Ag             | ±0.6                  | 10 <sup>11</sup> | STM         | O                              | EPSC                                               |                                                                              | 21        |

| Bi <sub>2</sub> O <sub>2</sub> Se     | Au/Au             | 0.8–2                 | 10 <sup>3</sup>  | LTM         | X                              |                                                    |                                                                              | 49        |

| MoSe <sub>2</sub>                     | Ag/ITO            | 1–1.25                | 10 <sup>2</sup>  | LTM         | O                              |                                                    | flexible memristor                                                           | 50        |

| WS <sub>2</sub>                       | Al/Pt             | 1.5–1.8               | 10 <sup>3</sup>  | LTM         | X                              |                                                    |                                                                              | 51        |

| GeS                                   | Ag/Pt             | ±0.5                  | 10 <sup>8</sup>  | coexisted   | O                              | potentiation and depression                        |                                                                              | 24        |

| MoS <sub>2</sub>                      | Ag/Ag             | 0.2–0.35              | 10 <sup>7</sup>  | coexisted   | O                              | potentiation and depression, PPF                   | flexible memristor                                                           | 31        |

| PdSeO <sub>x</sub> /PdSe <sub>2</sub> | Ti/Au             | 0.7–0.92              | 10 <sup>2</sup>  | LTM         | X                              | potentiation and depression, PPF, EPSC             | neuromorphic with ANN                                                        | 52        |

| WSe <sub>2</sub>                      | Ag/Ag             | ±0.5                  | 10 <sup>2</sup>  | LTM         | O                              |                                                    | 1T-1R                                                                        | 53        |

| WSe <sub>2</sub>                      | Ag/Ag             | 3.5–4                 | 10 <sup>4</sup>  | LTM         | O                              | potentiation and depression, EPSC, PPF             |                                                                              | 43        |

| WSe <sub>x</sub> O <sub>y</sub>       | graphene/graphene | 1–2                   | 10 <sup>2</sup>  | LTM         | X                              | SNDP, EPSC, SRDP                                   | flexible memristor                                                           | 44        |

| PdSe <sub>2</sub>                     | Ti/Au             | 0.75–1.5              | 10 <sup>3</sup>  | LTM         | X                              | STDP, PPF, PPD, potentiation and depression, EPSC  | synaptic array memorization                                                  | 52        |

| WS <sub>2</sub>                       | Pd/Pt             | 0.3–0.8               | 10 <sup>3</sup>  | coexisted   | X                              | STDP, PPF, SRDP, EPSC,                             | flexible memristor                                                           | 46        |

| MoS <sub>2</sub>                      | Ag/Au             | 0.7–1                 | 10 <sup>3</sup>  | LTM         | O                              |                                                    |                                                                              | 47        |

| WSe <sub>2</sub>                      | Pt/Pt             | ±2                    | 10 <sup>3</sup>  | LTM         | X                              | potentiation and depression, EPSC, PPF             | learning simulation/neuromorphic with ANN                                    | 1         |

| MoS <sub>2</sub>                      | Pt/Ti             | ±1.5                  | 10 <sup>2</sup>  | LTM         | X                              | potentiation and depression                        | neuromorphic with CNN                                                        | 48        |

| MoS <sub>2</sub>                      | Au/Au             | 0.8–1.2               | 10 <sup>2</sup>  | coexisted   | X                              | potentiation and depression, PPF, EPSC, SNDP, SRDP | learning simulation/neuromorphic with ANN/4-bit reservoir computing with CNN | this work |

<sup>a</sup>Degradation possibility: active metal can affect memory performance degradation to the device by electrode oxidation and metal diffusion because of the active metal characteristics in the CBRAM. The inert metal can prevent the active metal degradation issue. Specifically, the term “High” means a greater degradation possibility due to metal oxidation and diffusion when active metals are present. Conversely, the term “Low” signifies a reduced degradation possibility observed in configurations without active metals, thus effectively preventing degradation possibility. <sup>b</sup>Application: neuromorphic as MNIST pattern recognition simulation and the reservoir as a physical reservoir.

of RRAM with a Ag or Cu electrode, has attracted attention owing to the capability of the CBRAM to implement synaptic functions via short- and long-term memory mechanisms based on active metal-ion transitions.<sup>22–25</sup> However, active metals have high reactivity and atomic mobility, thus causing diffusion through an insulator or oxidization. These problems result in device performance degradation; consequently, the active metal is not a fab-friendly material in the semiconductor industry.

This study demonstrates the potential of using short- and long-term memories (STM and LTM, respectively) by applying the Au-atom-relaxation phenomenon in bilayer transition-metal dichalcogenides (TMDs) using Au electrodes and 2D layers. This approach offers a solution to the degradation issues related to the CBRAM. In addition, 2D material-based memristors have a high potential for several applications owing to their high ON/OFF ratio, threshold switching characteristics with a low-compliance current, increased switching speed, ultralow power consumption (fJ per switching), and gigahertz operation.<sup>26–31</sup> In terms of scalability, the atomic-scale thickness of 2D materials enables their applications in a variety of structures, such as three-dimensional (3D) vertical or lateral channels, thus presenting the possibility of increasing device density.<sup>32–39</sup> Specifically, research using a 2D electrode edge contact selector has demonstrated the capability to reduce off currents, thus improving power consumption and highlighting the potential for advances in energy-efficient neuromorphic computing research.<sup>40,41</sup> Furthermore, recent 2D memristor studies

suggest the emulation of various synaptic properties and their suitability for neuromorphic computing as well as structural improvements. Table 1 lists the previous studies related to STM and LTM characteristics and synaptic properties of other 2D memristors.<sup>1,21,24,42–53</sup> Here, we demonstrate the coexistence of STM and LTM properties in MoS<sub>2</sub>-based atomristors. Based on this combined capability, we emulated various synaptic characteristics, performed composite learning simulations, and presented application methods for LTM and STM using neuromorphic and reservoir computing. Except for the case of the active metal-based CBRAM, which is associated with a degradation issue, the coexistence of STM and LTM characteristics has rarely been reported. Previous studies have proposed the atomristor as a memory based on the formation of filaments in bilayer TMDs and suggested optimization methods based on the deposition rate and the TMDs. This study analyzes the STM and LTM characteristics of the Au/MoS<sub>2</sub>/Au crossbar-structure atomristor by investigating the programmable retention behaviors and demonstrates the possibility of artificial synaptic applications. The stable Au filaments demonstrate both STM and LTM characteristics during the filament-formation process involving dissociation, diffusion, and adsorption.<sup>54,55</sup> The coexistence of STM and LTM is demonstrated using multilevel retention and decay analyses. Short-term synaptic plasticity (STP) is verified by paired-pulse facilitation (PPF), excitatory postsynaptic current (EPSC), spike-rate-dependent plasticity (SRDP), and spike-number-dependent plasticity (SNDP). Potentiation and depression synaptic function are used to

realize long-term synaptic plasticity (LTP). By emulating both LTP and STP synaptic properties, we simulate brain activity in terms of long-term and short-term memory modulation based on learning intensity. Finally, a 4-bit reservoir computing is implemented using STM characteristics and an accuracy test using the Modified National Institute of Standard and Technology (MNIST) data set is executed based on the measured results.

## RESULTS AND DISCUSSION

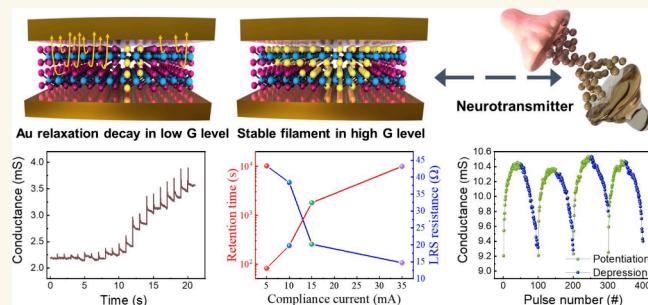

The 3D schematic of the Au/MoS<sub>2</sub>/Au device stack is shown in Figure 1a. The device features a metal–insulator–metal

**Figure 1.** (a) 3D schematic of the Au/MoS<sub>2</sub>/Au device with a crossbar structure. (b) Optical image of the device defining a  $1 \times 1 \mu\text{m}^2$  device area. (c) Raman spectrum analysis of the MoS<sub>2</sub> layer, indicating  $\text{E}^1_{2g}$  and  $\text{A}_{1g}$  peaks. (d)  $I$ – $V$  curve of the device between the LRS and HRS.

sandwich structure with a crossbar structure. Figure 1b presents an optical microscopy image of the device. Crossing metal electrodes define the device area, which is confined to a cell area of  $1 \times 1 \mu\text{m}^2$  in the crossbar structure. The bilayer MoS<sub>2</sub> film thickness (1.4 nm) was confirmed by atomic force microscopy (Figure S1).<sup>56</sup> Figure 1c depicts the Raman spectra with two main characteristic peaks,  $\text{E}^1_{2g}$  ( $380.8 \text{ cm}^{-1}$ ) and  $\text{A}_{1g}$  ( $401.5 \text{ cm}^{-1}$ ), and can be used for the quality analysis of the MoS<sub>2</sub> layer. These  $\text{E}^1_{2g}$  and  $\text{A}_{1g}$  peaks correspond to those in the Raman spectra reported in the literature.<sup>57</sup> Figure 1d represents the typical  $I$ – $V$  curve of the device in which the resistive switching changes between the low-resistance state (LRS) and high-resistance state (HRS). In the set process, a compliance current of 10 mA was used to prevent excessive breakdown owing to an overshoot phenomenon. Figure S2 showcases that when the set operation was continuously performed with increasing compliance current, the states could be clearly distinguished, and excessive breakdown was prevented. During the reset process, multilevel states can be achieved by increasing the voltage continuously (Figure S3). The conductance distributions of the LRS and HRS are presented in Figure S4 based on resistive switching from seven devices over 20 cycles. Figure S5 shows the direct current (DC) endurance over 150 cycles. Figure S6 illustrates the state transition of the device by the set and reset pulse switching processes. The current changes result from the formation and

rupture of the filaments while applying the programming pulses, thus demonstrating the feasibility of the device pulse control.

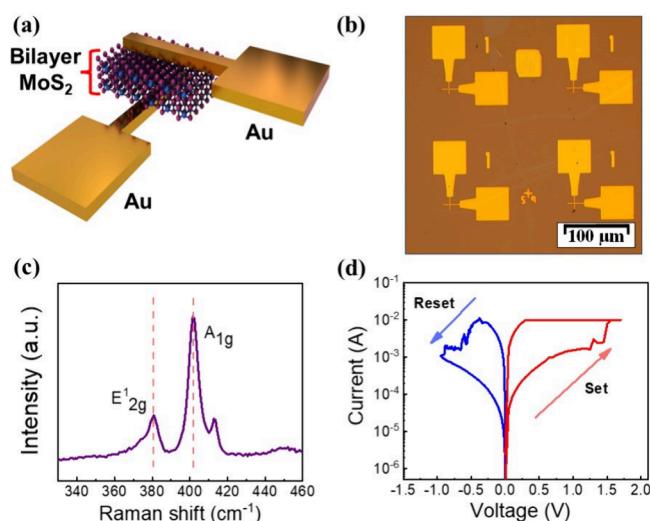

Figure 2a–c presents a switching mechanism at the atomic level in which STM and LTM characteristics can be selected based on the strength of the filament. Previous studies suggested the formation mechanism of the dissociation–diffusion–adsorption (DDA) filament in mono- to few-layer MoS<sub>2</sub> films based on a monolayer-like switching model, which is a metal-ion transition model within the TMD layer, similar to the CBRAM.<sup>54,55,58</sup> When a voltage is applied to the top Au electrode, metal atoms lose electrons to the electrode and become positively charged ions during the metal-atom dissociation process. The dissociation process is dominated by the atomization enthalpy of the metal, and Au has a relatively low-atomization enthalpy.<sup>54,59,60</sup> Subsequently, these metal ions diffuse between the top electrode and the MoS<sub>2</sub> surface, where they are adsorbed into the sulfur vacancies within the MoS<sub>2</sub> film. While applying the bias, this Au adsorption results in the formation of both stable and unstable filaments in the MoS<sub>2</sub> layer, thus lowering the device resistance (Figure 2a). Direct observations from previous studies using scanning tunneling microscopy and transmission electron microscopy experiments provided conclusive evidence for the atomic-scale resistive switching mechanism in the MoS<sub>2</sub> atomistor, thus confirming the presence of sulfur vacancies and the movement of Au ions through the Au-filament bridge.<sup>58,61</sup> Figure 2b shows the Au relaxation decay at a low-conductance level. The Au atoms in the unstable filaments return to the Au electrode owing to relaxation, and only the stable filaments remain after applying the voltage. In Figure S7, weak filament formation was induced by setting a compliance current of  $<10 \text{ mA}$  for the set DC sweep process. This unstable filament gradually faded owing to the relaxation phenomenon in the back sweep process (2 V–0 V), thus resulting in a decreasing current. Figure 2c demonstrates a strong set process in which strong and stable filaments are formed in the MoS<sub>2</sub> layer to yield LTM characteristics. In Figure S8, strong filament formation was induced by setting a compliance current above 10 mA during the DC set sweep process. The relaxation phenomenon is minimized owing to the stable filament even during the back sweep process (2 V–0 V) and the current remains stable, thus demonstrating the LTM properties. Even for a continuous set process with increasing compliance current, Figure S2 shows the relationship between the filament stability and relaxation phenomenon. In this study, the DDA mechanism in bi- and trilayer TMD films cannot be conclusively confirmed using fundamental mechanisms. Nevertheless, we evaluated the MoS<sub>2</sub> atomistor using mono-, bi-, and trilayer configurations in previous studies, attributing their memristive switching to a filamentary model.<sup>56</sup> This model is induced by defective grain boundaries within the TMD layers, which we analyzed with several the fabrication conditions.<sup>31,54,62–69</sup> This study suggests that short- and long-term phenomena can coexist depending on the strength and stability of the filament bridge during the switching process.

Figure 2d depicts the relaxation phenomenon that occurs in the models shown in Figure 2a,b in the low-conduction range observed during continuous pulse measurements. The inset indicates continuous programming input pulses, the amplitude of which increases by 0.025 V (from 1.5 to 2 V) with a pulse width of 10  $\mu\text{s}$ . When the amplitudes of the continuous programming pulses increase, conductance increases through

Figure 2. Schematic diagrams illustrating the movement of Au atoms in the  $\text{MoS}_2$  layer: (a) programming process at the low-conductance level with unstable filament formation, (b) Au relaxation effect owing to the presence of unstable filaments after the application of a voltage, and (c) stable filament formation at a high-conductance level. (d) Short-term memory analysis: continuous programming pulses with decay effects, (e) long-term memory analysis: multilevel states retention based on filament stability, and (f) correlation analysis depicting the relationship between retention and LRS resistance as a function of compliance current.

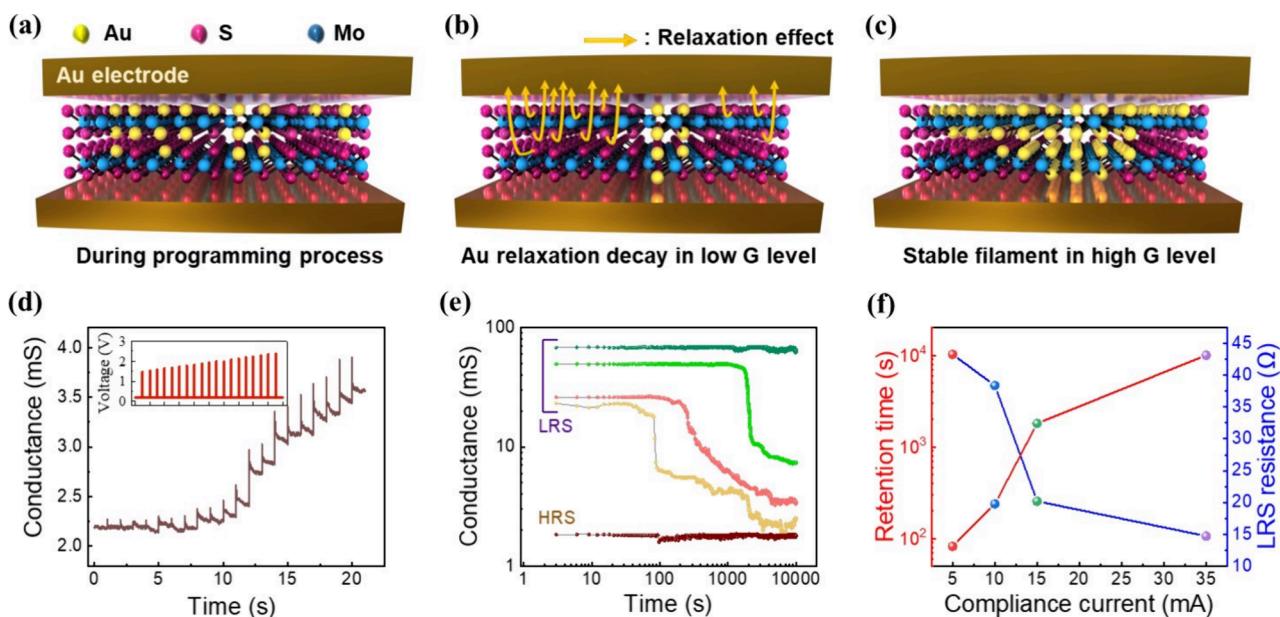

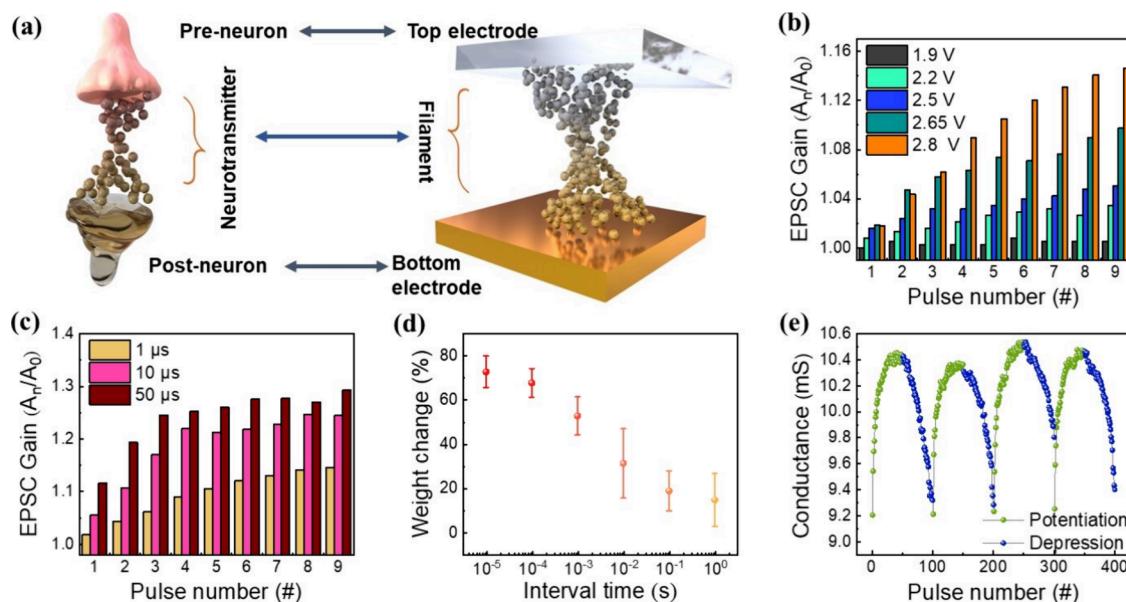

Figure 3. (a) Schematic of the imitation between a synaptic neural structure and device synaptic plasticity. Synaptic plasticity of the device: (b) EPSC gain values in response to different programming pulse amplitudes between 1.9 and 2.8 V and a pulse width of 1  $\mu$ s, (c) EPSC gain values with different programming pulse widths of 1–50  $\mu$ s and a pulse amplitude of 2.8 V, (d) PPF weight change at various times intervals, demonstrating STM synaptic characteristics, and (e) long-term potentiation and depression at a high-conductance level.

filament formation in the  $\text{MoS}_2$  layer. The continuous programming pulses can be used to implement multilevel states. In addition, the decay phenomenon is observed during each read interval between sequential pairs of continuous programming pulses. Fitting analysis demonstrates the relaxation time using the following relaxation function, which can be used to validate the decay characteristics,

$$I(t) = I_0 + Ae^{-t/\tau}$$

where  $I(t)$  is the current at a given time  $t$ ,  $I_0$  is the current in the stable state,  $A$  is the prefactor, and  $\tau$  is the relaxation time ( $\tau$ ).<sup>25,50,71</sup> Relaxation behaviors are observed over a decay time of 17 ms (Figure S9). During the transition from a low to a high conductance, the relaxation effect becomes less frequent at high-conductance levels ( $>10$  mS) owing to the formation of stable filaments (Figure S10). Figure 2e presents the results of DC retention in multilevel states with compliance with current control. The proportional retention capability in the range of  $10^2$ – $10^4$  s appears between multilevel states based on the

conductance levels. In addition, strengthening the filaments improves retention capabilities up to  $10^4$  s, as represented by the dark-green point in the figure. Figure 2f shows the trends of programmable retention and LRS resistance based on the compliance current. As compliance current increases, the size and stability of conductive filaments improve, thus resulting in a decrease in LRS resistance. Furthermore, a greater decrease in LRS resistance leads to an improvement in retention capabilities. This indicates the correlation between filament stability and data-retention capability based on the MoS<sub>2</sub> atomristor.

Figure 3a depicts the similarity between the learning process based on the neurotransmitter intensity between synaptic neurons and the resistance changes owing to the filament stability between the memristor electrodes. Linear changes in synaptic weight directly lead to learning and memory activities in the neuromorphic system via synaptic plasticity.<sup>72–77</sup> This study confirms the availability of a synaptic device in the neuromorphic system using STM and LTM properties. Figure 3b,c demonstrates linear conductance changes based on the EPSC synaptic function using 10 programming pulses. Figure 3b depicts the EPSC gain values in response to five programming pulse amplitudes in the range of 1.9–2.8 V with 1  $\mu$ s pulse widths. As the pulse amplitude increases, the EPSC gain increases in response to the device conductance change. This suggests the presence of spike amplitude-dependent plasticity in which the memristor weight can be controlled depending on the amplitude of the pulse stimulus. Figure 3c shows the EPSC gain owing to different pulse widths in the range of 1–50  $\mu$ s with a 2.8 V pulse amplitude. As the pulse width increases, the EPSC gain conductance increases correspondingly. This behavior reveals that a high-pulse width further activates the device, and this substantially modulates synaptic weights. The results obtained using five consecutive programming pulses with different pulse widths and amplitudes confirm that the device exhibits a linear response (Figure S11).

Figure 3d illustrates the PPF synaptic function, which demonstrates the changes in the intensities of two synaptic stimuli over time at different intervals (Figure S12).<sup>78–82</sup> As the interval time increases, the magnitude of current decay increases, which is analogous to the STM effect. Various intervals ranging from 10  $\mu$ s to 1 s are added between two identical programming pulses with a pulse amplitude of 2.5 V and pulse width of 7  $\mu$ s. Weight changes are calculated using the following equation,

$$\Delta W = (G_2 - G_1)/G_1 \times 100(\%)$$

where  $G_1$  and  $G_2$  are the conductance values of the device measured after the first and second programming pulses, respectively. The synaptic weight change of the memristor increases as the interval between two programming pulses decreases. Figure 3e displays long-term potentiation and depression at a high conductance level. To improve linearity and symmetrical properties, an incremental pulse configuration was used as the programming pulse input (Figure S13). Therefore, achieving an artificial synaptic function using synaptic plasticity is feasible using this device with linear and symmetrical properties.

The SRDP characteristic refers to the primary and fundamental characteristics of biological synapses, where the strengthening or weakening of the synapse is determined by the frequency of the signal. In this study, the SRDP

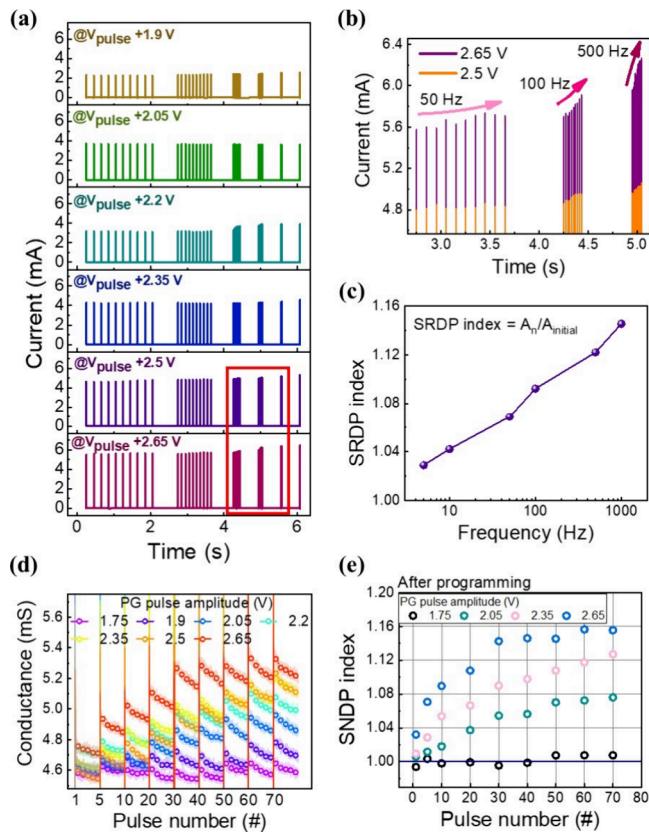

characteristics are emulated using various programming pulse amplitudes and frequencies in the device. Figure 4a illustrates

Figure 4. (a) Pulse-frequency-dependent current response in trains of 10 pulses at frequencies between 5 and 1000 Hz and amplitudes between 1.9 and 2.65 V. (b) Magnification of current results at frequencies between 50 and 500 Hz and amplitudes between 2.5 and 2.65 V. (c) Plot of the SRDP index as a function of spike frequency. (d) Pulse-number-dependent conductance response at the number of pulses between 1 and 70 and amplitudes between 1.75 and 2.65 V. (e) Plot of the SNDP index immediately after applying programming pulses.

the current changes by the applied programming pulse (in the range of 1.9–2.65 V) and frequency (in the range of 5–1000 Hz), indicating the response of the device at each programming pulse amplitude. Despite the use of the same programming pulse amplitude, the current responses increase as a function of the spike rate, which corresponds to the frequency. Figure 4b shows a magnified view of the current results with frequencies ranging from 50 to 500 Hz, and programming pulse amplitudes ranging from 2.5 to 2.65 V. This figure shows the intensified response of the device at increasing frequencies, focusing its dependence on the spike rate. This aligns with biological synaptic characteristics, further validating the emulation of SRDP using the device. Figure 4c presents the SRDP index results for a 2.5 V programming pulse amplitude at all tested frequencies. It was found that the current gain consistently increased, thus indicating that higher programming pulse frequencies induce a stronger device response. SNDP behaviors can be an important feature of neuromorphic systems that reflects the ability of synaptic devices to mimic the adaptive learning ability of the human brain. Figure 4d illustrates the SNDP characteristics with decay properties. Each pulse was set to have amplitudes in the range

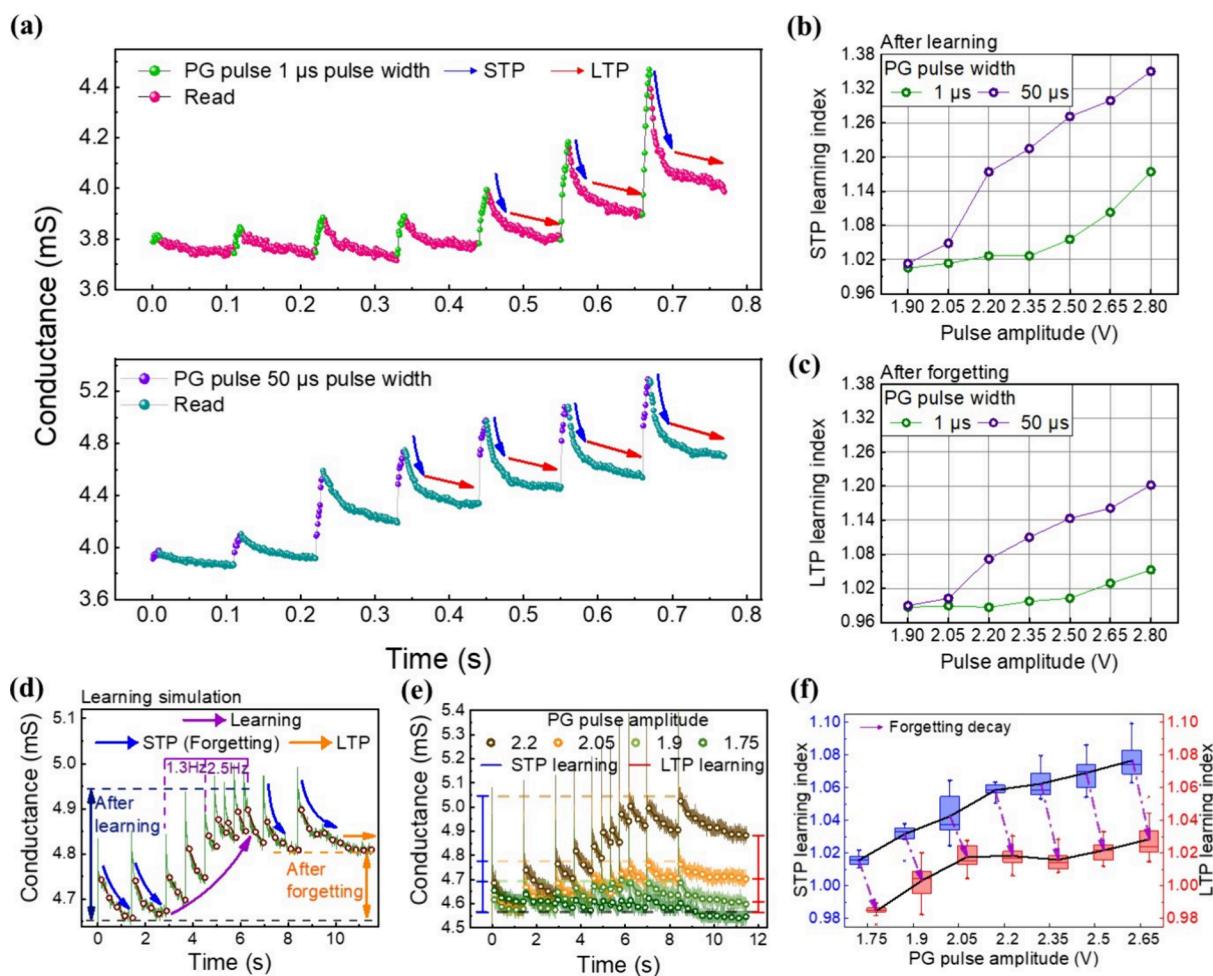

**Figure 5.** (a) Conductance changes under various voltages (1.9 to 2.8 V), illustrating the mixed influence of STP and LTP on device behavior. (b) STP learning response following programming, showing enhanced transmission with increased pulse width and amplitude. (c) LTP learning index after the forgetting process, indicating memory retention capabilities of the device with stronger programming inputs. (d) Learning simulation result controlling learning frequency to mimic STP and LTP. (e) The effect of learning intensity in terms of STP and LTP learning. (f) The results of 10 cycles of STP and LTP learning intensity according to pulse frequency and amplitude.

of 1.75–2.65 V and a pulse width of 15  $\mu$ s, and the number of applied pulses was in the range of 1–70 (generated at 1 s intervals). As the number of pulses increases, the conductance of the device increases linearly and is also proportional to the programming pulse amplitude. Consequently, Figure 4e depicts the device state outcome immediately after the application of each programming pulse number according to the different pulse amplitudes, thus illustrating that the device can elicit stronger responses by increasing the pulse number and amplitude. Figure S14 shows the conductance level difference immediately after programming and after the 1 s decay by considering the device with STP decay for 1 s readings. As a result, the SNDP index values are proportional to both the pulse number and amplitude immediately after programming and after STP decays.

Synaptic plasticity, the ability of synapses to change their strengths and connectivities in response to the intensity and frequency of learning stimuli, is essential for the formation of long-term and short-term memories in the brain. Figure 5 presents the characteristics of STP and LTP learning that control the processes of learning and forgetting, to apply programmable retention properties mimicking synaptic plasticity.<sup>83–86</sup> Figure 5a shows the conductance changes of the device at different voltages ranging from 1.9 to 2.8 V with a

read interval of 0.1 s, thus demonstrating the mixed effects of LTP and STP. The detailed pulse input schematics are shown in Figure S15. During the learning process, we applied programming pulses with increasing amplitudes and observed that the conductance increased linearly and proportionally. We also varied the pulse width from 1 to 50  $\mu$ s and found that the conductance increased proportionally (between the green and purple circles). This indicates that the device can be activated in different manners based on the intensity of external programming input (learning). After the application of 10 programming pulses, the device decreases its conductance with a decay effect, thus emulating the forgetting process in synaptic plasticity. Figure S16 illustrates the effects of STP and LTP learning on the conductance of the device during the programming and reading processes that simulate the learning and forgetting mechanisms in synaptic plasticity. The blue arrow indicates the decay effect after programming as an STP characteristic (forgetting). Additionally, the red arrow exhibits LTP characteristics after the decay effect (transition from learning to long-term memory). This ratio of long-term and short-term plasticity varies by adjusting the intensity and frequency of the programming input (learning strength). Figure 5b shows the amount of STP learning response immediately after programming, thus revealing that a

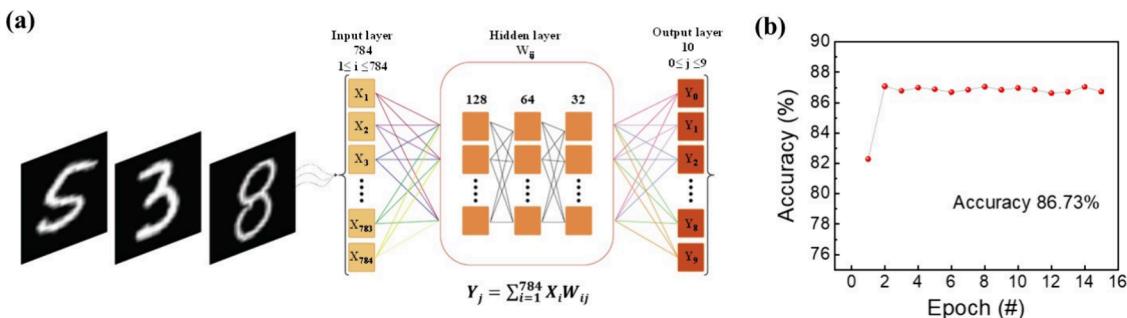

Figure 6. Image classification simulation using the MNIST handwritten digit data set: (a) schematic of neural network system framework for pattern recognition and (b) accuracy results during 15 learning epochs, achieving a recognition accuracy of 86.73%.

programming pulse width of  $50\ \mu\text{s}$  results in a stronger transmission than that elicited for a width of  $1\ \mu\text{s}$ , with the STP learning index linearly increasing according to pulse amplitude. Figure 5c shows the LTP learning index; findings suggest that the device can memorize the state after the forgetting process. In this learning simulation, it is found that with programming pulses with widths  $<1\ \mu\text{s}$  and amplitudes of  $2.2\ \text{V}$ , the LTP index drops by  $<1$  unit owing to the lack of learning strength (i.e., no transition from learning to long-term memory). Additionally, when using  $50\ \mu\text{s}$  compared with  $1\ \mu\text{s}$ , the LTP learning index is significantly enhanced by a stronger learning effect, thus indicating a stronger transition from learning to memory effect. This demonstrates the capability of the  $\text{MoS}_2$  atomistor to implement long-term and short-term memory simultaneously depending on the intensity of learning.<sup>1,87</sup>

Figure 5d illustrates the simulated learning results by controlling the learning frequency to emulate STP and LTP by fixing the programming pulse width and amplitude. After the application of two programming pulses (with a  $1.5\ \text{s}$  interval) during the  $0\text{--}3\ \text{s}$  period, the device was observed to return to its initial state owing to its STP characteristics. For a period in the range of  $3\text{--}6.25\ \text{s}$ , the frequency of programming pulses was increased to  $1.3$  and  $2.5\ \text{Hz}$ ; this enhanced the repetition of learning, and a noticeable increase in device conductance (purple arrow) was observed. Finally, for a period in the range of  $8.5\text{--}11\ \text{s}$ , the learning frequency was reduced and the forgetting effect was examined with the decay lasting for more than  $2\ \text{s}$ . While STP characteristics were observed in all learning phases (forgetting), the reinforcement LTP characteristic after the decay effect was shown by intensifying the training strength based on the training frequency modulation. Ultimately, the transition from learning to long-term memory is indicated by the orange arrow. Figure 5e demonstrates that varying the amplitude from  $1.75$  to  $2.2\ \text{V}$  (using the same frequency setting) results in different STP and LTP learning results, thus verifying the effects of both learning frequency and intensity. The programming pulse at the amplitude setting of  $1.75\ \text{V}$  did not induce stimulation owing to the lack of learning strength, but under the same frequency condition, the  $2.2\ \text{V}$  setting showed the learning effect associated with the improvement of the LTP properties from  $4.6$  to  $4.9\ \text{mS}$ . Based on the training intensity according to amplitude, Figure 5f shows the results of 10 cycles of learning simulations (as a boxplot) using programming pulse amplitudes ranging from  $1.75$  to  $2.65\ \text{V}$ . The STP and LTP learning indices both increase linearly as a function of the programming pulse amplitude. Moreover, despite the same

learning simulation conditions, an increase in intensity and learning frequency leads to a higher probability of learning transition to long-term memory. Ultimately, using  $\text{MoS}_2$  atomistors demonstrates the feasibility of both LTP and STP properties based on learning intensity and frequency. This conclusively applies programmable retention characteristics to synaptic plasticity, perfectly emulating the brain's phenomena of learning, forgetting, and long- and short-term memory.

The human brain executes learning and memory functions by adjusting the connection strength of synapses between neurons. The pivotal roles of learning and memory in these biological synapses are crucial for the realization of neuromorphic computing. Thus, conducting learning based on the linear and symmetric synaptic characteristics of LTP and LTD, as depicted in Figure 3e, indicates the potential of  $\text{MoS}_2$  devices as neuromorphic computing components. Figure 6a shows a simulation schematic emphasizing the fact that the linearity of LTP and LTD serves as a crucial indicator for learning tasks using the MNIST handwritten digit data set. In the artificial neural network (ANN) simulation environment for on-chip learning using potentiation and depression curves, three hidden layers responsible for learning consist of  $128$ ,  $64$ , and  $32$  neurons, respectively. The architecture involves fully connected input, hidden, and output layers, thus showcasing the characteristics of a multilayer perceptron, which is a type of ANN. Moreover, the interconnected lines between each neuron exhibit online learning characteristics with weights being updated in real time reflecting the linearity of long-term potentiation and depression. Additionally, linear and symmetrical synaptic characteristics (which are used as a weight) of the device improve the learning ability of the ANN in this process. Linearity affects the degree of directness between the input and output, and symmetry distributes the learning possibilities uniformly during the process of updating synaptic weights.<sup>88–90</sup> Figure 6b illustrates the accuracy of digit recognition using the potentiation and depression characteristics shown in Figure 3e as weights for the ANN, based on a data set of  $60,000$  training images. With each epoch, the accuracy consistently increases and finally reaches  $86.73\%$ . These results demonstrate that the synaptic properties of the  $\text{Au}/\text{MoS}_2/\text{Au}$  device can be applied in a hardware-based neuromorphic system.

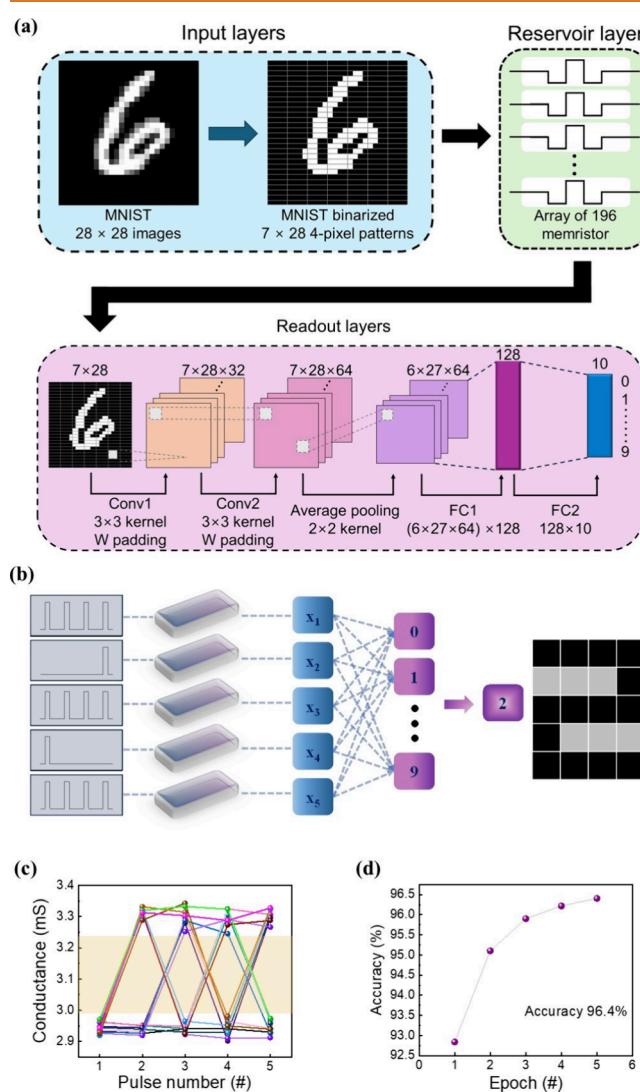

Reservoir computing is a system that processes temporal and sequential inputs using STM properties.<sup>91–95</sup> In a reservoir computing system, the memristor serves as a reservoir layer based on high-dimensional mapping, enabling applications such as image recognition, image generation, and time series analysis. The 4-bit reservoir computing data obtained in this

study demonstrate the potential of reservoir computing for tasks like image generation and recognition. Figure 7a depicts a

Figure 7. Reservoir computing system: (a) schematic of reservoir computing consisting with input, reservoir and readout layer, (b) process schematics from input pulse train to output nodes to implement digits in  $5 \times 4$  pixels with five rows, (c) results of 16 different states using Au/MoS<sub>2</sub>/Au, four bits as physical reservoir, and (d) convolutional neural network-based artificial neural network in image recognition using reservoir computing, achieving an accuracy of 96.4% with MNIST database images.

schematic of a reservoir computing system consisting of input, reservoir, and readout layers. In the input layer, the temporal input is connected to the reservoir layer. In the reservoir layer, which operates as a nonlinear system, the input signal is mapped onto a higher-dimensional space based on the property according to which the signal returns to its original state over time. The readout layer generates the desired output based on the output of the reservoir layer. A computing system based on a nonlinear dynamic system can efficiently process various input signals. Implementing the physical reservoir suggests the possibility of using this system in image generation, as shown in Figure 7b. One pulse train can implement four bits, and five rows can be parallelized to implement 0–9 digits using a  $5 \times 4$  pixel array. Figure 7c

reveals the potential for system expansion by implementing all states from 0000 to 1111 using an Au/MoS<sub>2</sub>/Au device (Figures S17 and S18). To implement four bits of data within the physical reservoir, four consecutive pulse streams can be applied with the same programming pulse (pulse amplitude of 1.6 V and pulse width of 100  $\mu$ s). The conductance interval within the range of 2.99–3.24 mS can be used to distinguish values between zero and one. Additionally, an ANN based on a convolutional neural network (CNN) was devised utilizing the MNIST database to validate the efficiency of reservoir computing in image recognition (as depicted in the reservoir computing schematic in Figure 7a). Table S1 summarizes the previous studies related to reservoir computing and application based on a neural network using memristors. Rarely has simulations using CNN integrated with physical reservoir been reported. To integrate MNIST images into a 4-bit reservoir computing system, preprocessing is essential to adapt the images for the input layer. Specifically, each MNIST image, consisting of  $28 \times 28$  pixels with values ranging from 0 to 255 (0 for darkness, and 255 for brightness), is binarized to either zero or one and then grouped into sets of four pixels, forming one group. In total, 196 groups were created, each representing one of the 16 states from [0000] to [1111]. These states were then arranged into 196 virtual arrays and aligned with the normalized current values derived from the physical reservoir layer in our memristor. The readout layer of the reservoir computing system was constructed based on CNN, a type of ANN specialized in recognizing and interpreting local patterns in images. The CNN network used in this device comprised two convolution layers, an average pooling layer, and fully connected layers. The parameters for the first convolution layer include a kernel width of 3, kernel height of 3, one input channel, 32 output channels, and a stride of 1. The second convolution layer was configured similarly, except for the input channel, which was set to 32, and the output channel, which was 64. All convolution layers utilized zero padding to prevent the reduction of image data and applied a rectified linear unit activation function. The image of size  $7 \times 28 \times 64$  passed through the two convolution layers and through the average pooling layer to reduce noise. The input size entering the fully connected layer was  $6 \times 27 \times 64$  and corresponded to the final output image size of the average pooling layer. A hidden layer with 100 neurons was present between this input and the output layer; ultimately, the output layer determined the label of the image. Figure 7e demonstrates an accuracy of 96.4% achieved after five epochs using 50,000 training images in off-chip training using the described configuration. These findings suggest promising capabilities for image generation and recognition in our MoS<sub>2</sub> atomristor.

## CONCLUSIONS

The coexistence of STM and LTM characteristics was demonstrated in a Au/MoS<sub>2</sub>/Au device using programmable retention characteristics. The device shows promising synaptic properties and can be potentially applied in neuromorphic computing. This study presented complex applicable characteristics regarding the coexistence of short- and long-term effects using an Au-filament model within a MoS<sub>2</sub> layer. At low-conductance levels, the STM properties showed linear weight changes based on the EPSC, PPF, SRDP, and SNDP synaptic functions. Programmable retention, symmetric potentiation, and depression demonstrate the LTM characteristics at high-conductance levels. In learning simulations, programmable

retention and STP and LTP complex synaptic plasticity perfectly emulated the synaptic functions of learning, forgetting, LTM, and STM phenomena. Handwritten digits were recognized with 86.73% accuracy, and pattern recognition simulations using synaptic characteristics highlighted that the devices improved the learning of ANNs. Furthermore, we implemented 16 states as physical reservoirs using 4-bit reservoir computing by utilizing the STM characteristics of the device. Finally, to confirm the efficiency of the implemented reservoir computing, we performed CNN-based off-chip training using a physical reservoir and obtained a recognition rate of 96.4%. The results of this study can be applied to the integration of MoS<sub>2</sub> devices into neuromorphic systems, thus providing the opportunities for implementing STM and LTM effects with advanced synaptic plasticity.

## METHODS

A bilayer MoS<sub>2</sub> film was synthesized by sulfurizing a metallic Mo film deposited on sapphire using an e-beam evaporator. The sulfurization process was conducted in a three-zone tube furnace at 550 °C for 15 min with the middle zone containing the sapphire/Mo stack. The first zone contained a crucible of sulfur powder heated to 220 °C. All electrodes were patterned with crossbar structures using e-beam lithography. Additionally, 2 nm Cr/100 nm Au bottom electrodes were deposited on a 285 nm SiO<sub>2</sub>/Si substrate using an e-beam evaporator. The MoS<sub>2</sub> film was coated with a polystyrene (PS) film and subsequently separated from the sapphire substrate using a water-assisted transfer method. Following the transfer of the MoS<sub>2</sub> film onto the bottom electrodes, the film was dissolved using toluene. The top electrodes were patterned using the same method as that used for patterning the bottom electrodes. Consequently, a crossbar structure with a 1 × 1  $\mu\text{m}^2$  cell size was defined. The top electrodes were fabricated using an e-beam evaporator from CHA Industries (SE-1000-RAP) under a chamber pressure of approximately  $5 \times 10^{-6}$  Torr.

## ASSOCIATED CONTENT

### Supporting Information

The Supporting Information is available free of charge at <https://pubs.acs.org/doi/10.1021/acsnano.4c00333>.

Bilayer MoS<sub>2</sub> film thickness inspection, multilevel states by DC incremental reset repetition, DC incremental compliance current set repetition, device-to-device conductance distribution of LRS and HRS, DC endurance data, transient set and reset characteristics during pulse switching, filament stability depending on compliance current during DC set sweep, the relaxation effect and its exponential decay fitting at a low-conductance level, state transition from low- to high-conductance levels during consecutive increasing programming set pulses with decay properties at low-conductance levels and stable filament formation at high-conductance levels, EPSC results using five consecutive pulses with different pulse widths and amplitudes showing a general tendency of increasing conductance change as pulse amplitude and width increase, an example of PPF input voltage and transient output current characteristics, input voltage schematic of potentiation and depression, SNDP index after programming and relaxation, input voltage schematic of STP and LTP characteristics, magnified conductance change during programming and relaxation, and 16 states of the device with different pulse streams from

0000 to 1111 and device-to-device reservoir computing implementation ([PDF](#))

## AUTHOR INFORMATION

### Corresponding Authors

Deji Akinwande – *Microelectronics Research Center, The University of Texas at Austin, Austin, Texas 78758, United States*;  [orcid.org/0000-0001-7133-5586](https://orcid.org/0000-0001-7133-5586); Email: [deji@ece.utexas.edu](mailto:deji@ece.utexas.edu)

Sungjun Kim – *Division of Electronics and Electrical Engineering, Dongguk University, Seoul, Seoul 04620, Korea*;  [orcid.org/0000-0002-9873-2474](https://orcid.org/0000-0002-9873-2474); Email: [sungjun@dongguk.edu](mailto:sungjun@dongguk.edu)

### Authors

Yoonseok Lee – *Division of Electronics and Electrical Engineering, Dongguk University, Seoul, Seoul 04620, Korea*; *Microelectronics Research Center, The University of Texas at Austin, Austin, Texas 78758, United States*

Yifu Huang – *Microelectronics Research Center, The University of Texas at Austin, Austin, Texas 78758, United States*

Yao-Feng Chang – *Intel Corporation, Hillsboro, Oregon 97124, United States*;  [orcid.org/0000-0002-8943-9305](https://orcid.org/0000-0002-8943-9305)

Sung Jin Yang – *Microelectronics Research Center, The University of Texas at Austin, Austin, Texas 78758, United States*;  [orcid.org/0000-0002-0914-6378](https://orcid.org/0000-0002-0914-6378)

Nicholas D. Ignacio – *Microelectronics Research Center, The University of Texas at Austin, Austin, Texas 78758, United States*;  [orcid.org/0000-0001-8663-3033](https://orcid.org/0000-0001-8663-3033)

Shanmukh Kutagulla – *Microelectronics Research Center, The University of Texas at Austin, Austin, Texas 78758, United States*;  [orcid.org/0000-0002-4078-8053](https://orcid.org/0000-0002-4078-8053)

Sivasakthya Mohan – *Microelectronics Research Center, The University of Texas at Austin, Austin, Texas 78758, United States*;  [orcid.org/0000-0002-4529-6226](https://orcid.org/0000-0002-4529-6226)

Sunghun Kim – *Division of Electronics and Electrical Engineering, Dongguk University, Seoul, Seoul 04620, Korea*

Jungwoo Lee – *Division of Electronics and Electrical Engineering, Dongguk University, Seoul, Seoul 04620, Korea*

Complete contact information is available at: <https://pubs.acs.org/10.1021/acsnano.4c00333>

### Notes

The authors declare no competing financial interest.

## ACKNOWLEDGMENTS

This research was supported by the MOTIE (Ministry of Trade, Industry, and Energy) in Korea, under the Fostering Global Talents for Innovative Growth Program (P0017307) supervised by the Korea Institute for Advancement of Technology (KIAT) and supported by the National Research Foundation of Korea (NRF) grant funded by the Ministry of Science and ICT (RS-2024-00356939). D.A acknowledges the National Science Foundation (NSF) grant no. 2329191.

## REFERENCES

- (1) Cheng, S.; Zhong, L.; Yin, J.; Duan, H.; Xie, Q.; Luo, W.; Jie, W. Controllable Digital and Analog Resistive Switching Behavior of 2D Layered WSe<sub>2</sub> Nanosheets for neuromorphic Computing. *Nanoscale* **2023**, *15* (10), 4801–4808.

- (2) Yang, S.; Kim, T.; Kim, S.; Kim, S.; Kim, T. H.; Ismail, M.; Mahata, C.; Kim, S.; Cho, S. Demonstration of Synaptic Character-

istics in VRRAM with TiN Nanocrystals for neuromorphic System. *Adv. Mater. Interfaces* **2023**, *10* (21), 2300290 DOI: [10.1002/admi.202300290](https://doi.org/10.1002/admi.202300290).

(3) Chaudhary, M.; Yang, T. Y.; Chen, C. T.; Lai, P. C.; Hsu, Y. C.; Peng, Y. R.; Kumar, A.; Lee, C. H.; Chueh, Y. L. Emulating neuromorphic and In-Memory Computing Utilizing Defect Engineering in 2D-Layered WSeO<sub>x</sub> and WSe<sub>2</sub> Thin Films by Plasma-Assisted Selenization Process. *Adv. Funct. Mater.* **2023**, 2303697 DOI: [10.1002/adfm.202303697](https://doi.org/10.1002/adfm.202303697).

(4) So, H.; Lee, J. K.; Kim, S. Short-Term Memory Characteristics in n-Type-ZnO/p-Type-NiO Heterojunction Synaptic Devices for Reservoir Computing. *Appl. Surf. Sci.* **2023**, *625*, No. 157153.

(5) Shen, Z.; Zhao, C.; Qi, Y.; Xu, W.; Liu, Y.; Mitrovic, I. Z.; Yang, L.; Zhao, C. Advances of RRAM Devices: Resistive Switching Mechanisms, Materials and Bionic Synaptic Application. *Nanomaterials* **2020**, 1437.

(6) Zhang, W.; Gao, B.; Tang, J.; Li, X.; Wu, W.; Qian, H.; Wu, H. Analog-Type Resistive Switching Devices for neuromorphic Computing. *Phys. Status Solidi RRL* **2019**, *13* (10), 1900204 DOI: [10.1002/pssr.201900204](https://doi.org/10.1002/pssr.201900204).

(7) Nowak, J. J.; Robertazzi, R. P.; Sun, J. Z.; Hu, G.; Abraham, D. W.; Trouilloud, P. L.; Brown, S.; Gaidis, M. C.; O'Sullivan, E. J.; Gallagher, W. J.; Worledge, D. C. Demonstration of Ultralow Bit Error Rates for Spin-Torque Magnetic Random-Access Memory with Perpendicular Magnetic Anisotropy. *IEEE Magn. Lett.* **2011**, *2*, 3000204 DOI: [10.1109/LMAG.2011.2155625](https://doi.org/10.1109/LMAG.2011.2155625).

(8) Zhao, W. S.; Zhang, Y.; Devolder, T.; Klein, J. O.; Ravelosona, D.; Chappert, C.; Mazoyer, P. Failure and Reliability Analysis of STT-MRAM. *Microelectronics Reliability* **2012**, *52* (9–10), 1848–1852.

(9) Mikolajick, T.; Dehm, C.; Hartner, W.; Kasko, I.; Kastner, M. J.; Nagel, N.; Moert, M.; Mazure, C. FeRAM Technology for High Density Applications. *Microelectron. Reliab.* **2001**, *41*, 947 DOI: [10.1016/S0026-2714\(01\)00049-X](https://doi.org/10.1016/S0026-2714(01)00049-X).

(10) Park, J.; Kim, T. H.; Kwon, O.; Ismail, M.; Mahata, C.; Kim, Y.; Kim, S.; Kim, S. Implementation of Convolutional Neural Network and 8-Bit Reservoir Computing in CMOS Compatible VRRAM. *Nano Energy* **2022**, *104*, No. 107886.

(11) Hatayama, S.; Sutou, Y.; Shindo, S.; Saito, Y.; Song, Y. H.; Ando, D.; Koike, J. Inverse Resistance Change Cr<sub>2</sub>Ge<sub>2</sub>Te<sub>6</sub>-Based PCRAM Enabling Ultralow-Energy Amorphization. *ACS Appl. Mater. Interfaces* **2018**, *10* (3), 2725–2734.

(12) Lanza, M.; Sebastian, A.; Lu, W. D.; Le Gallo, M.; Chang, M. F.; Akinwande, D.; Puglisi, F. M.; Alshareef, H. N.; Liu, M.; Roldan, J. B. memristive Technologies for Data Storage, Computation, Encryption, and Radio-Frequency Communication. *Science*, American Association for the Advancement of Science, 2022, eabj9979 DOI: [10.1126/science.abj9979](https://doi.org/10.1126/science.abj9979).

(13) Hong, X.; Loy, D. J.; Dananjaya, P. A.; Tan, F.; Ng, C.; Lew, W. Oxide-Based RRAM Materials for neuromorphic Computing. *J. Mater. Sci.*; Springer: New York LLC, 2018; pp 8720–8746. DOI: [10.1007/s10853-018-2134-6](https://doi.org/10.1007/s10853-018-2134-6).

(14) Zhao, M.; Gao, B.; Tang, J.; Qian, H.; Wu, H. Reliability of Analog Resistive Switching Memory for neuromorphic Computing. *Appl. Phys. Rev.*, American Institute of Physics Inc. 2020 011301. DOI: [10.1063/1.5124915](https://doi.org/10.1063/1.5124915).

(15) Ahn, W.; Jeong, H. B.; Oh, J.; Hong, W.; Cha, J. H.; Jeong, H. Y.; Choi, S. Y. A Highly Reliable Molybdenum Disulfide-Based Synaptic Memristor Using a Copper Migration-Controlled Structure. *Small* **2023**, *19* (33), 2300223 DOI: [10.1002/smll.202300223](https://doi.org/10.1002/smll.202300223).

(16) Zhang, Z.-D.; Zhong, Y.-N.; Shen, C.; Huang, H.-T.; Lu, Z.-N.; Xu, J.-L.; Gao, X.; Wang, S.-D. A Hybrid Memristor with Oxide-Polymer Heterojunction. *Appl. Phys. Lett.* **2022**, *121* (19), 191905 DOI: [10.1063/5.0123496](https://doi.org/10.1063/5.0123496).

(17) Kitsios, S.; Bousoulas, P.; Spithouris, D.; Kainouriaki, M.; Tsigkourakos, M.; Chatzopoulou, P.; Dimitrakopoulos, G. P.; Komninou, P.; Tsoukalas, D. Demonstration of Enhanced Switching Variability and Conductance Quantization Properties in a SiO<sub>2</sub> Conducting Bridge Resistive Memory with Embedded Two-Dimensional MoS<sub>2</sub> Material. *ACS Applied Electronic Materials* **2022**, *4* (6), 2869–2878.

(18) Ge, J.; Zhang, S.; Liu, Z.; Xie, Z.; Pan, S. Flexible Artificial Nociceptor Using a Biopolymer-Based Forming-Free Memristor. *Nanoscale* **2019**, *11* (14), 6591–6601.

(19) Hu, P.; Hossain, S.; Liu, Z.; Meng, D.; Wang, Y.; Ou, T. H.; Yang, H.; Chen, B.; Cai, Z.; Shi, Y.; Barnell, M.; Wu, Q.; Cronin, S. B.; Wu, W. Hybrid Tuning of Sub-Filaments to Improve Analog Switching Performance in memristive Devices. *Adv. Mater. Technol.* **2023**, *8* (15), 2300109 DOI: [10.1002/admt.202300109](https://doi.org/10.1002/admt.202300109).

(20) Yang, S.; Kim, T.; Kim, S.; Chung, D.; Kim, T. H.; Lee, J. K.; Kim, S.; Ismail, M.; Mahata, C.; Kim, S.; Cho, S. Synaptic Plasticity and Non-Volatile Memory Characteristics in TiN-Nanocrystal-Embedded 3D Vertical Memristor-Based Synapses for neuromorphic Systems. *Nanoscale* **2023**, *15* (32), 13239–13251.

(21) Chen, S.; Mahmoodi, M. R.; Shi, Y.; Mahata, C.; Yuan, B.; Liang, X.; Wen, C.; Hui, F.; Akinwande, D.; Strukov, D. B.; Lanza, M. Wafer-Scale Integration of Two-Dimensional Materials in High-Density memristive Crossbar Arrays for Artificial Neural Networks. *Nature Electronics* **2020**, *3* (10), 638–645.

(22) Xu, X.; Cho, E. J.; Bekker, L.; Talin, A. A.; Lee, E.; Pascall, A. J.; Worsley, M. A.; Zhou, J.; Cook, C. C.; Kuntz, J. D.; Cho, S.; Orme, C. A. A Bioinspired Artificial Injury Response System Based on a Robust Polymer Memristor to Mimic a Sense of Pain, Sign of Injury, and Healing. *Adv. Sci.* **2022**, *9* (15), 2200629 DOI: [10.1002/advs.202200629](https://doi.org/10.1002/advs.202200629).

(23) Kwon, O.; Shin, J.; Chung, D.; Kim, S. Energy Efficient Short-Term Memory Characteristics in Ag/SnO<sub>x</sub>/TiN RRAM for neuromorphic System. *Ceram. Int.* **2022**, *48* (20), 30482–30489.

(24) Ali, A.; Abbas, H.; Hussain, M.; Jaffery, S. H. A.; Hussain, S.; Choi, C.; Jung, J. Versatile GeS-Based CBRAM with Compliance-Current-Controlled Threshold and Bipolar Resistive Switching for Electronic Synapses. *Appl. Mater. Today* **2022**, *29*, No. 101554.

(25) Abbas, H.; Abbas, Y.; Hassan, G.; Sokolov, A. S.; Jeon, Y. R.; Ku, B.; Kang, C. J.; Choi, C. The Coexistence of Threshold and Memory Switching Characteristics of ALD HfO<sub>2</sub>memristor Synaptic Arrays for Energy-Efficient neuromorphic Computing. *Nanoscale* **2020**, *12* (26), 14120–14134.

(26) Naqi, M.; Kang, M. S.; Liu, N.; Kim, T.; Baek, S.; Bala, A.; Moon, C.; Park, J.; Kim, S. Multilevel Artificial Electronic Synaptic Device of Direct Grown Robust MoS<sub>2</sub> Based Memristor Array for In-Memory Deep Neural Network. *NPJ 2D Mater. Appl.* **2022**, *6* (1), 53 DOI: [10.1038/s41699-022-00325-5](https://doi.org/10.1038/s41699-022-00325-5).

(27) Yang, S. J.; Dahan, M. M.; Levit, O.; Makal, F.; Peterson, P.; Alikpala, J.; Nibhanupudi, S. T.; Luth, C. J.; Banerjee, S. K.; Kim, M.; Roessler, A.; Yalon, E.; Akinwande, D. Reconfigurable Low-Voltage Hexagonal Boron Nitride Nonvolatile Switches for Millimeter-Wave Wireless Communications. *Nano Lett.* **2023**, *23* (4), 1152–1158.

(28) Völkel, L.; Braun, D.; Belete, M.; Kataria, S.; Wahlbrink, T.; Ran, K.; Kistermann, K.; Mayer, J.; Menzel, S.; Daus, A.; Lemme, M. C. Resistive Switching and Current Conduction Mechanisms in Hexagonal Boron Nitride Threshold memristors with Nickel Electrodes. *Adv. Funct. Mater.* **2024**, 2300428 DOI: [10.1002/adfm.202300428](https://doi.org/10.1002/adfm.202300428).

(29) Dastger, G.; Abbas, H.; Kim, D. Y.; Eom, J.; Choi, C. Synaptic Characteristics of an Ultrathin Hexagonal Boron Nitride (h-BN) Diffusive Memristor. *Phys. Status Solidi RRL* **2021**, *15* (1), 2000473 DOI: [10.1002/pssr.202000473](https://doi.org/10.1002/pssr.202000473).

(30) Dong, Z.; Hua, Q.; Xi, J.; Shi, Y.; Huang, T.; Dai, X.; Niu, J.; Wang, B.; Wang, Z. L.; Hu, W. Ultrafast and Low-Power 2D Bi<sub>2</sub>O<sub>2</sub>Se memristors for neuromorphic Computing Applications. *Nano Lett.* **2023**, *23* (9), 3842–3850.

(31) Feng, X.; Li, Y.; Wang, L.; Chen, S.; Yu, Z. G.; Tan, W. C.; Macadam, N.; Hu, G.; Huang, L.; Chen, L.; Gong, X.; Chi, D.; Hasan, T.; Thean, A. V. Y.; Zhang, Y. W.; Ang, K. W. A Fully Printed Flexible MoS<sub>2</sub> memristive Artificial Synapse with Femtojoule Switching Energy. *Adv. Electron. Mater.* **2019**, *5* (12), 1900740 DOI: [10.1002/aelm.201900740](https://doi.org/10.1002/aelm.201900740).

(32) Krishnaprasad, A.; Dev, D.; Shawkat, M. S.; Martinez-Martinez, R.; Islam, M. M.; Chung, H. S.; Bae, T. S.; Jung, Y.; Roy, T. Graphene/MoS<sub>2</sub>/SiO<sub>x</sub> memristive Synapses for Linear Weight Update. *npj 2D Materials and Applications* **2023**, *7* (1), 1–8.

(33) Zhang, D.; Yeh, C. H.; Cao, W.; Banerjee, K. 0.5T0.5R-An Ultracompact RRAM Cell Uniquely Enabled by van Der Waals Heterostructures. *IEEE Trans. Electron Devices* **2021**, *68* (4), 2033–2040.

(34) Yeh, C. H.; Zhang, D.; Cao, W.; Banerjee, K. 0.5T0.5R -Introducing an Ultra-Compact Memory Cell Enabled by Shared Graphene Edge-Contact and h-BN Insulator. *IEEE Int. Electron Devices Meet.* **2020**, *2020*, 12.3.1–12.3.4.

(35) Pi, S.; Li, C.; Jiang, H.; Xia, W.; Xin, H.; Yang, J. J.; Xia, Q. Memristor Crossbar Arrays with 6-Nm Half-Pitch and 2-Nm Critical Dimension. *Nat. Nanotechnol.* **2019**, *14* (1), 35–39.

(36) Choi, M. S.; Ali, N.; Ngo, T. D.; Choi, H.; Oh, B.; Yang, H.; Yoo, W. J. Recent Progress in 1D Contacts for 2D-Material-Based Devices. *Adv. Mater.* **2022**, *34* (39), 2202408 DOI: [10.1002/adma.202202408](https://doi.org/10.1002/adma.202202408).

(37) Jeong, J.; Kiem, D. H.; Guo, D.; Duan, R.; Watanabe, K.; Taniguchi, T.; Liu, Z.; Han, M. J.; Zheng, S.; Yang, H. Spin-Selective Memtransistors with Magnetized Graphene. *Adv. Mater.* **2024**, *36*, 2310291.

(38) Chan, Y. T.; Fu, Y.; Yu, L.; Wu, F. Y.; Wang, H. W.; Lin, T. H.; Chan, S. H.; Wu, M. C.; Wang, J. C. Compacted Self-Assembly Graphene with Hydrogen Plasma Surface Modification for Robust Artificial Electronic Synapses of Gadolinium Oxide memristors. *Advanced Materials Interfaces* **2020**, *7* (20), 1–10.

(39) Trstenjak, U.; Goß, K.; Gutsche, A.; Jo, J.; Wohlgemuth, M.; Dunin-Borkowski, R. E.; Gunkel, F.; Dittmann, R. Heterogeneous Integration of Graphene and HfO<sub>2</sub>Memristors. *Adv. Funct. Mater.* **2024**, *34*, 2309558.

(40) Xie, J.; Patoary, N.; Laskar, A. R.; Ignacio, N. D.; Zhan, X.; Celano, U.; Akinwande, D.; Esqueda, I. S. Quantum Conductance in Vertical Hexagonal Boron Nitride memristors with Graphene-Edge Contacts. *Nano Lett.* **2024**, *24*, 2473.

(41) Seo, S.; Lim, J.; Lee, S.; Alimkhanuly, B.; Kadyrov, A.; Jeon, D.; Lee, S. Graphene-Edge Electrode on a Cu-Based Chalcogenide Selector for 3D Vertical Memristor Cells. *ACS Appl. Mater. Interfaces* **2019**, *11* (46), 43466–43472.

(42) Tang, Y.; Lei, P.; Liao, K.; Jiang, T.; Chen, S.; Xie, Q.; Luo, W.; Zhao, Y.; Jie, W. Observation of Nonvolatile Resistive Switching Behaviors in 2D Layered InSe Nanosheets through Controllable Oxidation. *Appl. Phys. Lett.* **2021**, *119* (13), 133103 DOI: [10.1063/5.0061792](https://doi.org/10.1063/5.0061792).

(43) Luo, S.; Liao, K.; Lei, P.; Jiang, T.; Chen, S.; Xie, Q.; Luo, W.; Huang, W.; Yuan, S.; Jie, W.; Hao, J. A Synaptic Memristor Based on Two-Dimensional Layered WSe<sub>2</sub>nanosheets with Short- And Long-Term Plasticity. *Nanoscale* **2021**, *13* (13), 6654–6660.

(44) He, H. K.; Yang, F. F.; Yang, R. Flexible Full Two-Dimensional memristive Synapses of Graphene/WSe<sub>2</sub>-: XO<sub>y</sub>/Graphene. *Phys. Chem. Chem. Phys.* **2020**, *22* (36), 20658–20664.

(45) Li, Y.; Loh, L.; Li, S.; Chen, L.; Li, B.; Bosman, M.; Ang, K. W. Anomalous Resistive Switching in memristors Based on Two-Dimensional Palladium Diselenide Using Heterophase Grain Boundaries. *Nature Electronics* **2021**, *4* (5), 348–356.

(46) Yan, X.; Zhao, Q.; Chen, A. P.; Zhao, J.; Zhou, Z.; Wang, J.; Wang, H.; Zhang, L.; Li, X.; Xiao, Z.; Wang, K.; Qin, C.; Wang, G.; Pei, Y.; Li, H.; Ren, D.; Chen, J.; Liu, Q. Vacancy-Induced Synaptic Behavior in 2D WS<sub>2</sub> Nanosheet-Based Memristor for Low-Power neuromorphic Computing. *Small* **2019**, *15* (24), 1–9.

(47) Zhao, X.; Fan, Z.; Xu, H.; Wang, Z.; Xu, J.; Ma, J.; Liu, Y. Reversible Alternation between Bipolar and Unipolar Resistive Switching in Ag/MoS<sub>2</sub>/Au Structure for Multilevel Flexible Memory. *Journal of Materials Chemistry C* **2018**, *6* (27), 7195–7200.

(48) Tang, B.; Veluri, H.; Li, Y.; Yu, Z. G.; Waqar, M.; Leong, J. F.; Sivan, M.; Zamburg, E.; Zhang, Y. W.; Wang, J.; Thean, A. V. Y. Wafer-Scale Solution-Processed 2D Material Analog Resistive Memory Array for Memory-Based Computing. *Nat. Commun.* **2022**, *13* (1), 1–9.

(49) Xia, Y.; Wang, J.; Chen, R.; Wang, H.; Xu, H.; Jiang, C.; Li, W.; Xiao, X. 2D Heterostructure of Bi<sub>2</sub>O<sub>2</sub>Se/Bi<sub>2</sub>SeO<sub>x</sub> Nanosheet for Resistive Random Access Memory. *Adv. Electron. Mater.* **2022**, *8* (9), 2200126 DOI: [10.1002/aelm.202200126](https://doi.org/10.1002/aelm.202200126).

(50) Saini, S.; Dwivedi, A.; Lodhi, A.; Khandelwal, A.; Tiwari, S. P. Flexible Forming Free Resistive Memory Device with 2D Material MoSe<sub>2</sub>as Switching Layer. In *2023 7th IEEE Electron Devices Technology and Manufacturing Conference (EDTM): Strengthen the Global Semiconductor Research Collaboration After the Covid-19 Pandemic, March 7th-10th, 2023, Coex, Seoul, Korea*; Institute of Electrical and Electronics Engineers Inc., 2023. DOI: [10.1109/EDTM55494.2023.10103025](https://doi.org/10.1109/EDTM55494.2023.10103025).

(51) Das, U.; Bhattacharjee, S.; Mahato, B.; Prajapat, M.; Sarkar, P.; Roy, A. Uniform, Large-Scale Growth of WS<sub>2</sub> Nanodomains via CVD Technique for Stable Non-Volatile RRAM Application. *Mater. Sci. Semicond. Process.* **2020**, *107*, No. 104837.

(52) Li, Y.; Chen, S.; Yu, Z.; Li, S.; Xiong, Y.; Pam, M. E.; Zhang, Y. W.; Ang, K. W. In-Memory Computing Using Memristor Arrays with Ultrathin 2D PdSeO<sub>x</sub>/PdSe<sub>2</sub> Heterostructure. *Adv. Mater.* **2022**, *34* (26), 2201488 DOI: [10.1002/adma.202201488](https://doi.org/10.1002/adma.202201488).

(53) Sivan, M.; Li, Y.; Veluri, H.; Zhao, Y.; Tang, B.; Wang, X.; Zamburg, E.; Leong, J. F.; Niu, J. X.; Chand, U.; Thean, A. V. Y. All WS<sub>2</sub> 1T1R Resistive RAM Cell for Future Monolithic 3D Embedded Memory Integration. *Nat. Commun.* **2019**, *10* (1), 1–12.

(54) Wu, X.; Ge, R.; Akinwande, D.; Lee, J. C. Understanding of Multiple Resistance States by Current Sweeping in MoS<sub>2</sub>-Based Non-Volatile Memory Devices. *Nanotechnology* **2020**, *31* (46), 465206.

(55) Wu, X.; Ge, R.; Huang, Y.; Akinwande, D.; Lee, J. C. Resistance State Evolution under Constant Electric Stress on a MoS<sub>2</sub>non-Volatile Resistive Switching Device. *RSC Adv.* **2020**, *10* (69), 42249–42255.

(56) Huang, Y.; Gu, Y.; Mohan, S.; Dolocan, A.; Ignacio, N. D.; Kutagulla, S.; Matthews, K.; Londoño-Calderon, A.; Chang, Y. F.; Chen, Y. C.; Warner, J. H.; Pettes, M. T.; Lee, J. C.; Akinwande, D. Reliability Improvement and Effective Switching Layer Model of Thin-Film MoS<sub>2</sub> memristors. *Adv. Funct. Mater.* **2024**, *2214250* DOI: [10.1002/adfm.202214250](https://doi.org/10.1002/adfm.202214250).

(57) Lee, C.; Yan, H.; Brus, L. E.; Heinz, T. F.; Hone, J.; Ryu, S. Anomalous Lattice Vibrations of Single- and Few-Layer MoS<sub>2</sub>. *ACS Nano* **2010**, *4* (5), 2695–2700.

(58) Hus, S. M.; Ge, R.; Chen, P. A.; Liang, L.; Donnelly, G. E.; Ko, W.; Huang, F.; Chiang, M. H.; Li, A. P.; Akinwande, D. Observation of Single-Defect Memristor in an MoS<sub>2</sub> Atomic Sheet. *Nat. Nanotechnol.* **2021**, *16* (1), 58–62.

(59) Murthy, A. A.; Stanev, T. K.; Dos Reis, R.; Hao, S.; Wolverton, C.; Stern, N. P.; Dravid, V. P. Direct Visualization of Electric-Field-Induced Structural Dynamics in Monolayer Transition Metal Dichalcogenides. *ACS Nano* **2020**, *14* (2), 1569–1576.

(60) Iyikanat, F.; Sahin, H.; Senger, R. T.; Peeters, F. M. Ag and Au Atoms Intercalated in Bilayer Heterostructures of Transition Metal Dichalcogenides and Graphene. *APL Mater.* **2014**, *2* (9), No. 092801, DOI: [10.1063/1.4893543](https://doi.org/10.1063/1.4893543).

(61) Liu, Y.; Guo, J.; Zhu, E.; Liao, L.; Lee, S. J.; Ding, M.; Shakir, I.; Gambin, V.; Huang, Y.; Duan, X. Approaching the Schottky-Mott Limit in van Der Waals Metal-Semiconductor Junctions /639/301/1005/1007 /639/166/987 /639/925/357/1018 /639/925/927/1007 /120 /128 /140/133 /142 /142/126 /144 Letter. *Nature* **2018**, *557* (7707), 696–700.

(62) Bai, N.; Xu, M.; Hu, C.; Ma, Y.; Wang, Q.; He, D.; Qi, J.; Li, Y. Resistive Switching Behaviors Mediated by Grain Boundaries in One Longitudinal Al/MoS<sub>2</sub>&PVP/ITO Device. *Mater. Sci. Semicond. Process.* **2019**, *91*, 246–251.

(63) Cheng, P.; Sun, K.; Hu, Y. H. memristive Behavior and Ideal Memristor of 1T Phase MoS<sub>2</sub> Nanosheets. *Nano Lett.* **2016**, *16* (1), 572–576.

(64) Sangwan, V. K.; Jariwala, D.; Kim, I. S.; Chen, K. S.; Marks, T. J.; Lauhon, L. J.; Hersam, M. C. Gate-Tunable memristive

Phenomena Mediated by Grain Boundaries in Single-Layer MoS<sub>2</sub>. *Nat. Nanotechnol.* **2015**, *10* (5), 403–406.

(65) Li, X. D.; Wang, B. Q.; Chen, N. K.; Li, X. B. Resistive Switching Mechanism of MoS<sub>2</sub> Based atomristor. *Nanotechnology* **2023**, *34* (20), 205201 DOI: [10.1088/1361-6528/acb69d](https://doi.org/10.1088/1361-6528/acb69d).

(66) Jang, H. Y.; Kwon, O.; Nam, J. H.; Kwon, J. D.; Kim, Y.; Park, W.; Cho, B. Highly Reproducible Heterosynaptic Plasticity Enabled by MoS<sub>2</sub>/ZrO<sub>2</sub>-XHeterostructure Memtransistor. *ACS Appl. Mater. Interfaces* **2022**, *14* (46), 52173–52181.

(67) Bhattacharjee, S.; Caruso, E.; McEvoy, N.; Ó Coileáin, C.; O'Neill, K.; Ansari, L.; Duesberg, G. S.; Nagle, R.; Cherkaoui, K.; City, F.; Hurley, P. K. Insights into Multilevel Resistive Switching in Monolayer MoS<sub>2</sub>. *ACS Appl. Mater. Interfaces* **2020**, *12* (5), 6022–6029.

(68) Prakash, R.; Sharma, S.; Kumar, A.; Kaur, D. Improved Resistive Switching Performance in Cu-Cation Migrated MoS<sub>2</sub> Based ReRAM Device Incorporated with Tungsten Nitride Bottom Electrode. *Curr. Appl. Phys.* **2019**, *19* (3), 260–265.

(69) Lei, X.; Zhu, X.; Wang, H.; Dai, Y.; Zhang, H.; Zhai, C.; Wang, S.; Yan, J.; Zhao, W. Nonvolatile and Volatile Resistive Switching Characteristics in MoS<sub>2</sub> Thin Film for RRAM Application. *J. Alloys Compd.* **2023**, *969* (July), No. 172443.

(70) Abbas, Y.; Jeon, Y. R.; Sokolov, A. S.; Kim, S.; Ku, B.; Choi, C. Compliance-Free, Digital SET and Analog RESET Synaptic Characteristics of Sub-Tantalum Oxide Based neuromorphic Device. *Sci. Rep.* **2018**, *8* (1), 1228 DOI: [10.1038/s41598-018-19575-9](https://doi.org/10.1038/s41598-018-19575-9).

(71) Chang, T.; Jo, S. H.; Lu, W. Short-Term Memory to Long-Term Memory Transition in a Nanoscale Memristor. *ACS Nano* **2011**, *5* (9), 7669–7676.

(72) Sun, F.; Lu, Q.; Hao, M.; Wu, Y.; Li, Y.; Liu, L.; Li, L.; Wang, Y.; Zhang, T. An Artificial neuromorphic Somatosensory System with Spatio-Temporal Tactile Perception and Feedback Functions. *NPJ Flexible Electron.* **2022**, *6* (1), 72 DOI: [10.1038/s41528-022-00202-7](https://doi.org/10.1038/s41528-022-00202-7).

(73) Tang, X.; Yang, L.; Huang, J.; Chen, W.; Li, B.; Yang, S.; Yang, R.; Zeng, Z.; Tang, Z.; Gui, X. Controlling Sulfurization of 2D Mo<sub>2</sub>C Crystal for Mo<sub>2</sub>C/MoS<sub>2</sub>-Based Memristor and Artificial Synapse. *NPJ Flexible Electron.* **2022**, *6* (1), 93 DOI: [10.1038/s41528-022-00227-y](https://doi.org/10.1038/s41528-022-00227-y).

(74) Mahata, C.; Park, J.; Ismail, M.; Kim, S. Demonstration of Electronic and Optical Synaptic Properties Modulation of Reactively Sputtered Zinc-Oxide-Based Artificial Synapses. *J. Alloys Compd.* **2023**, *938*, No. 168539.

(75) Ismail, M.; Rasheed, M.; Mahata, C.; Kang, M.; Kim, S. Mimicking Biological Synapses with A-HfSiO<sub>x</sub>-Based Memristor: Implications for Artificial Intelligence and Memory Applications. *Nano Convergence* **2023**, *10* (1), 33 DOI: [10.1186/s40580-023-00380-8](https://doi.org/10.1186/s40580-023-00380-8).

(76) Lee, Y.; Park, J.; Chung, D.; Lee, K.; Kim, S. Multi-Level Cells and Quantized Conductance Characteristics of Al<sub>2</sub>O<sub>3</sub>-Based RRAM Device for neuromorphic System. *Nanoscale Res. Lett.* **2022**, *17* (1), 0–9.

(77) Kim, C.; Lee, Y.; Kim, S.; Kang, M.; Kim, S. Diverse Synaptic Weight Adjustment of Bio-Inspired ZrO<sub>x</sub>-Based memristors for neuromorphic System. *Mater. Sci. Semicond. Process.* **2023**, *157*, No. 107314.

(78) Lin, C. Y.; Chen, J.; Chen, P. H.; Chang, T. C.; Wu, Y.; Eshraghian, J. K.; Moon, J.; Yoo, S.; Wang, Y. H.; Chen, W. C.; Wang, Z. Y.; Huang, H. C.; Li, Y.; Miao, X.; Lu, W. D.; Sze, S. M. Adaptive Synaptic Memory via Lithium Ion Modulation in RRAM Devices. *Small* **2020**, *16* (42), 2003964 DOI: [10.1002/smll.202003964](https://doi.org/10.1002/smll.202003964).

(79) Kim, J.; Kim, D.; Min, K. K.; Kraatz, M.; Han, T.; Kim, S. Effect of Al Concentration on Ferroelectric Properties in HfAlO<sub>x</sub>-Based Ferroelectric Tunnel Junction Devices for Neuroinspired Applications. *Adv. Intell. Syst.* **2023**, *5* (8), 2300080 DOI: [10.1002/aisy.202300080](https://doi.org/10.1002/aisy.202300080).

(80) Ismail, M.; Mahata, C.; Kim, S. Electronic Synaptic Plasticity and Analog Switching Characteristics in Pt/TiO<sub>x</sub>/AlO<sub>x</sub>/AlTaON/TaN Multilayer RRAM for Artificial Synapses. *Appl. Surf. Sci.* **2022**, *599*, No. 153906.

(81) Kim, D.; Jeon, B.; Lee, Y.; Kim, D.; Cho, Y.; Kim, S. Prospects and Applications of Volatile memristors. *Appl. Phys. Lett.* **2022**, *121* (1), No. 010501, DOI: [10.1063/5.0093964](https://doi.org/10.1063/5.0093964).

(82) Kim, J.; Choi, J. H.; Kim, S.; Choi, C.; Kim, S. Transition of Short-Term to Long-Term Memory of Cu/TaO<sub>x</sub>/CNT Conductive Bridge Random Access Memory for neuromorphic Engineering. *Carbon* **2023**, *215*, No. 118438.

(83) Laborieux, A.; Ernoult, M.; Hirtzlin, T.; Querlioz, D. Synaptic Metaplasticity in Binarized Neural Networks. *Nat. Commun.* **2021**, *12* (1), 1–12.

(84) Zhu, W.; Li, J. Synaptic Learning and Forgetting Behavior in Ag/AlN/Al Memristor Wit Annealing Effect. *IEEE Access* **2019**, *7*, 163358–163364.

(85) Wang, Z. Q.; Xu, H. Y.; Li, X. H.; Yu, H.; Liu, Y. C.; Zhu, X. J. Synaptic Learning and Memory Functions Achieved Using Oxygen Ion Migration/Diffusion in an Amorphous InGaZnO Memristor. *Adv. Funct. Mater.* **2012**, *22* (13), 2759–2765.

(86) Yin, X. B.; Yang, R.; Xue, K. H.; Tan, Z. H.; Zhang, X. D.; Miao, X. S.; Guo, X. Mimicking the Brain Functions of Learning, Forgetting and Explicit/Implicit Memories with SrTiO<sub>3</sub>-Based memristive Devices. *Phys. Chem. Chem. Phys.* **2016**, *18* (46), 31796–31802.

(87) So, H.; Lee, J.; Mahata, C.; Kim, S.; Kim, S. Synaptic Properties and Short-Term Memory Dynamics of TiO<sub>2</sub>/WO<sub>x</sub> Heterojunction Memristor for Reservoir Computing. *Adv. Mater. Technol.* **2024**, *9*, 2301390.

(88) Seo, S.; Kang, B. S.; Lee, J. J.; Ryu, H. J.; Kim, S.; Kim, H.; Oh, S.; Shim, J.; Heo, K.; Oh, S.; Park, J. H. Artificial van Der Waals Hybrid Synapse and Its Application to Acoustic Pattern Recognition. *Nat. Commun.* **2020**, *11* (1), 3936 DOI: [10.1038/s41467-020-17849-3](https://doi.org/10.1038/s41467-020-17849-3).

(89) Li, D.; Ren, H.; Chen, Y.; Tang, Y.; Liang, K.; Wang, Y.; Li, F.; Liu, G.; Meng, L.; Zhu, B. Bidirectionally Photoresponsive Optoelectronic Transistors with Dual Photogates for All-Optical-Configured neuromorphic Vision. *Adv. Funct. Mater.* **2023**, *2303198* DOI: [10.1002/adfm.202303198](https://doi.org/10.1002/adfm.202303198).

(90) Park, Y.; Kim, M. K.; Lee, J. S. Ion-Gating Synaptic Transistors with Long-Term Synaptic Weight Modulation. *Journal of Materials Chemistry C* **2021**, *9* (16), 5396–5402.

(91) Zhong, Y.; Tang, J.; Li, X.; Gao, B.; Qian, H.; Wu, H. Dynamic Memristor-Based Reservoir Computing for High-Efficiency Temporal Signal Processing. *Nat. Commun.* **2021**, *12* (1), 408 DOI: [10.1038/s41467-020-20692-1](https://doi.org/10.1038/s41467-020-20692-1).

(92) Kim, D.; Kim, J.; Yun, S.; Lee, J.; Seo, E.; Kim, S. Ferroelectric Synaptic Devices Based on CMOS-Compatible HfAlO<sub>x</sub> for neuromorphic and Reservoir Computing Applications. *Nanoscale* **2023**, *15* (18), 8366–8376.

(93) Ding, G.; Chen, R. S.; Xie, P.; Yang, B.; Shang, G.; Liu, Y.; Gao, L.; Mo, W. A.; Zhou, K.; Han, S. T.; Zhou, Y. Filament Engineering of Two-Dimensional h-BN for a Self-Power Mechano-Nociceptor System. *Small* **2022**, *18* (16), 2200185 DOI: [10.1002/smll.202200185](https://doi.org/10.1002/smll.202200185).

(94) Ryu, H.; Kim, S. Implementation of a Reservoir Computing System Using the Short-Term Effects of Pt/HfO<sub>2</sub>/TaO<sub>x</sub>/TiN memristors with Self-Rectification. *Chaos, Solitons Fractals* **2021**, *150*, No. 111223.

(95) Farronato, M.; Mannocci, P.; Melegari, M.; Ricci, S.; Compagnoni, C. M.; Ielmini, D. Reservoir Computing with Charge-Trap Memory Based on a MoS<sub>2</sub> Channel for neuromorphic Engineering. *Adv. Mater.* **2023**, *35* (37), 2205381 DOI: [10.1002/adma.202205381](https://doi.org/10.1002/adma.202205381).