# A Wideband Millimeter-Wave CMOS Receiver Using a Reconfigurable Low-Noise Amplifier With a 3-Winding Transformer Load

Mohammad Ghaedi Bardeh<sup>✉</sup>, *Graduate Student Member, IEEE*,

Mohamad Mahdi Rajaei Rizi<sup>✉</sup>, *Graduate Student Member, IEEE*, Navid Naseh<sup>✉</sup>, *Member, IEEE*,

Jeyanandh Paramesh<sup>✉</sup>, *Senior Member, IEEE*, and Kamran Entesari<sup>✉</sup>, *Senior Member, IEEE*

**Abstract**—This article presents a CMOS millimeter-wave (mm-wave) wideband image-reject (IR) receiver using a reconfigurable low-noise amplifier (LNA) with a 3-winding transformer load in 22-nm fully depleted silicon-on-insulator (FDSOI). The complete analysis of the proposed 3-winding transformer load is presented, where the location of the poles and zeros and also the equation for the first port, self-impedance ( $Z_{11}$ ) are calculated and a design strategy along with a comparison with the conventional double-tuned transformer load is performed. Based on this approach, an mm-wave wideband/reconfigurable receiver is presented with three major contributions including: 1) wideband/reconfigurable frequency mode operation; 2) canceling interfere signals right after LNA to relax mixer linearity requirements; and 3) on-chip image-rejection using a three-stage resistor-capacitor (RC)-capacitor-resistor (CR) filter with tunable resistors for optimum operation. The 3-dB bandwidth in wideband mode is from 21.5 to 32.5 GHz with a peak gain of 45.5 dB at 22.5 GHz, and for both low-frequency and high-frequency reconfigurable modes, it is from 21.5 to 26.5 GHz with a peak gain of 45.45 dB at 22 GHz and from 27 to 32 GHz with a peak gain of 46.58 dB at 29 GHz, respectively. The measured noise figure (NF) value shows a minimum of 2.9 dB at 30 GHz. The image rejection is better than 30 dB for the 19–34-GHz range and the minimum  $OP_{1dB}$  is  $-2.8$  dBm over the same frequency range. The entire chip has a power consumption of 94.8 mW with the dimensions of  $2.331 \times 0.756$  mm excluding the pads.

**Index Terms**—Double-tuned transformer, fully depleted silicon-on-insulator (FDSOI) CMOS,  $I/Q$  local oscillator (LO) distribution, image rejection, low-noise amplifier (LNA), mixer, resistor-capacitor (RC)-capacitor-resistor (CR) poly-phase filter (PPF), 3-winding transformer load, wideband receiver.

## I. INTRODUCTION

THE growth of 5G technology marks a significant milestone in the evolution of wireless communications, promising high speed, reliability, and efficiency. In addition, millimeter-wave (mm-wave) frequency bands defined for 5G applications such as n257 (26.50–29.50 GHz), n258

Received 23 June 2024; revised 5 September 2024 and 21 October 2024; accepted 19 November 2024. This work was supported by the National Science Foundation (NSF) under Award 2116498. (Mohammad Ghaedi Bardeh and Mohamad Mahdi Rajaei Rizi are co-first authors.) (Corresponding author: Mohammad Ghaedi Bardeh.)

The authors are with the Department of Electrical and Computer Engineering, Texas A&M University, College Station, TX 77843 USA (e-mail: m.ghaedi95@tamu.edu).

Color versions of one or more figures in this article are available at <https://doi.org/10.1109/TMTT.2024.3506657>.

Digital Object Identifier 10.1109/TMTT.2024.3506657

(24.25–27.5 GHz), n259 (39.5–43.5 GHz), n260 (37–40 GHz), and n261 (27.5–28.35 GHz) [1] further increase the capacity of wireless communications and offer wider bandwidths compared to lower frequency bands. Therefore, the implementation of wideband phased array systems emerges as a critical enabler for 5G, particularly in exploiting the mm-wave spectrum. In order to be able to exploit all the positive features of 5G communications, the design and implementation of wideband (20–44 GHz) receivers are crucial [2].

Wideband mm-wave receivers covering the mentioned frequency range have been extensively researched in the literature [1], [2], [3], [4], [5], [6], [7], [8], [9], [10], which address both circuit- and architecture-level challenges. In mm-wave frequencies, low-noise amplifier (LNA) as the first block of the reception chain should address requirements of gain, noise, linearity, and input return loss of  $>10$  dB over an extensive bandwidth. The use of 3-winding transformers has been recently increased as the primary method to fulfill the wideband performance of the LNA; Ke et al. [11] highlight significant advancements in mm-wave LNA design by utilizing 3-winding transformer architectures to enhance performance across a broad frequency range. This work introduces a tricoupled transformer to achieve simultaneous  $G_m$  boosting and enhanced noise cancellation, resulting in a low noise figure (NF) of 3.8 dB and a peak gain of 22.4 dB, making it highly effective for mm-wave applications. Similarly, Kim et al. [12] leverage a 3-winding transformer combined with large transistors, achieving an ultralow NF of 2.2–3.2 dB over 32–46 GHz, while offering superior gain and efficient power consumption. Zou et al. [13] incorporate a capacitor-assisted triple-winding transformer, further enhancing design flexibility and allowing independent control of coupling coefficients, which leads to a remarkable 0.8–1.5-dB NF and minimized gain ripple of  $\pm 0.75$  dB across a 6–12-GHz bandwidth. Across all three designs, the strategic use of 3-winding transformers enables improved noise suppression, broader bandwidth, and efficient gain control, making these LNAs ideal for high-performance wideband applications. In this work, the primary focus is on leveraging the 3-winding transformer to implement an mm-wave LNA that incorporates two auxiliary paths alongside the

main path. These auxiliary paths introduce a configurability feature, allowing for improved  $OP_{1dB}$  performance and extended bandwidth when operating in wideband mode. This innovative use of the 3-winding transformer enhances both linearity and bandwidth, addressing the requirements of high-performance mm-wave applications. While having a wideband LNA, mixer, and quadrature local oscillator (LO) distribution are the main circuit-level challenges of realizing wideband receivers, coming up with an architecture that incorporates acceptable image-rejection and unwanted in-band/out-of-band interfering signal cancellations over a wide frequency band of operation is also challenging [3], [4]. To address the above challenges, a wideband mm-wave receiver using a wideband/reconfigurable LNA and on-chip image-rejection circuitry with a high image-rejection ratio (IRR) is presented. In this work, which is the expansion of [14], a reconfigurable LNA utilizing a novel 3-winding transformer load is proposed, which allows both the LNA and receiver to function in two wideband and reconfigurable modes, enabling out-of-band interfering signal rejection right after the LNA to relax the linearity requirements of the mixer stage. To the authors' knowledge, the complete analysis of the proposed 3-winding transformer load along with the location of poles and zeros and the equation for the  $Z_{11}$  of the first port is presented, and a design strategy, as well as a comparison with the conventional double-tuned transformer, is provided in this article. Based on this load, an mm-wave wideband/reconfigurable receiver is presented with three major contributions as follows: 1) wideband/reconfigurable frequency mode operation using a novel 3-winding transformer load in the LNA; 2) in-band and out-of-band interference cancellation using the LNA's reconfigurable functionality to prevent the proposed receiver from saturation; and 3) incorporation of an on-chip image-rejection circuitry based on a three-stage resistor-capacitor (RC)-capacitor-resistor (CR) filter with tunable resistors for optimum performance.

There have been several works in the literature to realize wideband mm-wave receivers with high IRR and interference cancellation. In [8], [9], and [10], a common approach is used to achieve wideband operation by using the conventional double-tuned transformer. Although this approach results in a sufficient wideband operating frequency, it does not provide the reconfigurability option. In terms of image rejection, Mondal et al. [8] use four cascaded bandpass loads, while Mondal and Paramesh [9] use an image-reject (IR) heterodyne architecture based on the Cartesian complex-weighting operation. In [6], an mm-wave wideband receiver is presented using a double-tuned transformer as the load of the LNA, but Port 1 is utilized as the output ( $Z_{11}$ ) instead of Port 2 ( $Z_{21}$ ), achieving wider bandwidth compared to the conventional double-tuned transformer; however, the image rejection is performed using off-chip components. In [3], a 20–44-GHz receiver with >75-dB IRR is presented. The receiver takes advantage of using an ultra-wideband three-stage LNA and has selected RF, LO, and intermediate frequency (IF) in a way that the image signal is below 12 GHz; therefore, it utilizes a high-pass filter as the input matching network of the LNA to suppress the image signal and enhance

IRR. However, the disadvantage of this architecture is that the downconversion unit is not fully realized on-chip. In [2], a 20–42-GHz receiver with on-chip image rejection circuitry is presented, where the enhancement of IRR is achieved by using a low-pass filter after the mixer; however, it does not provide a solution to cancel the interference signals. In [4], a 24.5–43.5-GHz receiver employs a wideband LNA and utilizes a two-stage transformer-based  $IQ$  network, achieving a minimum of 30-dB IRR over the entire frequency band of operation, but the area of the  $IQ$  network is relatively bulky compared to other approaches for implementing  $IQ$  networks, such as RC-CR filters. In [15], a reconfigurable dual-band LNA is presented, which takes advantage of magnetic–electric hybrid coupling technology. This technology includes a conventional double-tuned transformer, where a third inductor with a series switch to ground is coupled with the double-tuned transformer. When the switch is off, the structure operates in the low-frequency mode, and when the switch is on, the effective value of the inductors of the double-tuned transformer reduces, resulting in a smaller inductor value and allowing operation in the high-frequency mode. The disadvantage of this approach is that it works only in reconfigurable mode and cannot operate in wideband mode.

In this work, a CMOS wideband mm-wave receiver covering 21.5–32.5 GHz with on-chip image rejection circuitry and reconfigurable LNA is presented with wideband/reconfigurable operation. Because of its reconfigurable nature, the receiver cancels the effect of in-band/out-of-band interfering signals right after the LNA, preventing the forthcoming receiver blocks from saturation. A complete analysis of the proposed 3-winding transformer load of the reconfigurable LNA is also presented.

## II. 3-WINDING TRANSFORMER LOAD

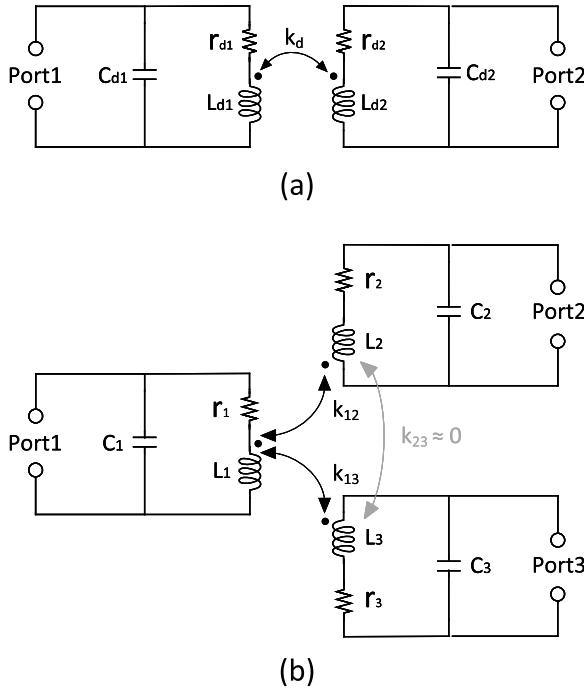

Shaping the frequency response of an amplifier is accomplished by its load [16]. The most popular load in wideband amplifiers is the conventional double-tuned transformer, as shown in Fig. 1(a), and has been used extensively in the literature [6], [17], [18], [19], [20], [21].

The frequency response of the double-tuned transformer has two poles and one zero, which is between the two poles; therefore, it has two peaks and one null in the middle of the two peaks. The values of the two poles and one zero of the double-tuned transformer in Fig. 1(a) are given by [6]

$$\omega_{p1,D-p2,D} = \frac{\omega_{d2}}{\sqrt{1 \pm k_d}} \quad (1)$$

$$\omega_{z,D} = \frac{\omega_{d2}}{\sqrt{1 - k_d^2}} \quad (2)$$

where  $\omega_{d2} = (1/(L_{d2}C_{d2}))^{1/2}$  and for simplicity  $\omega_{d1} = \omega_{d2}$ , ( $L_{d1}C_{d1} = L_{d2}C_{d2}$ ). The design approach is as follows: first  $\omega_{d1}$  is specified, and then by increasing the coupling factor ( $k_d$ ), the bandwidth and ripple are increased. Although the double-tuned transformer is capable of covering a fairly wide frequency range, there are two main problems with this load: 1) in ultra-wideband situations, the performance is degraded by increasing the ripple in the frequency response,

Fig. 1. (a) Conventional double-tuned transformer. (b) Proposed 3-winding transformer.

with some efforts to marginally extend its bandwidth [6] by using Port 1 as the output port instead of Port 2; however, the bandwidth extension is still limited and 2) the double-tuned transformer's reconfigurability, utilized via tunable capacitors, is also limited.

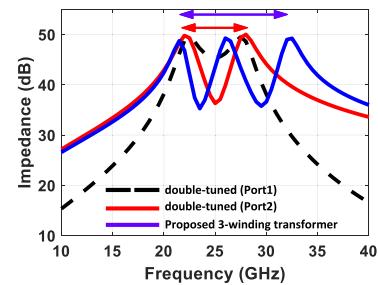

In this work, a wideband reconfigurable load is presented for the LNA part of the receiver that takes advantage of a 3-winding transformer shown in Fig. 1(b). In this configuration, the primary inductor ( $L_1$ ) is coupled with two secondaries ( $L_2$  and  $L_3$ ), and the coupling factors are  $k_{12}$  and  $k_{13}$ , respectively, while the two secondaries are not coupled ( $k_{23} \approx 0$ ). By comparing the two loads [Fig. 1(a) and (b)], it can be intuitively observed that the proposed reconfigurable load has a wider bandwidth compared to the double-tuned transformer, as it consists of three poles (three peaks) and two zeros (two nulls) with the zeros located between the poles. Fig. 2 shows the simulated frequency response comparison of three scenarios where, in all of them, Port 1 is excited by ac. The black dashed line shows  $Z_{21}$ , the red line shows  $Z_{11}$  of the double-tuned transformer, and the blue line shows  $Z_{11}$  of the proposed 3-winding transformer. It can be seen that the proposed transformer has at least 80% wider bandwidth; therefore, this structure can be used in ultra-wideband applications.

To prove the above statement mathematically, the number and location of poles and zeros are quantitatively specified in the following. The transfer function of  $Z_{11}$  for Port 1 of the proposed load in Fig. 1(b) has a polynomial in its denominator of order 6, and finding the closed-form solutions for the poles and zeros of  $Z_{11}$  in this case is much more challenging compared to the double-tuned transformer. Therefore, to simplify the problem, four assumptions are made: 1) the primary inductor ( $L_1$ ) is coupled to the two secondaries ( $L_2$  and  $L_3$ ); 2) the two secondary inductors

Fig. 2. Frequency response comparison of double-tuned and proposed 3-winding transformers. ( $Y$ -axis represents the magnitude of the corresponding impedance in  $\Omega$ . The black dashed, red, and blue curves represent  $Z_{21}$ ,  $Z_{11}$  of double-tuned transformer, and  $Z_{11}$  of the proposed 3-winding transformer, respectively.)

( $L_2$  and  $L_3$ ) are not coupled; 3) the transfer function of Port 1 ( $Z_{11}$ ) is considered; and 4) to find the location of poles and zeros, and for simplicity, the quality factors of the three tanks are assumed to be infinite at first step. As proved in Appendix A, the zero locations can be written as follows:

$$\begin{aligned}\omega_{z1,T} &= \omega_2 \times \frac{\sqrt{1-k^2}}{\sqrt{1-2k^2}} \\ \omega_{z2,T} &= \omega_3 \times \frac{\sqrt{1-k^2}}{\sqrt{1-2k^2}}.\end{aligned}\quad (3)$$

The above equation provides some interesting insights about the proposed transformer: 1) the locations of the two zeros are almost equal to the resonant frequencies of the secondaries and 2) if two zeros are intended, the resonant frequencies of the two secondaries cannot be equal. This feature is added due to the presence of two secondaries compared to the conventional double-tuned transformer, where for simplicity, the resonant frequencies of the primary and secondary are assumed to be equal ( $L_{d1}C_{d1} = L_{d2}C_{d2}$ ), which introduces an additional degree of freedom, since in the proposed load  $L_1C_1 = L_2C_2$  but  $L_1C_1 \neq L_3C_3$ .

The poles as proved in Appendix B can be written as follows:

$$\begin{aligned}\omega_{p1,T} &\approx \omega_1 \sqrt{1-k} \\ \omega_{p2,T} &= \omega_2 \frac{\left(\frac{\omega_1}{\omega_{p1,T}}\right) \left(\frac{\omega_3}{\omega_{p3,T}}\right)}{\sqrt{1-2k^2}} \\ \omega_{p3,T} &\approx \omega_3 \sqrt{0.5 \left(\frac{1}{\xi_3^2} + 1\right)} \sqrt{(1 + \sqrt{2k})(1 + k^2)}.\end{aligned}\quad (4)$$

The results for  $\omega_{p3}$  in (4) imply that its location has a linear dependence on  $\omega_3$  and is also dependent on coupling factor and  $\xi_3$ .

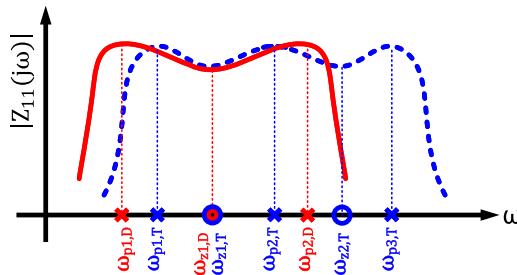

Fig. 3 shows a comparison between the pole-zero locations of the conventional double-tuned transformer and the proposed 3-winding transformer, where  $\omega_{d1} = \omega_{d2} = \omega_1 = \omega_2$  and  $\omega_1 \neq \omega_3$  (to have two distinct zeros). Therefore, for the conventional one, two poles are split compared to  $\omega_1$  with the factors of  $(1/(1 \pm k)^{1/2})$ , and the zero is between the two split poles, with its value being almost equal to  $\omega_1$ . For the proposed 3-winding transformer, due to the freedom of choosing  $\xi_3^2$ , the bandwidth coverage can be significantly higher than that of the double-tuned transformer. Another useful observation, as shown in

Fig. 3. Effect of the location of poles and zeros for double-tuned transformer and the proposed triple-coupled transformer on the frequency response of  $Z_{11}$  with the assumption of  $\omega_1 = \omega_2$ .

Fig. 3, is the equality (with the condition of  $k \ll 1$ ) of the first pole ( $\omega_{p1}$ ) for both loads. Additionally, similar to the

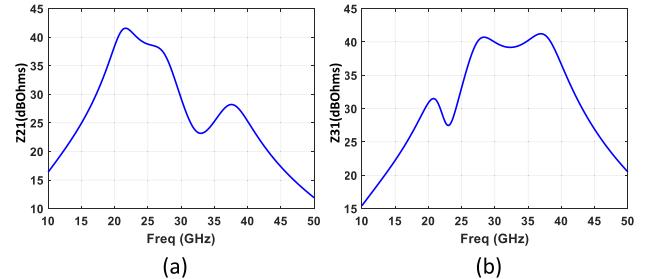

Fig. 5. ADS simulations of the frequency response including the effect of finite  $Q$  of the inductors. (a) Magnitude of  $Z_{21}$  in  $\text{dB}\Omega$ . (b) Magnitude of  $Z_{31}$  in  $\text{dB}\Omega$ .

double-tuned transformer, the zeros for the proposed load are near  $\omega_2$  and  $\omega_3$ .

For the first-order approximation, the effects of the limited quality factor of the inductors are neglected, yielding zeros and poles provided in (3) and (4), respectively. While these equations disregard the finite quality factor, they serve as an acceptable starting point for managing the location of zeros and poles in the design. However, it is essential to assess the accuracy of this approximation. In this regard, a general frequency response for  $Z_{11}(s)$  of the 3-winding transformer with limited quality factors for inductors is derived in Appendix C.

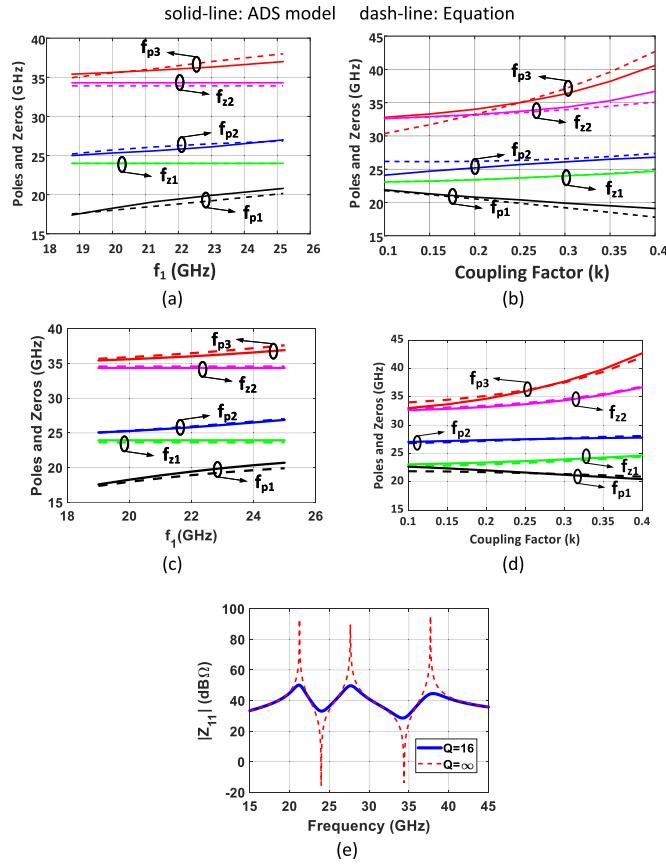

Fig. 4 shows the comparison of the pole–zero frequencies of the 3-winding transformer for different cases. Fig. 4(a) and (b) depicts the poles and zeros as a function of  $f_1(\omega_1)$  since all poles and zeros can be expressed in terms of  $\omega_1$ , and as a function of the coupling factor ( $k$ ), respectively. From Fig. 4(a) and (b), it is evident that the approximations utilized to simplify and find general formulas for poles are valid and do not significantly affect accuracy. Moreover, Fig. 4(c) and (d) displays the poles and zeros for the case of finite quality factor ( $Q = 16$ ). The dashed lines represent values derived by MATLAB poles and zeros using the  $Z_{11}(s)$  transfer function obtained in (28), while the solid lines display the advanced design system (ADS) simulation results. As shown, there is a close match between the simulation and calculation values, validating the derivations presented in Appendix C. Furthermore, Fig. 4(e) illustrates the simulated magnitude of  $Z_{11}$  for both infinite and finite quality factors in the 3-winding transformer. As observed, the location of the peaks (poles) and notches (zeros) are in close proximity for both cases. Thus, zeros and poles provided in (3) and (4) offer a reliable starting point for designing a 3-winding transformer as a load for a wideband amplifier, effectively shaping the frequency response.

Another interesting feature of the proposed 3-winding transformer is that the load can be reconfigured. By choosing the output voltage at Port 2 or Port 3, the frequency responses of  $Z_{21}$  and  $Z_{31}$  in Fig. 5(a) and (b) are achieved, which can be used to cancel the interfering signals, thus increasing the linearity of the system.

### III. WIDEBAND RECEIVER

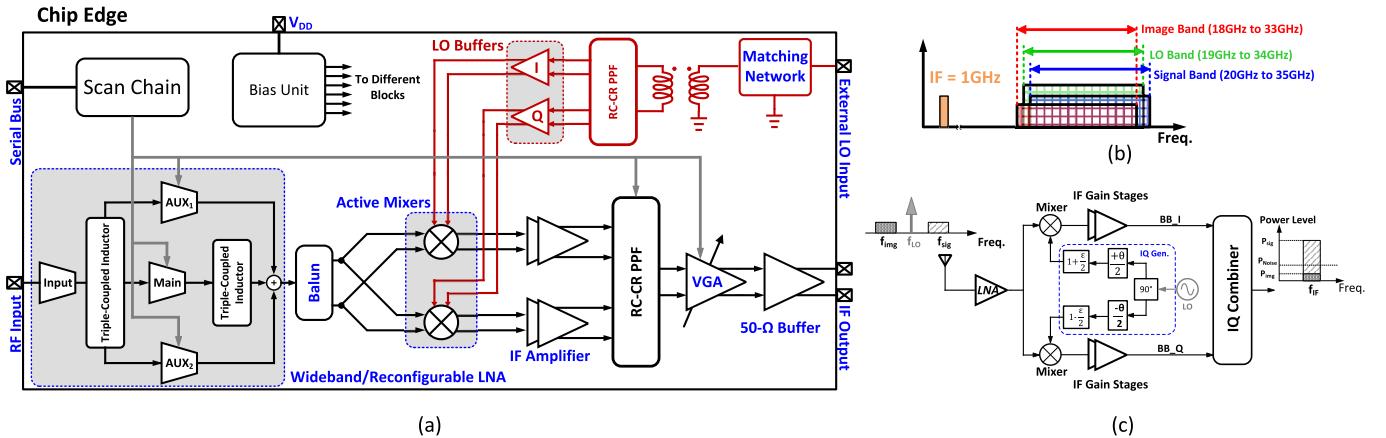

The previously mentioned techniques were utilized to design a wideband, reconfigurable LNA incorporated in a quadrature

Fig. 6. (a) Block diagram of the receiver chip. (b) Frequency plan of the receiver. (c) Image existence at the output of the receiver due to gain and phase mismatch of the LO *I/Q* paths.

IR receiver. Fig. 6(a) illustrates the block diagram of the receiver. The LNA covers the frequency range of 20–35 GHz. Subsequently, the LNA output signal drives two *I/Q* active downconvert mixers. A single-ended external LO is fed into the chip, and an RC-CR poly-phase filter (PPF) is employed to generate the quadrature LO. Then, the downconverted *I/Q* signals, ranging from 500 MHz to 1.5 GHz, are combined by another PPF for image removal; the bandwidth of the IF circuitry is 1 GHz covering multiple channels occupied by 5G 64-quadratic-amplitude modulation (QAM) signals with 100-MHz bandwidth [22]. The frequency plan of the proposed receiver is presented in Fig. 6(b); as can be seen in this figure, the LO is low-side injected. As a result, the image band is 1 GHz below the LO band, while the signal band is 1 GHz above the LO band.

#### A. System-Level Analysis

Fig. 6(c) demonstrates the simplified block diagram of the IR receiver. The gain and phase imbalances between the *I* and *Q* paths of the receiver affect the IRR and contribute to receiver performance degradation. The spectrum at the output consists of two main undesired components, including noise and image signals. For the sake of analysis, the presence of the image signal is considered as a noise floor increase, and the SNR<sub>total</sub> is related to SNR<sub>Noise</sub> and SNR<sub>Image</sub> by the following equation [22]:

$$\text{SNR}_{\text{total}} = \frac{1}{\frac{1}{\text{SNR}_{\text{Noise}}} + \frac{1}{\text{SNR}_{\text{Image}}}}. \quad (5)$$

Assuming a 100-MHz modulation bandwidth and  $-70$ -dBm sensitivity for the receiver, a minimum SNR<sub>total</sub> of 21 dB for 64-QAM modulation is required [22]. Thus, considering the following equation, the required NF<sub>RX</sub> is 3 dB:

$$P_{\text{sen}} = -174 + 10\log(\text{BW}) + \text{NF}_{\text{RX}} + \text{SNR}_{\text{total}}. \quad (6)$$

Assuming a 3-dB margin for the receiver, the following criterion should be fulfilled:

$$\text{IRR} = \text{SNR}_{\text{Noise}} + 3 \text{ dB}. \quad (7)$$

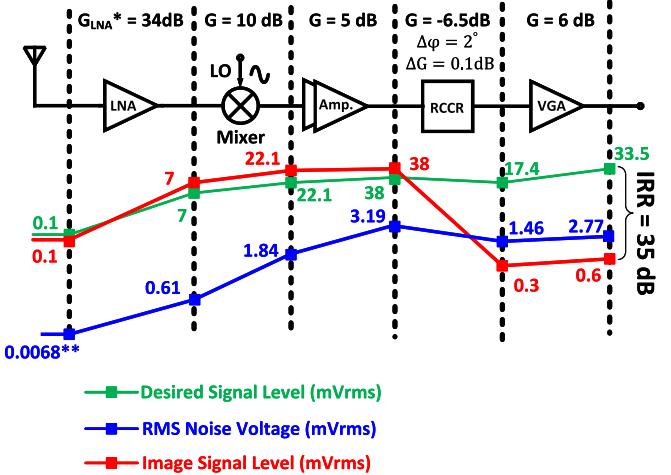

Fig. 7. Desired signal (input power level is  $-70$  dBm), rms voltage noise density, image voltage level diagram, and required specifications for the IRR  $> 35$  dB. (Values are based on simulation.) \*The LNA gain reported includes a source (antenna) impedance of  $50 \Omega$ . \*\*This value reported for rms noise voltage is an equivalent of the KTB power level.

By substituting (7) into (5), we arrive at

$$\text{IRR} \geq 26 \text{ dB}. \quad (8)$$

Because of the process voltage temperature (PVT) variations of RC-CR components, the targeted value for the IRR is 30 dB over the entire RF bandwidth, resulting in a required *I/Q* gain and phase mismatch of 0.1 dB and  $2^\circ$ , respectively.

Fig. 7 displays the simulated root-mean-squared (rms) noise voltage, desired signal, and image level variations over different blocks of the proposed receiver. The noise voltage after the RC-CR drops because the noise at the frequency of the image band is attenuated. Besides, as illustrated in Fig. 7, the SNR<sub>Noise</sub> and SNR<sub>Image</sub> are 21.7 and 35 dB, respectively. According to (5), the resulted SNR<sub>total</sub> is  $\approx 21$  dB, thereby confirming the required SNR for the targeted modulation. It is noteworthy that Fig. 7 depicts a scenario where the signal power level is equal to the sensitivity of the receiver, and noise predominates over the image. However, as the signal and image levels increase, the image contribution in (5) becomes more significant, while the impact of noise diminishes due

Fig. 8. Schematic of the proposed LNA used in the receiver.

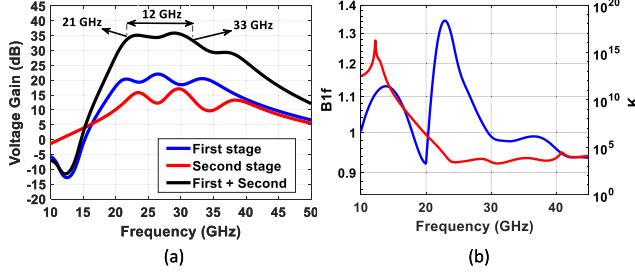

Fig. 9. Postlayout simulation results of LNA. (a) Voltage gain for the first and second stages [14]. (b) Stability factors across 15–45 GHz.

to the higher level of the desired signal. Thus, the targeted  $>30$ -dB value for IRR is a sensible choice.

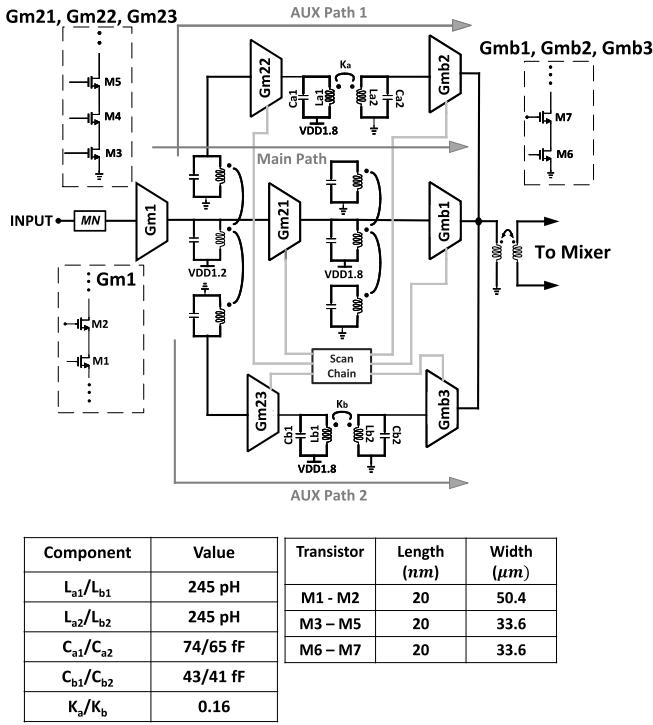

### B. Wideband/Reconfigurable LNA

To take advantage of the two main features (wideband, reconfigurable) of the proposed 3-winding transformer load, the block diagram of the proposed mm-wave reconfigurable single-ended LNA is shown in Fig. 8. Depending on the output port of the 3-winding transformer load, the LNA has three paths: 1) the main path where the output voltage is from Port 1; 2) auxiliary Path 1; and 3) auxiliary Path 2, where the output voltage is from Ports 2 and 3 of the 3-winding transformer, respectively. When the main path is on and the two other paths are off, the LNA operates in wideband mode ( $Z_{11}$ , according to the 3-winding load). In wideband mode, the proposed LNA has three stages: the first two stages consist of two cascaded  $G_m$  cells ( $G_{m1}$  and  $G_{m21}$ ) with two 3-winding transformer loads to achieve a flat response over the frequency band of operation. After these two stages, there is a buffer stage realized with a  $G_m$  cell ( $G_{mb1}$ ) followed by a  $50\Omega$  single-ended wideband output matching network.

When auxiliary Path 1 (2) is on and the other paths are off, the low (high) frequencies of the wideband response are selected. To better shape the frequency response and provide better out-of-band rejection, two conventional double-tuned transformers are cascaded with the first stage of auxiliary Path 1 (2), and then, the signal is conveyed to the output through a buffer stage.  $G_{m1}$  uses a common-source (CS) cascode structure with source-degeneration inductance for optimized noise performance and input return loss. To achieve better isolation between the input and output, the  $G_m$  cells in the second stages,  $G_{m21}$ ,  $G_{m22}$ , and  $G_{m23}$ , are realized using three cascode transistors, and finally, the buffer stage uses a conventional cascode structure. The detailed information about the size of transistors and the values of passive elements in the proposed reconfigurable LNA is reported in the tables shown in Fig. 8. The input matching is designed to provide a zero at low frequencies to filter unwanted signals as well as provide a better than  $-10$ -dB input return loss for the entire frequency band of interest. The interface between the LNA and mixer is realized through a buffer, as shown in Fig. 8, and the interface load is a conventional double-tuned transformer. Postlayout simulation results of the proposed LNA voltage gain are shown in Fig. 9(a), where a 3-dB frequency band from 21 to 33 GHz is achieved. Additionally, postlayout simulations show that the LNA NF varies between 2.5 and 3.5 dB within this bandwidth. Also, Fig. 9(b) shows the simulated stability factors of the LNA across the frequency of 10–45 GHz; two stability factors of  $K_f$  and  $B1f$  are utilized to examine the stability condition of the LNA. It can be inferred from Fig. 9(b) that  $K_f > 1$  and  $B1f > 0$ , ensuring the stability of the LNA.

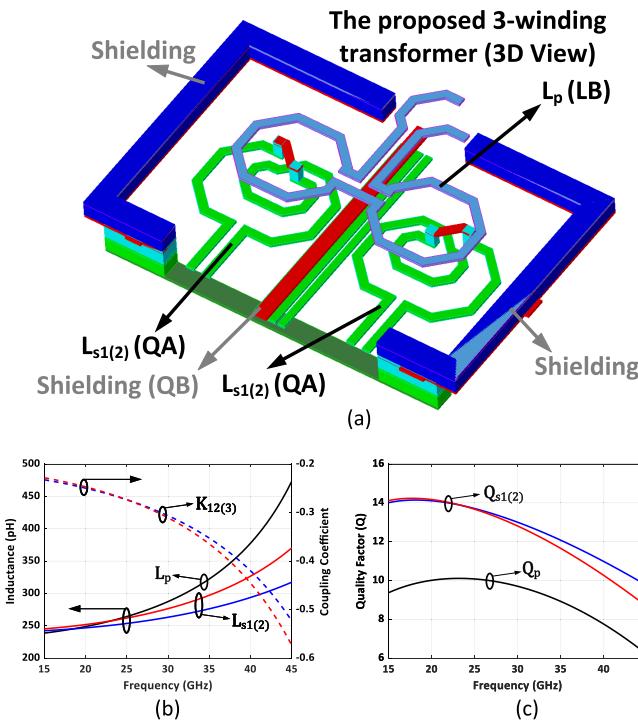

The 3-D layout view of the proposed 3-winding transformer is shown in Fig. 10(a), where the top three metal layers (LB, QB, and QA) in the stack-up of Global Foundries 22-nm CMOS fully depleted silicon-on-insulator (FDSOI) [21] are used. The primary inductor is implemented in the LB metal layer, and to reduce the parasitic coupling between the primary and the secondaries, the QA metal layer is used to design symmetric secondary inductors, with QA and QB ground metal layers placed between the two secondaries to prevent coupling between them. Additionally, Fig. 10(a) and (b) shows the inductance, coupling factor, and quality factor values of two 3-winding transformers, which are optimized for flat frequency response. The coupling and quality factors are very close to each other for each case. The inductances for the second stage are slightly different from those of the first stage.

To ensure freedom in the measurement process, all the biasing networks and capacitors are tunable. The tunable capacitors are designed to ensure an optimized  $C_{ON}/C_{OFF} \approx 3$  ratio and the maximum available quality factor.

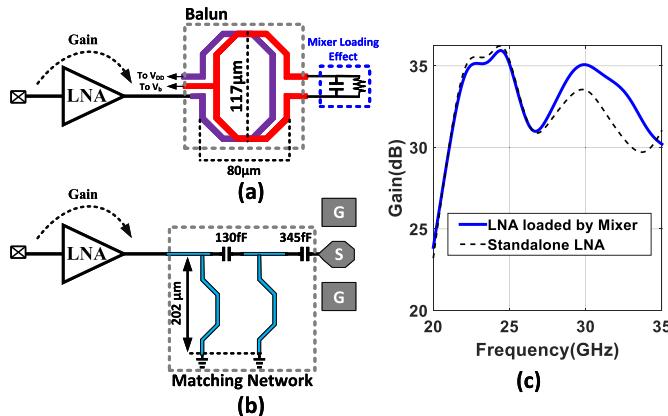

The LNA designed in [14] is integrated into the proposed receiver. However, the mixer topology as will be discussed later uses differential signaling, which necessitates loading the LNA with a balun to properly interface with the mixers. Fig. 11(a) shows the layout of the balun, with its secondary side connected to a resistive–capacitive network impedance to compensate for the inductance of the balun. Fig. 11(b), on the other hand, displays the structure employed in [14] for matching the output port to  $50\Omega$ . As illustrated in

Fig. 10. (a) Three-dimensional view layout of the proposed 3-winding transformer. The characteristics of the 3-winding transformer used in the first. (b) Inductance value and coupling factor for the first stage. (c) Quality factor ( $Q$ ) of the first stage.

Fig. 11(c), the simulated gain of the LNA in both cases is close, indicating that the interface does not negatively impact the gain performance of the LNA.

### C. RF Mixer

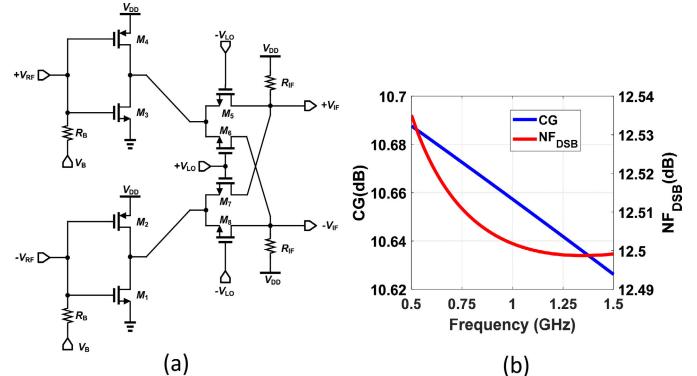

Fig. 12(a) shows the schematic of the employed double-balanced Gilbert cell active mixer [23]. The differential input RF signal drives the CMOS  $G_m$  cells ( $M_1-M_4$ ), and the switching quad transistors ( $M_5-M_8$ ), controlled by a sinusoidal LO, commutate the RF current between two resistors ( $R_{IF}$ ) to downconvert the input RF signal. With a given  $g_m$  for  $M_1$  or  $M_3$ , the inclusion of pMOS transistors aids in reducing dc flowing through switching quad and  $R_{IF}$ , as a portion of the bias current of  $M_1/M_3$  is provided by  $M_2/M_4$ . As a result, the

Fig. 12. (a) Schematic of the double balanced mixer with nMOS-pMOS  $G_m$  cells. [( $W/L$ )<sub>1,3</sub> = 19.2  $\mu\text{m}$ /20 nm, ( $W/L$ )<sub>2,4</sub> = 4.48  $\mu\text{m}$ /20 nm, ( $W/L$ )<sub>5-8</sub> = 5.4  $\mu\text{m}$ /20 nm,  $R_{IF}$  = 250  $\Omega$ ,  $I_{D1,3}$  = 4.5 mA,  $I_{D2,4}$  = 4 mA, and  $I_{D5-8}$  = 0.25 mA]. (b) Simulated CG and double sideband NF of the mixer versus IF.

$R_{IF}$  and the conversion gain (CG) are increased. Furthermore, the RF signal is applied to the gate of pMOS transistors, which slightly boosts the overall  $G_m$  of the active mixer. Also, the dc voltage of the  $M_{1,3}$ 's drain nodes is adjusted by the dc voltage of the LO signal fed to the gates of  $M_{5-8}$ . The mixer is employed in both in-phase and quadrature paths of the receiver each of which draws 8.9-mA current from a 1.2-V supply and provides a simulated CG and double sideband NF of 10.5 and 12.5 dB, respectively [see Fig. 12(b)].

### D. LO Path Chain Design

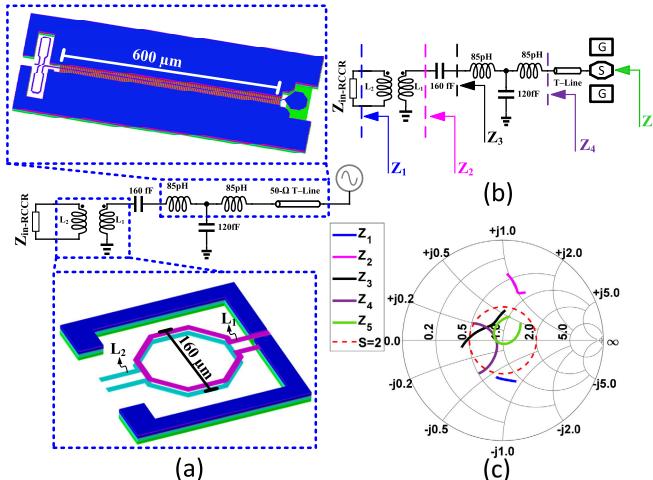

1) *Matching Network Design*: An external, single-ended LO signal is fed into the chip through a ground signal ground (GSG) pad, and a transmission line conveys this signal to a matching network [see Fig. 13(a)]. The matching network, along with a subsequent balun and an RC-CR PPF arrangement, collectively determines the input impedance of the receiver's LO port. The layout strategy necessitates placing the mm-wave components, such as mixers and the LO buffers, in close proximity; this requires utilizing a relatively long transmission line that is implemented by the slow-wave structure and exhibiting a simulated insertion loss of less than 0.9 dB across the frequency of operation.

Fig. 13(b) depicts the various observation nodes for the wideband matching network design; the impedance of each node versus frequency (19–34 GHz) is plotted on the Smith chart in Fig. 13(c). Notably,  $Z_1$  displays resistive-capacitive characteristics with the real part of the impedance relatively close to 50  $\Omega$ , achieved by selecting appropriate values for the RC-CR resistors (i.e., 100  $\Omega$ ). The reactive part of  $Z_1$ , however, is significantly capacitive. The adjacent component of the RC-CR filter is the balun, designed to provide the necessary differential input for RC-CR excitation. This is essential to clarify that the balun's design objective is to maximize the coupling factor between the two turns, rather than tuning out the capacitive part of the  $Z_1$ .

In this regard, the  $Z_2$  indicates resistive-inductive behavior; a series capacitor is employed to compensate for the excess inductance introduced by the balun. However,  $Z_3$  is observed to lack sufficient bandwidth. To address this, a T-network with two compact inductors is utilized to ensure the

Fig. 13. (a) Schematic of the matching network and layout of transmission line, inductors, and balun employed in the matching network. (b) Different observation nodes for wideband matching circuit design. (c) Simulated impedance at various nodes versus frequency.

Fig. 14. (a) Schematic of the RC-CR PPF to generate in-phase and quadrature LO ( $R_1 = R_2 = 100 \Omega$ ,  $C_1 = 66 \text{ fF}$ , and  $C_2 = 53 \text{ fF}$ ). (b) Metal routing handles the connections at the input of the PPF. (c) Simulated (including the EM effects) phase mismatch of the RC-CR versus frequency: blue curve represents the circuit with no capacitor adjustment (i.e.,  $C_1 = 66 \text{ fF}$  and  $C_2 = 53 \text{ fF}$ ), red curve signifies the circuit with capacitor adjustment (i.e.,  $R_1 = R_2 = 100 \Omega$ ,  $C_1 = 91 \text{ fF}$ , and  $C_2 = 47 \text{ fF}$ ), and black dashed curve is the pure schematic result with values mentioned in (a). (d) Simulated gain mismatch versus frequency [color codes are as mentioned in (c)].

desired matching performance over the operating bandwidth. Fig. 13(a) illustrates that the area penalty incurred by using the inductors is negligible compared to the transmission line size.  $Z_4$  represents the impedance seen after the T-network, which is almost within the targeted circle  $\text{VSWR} = 2$ . Considering the transmission line and GSG pad effects, the final impedance observed by measuring probes,  $Z_5$ , is adequately close to  $50 \Omega$ .

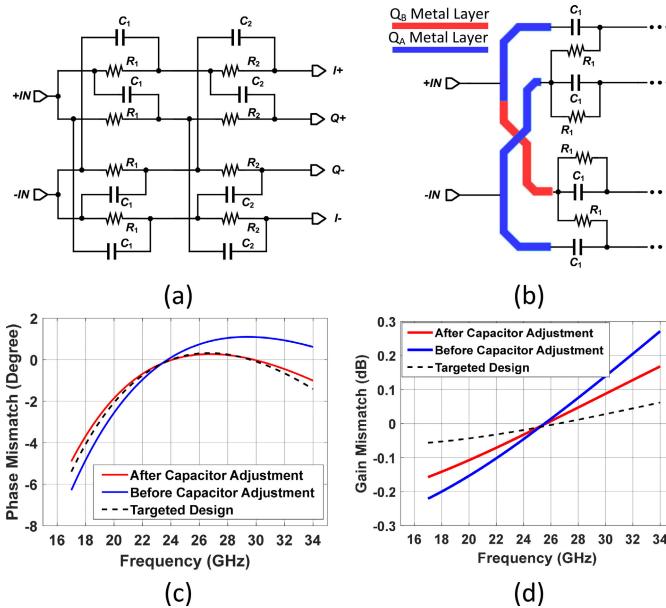

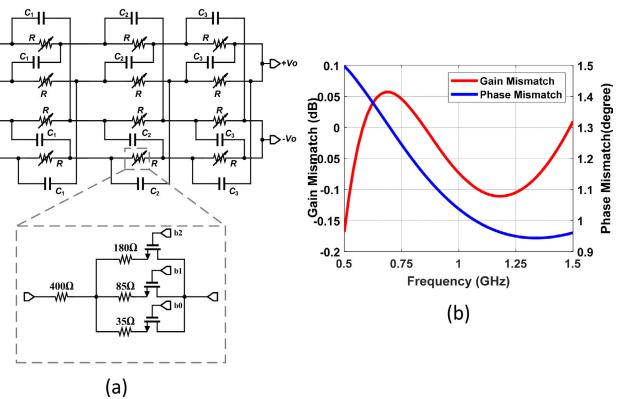

2) *I/Q LO Generation*: To generate the *I/Q* LO signal, a second-order RC-CR PPF is utilized. Fig. 14(a) shows the schematic of the RC-CR PPF. The value of resistors and capacitors are selected such that the pole frequencies are at 24 and 30 GHz [see the dashed curves in Fig. 14(c) and (d)].

The metal routing connecting the components of the RC-CR PPFs exhibits capacitive and inductive parasitic effects, influencing the phase and gain responses of the circuit. Layout considerations for mm-wave RC-CRs are presented in [24] and taken into account for this work as well.

The parasitic effects of routing change the place of the RC-CR PPF poles, supposed to be at  $\frac{1}{2\pi R_1 C_1}$  and  $(1/2\pi R_2 C_2)$ . Therefore, to compensate for the effect of routing, a full-wave electromagnetic (EM) simulation is performed to model the entire routing of PPF layout, and the capacitors,  $C_1$  and  $C_2$ , must be readjusted such that the poles are located at 24 and 30 GHz.

Fig. 14(c) and (d) shows the simulated phase and gain mismatch of the PPF for different cases, respectively. In the blue curve in Fig. 14(c), it is depicted that the routing parasitic effects degrade the phase performance of the network by pushing the high-frequency pole beyond the 34 GHz, which is out of the frequency of interest, and as a consequence, the phase mismatch is exacerbated by  $1.5^\circ$ . This observation verifies the need to adjust the capacitor values. After adjusting the capacitors  $C_1$  and  $C_2$ , the red curves in Fig. 14(c) and 14(d) are obtained, yielding  $3^\circ$  and 0.3-dB phase and gain mismatch, respectively.

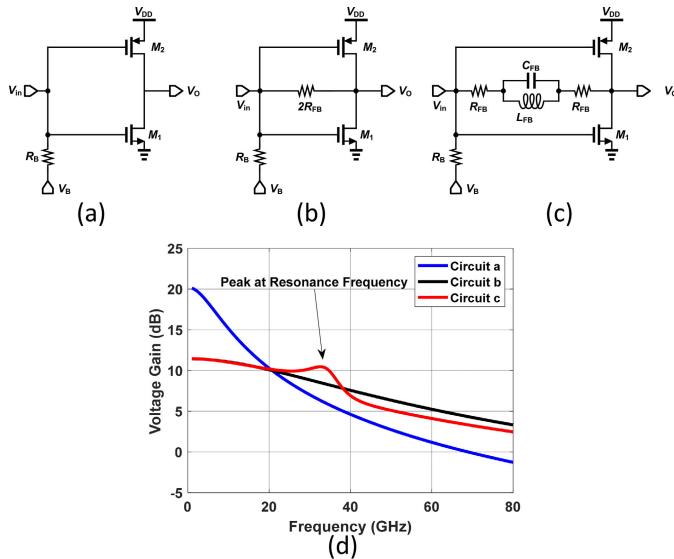

#### E. LO Buffers

The LO buffers serve to compensate for losses in the LO path caused by the RC-CR PPF and drive the capacitive load of the mixer's switching quad gates. These buffers require wide bandwidth, from 19 to 34 GHz. Class AB drivers, known for their push-pull behavior, are suitable for this task and have been used in similar applications [2], [25], [26]. Fig. 15 presents three class AB CMOS inverters, differing in feedback impedance. In Fig. 15(a), the nonflat frequency response results from a low-frequency pole due to the load capacitor and transistor parasitics. Adding a  $300\text{-}\Omega$  resistor shifts this pole but limits voltage gain. Fig. 15(c) introduces an *LC* resonator, achieving 2-dB gain peaking at resonance frequency  $\omega_{FB}$ , with less than 1.5-dB gain variation over the entire bandwidth.

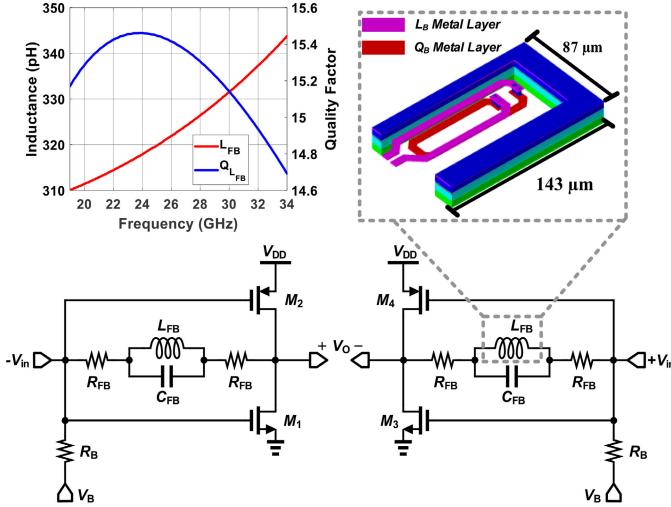

The differential LO buffer, used in both the *I* and *Q* paths of the receiver, along with the  $L_{FB}$  layout—a stacked inductor implemented with  $Q_B$  and  $L_B$  metal layers—are shown in Fig. 16. This stacked design minimizes the inductor area while maintaining a high quality factor of 15. Each LO buffer consumes 8 mA from a 1.2-V power supply.

#### F. IF Circuits

After signal downconversion, the IF signal undergoes amplification in both the *I* and *Q* paths. Subsequently, the *IQ* signal is combined with an RC-CR PPF to eliminate the image signal. Following additional amplification, the signal is routed to the output pads through a  $50\text{-}\Omega$  buffer for measurement. RC-CR PPFs generally introduce a high loss in the signal path when implemented with more than two stages. However, in the IF section of the receiver, the loss can be easily compensated by adding extra gain stages. Thus, using a three-stage RC-CR

Fig. 15. Three different LO buffer candidates. (a) Feedback-less. (b) Resistive feedback. (c) Feedback with tuned LC resonator [ $(W/L)_1 = 6.6 \mu\text{m}/20 \text{ nm}$ ,  $(W/L)_2 = 9.3 \mu\text{m}/20 \text{ nm}$ ,  $R_{FB} = 150 \Omega$ ,  $C_{FB} = 60 \text{ fF}$ , and  $L_{FB} = 330 \text{ pH}$ ]. (d) Simulated voltage gain of the circuits (a)–(c).

Fig. 16. Schematic of the LO buffers along with the layout of  $L_{FB}$  and EM simulation results of the inductor [ $(W/L)_{1,3} = 6.6 \mu\text{m}/20 \text{ nm}$ ,  $(W/L)_{2,4} = 9.3 \mu\text{m}/20 \text{ nm}$ ,  $R_{FB} = 150 \Omega$ ,  $C_{FB} = 60 \text{ fF}$ ,  $L_{FB} = 330 \text{ pH}$ , and  $I_{D1-4} = 4 \text{ mA}$ ].

PPF allows for more accurate combination of the  $I/Q$  signals with a negligible gain compensation effort.

Fig. 17(a) depicts the implemented three-stage PPF with programmable resistors, each of which is controlled by 3 bits ranging from 420 to 580  $\Omega$ . The  $\pm 15\%$  tunability of resistors helps overcome the process variation of components after fabrication. Fig. 17(b) illustrates that the simulated phase and gain mismatch for the center code of the resistors ( $b_2b_1b_0 = \overline{010}$ ) over the IF range, 500 MHz–1.5 GHz, are less than  $1.5^\circ$  and 0.2 dB, respectively.

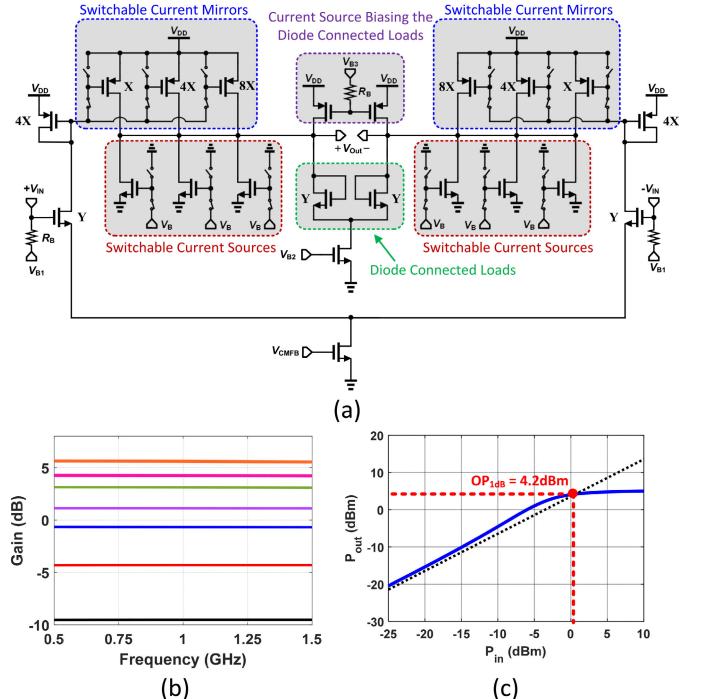

Fig. 18(a) shows the schematic of the variable gain amplifier (VGA). The circuit of the VGA is composed of five parts.

- 1) Input transistors converting the input voltage to the current.

- 2) Current mirror banks that multiplies the current; gain control occurs in this part by turning one branch on or off.

Fig. 17. (a) Schematic of IF RC-CR PPF for  $I-Q$  combination and image rejection ( $C_1 = 256 \text{ fF}$ ,  $C_2 = 324 \text{ fF}$ , and  $C_3 = 532 \text{ fF}$ ). (b) Simulated phase and gain mismatch versus frequency.

Fig. 18. (a) VGA schematic. (b) Simulated gain versus frequency for different states. (c) Simulated VGA's OP<sub>1dB</sub> at maximum gain.

- 3) Current source banks that are used to bias each branch of current mirrors.

- 4) Diode connected loads that are sized the same as the input transistors.

- 5) The pMOS current sources used to bias the diode-connected loads.

The scaling factor depicted in Fig. 18(a) along with the intrinsic  $r_o$  of the transistors are the main contributors of the VGA gain. As illustrated in Fig. 18(b), the gain of the VGA spans from  $-10$  to  $6$  dB. The VGA draws  $1.8$  and  $4.8$  mA from a  $1.2$ -V supply at the lowest and highest gain, respectively. Additionally, the VGA has a simulated OP<sub>1dB</sub> of  $4.2$  dBm at  $1$  GHz when operating at maximum gain state [see Fig. 18(c)].

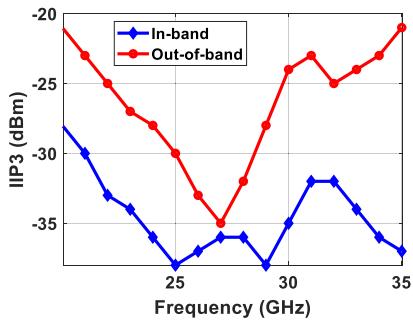

Fig. 19 displays the in-band and out-of-band 3rd order input intercept point (IIP3) of the receiver. To simulate the in-band IIP3, a two-tone test is conducted, each with the same amplitude and 200-MHz separation, inside the amplification bandwidth of the LNA when it

Fig. 19. Simulated in-band and out-of-band IIP3 of the receiver.

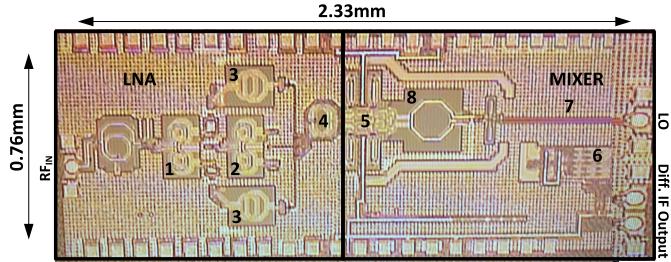

Fig. 20. Die photograph of the proposed wideband mm-wave receiver (1. first-stage wideband load, 2. second-stage wideband load, 3. double-tuned transformer for reconfigurable mode, 4. balun between LNA and mixer, 5. RC-CR section, 6. IF amplifier, 7. t-line for LO, and 8. matching network of LO).

is configured to operate in wideband mode. For out-of-band IIP3, however, the LNA is first configured to operate over the lower frequency band (i.e., 20–27 GHz), and the frequencies of the test signals are swept from 28 to 35 GHz. Subsequently, the LNA is configured to the high-frequency band, with the test signals covering from 20 to 28 GHz. As shown in Fig. 19, the receiver's in-band IIP3 is more than  $-38$  dBm with a gain of 45 dB, and the out-of-band IIP3 from 20 to 25 GHz and from 28 to 35 GHz, covering 80% of the operational bandwidth, achieving a 7–10-dB IIP3 improvement due to the reconfigurability of the LNA.

#### IV. FABRICATION AND MEASUREMENTS

The proposed mm-wave wideband/reconfigurable receiver with on-chip image rejection is fabricated in 22-nm CMOS FDSOI technology by Global Foundries occupying an area of  $2.331 \times 0.765$  mm (excluding pads). The photograph of the die is shown in Fig. 20. This fabricated receiver is measured on wafer and by probing input RF and LO, output IF, and dc biases. The effect of cables and RF probes are de-embedded using through, open, short, and matched (TOSM) calibration method. The Rohde & Schwarz ZVA67 network analyzer and FSV40 spectrum analyzer and Keysight 346CK01 noise source were used to perform  $S$ -parameter, linearity, image rejection, NF, and CG measurements. The total power consumption of the receiver is 94.8 mW drawn from 1.2-/1.8-V power supply. Table I presents the contribution of each block.

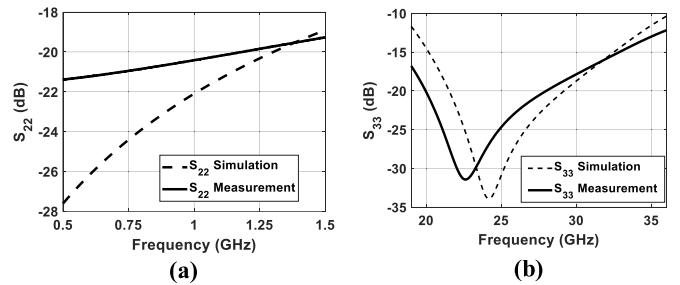

The measured and simulated  $S_{11}$  of LO and IF ports are illustrated in Fig. 21. As can be seen in Fig. 21, the measured  $S_{11}$  shows enough conformity compared to simulated reflection factors for both LO and IF ports.

TABLE I

POWER CONSUMPTION DETAILS

| Component      | Power consumption [mW] | Power Supply Voltage [V] |

|----------------|------------------------|--------------------------|

| LNA            | 35                     | 1.2/1.8                  |

| Mixers         | 21.6                   | 1.2                      |

| LO Buffers     | 15.84                  | 1.2                      |

| VGA            | 3.9                    | 1.2                      |

| IF Amplifier   | 15.2                   | 1.2                      |

| Bias Circuitry | 3.3                    | 1.2                      |

| Receiver       | 94.8                   | 1.2/1.8                  |

Fig. 21. Receiver reflection factor measurement. (a) IF port. (b) External LO port.

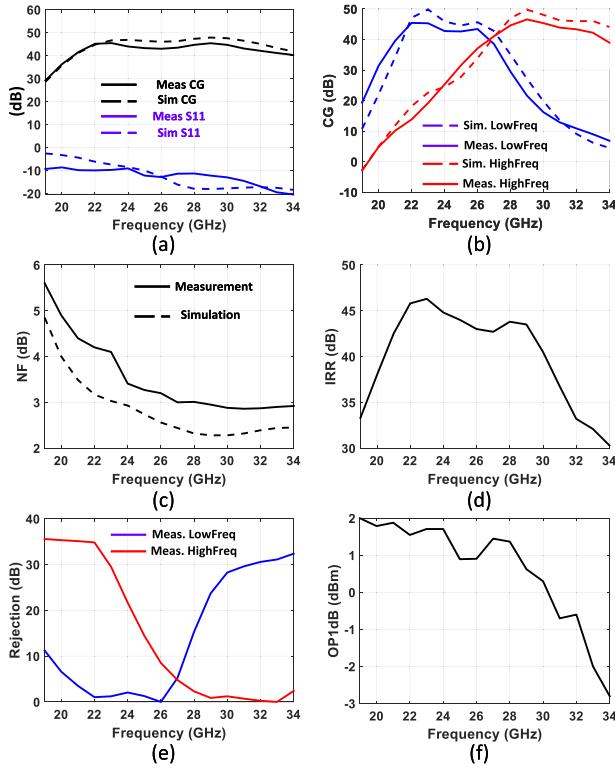

Fig. 22 shows the simulated and measured results of the proposed receiver. Fig. 22(a) shows the CG of the receiver when operating in wideband mode along with the  $S_{11}$  of the RF port. The 3-dB bandwidth for the CG is from 21.5 to 32.5 GHz with a peak gain of 45.5 dB at 22.5 GHz. The CG for both low-frequency and high-frequency reconfigurable modes is shown in Fig. 22(b), where the 3-dB bandwidth is from 21.5 to 26.5 GHz with a peak gain of 45.45 dB at 22 GHz and from 27 to 32 GHz with a peak gain of 46.58 dB at 29 GHz for the low-frequency and high-frequency modes, respectively. Fig. 22(c) shows the simulated and measured NF results, where the minimum measured NF is 2.9 dB at 29 GHz. To measure the IRR of the receiver, the circuit is initially excited with a continuous wave (CW) signal at the image frequency band, and the corresponding output is recorded. Subsequently, the circuit is excited with an identical CW signal at the signal frequency band, maintaining the same amplitude at the input, and the output is again measured. The IRR is, then, determined by calculating the ratio of the signal power to the image power. Note that the image and signal frequency bands are shown in Fig. 6(b). This measurement is performed over the bandwidth of operation. Fig. 22(d) shows the measured IRR of the receiver in wideband mode. For the frequency range of 19–34 GHz, the IRR is better than 30 dB. The primary sources of the limited IRR are the  $IQ$  mismatches in the RC-CR PPF used in the LO and IF paths. However, the RC-CR in the LO path contributes more significantly to the limited IRR, as it is a two-stage filter, resulting in greater  $IQ$  gain and phase mismatches. In contrast, the RC-CR in the IF path is a three-stage PPF, which leads to reduced  $IQ$  mismatches. The normalized in-band/out-of-band rejection of the reconfigurable modes compared to the wideband mode is shown in Fig. 22(e), where up to 30-dB out-of-band rejection is achieved. Finally, Fig. 22(f) shows the output-referred  $P_{1dB}$  linearity measurement, which varies between  $-2.8$  and  $2$  dBm.

Fig. 22. (a) Measured and simulated results of the CG versus input RF and S11 of RF port. (b) Measured and simulated CG for reconfigurable modes. (c) Measured and simulated NF. (d) Measured IRR. (e) Rejection of reconfigurable modes compared to wideband mode. (f) Measured output  $P_{1dB}$ .

TABLE II

PERFORMANCE COMPARISON WITH THE STATE-OF-THE-ART 3-WINDING MM-WAVE LNAs

|                              | [14] RFIC'23                     | [11] JSSC'24     | [12] TMTT'24    | [13] TCAS'23      |

|------------------------------|----------------------------------|------------------|-----------------|-------------------|

| Process                      | 22nm FDSOI                       | 40nm CMOS        | 65nm CMOS       | 130nm CMOS SOI    |

| Frequency (GHz)              | 21.6-34.2                        | 51.6-73.7        | 32-46           | 6-12              |

| Freq. Operation Mode         | WB <sup>b</sup> /RC <sup>c</sup> | WB <sup>b</sup>  | WB <sup>b</sup> | WB <sup>b</sup>   |

| % FBW                        | 45                               | 35.3             | 35.9            | 66.7              |

| Minimum NF (dB)              | 2.3                              | 3.78             | 2.2             | 0.8               |

| Peak Gain (dB)               | 32.4                             | 22.4             | 21.5            | 23.3              |

| Min. OP <sub>1dB</sub> (dBm) | -6                               | 7.2 <sup>a</sup> | -               | -1.7 <sup>a</sup> |

| Power (mW)                   | 35                               | 34               | 22              | 66                |

| Area (mm <sup>2</sup> )      | 0.74                             | 0.12             | 0.16            | 1.41              |

<sup>a</sup> Approximated as  $(Gain_{dB} - 1) + IP_{1dB}$  when measured result not available. <sup>b</sup> Wideband. <sup>c</sup> Re-configurable

Table II provides a comparison between the standalone LNA presented in [14] and employed in this work as a part of the receiver, and other state-of-the-art mm-wave LNAs utilizing 3-winding transformer structure. The significance of the 3-winding transformer lies in its versatility, as it can be customized for various design objectives such as  $G_m$  boosting, noise cancellation, bandwidth enhancement, and/or frequency mode reconfigurability. The three references of [11], [12], and [13] employ the idea of 3-winding transformer structure toward different design goals, as explained in Section I. As shown in Table II, Ke et al. [11] achieve remarkable linearity and high gain attributed to the  $G_m$  boosting technique. In [12], the 3-winding transformer is combined with a multiarray transistor strategy, resulting in an impressive NF of 2.2 dB. Meanwhile, Zou et al. [13] achieve an outstanding NF of 0.8 dB by an auxiliary capacitor alongside the 3-winding transformer to independently control

TABLE III

PERFORMANCE COMPARISON WITH THE STATE-OF-THE-ART MM-WAVE WIDEBAND RECEIVERS

| References \ Specs      | This work                                                                                          | [6] MTT'20        | [3] <sup>f</sup> MTT'20 | [7] EuMIC'18         | [4] JSSC'20     | [2] MTT'2021            | [9] JSSC'19               |

|-------------------------|----------------------------------------------------------------------------------------------------|-------------------|-------------------------|----------------------|-----------------|-------------------------|---------------------------|

| Technology              | 22nm CMOS FDSOI                                                                                    | 65nm CMOS         | 22nm CMOS FDSOI         | 130nm ST SiGe BiCMOS | 45nm CMOS SOI   | 22nm CMOS FDSOI         | 45nm CMOS SOI             |

| on-chip image-rejection | YES                                                                                                | NO                | YES                     | NO                   | YES             | NO                      | YES                       |

| Freq operation mode     | WB/RC <sup>c</sup>                                                                                 | WB <sup>b</sup>   | WB <sup>b</sup>         | WB <sup>b</sup>      | WB <sup>b</sup> | WB <sup>b</sup>         | WB/RC <sup>c</sup>        |

| Freq (GHz)              | 21.5 – 32.5 <sup>WB</sup><br>21.5-26.5 <sup>c</sup> / <sub>b</sub> 27-32 <sup>c</sup> <sub>b</sub> | 26.5 – 32.5       | 20 – 44                 | 24 – 30              | 24.5 – 43.5     | 19.5 – 42               | 27 – 29.75/<br>28.75 – 35 |

| % FBW                   | 40.7                                                                                               | 20.34             | 75                      | 22.2                 | 55.9            | 73.2                    | 19.6                      |

| CG (dB)                 | 45.5                                                                                               | 29.5 <sup>a</sup> | 28.5 <sup>a</sup>       | 39.5                 | 35.2            | 25.3                    | 33/26.5                   |

| IRR (dB)                | > 30                                                                                               | -                 | > 75                    | > 18                 | > 32            | -                       | > 30                      |

| NF (dB)                 | 5.5 – 2.9                                                                                          | 5.3 – 6.6         | 3.3 – 5                 | 3.6 – 4.8            | 3.2 – 6.1       | 2.7 – 4.2               | 5.7/8.5                   |

| OP <sub>1dB</sub> (dBm) | -2.8 – 2                                                                                           | 0.5 <sup>b</sup>  | -1 – 3 <sup>b</sup>     | 15                   | 9 – 27          | -1.7 – 1.3 <sup>b</sup> | 2/2.5                     |

| Power (mW)              | 94.8                                                                                               | 33                | 70                      | 1270                 | 60              | 102                     | 52.5                      |

| Area (mm <sup>2</sup> ) | 1.78 (pad excluded)                                                                                | 0.65              | 1.8                     | 4.05                 | 0.77            | 0.9                     | 0.46                      |

<sup>a</sup> Output IF amplifier and IQ mixer gain are excluded. <sup>b</sup>  $OP_{1dB} = (CG_{dB} - 1) + IP_{1dB}$

<sup>c</sup> IQ mixer and output IF amplifier are off-chip. <sup>f</sup> WB: Wideband RC:Reconfigurable

each effective coupling strength. However, this study centers on utilizing the 3-winding transformer to design an mm-wave LNA with two auxiliary paths integrated with the main signal path. These auxiliary paths provide a configurable feature that enables the optimization of  $OP_{1dB}$  performance and broadens the bandwidth when operating in wideband mode. By adopting this novel approach, the 3-winding transformer not only improves linearity but also extends the bandwidth, meeting the demands of advanced mm-wave systems. As shown in Table II, relatively high fractional bandwidth (FBW) is achieved compared to [11] and [12] although the 3-winding transformer's application is not limited to bandwidth enhancement, as highlighted in Table II. In [13], however, higher FBW is achieved but at a lower center frequency without reconfigurability operation mode which is one of the main contributions of this work.

Table III shows the comparison of the proposed receiver with the state-of-the-art mm-wave receivers, where the proposed receiver, along with [3] and [4], uses an on-chip image rejection receiver. This work is the only one that has both wideband and reconfigurable features. The frequency response of [3] is wider than that of the proposed receiver, but this work has a wider bandwidth than [6], which uses a conventional double-tuned transformer as the load of the LNA. As shown in Table III, there are limitations in bandwidth extension in the 3-winding transformer, and this work does not surpass some state-of-the-art designs, none of which utilize 3-winding transformer, in terms of FBW. As detailed in [2] and [3], the three-stage approach for wideband LNA design provides more FBW, which is also highlighted in Table II. However, in [3], the receiver leverages a dual-conversion architecture with an off-chip second stage of downconversion resulting in a high first IF of 16 GHz, which is at the output of the chip. As a result, the required frequency range for the LO is decreased, resulting in less challenging design of the LO paths at the cost of dual conversion. Compared to other references, the proposed receiver exhibits competitive FBW. The CG for this work is higher than other references (although some references have not included the gain of the buffer stage), due to the relatively high gain of the LNA,

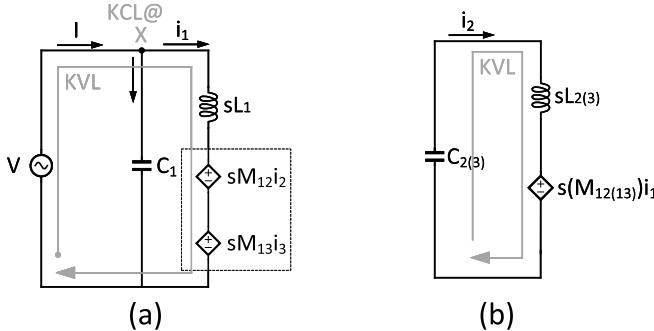

Fig. 23. (a) KVL and KCL in the primary side of the proposed transformer with considering the effect of two secondaries. (b) KVL in the secondary side.

resulting in the relatively low NF. The output-referred  $P_{1dB}$  ranges from  $-2.8$  to  $2$  dBm from  $19$  to  $34$  GHz. The power consumption is relatively higher than other references, except for [7], due to the high power consumption in the LNA, and the area is comparable to other references.

## V. CONCLUSION

This article presents a fully integrated CMOS mm-wave wideband image-reject receiver using a reconfigurable LNA in  $22$ -nm FDSOI, where the complete analysis of the proposed 3-winding transformer including the location of the poles and zeros along with the equation for  $Z_{11}$  are presented. Based on this 3-winding transformer, an mm-wave wideband/reconfigurable receiver is realized with three major contributions including: 1) wideband/reconfigurable frequency mode operation; 2) canceling interfering signals right after the LNA to relax mixer linearity requirements; and 3) using on-chip image rejection with a three-stage RC-CR filter with tunable resistors for optimum operation. The 3-dB bandwidth in wideband mode is from  $21.5$  to  $32.5$  GHz with a peak gain of  $45.5$  dB at  $22.5$  GHz, and for both low-frequency and high-frequency reconfigurable modes, it is  $21.5$ – $26.5$  GHz with a peak gain of  $45.45$  dB at  $22$  GHz and  $27$ – $32$  GHz with a peak gain of  $46.58$  dB at  $29$  GHz, respectively. The measured NF shows the minimum value of  $2.9$  dB at  $30$  GHz. The image rejection is better than  $30$  dB for  $19$ – $34$  GHz and the minimum  $OP_{1dB}$  is  $-2.8$  dBm.

## APPENDIX A

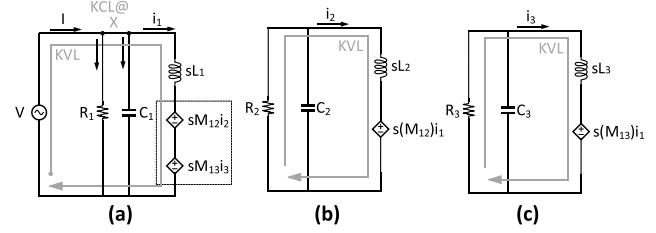

This section presents derivation to approximate the location of the zeros of the 3-winding transformer. According to Fig. 23(a), KVL and KCL at node X on the primary side, considering the effect of the two secondaries onto the primary, result in

$$V = sL_1 i_1 + sM_{12} i_2 + sM_{13} i_3 \quad (9)$$

$$I = i_1 + sC_1 V. \quad (10)$$

Now according to (9) and (10), if  $i_2$  and  $i_3$  are written based on  $i_1$ ,  $Z_{11} = (V/I)$  can be obtained. To do so, according to Fig. 23(b)

$$i_{2(3)} = \frac{-s^2 M_{12(13)} C_{2(3)}}{1 + s^2 L_{2(3)} C_{2(3)}} i_1. \quad (11)$$

Fig. 24. ADS simulation with ideal elements when (a)  $C_3$  and (b)  $C_2$  are swept. (Y-axis represents the magnitude of the impedance of  $Z_{11}$  in  $\text{dB}\Omega$ .)

By replacing (11), and (9) into (10), the equation for  $Z_{11}$  is achieved

$$Z_{11} = \frac{V}{I} = \frac{N(s)}{D(s)} \quad (12)$$

$$N(s) = L_1 s (C_2 C_3 L_2 L_3 (1 - k_{12}^2 - k_{13}^2) s^4 + (C_2 L_2 (1 - k_{12}^2) + C_3 L_3 (1 - k_{13}^2)) s^2 + 1) \quad (13)$$

$$D(s) = C_1 C_2 C_3 L_1 L_2 L_3 (1 - k_{12}^2 - k_{13}^2) s^6 + (C_1 C_2 L_1 L_2 (1 - k_{12}^2) + C_1 C_3 L_1 L_3 (1 - k_{13}^2) + C_2 C_3 L_2 L_3) s^4 + (C_1 L_1 + C_2 L_2 + C_3 L_3) s^2 + 1. \quad (14)$$

First, the location of zeros can be extracted from (13). As shown, one zero is at dc and another is at infinity and two other zeros are found by solving  $N(s) = 0$  and assuming  $s^2 = t$

$$C_2 C_3 L_2 L_3 (1 - k_{12}^2 - k_{13}^2) t^2 + (C_2 L_2 (1 - k_{12}^2) + C_3 L_3 (1 - k_{13}^2)) t + 1 = 0. \quad (15)$$

Due to practical layout symmetry,  $L_2 = L_3$ , and therefore, the coupling factors are assumed to be equal ( $k_{12} = k_{13} = k$ ). Also, the following assumptions are made:

$$\omega_1^2 = \frac{1}{L_1 C_1} \quad \omega_2^2 = \frac{1}{L_2 C_2} \quad \omega_3^2 = \frac{1}{L_3 C_3}. \quad (16)$$

With the above assumptions, solving (15) yields zero frequencies provided in (3).

## APPENDIX B

This section presents derivation to approximate the location of the poles of the 3-winding transformer. To find the location of poles using (14), after applying (16) to (14), assuming  $s^2 = t$

$$D(t) = (1 - 2k^2) \frac{t^3}{\omega_1^2 \omega_2^2 \omega_3^2} + \left( \frac{1 - k^2}{\omega_1^2 \omega_2^2} + \frac{1 - k^2}{\omega_1^2 \omega_3^2} + \frac{1}{\omega_2^2 \omega_3^2} \right) t^2 + \left( \frac{1}{\omega_1^2} + \frac{1}{\omega_2^2} + \frac{1}{\omega_3^2} \right) t + 1. \quad (17)$$

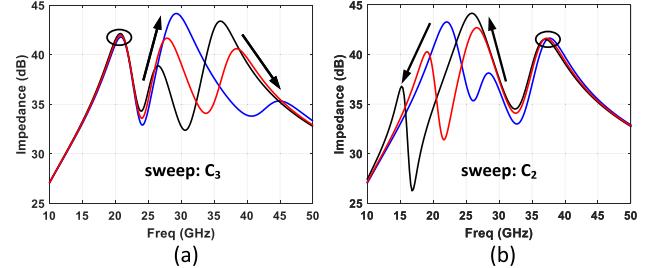

As shown in (17), the equation is of order 3, and closed-form solutions for the poles (i.e., when  $D(t) = 0$ ) are not intuitive. To simplify the analysis, the following assumptions are made: first, if the location of the first pole ( $\omega_{p1}$ ) is desired, the term  $(t/\omega_3)$ , with  $\omega_3 > \omega_1$  and  $\omega_2$ , in the  $D(t)$  equation is negligible since  $\omega_{p1} < \omega_3$ . Fig. 24(a) shows the ADS

simulation of  $Z_{11}$  for Port 1 of the proposed load when  $C_3$  is changing. As can be seen, the location of  $\omega_{p1}$  does not change; therefore, we assume  $C_3 = 0$ , resulting in  $\omega_3 \approx \infty$ , which is consistent with the assumption that  $\omega_3 > \omega_1$ . The following coefficients in (17) can, thus, be neglected:

$$\begin{aligned} \frac{1}{\omega_3^2} &\approx 0 \\ \frac{1-k^2}{\omega_1^2\omega_3^2} + \frac{1}{\omega_2^2\omega_3^2} &\approx 0 \\ (1-2k^2)\frac{1}{\omega_1^2\omega_2^2\omega_3^2} &\approx 0. \end{aligned} \quad (18)$$

Therefore,  $D(t)$  can be written as

$$D(t) = \left(\frac{1-k^2}{\omega_1^2\omega_2^2}\right)t^2 + \left(\frac{1}{\omega_1^2} + \frac{1}{\omega_2^2}\right)t + 1 = 0. \quad (19)$$

According to the following definitions:

$$\left(\frac{\omega_2}{\omega_1}\right)^2 = \xi_2^2 \quad \left(\frac{\omega_3}{\omega_1}\right)^2 = \xi_3^2. \quad (20)$$

The first pole ( $\omega_{p1,T}$ ) is given by

$$\omega_{p1,T} = \omega_1 \sqrt{0.5(1+\xi_2^2)} \sqrt{1 - \sqrt{1 - \xi_2^2 \frac{4(1-k^2)}{(1+\xi_2^2)^2}}} \xrightarrow{\xi_2 \approx 1 \& \left(\frac{1}{\xi_2} + \xi_2\right)^2 \approx 4} \omega_{p1,T} \approx \omega_1 \sqrt{1-k}. \quad (21)$$

According to (21),  $\omega_{p1}$  depends on  $\omega_1$  and the coupling factor between primary and secondary. To find the second pole, similar to the first assumption, changing  $C_2$  has no effect on the third pole as shown by ADS simulations in Fig. 24(b). Therefore, assuming  $C_2 \approx \infty$ , then term  $(t/\omega_2)$  is dominant, and (17) can be rewritten as

$$D(t) = (1-2k^2)\frac{t^2}{\omega_1^2\omega_3^2} + \left(\frac{1-k^2}{\omega_1^2} + \frac{1}{\omega_3^2}\right)t + 1 = 0. \quad (22)$$

After solving the equation for  $\omega_{p3}$

$$\begin{aligned} \omega_{p3,T} &= \omega_3 \sqrt{0.5\left(\frac{1}{\xi_3^2} + 1 - k^2\right)} \\ &\times \frac{1}{\sqrt{1-2k^2}} \sqrt{\left(1 + \sqrt{1 - \frac{(1-2k^2)}{\left(\xi_3 0.5(1-k^2) + \frac{1}{2\xi_3}\right)^2}}\right)} \\ &\xrightarrow{\xi_3 0.5(1-k^2) + \frac{1}{2\xi_3} \approx 1 \& k^2 \ll 1} \omega_{p3,T} \approx \omega_3 \sqrt{0.5\left(\frac{1}{\xi_3^2} + 1\right)} \sqrt{(1 + \sqrt{2k})(1 + k^2)}. \end{aligned} \quad (23)$$

In order to find the second pole ( $\omega_{p2}$ ),  $D(t)$  can be written in the standard form as

$$\begin{aligned} D(t) &= \left(\frac{t}{\omega_{p1,T}^2} - 1\right) \left(\frac{t}{\omega_{p2,T}^2} - 1\right) \left(\frac{t}{\omega_{p3,T}^2} - 1\right) \\ &= \frac{t^3}{\omega_{p1,T}^2\omega_{p2,T}^2\omega_{p3,T}^2} + \dots \end{aligned} \quad (24)$$

Fig. 25. (a) KVL and KCL in the primary side of the proposed transformer with considering the effect of two secondaries including the effect of (b) and (c) KVL in the secondary side.

By comparing (17) and (24), it can be concluded that the coefficients for the term  $t^3$  have to be equal. Therefore,  $\omega_{p2}$  can be written as

$$\omega_{p2,T} = \omega_2 \frac{\left(\frac{\omega_1}{\omega_{p1,T}}\right) \left(\frac{\omega_3}{\omega_{p3,T}}\right)}{\sqrt{1-2k^2}}. \quad (25)$$

## APPENDIX C

This appendix presents a more accurate analysis by considering the effect of the limited quality factor of each inductance utilized in the 3-winding transformer. To extract  $Z_{11}$  transfer function, the equivalent circuit of each turn is displayed in Fig. 25. The following equations are KVL and KCL of Fig. 25(a) for the primary turn:

$$\begin{aligned} V &= sL_1i_1 + sM_{12}i_2 + sM_{13}i_3 \\ I &= i_1 + sC_1V + \frac{V}{R_1}. \end{aligned} \quad (26)$$

To find  $i_1$  and  $i_2$ , by referring to Fig. 25(b) and (c), the following equation can be written:

$$\begin{aligned} i_2 &= \frac{-sM_{12}\left(\frac{1}{R_2} + sC_2\right)}{1 + s\frac{L_2}{R_2} + s^2L_2C_2}i_1 \\ i_3 &= \frac{-sM_{13}\left(\frac{1}{R_3} + sC_3\right)}{1 + s\frac{L_3}{R_3} + s^2L_3C_3}i_1. \end{aligned} \quad (27)$$

By substituting (27) into (26),  $Z_{11}(s)$  can be written as follows:

$$Z_{11}(s) = \frac{N(s)}{D(s)}L_{1s}. \quad (28)$$

In which,  $N(s)$  and  $D(s)$  are

$$\begin{aligned} N(s) &= A_0 + A_1s + A_2s^2 + A_3s^3 + A_4s^4 \\ D(s) &= B_0 + B_1s + B_2s^2 + B_3s^3 + B_4s^4 + B_5s^5 + B_6s^6. \end{aligned} \quad (29)$$

The coefficients of the numerator are as follows:

$$\begin{aligned} A_0 &= 1 \\ A_1 &= \frac{1-k^2}{Q_2\omega_2} + \frac{1-k^2}{Q_3\omega_3} \\ A_2 &= \frac{1-k^2}{\omega_2^2} + \frac{1-k^2}{\omega_3^2} + \frac{1-2k^2}{Q_2Q_3\omega_2\omega_3} \\ A_3 &= \frac{2-4k^2}{Q_3\omega_3\omega_2^2} + \frac{2-4k^2}{Q_2\omega_2\omega_3^2} \\ A_4 &= \frac{1-2k^2}{\omega_2^2\omega_3^2}. \end{aligned} \quad (30)$$

Besides, the coefficients of the denominator are as follows:

$$\begin{aligned}

B_0 &= 1 \\

B_1 &= \frac{1}{Q_1\omega_1} + \frac{1}{Q_2\omega_2} + \frac{1}{Q_3\omega_3} \\

B_2 &= \frac{1}{\omega_1^2} + \frac{1}{\omega_2^2} + \frac{1}{\omega_3^2} + \frac{1-k^2}{Q_1Q_2\omega_1\omega_2} + \frac{1-k^2}{Q_1Q_3\omega_1\omega_3} \\

&\quad + \frac{1}{Q_2Q_3\omega_2\omega_3} \\

B_3 &= \frac{1-k^2}{\omega_1^2\omega_2Q_2} + \frac{1-k^2}{\omega_1^2\omega_3Q_3} + \frac{1-k^2}{\omega_2^2\omega_1Q_1} + \frac{1-k^2}{\omega_3^2\omega_1Q_1} \\

&\quad + \frac{1-2k^2}{\omega_1\omega_2\omega_3Q_1Q_2Q_3} \\

B_4 &= \left( \frac{1-k^2}{\omega_1^2\omega_2^2} + \frac{1-k^2}{\omega_1^2\omega_3^2} + \frac{1}{\omega_2^2\omega_3^2} \right) \\

&\quad + \frac{1-2k^2}{\omega_2\omega_3\omega_1^2Q_2Q_3} + \frac{1-2k^2}{\omega_1\omega_3\omega_2^2Q_1Q_3} + \frac{1-2k^2}{\omega_1\omega_2\omega_3^2Q_1Q_2} \\

B_5 &= \frac{1-2k^2}{\omega_1^2\omega_2^2\omega_3Q_3} + \frac{1-2k^2}{\omega_1^2\omega_3^2\omega_2Q_2} + \frac{1-2k^2}{\omega_2^2\omega_3^2\omega_1Q_1} \\

B_6 &= \frac{1-2k^2}{\omega_1^2\omega_2^2\omega_3^2}. \tag{31}

\end{aligned}$$

Note that the definition of  $\omega_{1,2,3}$  is provided in (16). Besides, the coupling factors are assumed to be equal ( $k_{12} = k_{13} = k$ ).

#### ACKNOWLEDGMENT

The authors would like to thank Global Foundries for the chip fabrication.

#### REFERENCES

- [1] S. Mondal, R. Singh, and J. Paramesh, "A reconfigurable 28/37 GHz hybrid-beamforming MIMO receiver with inter-band carrier aggregation and RF-domain LMS weight adaptation," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2018, pp. 72–74.

- [2] L. Gao and G. M. Rebeiz, "A 20–42-GHz IQ receiver in 22-nm CMOS FD-SOI with 2.7–4.2-dB NF and -25-dBm IP1dB for wideband 5G systems," *IEEE Trans. Microw. Theory Techn.*, vol. 69, no. 11, pp. 4951–4960, Nov. 2021.

- [3] L. Gao, Q. Ma, and G. M. Rebeiz, "A 20–44-GHz image-rejection receiver with >75-dB image-rejection ratio in 22-nm CMOS FD-SOI for 5G applications," *IEEE Trans. Microw. Theory Techn.*, vol. 68, no. 7, pp. 2823–2832, Jul. 2020.

- [4] M.-Y. Huang, T. Chi, S. Li, T.-Y. Huang, and H. Wang, "A 24.5–43.5-GHz ultra-compact CMOS receiver front end with calibration-free instantaneous full-band image rejection for multiband 5G massive MIMO," *IEEE J. Solid-State Circuits*, vol. 55, no. 5, pp. 1177–1186, May 2020.

- [5] J. Borremans et al., "A 40 nm CMOS 0.4–6 GHz receiver resilient to out-of-band blockers," *IEEE J. Solid-State Circuits*, vol. 46, no. 7, pp. 1659–1671, Jul. 2011.

- [6] R. Singh, S. Mondal, and J. Paramesh, "A millimeter-wave receiver using a wideband low-noise amplifier with one-port coupled resonator loads," *IEEE Trans. Microw. Theory Techn.*, vol. 68, no. 9, pp. 3794–3803, Sep. 2020.

- [7] A. Fonte, F. Plutino, L. Moquillon, S. Razafimandimby, and S. Pruvost, "5G 26 GHz and 28 GHz bands SiGe: C receiver with very high-linearity and 56 dB dynamic range," in *Proc. 13th Eur. Microw. Integr. Circuits Conf. (EuMIC)*, Sep. 2018, pp. 57–60.

- [8] S. Mondal, R. Singh, A. I. Hussein, and J. Paramesh, "A 25–30 GHz fully-connected hybrid beamforming receiver for MIMO communication," *IEEE J. Solid-State Circuits*, vol. 53, no. 5, pp. 1275–1287, May 2018.

- [9] S. Mondal and J. Paramesh, "A reconfigurable 28/37-GHz MMSE-adaptive hybrid-beamforming receiver for carrier aggregation and multi-standard MIMO communication," *IEEE J. Solid-State Circuits*, vol. 54, no. 5, pp. 1391–1406, May 2019.

- [10] S. Mondal, L. R. Carley, and J. Paramesh, "Dual-band, two-layer millimeter-wave transceiver for hybrid MIMO systems," *IEEE J. Solid-State Circuits*, vol. 57, no. 2, pp. 339–355, Feb. 2022.

- [11] J. Ke, Z. Lin, G. Feng, and Y. Wang, "A 52–73-GHz LNA with tri-coupled transformer for  $G_m$  boosting and enhanced noise canceling," *IEEE J. Solid-State Circuits*, vol. 59, no. 3, pp. 668–676, Jan. 2024.

- [12] J.-H. Kim, J.-T. Son, J.-T. Lim, H.-W. Choi, and C.-Y. Kim, "Ultralow noise figure and broadband CMOS LNA with three-winding transformer and large transistor," *IEEE Trans. Microw. Theory Techn.*, vol. 72, no. 5, pp. 2734–2744, May 2024.

- [13] T. Zou et al., "A 6–12 GHz wideband low-noise amplifier with 0.8–1.5 dB NF and  $\pm 0.75$  dB ripple enabled by the capacitor assisting triple-winding transformer," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 70, no. 7, pp. 2802–2813, Jul. 2023.

- [14] M. G. Bardeh, J. Fu, N. Naseh, J. Paramesh, and K. Entesari, "A mm-wave wideband/reconfigurable LNA using a 3-winding transformer load in 22-nm CMOS FDSOI," in *Proc. IEEE Radio Freq. Integr. Circuits Symp. (RFIC)*, Jun. 2023, pp. 121–124.

- [15] N.-Z. Sun, L. Gao, H.-Y. Li, J.-X. Xu, and X. Zhang, "A compact millimeter-wave reconfigurable dual-band LNA with image-rejection in 28-nm bulk CMOS for 5G applications," *IEEE J. Solid-State Circuits*, vol. 59, no. 10, pp. 3406–3416, Oct. 2024.

- [16] P. Heydari and M. Safiullah, "Evolution of broadband amplifier design: From single-stage to distributed topology," *IEEE Microw. Mag.*, vol. 24, no. 9, pp. 18–29, Sep. 2023.

- [17] B. Cui and J. R. Long, "A 1.7-dB minimum NF, 22–32-GHz low-noise feedback amplifier with multistage noise matching in 22-nm FD-SOI CMOS," *IEEE J. Solid-State Circuits*, vol. 55, no. 5, pp. 1239–1248, May 2020.

- [18] M. G. Bardeh, J. Fu, N. Naseh, J. Paramesh, and K. Entesari, "A wideband low RMS phase/gain error mm-wave phase shifter in 22-nm CMOS FDSOI," *IEEE Microw. Wireless Technol. Lett.*, vol. 33, no. 6, pp. 739–742, Jun. 2023.

- [19] M. Elkholy, S. Shakib, J. Dunworth, V. Aparin, and K. Entesari, "A wideband variable gain LNA with high OIP3 for 5G using 40-nm bulk CMOS," *IEEE Microw. Wireless Compon. Lett.*, vol. 28, no. 1, pp. 64–66, Jan. 2018.

- [20] A. Ershadi, S. Palermo, and K. Entesari, "A 22.2–43 GHz gate-drain mutually induced feedback low noise amplifier in 28-nm CMOS," in *Proc. IEEE Radio Freq. Integr. Circuits Symp. (RFIC)*, Jun. 2021, pp. 27–30.

- [21] J. Fu, M. G. Bardeh, J. Paramesh, and K. Entesari, "A millimeter-wave concurrent LNA in 22-nm CMOS FDSOI for 5G applications," *IEEE Trans. Microw. Theory Techn.*, vol. 71, no. 3, pp. 1031–1043, Mar. 2023.

- [22] T. Tuovinen, N. Tervo, and A. Pärssinen, "Analyzing 5G RF system performance and relation to link budget for directive MIMO," *IEEE Trans. Antennas Propag.*, vol. 65, no. 12, pp. 6636–6645, Dec. 2017.

- [23] B. Razavi, *RF Microelectronics* (Prentice-Hall Communications Engineering and Emerging Technologies Series), 2nd ed. Upper Saddle River, NJ, USA: Prentice-Hall, 2011.

- [24] S. Kulkarni, D. Zhao, and P. Reynaert, "Design of an optimal layout polyphase filter for millimeter-wave quadrature LO generation," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 60, no. 4, pp. 202–206, Apr. 2013.

- [25] A. Zandieh, N. Weiss, T. Nguyen, D. Haranne, and S. P. Voinigescu, "128-GS/s ADC front-end with over 60-GHz input bandwidth in 22-nm Si/SiGe FDSOI CMOS," in *Proc. IEEE BiCMOS Compound Semiconductor Integr. Circuits Technol. Symp. (BCICTS)*, Oct. 2018, pp. 271–274.

- [26] S.-F. Chao, J.-J. Kuo, C.-L. Lin, M.-D. Tsai, and H. Wang, "A DC-11.5 GHz low-power, wideband amplifier using splitting-load inductive peaking technique," *IEEE Microw. Wireless Compon. Lett.*, vol. 18, no. 7, pp. 482–484, Jul. 2008.