# Multilayer Ceramic Capacitor Vibration Source Model Library Development

Yifan Ding, Student Member, IEEE, Ming-Feng Xue, Jianmin Zhang, Senior Member, IEEE, Xin Hua, Benjamin Leung, Eric A. MacIntosh, Member, IEEE, and Chulsoon Hwang, Senior Member, IEEE

Abstract—When a multilayer ceramic capacitor (MLCC) is soldered on a printed circuit board (PCB), the capacitor deformation generates a force on the PCB, which serves as a source to excite PCB vibration and generate unwanted acoustic noise. A MLCC can be used under any loading conditions as long as the power supply voltage remains below its rated voltage; thus, the MLCC source mode can be extremely complicated because of different combinations including direct current voltage levels, alternating current noise amplitudes, and related frequencies. When the power rail is under different loading conditions, the PCB vibration amplitude can differ; however, the MLCC vibration source model should remain the same under a given condition. In this article, the MLCC equivalent source models are developed with a simplified method, and a source model library for the six MLCCs is constructed. A method for simplifying the MLCC equivalent source model is addressed from three aspects: frequency, power supply dc voltage, and ac noise amplitude. The developed source model library is validated by comparing the simulated and measured system vibration velocity. The proposed simplification method can significantly reduce model development efforts and enable the creation of a comprehensive source model library for MLCCs.

Index Terms—Acoustic noise, equivalent source model, multi-layer ceramic capacitor (MLCC), printed circuit board (PCB) vibration.

#### I. INTRODUCTION

ITH the rapid development of communication technology, electronic products are frequently updated, and requirements for the performance and size of electronic products are becoming more stringent. To ensure the stability of a power supply in an electronic system, capacitors are often used to reduce the power rail impedance of the system to stabilize the voltage. There are many types of capacitors, which, according to the type of dielectric utilized, can generally be divided into aluminum electrolytic capacitors, tantalum capacitors, and multilayer ceramic capacitors (MLCCs). Among these types,

Manuscript received 12 January 2024; revised 26 March 2024; accepted 21 April 2024. Date of publication 13 May 2024; date of current version 15 August 2024. This work was supported by National Science Foundation (NSF) under Grant IIP-1916535. (Corresponding author: Chulsoon Hwang.)

Yifan Ding and Chulsoon Hwang are with the Electromagnetic Compatibility Laboratory, Missouri University of Science and Technology, Rolla, MO 65401 USA (e-mail: dingyif@mst.edu; hwangc@mst.edu).

Ming-Feng Xue, Jianmin Zhang, Xin Hua, Benjamin Leung, and Eric A. MacIntosh are with Google LLC, Mountain View, CA 94043 USA (e-mail: mingfengx@google.com; jianmin@google.com; xihua@google.com; benleung@google.com; ericmac@google.com).

Color versions of one or more figures in this article are available at https://doi.org/10.1109/TEMC.2024.3397610.

Digital Object Identifier 10.1109/TEMC.2024.3397610

MLCCs are widely used because of their compact size, high capacitance density, and smaller equivalent series inductance and resistance.

Research on MLCCs involves many fields. In view of the characteristics of capacitors that can stabilize the system voltage, some studies have focused on the selection of appropriate capacitors to reduce the impedance of the power distribution network (PDN). The study in [1] developed basic models of a multilayer printed circuit board (PCB) power distribution bus, indicating that multilayer board decoupling capacitor placement strategies must emphasis on minimizing interconnect inductance. The theoretical basis of a novel technique suppressing cavity-mode resonances within the power-bus using discrete capacitors was built from the research in [2]. Guidelines for an optimized selection and placement of these capacitors were specified. Decoupling capacitors have been appropriately selected via a simple yet efficient "poles and zeros" algorithm for optimizing the PDN impedance, as introduced in [3]. Alternative methods for capacitor optimization can be achieved by using a genetic algorithm [4], [5] or other machine learning algorithms [6], [7], [8]. For characterizing the electrical properties of an MLCC, a physics-based circuit micromodel that included an inductance and capacitance model was established based on the partialelement equivalent-circuit method [9], as introduced in [10]. One part of this model, the equivalent inductance model, was further extended to a more complete model that could include the local environment for a two-terminal capacitor in [11] and a more complicated eight-terminal capacitor in [12]. Many studies have also focused on MLCC structures. Various dielectric materials, for example, the NiO-doped BaTiO<sub>3</sub> material in [13] and the CaCu<sub>3</sub>Ti<sub>4</sub>O<sub>12</sub> dielectric in [14], have been investigated to assess the performance and possibility of applications for MLCCs. Research has also focused on the usage limitations of these capacitors. For example, Gu et al. [15] explored the failure prognostics of an MLCC in temperature-humidity-bias conditions. In [16], a failure analysis of an MLCC board-level interconnect caused by monotonic bending stress was conducted.

In addition to the above studies on usage and failure analyses, there is widespread concern regarding the inclusion of ML-CCs in electronic products: the electrical-noise-induced acoustic noise issue. The root cause of this problem is the piezoelectric characteristic of the widely used MLCC dielectric BaTiO<sub>3</sub>. When an MLCC is soldered onto a PCB with alternating current (ac) noise applied, the piezoelectric medium inside the MLCC is subjected to the alternating electrical field, resulting in

0018-9375 © 2024 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See https://www.ieee.org/publications/rights/index.html for more information.

deformation following the expansion and contraction of the MLCC dielectric, which causes the PCB to vibrate and possibly generate acoustic noise [17]. This issue arises concerns especially in the hearable and wearable electrical devices, such as the earbuds, phones, watches, tablets, and even laptops. Considering this unavoidable issue caused by the MLCC, it is highly desirable to determine which capacitor among available choices will introduce weaker side effects into a system. Some studies have focused on "singing capacitor" noise issues. Simulation and measurement methodologies were introduced in [18] and [19], respectively, to obtain the noise via different methods. An automatic simulation flow was proposed for these investigations in [20]. Moving closer to the source of the noise issue, Ding et al. [21] defined the equivalent source as a force and introduced a methodology, for the first time, to quantify the force produced by an MLCC that results in PCB vibration. In [22], multiple types of equivalent sources were investigated to assess different application scenarios. Based on these studies, it is possible to develop a singing capacitor equivalent source model library to aid in the selection of capacitors with better performance and to provide insights for predicting system performance.

However, there are challenges in building an MLCC source model library. First, a large number of capacitors must be included in the source model library. Second, the equivalent source may be related to many factors. Thus far, the specific relationships between the equivalent source model and the capacitor type, capacitance value, frequency, and supply voltage level remain unknown. In this article, to investigate reasonable solutions for the abovementioned issues, the singing capacitor source model is simplified from the perspective of frequency, power supply direct current (dc) voltage level, and ac noise amplitude, and an equivalent source model library for six different MLCCs is built.

The rest of this article is organized as follows. The MLCC equivalent source model format is determined in Section II, together with an equivalent source extraction methodology for extracting the source model under limited conditions. The equivalent source model is simplified in terms of frequency and supply voltage in Section III. Following these investigations, the simplified source model is summarized and a source model library is built for six different MLCCs in Section IV, with model validation and usage examples. Finally, Section V concludes this article.

# II. SINGING CAPACITOR EQUIVALENT SOURCE MODEL AND QUANTIFICATION

To build a comprehensive library of singing capacitor equivalent sources, key steps include identifying the source manifestation, quantifying source values, and formatting the library for selected capacitors. This section gives the specific form of the equivalent source employed in this article and demonstrates the source extraction method for one example capacitor.

## A. MLCC Equivalent Source Model

Previous studies have made assumptions about the possible forms of equivalent sources for two-terminal capacitors based

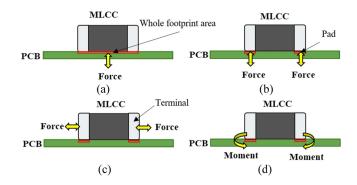

Fig. 1. Representative cases of MLCC equivalent sources.

on their internal deformation under an alternating electric field and the resultant PCB vibration response. The equivalent source from an MLCC can be intuitively modeled as a force applied to a footprint area that is perpendicular to the PCB plane (shown in Fig. 1(a) as assumed in [21]). Because MLCCs are generally connected to the PCB through soldering pads, another equivalent source model for a two-terminal capacitor consists of a pair of forces acting on the pad area [see Fig. 1(b)]. As stated in [23], the source can also be represented by combining the force pair in Fig. 1(b), another pair of forces applied normal to the MLCC terminals [see Fig. 1(c)], and one pair of moments representing the force in Fig. 1(c) transferred to the PCB via the capacitor pads [see Fig. 1(d)].

Each of the above four assumptions has been studied as a single source format in [22], and the advantages and suitable application scenarios were discussed. There are some special considerations to include when building a library of equivalent sources for verification and prediction purposes in simulations. First, the simulated PCB vibration response obtained by applying an equivalent source should be consistent with the measured vibration response over a wide frequency band. Second, a source that can be applied in the simulation without relying on the capacitor structure is preferred, because the material properties of the MLCC itself are not easy to obtain and meshing the MLCC will greatly increase the simulation time when the PCB has many capacitors mounted. Based on the results in [22], the equivalent source format shown in Fig. 1(d) is the most suitable choice for building a library. Thus, in the context of this article, the effect of PCB vibration caused by an MLCC will be modeled as a pair of moments.

### B. MLCC Equivalent Source Extraction Methodology

The combined simulation—measurement extraction methodology proposed in [21] and [22] for a moment-type source based on velocity de-embedding is written as

$$M_{\rm eq} = \frac{v_m}{v_s} \times M_{\rm unit} \tag{1}$$

where  $v_m$  is the measured velocity of the PCB vibration excited by the MLCC with a given power supply voltage at the observation point,  $v_s$  is the simulated velocity of the PCB vibration driven by the unit source at the same location,  $M_{\rm unit}$  is the unit moment excitation applied in the simulation, and  $M_{\rm eq}$  is the

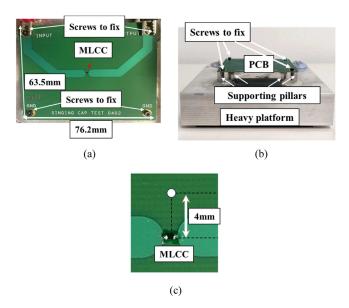

Fig. 2. Measurement setup for PCB vibration caused by an MLCC. (a) Top view of the setup. (b) Side view of the setup. (c) Location of the observation point to measure the PCB vibration.

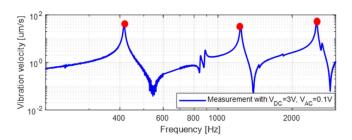

Fig. 3. Measured PCB vibration velocity at the observation point with a 3-V DC offset and 0.1-V AC noise from 200 to 3000 Hz.

MLCC equivalent moment under the given condition. The flow details have been clearly illustrated in [21].

To build an equivalent source library, one must first extract the equivalent source of a capacitor under one supply voltage condition. Here, a measurement was taken by using a laser Doppler vibrometer system, as described in [21]. The device under test (DUT) used in [22] is shown in Fig. 2(a) and (b). Four screws were used to fix the DUT. One 0402 capacitor from vendor 1 with a capacitance of 4.7  $\mu$ F was soldered onto pads with dimensions of 0.52 × 0.41 mm, with a pad center-to-center distance of 0.72 mm. A 3-V dc offset and 0.1-V ac sinusoidal noise from 200 to 3000 Hz was supplied to the power rail. The PCB vibration velocity was measured at the observation point at the location of the red dot in Fig. 2(c). The measured response is plotted in Fig. 3.

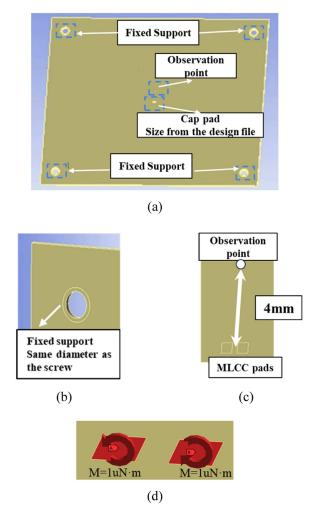

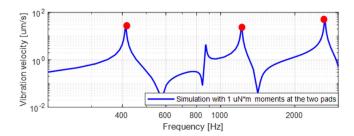

Simulations were performed in Ansys Mechanical by importing the PCB design file. The four fixed corners of the PCB, the pads at which the  $1-\mu N \cdot m$  unit moment pair is applied in opposite directions, and the observation location were set to be the same as the measurement. Details are shown in Fig. 4. The simulated PCB vibration velocity is displayed in Fig. 5.

To extract the equivalent source with better accuracy, as stated in [21], only the PCB vibrations at the mode resonances are

Fig. 4. Simulation setup for PCB vibration caused by a unit moment source. (a) PCB top view. (b) Example of a fixed support to mimic the screw in the measurement setup. (c) Location of the observation point to simulate the PCB vibration. (d) Application of a unit moment at the two pads.

Fig. 5. Simulated PCB vibration velocity at the observation point for one pair of unit moments from 200 to 3000 Hz.

considered when the equivalent moment is extracted. Specifically, three focused modes are shown as red dots in Fig. 5. The measured and simulated PCB vibration velocities at these modes are compared in Table I. Note that modes 1, 2, and 3 are the three focused modes, with measured frequencies of 416.5, 1235.5, and 2512.75 Hz and simulated frequencies of 412.28, 1215.8, and 2644.9 Hz, instead of the first three resonance frequencies of the board. Via velocity de-embedding, the equivalent source moments at these three modes were extracted, as given in Table I.

TABLE I

MEASURED, SIMULATED PCB VIBRATION VELOCITY, WITH THE EXTRACTED

MOMENT AT THE FOCUSED MODES

|                             | Mode 1 | Mode 2 | Mode 3 |

|-----------------------------|--------|--------|--------|

| Measured velocity [μm/s]    | 47.804 | 42.735 | 69.096 |

| Simulated velocity [µm/s]   | 30.206 | 28.593 | 55.406 |

| Equivalent Moment<br>[μΝ*m] | 1.58   | 1.49   | 1.25   |

The above extraction can be repeated for different power supply dc and ac voltage levels. However, sweeping all possible combinations in a brute-force manner is very time-consuming. Moreover, the above extraction method provides the equivalent moment source only at the selected resonance frequencies of the test-vehicle PCB. In practice, a comprehensive source format should be able to cover all possible supply voltage cases across the operating broadband. Frequency, dc voltage offset, and ac voltage noise are identified as key variables of the capacitor source. Thus far, all of this article is required for each given capacitor. Considering that a library includes the equivalent source for a large number of capacitors, a simplified method for building a library is needed to improve the efficiency.

# III. EQUIVALENT SOURCE MODEL SIMPLIFICATION AND GENERALIZATION

In this section, a method for simplifying the process of building a library in terms of frequency, power supply dc offset level, and power supply ac noise level is investigated, and a generalized MLCC equivalent source model is obtained. The capacitor used for this investigation is the same 0402 capacitor from vendor 1 presented in Section II-B.

#### A. Simplification in Terms of Frequency

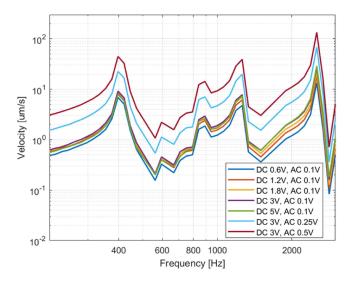

The first simplification focused on the frequency. For this step, the PCB vibration velocity at the observation point was measured under several power supply conditions, as plotted in Fig. 6. The entire data acquisition procedure took several hours. Because measuring the broadband vibration velocity response and extracting the corresponding source are time-consuming steps and the extracted equivalent moments are at the mode resonance frequencies only, it is worth evaluating the possibility of using the vibration or moment behavior at the mode frequencies to represent that over the broadband frequency.

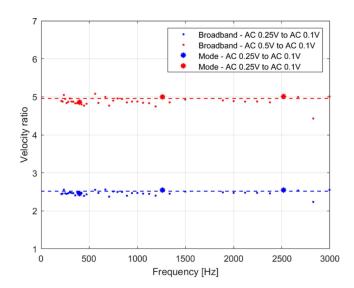

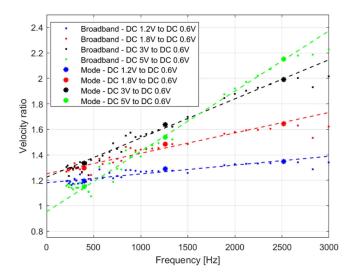

Here, the aim is to verify the ratio of the vibration velocity to a reference case in the broadband as the power supply dc offset or power supply ac noise level changes as a single variable. First, the supply voltage dc offset was fixed at 3 V. With the PCB vibration velocity for an ac noise amplitude of 0.1 V as a reference, the vibration velocity ratios for other ac noise amplitudes are shown in Fig. 7. Second, the supply voltage ac noise amplitude was fixed at 0.1 V. With the PCB vibration velocity for a dc offset of 0.6 V as a reference, the vibration velocity ratios of other dc offset levels are shown in Fig. 8. Ratios are employed in these two

Fig. 6. PCB vibration velocity measured in broadband with different power supply DC offsets and AC noise levels from 200 to 3000 Hz.

Fig. 7. Ratio of the PCB vibration velocity caused by different AC noise levels to the PCB vibration velocity caused by the 0.1-V reference ac noise level when the DC voltage is 3 V.

figures to indicate whether the source-induced PCB vibration behavior at the focused mode frequencies is consistent with that over the broadband. The small dots with a trend line were extracted from the measured frequencies within the frequency range of interest, and the large dots highlight ratios extracted from the focused resonance mode frequencies. It can be seen that in both plots, the trending lines depicted by the ratios at the mode frequencies consistently align with the broadband raw ratio trend. This observation indicates the possibility of applying linear curve fitting to extend the source extracted at focused resonance frequencies to the broadband.

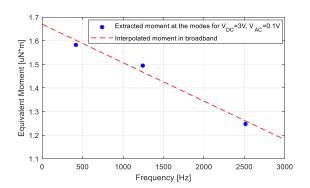

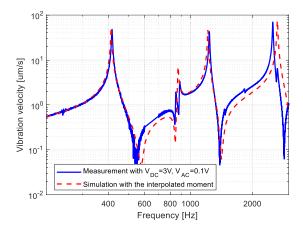

Fig. 9 shows the equivalent moment over the entire frequency range based on linear interpolation of the extracted moment, for a power supply dc voltage offset of 3 V and an ac noise amplitude of 0.1 V. To verify the performance of the synthesized broadband source mode, the frequency-dependent moment

Fig. 8. Ratio of the PCB vibration velocity caused by different DC noise levels to the PCB vibration velocity caused by the 0.6-V reference DC noise level when the AC voltage is 0.1 V.

Fig. 9. Extracted and interpolated equivalent moment source for the 0402 capacitor from vendor 1 for a supply DC voltage offset of 3 V and AC noise amplitude of 0.1 V.

value was applied in the simulation; these results are compared with the measured vibration velocity response in Fig. 10. The predicted response matched reasonably well with the actual PCB response. The discrepancy between the resonant frequencies might be caused by the manufacturing tolerance regarding the PCB dimensions and material properties. The measured vibration velocity shows two resonance peaks at approximately 800–900 Hz while the simulation shows only one resonance peak. This result occurs because the simulation model assumed a perfect symmetry for the upper and lower halves of the test board in Fig. 2(a). This comparison further validates the finding that for a given power supply dc voltage offset and ac noise level, the broadband moment values can be represented by linear interpolation of the moments extracted from the resonance frequencies as follows:

$$M(f) = \text{linear\_interp} (M(f_{\text{mode}})).$$

(2)

Here,  $f_{\rm mode}$  represents the focused mode frequencies at which the moments were extracted and f is the frequency in the bandwidth of interest.

Fig. 10. Comparison between the measured PCB vibration velocity for a supply DC voltage offset of 3 V and AC noise amplitude of 0.1 V and the simulated PCB vibration velocity based on the interpolated linear moment in Fig. 9.

Fig. 11. Extracted and interpolated equivalent moments for different supply DC voltage conditions with a reference AC noise amplitude of 0.1 V.

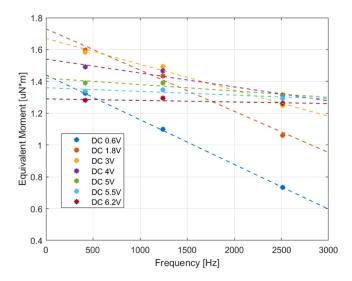

#### B. Simplification in Terms of Power Supply DC Voltage Level

A second investigation was conducted to simplify model library building for different supply dc voltage levels when the AC noise amplitude is fixed.

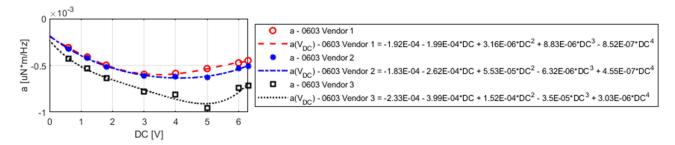

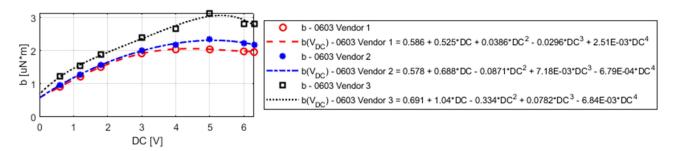

By applying the source extraction methodology for the same 0402 capacitor from Vendor 1 under different dc conditions with an ac noise level of 0.1 V, the equivalent moments at the resonance frequencies were obtained. After the frequency simplification and mode moment interpolation were performed, the moment curves over the broadband were obtained, as presented in Fig. 11. The linear interpolation worked well for all tested cases. Furthermore, the slopes and intercepts of the linear moment curves, represented by coefficients a and b with units of  $[\mu N \cdot m/Hz]$  and  $[\mu N \cdot m]$ , respectively, changed with dc offset. It can be concluded that for a specific ac noise amplitude  $V_{\text{AC\_ref}}$ , the general expression for the equivalent moment can be written as a linear function of frequency, as follows:

$$M(V_{DC}, f) = a(V_{DC}) \times f + b(V_{DC}). \tag{3}$$

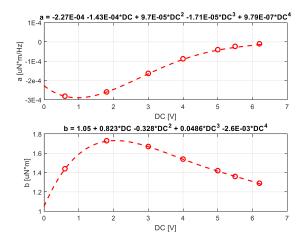

Fig. 12. Extracted and fitted linear fitting coefficients *a* and *b* under different supply DC voltage conditions.

Here,  $V_{\rm DC}$  is the power supply dc voltage offset, a and b are the linear fitting coefficients as a function of the dc offset, and f is the frequency. In this study case, the reference ac noise amplitude  $V_{\rm AC\_ref}$  is 0.1 V, and the dc offset level ranges from 0 V to the maximum allowed capacitor voltage of 6.3 V.

For each dc offset level, the corresponding linear fitting coefficients were extracted, as plotted in Fig. 12 (red circles). Fitted functions of a and b over the entire dc offset range of interest were obtained, and the coefficients of the unmeasured dc levels can be obtained from the interpolation function.

A similar study was performed for ac noise amplitudes of 0.25 and 0.5 V. Linear functions similar to (3) were also extracted, and coefficients a and b were computed. These coefficients show a proportional relationship with respect to the coefficients extracted for a 0.1-V ac noise amplitude. A detailed investigation of these trends is provided in the next section.

#### C. Simplification in Terms of Power Supply AC Voltage Level

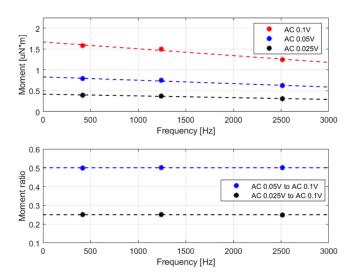

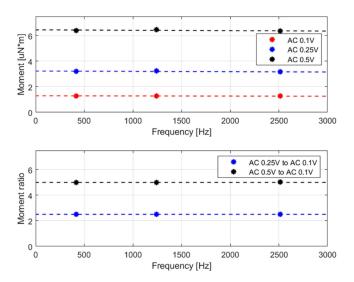

An investigation of the ac impact was performed as the last step of the model library simplification. This article was conducted with a fixed 3-V dc offset. Three ac noise amplitude conditions at 0.1, 0.05, and 0.02 V were tested.

Similarly, the mode moments were extracted and then extended to the entire broadband, as shown in Fig. 13, which indicates how the moment varies with changes in the ac noise amplitude. Taking the moment value for an ac noise amplitude of 0.1 V as a reference, the ratios of the moments for the other ac amplitude conditions to the reference moment were calculated, as shown in Fig. 13. The ratio of the two moments corresponds exactly to the ratio of the two ac levels, indicating that when the ac amplitude changes at a given dc condition, the equivalent moment changes at the same proportion.

To determine whether the above finding can be generalized to other dc and ac conditions, a similar study was conducted for the condition in which the supply dc voltage offset was 6.2 V. The ac level was set to 0.1 V, 0.25 V, or 0.5 V. As shown in Fig. 14, the obtained results are similar to those in Fig. 13; the ratio of

Fig. 13. Ratio of moments for different AC noise levels to moments for the 0.1-V reference AC noise level at a DC voltage of 3 V.

Fig. 14. Ratio of moments for different AC noise levels to moments for the 0.1-V reference AC noise level at a DC voltage of 6.2 V.

the two moments corresponds to the ratio of the two ac levels. Thus, it can be concluded that in the library building process, it is sufficient to measure and extract the moment for one reference ac noise condition for each dc offset level. Moments at the same dc level but different ac amplitudes can be calculated accordingly as follows:

$$M\left(V_{\mathrm{DC}}, V_{\mathrm{AC}}, f\right) = \frac{V_{\mathrm{AC}}}{V_{\mathrm{AC ref}}} \times M\left(V_{\mathrm{DC}}, V_{\mathrm{AC\_ref}}, f\right).$$

(4)

Here,  $V_{\rm DC}$  is the power supply dc voltage offset,  $V_{\rm AC}$  is the power supply ac voltage noise level,  $V_{\rm AC\_ref}$  is the reference power supply ac voltage noise level used to extract the reference equivalent moment profile  $M(V_{\rm DC},V_{\rm AC\_ref},f)$ , and f is the frequency. For the case studied in this article, within the frequency range of 200–3000 Hz, the focused ac noise amplitude  $V_{\rm AC}$  ranged from 0 V to 0.1 V, and the dc offset level  $V_{\rm DC}$  ranged from 0 V to the maximum allowed capacitor voltage of 6.3 V.

Fig. 15. 0402 capacitor library for coefficient a at a reference AC noise amplitude of 0.1 V.

#### D. Simplified Model Summary

Based on the above investigation, the equivalent moment source can be finally summarized as a function of frequency, power supply dc voltage offset, and ac noise level. The expression of the simplified source model is given as

$$M\left(V_{\mathrm{DC}}, V_{\mathrm{AC}}, f\right) = \frac{V_{\mathrm{AC}}}{V_{\mathrm{AC\_ref}}} \times \left(a\left(V_{\mathrm{DC}}\right) \times f + b\left(V_{\mathrm{DC}}\right)\right) \quad (5)$$

where  $V_{\rm DC}$  is the power supply dc voltage offset,  $V_{\rm AC}$  is the power supply ac voltage noise level,  $V_{\rm AC\_ref}$  is the reference power supply ac voltage noise level used to extract the linear fitting coefficients a and b, and f is the frequency. For the case studied in this article, within the frequency range of 200–3000 Hz, the focused ac noise amplitude  $V_{\rm AC}$  ranged from 0 to 0.1 V, and the dc offset level  $V_{\rm DC}$  ranged from 0 V to the maximum allowed capacitor voltage of 6.3 V.

The simplified source model shows that a comprehensive library can be built by extracting the equivalent moment under limited dc and ac voltage conditions at a certain mode resonance frequency. This procedure is summarized by the following three steps.

- To obtain moments over the entire frequency band of interest for all possible supply voltage conditions, from a frequency perspective, the broadband moment can be obtained via a linear interpolation of the mode moments.

- 2) For a given ac condition with different dc supply voltage conditions, the moment is a linear function of frequency, and the fitting coefficients are functions of the dc level. The fitting coefficients can be fitted from limited measurement cases performed for a certain dc condition.

- 3) For a given dc condition with different ac noise conditions, the moment will vary as the ac noise level changes at the same proportion over all frequencies.

Hence, for each dc condition, only one measurement for one reference ac is needed. For other ac levels, the moment can be calculated by using the corresponding ratio. In the equivalent source library, the values of a, b, and the reference ac level will be given instead of equivalent source values for different cases.

# IV. EQUIVALENT SOURCE MODEL LIBRARY AND USAGE EXAMPLE

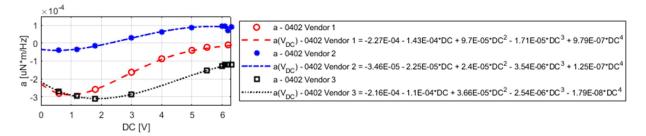

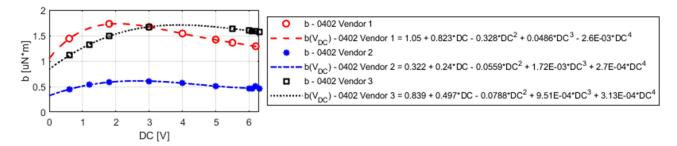

## A. MLCC Source Model Library

The MLCC equivalent source model library was first built for six capacitors, including three 0402 package-size capacitors

with a capacitance of 4.7  $\mu$ F from three different vendors and three 0603 package-size capacitors with a capacitance of 22  $\mu$ F from the same three vendors as the 0402 capacitors. All six capacitors have the same maximum allowed voltage of 6.3 V. Following the process described above, the equivalent moments of the six capacitors were extracted under the conditions of a 0.1-V reference ac noise level with different dc offsets. The coefficients a and b for constructing the library were obtained through curve fitting, as shown in Figs. 15, 16, 17, and 18. Each individual source model for different dc and ac conditions was determined via interpolation. These individual models formed a complete model set for each capacitor, and thus, the model library was established by including the model set from those individual capacitors. It should be noted that for all 0402 capacitors, the pad size was the same as that given in Section II-B. For all 0603 capacitors, the pad size was  $0.88 \times 0.65$  mm, and the pad center-to-center distance was 1.45 mm.

The fitted a coefficients of the three selected 0402 capacitors show a similar trend as the dc offset level changes; the fitted b coefficients show a similar trend as well. Within the focused dc supply voltage range, the value of a first decreases and then increases with the dc level whereas the value of b shows the opposite trend. The same trend was observed for the fitted a and b coefficients of the three selected 0603 capacitors. For some MLCCs, the value of a can be 0 at a certain dc voltage, which means that the equivalent moment is constant throughout the entire frequency range. One example is the 0402 capacitor from Vendor 2 at a 2.27-V dc offset level, where the a coefficient is 0, as shown in Fig. 15. However, this situation does not always arise. The results for the fitted a and b coefficients reveal that different voltage levels have different effects on the internal deformation of the capacitor and thus the energy transferred to the external carrier test-vehicle PCB.

Based on the developed equivalent moment source model shown in Figs. 15, 16, 17, and 18, it can be determined that the moment value of a source model is not necessarily proportional to its physical dimensions; indeed, a trend may not even arise, which means that, in some cases, an MLCC with a large body size can have smaller moment values than a smaller body-sized MLCC. This result occurs because the absolute value of the equivalent source is related not only to the size of the capacitor, but also to the capacitance value, internal structure, and medium used inside the capacitor, as well as the voltage and frequency at which the capacitor operates. In addition, even if the moment is the same for two different MLCC body sizes, the PCB vibrations excited by the two MLCCs differ as the center-to-center distance

Fig. 16. 0402 capacitor library for coefficient b at a reference AC noise amplitude of 0.1 V.

Fig. 17. 0603 capacitor library for coefficient a at a reference AC noise amplitude of 0.1 V.

Fig. 18. 0603 capacitor library for coefficient b at a reference AC noise amplitude of 0.1 V.

of the soldering pads for the two MLCCs varies. Because of this difference, the same applied moment will result in different PCB vibration responses.

### B. Library Usage Example

This section presents two examples to validate the MLCC source model and its usage.

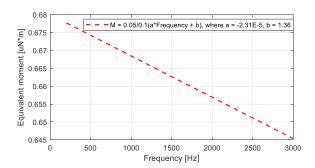

The first validation was conducted by predicting the PCB vibration velocities via the equivalent moment source derived from the source model library for the 0402 capacitor from vendor 1 investigated in the previous sections. The power rail had a 6-V dc offset and 0.05-V ac noise amplitude. As shown in Figs. 15 and 16, the reference ac amplitude  $V_{\rm AC\_ref}$  was 0.1 V. For this condition, when the supply dc voltage level was 6 V, based on the two figures, the coefficients a and b were calculated as  $-2.31 \times 10^{-5} \, \mu \rm N \cdot m/Hz$  and  $1.36 \, \mu \rm N \cdot m$ , respectively. Then, for an ac amplitude of 0.05 V, the ratio to the reference ac value was calculated from (5) as 0.5. The equivalent moment source for the 0402 vendor 1 capacitor with a 6-V dc offset and 0.05-V ac amplitude is plotted in Fig. 19. The predicted equivalent moment

Fig. 19. Calculated equivalent moment source for the 0402 capacitor from Vendor 1 at a supply DC voltage offset of 6 V and AC noise amplitude of 0.05 V.

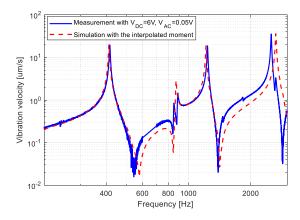

was applied to the two capacitor pads separately in opposite directions, as shown in Fig. 4(d). The simulated PCB vibration velocity response over the frequency range is provided in Fig. 20 as a dashed line.

To verify the accuracy of the simulated PCB vibrations obtained from the derived source model, another measurement was performed. The measurement setup shown in Fig. 3 was used,

Fig. 20. Comparison between the measured PCB vibration velocity for a supply DC voltage offset of 6 V and AC noise amplitude of 0.05 V and the simulated PCB vibration velocity based on the moment calculated in Fig. 19.

TABLE II COEFFICIENTS A AND B AND THE EQUIVALENT MOMENT FOR THE THREE 0402 CAPACITORS FOR A 3.3-V DC OFFSET AND 0.05-V 2000-Hz AC NOISE

| Vendor   | a (μN • m/Hz) | b (μN • m) | M (μN • m) |

|----------|---------------|------------|------------|

| Vendor 1 | -1.41E-4      | 1.63       | 0.68       |

| Vendor 2 | 4.01E-5       | 0.59       | 0.34       |

| Vendor 3 | -2.74E-4      | 1.69       | 0.57       |

and a 6-V dc power supply with 0.05-V ac noise was applied. The measured PCB vibration velocity is shown in Fig. 20 as a solid line. Comparison of the two curves shown in Fig. 20 confirms that the simulated vibration velocity obtained via the source model from the model library matches reasonably well with the measured PCB vibration response. This result validates the MLCC source model library and demonstrates the feasibility of the proposed method for obtaining the source model under any power rail loading conditions based on the interpolation method for the  $\alpha$  and b coefficient library.

In addition to the system-level vibration response prediction discussed above, the source model library can be used for selecting the appropriate decoupling capacitor to improve system acoustic performance while maintaining the requirement of low PDN impedance. For a 3.3-V dc power rail, the assumption is that there is a significant amount of ac noise (50 mV) at 2000 Hz. A related PDN simulation and PDN optimization can be achieved by following general power integrity modeling methodologies [3]. After the decoupling capacitors are selected and the PDN requirement met, the following step is to determine whether these capacitors are good for system acoustic performance. For this, the MLCC source model library can be used. As an example, assume that a  $4.7-\mu F$  0402 MLCC is used as one of the decoupling capacitors in the PDN. Similarly, the a and b coefficients at 3.3 V can be extracted for capacitors from the three different vendors. The equivalent moments are calculated by applying an ac noise amplitude of 0.05 V at a frequency of 2000 Hz to (5). Calculated equivalent moments for capacitors from three different vendors are given in Table II. Comparison shows that the 0402 capacitor from vendor 2 should be selected for the power rail under discussion. Because it is very unlikely that the electrical models are exactly the same in terms of parasitic parameters, multiple iterations of simulation and optimization are necessary, and a tradeoff between electrical and acoustic performance might be needed. This newly proposed combined electrical and acoustic optimization methodology will further improve system performance for mobile electronic devices, and the MLCC source model library is key to this success.

# V. CONCLUSION

This article started from the goal of building a comprehensive MLCC equivalent source model library. The equivalent source model format was determined as a pair of moments loaded on two capacitor pads. On the basis of being able to extract the equivalent source under certain conditions, the source model was simplified in terms of frequency, power supply dc voltage, and ac noise amplitude on the power rail. To obtain the moment over the entire frequency band of interest for all possible power supply loading conditions, from a frequency perspective, the broadband moment can be obtained via linear interpolation of the mode moments. Two linear fitting coefficients were extracted and fitted for different dc levels. As the ac noise amplitude varies, the moment will change proportionally throughout the entire frequency band. With the aid of the simplification method, the source model library can be constructed to cover all user cases in which only source model extraction under limited working conditions is needed. The equivalent source model can be obtained for other working conditions from the library via interpolation.

An equivalent source model library was built with six involved MLCCs as an example. The library was validated by a comparison of the simulated and measured PCB vibration velocities. The MLCC vibration source model is critical to system performance for mobile electronic devices, such as smart phones, watches, and ear buds, which can provide insight into characterizing the impact of MLCCs at the system level during the design stage. By predicting the unwanted impact of MLCCs on the PCB and strategically selecting capacitors or adjusting component placement, the acoustic noise generated by PCB vibrations via MLCC vibration can be significantly reduced or fully mitigated in actual product designs.

#### REFERENCES

- T. H. Hubing, J. L. Drewniak, T. P. Van Doren, and D. M. Hockanson, "Power bus decoupling on multilayer printed circuit boards," *IEEE Electromagn. Compat. Mag.*, vol. 9, no. 2, pp. 66–77, 2nd Quarter 2020.

- [2] M. Hampe and S. Dickmann, "Damping of cavity-mode resonances in PCB power-bus structures using discrete capacitors," *IEEE Trans. Electromagn. Compat.*, vol. 47, no. 4, pp. 880–888, Nov. 2005.

- [3] Y. Ding et al., "System level PDN impedance optimization utilizing the zeros of the decoupling capacitors," in *Proc. IEEE Int. Symp. Electromagn. Compat.*, Signal Power Integrity, 2023, pp. 249–254.

- [4] S. Kahng, "GA-optimization for finding decoupling capacitors to damp the rectangular power-bus resonances," in *Proc. 18th Int. Zurich Symp. Electromagn. Compat.*, 2007, pp. 103–106.

- [5] F. De Paulis et al., "A methodical approach for PCB PDN decoupling minimizing overdesign with genetic algorithm optimization," in *Proc. IEEE Int. Symp. Electromagn. Compat., Signal Power Integrity*, 2022, pp. 238–243.

- [6] L. Zhang, L. Jiang, J. Juang, Z. Yang, E.-P. Li, and C. Hwang, "Decoupling optimization for complex PDN structures using deep reinforcement learning," *IEEE Trans. Microw. Theory Techn.*, vol. 71, no. 9, pp. 3773–3783, Sep. 2023.

- [7] S. Hemaram and J. N. Tripathi, "Optimal design of a decoupling network using variants of particle swarm optimization algorithm," in *Proc. IEEE Int. Symp. Circuits Syst.*, 2021, pp. 1–5.

- [8] H. Manoharan et al., "Augmented genetic algorithm v2 with reinforcement learning for PDN decap optimization," in *Proc. IEEE Int. Symp. Electromagn. Compat.*, Signal Power Integrity, 2023, pp. 255–258.

- [9] A. Ruehli, G. Antonini, and L. Jiang, Circuit Oriented Electromagnetic Modeling Using the PEEC Techniques, Hoboken, NJ, USA: Wiley, 2017.

- [10] N. Bondarenko et al., "Development of simple physics-based circuit macromodel from PEEC," *IEEE Trans. Electromagn. Compat.*, vol. 58, no. 5, pp. 1485–1493, Oct. 2016.

- [11] T. Makharashvili et al., "Accurate inductance models of mounted twoterminal decoupling capacitors," *IEEE Trans. Electromagn. Compat.*, vol. 63, no. 1, pp. 237–245, Feb. 2021.

- [12] T. Makharashvili et al., "Circuit models for the inductance of eight-terminal decoupling capacitors," *IEEE Trans. Compon. Packag. Manuf. Technol.*, vol. 10, no. 1, pp. 142–150, Jan. 2020.

- [13] T. M. S. A. Hossain, M. A. Matin, M. A. Hakim, and M. F. Islam, "Fabrication and characterization of NiO-doped BaTiO3for multilayer ceramic capacitor," in *Proc. 10th Int. Conf. Elect. Comput. Eng.*, 2018, pp. 77–80.

- [14] J. Kulawk, D. Szwagierczak, and B. Synkiewicz, "Multilayer ceramic capacitors with CaCu3Ti4O12 dielectric," in *Proc. ISAF-ECAPD-PFM*, 2012, pp. 1–4.

- [15] J. Gu, M. H. Azarian, and M. G. Pecht, "Failure prognostics of multilayer ceramic capacitors in temperature-humidity-bias conditions," in *Proc. Int. Conf. Prognostics Health Manage.*, 2008, pp. 1–7.

- [16] H. Wang, C. Liang, T. Lu, H. Xiao, and W. Tian, "Failure analysis of multilayer ceramic capacitor board level interconnect caused by monotonic bending stress," in *Proc. 11th Int. Conf. Rel., Maintainability Saf.*, 2016, pp. 1–5.

- [17] Y. Ding et al., "Extraction for multilayer ceramic capacitor vibration induced force," in *Proc. IEEE Int. Symp. Electromagn. Compat., Signal Power Integrity*, 2023, pp. 115–119.

- [18] Y. Sun, S. Wu, J. Zhang, C. Hwang, and Z. Yang, "Simulation methodologies for acoustic noise induced by multilayer ceramic capacitors of power distribution network in mobile systems," *IEEE Trans. Electromagn. Compat.*, vol. 63, no. 2, pp. 589–597, Apr. 2021.

- [19] Y. Sun, S. Wu, J. Zhang, C. Hwang, and Z. Yang, "Measurement methodologies for acoustic noise induced by multilayer ceramic capacitors of power distribution network in mobile systems," *IEEE Trans. Electromagn. Compat.*, vol. 62, no. 4, pp. 1515–1523, Aug. 2020.

- [20] X. Yan et al., "A methodology for predicting acoustic noise from singing capacitors in mobile devices," *IEEE Trans. Electromagn. Compat.*, vol. 65, no. 4, pp. 1266–1270, Aug. 2023.

- [21] Y. Ding et al., "Equivalent force extraction methodology for electrical component induced PCB vibration," *IEEE Trans. Electromagn. Compat.*, vol. 66, no. 1, pp. 270–280, Feb. 2024.

- [22] Y. Ding et al., "Equivalent source investigation for PCB vibration excited by a multi-layer ceramic capacitor," *IEEE Trans. Electromagn. Compat.*, to be published, doi: 10.1109/TEMC.2024.3374254.

- [23] B. H. Ko, S. G. Jeong, Y. G. Ahn, K. S. Park, N. C. Park, and Y. P. Park, "Analysis of the correlation between acoustic noise and vibration generated by a multi-layer ceramic capacitor," *Microsystem Technol.*, vol. 20, pp. 1671–1677, 2014.

Ming-Feng Xue received the B.S. degree in electronic information engineering from Anhui University, Hefei, China, in 2005, the M.S. degree in electromagnetic field and microwave technology from Shanghai Jiao Tong University, Shanghai, China, in 2008, and the Ph.D. degree in electrical and computer engineering from the University of Illinois at Urbana-Champaign, Urbana, Illinois, in 2014, respectively.

After graduation, he was a Signal Integrity Engineer with Apple Inc. Since 2021, he has been a senior hardware engineer with Pixel Ecosystem team in

Google. His research interests include electromagnetic modeling, multiphysics simulation, and parallel computing.

**Jianmin Zhang** (Senior Member, IEEE) received the B.S. degree from Southeast University, Nanjing, China, and the M.S. and Ph.D. degrees in electrical engineering from the University of Missouri-Rolla with EMC lab in 2003 and 2007, respectively.

He is currently a Hardware Engineering manager with Google, Menlo Park, CA, USA. Before joining Google, he was a SI/PI and RFIC Technical Lead in Apple, a SMTS SI Engineer in Altera Corporation, and a Hardware Technical Lead in Cisco Systems. He has authored or coauthored more than 60 technical

papers including journals and conference papers, and reviewed more than 200 academic papers for journals, international conferences and book proposals. He has served as technical committee members, review board members, session chairs and co-chairs for conferences including IEEE EMC/SIPI Symposium, DesignCon, and EMC Europe etc. His research interests include signal integrity and power integrity for package, PCB and systems, RF desense, co-existence and EMC modeling and analysis, SIP module self-shielding and modeling techniques, singing capacitor source model development, and eNoise modeling and analysis.

Dr. Zhang was the recipient of the Technical Achievement Award from IEEE EMC Society in 2019 for contributions to the understanding and practice of RF de-sense and co-existence through modeling and measurements, and application in product design. He was the co-advisor of the Best Symposium Student Paper Award from IEEE EMC Society for the year 2018 and 2010He is also the recipient the Conference Best SI Paper Award from the International Microelectronics and Packaging Society in 2007, and the Best Symposium Paper Award and the Best Symposium Student Paper Award both from IEEE EMC Society in 2006.

**Xin Hua** received the B.S. and M.S. degrees in automotive engineering in China and the Ph.D. degree in mechanical engineering from the University of Kentucky, Lexington, KY, USA, in 2013.

He is currently a Hardware Engineer with Google, Menlo Park, CA, USA. Prior to that, he worked in the automotive and aerospace industries for about ten years. He specializes in vibro-acoustics with more than 30 publications.

Yifan Ding (Student Member, IEEE) received the B.S. degree in electrical engineering from Zhejiang University, Hangzhou, China, in 2019. She is currently working toward the Ph.D. degree in electrical engineering with the EMC Laboratory, Missouri University of Science and Technology, Rolla, MO, USA.

Her research interests include system-level power distribution network modeling and design optimization, power supply induced jitter analysis in I/O buffer, and acoustic noise in multilayer ceramic capacitors.

Benjamin Leung received the B.S. degree in electrical and computer engineering and computer science from University of Wisconsin—Madison, Madison, WI, USA in 1994, and the M. Eng. degree in electrical engineering from Cornell University, Ithaca, NY, USA, in 1996.

He worked in design and development of systems in various applications and industries, from telecommunication to consumer products, since 1996. He is currently with Google, Menlo Park, CA, USA, focusing on wearables systems design and development.

His current interests are on system miniaturization, system electrical and acoustic noise effects, and RF and antenna miniaturization.

Eric A. MacIntosh (Member, IEEE) received the Bachelor of Science degree in engineering (electrical) from the University of New Brunswick, Fredericton, NB, Canada, in 1999, and the Master of Science degree in electrical engineering from Stanford University, Stanford, CA, USA, in 2001.

He is currently a Senior Director of engineering for Pixel Ecosystem Products with Google, Mountain View, CA, USA. Previously, he was a Senior Engineering Manager with Amazon Lab126 and a Product Engineer for MindTribe and an Engineer with

IDEO. His interests have focused on wearable computing, audio products, and embedded systems.

**Chulsoon Hwang** (Senior Member, IEEE) received the Ph.D. degree in electrical engineering from the KAIST, Daejeon, South Korea, in 2012.

He was a Senior Engineer with Samsung Electronics, Suwon, South Korea, from 2012 to 2015. In July 2015, he was with the Missouri University of Science and Technology (formerly University of Missouri-Rolla), Rolla, MO, USA, where he is currently an Associate Professor. His research interests include RF desensitization, signal/power integrity in high-speed digital systems, EMI/EMC, hardware security, and

machine learning.

Dr. Hwang is currently an Associated Editor for IEEE TRANSACTIONS ON SIGNAL AND POWER INTEGRITY. He was a recipient of the AP-EMC Young Scientist Award, the Google Faculty Research Award, and Missouri S&T's Faculty Research Award. He has also been a co-recipient of eight Best/Best Student Paper Awards from various conferences.