# Modeling and Optimization of Peaking Inductors for X-band Circulator in Standard 0.18 $\mu\text{m}$ CMOS

Sakib Reza, and Ifana Mahbub

Department of Electrical and Computer Engineering

The University of Texas at Dallas, Texas, 75080, USA.

Email: {sakib.reza, ifana.mahbub}@utdallas.edu

*Abstract-Circulator* plays a crucial role in the operation of full-duplex radio systems. The major challenge in achieving full-duplex architecture is to isolate the transmitter (TX) channel from the receiver (RX) one. In this paper, an active circulator based on three bridged-T networks which consist of several peaking inductors exploiting a standard 0.18  $\mu\text{m}$  CMOS technology is designed. It is capable of boosting the isolation between the TX and RX channels over a wide frequency range. As part of the proposed circulator design, a tuning platform is devised to explore the impact of various design variables of the peaking inductors on radio frequency benchmarks. It regulates the isolation and insertion loss of the proposed circulator through the assessment of scattering parameters. The simulation results indicate that between the TX and RX channels, a maximum isolation of 43.38 dB at 9.6 GHz is achieved while maintaining at least 30.08 dB of isolation over the whole X-band. The proposed circulator exhibits promising characteristics as a potential choice for duplexer where substantial isolation and wide bandwidth are paramount.

**Index Terms**-full-duplex communication, circulator, peaking inductor, CMOS, isolation, insertion loss.

## I. INTRODUCTION

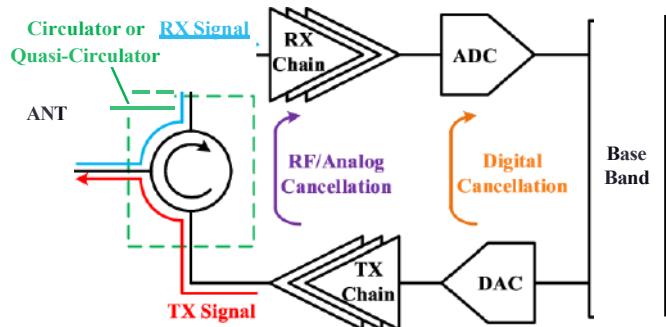

To address the escalating requirements of data transmission in radio systems, there has been a persistent endeavor to augment the frequency range and enhance their spectral efficiency. This is accomplished through the reinforcement of operating bandwidths and the implementation of sophisticated modulation methodologies. One potential approach to expand the radio band by two times maintaining a consistent frequency for simultaneous signal transmission and reception is to explore the implementation of an in-band full duplexing (IBFD) method [1]-[3]. The primary obstacle encountered within an IBFD setup pertains to the suppression of self-interference (SI) between transmit (TX) and receive (RX) channels. Various techniques such as the implementation of multiple antennas, electrical balance duplexers (EBDs), and circulators have been proposed as potential means to mitigate the effects of SI [4]. As the utilization of multi-antenna technology necessitates the incorporation of several antennas in each channel of the transceiver system, they might not be more cost-effective than the monostatic antenna system. The EBD requires a singular antenna for each channel; however, they are unsuitable for better area and bandwidth management. On the other hand, circulators as shown in Fig. 1 used as the shared antenna interfaces exploiting the nonreciprocity of active devices have emerged as an up-and-coming alterna-

Fig. 1. CMOS circulator in a monostatic full-duplex system [14].

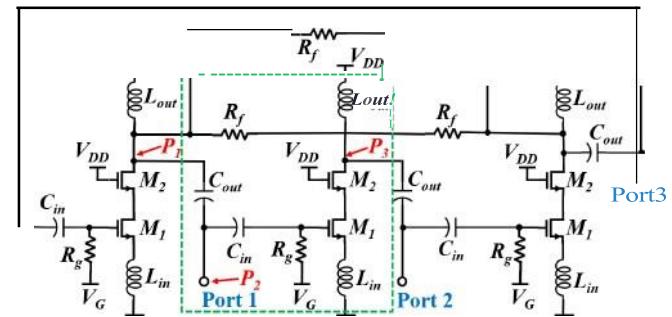

Fig. 2. Schematic of the proposed CMOS circulator.

tive owing to their better bandwidth manipulation, compact dimensions, and cost-effectiveness. Transistor-enabled active circulators limit high isolation bandwidth between the TX and RX, and a low insertion loss simultaneously. A number of active circulators have been proposed recently to meet the demand of high isolation where inductive peaking is employed for bandwidth enhancement [5]-[8]. Passive filtering including series and shunt peaking has been exploited to broaden amplifier bandwidth [9]-[13]. However, the impact of these peaking inductors on radio frequency (RF) benchmarks including isolations, insertion losses, and return losses has not been well addressed.

In this paper, an active circulator operating at X-band with an isolation of at least 30.08 dB between the TX and RX which is suitable for monostatic IBFD radar applications is proposed exploiting peaking inductors optimization in a standard 0.18  $\mu\text{m}$  CMOS technology. To the best of the authors' knowledge, this is the first paper to explore the impact of the different

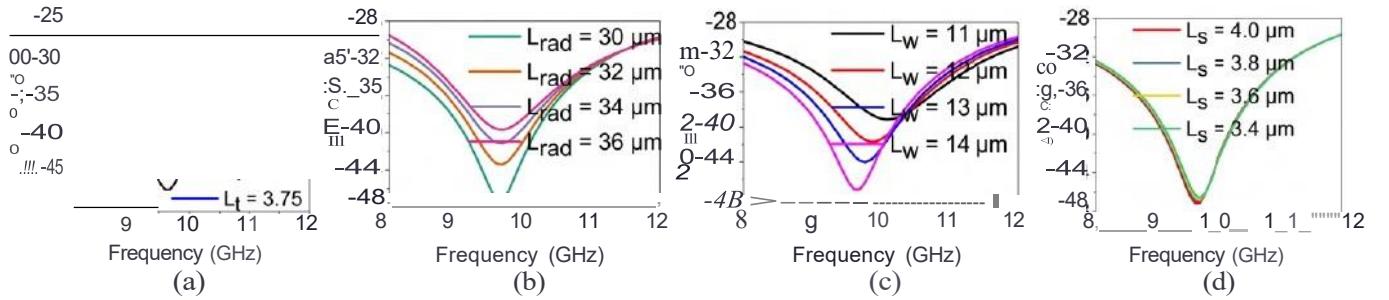

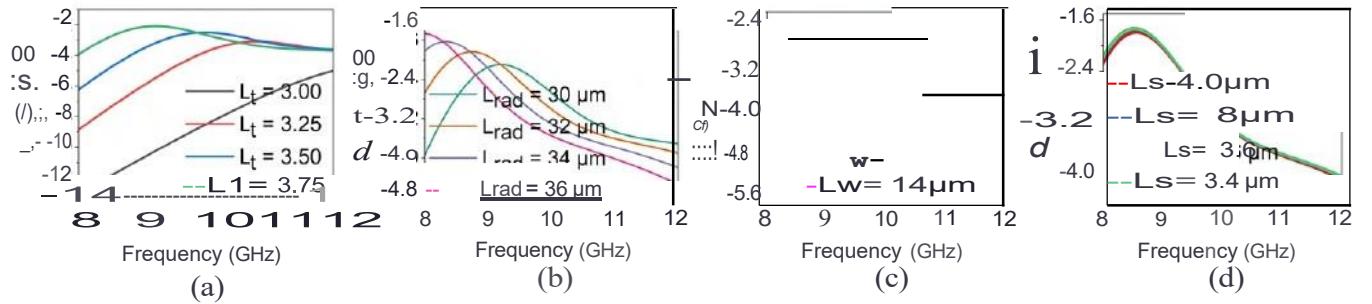

Fig. 3. Regulation of inductor parameters (a) number of turns ( $L_t$ ), (b) inner radius ( $L_{rad}$ ), (c) width ( $L_w$ ), and (d) inter-turn spacing ( $L_s$ ) on TX-RX isolation (S31).

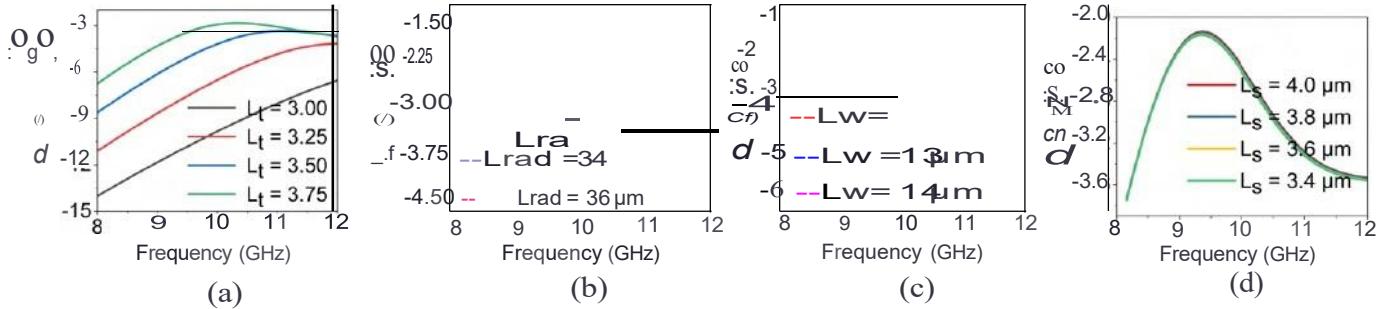

Fig. 4. Regulation of inductor parameters (a) number of turns ( $L_t$ ), (b) inner radius ( $L_{rad}$ ), (c) width ( $L_w$ ), and (d) inter-turn spacing ( $L_s$ ) on insertion loss (IL) from ANT to RX (S32).

Fig. 5. Regulation of inductor parameters (a) number of turns ( $L_t$ ), (b) inner radius ( $L_{rad}$ ), (c) width ( $L_w$ ), and (d) inter-turn spacing ( $L_s$ ) on insertion loss (IL) from TX to ANT (S21).

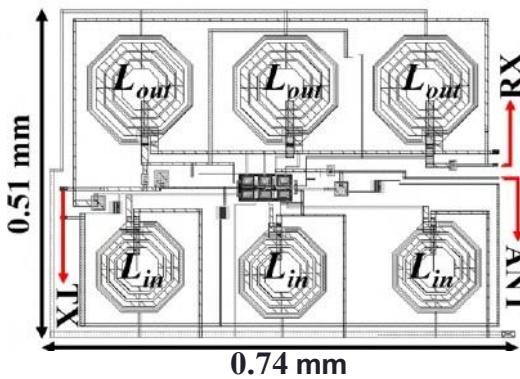

Fig. 6. Layout of the proposed CMOS circulator.

attributes of peaking inductors i.e., inductor width, number of turns, etc. on performance metrics including isolation and insertion loss through the assessment of circulator port parameters while satisfying the requirements of RF benchmarks including better bandwidth regulation.

## II. PROPOSED CMOS CIRCULATOR DESIGN

In this work, a three-port CMOS circulator in a standard  $0.18 \mu\text{m}$  CMOS technology using three bridged-T networks (BTNs) is proposed as shown in Fig. 2. Here ports denoted as 1, 2, and 3 of the circulator are linked to the TX, antenna (ANT), and the RX, respectively.  $P_1$  and  $P_3$  are mutually disconnected from one another and are interconnected to synthesize a circulator with a ring-like configuration. The BTN is a three-terminal asymmetric system with a bandstop characteristic of  $1S_{31}$  [5]. The green dotted line in Fig. 2 marks a single BTN. The input capacitor ( $G_{in}$ ), output capacitor ( $G_{out}$ ), and feedback resistor ( $R_1$ ) are the fundamental components of the BTN. Moreover, the BTN employs a grounded inductor ( $L_{in}$ ) to amplify the cancellation of  $1S_{31}$  and a cascode amplifier to yield boosted gain and isolation between the  $P_2$  and  $P_3$  for maximum transmission ratio. The cascode architecture includes the Common Source (CS) stage ( $M_1$ ) and Common Gate (CG) stage ( $M_2$ ).  $R_9$  is a high-

TABLE I

COMPARISON WITH RECENTLY REPORTED WORKS

| Metric                        | [15]               | [16]                | [17]               | This work          |

|-------------------------------|--------------------|---------------------|--------------------|--------------------|

| Technology                    | 0.65- $\mu$ m CMOS | 0.22- $\mu$ m FDSOI | 0.13- $\mu$ m CMOS | 0.18- $\mu$ m CMOS |

| Frequency (GHz)               | 6-7.5              | 60                  | 2.45               | 8-12               |

| $S_{11}$ (dB)                 | >10                | 8.5                 | 6                  | 8.8                |

| $S_{22}$ (dB)                 | >10                | 25                  | 10                 | 9.66               |

| $S_{33}$ (dB)                 | >10                | 8.8                 | 11                 | 10.1               |

| Insertion loss, $S_{21}$ (dB) | 6.47               | 6                   | >3.2               | <7.42              |

| Insertion loss, $S_{32}$ (dB) | 6.78               | 6.5                 | >6.97              | <7.27              |

| Isolation, $S_{31}$ (dB)      | 16.92              | 22                  | >20                | >30.08             |

| Noise Figure (dB)             | 8.16               | <b>NIA</b>          | 6.5                | 4.8                |

| Area (mm)                     | 1.53               | <b>NIA</b>          | <b>NIA</b>         | 0.38               |

| Power handling (TX-ANT) (dBm) | 17.3               | 10.18               | 8                  | 20                 |

| Power dissipation (mW)        | <b>NIA</b>         | 6                   | 121                | 7.6                |

All tabulated data are based on simulation.

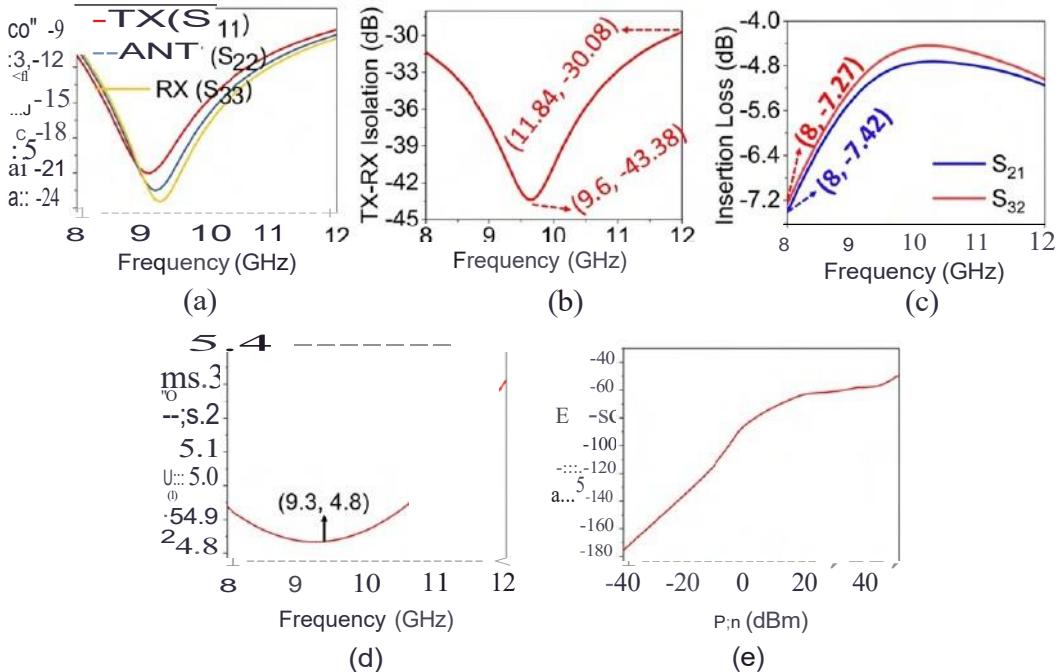

Fig. 7. Simulation results of (a) return loss, (b) TX-RX isolation ( $S_{31}$ ), (c) insertion loss  $S_{21}$  (from TX to ANT), and  $S_{32}$  (from ANT to RX), (d) Noise figure (from ANT to RX), (e) I dB compression point.

value resistor providing a DC path to the gate of transistors. As discussed earlier, one of the design pitfalls in devising efficient IBFD systems exploiting circulators is to achieve high isolation bandwidth and at the same time low insertion loss. Here, inductive peaking ( $L_{out}$ ) is employed in order to enhance the bandwidth. However,  $L_{out}$  should impact other performance metrics like TX-RX isolation, and insertion loss from the TX to ANT and the ANT to the RX. In Fig. 3, the regulation of different design variables of the peaking inductor,  $L_{out}$  on TX-RX isolation ( $S_{31}$ ) are explored. Fig. 3(a) demonstrates the impact of the number of turns ( $L_t$ ) on

$S_{31}$  revealing that as  $L_t$  increases  $S_{31}$  degrades. While  $L_t$  is tuned in Fig. 3(a), other inductor variables including inner radius ( $L_{rad}$ ), width ( $L_w$ ), and inter-turn spacing ( $L_s$ ) are set to 36  $\mu$ m, 14  $\mu$ m, and 4  $\mu$ m, respectively. In Fig. 3(b),  $L_{rad}$  is modulated keeping  $L_t$ ,  $L_w$ , and  $L_s$  as 3, 14  $\mu$ m and 4  $\mu$ m respectively pertaining that as  $L_{rad}$  increases  $S_{31}$  degrades but the peak of  $S_{31}$  remains constant with the change in frequency.  $L_w$  is tuned in Fig. 3(c) while  $L_t$ ,  $L_{rad}$ , and  $L_s$  are fixed to 3, 36  $\mu$ m, and 4  $\mu$ m, respectively, where it is noticed that as  $L_w$  increases,  $S_{31}$  improves. Finally,  $L_s$  is regulated in Fig. 3(d) placing  $L_t$ ,  $L_{rad}$ , and  $L_w$  as 3, 36  $\mu$ m, and 14  $\mu$ m,

respectively referring that  $S_{31}$  remains almost the same with the modulation of  $L_s$ . From Fig. 3, it can be concluded that to boost  $S_{31}$ ,  $L_t$  and  $L_{rad}$  are needed to be decreased while  $L_w$  demands to be increased. In a similar fashion, the impacts of design variables of  $L_{out}$  on the insertion loss from ANT to RX ( $S_{32}$ ) and TX to ANT ( $S_{21}$ ) are explored in Fig. 4 and Fig. 5, respectively, where it is proved that to improve the insertion losses,  $L_t$  and  $L_{rad}$  are needed to be increased which is the opposite case of isolation in Fig. 3. On the other hand, from Fig. 4(c) and 5(c) it is noticed that the peaks of  $S_{32}$  and  $S_{21}$  shift with frequency meaning a resonant frequency band is formed with the tuning of  $L_w$ . Also, from Fig. 4(d) and 5(d), it can be seen that insertion losses are almost the same with the tuning of  $L_s$  as in the case of isolation. As it is observed that  $L_t$  and  $L_{rad}$  impact the isolation and insertion loss in a non-harmonic fashion, a trade-off is demanded to meet the design specifications. Also, the value of  $L_w$  should be tuned to boost the isolation and minimize the insertion loss at a desired frequency.

### III. SIMULATION RESULTS

The proposed circulator is designed in the  $0.18 \mu\text{m}$  CMOS process. The layout of the proposed active circulator is depicted in Fig. 6. The area requirement of the circulator is  $0.51 \text{ mm} \times 0.74 \text{ mm}$ . Fig. 7 demonstrates the simulated return losses, isolation, insertion losses, and noise figure (NF) of the proposed circulator with optimized peaking inductors. Matching at TX, ANT and RX is less than 9 dB over the whole frequency range as demonstrated in Fig. 7(a). The simulated TX-RX isolation  $1S_{31}|$  (from transmitter to receiver) is a minimum of 30.08 dB within the whole frequency spectrum as depicted in Fig. 7(b). Finally, Fig. 7(c) represents the insertion loss  $IS21I$  (from TX to ANT) and  $IS32I$  (from ANT to RX) being lower than 7.42 and 7.27 dB, respectively within the operating band. Promising figures for insertion loss can't be achieved as the on-chip inductors suffer from low-quality factors. An NF of 4.8 dB from ANT to RX is achieved at  $9.3 \text{ GHz}$  as depicted in Fig. 7(d). Power handling capacity is calculated from 1-dB compression point as demonstrated in Fig. 7(e).

Table I compares the efficacy of the proposed design to the current state-of-the-art. It is capable of achieving 4-GHz bandwidth (X-band) with TX-to-RX isolation of at least 30.08 dB while consuming only 7.6 mW of power. Following the proposed tuning scheme for the design variables of the peaking inductor, the proposed CMOS circulator is capable of achieving the highest isolation while maintaining a comparable figure for the insertion loss.

### IV. CONCLUSION

An active circulator employing peaking inductors to achieve high isolation bandwidth was designed for this work using a standard  $0.18 \mu\text{m}$  CMOS process. Different design variables of the peaking inductor were regulated to accomplish a better trade-off between the isolation and insertion losses of the proposed circulator. This study is capable of achieving wideband

operation, boosted isolation, and comparable insertion loss competitive with that of leading-edge active circulators.

### V. ACKNOWLEDGEMENT

This work is based upon work supported by the National Science Foundation (NSF) under grant No. ECCS 2309413.

### REFERENCES

- (1) AT. Le, X. Huang, and Y. J. Guo, "A two-stage analog self-interference cancellation structure for high transmit power-in-band full-duplex radios," *IEEE Wireless Communications Letters*, vol. 11, no. 11, pp. 2425-2429, 2022.

- (2) J.-T. Lim, H.-W. Choi, J.-H. Song, and C.-Y. Kim, "An in-band full-duplex low noise amplifier integrated with an electrical balance duplexer without explicit matching," *IEEE Microwave and Wireless Technology Letters*, vol. 33, no. 8, pp. 1175-1178, 2023.

- (3) J. C. Dash and D. Sarkar, "A colinearly polarized full-duplex antenna with extremely high Tx-Rx isolation," *IEEE Antennas and Wireless Propagation Letters*, vol. 21, no. 12, pp. 2387-2391, 2022.

- (4) X. Huang, A. Tuyen Le, and Y. J. Guo, "Joint analog and digital self-interference cancellation for full duplex transceiver with frequency-dependent YQ imbalance," *IEEE Transactions on Wireless Communications*, vol. 22, no. 4, pp. 2364-2378, 2023.

- (5) S. Wang, C.-H. Lee, and Y.-B. Wu, "Fully integrated 10-GHz active circulator and quasi-circulator using bridged-T networks in standard CMOS," *IEEE Transactions on Very Large Scale Integration (VLSI) Systems*, vol. 24, no. 10, pp. 3184-3192, 2016.

- (6) B. Tang, X. Gui, J. Xu, Q. Xia, and L. Geng, "A dual interference-cancelling active quasi-circulator achieving 36-dB isolation over 6-GHz bandwidth," *IEEE Microwave and Wireless Components Letters*, vol. 29, no. 6, pp. 409-411, 2019.

- (7) D.-J. Huang, J.-L. Kuo, and H. Wang, "A 24-GHz low power and high isolation active quasi-circulator," in *2012 IEEF IMTT-S International Microwave Symposium Digest*, 2012, pp. 1-3.

- (8) B. Tang, J. Xu, and L. Geng, "Integrated active quasi-circulator with 27 dB isolation and 0.8-6.8 GHz wideband by using feedback technique," in *2018 IEEE MTT-S International Wireless Symposium (IWS)*, 2018, pp. 1-4.

- (9) S. Reza and A. Roy, "3-5 GHz multifinger CMOS LNA using a simultaneous noise and impedance matching technique by a significant reduction of broadband impedance variation of metal-oxide-semiconductor field-effect transistor," *ET Circuits, Devices and Systems*, vol. 14, no. 07, pp. 956-965, 2020.

- (10) S. Reza et al., "Stability analysis of multifinger CMOS RF amplifiers," in *2019 2nd International Conference on Engineering and Technology (IC/ET)*, 2019, pp. 1-6.

- (11) S. Reza, *Finger-regulated simultaneous noise and input matching technique with wideband impedance settlement for CMOS low noise amplifiers*. Department of Electrical and Electronic Engineering (EEE), BUET, 2021.

- (12) S. Reza and I. Mahbub, "A 2.98 dB NF, 2.52 mW low noise amplifier for a brain neuromodulation implant," in *2024 IEEE 17th Dallas Circuits and Systems Conference (DCAS)*, 2024, pp. 1-3.

- (13) S. Reza et al., "Finger-regulated simultaneous noise and input matching (FRSNIM) guided CMOS LNA," in *2024 IEEE 67th International Midwest Symposium on Circuits and Systems (MWSCAS)*, 2024.

- (14) Z. Deng, H. Qian, and X. Luo, "Tunable quasi-circulator based on a compact fully-reconfigurable  $180^\circ$  hybrid for full-duplex transceivers," *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 66, no. 8, pp. 2949-2962, 2019.

- (15) A. Hotkar and J. Mukherjee, "Design of cryogenic circulator in 65-nm CMOS technology using all-pass filter architecture," in *2023 IEEE Microwaves, Antennas, and Propagation Conference (MAPCON)*, 2023, pp. 1-6.

- (16) S. Chowdhury and M. Hasan, "Design of a 60 GHz active quasi-circulator in 22nm FDSOI process," in *2023 IEEE 16th Dallas Circuits and Systems Conference (DCAS)*, 2023, pp. 1-4.

- (17) K. B. Brito, R. N. de Lima, V. Kible, and R. C. S. Freire, "A 2.45 GHz CMOS active quasi-circulator with a built-in rectifier," in *2018 IEEE 9th Latin American Symposium on Circuits and Systems (LASCAS)*, 2018, pp. 1-4.