# Strained-topological-insulator spin-orbit-torque random-access-memory bit cell for energy-efficient processing in memory

Md Golam Morshed<sup>1,\*</sup>, Hamed Vakili<sup>2</sup>, Mohammad Nazmus Sakib,<sup>1</sup> Samiran Ganguly<sup>3</sup>, Mircea R. Stan<sup>1</sup>, and Avik W. Ghosh<sup>1,4</sup>

<sup>1</sup>*Department of Electrical and Computer Engineering, University of Virginia, Charlottesville, Virginia 22904, USA*

<sup>2</sup>*Department of Physics and Astronomy and Nebraska Center for Materials and Nanoscience, University of Nebraska, Lincoln, Nebraska 68588, USA*

<sup>3</sup>*Department of Electrical and Computer Engineering, Virginia Commonwealth University, Richmond, Virginia 23284, USA*

<sup>4</sup>*Department of Physics, University of Virginia, Charlottesville, Virginia, 22904, USA*

(Received 11 August 2024; revised 14 October 2024; accepted 23 December 2024; published 28 January 2025)

We present a design of a strained-topological-insulator spin-orbit-torque random-access-memory (STI SOTRAM) bit cell comprising a piezoelectric/magnet (gating)/topological insulator (TI)/magnet (storage) heterostructure that leverages the TI's high charge-to-spin conversion efficiency coupled with the piezo-induced strain-based gating mechanism for low-power in-memory computing. The piezo-induced strain effectively modulates the conductivity of the topological surface state by altering the gating magnet's magnetization from out of to in plane, facilitating the storage magnet's spin-orbit-torque (SOT) switching. Through comprehensive coupled stochastic Landau-Lifshitz-Gilbert simulations, we explore the device dynamics, anisotropy-stress phase space for switching, and write conditions and demonstrate a significant reduction in energy dissipation compared to conventional heavy-metal-based SOT switching. Additionally, we project the energy consumption for in-memory Boolean operations (AND and OR). Our findings suggest the promise of the STI SOTRAM for low-power, high-performance edge computing.

DOI: 10.1103/PhysRevApplied.23.014071

## I. INTRODUCTION

Electronics in the edge computing era poses unique challenges that may need heterogeneous combinations of materials with diverse attributes, and devices and circuits that capitalize on those attributes [1,2]. Along this path, the intersection of magnetism, topology, and strain offers a highly complementary suite of symmetries and tunable properties that could play off of each other strategically. For instance, strain can alter the energy landscape [3] of a magnet and rotate it by 90° [4]. Rotating a magnet out of plane can modulate spin conductivity of a three-dimensional (3D) topological insulator (TI) by breaking time-reversal symmetry and gapping its topological surface states (TSS) [5–7]. Conversely, a TI can act on the magnet when its spin-momentum-locked TSS write spin information onto the free layer of a magnetic tunnel junction (MTJ) with a current driven spin-orbit torque (SOT), its spin Hall angle (SHA) exceeding unity [8–11]. Integrating these properties into a single stack may allow us to naturally integrate multiple

functionalities into a compact, vertical monolithic structure.

In this paper, we will discuss an example stack, a multifunctional device composed out of a four-layer piezo/magnet/TI/magnet structure (Fig. 1), which exploits the above attributes to achieve both logic and memory functions in a single bit cell. Here strain actuates a bottom magnet in and out of the TI plane with a voltage-gated piezo, which modulates the TSS and drives a top storage magnet into a write mode, a read mode, or a logic mode using a sense amplifier. Since selector and storage magnets are co-located in a vertical geometry, the structure is scalable and naturally suited for a processing-in-memory (PIM) architecture. In contrast to traditional Von Neumann architecture (separate memory and logic cores with data-transfer latency) [12,13], key processing tasks are performed locally within a PIM [14–17], allowing the pre-processed data to be transferred to the primary processing unit with reduced latency [18]. The individual memory cells in a PIM architecture (bit cells) are often organized in a crossbar layout. Selectors control each row and column of the crossbar grid, enabling the bit cells for read or write operations. Utilizing sense amplifiers, the entire row

\*Contact author: mm8by@virginia.edu

of the crossbar can be read by comparing the state of the bit cells with a known reference voltage or current to perform logic operations within the memory [19–21].

The specific design of the stack depends on the convenience of fabrication (e.g., here we assume the thick piezo layer sits at the bottom, the bottom magnet on it to share the strain, then the TI to feel its proximal magnetization, and finally, the top magnet to get a write operation on it). Other lateral or flipped structures may well serve as better designs, if only for ease of fabrication. The core functionality, however, is employing SOT from a single-channel material, in this case, the TI delivers both high SHA and simultaneously gate tunability. Let us now discuss these two features separately.

Magnetic random access memory (MRAM) is a leading contender for a PIM bit cell due to its nonvolatility, high-speed, low-power consumption, high endurance, scalability, and excellent compatibility with complementary metal-oxide-semiconductor (CMOS) process technology [17,22,23]. The fundamental building block for MRAM devices is an MTJ, which consists of a thin insulator sandwiched between two magnetic layers—a “pinned layer” whose magnetization is fixed and a “free layer” whose magnetization can be reoriented by a spin current. Conventional MRAM uses current in the overhead to apply a magnetic field to write data on the MTJ free layer. Recently, a current-induced SOT mechanism, resulting from either the spin Hall effect [24,25] or the Rashba effect [26], has emerged as a promising approach for energy-efficient switching of the MTJ’s free layer. SOT-based switching addresses several limitations of its already commercialized counterpart, spin-transfer torque- (STT) based switching, such as the need for high write voltages, shared read-write paths creating read disturbs, and degradation of the insulating layer [27–29]. SOT-based MRAM (SOTRAM) is a three-terminal device featuring a decoupled read-write path and in-plane charge-current flow in the nonmagnetic layer underneath the MTJ free layer with a high charge-to-spin conversion efficiency, yielding a low write current and infinite endurance [24,25]. SOTRAM is attractive as a high-density last-level-embedded cache [30,31], with distinct advantages for PIM-like edge-based motion detection and cross-modality object recognition [23,32]. They do suffer from the higher footprint associated with the third terminal, a higher charge current needed to supply the spin current orthogonal to it, and the need for a field assist when the free-layer spin stagnates onto a symmetry direction in the magnet/heavy metal (HM) interfacial plane. Consequently, achieving a significantly high charge-to-spin conversion efficiency (large SHA) is essential to bypass these challenges for energy-efficient applications.

Traditional SOT devices typically utilize HMs such as Pt [25,33], Ta [24], and W [34] as spin current injectors; however, these HMs exhibit low SHA (Pt, 0.08; Ta, 0.15;

W, 0.4 [35]), leading to low charge-to-spin conversion efficiency [11]. Recently, TIs have garnered attention as an attractive spin source for SOT switching [8–10,36,37]. TIs are characterized by their spin-momentum-locked TSS, insulating bulk states, and SHA greater than unity [38–40]. The conducting TSS arise from band inversion at the surface, mediated by strong spin-orbit coupling, and are topologically protected by time-reversal symmetry [41–43]. More encouragingly, sputtered TIs such as  $\text{Bi}_2\text{Se}_3$  show very high ( $> 10$ ) SHAs, primarily because of the reduction in bulk conductivity that would otherwise shunt current away from the TSS, as well as better defect control that suppresses unwanted surface scattering. These attributes make TIs highly efficient spin-current injectors for SOT switching, facilitating energy-efficient information writing [44].

Conversely, a magnet’s ability to modulate the spin conductivity of the TSS of a TI, when in proximity with the TI, based on its magnetization direction, offers a pathway for an intrinsic gating mechanism to control the TI surface current [5,45]. Switching the magnet (gating magnet hereafter) from in-plane to out-of-plane orientations, gaps in the TSS can be opened, thereby modulating the spin conductivity [6,7]. This  $90^\circ$  switching of the gating magnet can be achieved through various mechanisms, such as strain [46–49], voltage-control magnetic anisotropy [50], and changing the anisotropy by an applied voltage [5,51]. Nonetheless, strain-induced  $90^\circ$  switching of magnets is very energy efficient [3,48,49,52], where a piezoelectric material induces electrical strain in response to an applied gate voltage to facilitate switching from in plane to out of plane and vice versa.

In this paper, we model the aforementioned potentially compact and energy-efficient four-layer piezoelectric/magnet/TI/magnet (MTJ) stack, which we refer to as a strained-topological-insulator spin-orbit-torque random access memory (STI SOTRAM). We argue that this structure is naturally suited as a compact bit cell in an in-memory computing architecture. We employ stochastic Landau-Lifshitz-Gilbert (LLG) simulation to analyze the device dynamics. We present the device’s functionality, the required phase space for stress generated by the piezo-induced strain and the gating magnet’s anisotropy, and the writing condition’s phase space (writing voltage vs time or delay) of the MTJ. We estimate the energy cost for gating and writing mechanisms and find that energy dissipation is significantly reduced compared to HM-based SOT switching, which indicates the benefits of utilizing TI as a spin source and an intrinsic gating mechanism as opposed to an access transistor traditionally used. Furthermore, we project the energy cost for 2-bit AND and OR operations, which shows lower-energy costs than traditional SOT switching. Finally, we show the impact of various material parameters on the device metric.

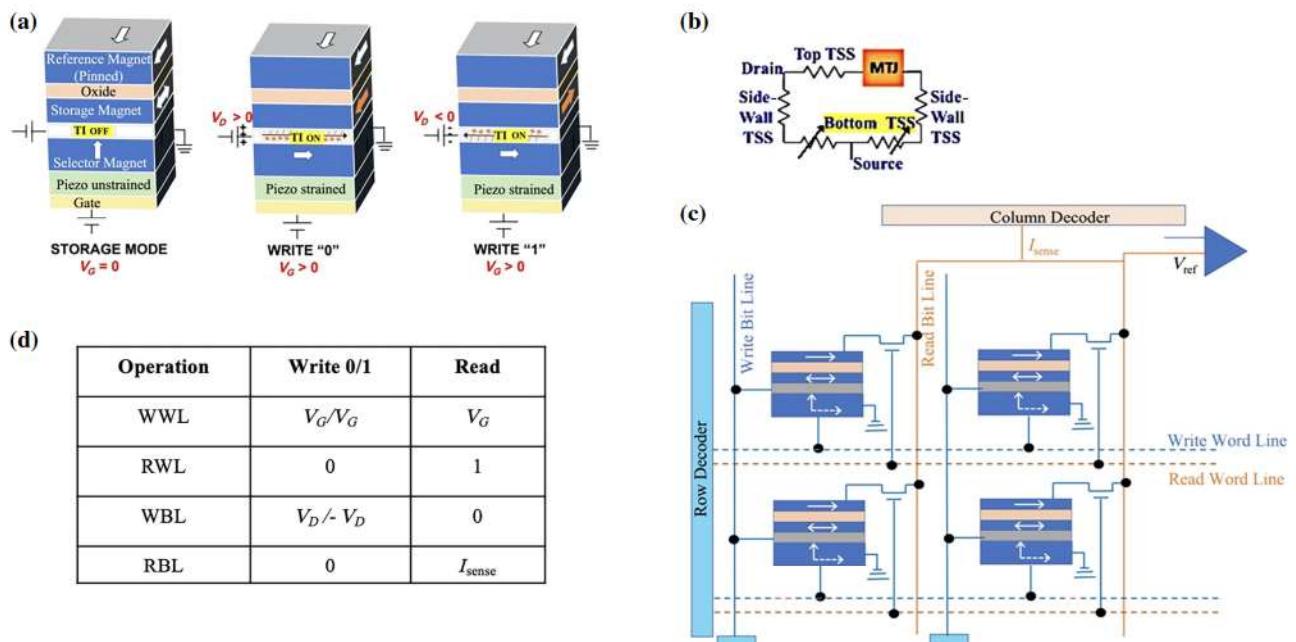

FIG. 1. (a) Schematic of a compact, low-power STI SOTRAM. An out-of-plane gating (selector) magnet gaps the bottom surface states of the TI and places the upper magnet in storage mode (left). The strain generated by the piezoelectric rotates the selector magnet from out of plane to in plane, restoring the bottom-layer surface states and activating the TI. The drain polarity  $V_D$  sets the storage bit with  $m_{2y}$  (bit "0") or  $-m_{2y}$  (bit "1") using high SHA SOT (middle and right, respectively). The fixed layer of the MTJ reads the state as "0" (parallel) or "1" (antiparallel). (b) Equivalent resistance model of the TI. An out-of-plane gating magnet breaks the current path in the bottom TSS. (c) Schematic of a PIM crossbar architecture where each activated stack (bit cell) can be selected by activating the row column. Two selected bit cells can feed to a sense amplifier that processes the local inputs by comparing with a reference voltage or current and performing Boolean logic operations (e.g., AND, OR, etc.), thereby processing local data from the magnetic memory. (d) Biasing condition for read-write operations. WWL, write word line; RWL, read word line; WBL, write bit line; RBL, read bit line.

## II. STI SOTRAM BIT-CELL DESIGN FOR PIM

Figure 1(a) depicts the schematic of the compact four-layer structure of the device comprising a piezoelectric/gating magnet/TI/MTJ stack in the vertical direction. The device contains a gating (selector) magnet at the bottom whose magnetization can be switched in and out of the plane of the TI in nanoseconds with a voltage-gated piezoelectric at a low-energy cost (approximately 10 aJ) [4,52,53]. An out-of-plane selector magnet gaps the bottom surface states of the TI, leading to breaking the current path [Fig. 1(b)] and places the upper MTJ free layer in storage mode [Fig. 1(a), left]. Activating the TI bottom surface with applied voltage restores the current path and drives the top MTJ free layer into one of three modes—(i) altering its magnetization with drain bias for data writing [Fig. 1(a), middle and right], (ii) discharging its stored magnetization state for data reading, the output set by its low (parallel) or high (antiparallel) resistance relative to the MTJ pinned layer; (iii) or execute a logic operation (e.g., bitwise AND, OR, etc.) using a sense amplifier [Fig. 1(c)]. Two selected bit cells can feed their voltage or current to a sense amplifier that processes the local inputs by comparing them with a reference voltage or current and performing Boolean

logic operations. For example, for current-based sensing, if the current of the bit cells is  $I_c$ , AND and OR operations can be performed by selecting a reference current of  $1.5I_c$  and  $0.5I_c$ , respectively. Similarly, we can choose different reference voltages for a voltage-based sensing scheme (discussed later). Since selector and storage magnets are co-located in a vertical geometry, the structure is scalable and naturally suited for a PIM architecture that preprocesses stored data locally, all with the same vertically integrated, compact bit cell as shown in Fig. 1(c). Figure 1(d) shows the biasing condition for various operations.

From Mars rovers to mine robots, edge computing avoids cloud access that is either unavailable or unreliable. Energy and latency are its main concerns. Our device gating energy is low because the strain is remarkably energy efficient, while our write energy is low because TIs offer a very high SHA. Our results (Fig. 5) show that at the individual bit-cell level, our device requires much lower energy (approximately 2–6×) than 45-nm dynamic and static random access memory (DRAM, SRAM) and HM-based SOTRAM with a lower or comparable speed (2 ns), further improvable with larger band-gap TIs. Moreover, at a PIM architecture level, we significantly outperform DRAM on both nonvolatility and energy cost

by rolling memory and logic into a single unit, reducing data-transit latency from approximately mm-cm data-bus lengths between separate memory-logic cores to just approximately  $\mu\text{m-mm}$  array dimensions, as the sense amplifier processes suitably segmented data from locally accessed storage magnets. At data-transfer rates of approximately Mbps-Gbps, this enables a  $2\text{--}3\times$  speedup over traditional Von Neumann architecture, in addition to the energy gain. Our device exploits the TI as a unique semiconducting channel that delivers high SOT without field assist for low-energy write and voltage gating with strain for low-power row-column select in PIM architecture.

### III. METHODS

To characterize the magnetization dynamics in our device, we solve a coupled stochastic LLG equation in the macrospin limit using the fourth-order Runge-Kutta method. As explained in detail in Sec. II, the device consists of a piezoelectric/gating magnet/TI/MTJ heterostructure. We simultaneously solve the magnetization dynamics of the gating magnet and the MTJ free layer. In the case of the gating magnet, the LLG equation is described as

$$\frac{1 + \alpha_1^2}{\gamma} \cdot \frac{\partial \mathbf{m}_1}{\partial t} = -\mu_0 \cdot (\mathbf{m}_1 \times \mathbf{H}_{\text{eff1}}) - \alpha_1 \mu_0 \cdot \mathbf{m}_1 \times (\mathbf{m}_1 \times \mathbf{H}_{\text{eff1}}), \quad (1)$$

where  $\mathbf{m}_1 = \mathbf{M}_1/M_{s1}$  is the normalized magnetization and  $M_{s1}$  is the saturation magnetization of the gating magnet.  $\alpha_1$ ,  $\mu_0$ , and  $\gamma$  are magnetic damping coefficient, permeability of free space, and gyromagnetic ratio, respectively. We consider  $\mathbf{H}_{\text{eff1}} = \mathbf{H}_{k1} + \mathbf{H}_{\text{stress}} + \mathbf{H}_{\text{th}}$ , where  $\mathbf{H}_{k1}$  and  $\mathbf{H}_{\text{stress}}$  are the effective anisotropy field and stress field of the gating magnet, respectively [54,55].  $H_{k1} = (2K_{u1})/(\mu_0 M_{s1}) - M_{s1}$  ( $K_{u1}$  is the uniaxial anisotropy of the gating magnet).  $H_{\text{stress}} = (3\lambda_s \sigma_s)/(\mu_0 M_{s1})$  ( $\lambda_s$  is the magnetostriction coefficient of the gating magnet, and  $\sigma_s$  is the stress generated by the electrical strain induced by the piezoelectric).

For the MTJ free layer, the switching is facilitated by the SOT arising from the TI, and the LLG equation takes the form:

$$\frac{1 + \alpha_2^2}{\gamma} \cdot \frac{\partial \mathbf{m}_2}{\partial t} = -\mu_0 \cdot (\mathbf{m}_2 \times \mathbf{H}_{\text{eff2}}) - \alpha_2 \mu_0 \cdot \mathbf{m}_2 \times (\mathbf{m}_2 \times \mathbf{H}_{\text{eff2}}) - \frac{\hbar}{2e} \cdot \frac{\theta_{sh}^{\text{eff}} J}{M_{s2} t_{f2}} \cdot \mathbf{m}_2 \times (\mathbf{m}_2 \times \sigma_p), \quad (2)$$

where  $e$  is the elementary charge,  $\hbar$  is the reduced Plank constant,  $\theta_{sh}^{\text{eff}}$  is the effective SHA of the TI,  $t_{f2}$  is the thickness of the MTJ free layer,  $J$  is the surface current density of the TI, and  $\sigma_p$  is the unit vector along the

TABLE I. Material parameters.

| Dimension                                       |                    |                                                 |

|-------------------------------------------------|--------------------|-------------------------------------------------|

| Length                                          | $L$                | 20 nm                                           |

| Width                                           | $W$                | 40 nm                                           |

| Gating magnet: TbCo                             |                    |                                                 |

| Thickness                                       | $t_{f1}$           | 2.5 nm                                          |

| Saturation magnetization                        | $M_{s1}$           | $200 \times 10^3 \text{ A/m}$ [66,69]           |

| Damping                                         | $\alpha_1$         | 0.4                                             |

| Uniaxial anisotropy                             | $K_{u1}$           | $64 \times 10^3 \text{ J/m}^3$ [10,66]          |

| Magnetostrictive coefficient                    | $\lambda_s$        | $400 \times 10^{-6}$ [65]                       |

| Young's modulus                                 | $Y$                | $100 \times 10^9 \text{ Pa}$ [64]               |

| MTJ-free layer: TbCo                            |                    |                                                 |

| Thickness                                       | $t_{f2}$           | 12.5 nm                                         |

| Saturation magnetization                        | $M_{s2}$           | $400 \times 10^3 \text{ A/m}$ [69,75]           |

| Damping                                         | $\alpha_2$         | 0.01                                            |

| Topological insulator: $\text{Bi}_2\text{Se}_3$ |                    |                                                 |

| Thickness                                       | $t_{\text{TI}}$    | 8 nm [10,36]                                    |

| Spin Hall angle                                 | $\theta_{sh}$      | 3.5 [35]                                        |

| Spin-diffusion length                           | $\lambda$          | 6.2 nm [76]                                     |

| Conductivity                                    | $\sigma_c$         | $5.7 \times 10^4 \Omega^{-1}\text{m}^{-1}$ [35] |

| Piezoelectric: PZT                              |                    |                                                 |

| Thickness                                       | $t_{\text{piezo}}$ | 100 nm                                          |

| Piezoelectric constant                          | $d_{31}$           | $1.8 \times 10^{-10} \text{ m/V}$ [3]           |

| Max. strain                                     | $\epsilon$         | 1000 ppm (0.1%) [52]                            |

| Relative dielectric constant                    | $\epsilon_r$       | 1000 [3]                                        |

spin-polarization direction. The other variables and constants have the same meaning as defined in Eq. (1), and a subscript of 2 represents the parameter for the MTJ free layer.  $\theta_{sh}^{\text{eff}} = \theta_{sh}(1 - \text{sech}(t_{\text{TI}}/\lambda))$ , where  $\theta_{sh}$ ,  $t_{\text{TI}}$ , and  $\lambda$  are the SHA, thickness, and spin diffusion length of the TI. In Eq. (2),  $\mathbf{H}_{\text{eff2}} = \mathbf{H}_d + \mathbf{H}_{\text{th}}$ .  $\mathbf{H}_d$  is the demagnetization field of the in-plane MTJ free layer and expressed as  $H_d = -M_{s2}[N_{dx} N_{dy} N_{dz}]$ , where  $N_{dx}$ ,  $N_{dy}$ ,  $N_{dz}$  are the demagnetization factors of the free layer along  $x$ ,  $y$ ,  $z$  axis, respectively.

In both Eqs. (1) and (2),  $\mathbf{H}_{\text{th}}$  is a random thermal field with zero mean ( $\mu = 0$ ) and standard deviation

$$\text{SD} = \sqrt{\frac{2\alpha k_B T}{\mu_0^2 \gamma M_s V \Delta t}}, \quad (3)$$

where  $\alpha$ ,  $M_s$ , and  $V$  are the damping coefficient, saturation magnetization, and volume of the respective magnets.  $\Delta t$  is the simulation time step, which is taken to be  $10^{-12}$  for all the simulations.  $\mu_0$ ,  $\gamma$ ,  $k_B$ , and  $T$  have their usual meanings.

Throughout our study, we use TbCo as both the gating magnet and the MTJ free-layer magnet,  $\text{Bi}_2\text{Se}_3$  as the TI, and  $\text{Pb}(\text{Zr}, \text{Ti})\text{O}_3$  (PZT) as the piezoelectric materials unless otherwise specified. The used parameters are listed in Table I.

The modulation of the surface current density  $J$  of the TI by the gating magnet is modeled separately with an empirical function, described next.

#### IV. RESULTS AND DISCUSSION

The first functional block of the entire stack is the piezoelectric/gating magnet heterostructure. Applying a voltage to the piezoelectric (PZT), electrical strain is generated and transferred to the adjacent gating magnet (TbCo) via the magnetostriction effect. This strain is then converted into stress via the elastic modulus of the gating magnet, which counteracts the uniaxial anisotropy of the gating magnet. When the stress is sufficient, it can switch the gating magnet from out of plane to in plane with minuscule energy consumption in the order of approximately 10 aJ [4,52,53] (energy cost estimation for our device is shown later). The strain-induced switching of the gating magnet facilitates the opening and closing of the band gap in the TSS of the TI ( $\text{Bi}_2\text{Se}_3$ ), depending on the out-of-plane and in-plane magnetization orientation of the gating magnet, respectively.

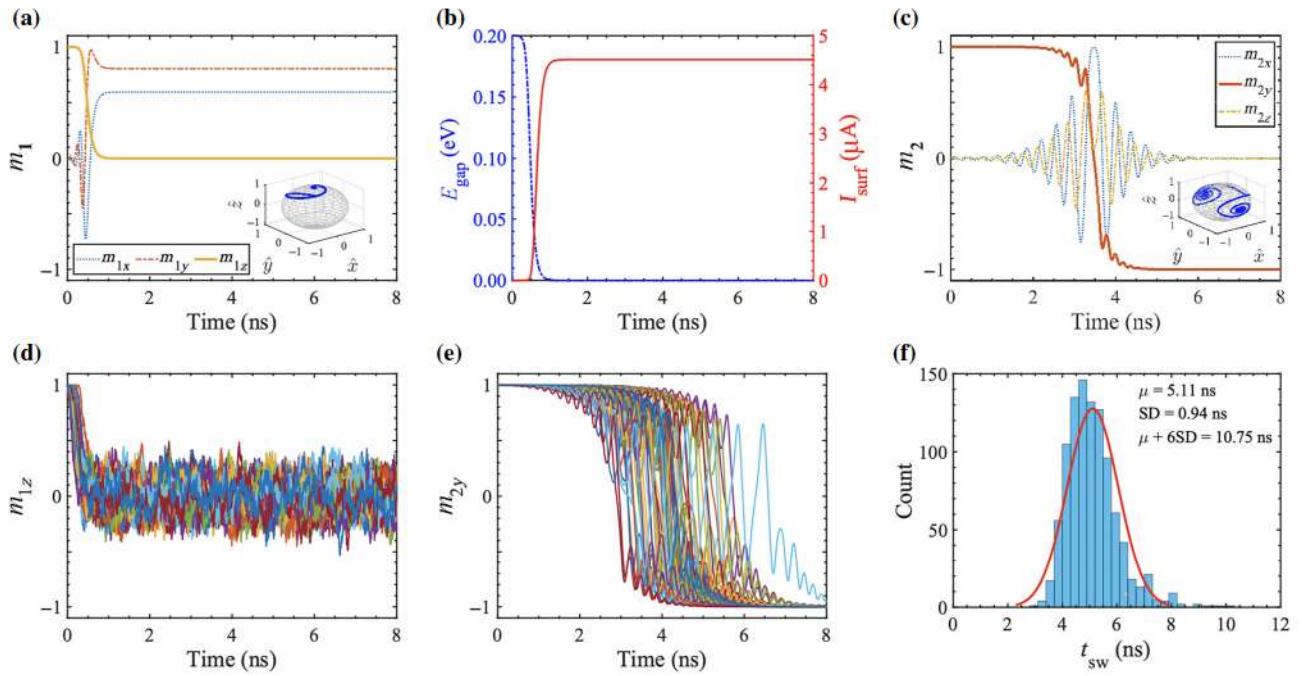

Figure 2(a) shows the magnetization dynamics of the gating magnet under the influence of the stress induced by the piezoelectric strain. We started with an out-of-plane magnetization ( $m_{1z} = +1$ ) for the gating magnet, which corresponds to the OFF state of the device as it opens a band gap in the TSS and, hence, no current flow. Under the influence of stress, it takes a very short time, approximately 1 ns for the  $90^\circ$  switching ( $m_{1z} = 0$ ) of the gating magnet for a stress  $\sigma_s = 100$  MPa. The switching delay depends on the strength of  $\sigma_s$  and the material parameters of the gating magnet. The out-of-plane magnetization component ( $m_{1z}$ ) is fed to the next block (TI) dynamically, which modulates the band gap in the TSS and, hence, the surface current. We consider a Dirac Hamiltonian form to model the surface state of the TI. In the presence of a magnet in proximity to the TI, the Hamiltonian can be expressed as  $H = \hbar v_F(\boldsymbol{\sigma} \times \mathbf{k}) \cdot \hat{z} + M_0 \mathbf{M}_1 \cdot \boldsymbol{\sigma}$  [5,56], where  $v_F$  is the Fermi velocity,  $\mathbf{k}$  is the wave vector,  $\boldsymbol{\sigma}$  is the Pauli spin matrices,  $M_0$  is the exchange strength between the gating magnet and TI, and  $\mathbf{M}_1$  is magnetization of the gating magnet. From simple algebra, for the case of an out-of-plane magnetization orientation of the gating magnet, we can show the energy dispersion takes the form  $E = \pm \sqrt{\hbar^2 v_F^2 |\mathbf{k}|^2 + (M_0 m_{1z})^2}$ ,

where  $|\mathbf{k}| = \sqrt{k_x^2 + k_y^2}$ . This gives rise to a band gap  $E_{\text{gap}} = \sqrt{(2M_0 m_{1z})^2}$  at  $\mathbf{k} = 0$ . The band gap will modulate the surface current of the TI as  $I_{\text{surf}} = I_{0,\text{surf}} e^{-E_{\text{gap}}/k_B T}$ , where  $I_{0,\text{surf}}$  represents the surface current needed to switch the MTJ free layer for a specific switching delay. Figure 2(b) shows the evolution of the  $E_{\text{gap}}$  and the  $I_{\text{surf}}$  with time in response to the magnetization dynamics of the gating magnet [Fig. 2(a)]. Initially, when  $m_{1z} = +1$ , a band gap of  $2M_0$  opened, and we get vanishing surface current. As the gating magnet switches ( $m_{1z} = 0$ ) by the stress, the conductivity of the TSS is restored since the band gap is closed. We use  $M_0 = 0.1$  eV, a typical value for  $\text{Bi}_2\text{Se}_3$  [5,45]. Note that we cannot open an infinite band gap as it is limited by the

bulk band gap of the TI (0.3 eV for  $\text{Bi}_2\text{Se}_3$  [57,58]). We use  $I_{0,\text{surf}} = 6I_{c,\text{surf}}$  while generating Fig. 2(b), where  $I_{c,\text{surf}}$  is the critical surface current needed to switch the MTJ free layer.

We utilize an in-plane magnet-based MTJ for our device for primarily two reasons: (i) SOT can provide deterministic switching without an external field assist only for an in-plane magnet because of in-plane spin polarization (orthogonal to the charge current) [8,24,59], and (ii) we are limited by the interaction between the TI and the MTJ free layer as such an out-of-plane free layer will open the gap in the TSS and hence no current conduction [5–7]. While utilizing an in-plane magnet occupies more area than a perpendicular magnetic anisotropy (PMA) magnet, our design integrates the gating and storage magnets within the same stack. This configuration offers both area and energy-efficiency advantages, along with the added benefit of field-free switching. Extensive research is underway for field-free switching of PMA magnets. However, these require a graded structure or an added magnet that provides the symmetry-breaking field and adds structural complexity [60,61]. We use an in-plane magnet of “type y” (easy axis in  $y$  direction). The critical current density for switching  $J_c$  for this type of MTJ is expressed as [59,62,63]

$$J_c = \frac{2e\alpha_2\mu_0 M_{s2} t_f 2}{\hbar\theta_{sh}^{\text{eff}}} \left( H_{\text{in}} + \frac{H_{\text{out}}}{2} \right). \quad (4)$$

$H_{\text{in}}$  is the in-plane shape anisotropy of the free layer, and  $H_{\text{out}}$  is the out-of-plane demagnetization component. The other variables and constants have the same meaning defined in Sec. III. Using the parameters listed in Table I, we find  $J_c = 1.88 \times 10^{10}$  A/m<sup>2</sup>, which is at least one order of magnitude less than conventional HM-based SOT switching [35,59] and laid the foundation of energy-efficient switching. This amount of critical current density needs to be supplied by the top surface states of TI for the switching of MTJ free layer, from which we can estimate the critical surface current  $I_{c,\text{surf}} = J_c W t_{\text{surf}} = 0.75$   $\mu\text{A}$  ( $W$  is the device width,  $t_{\text{surf}} = 1$  nm is the thickness of the TI top surface [36]).

Figure 2(c) shows the magnetization dynamics of the MTJ free layer in response to the SOT generated by the TI surface current. We can clearly see the magnetization switching ( $m_{2y} = +1$  to  $m_{2y} = -1$ ) with a switching delay of approximately 4 ns for a surface current of  $6I_{c,\text{surf}}$ . Note that Figs. 2(a)–2(c) are generated in the absence of a thermal field. Figures 2(d) and 2(e) show the magnetization dynamics of the gating magnet and the MTJ free layer, respectively, under the influence of the thermal field for 50 simulation runs for the same current as without the thermal case, and we can see the stochastic behavior of the magnetization dynamics. Figure 2(f) shows the histogram from 1000 simulations runs, and we find a switching time of 10.75 ns, calculated by  $t_{\text{sw}} = \mu + 6\text{SD}$ , corresponding to

FIG. 2. Coupled LLG simulations showing gating magnet switching with strain (a), turning ON TSS (closing band gap) and hence delivering surface current (b), and switching the MTJ free layer with SOT (c) without the thermal field. (d),(e) Magnetization dynamics for the gating magnet and the MTJ free layer, respectively, influenced by the stochastic thermal field (50 simulations). (f) Histogram of switching time from 1000 stochastic simulations to estimate the switching time corresponding to  $\text{WER} = 10^{-9}$ . The switching time is calculated as  $t_{\text{sw}} = \mu + 6 \text{ SD}$  from the histogram. The results are generated using  $I_{0,\text{surf}} = 6I_{c,\text{surf}}$ .

a write error rate  $\text{WER} = 10^{-9}$ , which is the industry standard for memory applications [28]. In the subsequent part of the paper, we calculate  $t_{\text{sw}}$  similarly unless otherwise specified.

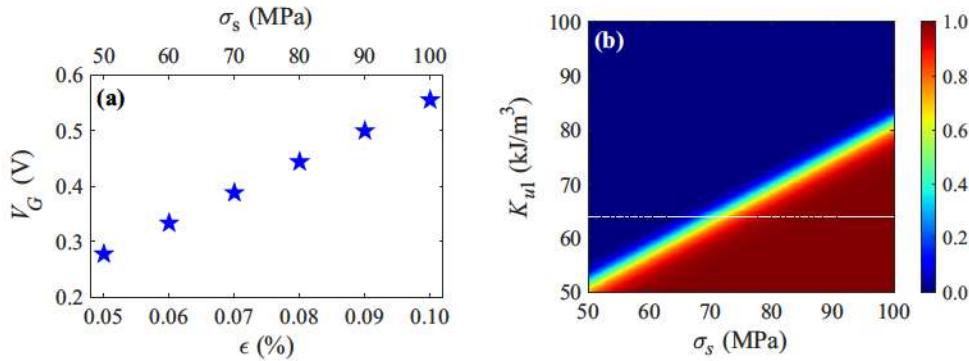

Figure 2 demonstrates the functionality of the device. We will now delve into the details and constraints of the individual blocks. Beginning from the bottom to up, the piezoelectric-gating magnet stack enables the strain-driven out-of-plane to in-plane switching. As discussed earlier, the switching is governed by the competition between the uniaxial anisotropy energy and the stress energy induced by the strain. PZT typically can generate an electrical strain of  $0.05\% - 0.1\%$  ( $500 - 1000$  ppm) in response to an applied voltage [52], which sets the achievable stress-energy limit to counteract the anisotropy energy. The relation between the applied voltage and strain is  $V_G/t_{\text{piezo}} = \epsilon/d_{31}$  [3,52], where  $V_G$ ,  $t_{\text{piezo}}$ ,  $\epsilon$ ,  $d_{31}$  are the applied gate voltage, thickness of piezoelectric, strain, and piezoelectric constant, respectively. The typical  $d_{31}$  constant for PZT is  $1.8 \times 10^{-10}$  [3]. TbCo has Young's modulus of 100 GPa [64] and  $\lambda_s = 400 \times 10^{-6}$  [65], which gives a range of stress  $\sigma_s$  from 50 to 100 MPa. Figure 3(a) shows the gate voltage required for generating the strain (stress) for a 100-nm-thick PZT. The critical question is whether this stress is sufficient to overcome the anisotropy barrier. TbCo has a low uniaxial anisotropy

$K_{u1}$  of  $64 \text{ kJ/m}^3$  [10,66]. Considering the demagnetization effect, the effecting anisotropy becomes  $38.9 \text{ kJ/m}^3$  ( $K_{\text{eff}} = K_{u1} - \frac{1}{2}\mu_0 M_{s1}^2$ ). Conversely, the stress energy  $E_{\text{stress}} = \frac{3}{2}\lambda_s\sigma_s$  [54,55] ranges from 30 to  $60 \text{ kJ/m}^3$  depending on the amount of strain (stress) shown in Fig. 3(a). Figure 3(b) presents the phase space for anisotropy and stress for the switching probability of the MTJ-free layer (colormap). The  $P_{\text{sw}}$  is calculated from  $10^5$  stochastic LLG runs [67] for 10 ns with a surface current of  $6I_{c,\text{surf}}$ . The figure illustrates the reciprocal relation between the  $K_{u1}$  and  $\sigma_s$ , and the range of  $K_{u1}$  and  $\sigma_s$  for a working device. This phase space is relevant because  $K_{u1}$  can be tuned by adjusting the composition of TbCo and alloying [68,69], while  $\sigma_s$  is adjustable through applied gate voltage.

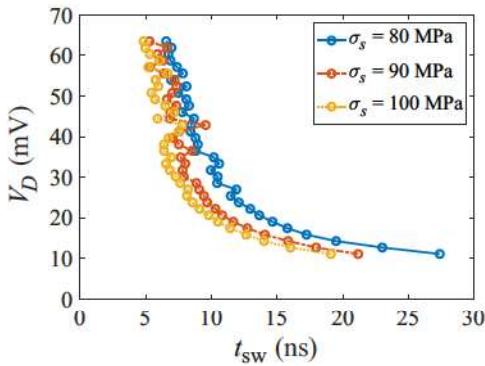

Next, we consider the voltage requirement for the MTJ write operation (switching the MTJ free layer). For the write operation, three key quantities are the switching time, switching current or voltage, and WER. We calculate the switching voltage vs switching time for various stress values in Fig. 4, showing the typical reciprocal relation for spin-torque switching [70–72]. The switching voltage shown in Fig. 4(a) corresponds to  $\text{WER} = 10^{-9}$ . As  $\sigma_s$  increases, the out-to-in-plane switching time of the gating magnet is reduced, and it requires less time for the band gap to close, which is attributed to the lower overall switching time of the device. We vary the surface

FIG. 3. (a) Gate-voltage requirement in the PZT to generate electrical strain (stress). The capacity to generate strain in the PZT limits the maximum achievable stress. (b) Gating magnet's uniaxial anisotropy vs stress phase space for the switching probability (colorplot) of the MTJ free layer. The probability of switching is calculated from  $10^5$  stochastic simulations. The dash-dotted line represents the TbCo uniaxial anisotropy ( $K_{ul} = 64$  kJ/m<sup>3</sup>).

current from 3.5 to 20 times the critical surface current and let the magnetization evolve until it reaches 95% of its final value ( $m_{2y} = -0.95$ ) [73]. We denote the time as the switching time for the individual switching event, and from the switching-time distribution of 1000 simulations, we calculate the  $t_{sw}$  corresponding to WER =  $10^{-9}$ . While calculating the total current requirement for the required surface current, we consider a  $I_{surf}/I_{tot} = 15\%$  (see more discussion later).

Furthermore, we estimate the energy consumption for the switching process. The energy has two components: the gating energy and the switching energy. The energy associated with the gating mechanism comes from the applied voltage in the piezoelectric and can be estimated as  $E_{piezo} = \frac{1}{2}C_p V_G^2$  [3,52], where  $C_p$  is the capacitance of the PZT, and  $V_G$  is the applied gate voltage. For the case of 0.1% strain, we get  $V_G = 0.56$  V and  $C_p = \epsilon_r \epsilon_0 WL/t_{piezo} = 0.071 \times 10^{-15}$  F ( $L$  is the length of the device,  $\epsilon_0$  and  $\epsilon_r = 1000$  [3] are the permittivity of free space and the relative permittivity of PZT, respectively). We obtain  $E_{piezo} = 11.13$  aJ, which is minuscule and

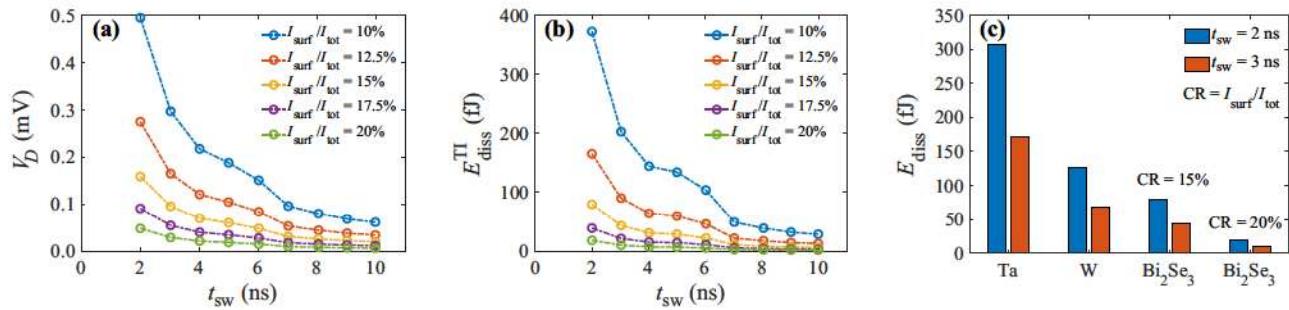

consistent with previous studies [4,52,53]. The other part of the energy is the  $I^2R$  loss in the TI. TI is typically modeled as parallel surface and bulk channels (bulk channel accounts for the shunting through the bulk states) [36, 58]. The bulk resistance is  $R_{bulk} = L/\sigma_c W t_{bulk} = 1.46$  k $\Omega$ , where  $\sigma_c$  is the average conductivity of the TI ( $\sigma_c = 5.7 \times 10^4$   $\Omega^{-1}$  m<sup>-1</sup> for Bi<sub>2</sub>Se<sub>3</sub> [35]), and  $t_{bulk}$  is the thickness of the bulk state of TI. We use  $t_{bulk} = 6$  nm since the TI is 8 nm thick and the thickness of the top and the bottom surface is 1 nm each [36]. We estimate  $R_{surf}$  based on the current distribution in the top surface channel, which is found to be 30% of the total current as previously reported in both theory [58] and experiments [36]. This makes  $R_{surf} = 1.94$  k $\Omega$ . Nonetheless, the bottom surface needs to be grounded through the gating magnet for the gating mechanism to work for our vertical structure [Fig. 1(b)]. Therefore, we divide the bottom surface resistance equally with a ground in the middle and estimate the equivalent resistance  $R_{eq} = 633.5$   $\Omega$ , and eventually, we achieve 15% current through the top surface channel of the TI for the resistance configuration shown in Fig. 1(b). Shunting through the bulk in TI is an open question, and it requires materials with a higher band gap to get more current in the surface [58]. For high-speed applications, we want the switching time in single-digit nanoseconds [28,31,74]. We estimate the energy used in this operation regime. Figure 5(a) shows the voltage requirement for  $t_{sw}$  for 2–10 ns (WER =  $10^{-9}$ ), while Fig. 5(b) shows the energy consumption for the writing operation for a range of  $I_{surf}/I_{tot}$ .  $I_{surf}/I_{tot}$  can be varied by tuning the conductivity, bulk band gap, and thickness of the TI [36]. Our analysis suggests energy consumption in the TI is in the order of < 100 fJ, even with a low current ratio of 15% in the top surface, which is energy efficient compared to HM-based SOT switching [Fig. 5(c)], consistent with previous studies [10,35]. If we increase the top surface current, the energy consumption will be decreased further. Figure 5(c) shows

FIG. 4. Supplied drain voltage to the TI for write operation. We use  $I_{surf}/I_{tot} = 15\%$ .

FIG. 5. (a) Drain-voltage requirement for high-speed switching (2–10 ns). (b) Energy dissipation in the TI during the writing process. (c) Comparison of energy dissipation between traditional HM- and TI-based SOT mechanism. TI consumes orders of magnitude less energy than the HM.

the energy-consumption comparison between HM- and TI-based switching, which shows an order-of-magnitude reduction in energy consumption for TI. Although the conductivity of HM is very high, the current dictates the  $I^2R$  loss, and TI requires a significantly low current because of its higher SHA [35].

The total energy consumption for writing operation  $E_{\text{write}} = E_{\text{piezo}} + E_{\text{TI}}$ , which is dominated by the  $E_{\text{TI}}$  because of the minuscule energy in the gating mechanism. This suggests the advantage of the stain-based intrinsic gating mechanism because it eliminates the need for an access transistor for the write operation, costs negligible energy, and has a reduced footprint compared to a CMOS access transistor. The energy consumption in TI will be much lower if we incorporate other TIs with higher SHAs. For example, for BiSb (SHA = 10 and  $\sigma_c = 1.5 \times 10^5 \Omega^{-1} \text{ m}^{-1}$  [35]), the energy consumption is approximately 0.9 fJ and approximately 0.2 fJ for a current ratio of 15% and 20%, respectively, which is approximately 100× lower than  $\text{Bi}_2\text{Se}_3$  and approximately 1000× lower than traditional HM.

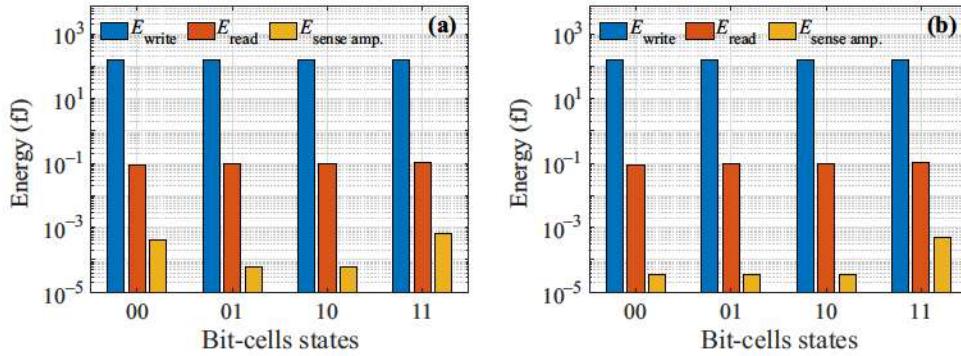

The above-estimated write energy is at the bit-cell level. Now, we project the energy cost for a PIM array from the bit-cell energy. In particular, we show the projection for a 2-bit Boolean AND and OR operation using the PIM cross-bar array [Fig. 1(c)]. Before doing the projection, we need to estimate the read energy cost. For reading operation, we use a small sense current  $I_{\text{sense}} = 1 \mu\text{A}$ , significantly less than the write current, eliminating the risk of an accidental switch. We assume a resistance area product for the MTJ  $R_{PA} = 2 \Omega \mu\text{m}^2$  and a TMR = 100% [77], which makes  $R_P = 2.5 \text{ k}\Omega$  and  $R_{AP} = 5 \text{ k}\Omega$ , respectively ( $R_P$  and  $R_{AP}$  are the resistance of MTJ in parallel and antiparallel state, respectively). We consider a 16-nm PTM HP model for the read access transistor with a  $R_{ON} = 5 \text{ k}\Omega$ . We need to keep the gate voltage ON for the read operation so that the TI surface state is conductive, adding the gating energy during the read operation. Considering this, we found a read energy  $E_{\text{read}}$  of approximately 45 aJ and approximately 55 aJ for parallel (bit “0”) and antiparallel

(bit “1”) states at a read speed of 4 ns [78]. For in-memory 2-bit AND and OR operations, we need to select two bit cells simultaneously, and the PIM operation is done by comparing the sense voltage from the bit cells with a reference voltage  $V_{\text{ref}}$  through a sense amplifier [see Fig. 1(b)], where  $V_{\text{ref}}$  is set to a value depending on the operation we want to perform. For two bit cells, we will have  $\{R_{AP}, R_{AP}\}$ ,  $\{R_{AP}, R_P\}$ ,  $\{R_P, R_{AP}\}$ ,  $\{R_P, R_P\}$  combinations in the resistance states of the MTJ, corresponding to sense voltages  $\{V_{AP}, V_{AP}\}$ ,  $\{V_{AP}, V_P\}$ ,  $\{V_P, V_{AP}\}$ ,  $\{V_P, V_P\}$ . Setting a  $V_{\text{ref}} = (V_{AP,AP} + V_{AP,P})/2$  ensures the sense amplifier will produce a logic “1” output only when both the bit cells are in the antiparallel state (logic AND). Similarly, for logic OR,  $V_{\text{ref}} = (V_{AP,P} + V_{P,P})/2$  will serve the purpose. For the resistance and sense current used in our study, we get  $V_{AP,AP} = 5 \text{ mV}$ ,  $V_{AP,P} = 4.29 \text{ mV}$ ,  $V_{P,AP} = 4.29 \text{ mV}$ ,  $V_{P,P} = 3.75 \text{ mV}$ , which give  $V_{\text{ref, AND}} = 4.65 \text{ mV}$ ;  $V_{\text{ref, OR}} = 4.02 \text{ mV}$ . We can set the reference voltage by tuning the reference resistance of the sense amplifier, and therefore, we can perform reconfigurable in-memory computing by tuning the reference voltage. The energy components for a full-cycle (write-read) in-memory Boolean computing are summarized in Fig. 6, which shows that  $E_{\text{write}}$  is the dominant contribution. This suggests the energy efficiency of the STI SOTRAM bit cell for in-memory computing because the write energy of STI SOTRAM is much smaller than that of a conventional HM-based device, as shown in Fig. 5 (see the comparison with other emerging technology in Table II). Note that we assume a symmetric write operation [79] for both bits “0” and “1”, and the energy associated with the sense amplifier is estimated as  $\frac{1}{2}C\Delta V^2$ , where  $C$  is the capacitance of the sense amplifier (typically 1 pF [80,81]) and  $\Delta V$  is the difference between the sense voltage and the reference voltage. The estimated total area for the Boolean operation is 6720 nm<sup>2</sup>, which includes the area of the bit cells and the read-access transistor ( $W/L = 10/1$ ).

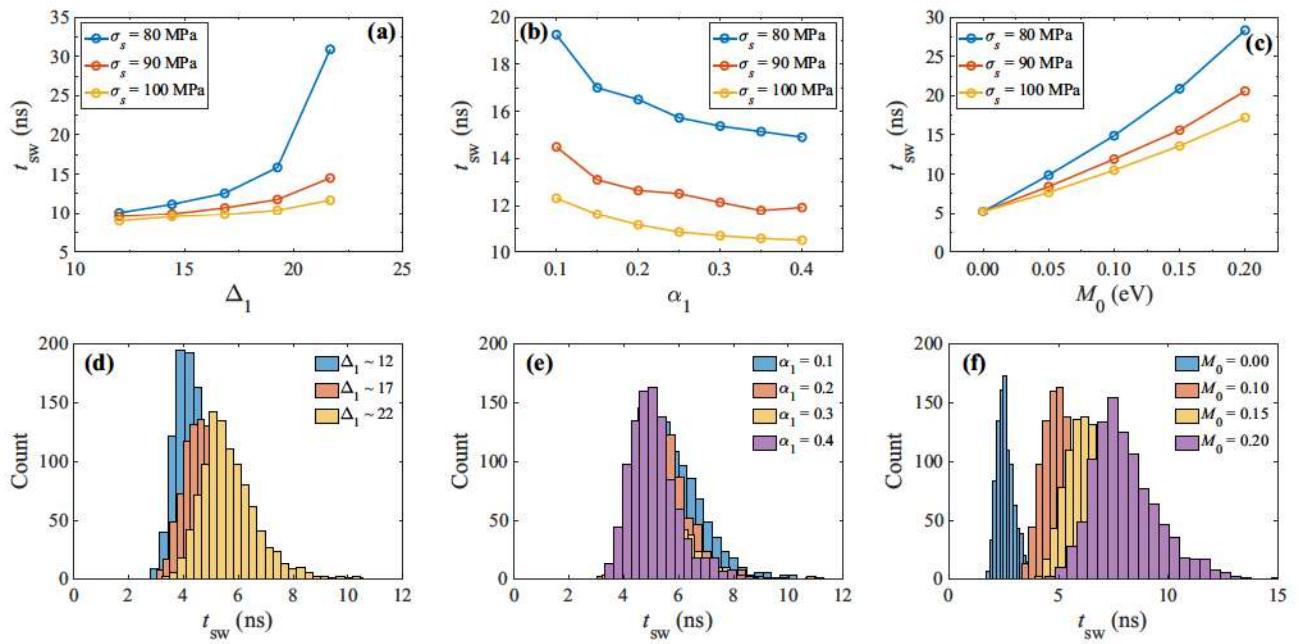

Finally, we present the effect of various key parameters on device switching time or delay  $t_{sw}$ . We show the effect of the thermal stability factor  $\Delta_1$  and damping coefficient

FIG. 6. Energy consumption for in-memory (a) AND and (b) OR operations.  $E_{\text{write}}$  and  $E_{\text{read}}$  are the combined energy for both the bit cells, while  $E_{\text{sense amp.}}$  represents the energy associated with a single sense amplifier.

$\alpha_1$  of the gating magnet and the exchange constant between the TI and the gating magnet  $M_0$  on  $t_{\text{sw}}$  for various  $\sigma_s$  values. In Fig. 7, the top panel shows the  $t_{\text{sw}}$  while the bottom panel shows the histogram of  $t_{\text{sw}}$  from 1000 simulations. For the case of varying  $\Delta_1$ , as it increases, the switching time of the gating magnet will increase for a specific  $\sigma_s$ , which increases the overall switching time of the device. While for a higher  $\alpha_1$ ,  $t_{\text{sw}}$  reduces as the gating magnet switching time reduces with a large damping coefficient because the gating magnet dynamics is governed by precessional and damping torques. We note that the switching dynamics of the free-layer magnet are influenced by its damping coefficient ( $\alpha_2$ ), which directly impacts the  $t_{\text{sw}}$ . In the case of SOT-driven switching, particularly for an in-plane magnet, an increase in the damping coefficient increases the critical current density required for switching [see Eq. (4)], as damping acts as a resistive force opposing the switching process [59,72]. Consequently, a higher  $\alpha_2$  increases  $t_{\text{sw}}$ , while a lower  $\alpha_2$  reduces it for a given current density. Lastly, if we increase  $M_0$ ,  $t_{\text{sw}}$  increases because the

gap opening is larger, and it takes longer to provide sufficient surface-state current in the TI. Note that even if we get a large  $M_0$ , the TSS band gap cannot be infinitely large as we are limited by the bulk band gap of the TI. In contrast, we need a larger value of  $M_0$  for a high ON-OFF ratio, which suggests the need for a TI with larger bulk band gap [45].

## V. CHALLENGES AND OPPORTUNITIES

The above results show excellent promise for utilizing the STI SOTRAM for an energy-efficient bit-storage device. However, it is worth discussing the challenges associated with implementing STI SOTRAM devices. We will separate these discussions into two categories—material issues vs device issues.

### A. Material challenges

Material issues exist [85] since we need three separate interfacial processes with input-output isolation—(a) strain

TABLE II. Stoplight chart for existing vs emerging memory technology [17,31,74,82–84]. Our device uses nonvolatile magnetic SOT technology, albeit with a superior TI underlayer with both a large SHA ( $> 10$ ) for low-power write and a gate-tunable band gap for energy-efficient (approximately 10s of aJ) row-column select. The resulting vertical structure of the selector-storage stack (Fig. 1) is well suited for compact, low-latency in-memory edge computing.

|              | SRAM<br>(45 nm)  | DRAM             | Flash<br>(NAND) | Flash<br>(NOR)  | FeRAM            | ReRAM                             | PCRAM                                                   | STTRAM            | SOTRAM            | STI<br>SOTRAM    |

|--------------|------------------|------------------|-----------------|-----------------|------------------|-----------------------------------|---------------------------------------------------------|-------------------|-------------------|------------------|

| Memory type  | Charge           | Charge           | Charge          | Charge          | FE capacitor     | Oxide charge                      | VO <sub>2</sub> , GST Bi <sub>2</sub> O <sub>3</sub> Se | Tunnel junction   | Tunnel junction   | Tunnel junction  |

| Endurance    | 10 <sup>16</sup> | 10 <sup>16</sup> | 10 <sup>4</sup> | 10 <sup>6</sup> | 10 <sup>10</sup> | 10 <sup>5</sup> – 10 <sup>8</sup> | 10 <sup>4</sup> – 10 <sup>9</sup>                       | >10 <sup>15</sup> | >10 <sup>15</sup> | >10 <sup>6</sup> |

| Read time    | 1–100 ns         | 30 ns            | ~1 $\mu$ s      | ~50 ns          | <10 ns           | <10 ns                            | <10 ns                                                  | <10 ns            | <10 ns            | <10 ns           |

| Write time   | 1–100 ns         | 50 ns            | 0.1–1 ms        | 1 – 10 $\mu$ s  | ~30 ns           | <10 ns                            | <50 ns                                                  | <10 ns            | <10 ns            | <10 ns           |

| Erase time   |                  | 50 ns            | 0.1 ms          | 10 ms           |                  |                                   |                                                         |                   |                   |                  |

| Write energy | ~ fJ             | ~10 fJ           | ~10 fJ          | ~100 pJ         | ~100 fJ          | 0.1–1 pJ                          | 10 pJ                                                   | ~100 fJ           | <100 fJ           | 1–100 fJ         |

| Size $F^2$   | 50–120           | 6–10             | 10              | 5               | 15–34            | 6–10                              | 4–10                                                    | 6–20              | 6–20              | 15–25            |

| Standby      | Current Leakage  | Refresh current  | None            | None            | None             | None                              | None                                                    | None              | Field assist      | No assist        |

| High voltage | No               | 2 V              | 10 V            | <10 V           | <3 V             | <3 V                              | <3 V                                                    | 3 V               | <1.5 V            | <1 V             |

| Nonvolatile  | No               | No               | Yes             | Yes             | Yes              | Yes                               | Yes                                                     | Yes               | Yes               | Yes              |

FIG. 7. Variation in switching time with respect to (a) the thermal stability factor of the gating magnet, (b) the damping coefficient of the gating magnet, and (c) the exchange strength between the TI and the gating magnet. (d)–(f) Histograms of the switching time from 1000 stochastic LLG simulations corresponding to (a)–(c), respectively. We use  $I_{0,\text{surf}} = 6I_{c,\text{surf}}$  while calculating the  $t_{\text{sw}}$ .

rotating the bottom selector magnet, (b) modulating the TSS with such rotation, and (c) TSS writing information onto the top storage magnet. Let us discuss these three processes one by one.

**(a) Can strain switch a magnet by 90°?** The magnetocrystalline anisotropy density  $K_u$  is often larger than stress energy. We will need to compositionally tune sputtered magnets like amorphous TbCo [68,69,86], or tailor film thickness of epitaxially grown CoFe to approach a small  $K_u$  near the out-of-plane to in-plane crossover [87]. The resulting low  $K_u$  can be overcome with stress, while being large enough to avoid spontaneous thermal fluctuations. The condition for switching is  $(3/2)\lambda_s\sigma_s > K_u$ , where  $\sigma_s$  is the uniaxial stress. The magnets referenced above have magnetostriction coefficient  $\lambda_s \sim 200-400 \times 10^{-6}$  [65,88] with elastic moduli approximately 100 GPa [64] and strain approximately 0.1%, which gives  $(3/2)\lambda_s\sigma_s \sim 30-60 \text{ kJ/m}^3$  and suggests successful switching of the magnetization if we can keep  $K_u$  lower.

**(b) Can a rotated magnet kill the TSS?** Theory [7] and experiments [6] show that an interfacing out-of-plane magnet opens a TSS band gap, leaving only chiral quantum anomalous edge states with significantly diminished spin-surface current. A 3D tight-binding-based study suggests the same, even accounting for bands along the patterned TI side walls [45]. Critically, the magnet must adjoin the TI, providing at least 50 mV exchange coupling. The  $g$  factor for the Zeeman gap is highly material

dependent (approximately 18 for  $\text{Bi}_2\text{Se}_3$ , approximately 6 for  $\text{Sb}_2\text{Te}_2\text{Se}$  [89]), while that depends on bulk band gap due to the magnetic proximity effect (approximately 20 meV for  $\text{EuS}/\text{Bi}_2\text{Se}_3$  [90], approximately 100 meV for  $\text{MnBi}_2\text{Se}_4/\text{Bi}_2\text{Se}_3$  [91]).

**(c) Can an activated TI write efficiently on the top magnet, accounting for small TI band gap and current shunting?** SHA, even in sputtered TI, can be large (approximately 10–20, about 100× greater than conventional HMs, e.g., Pt), switching magnets very efficiently [35,92]. TIs have small bulk band gaps approximately 100–300 meV that shunt current into the bulk and sidewalls. However, previous studies suggest that even for a modest band-gap TI, an ON-OFF ratio of approximately 10 might be able to flip spins of a magnet with a low WER [45]. This self-correction happens through internal anisotropy fields [93], an increased band gap with thin-film quantization [35,94], and reduced charge current with gap opening. To avoid current shunting into the storage magnet, a thin layer of insulating  $\text{NiO}$  [95] or  $\text{MgO}$  [96] can be grown that transmits magnon torque between the magnet and TI, or else use an insulating  $\text{BaFe}_{12}\text{O}_{19}$  as the storage magnet [97].

**(d) Can we separate conductive bulk states from surface states in a TI?** Critical to the success of our device is the ability to clearly isolate TI surface states from its conductive bulk states, and reliably place the Fermi energy roughly midgap. This is an ongoing topic of research where there has been considerable activity

but no consensus mechanism or widely accepted solution as of now, especially since typical TIs have small band gaps [98,99]. Specifically for  $\text{Bi}_2\text{Se}_3$ , the culprit can be unintentional vacancies and dopants, oxidation, and substrate-induced strain or charge transfer [100–103]. To avoid these effects, we need careful synthesis with precise control of stoichiometry [104,105], high purity Bi and Se precursors [106,107], Se-rich growth conditions [108] followed by postgrowth annealing and controlled cooling (quenching) to avoid vacancies [109,110], and a chemically inert or lattice-matched substrate [111]. Keeping the sample encapsulated (e.g., in  $h$ -BN) or in a vacuum or inert-gas environment would minimize exposure to air or oxidation [112–114]. Characterization tools such as x-ray photoelectron spectroscopy (XPS) can reveal the purity of the chemical composition [115], while angle-resolved photoelectron spectroscopy (ARPES) can provide information about the Fermi energy relative to the band edges [102,116,117]. A low carrier density ( $< 10^{18} \text{ cm}^3$ ) measured in the Hall effect [118] and temperature-dependent resistivity measurements can distinguish between metallic and semiconducting states [36,99,103]. A subsequent reliable measurement of high SOT, as mentioned earlier in subsection (c), will likely be attributable unequivocally to dominant spin-polarized surface states [119,120]. Compensatory doping can be used to counterbalance unintentional doping [103,121,122], while resonant doping and proximity effects from magnetic layers can help further move and pin the Fermi energy towards midgap or the Dirac point [123,124].

**(e) Can we grow and pattern the heterogeneous stack?** To grow the stack with compatible processing temperatures, we will need to sputter the  $\text{Bi}_2\text{Se}_3$  directly onto a magnet on a piezo, such as  $\text{Pb}(\text{Zr},\text{Ti})\text{O}_3(\text{PZT})/\text{Pb}(\text{Mg}_{1/3}\text{Nb}_{2/3})\text{O}_3\text{-PbTiO}_3$  (PMNT). Previous experiments show that amorphous TI retains band gap, topological protection, and high SHA [35,125,126], even after patterning with wet etching [127]. Besides mechanical decoupling, the stacks are also electrically decoupled, as the strains on a common piezo substrate stay localized around the contacts [4,128].

## B. Device-circuit-architecture issues

Table II shows projected performance metrics for our device vs competing memory technology, especially for PIM and embedded applications.

**(a) Key application space.** Our device is similar to a DRAM crossbar, complementary to nonvolatile memory in the low-power and embedded space, and competitive in NAND space with similar trade benefits as MRAM and SOTRAM. It capitalizes on SOT technology, which is attractive as the last-level-embedded cache for digital AI and stand-alone off-chip cache for analog AI. The device uses a superior TI channel that is both spin selective with

high SOT efficiency and gate tunable with low-power strain gating. For in-memory computing in embedded applications (image processing, combinatorial optimization) for edge intelligence, error tolerance and retention needs are low while energy and latency are premium. Our energy budget is low with write voltage  $< 100 \text{ mV}$  for thin film (approximately  $1 \mu\text{m}$  on conducting substrate)/2D monolayer piezos. Our device projects excellent metrics with approximately  $2\text{--}3 \times$  improvement over DRAM in energy-delay products.

**(b) Critical current and voltage.** Our projected current density approximately  $10^5\text{--}10^6 \text{ A/cm}^2$  is typical of STTRAMs and can be further reduced with higher SHA. Since the TSS are metallic in ON state (conductivity of BiSe approximately  $8000\text{--}60\,000 \Omega^{-1}\text{m}^{-1}$ ), our room-temperature write voltage is projected to be  $< 100 \text{ mV}$ .

**(c) Back-end-of-the-line (BEOL) integration.** TIs can be sputtered and wet etched while retaining high SHA, so usual BEOL metallization steps should work. Both TI and magnets should survive  $85^\circ\text{--}100^\circ\text{C}$  processing temperatures. Thermal degradation of TI does not usually occur below  $300^\circ\text{C}$ .

**(d) Endurance, stability, and device-to-device variations.** While HM-based SOTRAM endurance is approximately  $10^{15}$ , piezo fatigue and TI endurance limit our STI SOTRAM device to approximately  $5 \times 10^6$  cycles [129,130]. While this is significantly lower endurance, we believe this would suffice for hyperdense, nonvolatile persistent cells in PIM applications, where the probability of data overwrite per cell is very low (approximately  $10^{-3}$ , easily error corrected [131]).

**(e) Data retention, read disturb tolerance and scalability.** The lower selector magnet needs small out-of-plane anisotropy for strain gating, while the upper storage magnet needs a higher barrier consistent with SOTRAM technology with 10-year retention. Like SOT, we avoid read disturbs with separate read-write paths (unlike SOT, we do not need field assist to circumvent stagnation, as our TI spins and storage magnet are in plane). The top MTJ requires ion milling and mesa etching, which the TSS are known to survive.

**(f) Density.** Our device footprint is similar to three-terminal SOT, slightly bigger than STTRAM, DRAM, and flash. We compete on density (and latency) by rolling storage and processing into one bit cell, along with nonvolatile magnetic storage and ultralow energy field-free write using strain gating (approximately 10 aJ), and high SHA (approximately 10), key metrics for embedded applications and edge intelligence.

## VI. CONCLUSION

In summary, we demonstrated a four-layer piezoelectric/magnet/TI/MTJ bit-cell design with reduced energy cost and footprint for in-memory computing. Eliminating

an access transistor with a built-in strain-based gating mechanism has proved energy efficient, yielding an overall reduced energy cost. High-speed operation is achieved with significantly less energy than the traditional SOT metals at the device and array level. Our results suggest this heterogeneous stack may provide a compact and energy-efficient design for low-power, high-speed *in situ* applications.

The challenges at this time are the yet-to-be-demonstrated ability to fabricate the entire stack, the lower endurance associated with TIs (which is a lesser issue with PIM as the data overwrite per cell is low), ensuring the bulk-insulating properties of the TI itself, and the established challenges with SOT, such as higher footprint (again, PIM saves at the circuit level by rolling memory and logic into one unit), and higher current (but lower voltage since the HM has lower resistance). The in-plane spins help with field assist but hurt with scaling. Out-of-plane field-free switching has been demonstrated with SOTs and with Weyl semimetals [132–134].

## ACKNOWLEDGMENTS

We thank S. Joseph Poon at the University of Virginia, Supriyo Bandyopadhyay at Virginia Commonwealth University, Joseph A. Hagmann at Mitre, Patrick Taylor, George de Coster, and Mahesh R Neupane at Army Research Laboratories, Andrew D. Kent at New York University, Daniel B. Gopman at the National Institute of Standards at Technology, and Steve Kramer at Micron for insightful discussions. This work was supported in part by the NSF I/UCRC on Multi-functional Integrated System Technology (MIST) Center; IIP-1439644, IIP-1439680, IIP-1738752, IIP-1939009, IIP-1939050, and IIP-1939012. The calculations were performed using the computational resources from high-performance computing systems at the University of Virginia (Rivanna).

[1] A. Roohi, S. Angizi, and D. Fan, in *Frontiers of Quality Electronic Design (QED): AI, IoT and Hardware Security* (Springer, Cham, Switzerland, 2022), p. 415.

[2] Maximizing Edge Intelligence Requires More Than Computing | SEMI (2024), [Online: accessed June 7, 2024].

[3] K. Roy, S. Bandyopadhyay, and J. Atulasimha, Hybrid spintronics and straintronics: A magnetic technology for ultra low energy computing and signal processing, *Appl. Phys. Lett.* **99**, 063108 (2011).

[4] A. K. Biswas, H. Ahmad, J. Atulasimha, and S. Bandyopadhyay, Experimental demonstration of complete 180° reversal of magnetization in isolated Co nanomagnets on a PMN–PT substrate with voltage generated strain, *Nano Lett.* **17**, 3478 (2017).

[5] X. Duan, X.-L. Li, X. Li, Y. G. Semenov, and K. W. Kim, Highly efficient conductance control in a topological insulator based magnetoelectric transistor, *J. Appl. Phys.* **118**, 224502 (2015).

[6] J.-C. Rojas-Sánchez, S. Oyarzún, Y. Fu, A. Marty, C. Vergnaud, S. Gambarelli, L. Vila, M. Jamet, Y. Ohtsubo, A. Taleb-Ibrahimi, P. Le Fèvre, F. Bertran, N. Reyren, J.-M. George, and A. Fert, Spin to charge conversion at room temperature by spin pumping into a new type of topological insulator:  $\alpha$ -Sn films, *Phys. Rev. Lett.* **116**, 096602 (2016).

[7] J. M. Marmolejo-Tejada, K. Dolui, P. Lazić, P.-H. Chang, S. Smidstrup, D. Stradi, K. Stokbro, and B. K. Nikolić, Proximity band structure and spin textures on both sides of topological-insulator/ferromagnetic-metal interface and their charge transport probes, *Nano Lett.* **17**, 5626 (2017).

[8] A. R. Mellnik, J. S. Lee, A. Richardella, J. L. Grab, P. J. Mintun, M. H. Fischer, A. Vaezi, A. Manchon, E.-A. Kim, N. Samarth, and D. C. Ralph, Spin-transfer torque generated by a topological insulator, *Nature* **511**, 449 (2014).

[9] Y. Fan, P. Upadhyaya, X. Kou, M. Lang, S. Takei, Z. Wang, J. Tang, L. He, L.-T. Chang, M. Montazeri, G. Yu, W. Jiang, T. Nie, R. N. Schwartz, Y. Tserkovnyak, and K. L. Wang, Magnetization switching through giant spin–orbit torque in a magnetically doped topological insulator heterostructure, *Nat. Mater.* **13**, 699 (2014).

[10] J. Han, A. Richardella, S. A. Siddiqui, J. Finley, N. Samarth, and L. Liu, Room-temperature spin-orbit torque switching induced by a topological insulator, *Phys. Rev. Lett.* **119**, 077702 (2017).

[11] N. H. D. Khang, Y. Ueda, and P. N. Hai, A conductive topological insulator with large spin Hall effect for ultralow power spin–orbit torque switching, *Nat. Mater.* **17**, 808 (2018).

[12] W. A. Wulf and S. A. McKee, Hitting the memory wall: Implications of the obvious, *ACM SIGARCH Computer Architecture News* **23**, 20 (1995).

[13] X. Zou, S. Xu, X. Chen, L. Yan, and Y. Han, Breaking the Von Neumann bottleneck: Architecture-level processing-in-memory technology, *Sci. China Inform. Sci.* **64**, 160404 (2021).

[14] D. Patterson, T. Anderson, N. Cardwell, R. Fromm, K. Keeton, C. Kozyrakis, R. Thomas, and K. Yelick, A case for intelligent RAM, *IEEE Micro* **17**, 34 (1997).

[15] S. Ghose, A. Boroumand, J. S. Kim, J. Gómez-Luna, and O. Mutlu, Processing-in-memory: A workload-driven perspective, *IBM J. Res. Dev.* **63**, 1 (2019).

[16] N. Verma, H. Jia, H. Valavi, Y. Tang, M. Ozatay, L.-Y. Chen, B. Zhang, and P. Deaville, In-memory computing: Advances and prospects, *IEEE Solid-State Circuits Mag.* **11**, 43 (2019).

[17] P. Mannocci, M. Farronato, N. Lepri, L. Cattaneo, A. Glukhov, Z. Sun, and D. Ielmini, In-memory computing with emerging memory devices: Status and outlook, *APL Mach. Learn.* **1**, 010902 (2023).

[18] O. Mutlu, S. Ghose, J. Gómez-Luna, and R. Ausavarungnirun, Processing data where it makes sense: Enabling in-memory computation, *Microprocess. Microsyst.* **67**, 28 (2019).

[19] F. Parveen, S. Angizi, Z. He, and D. Fan, in *2017 IEEE/ACM International Symposium on Low Power Electronics and Design (ISLPED)* (IEEE, Taipei, 2017), p. 1.

[20] J. Lee, B.-G. Park, and Y. Kim, Implementation of Boolean logic functions in charge trap flash for in-memory computing, *IEEE Electron Device Lett.* **40**, 1358 (2019).

[21] X. Xie, Z. Liang, P. Gu, A. Basak, L. Deng, L. Liang, X. Hu, and Y. Xie, in *2021 IEEE International Symposium on High-Performance Computer Architecture (HPCA)* (IEEE, Seoul, 2021), p. 570.

[22] D. Fan, S. Angizi, and Z. He, in *2017 IEEE Computer Society Annual Symposium on VLSI (ISVLSI)* (IEEE, Bochum, 2017), p. 683.

[23] Z. He, Y. Zhang, S. Angizi, B. Gong, and D. Fan, Exploring a SOT-MRAM based in-memory computing for data processing, *IEEE Trans. Multi-Scale Comput. Syst.* **4**, 676 (2018).

[24] L. Liu, C.-F. Pai, Y. Li, H. W. Tseng, D. C. Ralph, and R. A. Buhrman, Spin-torque switching with the giant spin Hall effect of tantalum, *Science* **336**, 555 (2012).

[25] L. Liu, O. J. Lee, T. J. Gudmundsen, D. C. Ralph, and R. A. Buhrman, Current-induced switching of perpendicularly magnetized magnetic layers using spin torque from the spin Hall effect, *Phys. Rev. Lett.* **109**, 096602 (2012).

[26] I. M. Miron, K. Garello, G. Gaudin, P.-J. Zermatten, M. V. Costache, S. Auffret, S. Bandiera, B. Rodmacq, A. Schuhl, and P. Gambardella, Perpendicular switching of a single ferromagnetic layer induced by in-plane current injection, *Nature* **476**, 189 (2011).

[27] G. Prenat, K. Jabeur, G. Di Pendina, O. Boulle, and G. Gaudin, in *Spintronics-based Computing* (Springer, Cham, Switzerland, 2015), p. 145.

[28] I. Ahmed, Z. Zhao, M. G. Mankalale, S. S. Sapatnekar, J.-P. Wang, and C. H. Kim, A comparative study between spin-transfer-torque and spin-Hall-effect switching mechanisms in PMTJ using SPICE, *IEEE J. Explor. Solid-State Comput. Devices Circuits* **3**, 74 (2017).

[29] Q. Shao, P. Li, L. Liu, H. Yang, S. Fukami, A. Razavi, H. Wu, K. Wang, F. Freimuth, Y. Mokrousov, M. D. Stiles, S. Emori, A. Hoffmann, J. Åkerman, K. Roy, J.-P. Wang, S.-H. Yang, K. Garello, and W. Zhang, Roadmap of spin-orbit torques, *IEEE Trans. Magn.* **57**, ArticleSequenceNumber:800439 (2021).

[30] K. Garello, F. Yasin, S. Couet, L. Souriau, J. Swerts, S. Rao, S. Van Beek, W. Kim, E. Liu, S. Kundu, D. Tsvetanova, K. Croes, N. Jossart, E. Grimaldi, M. Baumgartner, D. Crotti, A. Fumémont, P. Gambardella, and G. Kar, in *2018 IEEE Symposium on VLSI Circuits* (IEEE, Honolulu, 2018), p. 81.

[31] F. Oboril, R. Bishnoi, M. Ebrahimi, and M. B. Tahoori, Evaluation of hybrid memory technologies using SOT-MRAM for on-chip cache hierarchy, *IEEE Trans. Comput. Aided Des. Integr. Circuits Syst.* **34**, 367 (2015).

[32] T. Kim, Y. Jang, M.-G. Kang, B.-G. Park, K.-J. Lee, and J. Park, SOT-MRAM digital PIM architecture with extended parallelism in matrix multiplication, *IEEE Trans. Comput.* **71**, 2816 (2022).

[33] V. Ostwal, A. Penumatcha, Y.-M. Hung, A. D. Kent, and J. Appenzeller, Spin-orbit torque based magnetization switching in Pt/Cu/[Co/Ni]5 multilayer structures, *J. Appl. Phys.* **122**, 213905 (2017).

[34] C.-F. Pai, L. Liu, Y. Li, H. W. Tseng, D. C. Ralph, and R. A. Buhrman, Spin transfer torque devices utilizing the giant spin Hall effect of tungsten, *Appl. Phys. Lett.* **101**, 122404 (2012).

[35] T. Fan, N. H. D. Khang, S. Nakano, and P. N. Hai, Ultra-high efficient spin orbit torque magnetization switching in fully sputtered topological insulator and ferromagnet multilayers, *Sci. Rep.* **12**, 1 (2022).

[36] Y. Wang, D. Zhu, Y. Wu, Y. Yang, J. Yu, R. Ramaswamy, R. Mishra, S. Shi, M. Elyasi, K.-L. Teo, Y. Wu, and H. Yang, Room temperature magnetization switching in topological insulator-ferromagnet heterostructures by spin-orbit torques, *Nat. Commun.* **8**, 1 (2017).

[37] M. Dc, R. Grassi, J.-Y. Chen, M. Jamali, D. Reifsnyder Hickey, D. Zhang, Z. Zhao, H. Li, P. Quarterman, Y. Lv, M. Li, A. Manchon, K. A. Mkhoyan, T. Low, and J.-P. Wang, Room-temperature high spin-orbit torque due to quantum confinement in sputtered  $\text{Bi}_x\text{Se}(1-x)$  films, *Nat. Mater.* **17**, 800 (2018).

[38] M. Z. Hasan and C. L. Kane, Colloquium: Topological insulators, *Rev. Mod. Phys.* **82**, 3045 (2010).

[39] Y. Ando, Topological insulator materials, *J. Phys. Soc. Jpn.* **82**, 102001 (2013).

[40] Y. Tokura, K. Yasuda, and A. Tsukazaki, Magnetic topological insulators, *Nat. Rev. Phys.* **1**, 126 (2019).

[41] M. S. Bahramy, P. D. C. King, A. de la Torre, J. Chang, M. Shi, L. Patthey, G. Balakrishnan, Ph. Hofmann, R. Arita, N. Nagaosa, and F. Baumberger, Emergent quantum confinement at topological insulator surfaces, *Nat. Commun.* **3**, 1 (2012).

[42] S. Barua, K. P. Rajeev, and A. K. Gupta, Evidence for topological surface states in metallic single crystals of  $\text{Bi}_2\text{Te}_3$ , *J. Phys.: Condens. Matter* **27**, 015601 (2014).

[43] Y. Wang, P. Deorani, K. Banerjee, N. Koirala, M. Brahlek, S. Oh, and H. Yang, Topological surface states originated spin-orbit torques in  $\text{Bi}_2\text{Se}_3$ , *Phys. Rev. Lett.* **114**, 257202 (2015).

[44] H. Wu, A. Chen, P. Zhang, H. He, J. Nance, C. Guo, J. Sasaki, T. Shirokura, P. N. Hai, B. Fang, S. A. Razavi, K. Wong, Y. Wen, Y. Ma, G. Yu, G. P. Carman, X. Han, X. Zhang, and K. L. Wang, Magnetic memory driven by topological insulators, *Nat. Commun.* **12**, 1 (2021).

[45] H. Vakili, S. Ganguly, G. J. de Coster, M. R. Neupane, and A. W. Ghosh, Low power in-memory computation with reciprocal ferromagnet/topological insulator heterostructures, *ACS Nano* **16**, 20222 (2022).

[46] J. Atulasimha and S. Bandyopadhyay, Bennett clocking of nanomagnetic logic using multiferroic single-domain nanomagnets, *Appl. Phys. Lett.* **97**, 173105 (2010).

[47] K. Roy, S. Bandyopadhyay, and J. Atulasimha, Switching dynamics of a magnetostrictive single-domain nanomagnet subjected to stress, *Phys. Rev. B* **83**, 224412 (2011).

[48] M. Trassin, Low energy consumption spintronics using multiferroic heterostructures, *J. Phys.: Condens. Matter* **28**, 033001 (2015).

[49] S. Bandyopadhyay, J. Atulasimha, and A. Barman, Magnetic straintronics: Manipulating the magnetization of magnetostrictive nanomagnets with strain for energy-efficient applications, *Appl. Phys. Rev.* **8**, 041323 (2021).

[50] S. Manipatruni, D. E. Nikonov, C.-C. Lin, B. Prasad, Y.-L. Huang, A. R. Damodaran, Z. Chen, R. Ramesh, and I. A. Young, Voltage control of unidirectional anisotropy

in ferromagnet-multiferroic system, *Sci. Adv.* **4**, eaat4229 (2018).

[51] Y. G. Semenov, X. Duan, and K. W. Kim, Electrically controlled magnetization in ferromagnet-topological insulator heterostructures, *Phys. Rev. B* **86**, 161406 (2012).

[52] K. Roy, S. Bandyopadhyay, and J. Atulasimha, Energy dissipation and switching delay in stress-induced switching of multiferroic nanomagnets in the presence of thermal fluctuations, *J. Appl. Phys.* **112**, 023914 (2012).

[53] M. S. Fashami, K. Roy, J. Atulasimha, and S. Bandyopadhyay, Magnetization dynamics, Bennett clocking and associated energy dissipation in multiferroic logic, *Nanotechnology* **22**, 155201 (2011).

[54] D. Winters, M. A. Abeed, S. Sahoo, A. Barman, and S. Bandyopadhyay, Reliability of magnetoelastic switching of nonideal nanomagnets with defects: A case study for the viability of straintronic logic and memory, *Phys. Rev. Appl.* **12**, 034010 (2019).

[55] P. K. Mishra, N. Halavath, and S. Bhuktare, Strain-mediated voltage controlled magnetic anisotropy based switching for magnetic memory applications, *J. Appl. Phys.* **134**, 123905 (2023).

[56] R. Yu, W. Zhang, H.-J. Zhang, S.-C. Zhang, X. Dai, and Z. Fang, Quantized anomalous Hall effect in magnetic topological insulators, *Science* **329**, 61 (2010).

[57] S. Cho, N. P. Butch, J. Paglione, and M. S. Fuhrer, Insulating behavior in ultrathin bismuth selenide field effect transistors, *Nano Lett.* **11**, 1925 (2011).

[58] Y. Xie, H. Vakili, S. Ganguly, and A. W. Ghosh, Anatomy of nanomagnetic switching at a 3D topological insulator PN junction, *Sci. Rep.* **13**, 1 (2023).

[59] S. Fukami, T. Anekawa, C. Zhang, and H. Ohno, A spin-orbit torque switching scheme with collinear magnetic easy axis and current configuration, *Nat. Nanotechnol.* **11**, 621 (2016).

[60] G. Yu, P. Upadhyaya, Y. Fan, J. G. Alzate, W. Jiang, K. L. Wong, S. Takei, S. A. Bender, L.-T. Chang, Y. Jiang, M. Lang, J. Tang, Y. Wang, Y. Tserkovnyak, P. K. Amiri, and K. L. Wang, Switching of perpendicular magnetization by spin-orbit torques in the absence of external magnetic fields, *Nat. Nanotechnol.* **9**, 548 (2014).

[61] G. Yu, L.-T. Chang, M. Akyol, P. Upadhyaya, C. He, X. Li, K. L. Wong, P. K. Amiri, and K. L. Wang, Current-driven perpendicular magnetization switching in Ta/CoFeB/[TaO<sub>x</sub> or MgO/TaO<sub>x</sub>] films with lateral structural asymmetry, *Appl. Phys. Lett.* **105**, 102411 (2014).

[62] J. A. Katine, F. J. Albert, R. A. Buhrman, E. B. Myers, and D. C. Ralph, Current-driven magnetization reversal and spin-wave excitations in Co /Cu /Co pillars, *Phys. Rev. Lett.* **84**, 3149 (2000).

[63] K.-S. Lee, S.-W. Lee, B.-C. Min, and K.-J. Lee, Threshold current for switching of a perpendicular magnetic layer induced by spin Hall effect, *Appl. Phys. Lett.* **102**, 112410 (2013).

[64] S. Yoshino, H. Takagi, S. Tsunashima, M. Masuda, and S. Uchiyama, Perpendicular magnetic anisotropy of TbCo films, *Jpn. J. Appl. Phys.* **23**, 188 (1984).

[65] J. Betz, K. Mackay, and D. Givord, Magnetic and magnetostrictive properties of amorphous Tb<sub>(1-x)</sub>Co<sub>x</sub> thin films, *J. Magn. Magn. Mater.* **207**, 180 (1999).

[66] F. Büttner, I. Lemesh, and G. S. D. Beach, Theory of isolated magnetic skyrmions: From fundamentals to room temperature applications, *Sci. Rep.* **8**, 1 (2018).

[67] A. Shukla, L. Heller, M. G. Morshed, L. Rehm, A. W. Ghosh, A. D. Kent, and S. Rakheja, in *2023 24th International Symposium on Quality Electronic Design (ISQED)* (IEEE, San Francisco, 2023), p. 1.

[68] Z. Zhao, M. Jamali, A. K. Smith, and J.-P. Wang, Spin Hall switching of the magnetization in Ta/TbFeCo structures with bulk perpendicular anisotropy, *Appl. Phys. Lett.* **106**, 132404 (2015).

[69] J. Finley and L. Liu, Spin-orbit-torque efficiency in compensated ferrimagnetic cobalt-terbium alloys, *Phys. Rev. Appl.* **6**, 054001 (2016).

[70] D. Bedau, H. Liu, J.-J. Bouzaglou, A. D. Kent, J. Z. Sun, J. A. Katine, E. E. Fullerton, and S. Mangin, Ultrafast spin-transfer switching in spin valve nanopillars with perpendicular anisotropy, *Appl. Phys. Lett.* **96**, 022514 (2010).

[71] Q. Wang, J. Domann, G. Yu, A. Barra, K. L. Wang, and G. P. Carman, Strain-mediated spin-orbit-torque switching for magnetic memory, *Phys. Rev. Appl.* **10**, 034052 (2018).

[72] M. G. Morshed, L. Rehm, A. Shukla, Y. Xie, S. Ganguly, S. Rakheja, A. D. Kent, and A. W. Ghosh, Reduced sensitivity to process, voltage and temperature variations in activated perpendicular magnetic tunnel junctions based stochastic devices, *arXiv:2310.18781*.

[73] U. Roy, T. Pramanik, L. F. Register, and S. K. Banerjee, Write error rate of spin-transfer-torque random access memory including micromagnetic effects using rare event enhancement, *IEEE Trans. Magn.* **52**, ArticleSequenceNumber:3402106 (2016).

[74] S. Yu and P.-Y. Chen, Emerging memory technologies: Recent trends and prospects, *IEEE Solid-State Circuits Mag.* **8**, 43 (2016).

[75] S. Honda, M. Nawate, M. Yoshiyama, and T. Kusuda, Magnetization properties of bias modulated TbCo films with short periodic modulation, *IEEE Trans. Magn.* **23**, 2952 (1987).

[76] P. Deorani, J. Son, K. Banerjee, N. Koirala, M. Brahlek, S. Oh, and H. Yang, Observation of inverse spin Hall effect in bismuth selenide, *Phys. Rev. B* **90**, 094403 (2014).

[77] L. Rehm, C. C. M. Capriata, S. Misra, J. D. Smith, M. Pinarbasi, B. G. Malm, and A. D. Kent, Stochastic magnetic actuated random transducer devices based on perpendicular magnetic tunnel junctions, *Phys. Rev. Appl.* **19**, 024035 (2023).

[78] L. Wei *et al.*, in *2019 IEEE International Solid-State Circuits Conference - (ISSCC)* (IEEE, San Francisco, 2019), p. 214.

[79] M. Y. Song, C. M. Lee, S. Y. Yang, G. L. Chen, K. M. Chen, I. J. Wang, Y. C. Hsin, K. T. Chang, C. F. Hsu, S. H. Li, J. H. Wei, T. Y. Lee, M. F. Chang, X. Y. Bao, C. H. Diaz, and S. J. Lin, in *2022 IEEE Symposium on VLSI Technology and Circuits (VLSI Technology and Circuits)* (IEEE, Honolulu, 2022), p. 377.

[80] R. C. Tozer, A low input capacitance sense amplifier for impedance imaging applications, *Meas. Sci. Technol.* **3**, 508 (1992).

[81] A. Conte, G. L. Giudice, G. Palumbo, and A. Signorello, A high-performance very low-voltage current sense amplifier for nonvolatile memories, *IEEE J. Solid-State Circuits* **40**, 507 (2005).

[82] S. A. Wolf, J. Lu, M. R. Stan, E. Chen, and D. M. Treger, The promise of nanomagnetics and spintronics for future logic and universal memory, *Proc. IEEE* **98**, 2155 (2010).

[83] T. Endoh, H. Koike, S. Ikeda, T. Hanyu, and H. Ohno, An overview of nonvolatile emerging memories—spintronics for working memories, *IEEE J. Emerging Sel. Top. Circuits Syst.* **6**, 109 (2016).

[84] A. Sebastian, M. Le Gallo, R. Khaddam-Aljameh, and E. Eleftheriou, Memory devices and applications for in-memory computing, *Nat. Nanotechnol.* **15**, 529 (2020).

[85] T. Schenk, M. Pesić, S. Slesazeck, U. Schroeder, and T. Mikolajick, Memory technology—a primer for material scientists, *Rep. Prog. Phys.* **83**, 086501 (2020).

[86] N. Anuniwat, M. Ding, S. J. Poon, S. A. Wolf, and J. Lu, Strain-induced enhancement of coercivity in amorphous TbFeCo films, *J. Appl. Phys.* **113**, 043905 (2013).

[87] R. Mandal, J. W. Jung, K. Masuda, Y. K. Takahashi, Y. Sakuraba, S. Kasai, Y. Miura, T. Ohkubo, and K. Hono, Investigation of Gilbert damping of a tetragonally distorted ultrathin  $Fe_{0.5}Co_{0.5}$  epitaxial film with high magnetic anisotropy, *Appl. Phys. Lett.* **113**, 232406 (2018).

[88] K. Serizawa, M. Ohtake, T. Kawai, M. Futamoto, F. Kirino, and N. Inaba, Magnetostriction Behaviors of  $Fe_{100-x}Co_x$  alloy epitaxial thin films under rotating magnetic field, *J. Magn. Soc. Jpn.* **43**, 50 (2019).

[89] Y.-S. Fu, T. Hanaguri, K. Igarashi, M. Kawamura, M. S. Bahramy, and T. Sasagawa, Observation of Zeeman effect in topological surface state with distinct material dependence, *Nat. Commun.* **7**, 1 (2016).

[90] J. Wang, T. Wang, M. Ozerov, Z. Zhang, J. Bermejo-Ortiz, S.-K. Bac, H. Trinh, M. Zhukovskyi, T. Orlova, H. Ambaye, J. Keum, L.-A. de Vaulchier, Y. Guldner, D. Smirnov, V. Lauter, X. Liu, and B. A. Assaf, Energy gap of topological surface states in proximity to a magnetic insulator, *Commun. Phys.* **6**, 1 (2023).

[91] A. K. Kaveev, S. M. Suturin, V. A. Golyashov, K. A. Kokh, S. V. Eremeev, D. A. Estyunin, A. M. Shikin, A. V. Okotrub, A. N. Lavrov, E. F. Schwier, and O. E. Tereshchenko, Band gap opening in the  $Bi_2Sb_2Te_3$  topological surface state induced by ferromagnetic surface reordering, *Phys. Rev. Mater.* **5**, 124204 (2021).