# Nonlinear Ion Dynamics Enable Spike Timing Dependent Plasticity of Electrochemical Ionic Synapses

Mantao Huang, Longlong Xu, Jesús A. del Alamo, Ju Li, and Bilge Yildiz\*

**Programmable synaptic devices that can achieve timing-dependent weight updates are key components to implementing energy-efficient spiking neural networks (SNNs). Electrochemical ionic synapses (EIS) enable the programming of weight updates with very low energy consumption and low variability. Here, the strongly nonlinear kinetics of EIS, arising from nonlinear dynamics of ions and charge transfer reactions in solids, are leveraged to implement various forms of spike-timing-dependent plasticity (STDP). In particular, protons are used as the working ion. Different forms of the STDP function are deterministically predicted and emulated by a linear superposition of appropriately designed pre- and post-synaptic neuron signals. Heterogeneous STDP is also demonstrated within the array to capture different learning rules in the same system. STDP timescales are controllable, ranging from milliseconds to nanoseconds. The STDP resulting from EIS has lower variability than other hardware STDP implementations, due to the deterministic and uniform insertion of charge in the tunable channel material. The results indicate that the ion and charge transfer dynamics in EIS can enable bio-plausible synapses for SNN hardware with high energy efficiency, reliability, and throughput.**

## 1. Introduction

Artificial neural networks have shown promising applications in a wide range of fields including image and speech recognition, natural language processing, and content generation.<sup>[1-3]</sup> However, such computations are becoming prohibitively energy-intensive to perform on conventional digital computers.<sup>[4-6]</sup> Human brains function with spiking signals from billions of neurons with trillions of synaptic connections, at a power consumption of only tens of watts.<sup>[7]</sup> Inspired by the energy-efficient spike-based biological systems, spiking neural networks (SNNs) have the potential to realize substantial enhancements in the energy efficiency of computing. SNNs are spike-driven networks that use sparse and asynchronous spiking events and biologically realistic behavior of synapses and neurons for carrying out computations.<sup>[8-11]</sup> These systems are adaptive, as they can perform online learning to adapt to new situations over time, while traditional neural

M. Huang, J. Li, B. Yildiz

Department of Nuclear Science and Engineering

Massachusetts Institute of Technology

Cambridge, MA 02139, USA

E-mail: [byildiz@mit.edu](mailto:byildiz@mit.edu)

L. Xu, J. Li, B. Yildiz

Department of Materials Science and Engineering

Massachusetts Institute of Technology

Cambridge, MA 02139, USA

J. A. del Alamo, B. Yildiz

Microsystems Technology Laboratories

Massachusetts Institute of Technology

Cambridge, MA 02139, USA

J. A. del Alamo

Department of Electrical Engineering and Computer Science

Massachusetts Institute of Technology

Cambridge, MA 02139, USA

The ORCID identification number(s) for the author(s) of this article can be found under <https://doi.org/10.1002/adma.202418484>

© 2025 The Author(s). Advanced Materials published by Wiley-VCH GmbH. This is an open access article under the terms of the [Creative Commons Attribution-NonCommercial-NoDerivs](#) License, which permits use and distribution in any medium, provided the original work is properly cited, the use is non-commercial and no modifications or adaptations are made.

DOI: [10.1002/adma.202418484](https://doi.org/10.1002/adma.202418484)

networks need to be trained with backpropagation in separate cycles. SNNs can implement local learning rules, taking input from pre- and post-synaptic neurons, offering the potential for powering low-energy smart devices with adaptive sensory processing<sup>[12]</sup> and real-time learning.<sup>[13]</sup> Artificial spiking neurons have also shown promise to interface with biochemical signals by leveraging ion-based operating mechanisms in organic materials.<sup>[14-16]</sup>

One of the key components to implementing SNN hardware is the synaptic device that has to emulate timing-dependent learning rules, such as spike-timing-dependent plasticity (STDP). STDP is an important learning rule in brain synapses.<sup>[17]</sup> Emulating STDP serves as a basis for further explorations to achieve more bio-realistic and more capable machine intelligence beyond traditional deep neural networks.<sup>[9]</sup> STDP learning rules essentially strengthen or weaken the synaptic connection between two neurons when the spiking events of the pre-and post-synaptic neuron take place in a specific temporal sequence.<sup>[18]</sup> The synaptic weight change, or conductance change,  $\Delta G$ , is a function of the relative timing,  $\Delta t$ , of the spiking events, and such a function is called the STDP function. One common form of STDP is that the synaptic weight change is positive if the post-neuron fires shortly after the pre-neuron, and negative if the pre-neuron fires shortly after the post-neuron. The modulation strength in this form of STDP increases when the pre-and post-synaptic

neurons fire close to each other, and the magnitude decreases with increasing  $\Delta t$  between the two firing events. STDP has been shown to enable coincidence detection,<sup>[19]</sup> latency reduction,<sup>[20]</sup> and supervised and unsupervised learning.<sup>[21]</sup> STDP has remarkable diversity in the sign, symmetry, and shape of plasticity.<sup>[18]</sup> Heterogeneous STDP functions are also observed to occur in the same brain region, even at synapses from the same pre-synaptic neurons connecting to different post-synaptic neuron types.<sup>[22,23]</sup> For example, in the dorsal cochlear nucleus, synapses that connect the parallel fiber to fusiform cells follow different synaptic plasticity rules compared to the synapses that connect the same parallel fiber to the cartwheel cells.<sup>[22]</sup> Such diversity and versatility of biologically observed STDP require the hardware platform to have the same flexibility to implement these different STDP forms.

Programmable resistors based on conductive filament formation,<sup>[19,24–27]</sup> phase-change mechanism,<sup>[28,29]</sup> and ferroelectricity<sup>[30–32]</sup> have been explored to implement time-dependent update rules such as STDP for SNN hardware. The stochasticity of the conducting filament-forming process causes high variability in conductance updates and unreliability of training.<sup>[33]</sup> The phase-change mechanism has been associated with high energy consumption and conductance drift.<sup>[33,34]</sup> Ferroelectric tunneling junctions (FTJs) and ferroelectric field effect transistors (FeFETs) have increased variability from the nonuniformity of the polycrystalline ferroelectric layer and stochastic switching kinetics.<sup>[35]</sup> Engineering of materials, processing, and operation protocols could improve the variability of these devices.<sup>[36–38]</sup> The variability can also be partially compensated by SNN design such as the homeostasis mechanism<sup>[39]</sup> using more complex synapses and neurons. However, the variations of the modulation characteristics such as the threshold voltage could become a key challenge for achieving good reliability and high performance with spiking neural networks.<sup>[19]</sup> It is highly desirable to implement reliable time-dependent learning rules with low variability, low energy consumption, fast operation speed, and lean footprint.

Electrochemical ionic synapses (EIS), also known as electrochemical random-access memory (ECRAM), are three-terminal programmable resistors with conductance controlled deterministically by electrochemical charge insertion.<sup>[40–47]</sup> The conductance of a channel material is modulated by ion and electron insertion/extraction, controlled by an applied electrochemical potential difference at a gate terminal with respect to the channel.<sup>[47]</sup> Due to their low energy consumption, low variability, and deterministic charge-controlled conductivity modulation, EIS devices are being studied and pursued for their potential to enable energy-efficient analog neural networks.<sup>[40,41,43]</sup> Using the intrinsic nonlinearity of EIS devices could be one effective way to emulate STDP in an energy-efficient and controllable manner. To date, achieving STDP with EIS has not been shown in the field, and demonstrating this is the goal of this paper. EIS devices have a very strong nonlinear response to applied voltage.<sup>[45,42]</sup> This arises from the nonlinear electric field dependence of ion transport and interfacial charge transfer kinetics in EIS, as well as the nonlinear dependence of electronic conductivity on the concentration of ions and electrons inserted in certain channel materials.<sup>[44,47]</sup> This nonlinear kinetics of EIS presents an opportunity to achieve timing-dependent weight updates in a synaptic device as needed for STDP and SNNs.

In this paper, we leverage the nonlinearity of EIS to achieve various forms of STDP learning rules. We use proton as the working ion in the EIS devices.<sup>[44,45,48]</sup> We reliably predict and design the form of the STDP function based on the pre-and post-neuron signals superimposed at the gate of EIS. We show that the timing-dependent weight update allows heterogeneous choices of STDP function shapes in synapses from a single neuron connecting to different post-synaptic neurons. We control the response timescales from milliseconds down to nanoseconds, with lower variability and lower energy consumption than other STDP attempts in the field. Our approach here leverages the intrinsic nonlinearities of the EIS device, without the need for transistors at each synapse, so the system has reduced footprint and fabrication complexity. These results point to the potential of EIS to serve as programmable synapses to enable reliable hardware implementations of SNN with high energy efficiency and high throughput.

## 2. Results and Discussion

### 2.1. Strongly Nonlinear Response of Electrochemical Ionic Synapses

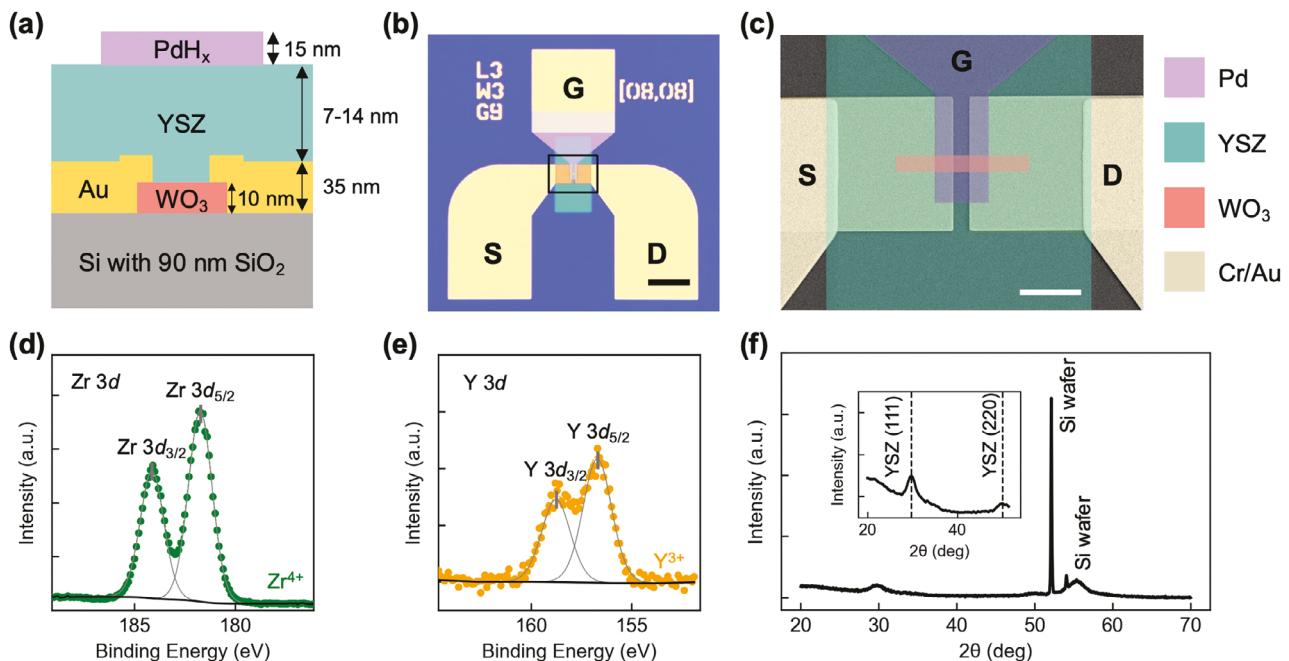

In this study, we focus on EIS devices using protons as the working ion.<sup>[44,45,48]</sup> Figure 1a–c shows the device structure and microscope images of an example EIS device fabricated in this work (see Experimental Section for device fabrication process). The devices consist of a 10 nm thick  $\text{WO}_3$  channel, a 7–14 nm thick yttria-stabilized zirconia (YSZ) layer as the solid-state electrolyte, and a 15 nm thick top Pd layer as the hydrogen reservoir layer and the gate. Source and drain contacts are made of Au with a Cr adhesion layer, connecting to the side of the channel. The channel lateral dimensions varied between 3 and 40  $\mu\text{m}$  for the width and length in different EIS devices used. The  $\text{WO}_3$  channel has tunable electronic conductance that is determined by the proton concentration in it, as we have shown in our earlier work.<sup>[44]</sup> The YSZ electrolyte is fully oxidized, as seen from the Zr 3d and Y 3d X-ray photoelectron emission peaks (Figure 1d,e), showing that the Zr and Y have valences of +4 and +3, respectively. The YSZ electrolyte is largely amorphous, as seen from the X-ray diffraction pattern in Figure 1f, and this is consistent with a film deposited at room temperature. The fully oxidized YSZ electrolyte is insulating for electrons, but its amorphous and likely nanoporous nature makes it conductive to protons through absorbed  $-\text{OH}$  groups.<sup>[49]</sup> The Pd layer becomes a hydrogen reservoir in the form of  $\text{PdH}_x$  when exposed to hydrogen-containing forming-gas prior to experiments.<sup>[44]</sup>

The application of a gate voltage that is higher than the open circuit voltage ( $-0.3$ – $0$  V, depending on the proton concentration in the  $\text{WO}_3$  channel<sup>[44]</sup>) oxidizes hydrogen in  $\text{PdH}_x$  and drives the protons from the reservoir through the electrolyte into the channel layer with electrons flowing through the external circuit from the gate to the channel. The electrons inserted into the  $\text{WO}_3$  along with the protons, lead to the filling of in-gap states of  $\text{WO}_3$  and increase its electronic conductivity.<sup>[44]</sup> The application of a gate voltage lower than the open circuit voltage reverses the process.

**Figure 1.** Structure and chemical characterizations of electrochemical ionic synapses (EIS) studied for emulating STDP functions. a) Schematic device structure with the gate ( $\text{PdH}_x$ ), electrolyte (yttria-stabilized zirconia, YSZ), channel ( $\text{WO}_3$ ), and source-drain (Au) contacts shown, and b) optical microscope image from the top of EIS devices experimentally characterized. S: source, D: drain, G: gate. The channel width and length are both  $3\ \mu\text{m}$  and the gate width is  $9\ \mu\text{m}$ . Scalebar,  $50\ \mu\text{m}$ . c) Top-view false-colored scanning electron microscope image of the device. Scalebar,  $10\ \mu\text{m}$ . d,e) X-ray photoelectron spectroscopy of the YSZ electrolyte centered at Zr 3d (d) and Y 3d (e). f) Grazing incidence X-ray diffraction pattern of the YSZ electrolyte layer. Inset, zoomed-in diffraction pattern near YSZ-related features. The diffraction pattern shows that YSZ is largely amorphous.

Because of the small size of the proton and the high sensitivity of the  $\text{WO}_3$  electronic conductivity to hydrogen concentration,<sup>[44]</sup> the device allows for high-speed (ns regime) modulation and high energy efficiency.<sup>[45]</sup> We have experimentally shown that these devices could be programmed reliably with very low energy consumption, close to  $20\ \text{aJ}$  per programming pulse for the proton transfer during the peak voltage of the pulses, with order of  $f\text{j}$  per pulse including the charging and discharging transients.<sup>[45]</sup> We use these protonic EIS devices to experimentally quantify the nonlinearity of the conductance change and leverage that nonlinearity to achieve timing-based conductance updates emulating different STDP forms.

The conductance change in an EIS has a strongly nonlinear dependence on the gate voltage when the gate voltage is away from the open circuit potential. This nonlinear dependence is a result of nonlinear ion transport through the electrolyte, nonlinear reaction kinetics at the interfaces as well as nonlinear dependence of the conductance of the channel on the inserted ion concentration.<sup>[44,47]</sup> When a strong electric field is present across the electrolyte, the energy barrier for ion conduction is lowered,<sup>[50]</sup> giving rise to a field-enhanced ionic conductivity,  $\sigma$ . The dependence of  $\sigma$  on the electric field,  $E$  through the electrolyte is approximately proportional to  $\sinh(\frac{q\sqrt{E}}{2k_B T})$ , where  $q$  is the ion charge,  $l_k$  is the hopping distance,  $k_B$  is the Boltzmann constant, and  $T$  is temperature. Similarly, the reaction kinetics at the interfaces can be described by the Butler–Volmer equation,<sup>[51]</sup>  $j = j_0(e^{\frac{\alpha zFV_i}{RT}} - e^{-\frac{(1-\alpha)zFV_i}{RT}})$ , where  $j$  is the reaction current density,  $j_0$  is the exchange current density,  $\alpha$  is the charge transfer coefficient

for the interface,  $F$  is the Faraday constant,  $R$  is the ideal gas constant,  $z$  is the ion charge number, and  $V_i$  is the overpotential at the interface. When  $\alpha$  is 0.5, the expression of  $j$  simplifies also to a sinh dependence on the local voltage such that  $j \propto \sinh \frac{zFV_i}{2RT}$ . This nonlinear voltage dependence has been experimentally observed for EIS devices with various ions.<sup>[45,42]</sup> The sinh relation has been used to explain and model the voltage dependence of conductance modulation for our EIS devices earlier.<sup>[45,42]</sup>

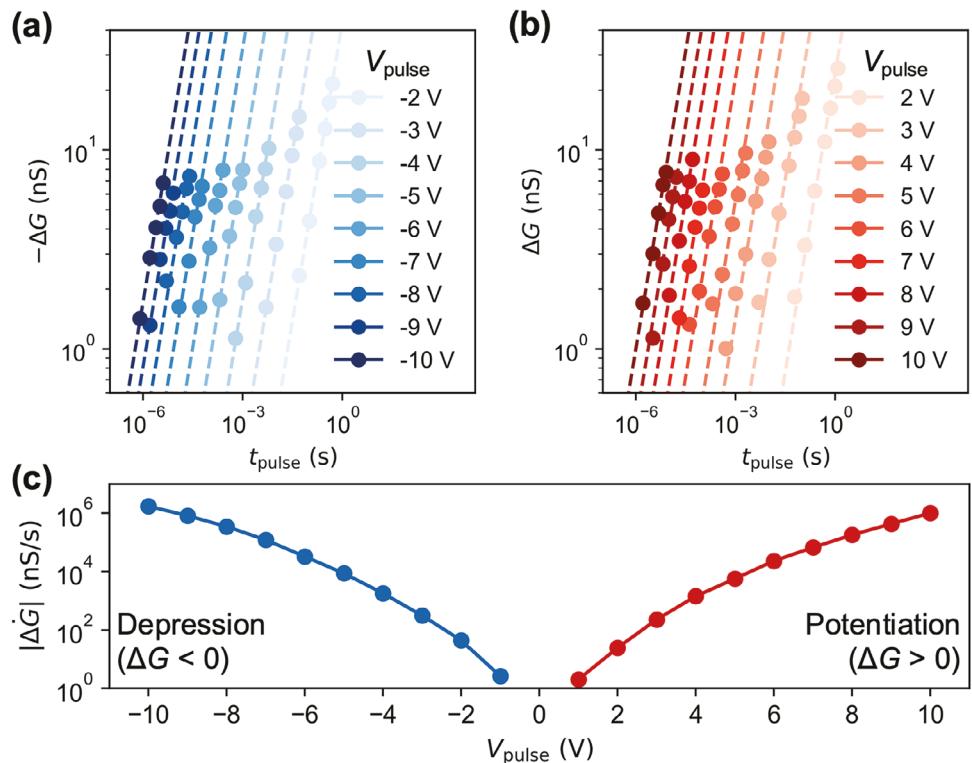

Figure 2a,b shows the conductance change of a device with a YSZ thickness ( $t_{\text{YSZ}}$ ) of  $14\ \text{nm}$ , as a function of pulse duration ( $t_{\text{pulse}}$ ) and pulse voltage ( $V_{\text{pulse}}$ ). For the same  $V_{\text{pulse}}$ , the change in conductance achieved in each pulse,  $\Delta G$ , scales nearly linearly with  $t_{\text{pulse}}$ , with small deviations. However,  $\Delta G$  gets exponentially larger for higher  $V_{\text{pulse}}$ . For example, an increase of  $V_{\text{pulse}}$  from 2 to 4 V speeds up (requires a lower value of  $t_{\text{pulse}}$ ) conductance modulation by  $\approx 60$  times, and an increase from 2 to 6 V speeds up by  $\approx 1000$  times. Figure 2c shows the rate of conductance change ( $\Delta \dot{G}$ ) as a function of pulse voltage. In addition, temperature can introduce additional non-linearities and impact multiple aspects of device operation (see Section SI, Supporting Information for a discussion on the effect of temperature). Such nonlinear dependence of  $\Delta \dot{G}$  on  $V_G$  enables the timing-based update of conductance at the EIS, as we describe and illustrate below.

## 2.2. Timing-Dependent Programming of Nonlinear EIS Devices

To implement timing-dependent learning rules with EIS, we apply the linear superposition of the voltage waveforms from the

**Figure 2.** Strong nonlinear response of EIS to the applied gate voltage. a,b) Channel conductance change ( $\Delta G$ ) as a function of pulse duration ( $t_{\text{pulse}}$ ) and pulse voltage ( $V_{\text{pulse}}$ ). Dashed lines are linear fits of the log-log plot of  $\Delta G$  versus  $t_{\text{pulse}}$ . (a) For  $V_{\text{pulse}} < 0$ . (b) For  $V_{\text{pulse}} > 0$ . c) The rate of conductance change  $\dot{\Delta G}$  as a function of  $V_{\text{pulse}}$ , obtained from the intersect of the linear fit on the log-log plot in (a) and (b).

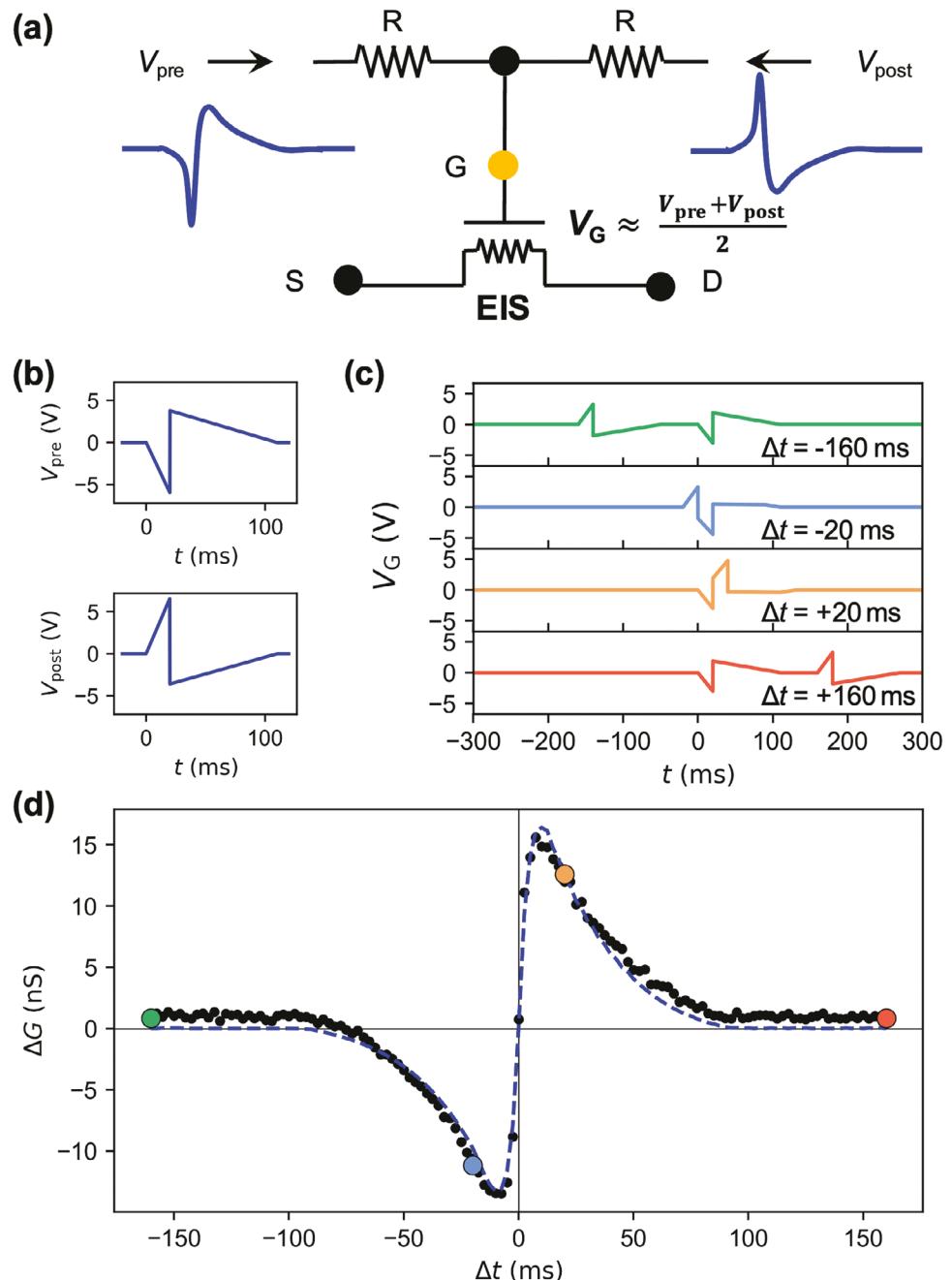

pre-and post-synaptic neurons to the gate of the EIS. The time dependence of the pre-and post-synaptic neuron firing waveforms is designed to target different forms of STDP. Figure 3a shows a simple and energy-efficient way to implement the linear superposition. A voltage divider is formed across the voltage waveforms from the pre-synaptic neuron ( $V_{\text{pre}}$ ) and the post-synaptic neuron ( $V_{\text{post}}$ ). For the voltage divider to produce the desired linear superposition of the voltages, the resistance of the resistors,  $R$ , needs to be much smaller than the gate resistance of the EIS device. The requirement is trivial to satisfy because the gate resistance of EIS devices is usually very high, for example, more than  $10 \text{ G}\Omega$  for a submicron device in ref. [45], because the electrolyte is electronically insulating (see Section SII, Supporting Information for achievable time scales). The resulting  $V_G$  waveform depends on the relative timing ( $\Delta t$ ) of the firing of the pre-and the post-synaptic neurons. Here we define  $\Delta t = t_{\text{post}} - t_{\text{pre}}$ , where  $t_{\text{post}}$  and  $t_{\text{pre}}$  are the times when the post- and pre-synaptic neuron fire, respectively.  $\Delta t$  is positive when the post-neuron fires after the pre-neuron. With an  $R$ -value sufficiently small, the gate voltage can be approximated by the formula  $V_G = (V_{\text{pre}} + V_{\text{post}})/2$ . The voltage divider structure does not consume energy when the neurons are in the resting state, and energy is only consumed during spiking events. (See Section SIII, Supporting Information for alternative circuit approaches).

Figure 3b-d shows an example of timing-based conductance modulation of a single EIS synapse to implement an STDP learning rule. Here we implement a common STDP form, where the conductance of a synapse increases for  $\Delta t > 0$  and decreases for

$\Delta t < 0$ . To achieve this form of STDP (Figure 3d), the  $V_{\text{pre}}$  and  $V_{\text{post}}$  waveform can be set to as shown in Figure 3b. The  $V_{\text{pre}}$  and  $V_{\text{post}}$  waveforms are designed such that they do not induce a large conductance change of the synapse if they fire alone. The self-compensating characteristic of  $V_{\text{pre}}$  and  $V_{\text{post}}$  waveforms ensures there is a significant net conductance change only when these two signals fire close enough and overlap in time. The shape of the  $V_{\text{pre}}$  and  $V_{\text{post}}$  are designed to enable targeted STDP forms, and the approach for designing such waveforms is described later in the section on obtaining different STDP forms. Depending on the timing of the firing of the pre-and post-synaptic neurons, the gate voltage ( $V_G(t) = (V_{\text{pre}}(t) + V_{\text{post}}(t))/2$ ) takes different waveforms for different  $\Delta t$  values, as shown in Figure 3c. In the experiments, the superimposed waveforms were calculated and applied to the gate of the EIS device using a function generator. After the  $V_G(t)$  waveform is complete, 0 V was applied to the EIS device as the resting potential, rather than an open circuit, for practical operation. Most of the conductance change takes place right after the spiking event, although the  $\Delta G$  quantified here is the conductance difference between right before and 20 s after the pre-synaptic neuron signal fires. (The delay time to read does not reflect the timescale of the conductance modulation). The resulting  $\Delta G$  as a function of relative timing,  $\Delta t$  is shown in Figure 3d. The amplitude of modulation is highest when the pre-and post-synaptic neurons fire close to each other (the absolute value of  $\Delta t$  is small). The resulting behavior clearly emulates the canonical STDP behavior seen in biological neural circuits. The  $\Delta G$  in Figure 3 is intentionally kept small to be comparable to the STDP

**Figure 3.** Timing-dependent programming of the EIS devices. a) The circuit used here to implement a linear superposition of voltage signals from the pre- and post-synaptic neurons. b) Waveforms of  $V_{pre}(t)$  and  $V_{post}(t)$  to achieve the canonical STDP function shown in (d). c) The waveforms at the gate terminal ( $V_G$ ) for  $\Delta t = -160$  ms,  $-20$  ms,  $+20$  ms, and  $+160$  ms (top to bottom). d) Conductance change ( $\Delta G$ ) after the firing of both the pre- and post-synaptic neurons, as a function of the relative timing of firing,  $\Delta t = t_{post} - t_{pre}$ , where  $t_{post}$  and  $t_{pre}$  are the times when the post- and pre-synaptic neuron fire, respectively. The black points are experimental data, and the dashed line is the modeled and calculated  $\Delta G$ . The  $\Delta G$  was calculated as the integration of the conductance change rate at each time segment multiplied by a scaling factor of 0.7 (see text for modeling of  $\Delta G$ ). The colored points correspond to the conductance change from the  $\Delta t$  and the  $V_G$  waveforms at four different  $\Delta t$  values shown in (c).

in synapses of the brain, where a single spiking event introduces only a small synaptic strength change.<sup>[17]</sup> The modulation ratio can be tuned by starting from different conductance levels, using waveforms with varying voltage or duration, and by continuously spiking to cause cumulative and larger changes in conductance as discussed in a later section. In addition, we maintain the

channel conductance in the  $\approx nS$  range, as this is the desirable and practical conductance level outlined in ref. [52]. This range prevents excessive current in metal lines and achieves low energy consumption in crossbar arrays. The devices offer flexibility in conductance, tunable over more than seven orders of magnitude by adjusting the ion concentration.<sup>[44]</sup> Additionally, the

conductance can be adjusted by modifying the channel's aspect ratio (see Section SIV, Supporting Information).

The shape of the timing-dependent conductance change curve can be qualitatively explained by the nonlinear dependence of the channel conductance change on the gate voltage. Because the conductance change is much greater at higher voltage, as explained above from the nonlinearity of the EIS, the conductance change from the portion of the  $V_G(t)$  waveform with a high voltage amplitude dominates. When  $\Delta t$  is close to 0 (e.g.,  $\Delta t = 20$  ms, and  $\Delta t = -20$  ms in Figure 3c), the conductance change is dominated by the large positive or negative voltage peak. When  $\Delta t$  is farther away from 0, the peak voltage becomes smaller, and the net conductance change becomes much smaller.

We model the time-dependent response of the EIS, to predict the learning curve from different  $V_G(t)$  waveforms, and to design  $V_{\text{pre}}(t)$  and  $V_{\text{post}}(t)$  waveforms. The STDP function can be calculated using the nonlinear dependence of conductance change on the gate voltage of EIS devices. If the spiking events of the pre- and the post-synaptic neuron take place at the same time, at  $t = 0$ , the waveforms are denoted as  $V_{\text{pre}}^0(t)$  and  $V_{\text{post}}^0(t)$  (such as those shown in Figure 3b). If the post-neuron spikes with a delay  $\Delta t$  relative to the pre-neuron, then we have  $V_{\text{post}}(t) = V_{\text{post}}^0(t - \Delta t)$  and  $V_{\text{pre}}(t) = V_{\text{pre}}^0(t)$ . The gate voltage waveform is therefore  $V_G(t) = \frac{V_{\text{pre}} + V_{\text{post}}}{2} = \frac{V_{\text{pre}}^0(t) + V_{\text{post}}^0(t - \Delta t)}{2}$ . Assuming there is no interaction between the time segments, we can calculate the change of conductance of the EIS as an integral of the rate of conductance change for each time segment:

$$\Delta G = \int \Delta \dot{G}(V_G(t)) dt = \int \Delta \dot{G} \left( \frac{V_{\text{pre}}^0(t) + V_{\text{post}}^0(t - \Delta t)}{2} \right) dt \quad (1)$$

where  $\Delta \dot{G}(V_G)$  is the rate of conductance change that depends on the gate voltage,  $V_G$ , and the limit of integration covers the whole period of the two spiking events. The rate of conductance change  $\Delta \dot{G}(V_G)$  is interpolated from the experimentally measured data in Figure 2c. The calculated time-dependence of the STDP curves (dashed lines in Figure 3d) show good agreement with the experimentally measured STDP from the EIS devices. We note that, after the conductance change from all  $\Delta t$  values is calculated through the integration in Equation (1), they are multiplied by a common factor between 0.5 and 0.7, such that the modeled conductance peak amplitude matches the experimental data. For a given combination of  $V_{\text{pre}}^0(t)$  and  $V_{\text{post}}^0(t)$ , a constant scaling factor is used. We attribute the discrepancy between the numerically modeled and experimentally measured STDP amplitudes to the complex dynamics of EIS. The conductance change of EIS cannot be treated as a simple integration over each time segment assumed to be non-interacting, also seen in Figure 2a,b. The behavior could be due to the intrinsic dynamics of the devices, including the capacitive processes such as the accumulation of ions at the interfaces.<sup>[47]</sup>

### 2.3. Implementing Different Bio-Realistic STDP Forms

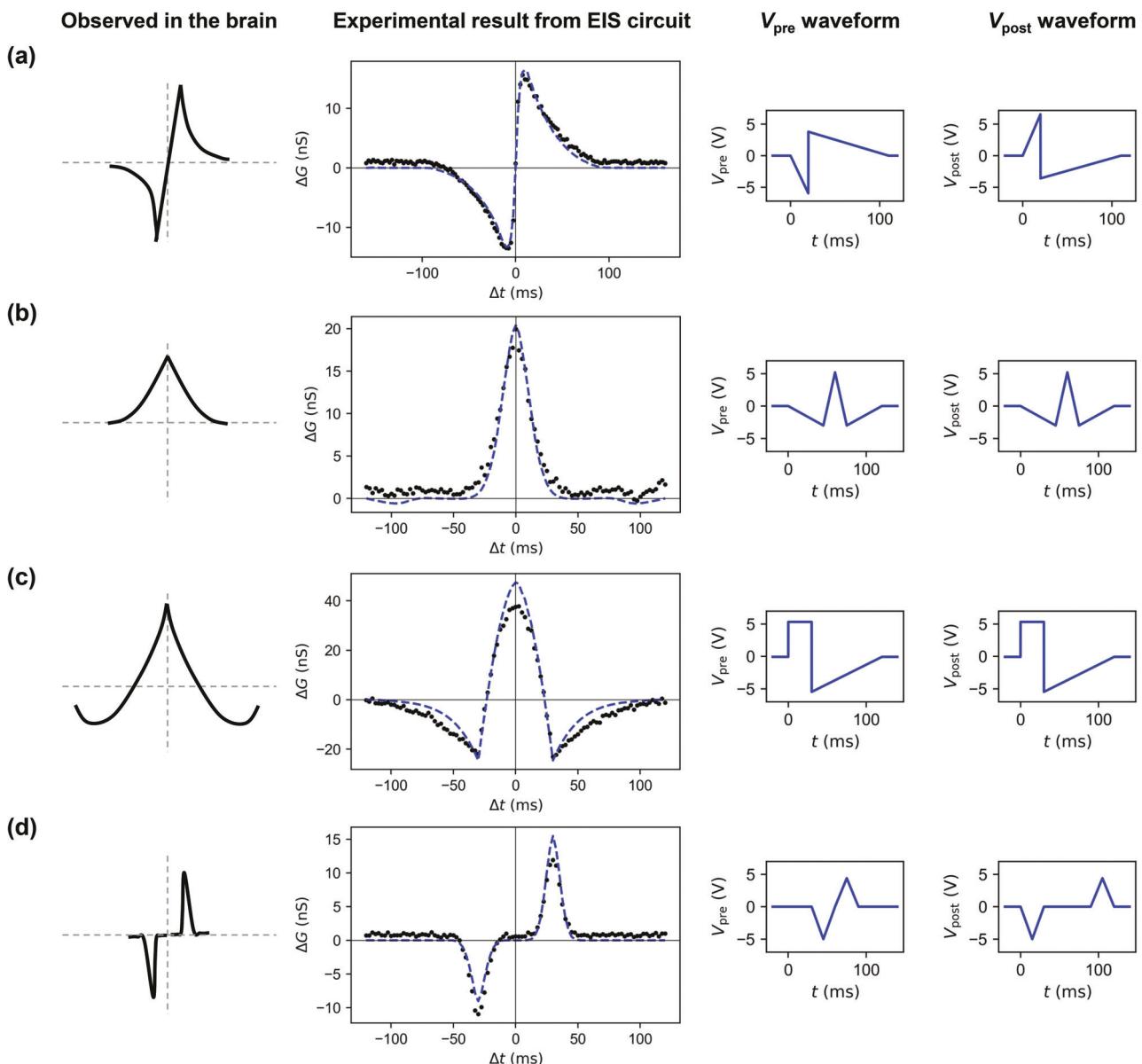

The diversity and versatility of biologically observed STDP forms demand high flexibility on the part of the hardware. We experi-

mentally demonstrate four typical STDP shapes by changing the waveforms of  $V_{\text{pre}}$  and  $V_{\text{post}}$ . A sketch of STDP forms that are observed in the brain, the experimentally measured STDP curves from our EIS circuit, and the  $V_{\text{pre}}$  and  $V_{\text{post}}$  waveforms used for each STDP form, are shown in Figure 4. The demonstrated STDP forms include: the conventional antisymmetric STDP form characterized in hippocampal cultures<sup>[17]</sup> (Figure 4a), long-term potentiation-only STDP form found at CA3–CA1 hippocampal synapses<sup>[53]</sup> (Figure 4b), bidirectional symmetric STDP form found in GABAergic hippocampal synapses<sup>[54]</sup> (Figure 4c) and antisymmetric STDP form with a region of no plasticity in a temporal range near  $\Delta t = 0$ , observed in inhibitory synapses in the entorhinal cortex<sup>[55]</sup> (Figure 4d). The dashed lines in Figure 4a–d show the simulated STDP (using the approach described above), which is in good agreement with the experimentally measured STDP data. The good agreement between the modeled and experimental results suggests that the timing-dependent conductance update is reliable and predictable. In biological neurons, the electrical signals that correspond to spiking events generally take similar forms<sup>[56]</sup> although they can produce different STDP functions. This is in contrast to the very different  $V_{\text{pre}}$  and  $V_{\text{post}}$  waveforms used here to capture different STDP forms. The origin of biological synapses showing different STDP functions from similar electrical signals has been attributed to chemical signals such as calcium concentration transients.<sup>[57]</sup> We cannot capture the details of chemistry at each synapse since the EIS device materials and ions used are the same for each STDP form. Instead, we consider the  $V_{\text{pre}}$  and  $V_{\text{post}}$  used here to represent a convolution of the spiking electrical signal and the local chemistry and molecular pathways that the STDP originates from.<sup>[58]</sup>

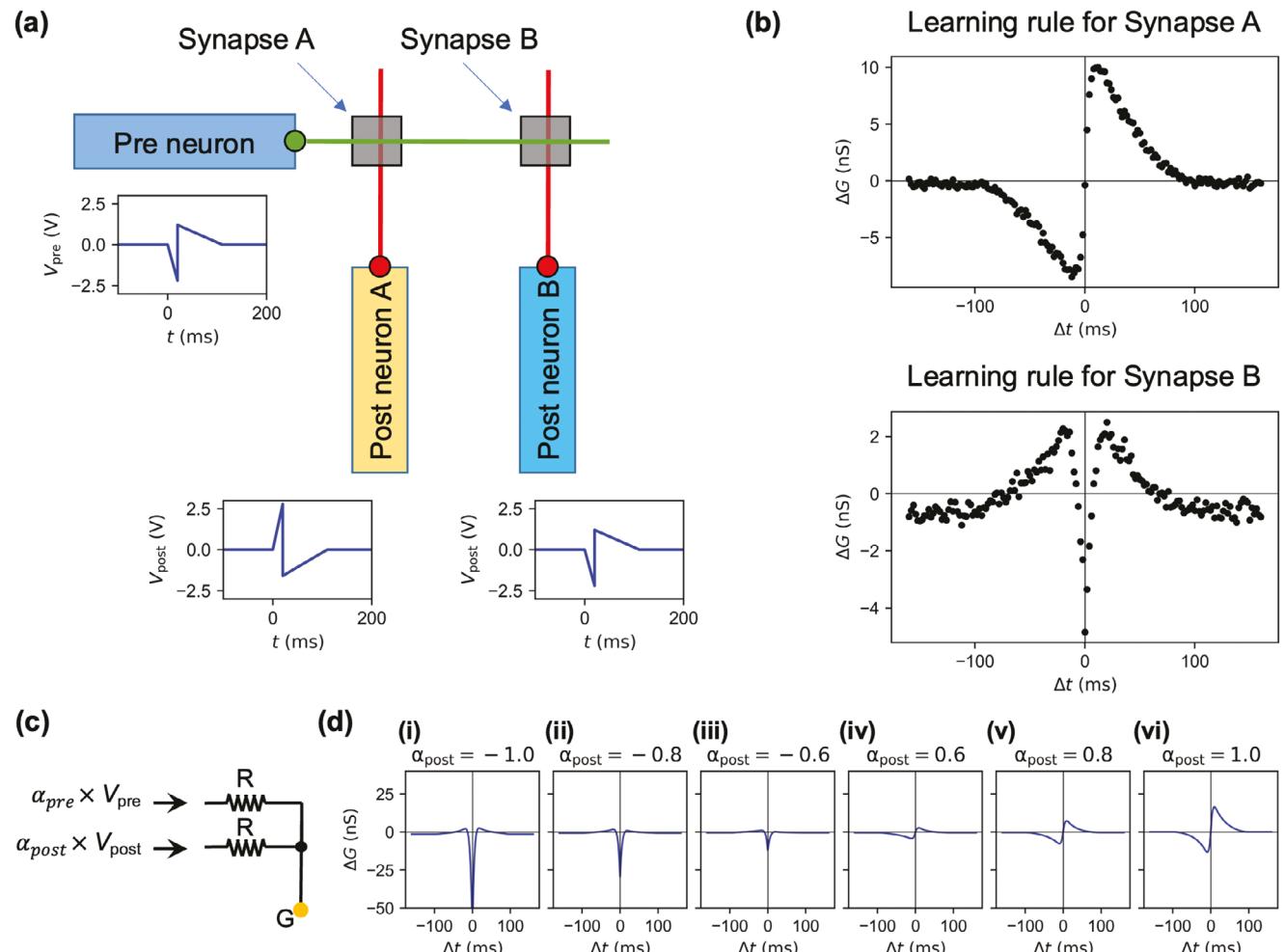

### 2.4. Heterogeneous Learning Rules and Dopamine-Modulated STDP

In biological systems, different STDP forms take place at synapses connecting the same pre-synaptic neurons to different post-synaptic neuron types.<sup>[22,23]</sup> In addition, the STDP form can be altered by neuromodulators including dopamine and acetylcholine.<sup>[59,60]</sup> We show that EIS is conducive to emulating these complex behaviors. We first emulate heterogeneous STDP rules using our EIS circuit (Figure 5a,b). The  $V_{\text{pre}}$  from the pre-synaptic neuron (labeled “Pre neuron”) is shared by two synapses (Synapse A and B), but these synapses receive different  $V_{\text{post}}$  waveforms from different post-synaptic neurons (labeled “Post neuron A” and “Post neuron B”). Therefore, the linear superposition of the  $V_{\text{pre}}$  and  $V_{\text{post}}$  is different in symmetry and shape on the EIS representing Synapse A and Synapse B. As a result, we obtain different STDP forms for the two synapses, shown in Figure 5b. This result closely resembles, for example, the STDP variations observed in synapses at parallel fiber inputs onto fusiform and cartwheel cells.<sup>[22]</sup>

EIS can also be used in the emulation of dopamine-modulated STDP behavior. A potential local circuit approach is exemplified in Figure 5c,d, where the pre- and post-synaptic neuron signals are multiplied by factors  $\alpha_{\text{pre}}$  and  $\alpha_{\text{post}}$ , respectively. These factors emulate the dopamine level of each neuron. Figure 5d shows the simulated STDP forms when  $\alpha_{\text{post}}$  is modulated from +1 to -1

**Figure 4.** Emulating different STDP forms observed in the brain by varying the  $V_{\text{pre}}$  and  $V_{\text{post}}$  waveforms. a) The conventional antisymmetric STDP form is characterized in hippocampal cultures.<sup>[17]</sup> b) Long-term potentiation only STDP form found at CA3–CA1 hippocampal synapses.<sup>[53]</sup> c) Bidirectional symmetric STDP form, found in GABAergic hippocampal synapses.<sup>[54]</sup> d) Antisymmetric STDP form with a region of no plasticity in a temporal range near  $\Delta t = 0$ , observed in inhibitory synapses in the entorhinal cortex.<sup>[55]</sup> For each type, from left to right: the sketch of the targeted STDP shape, the STDP learning curve obtained from experimental (black points) and simulated data (dashed lines), and the  $V_{\text{pre}}$  and  $V_{\text{post}}$  waveforms to obtain the targeted STDP form.

while keeping  $\alpha_{\text{pre}}$  constant as 1. The input  $V_{\text{pre}}$  and  $V_{\text{post}}$  waveforms from Figure 3b are used for the simulation. The results show that the STDP shape changes from the conventional asymmetric with  $\alpha_{\text{post}} = 1$  on the right, to become symmetrical and negative near  $\Delta t = 0$  with  $\alpha_{\text{post}} = -1$  on the left. A second approach is to use a third signal related to the dopamine level that can be superimposed onto the  $V_{\text{pre}}$  and  $V_{\text{post}}$  of each synapse. Simulated examples of dopamine-modulated STDP similar to those in biological observations, are shown in Figures S2 and S3 (Supporting Information).

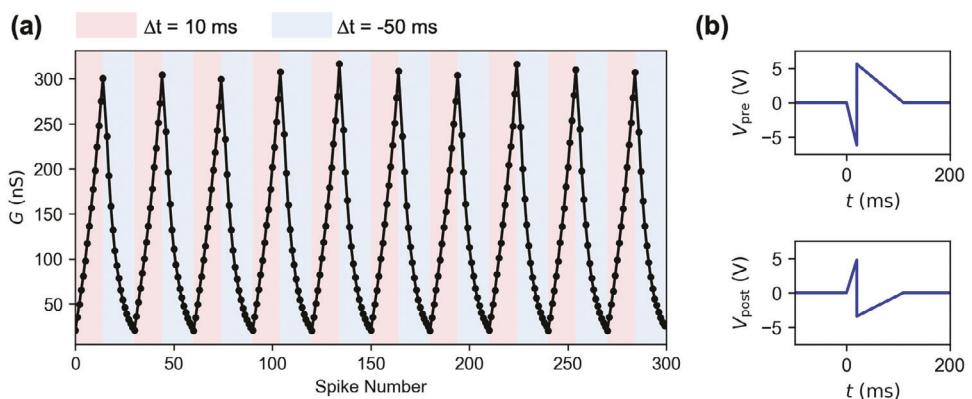

## 2.5. Cumulative Modulation and Consistent Cycling from STDP

Long-term potentiation (LTP) involves a persistent strengthening of synapses depending on recent patterns of activity, while long-term depression (LTD) involves a persistent weakening of the synapse strengths. These mechanisms are key to synaptic plasticity, which is fundamental to learning and memory. To illustrate the cumulative effect of multiple spiking events, it is essential to examine continuous spiking in the context of LTP and LTD. **Figure 6** shows the results of EIS conductance

**Figure 5.** Heterogeneous and evolving STDP. a) Schematic configuration to implement heterogeneous STDP. Different STDP forms are obtained at two EIS synapses (Synapse A and B) connecting the same pre-synaptic neuron (Pre neuron) to two different post-synaptic neurons (Post neuron A, and Post neuron B). The voltage waveforms for the  $V_{\text{pre}}$  and  $V_{\text{post}}$  of the corresponding neurons are shown. b) The resulting STDP forms at the two synapses, A and B. c) Circuit for emulating dopamine-modulated STDP scales the pre- and post-synaptic neuron signals that are combined to serve as  $V_G$  of the EIS. d) Simulated STDP forms as a function of the scaling factor of the post-synaptic neuron ( $\alpha_{\text{post}}$ ).  $\alpha_{\text{post}}$  changes from  $-1$  (i) to  $+1$  (vi), while the scaling factor for the pre-synaptic neuron ( $\alpha_{\text{pre}}$ ) is kept at  $1$ .

**Figure 6.** Cumulative LTP and LTD from continuous spiking events. a) Conductance changes for continuous spiking events with varying  $\Delta t$ . The conductance increases with positive  $\Delta t$  (LTP) and decreases with negative  $\Delta t$  (LTD), showing the cumulative and consistent modulation. The conductance is cycled between low and high states through alternating LTP and LTD events over 10 cycles. b) Waveforms of  $V_{\text{pre}}(t)$  and  $V_{\text{post}}(t)$  to generate LTP and LTD in (a).

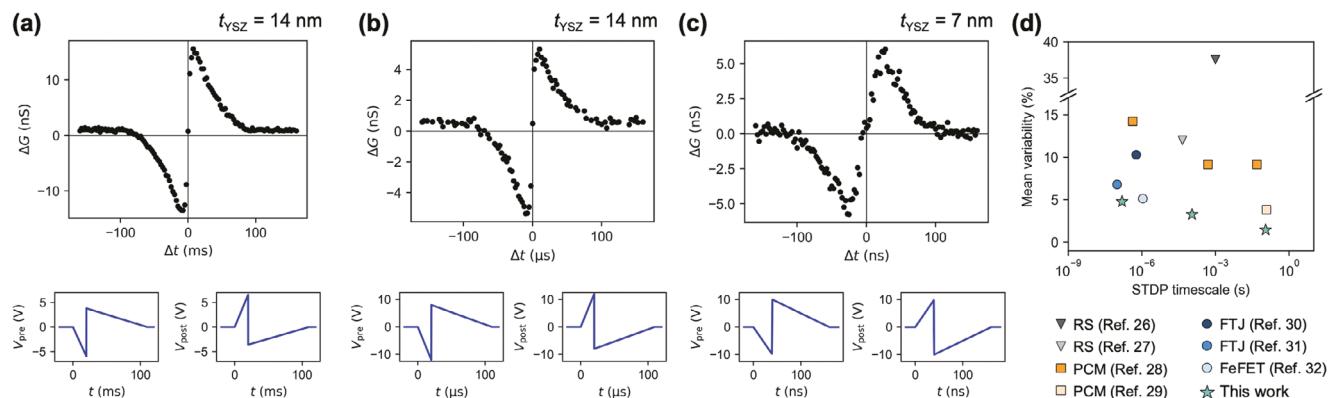

**Figure 7.** Experimentally measured STDP with timescales from milliseconds down to nanoseconds. For each time scale, the  $\Delta G$  versus  $\Delta t$  (top) and the waveforms for  $V_{pre}(t)$  and  $V_{post}(t)$  (bottom) are shown. a) Time scale regime of 100 ms, with a peak voltage level of 6.5 V using a device with a YSZ electrolyte thickness ( $t_{YSZ}$ ) of 14 nm. b) Time scale regime of 100  $\mu$ s, with a peak voltage level of 10 V using a device with  $t_{YSZ} = 14$  nm. c) Time scale regime of 100 ns, with a peak voltage level of 10 V using a device with  $t_{YSZ} = 7$  nm. d) Comparison of variability and programming timescale for synaptic devices implementing STDP, including the EIS devices in this work, and devices based on resistive switching (RS),<sup>[26,27]</sup> phase-change materials (PCM),<sup>[28,29]</sup> ferroelectric tunnel junctions (FTJ),<sup>[30,31]</sup> and ferroelectric field effect transistors (FeFET).<sup>[32]</sup>

modulation from continuous spiking, where the time delay,  $\Delta t$ , controls the direction of the conductance update, and the process was repeated for multiple cycles. Positive  $\Delta t$  spiking events result in a cumulative increase in conductance, while negative  $\Delta t$  events result in a cumulative decrease. The results clearly demonstrate the cumulative effect of multiple spiking events. Furthermore, the conductance can be cycled between low and high states by alternately applying positive (LTP) and negative (LTD) spiking events, with a max/min ratio greater than 10x and excellent consistency. The conductance max/min ratio can be further tuned by using pulses of larger voltage or longer durations, as shown in Figure 2. The versatility and consistency in the cumulative changes indicate that our EIS devices can effectively emulate the long-term plasticity observed in biological synapses, providing a robust foundation for implementing more complex learning rules and functionalities in SNN hardware.

## 2.6. Energy Efficient STDP with Low Variability and Flexible Timescales from Milliseconds to Nanoseconds

The energy consumption, variability and speed of STDP using our EIS circuit are important performance characteristics for implementing SNN hardware. We harness the fast operation speed of EIS devices (down to nanoseconds), low energy consumption and the intrinsic low variability and deterministic nature of the conductance modulation, and demonstrate that the EIS devices can achieve a good combination of the three.

Due to the strong field enhancement of the transport and interfacial reaction kinetics, the timescale of the conductance modulation can be tuned by the voltage amplitudes of the  $V_{pre}$  and  $V_{post}$  waveforms, by the thickness of the electrolyte, and by interface chemistry. As shown in Figure 7a–c, the canonical STDP behavior is implemented experimentally at a timescale ranging from milliseconds to nanoseconds. Millisecond timescales are more relevant for biological systems, and nanosecond timescales enable neuromorphic computing devices that potentially react and learn a million times faster than biological systems.

To assess the variability of the devices, we take the  $\Delta G$  versus  $\Delta t$  data and calculate the mean absolute difference of the measured  $\Delta G$  from the smooth curve fitted to the experimental STDP data. If the device has no variability, the resulting experimental  $\Delta G$  versus  $\Delta t$  should follow a smooth curve, because the  $V_G$  waveform changes smoothly with  $\Delta t$ , and thus we should expect 0 (zero) difference between the measured  $\Delta G$  and the smooth fitted curve. Any non-zero difference is a measure of the variability among each  $V_G$  applied to the device at each  $\Delta t$ . This is akin to the cycle-to-cycle variability of memristive devices.<sup>[61]</sup> This simple metric allows us to compare the variability of our devices to other non-volatile synaptic devices with published STDP results.<sup>[26–32]</sup> We characterize the timescales of the STDP by the length of voltage waveforms applied. A comparison of variability and STDP timescale, including values calculated based on the  $\Delta G$  versus  $\Delta t$  data of our devices in Figure 7a–c and extracted from published results, is shown in Figure 7d. Importantly, we consistently achieve lower variability (<5%) at all timescales with the EIS, compared to other mechanisms (RS, PCM, FTJ, FeFET) reported to emulate STDP in the literature. Additionally, we evaluated the device-to-device variability for STDP implementation (see Section SVI, Supporting Information) and found a variability of  $\approx 6\%$ . This is a remarkably low variability, given that it is quantified at the very low conductance regime (10–100 nS), much lower than the variability of other device types, which never quantified variability at this low of a conductance target range, as we summarize in Table 1 below, and it is well below the target maximum variability value for reliable training of networks.<sup>[52]</sup> We also believe that this variability of EIS devices can be brought down even more by leveraging the state-of-the-art fabrication technologies in the industry, which surpass those at university laboratories.

We estimate the energy consumption of the STDP-performing EIS devices. Since no power is needed at rest when there are no spiking events, the idling power consumption is zero for the synapses. The energy associated with electrochemical proton insertion is estimated to be below 1.0 fJ per spiking event, using data for  $WO_3$  intercalation,<sup>[44]</sup> and by assuming that a peak voltage (10 V) is applied during the whole process. In addition,

**Table 1.** Advantages of utilizing EIS to implement STDP. The comparisons are with respect to RRAM as the most commonly studied device concept, and to other best contender device concepts.

| Characteristics                      | EIS [this work]                                        | Best contender                                           | RRAM                                               |

|--------------------------------------|--------------------------------------------------------|----------------------------------------------------------|----------------------------------------------------|

| Device-to-device variability         | $\approx 6\%$ ( $10 \text{ nS} < G < 100 \text{ nS}$ ) | FeFET, 40% ( $G \approx 2 \mu\text{S}$ ) <sup>[66]</sup> | 80% ( $G \approx 10 \mu\text{S}$ ) <sup>[67]</sup> |

| Programming speed                    | 160 ns                                                 | FTJ, 100 ns <sup>[31]</sup>                              | 1 $\mu\text{s}$ <sup>[68]</sup>                    |

| Energy consumption per spiking event | $< 60 \text{ fJ}$                                      | FTJ, $\approx 2 \text{ pJ}$ <sup>[31]</sup>              | $\approx 7 \text{ pJ}$ <sup>[62]</sup>             |

energy is consumed by the resistors, and the charging and discharging of the capacitance of the EIS gate need to be considered. We calculated the full energy consumption of the circuit by integrating the power during the spiking events (see Section **SVII**, Supporting Information). The calculation shows that the energy consumption of each spike event is  $\approx 27\text{--}54 \text{ fJ}$  for the STDP behavior shown in Figure 7c. We estimated the energy consumption of STDP by other types of resistance switching devices from literature using waveforms and testing protocols extracted from the plots, the estimated energy consumption per spiking event are:  $\approx 7 \text{ pJ}$ ,  $\approx 150 \text{ pJ}$ ,  $\approx 2 \text{ pJ}$ , and  $\approx 0.9 \text{ nJ}$  for RRAM,<sup>[62]</sup> PCM,<sup>[29]</sup> FTJ<sup>[31]</sup> and FeFET,<sup>[32]</sup> respectively. The comparison shows the superior energy efficiency of EIS for implementing STDP.

Major advantages of utilizing EIS to emulate STDP are summarized in Table 1, in comparison to other device concepts that attempted to emulate STDP in the field. The comparison shows that EIS simultaneously provides the least variability and the least energy consumption while being able to operate at a speed regime of nanoseconds. Furthermore, for the protonic EIS focus of our paper, all the functional materials and fabrication processes are CMOS-compatible. The oxides in the devices are deposited with scalable sputtering processes at room temperature, and the Au layers used for electrical contacts can be replaced with CMOS-compatible materials such as W. Pd has been used in CMOS processes as a contact material.<sup>[63]</sup> Additionally, the Pd top gate can be replaced with a  $\text{WO}_3$  layer to form a symmetric device,<sup>[64,66]</sup> eliminating the need for Pd metal. These silicon-compatible materials and processes facilitate integration with peripheral circuits, bringing the device closer toward commercial applications.

### 3. Conclusion

We leverage nonlinear ion dynamics and charge transfer reactions controllably in protonic EIS, to achieve spike timing-dependent weight programming. This allowed us to emulate different bio-realistic STDP functions at timescales tunable from milliseconds down to nanoseconds. The resulting STDP has very low energy consumption and lower variability than other hardware STDP implementations in the field. The EIS circuit also allows for heterogeneous STDP where the synapses from a single neuron can have different learning rules depending on the behavior of the post-synaptic neurons. The strongly nonlinear behavior of conductance modulation is general across EIS devices with different ions, so that a broad range of EIS ions, materials, and devices can be applied to emulate STDP. The approach could enable reliable SNN hardware implementations with high energy efficiency and high throughput.

### 4. Experimental Section

*Device Fabrication:* The EIS devices were fabricated on Si substrates with 90 nm thermal  $\text{SiO}_2$  oxide. First, the channel was patterned using electron-beam lithography with polymethyl methacrylate (PMMA) resist. The  $\text{WO}_3$  channel (10 nm thick) was grown by reactive sputtering using a W target in a gas environment with an  $\text{Ar}:\text{O}_2$  ratio of 9.3:2.7 at 3 mTorr at room temperature, followed by liftoff. The source and drain contacts were patterned and deposited by electron-beam lithography and electron-beam evaporation of Cr 5 nm and Au 35 nm, followed by liftoff. The YSZ solid-state electrolyte (14 or 7 nm thick) was grown by RF sputtering from a YSZ (8 mol.% yttrium oxide doped zirconium oxide) target with  $\text{Ar}:\text{O}_2$  ratio of 15:4 at 3 mTorr at room temperature, followed by photolithography and ion milling. Finally, the Pd reservoir layer was patterned and deposited with electron-beam lithography, and electron-beam evaporation followed by liftoff. The Pd layer becomes  $\text{PdH}_x$  when placed in the hydrogen-forming gas environment during testing.

*Electrical Measurements:* The samples were mounted, wire bonded to a custom-designed PCB, and placed in a gas-enclosed box with feed-throughs for making electrical connections to the devices. The box was filled with hydrogen-forming gas composed of 4%  $\text{H}_2$  and  $\text{N}_2$ . The hydrogen content in  $\text{PdH}_x$  under the gas environment was estimated to be  $x \approx 0.65$  at 20  $^{\circ}\text{C}$ .<sup>[65]</sup> The channel conductance was measured using a semiconductor analyzer (B1500A) with a bias voltage of 0.1 V, and the gate waveforms were generated by a SIGLENT 2000X function generator. Before each STDP measurement, the devices were first initialized to  $\approx 1000 \text{ nS}$  by applying voltage pulses to the gate, to have a consistent initial conductance state in the experiments.

*Conductance Change Calculation from  $V_G$  Waveforms:* The conductance change from a  $V_G$  waveform is calculated using Equation (1). The conductance change rate is interpolated from the experimentally measured data, such as that shown in Figure 2 in this work. To calculate the effect of a voltage waveform from a voltage, the waveform is first numerically sliced into segments of length  $\tau$ , which is chosen so that  $\tau$  is sufficiently small for each waveform. The conductance change from each time segment is then added up to get the final expected conductance change. After the conductance change from all  $\Delta t$  values is calculated, they are multiplied by a common factor: 0.7, 0.5, 0.65, and 0.7 for Figure 4a–d, respectively. The reason for this factor is explained in the manuscript.

### Supporting Information

Supporting Information is available from the Wiley Online Library or from the author.

### Acknowledgements

This work was supported by the MIT Quest for Intelligence program, and by the National Science Foundation (NSF) through the Future of Semiconductors Program under award number 2235462. This work was carried out in part through the use of MIT.nano's fabrication and characterization facilities.

Open access funding enabled and organized by MIT Hybrid 2025.

## Conflict of Interest

The authors declare no conflict of interest.

## Data Availability Statement

The data that support the findings of this study are available from the corresponding author upon reasonable request.

## Keywords

electrochemical ionic synapses, nanoionics, spike-timing-dependent plasticity, spiking neural networks

Received: November 26, 2024

Revised: January 14, 2025

Published online: January 29, 2025

[1] Y. LeCun, Y. Bengio, G. Hinton, *Nature* **2015**, *521*, 436.

[2] D. Silver, J. Schrittwieser, K. Simonyan, I. Antonoglou, A. Huang, A. Guez, T. Hubert, L. Baker, M. Lai, A. Bolton, Y. Chen, T. Lillicrap, F. Hui, L. Sifre, G. van den Driessche, T. Graepel, D. Hassabis, *Nature* **2017**, *550*, 354.

[3] T. Brown, B. Mann, N. Ryder, M. Subbiah, J. D. Kaplan, P. Dhariwal, A. Neelakantan, P. Shyam, G. Sastry, A. Askell, S. Agarwal, A. Herbert-Voss, G. Krueger, T. Henighan, R. Child, A. Ramesh, D. Ziegler, J. Wu, C. Winter, C. Hesse, M. Chen, E. Sigler, M. Litwin, S. Gray, B. Chess, J. Clark, C. Berner, S. McCandlish, A. Radford, I. Sutskever, et al., *Advances in Neural Information Processing Systems*, (Eds: H. Larochelle, M. Ranzato, R. Hadsell, M. F. Balcan, H. Lin), Curran Associates, Inc., New York, **2020**, pp. 1877–1901.

[4] W. Zhang, B. Gao, J. Tang, P. Yao, S. Yu, M.-F. Chang, H.-J. Yoo, H. Qian, H. Wu, *Nat. Electron.* **2020**, *3*, 371.

[5] Semiconductor Research Corporation, *Decadal Plan for Semiconductors*, Semiconductor Research Corporation, Durham, NC, USA **2021**.

[6] A. Mehonic, A. J. Kenyon, *Nature* **2022**, *604*, 255.

[7] V. Balasubramanian, *Proc. Natl. Acad. Sci. U.S.A.* **2021**, *118*, 2107022118.

[8] W. Maass, *Neural Networks* **1997**, *10*, 1659.

[9] K. Roy, A. Jaiswal, P. Panda, *Nature* **2019**, *575*, 607.

[10] N. Rathi, I. Chakraborty, A. Kosta, A. Sengupta, A. Ankit, P. Panda, K. Roy, *ACM Comput. Surv.* **2023**, *55*, 1.

[11] X. Liang, Y. Luo, Y. Pei, M. Wang, C. Liu, *Nat. Electron.* **2022**, *5*, 859.

[12] F. Zhou, Y. Chai, *Nat. Electron.* **2020**, *3*, 664.

[13] P. A. Merolla, J. V. Arthur, R. Alvarez-Icaza, A. S. Cassidy, J. Sawada, F. Akopyan, B. L. Jackson, N. Imam, C. Guo, Y. Nakamura, B. Brezzo, I. Vo, S. K. Esser, R. Appuswamy, B. Taba, A. Amir, M. D. Flickner, W. P. Risk, R. Manohar, D. S. Modha, *Science* **2014**, *345*, 668.

[14] T. Sarkar, K. Lieberth, A. Pavlou, T. Frank, V. Mailaender, I. McCulloch, P. W. M. Blom, F. Torricelli, P. Gkoupidenis, *Nat. Electron.* **2022**, *5*, 774.

[15] P. C. Harikesh, C.-Y. Yang, H.-Y. Wu, S. Zhang, M. J. Donahue, A. S. Caravaca, J.-D. Huang, P. S. Olofsson, M. Berggren, D. Tu, S. Fabiano, *Nat. Mater.* **2023**, *22*, 242.

[16] P. C. Harikesh, C.-Y. Yang, D. Tu, J. Y. Gerasimov, A. M. Dar, A. Armada-Moreira, M. Massetti, R. Kroon, D. Bliman, R. Olsson, E. Stavrinidou, M. Berggren, S. Fabiano, *Nat. Commun.* **2022**, *13*, 901.

[17] G. Bi, M. Poo, *J. Neurosci.* **1998**, *18*, 10464.

[18] N. Caporale, Y. Dan, *Annu. Rev. Neurosci.* **2008**, *31*, 25.

[19] M. Prezioso, M. R. Mahmoodi, F. M. Bayat, H. Nili, H. Kim, A. Vincent, D. B. Strukov, *Nat. Commun.* **2018**, *9*, 5311.

[20] S. Song, K. D. Miller, L. F. Abbott, *Nat. Neurosci.* **2000**, *3*, 919.

[21] P. U. Diehl, M. Cook, *Front. Comput. Neurosci.* **2015**, *9*, 99.

[22] T. Tzounopoulos, Y. Kim, D. Oertel, L. O. Trussell, *Nat. Neurosci.* **2004**, *7*, 719.

[23] E. Fino, L. Venance, *Neuropharmacology* **2011**, *60*, 780.

[24] T. Ohno, T. Hasegawa, T. Tsuruoka, K. Terabe, J. K. Gimzewski, M. Aono, *Nat. Mater.* **2011**, *10*, 591.

[25] W. Wang, G. Pedretti, V. Milo, R. Carboni, A. Calderoni, N. Ramaswamy, A. S. Spinelli, D. Ielmini, *Sci. Adv.* **2018**, *4*, eaat4752.

[26] Z. Wang, S. Joshi, S. E. Savel'ev, H. Jiang, R. Midya, P. Lin, M. Hu, N. Ge, J. P. Strachan, Z. Li, Q. Wu, M. Barnell, G.-L. Li, H. L. Xin, R. S. Williams, Q. Xia, J. J. Yang, *Nat. Mater.* **2017**, *16*, 101.

[27] Y. Li, Y. Zhong, J. Zhang, L. Xu, Q. Wang, H. Sun, H. Tong, X. Cheng, X. Miao, *Sci. Rep.* **2014**, *4*, 4906.

[28] Y. Li, Y. Zhong, L. Xu, J. Zhang, X. Xu, H. Sun, X. Miao, *Sci. Rep.* **2013**, *3*, 1619.

[29] D. Kuzum, R. G. D. Jeyasingh, B. Lee, H.-S. P. Wong, *Nano Lett.* **2012**, *12*, 2179.

[30] S. Boyn, J. Grollier, G. Lecerf, B. Xu, N. Locatelli, S. Fusil, S. Girod, C. Carrétéro, K. Garcia, S. Xavier, J. Tomas, L. Bellaïche, M. Bibes, A. Barthélémy, S. Saïghi, V. Garcia, *Nat. Commun.* **2017**, *8*, 14736.

[31] S. Majumdar, H. Tan, Q. H. Qin, S. Van Dijken, *Adv. Electron. Mater.* **2019**, *5*, 1800795.

[32] Y. Peng, G. Zhang, W. Xiao, F. Liu, Y. Liu, G. Wang, S. Wang, X. Yu, G. Han, Y. Hao, *IEEE J. Electron Devices Soc.* **2021**, *9*, 1145.

[33] Z. Wang, H. Wu, G. W. Burr, C. S. Hwang, K. L. Wang, Q. Xia, J. J. Yang, *Nat. Rev. Mater.* **2020**, *5*, 173.

[34] J. Li, B. Luan, C. Lam, presented at 2012 IEEE Int. Reliability Physics Symposium (IRPS), IEEE, Anaheim, CA, USA **2012**.

[35] N. Zagni, F. M. Puglisi, P. Pavan, M. A. Alam, *Proc. IEEE* **2023**, *111*, 158.

[36] S. Choi, S. H. Tan, Z. Li, Y. Kim, C. Choi, P.-Y. Chen, H. Yeon, S. Yu, J. Kim, *Nat. Mater.* **2018**, *17*, 335.

[37] M. Rao, H. Tang, J. Wu, W. Song, M. Zhang, W. Yin, Y. Zhuo, F. Kiani, B. Chen, X. Jiang, H. Liu, H.-Y. Chen, R. Midya, F. Ye, H. Jiang, Z. Wang, M. Wu, M. Hu, H. Wang, Q. Xia, N. Ge, J. Li, J. J. Yang, *Nature* **2023**, *615*, 823.

[38] D. Joksas, P. Freitas, Z. Chai, W. H. Ng, M. Buckwell, C. Li, W. D. Zhang, Q. Xia, A. J. Kenyon, A. Mehonic, *Nat. Commun.* **2020**, *11*, 4273.

[39] D. Querlioz, O. Bichler, C. Gamrat, in *The 2011 Int. Joint Conf. on Neural Networks*, IEEE, New York **2011**.

[40] E. J. Fuller, F. E. Gabaly, F. Léonard, S. Agarwal, S. J. Plimpton, R. B. Jacobs-Gedrim, C. D. James, M. J. Marinella, A. A. Talin, *Adv. Mater.* **2017**, *29*, 1604310.

[41] J. Tang, D. Bishop, S. Kim, M. Copel, T. Gokmen, T. Todorov, S. Shin, K. Lee, P. Solomon, K. Chan, W. Haensch, J. Rozen, in *2018 IEEE Int. Electron Devices Meeting (IEDM)*, IEEE, New York **2018**.

[42] S. Kim, T. Todorov, M. Onen, T. Gokmen, D. Bishop, P. Solomon, K.-T. Lee, M. Copel, D. B. Farmer, J. A. Ott, T. Ando, H. Miyazoe, V. Narayanan, J. Rozen, in *2019 IEEE Int. Electron Devices Meeting (IEDM)*, IEEE, New York **2019**.

[43] Y. Van De Burgt, E. Lubberman, E. J. Fuller, S. T. Keene, G. C. Faria, S. Agarwal, M. J. Marinella, A. Alec Talin, A. Salleo, *Nat. Mater.* **2017**, *16*, 414.

[44] X. Yao, K. Klyukin, W. Lu, M. Onen, S. Ryu, D. Kim, N. Emond, I. Waluyo, A. Hunt, J. A. del Alamo, J. Li, B. Yildiz, *Nat. Commun.* **2020**, *11*, 3134.

[45] M. Onen, N. Emond, B. Wang, D. Zhang, F. M. Ross, J. Li, B. Yildiz, J. A. del Alamo, *Science* **2022**, *377*, 539.

[46] J. Cui, F. An, J. Qian, Y. Wu, L. L. Sloan, S. Pidaparthi, J.-M. Zuo, Q. Cao, *Nat. Electron.* **2023**, *6*, 292.

[47] M. Huang, M. Schwacke, M. Onen, J. del Alamo, J. Li, B. Yildiz, *Adv. Mater.* **2023**, *35*, 2205169.

[48] M. Onen, N. Emond, J. Li, B. Yildiz, J. A. del Alamo, *Nano Lett.* **2021**, *21*, 6111.

[49] B. Scherrer, M. V. F. Schlupp, D. Stender, J. Martynczuk, J. G. Grolig, H. Ma, P. Kocher, T. Lippert, M. Prestat, L. J. Gauckler, *Adv. Funct. Mater.* **2013**, *23*, 1957.

[50] N. F. Mott, E. A. Davis, *Electronic Processes in Non-Crystalline Materials*, Clarendon Press, Oxford, **2012**.

[51] A. J. Bard, L. R. Faulkner, *Electrochemical Methods: Fundamentals and Applications*, Wiley, New York, **2001**.

[52] T. Gokmen, Y. Vlasov, *Front. Neurosci.* **2016**, *10*, 333.

[53] G. M. Wittenberg, S. S.-H. Wang, *J. Neurosci.* **2006**, *26*, 6610.

[54] M. A. Woodin, K. Ganguly, M. Poo, *Neuron* **2003**, *39*, 807.

[55] J. S. Haas, T. Nowotny, H. D. I. Abarbanel, *J. Neurophysiol.* **2006**, *96*, 3305.

[56] A. L. Hodgkin, A. F. Huxley, *J. Physiol.* **1952**, *117*, 500.

[57] T. Nevian, B. Sakmann, *J. Neurosci.* **2006**, *26*, 11001.

[58] D. E. Feldman, *Neuron* **2012**, *75*, 556.

[59] V. Pawlak, *Front. Syn. Neurosci.* **2010**, *2*, 146.

[60] K. N. Gurney, M. D. Humphries, P. Redgrave, *PLoS Biol.* **2015**, *13*, 1002034.

[61] *Resistive Switching: From Fundamentals of Nanoionic Redox Processes to Memristive Device Applications*, (Eds: D. Ielmini, R. Waser), Wiley-VCH Verlag GmbH & Co. KGaA, Weinheim, **2016**.

[62] I.-T. Wang, Y.-C. Lin, Y.-F. Wang, C.-W. Hsu, T.-H. Hou, in *2014 IEEE International Electron Devices Meeting*, IEEE, San Francisco, CA, USA **2014**, pp. 28.5.1–28.5.4.

[63] S. Jain, J. Bowers, M. Sysak, J. Heck, R. Feldesh, R. Jones, Y. Shetrit, M. Geva, (CMOS-Compatible Gold-Free Contacts) US9252118B2 **2016**.

[64] M. Schwacke, P. Źguns, J. Del Alamo, J. Li, B. Yildiz, *Adv. Electron. Mater.* **2024**, *10*, 2300577.

[65] F. D. Manchester, A. San-Martin, J. M. Pitre, *J. Phase Equilib.* **1994**, *15*, 62.

[66] S. De, A. Baig, B.-H. Qiu, F. Müller, H.-H. Le, M. Lederer, T. Kämpfe, T. Ali, P.-J. Sung, C.-J. Su, Y.-J. Lee, D. D. Lu, *Front. Nanotechnol.* **2022**, *3*, 826232.

[67] N. Gong, M. J. Rasch, S.-C. Seo, A. Gasasira, P. Solomon, V. Bragaglia, S. Consiglio, H. Higuchi, C. Park, K. Brew, P. Jamison, C. Catano, I. Saraf, F. F. Athena, C. Silvestre, X. Liu, B. Khan, N. Jain, S. McDermott, R. Johnson, I. Estrada-Raygoza, J. Li, T. Gokmen, N. Li, R. Pujari, F. Carta, H. Miyazoe, M. M. Frank, D. Koty, Q. Yang, et al., in *2022 International Electron Devices Meeting (IEDM)*, IEEE, New York **2022**, pp. 33.7.1–33.7.4.

[68] R. Li, P. Huang, Y. Feng, Z. Zhou, X. Wang, W. Shen, X. Ding, L. Liu, X. Liu, J. Kang, in *2020 IEEE Silicon Nanoelectronics Workshop (SNW)*, IEEE, New York **2020**, pp. 75–76.