# A CMOS 49–63-GHz Phase-Locked Stepped-Chirp FMCW Radar Transceiver

Xuyang Liu<sup>ID</sup>, *Graduate Student Member, IEEE*,

Md. Hedayatullah Maktoomi<sup>ID</sup>, *Graduate Student Member, IEEE*,

Mahdi Alesheikh<sup>ID</sup>, *Graduate Student Member, IEEE*, Payam Heydari, *Fellow, IEEE*,

and Hamidreza Aghasi<sup>ID</sup>, *Senior Member, IEEE*

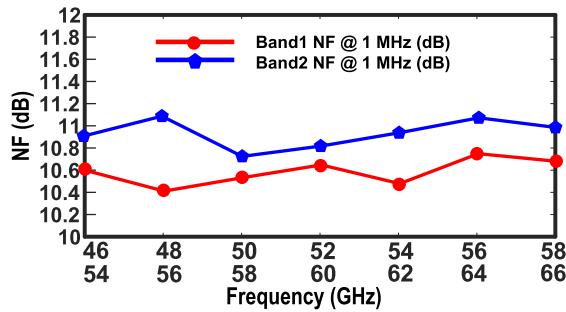

**Abstract**—A 49–63 GHz phase-locked stepped chirp frequency modulated continuous wave (FMCW) radar transceiver (TRX) in a 22-nm fully depleted silicon on insulator (FD-SOI) process is presented. To achieve the desired large bandwidth (BW), the frequency range is split into two sub-chirps, each controlled by distinct phase-locked loops (PLLs)—a reference PLL and a mixing PLL. This novel dual-PLL architecture facilitates a wide effective BW without the need for designing ultra-wideband TRX blocks. This radar TRX supports both free-running and phase-locked operations. The CMOS chip is co-integrated with linear arrays of series-fed patch antennas for each frequency band. The measured effective isotropic radiated power (EIRP) is 9 dBm with a phase noise (PN) of  $-101.09$  dBc/Hz at 1 MHz offset at 56 GHz. The receiver (RX) achieves a 10-dB noise figure (NF). The radar field measurement demonstrates a maximum distance of 5 m and a range resolution of 1.4 cm.

**Index Terms**—60 GHz, frequency modulated continuous wave (FMCW), phase-locked loop (PLL), radar, range resolution, stepped chirp.

## I. INTRODUCTION

WITH the rapid evolution of advanced driver assistance systems (ADASs) [1], [2], Internet of Things (IoT) [3], smart industry [4], [5], and healthcare, the need for frequency-modulated continuous-wave (FMCW) radar in both the unlicensed 60- and 77-GHz band is growing substantially [6], [7], [8]. Emerging applications such as IoT-based local-area sensing call for large-scale deployment of power-efficient, miniaturized radar nodes [9], [10]. These sensors must cover ranges from 10 cm to 50 m and provide fine detection capability characterized by range resolutions [11]. The range of coverage depends on the transmitted power which should be sufficiently high to overcome the propagation loss of the medium (e.g., air) and achieve acceptable receiver (RX) sensitivity, yet remain within the bounds of existing

Received 9 October 2024; revised 9 January 2025 and 16 March 2025; accepted 27 March 2025. This article was approved by Associate Editor Minoru Fujishima. This work was supported by the National Science Foundation (NSF) under Award 2233783. (Corresponding authors: Xuyang Liu; Hamidreza Aghasi.)

Xuyang Liu, Md. Hedayatullah Maktoomi, Mahdi Alesheikh, and Hamidreza Aghasi are with the High-Speed Integrated Electronics (HIE) Laboratory, UC Irvine, Irvine, CA 92697 USA (e-mail: xuyanl3@uci.edu; haghasi@uci.edu).

Payam Heydari is with the Nanoscale Communication Integrated Circuits (NCIC) Laboratory, UC Irvine, Irvine, CA 92697 USA.

Color versions of one or more figures in this article are available at <https://doi.org/10.1109/JSSC.2025.3556649>.

Digital Object Identifier 10.1109/JSSC.2025.3556649

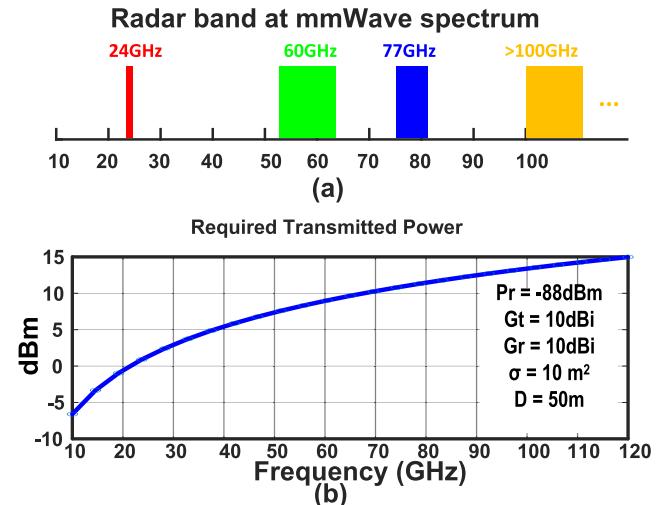

Fig. 1. (a) Radar frequency band at the mm-wave spectrum and (b) received power at 50 m distance versus frequency based on radar Friis equation.

radiation/communication regulations. In addition, these sensors must operate at high frequencies (i.e., small wavelengths) and across broad bandwidths (BWs), as both BW and frequency of operation contribute to resolution.

Existing commercial 24-/60-/77-GHz FMCW radar [12], [13], [14], [15], [16] exhibit relatively narrow BWs [see Fig. 1(a)], which inherently limits the range resolution. While operating above 100 GHz [17] facilitates broader BWs for a smaller fractional BW, the power generation efficiency and RX sensitivity are severely degraded, thereby limiting the range. As shown in Fig. 1(b), for an RX sensitivity of  $-88$  dBm, transmitter (TX) and RX antenna gains of 10 dBi and target with a radar cross section ( $\sigma$ ) of  $10$  m<sup>2</sup> located 50 m away, the required transmitted power to produce detectable signals on the RX side based on radar's Friis equation for frequencies above 100 GHz should be higher than 13 dBm [18], [19]. Generating such levels of power in light of severely limited output power available from an MOS device beyond 100 GHz is challenging [20]. Another issue that becomes increasingly more significant at high frequencies is the signal transfer from the TRX chip to the high-gain antenna. In particular, the RF signal transfer to the package antennas encounters increased insertion loss and group delay variation at higher frequencies due to skin effect [21], chip-to-package parasitic impedances [22], and the interconnect dimensions becoming

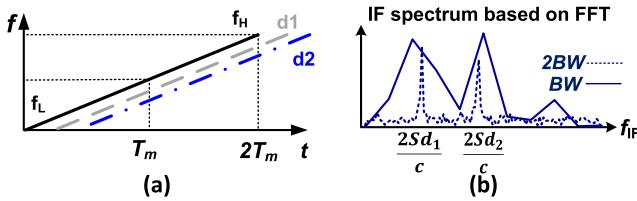

Fig. 2. Relationship between range resolution and synthetic BW. (a) FMCW chirp profile in the time domain. (b) Range resolution comparison using FFT for bandwidths of BW and 2BW.

comparable to the wavelength. For example, a 500- $\mu$ m wire-bond behaves as a  $\lambda/4$  transmission line at 150 GHz.

Rather than increasing the operating frequency to obtain a broader absolute BW, a potential solution involves deploying multiple lower frequency radars, each covering adjacent frequency sub-bands, and combining them to achieve the desired overall BW. However, this approach mandates precise phase and frequency synchronization across the deployed bands, which poses significant challenges and often results in high power consumption. This work presents a stepped chirp-based FMCW radar transceiver (TRX) which consists of two sub-bands, with each covering 7-GHz BW. By splitting the BW into two frequency bands, the wideband design challenges associated with critical components such as the power amplifier (PA), low noise amplifier (LNA), and voltage-controlled oscillator (VCO) are largely mitigated. More importantly, the two bands are phase and frequency synchronized using a low-power, scalable on-chip mechanism inspired by type-II analog phase-locked loops (PLLs), which is essential for the radar's high-resolution performance. The radar TRX chip is co-integrated with series-fed patch antenna arrays through a chip-to-package impedance matching network.

The rest of the article is organized as follows. Section II explains the necessity of widening the BW to enhance range resolution and the operation of the frequency-segmented phase-locked TRX architecture. Section III introduces the design of critical circuit blocks and chip-to-board and board-to-antenna interface design. Section IV demonstrates the TRX major performance measurements and the radar operation verification. Section V concludes the article.

## II. SYSTEM ARCHITECTURE OF STEPPED CHIRP RADAR

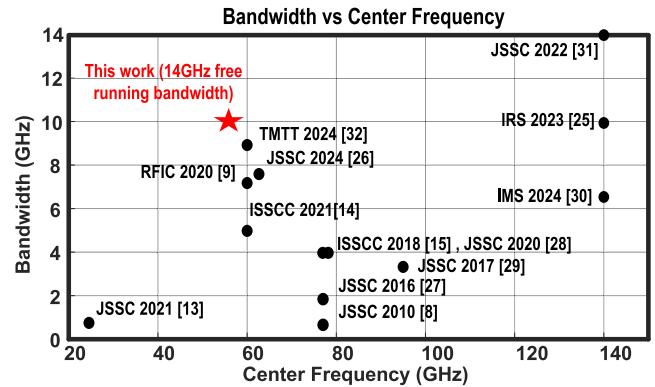

Range resolution is a key radar performance metric that defines the minimum distance between two closely spaced targets that can be distinctly identified by the radar in a single chirp interval [23]. The FMCW radar range resolution (RR) is inversely proportional to the chirp BW [11], [24], as illustrated in Fig. 2, i.e.,  $RR = c/2BW$  where  $c$  is the speed of light. Therefore, to improve range resolution, an increase in chirp BW is required. A larger BW can: 1) yield a greater frequency separation ( $\Delta f$ ) for the same distance resolution ( $\Delta d$ ) and 2) allow the same  $\Delta f$  but with a longer observation window for the same  $\Delta d$ . A snapshot of state-of-the-art phase-locked FMCW radars covering 20–140 GHz including this work is summarized in Fig. 3 [25], [26], [27], [28], [29], [30], [31], [32]. Given the constraints on the fractional BW of chirp generation circuits, such as VCOs utilizing varactor tuning, the majority of previous designs operating below 100 GHz have been limited to sub-10-GHz chirp BW. This highlights

Fig. 3. BW versus center frequency.

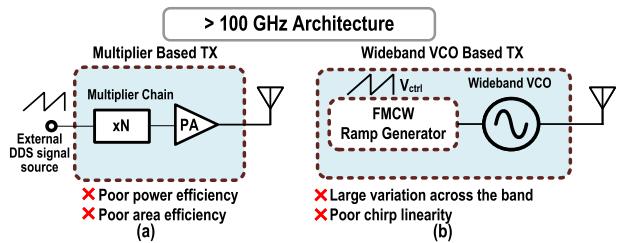

Fig. 4. Above 100-GHz wideband radar TX utilizing (a) multiplier chain and (b) VCO.

the need for innovative frequency synthesis architectures to overcome these BW challenges.

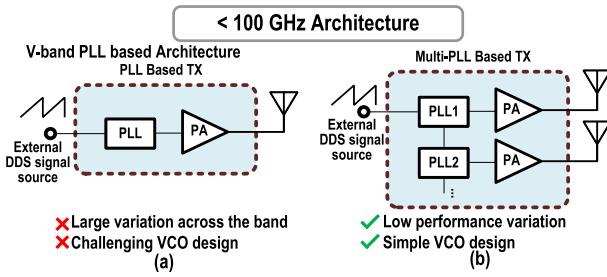

### A. Frequency Synthesis Planning

The present implementations of mm-wave radar are mostly centered around two predominant approaches for signal synthesis. To achieve greater BW for range resolution, single-chirp implementations often target operating frequencies above 100 GHz, where radar systems encounter several challenges. As depicted in Fig. 4(a), the first method employs an external FMCW signal generated by a direct digital frequency synthesizer (DDFS), which is subsequently passed through a chain of multipliers and a PA to boost the signal's power. This method is inefficient in terms of both area and power consumption due to two main factors: 1) the requirement for additional multiplier stages as the frequency increases owing to challenges in achieving high-frequency DDFS outputs [31] and 2) the reduced gain and efficiency of transistors within the PA as frequency rises. Alternatively, the second method uses wideband VCOs [see Fig. 4(b)], while mitigating some of the issues mentioned in Fig. 4(a). Nonetheless, this approach is not without its drawbacks, including the diminished quality factor of passive components and the augmented intrinsic noise of active devices at higher frequencies. This in turn degrades the oscillator's phase noise (PN), adversely affecting the signal-to-noise ratio (SNR) of the intermediate frequency (IF) signal. In addition, as shown in Fig. 4(b), calibration of the ramp generator to linearize the chirp for VCO-based FMCW radar is necessary to offset the impact of suboptimal  $K_{VCO}$  on the chirp's linearity [33].

Addressing the limitations and shortcomings of above 100-GHz configurations in Fig. 4, we explore PLL-based designs that can span below 100 GHz, e.g., a 49–63-GHz frequency

Fig. 5. Below 100-GHz wideband radar TX utilizing (a) one PLL and (b) coupled PLL.

range. Fig. 5 demonstrates two distinct configurations: one that employs a single PLL with wide BW coverage ( $\geq 10$  GHz), and another that integrates several sub-band PLLs. In Fig. 5(a), it is necessary for the VCO's fractional BW to be accordingly increased, a challenge at mm-wave frequencies predominantly due to the prevailing effect of device parasitics. In Fig. 5(b), segmentation of the frequency band into smaller sub-bands significantly mitigates the design challenges of wideband TRX blocks, such as the VCO, PA, and LNA. This approach lowers PA output power variations, improves the VCO linear tuning range, and reduces the oscillator PN.

It is noted that the design challenge of critical mm-wavefront-end blocks increases substantially with larger BWs mainly due to the limitations on wideband matching. On the radiation side, planar antenna configurations such as series-fed patch antennas, which are currently popular for FMCW radars due to their narrow field-of-view (FoV), can hardly achieve a radiation BW above 10 GHz. This is why despite achieving a total impressive BW of 9 GHz in [32], the design challenges of ensuring all subblocks operate across the same BW result in suboptimal PN and output power compared to [6].

In light of these design challenges, we propose dividing the entire BW into multiple smaller sub-bands, simplifying the design of critical building blocks, such as antennas, for each band. An architecture based on coupled PLLs, shown in Fig. 5(b), provides an effective means of extending the BW while preserving a uniform narrowband chirp profile across various sub-bands. Nevertheless, this approach demands novel synthesizer solutions to reduce power consumption, particularly as the number of PLLs increases.

### B. Stepped Chirp TRX Architecture

One solution to divide the BW into smaller sub-bands is the stepped chirp architecture [34]. A stepped-chirp radar sensor can achieve a maximum range resolution of  $c/(2\text{BW}_T)$ , where  $\text{BW}_T$  is the total synthetic BW comprised of  $N$  subbands with each covering a BW of  $\text{BW} = \text{BW}_T/N$ . The range resolution associated with  $\text{BW}_T$  is only obtained if the slopes of chirps corresponding with the sub-bands are identical [35]. This requirement is extremely challenging to meet in practice if the stepped chirps are realized by free-running VCOs, as there is no feedback loop to force the constant frequency difference.

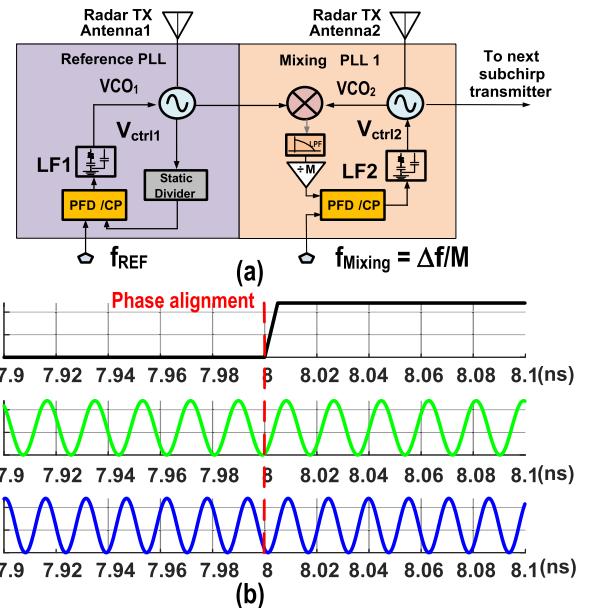

To resolve unwanted variations of free-running oscillators while significantly reducing the power consumption of the radar, we propose a new phase-locked stepped-chirp

Fig. 6. (a) Simplified TX block diagram and (b) timing diagram of VCO1 and VCO2 with respect to mixing PLL input reference.

generation structure. On the TX side, shown in Fig. 6(a),  $N$  sub-bands with frequency coverage of BW and spacing of  $\Delta f$  are realized using a circuit comprising one reference PLL and  $N - 1$  mixing PLLs. In this structure, the outputs of each pair of adjacent VCOs are fed to a mixer inside a mixing PLL. Under the locking condition, the output frequency of the  $i$ th mixing PLL,  $f_{\text{mix}_i}$ , is locked to the mixer's difference frequency component, i.e.,  $f_{\text{mix}_i} = |f_{\text{osc}_{i+1}} - f_{\text{osc}_i}|$ . By placing the mixer inside a PLL [36], the mixing spurs are substantially constrained. Following the phase-locking acquisition, the TX frequency synthesizer in Fig. 6(a) ensures that the frequency difference between two adjacent PLLs is locked to  $\Delta f$ , while also promising the synchronized sweep of their corresponding chirps with respect to the chirp generated by the reference PLL. The linearized loop analysis of a type-II PLL comprising mixers is detailed in [37] and for brevity is not repeated here. The other advantage of this stepped-chirp architecture is the deterministic phase relationship between two adjacent VCOs, as shown in Fig. 6(b), which facilitates the baseband signal stitching, discussed later.

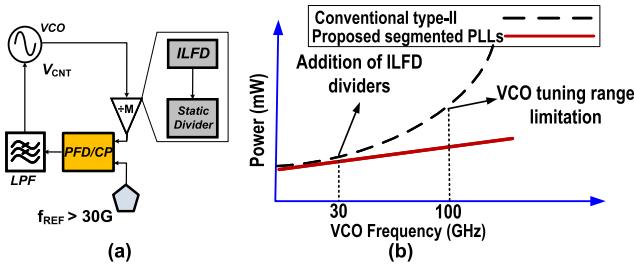

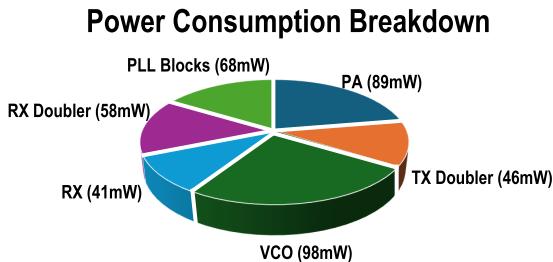

The coupled mixing PLLs offer significant power saving advantage compared to conventional type-II PLLs for the following reason: referring to power consumption breakdown in Fig. 7, an mm-wave type-II PLL consumes a considerable amount of power, as the VCO and divider chain's power consumption becomes increasingly significant with higher frequency/loop-division-ratios. The output frequency of the mixer inside the mixing PLL of the proposed architecture is set to  $\Delta f = 7$  GHz rather than the actual sub-band frequency, thereby significantly reducing the loop output frequency to a range manageable by digital dividers. This allows the removal of power-hungry frequency divider chains (e.g., injection-locked frequency dividers (ILFDs) [38] and current-mode logic (CML) dividers [39]) and replacing them with only a low-power mixer inside the loop. Owing to the use of mixing

Fig. 7. (a) Conventional type-II PLL architecture with ILFD at above 30 GHz and (b) power saving by adopting mixing PLLs for frequency above 30 GHz instead of type-II PLLs.

Fig. 8. (a) Proposed stepped-band RX, (b) conventional single-chirp FMCW signal, (c) stepped chirp FMCW signal, (d) stitched baseband signals in the time domain with phase alignment, and (e) resultant combined IF signal.

PLLs, adding more sub-bands to this design leads to a linear increase in power consumption as opposed to the super-linear growth characteristic of type-II PLLs [see Fig. 7(b)].

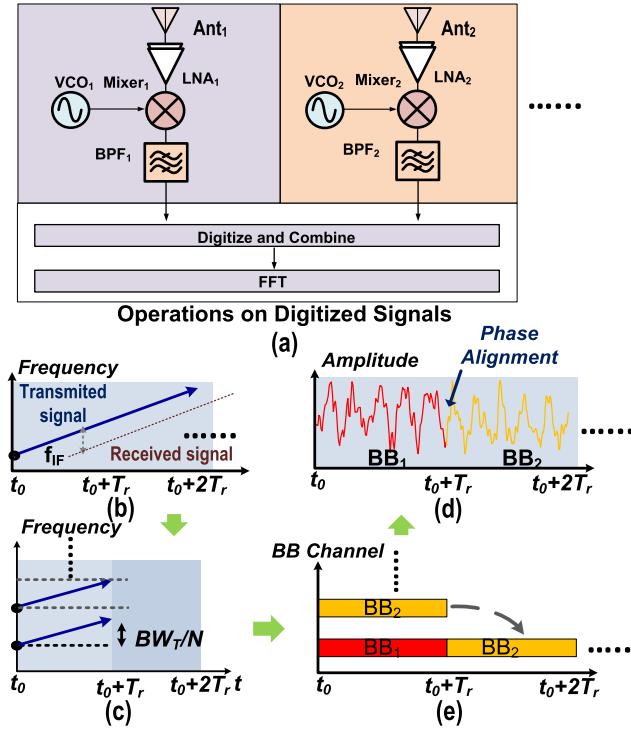

### C. IF Processing and Resolution Enhancement

The proposed RX architecture of the stepped-chirp radar TRX is shown in Fig. 8(a), where the LNA and mixer operate within the BW of each sub-band ( $BW = BW_T/N$ ). Therefore, the integrated noise of each sub-band RX is almost  $10\log(N)$  smaller than that of the conventional RX ( $(N-1)\Delta f + BW_T$ ). This smaller BW leads to higher RX sensitivity, which allows for longer ranges of operation. On the other hand, the design of wideband linear LNAs is challenging due to the variations of passive components with wider BW [40]. This issue is resolved in the proposed RX by operating the LNA across the BW of  $BW = BW_T/N$ . Finally, a lower sub-band BW, results in higher achievable SNR than conventional FMCW RXs, thereby relaxing the analog-to-digital converter (ADC)

resolution and power consumption, ( $P_{ADC} \propto f_{CLK} \times 2^{n_{bits}}$ ) [41].

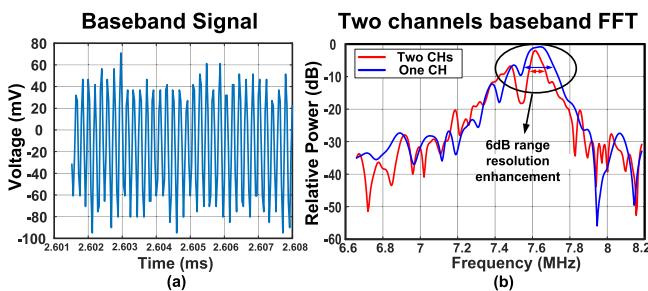

As compared with one single-band FMCW radar 1TX-1RX architecture, where a single baseband signal is sampled by one ADC, the stepped chirp architecture has two baseband signals coming from RX<sub>1</sub> and RX<sub>2</sub>, which combine in the digital domain to construct the same length of baseband signal as that of the single-chirp architecture. The signal processing is done by stitching different baseband signals [42] in time or frequency domain, as illustrated in Fig. 8(d) and (e). To analytically verify the RX principle of operation, we assume  $N$  transmitted chirps correspond to the sub-bands of the form shown in Fig. 8(c).

$$TX_i(t) = \cos[2\pi(f_i + St) \cdot t + \theta_i], \quad 0 \leq i \leq N-1 \quad (1)$$

where  $f_i$  is the initial frequency of the  $i$ th chirp,  $S = BW/T_r$  is the slope of each chirp, and  $\theta_i$  is the initial phase of each chirp. Assuming a single target with a reflection coefficient  $\sigma_0$  at distance  $R$  from the radar sensor, the reflected components of the sub-bands can be expressed as follows:

$$RX_i(t, R) = \sigma_0 \cos \left\{ 2\pi \left[ f_i + S \left( t - \frac{2R}{c} \right) \right] \cdot \left( t - \frac{2R}{c} \right) + \theta_i \right\} \quad 0 \leq i \leq N-1. \quad (2)$$

The IF signal is obtained by mixing the TX and RX signals and getting the lower frequency part as follows:

$$IF_i(t, R) = \frac{1}{2} \sigma_0 \cos \left( 2\pi S \cdot \frac{2R}{c} \cdot t + 2\pi f_i \frac{2R}{c} - \pi S \left( \frac{2R}{c} \right)^2 \right) \quad 0 \leq i \leq N-1. \quad (3)$$

The term  $\pi S((2R/c)^2)$  is small enough to be neglected. Therefore, the initial phase of the IF signal is only determined by the initial frequency  $f_i$  and round trip time ( $2R/c$ ). To validate the seamless stitching of the baseband waveform, consider two sub-bands. At the endpoint of the first sub-band ( $t = T_r$ ), the phase of the first baseband is

$$\varphi_{IF,1}(T_r, R) = 2\pi \cdot \frac{2R}{c} \cdot BW + 2\pi f_1 \frac{2R}{c}. \quad (4)$$

At the starting point of the second sub-band ( $t = 0$ ), the phase of the second baseband signal is

$$\varphi_{IF,2}(0, R) = 2\pi f_2 \frac{2R}{c}. \quad (5)$$

The phase difference between these two points is given by the following equation:

$$\Delta\varphi_{IF} = \varphi_{IF,2}(0, R) - \varphi_{IF,1}(T_r, R) = 2\pi \cdot \frac{2R}{c} \cdot \Delta f \quad (6)$$

where  $\Delta f = f_2 - f_1$  is the frequency offset between the two sub-bands. In the real implementation, to mitigate frequency pulling, we selected  $f_1 = 50$  GHz and  $f_2 = 57$  GHz with  $BW = 5$  GHz. The resulting phase difference  $\Delta\varphi_{IF}$  is constant and independent of time. This constancy ensures that the baseband signals of the two sub-bands can be seamlessly aligned by compensating for  $\Delta\varphi_{IF}$ .

Moreover, because the chirp slope is identical across sub-bands (enforced by the mixing PLL), the stitched IF signal

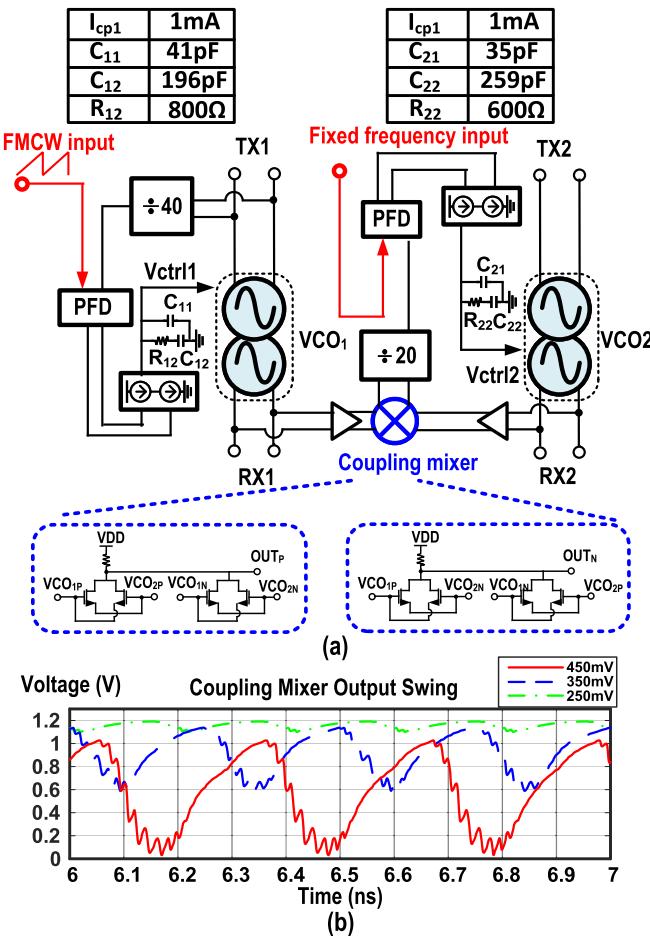

Fig. 9. (a) Frequency synthesizer block diagram with values of  $RC$  loop filter and the schematic of the fully balanced coupling mixer. (b) Simulated output swing of the coupling mixer for input swings of 250, 350, and 450 mV.

exhibits the same baseband peak as each IF signal. By applying FFT to the stitched baseband, an equivalent BW of  $N \cdot BW$  can be achieved, thus effectively enhancing the radar's range resolution.

### III. CIRCUIT IMPLEMENTATION AND PACKAGE

In this section, we will review the design and simulated performance of the circuit blocks inside the TX and RX, the chip-to-board interface and matching network, and the printed circuit board (PCB) patch antenna arrays.

#### A. Frequency Synthesizer

The frequency synthesizer block diagram is shown in Fig. 9(a). Both the reference and mixing PLLs are designed with a PFD, a CP, and a second-order loop filter. The outputs from both dual-core VCOs are directed to a low-power cross-connected differential fully balanced mixer block. The mixer's output is subsequently downconverted by a factor of 20. The input swing of the driving signal is crucial for properly driving the coupling mixer. The simulated output swing of the coupling mixer, as shown in Fig. 9(b), demonstrates that a 450 mVpp driving signal is required to achieve a 1 Vpp output swing. To ensure this, we include a common-source (CS) buffer stage between the VCO and coupling mixer,

Fig. 10. (a) Simulated chirp profile and (b) simulated frequency error versus ideal chirp.

which guarantees the 450 mV peak-to-peak input swing. The resulting 1 V peak-to-peak output is sufficient to drive the subsequent stage. The values of all the resistors and capacitors used in the second-order loop filter are provided in Fig. 9. The radar's targeted chirp rate is 200 MHz/μs, and the loop BWs of the reference and mixing PLLs are selected to be around 400 and 380 kHz to meet the desired performance. The simulated chirp profile is shown in Fig. 10(a). With the loop filter and charge pump current chosen accordingly, the chirp of the mixing PLL can be locked to that of the reference PLL. The frequency error between the simulated and ideal chirps is presented in Fig. 10(b). Since the modulation of the mixing PLL chirp depends on the reference PLL, the rms frequency error of the mixing PLL is higher than that of the reference PLL. Due to instability at the start of the chirp, the rms frequency error is calculated from 1.2 to 2 μs. The simulated frequency rms of reference PLL and Mixing PLL are 1130 and 1564 kHz, respectively. The simulated power consumption of reference PLL and mixing PLL (excluding the VCOs) is 46.8 and 18.1 mW, respectively.

#### B. Voltage Controlled Oscillators

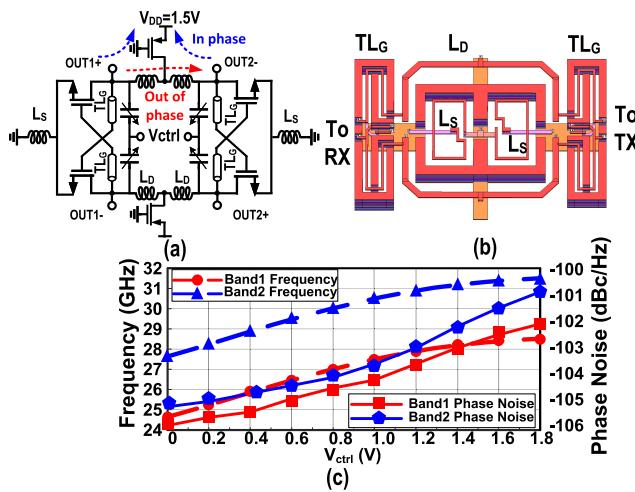

The principle of FMCW radar involves mixing the TX signal with a delayed and attenuated version received by the RX. Hence, it is common practice to share the LO signal between the TX and RX. In our design, we implement a dual-core coupled cross-coupled oscillator with source degeneration [43] as the core VCO for each sub-band, as shown in Fig. 11. The use of a dual-core VCO helps reduce signal routing complexity compared to using a single-core VCO combined with buffers and power splitters. In addition, the PN of the

Fig. 11. (a) Dual core VCO schematic, (b) EM structure, and (c) simulated frequency versus  $V_{ctrl}$  and PN at 1 MHz offset versus  $V_{ctrl}$ .

VCO can be improved by  $10\log(2) = 3$  dB by coupling two VCOs [44], [45]. The primary challenge in designing a functional dual-core VCO is the suppression of undesired oscillation modes. As illustrated in Fig. 11(a), when OUT1+ and OUT2- are out of phase, they are in differential mode and the oscillatory current does not pass through the PMOS transistors connected to  $V_{DD}$ . Conversely, if OUT1+ and OUT2- are in phase (common mode operation), the current flows through the PMOS devices. In this case, the PMOS devices, with their gates grounded and operating in the triode region, act as lossy resistors that degrade the  $Q$ -factor of the  $LC$  tank. As a result, the common-mode oscillation is eliminated, allowing only the differential mode to persist.

Compared to conventional cross-coupled VCO, a short T-line is added between the gate and the drain to further boost the voltage swing at the transistor's gate [43]. A thick-oxide transistor is chosen to allow a gate voltage swing of up to 2.4 V ( $2V_{DD}$ ), which contributes to larger voltage swings for better PN performance, while reducing flicker noise due to the larger gate area ( $W \times L$ ). The layout of each VCO is simulated with EM solvers to capture the coupling effect among the lines and inductors [see Fig. 11(b)]. Post-layout simulation results showing the frequency tuning range and PN characteristics of each sub-band VCO are shown in Fig. 11(c).

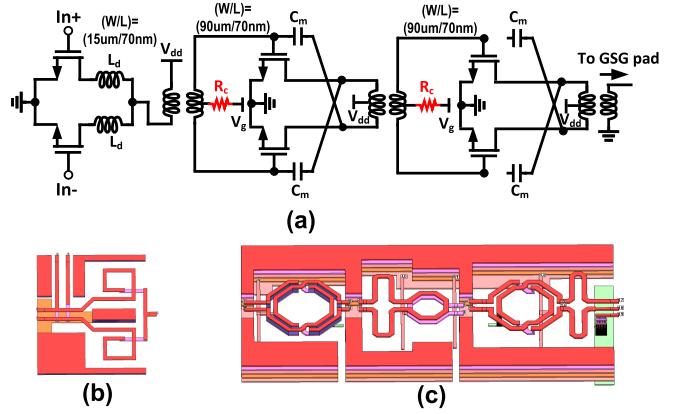

### C. Doubler and PA

In this design, we adopt a superharmonic configuration where the radiated frequency is twice that of the VCO oscillation frequency in each sub-band. A push-push frequency doubler in Fig. 12(a) is adopted to upconvert the VCO signal, which is followed by a two-stage transformer-coupled differential PA [46], [47]. Since we use the differential signaling, the mutual coupling capacitors only help with differential mode stability [48]. A 4-k $\Omega$  resistor  $R_c$  is added at each gate bias dc node to suppress the common-mode oscillations.

For the first sub-band, the frequency doubler provides an output power of  $-5$  dBm with an output impedance of  $(20 + j10)$   $\Omega$ . A thick gate-oxide transistor with a 70-nm gate length is chosen for the PA to support a higher

Fig. 12. (a) Schematic of frequency doubler and PA, EM structure of (b) doubler and (c) PA.

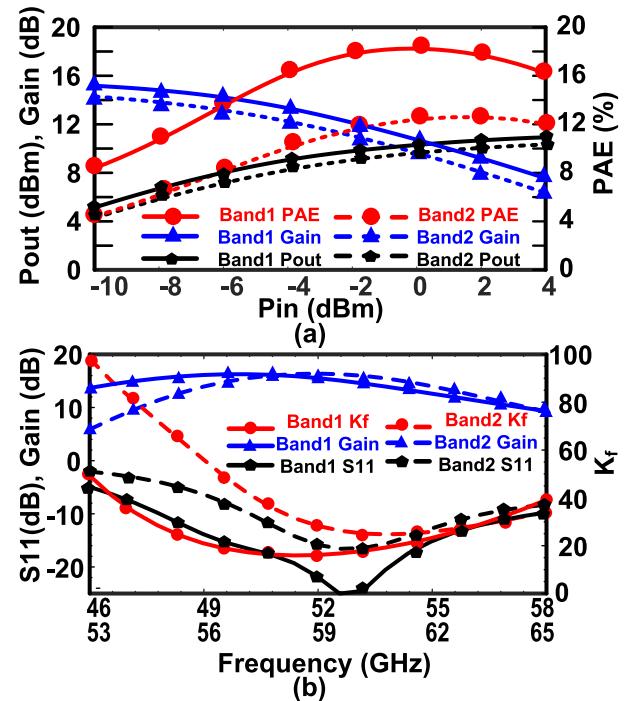

Fig. 13. PA simulation results for band1 and band2 (a)  $P_{out}$ , gain and PAE and (b)  $S_{11}$ ,  $S_{21}$ , and  $K_f$ .

supply voltage of 1.2 V, enhancing  $P_{sat}$ . The transistor widths for both stages are set at  $30 \mu\text{m} \times 3$  for both stages based on the power and gain requirements. Impedance matching between the frequency doubler and PA input is accomplished using an input balun, while the interstage matching is achieved through a stacked transformer. To further enhance impedance matching across a 12-GHz BW, an additional transmission line is incorporated within the matching network. Finally, the output of the second stage is matched to  $50\Omega$  load impedance through the output balun. Both the stages employ the over-neutralization technique [49] to bring the device stability factor above  $K_f = 1$ , while increasing the gain. The EM-simulated layouts of the doubler and PA are shown in Fig. 12(b) and (c). The insertion loss of the input balun, interstage matching, and output balun varies between 1.2 and 1.8 dB. The S-parameter simulation results are shown in Fig. 13(a) where 10 dB input-return is achieved across 46–58 GHz with a

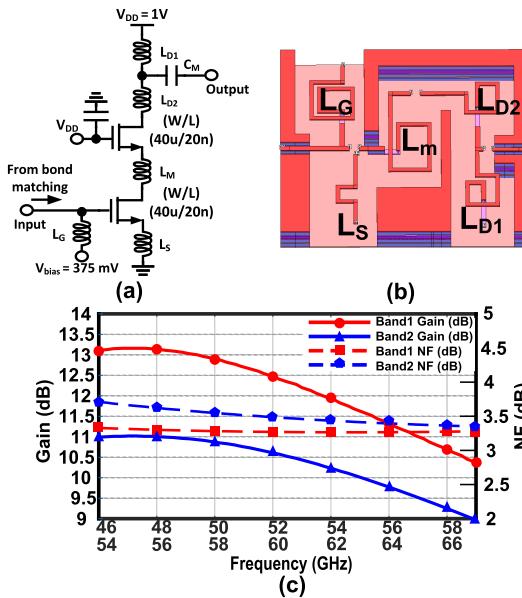

Fig. 14. (a) LNA schematic, (b) LNA EM structure, and (c) simulated conversion gain and NF for the low-frequency band and high-frequency band.

peak  $S_{21}$  of 16.3 dB and  $K_f$  of more than 24.7. The simulation plots for the output power ( $P_{out}$ ), large signal gain, and power added efficiency PAE are shown in Fig. 13(b). A 6.75-dBm output power, 17.7% of PAE, and a large signal gain of 11.87 dB is attained for an input power of  $-5$  dBm at 53 GHz.

The PA for the second sub-band, covering the 56–63-GHz frequency range, uses the same topology and device dimensions as the first band. The small signal S-parameter simulation results are presented in Fig. 13(a), showing a  $S_{11}$  better than  $rc10$  dB, a  $S_{21}$  of 14.5–15.8 dB, a  $K_f$  of greater than 15.9 across the designed band. The large signal simulation results, shown in Fig. 13(b), indicate that for the doubler's output power of  $-5$  dBm and the output impedance of  $(20 + j20) \Omega$ , the PA delivers an output power of 6 dBm, a PAE of 11.5%, and a large-signal gain of 11 dB at 60 GHz.

#### D. LNA and Mixer

A three-stage single-ended cascode LNA is employed in this design, where the first-stage schematic is shown in Fig. 14(a). The LNA's EM layout is shown in Fig. 14(b) where inductors are co-simulated to capture any unwanted mutual coupling. The input transistor is biased at optimum dc current to achieve a lower  $NF_{min}$ . An inductor  $L_M$  is inserted between CS and common-gate devices for a better power and noise matching [50], [51]. The EM-simulated layout of the LNA is shown in Fig. 14(b) and the simulated LNA single-stage gain and noise figure (NF) for each sub-band are shown in Fig. 14(c).

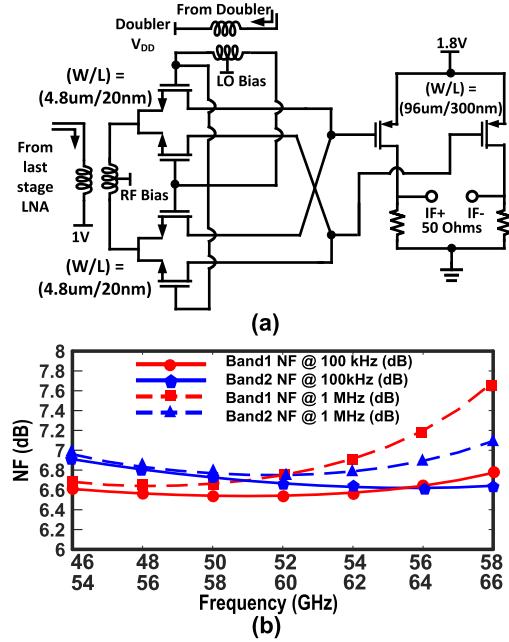

Following the LNA, a double-balanced passive mixer [see Fig. 15(a)] is deployed. Since no dc current passes through the switching transistors [52], [53], [54], the flicker noise from these switching transistors is substantially reduced. In addition, the mixer is connected to a large PMOS transistor ( $W/L = 96 \mu\text{m}/300 \text{ nm}$ ), introducing a large capacitive load to reduce the impact of flicker noise on the radar operation. In this design, flicker noise suppression is critical since the

Fig. 15. (a) Passive mixer and buffer schematic and (b) simulated NF at 100 kHz and 1 MHz offset.

Fig. 16. Illustration of (a) TX packaging matching and (b) RX packaging matching.

baseband range of interest is designed to be below 20 MHz. The total simulated NF at both 100 kHz and 1 MHz offset frequencies for both sub-bands is shown in Fig. 15(b). The NF at 100 kHz offset is just around 1 dB higher than that at 1 MHz, highlighting the advantage of the passive mixer and large capacitive load.

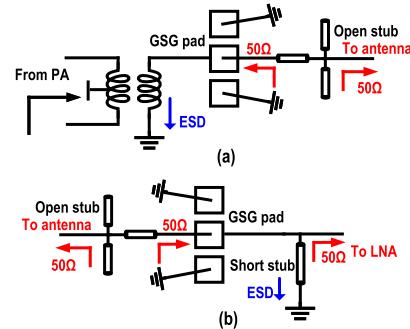

#### E. Wirebond Matching and Antenna Design

At higher operation frequencies, the design of the chip-to-board interface becomes crucial in minimizing losses between the PA and antenna, ensuring maximum radiated power. Wire-bonding, while low cost and highly durable for low-frequency packaging, suffers from large parasitic inductance that limits the BW. This limitation highlights the importance of the stepped chirp architecture, wherein each channel only needs to cover 7 GHz.

For matching on the chip side, electrostatic discharge (ESD) protection at the pad interface must be considered. On the TX side, a balun is used to convert the differential signal to single-ended. The short-to-ground inductor can serve as the ESD protection element while also matching the impedance at the ground-signal-ground (GSG) pad to  $50 \Omega$ , as illustrated

Fig. 17. (a) Top view of antennas and (b) simulated radiation pattern.

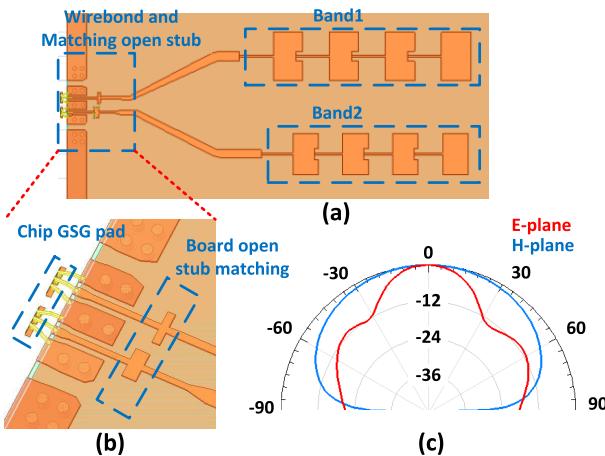

in Fig. 16(a). An open stub is added on the board to cancel out the parasitic effects introduced by the wirebond and transform the impedance back to  $50\ \Omega$  for the antenna. The RX side matching is similar to the TX side, as shown in Fig. 16(b). However, since the LNA is single-ended, a short stub is used to match the parasitic capacitance of the GSG pad. The HFSS view of chip-to-antenna interface is shown in Fig. 17(a), with a zoomed-in view of the interface shown in Fig. 17(b). Each sub-band employs a series-fed linear array of microstrip patch antennas. Patch antennas are commonly used in FMCW radars due to their compatibility with planar feed structures and their ability to provide broadside radiation [14], [55]. HFSS simulations indicate that the insertion loss of the interface network stays below 1.5 dB across both frequency bands, justifying the use of a wirebond for the interface. The simulated radiation pattern of the antennas is shown in Fig. 17(c), where more than 7 dBi of realized gain is achieved for each sub-band antenna array. Two-band series-fed patch antennas are designed to balance between the FoV and directivity, e.g., wide beamwidth for *H*-plane and narrow beamwidth for *E*-plane, as shown in Fig. 17(c).

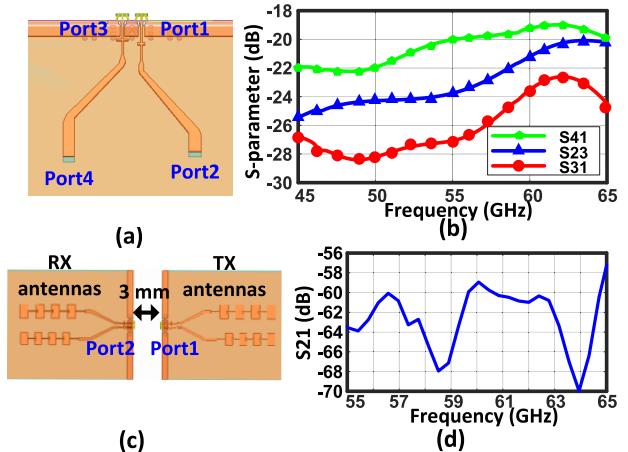

The coupling between two adjacent bands was simulated by replacing the series-fed patch antenna with a lumped port, as illustrated in Fig. 18(a). The electromagnetic (EM) simulation results, shown in Fig. 18(b), indicate attenuations exceeding 19 dB. The TX to RX leakage due to the standalone antenna was also simulated, as depicted in Fig. 18(c). The simulation setup places the two antenna boards at a separation distance of 3 mm to accommodate the chip. The isolation between TX and RX is below  $-58\text{ dB}$  across the 55–65 GHz frequency range as shown in Fig. 18(d). It should be noted that this simulation only characterizes the coupling between the two antennas due to radiation and does not account for on-chip TX-to-RX leakage. Two other mechanisms in this design provide more isolation between adjacent bands for both TX and RX antennas: 1) the bandpass profile of the antennas, each centered at its designated sub-band frequency and 2) the input matching network comprising the chip-to-board interface and the LNA input matching, designed to capture only the target sub-band BW.

Fig. 18. (a) EM simulation testbench for characterizing isolation between adjacent channels, (b) simulated  $S_{41}$ ,  $S_{23}$ , and  $S_{31}$ , (c) EM simulated TX to RX leakage characterization, and (d) simulated  $S_{21}$  representing TX to RX leakage.

#### IV. MEASUREMENT RESULTS

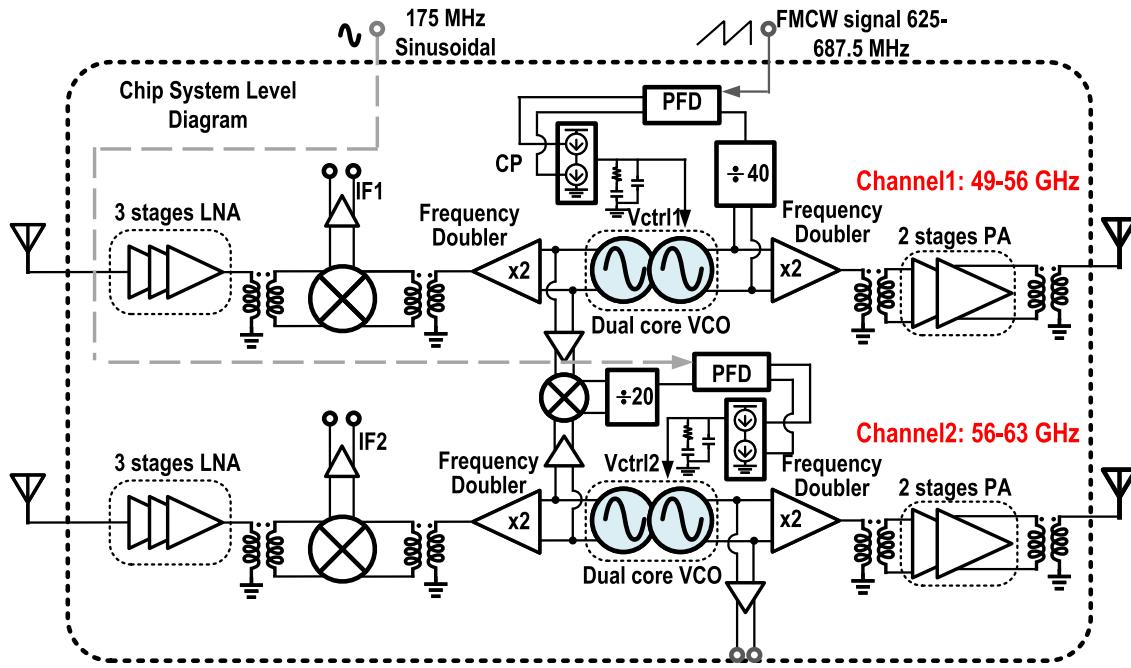

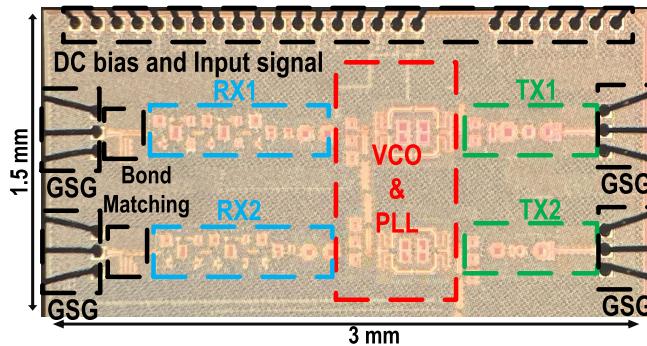

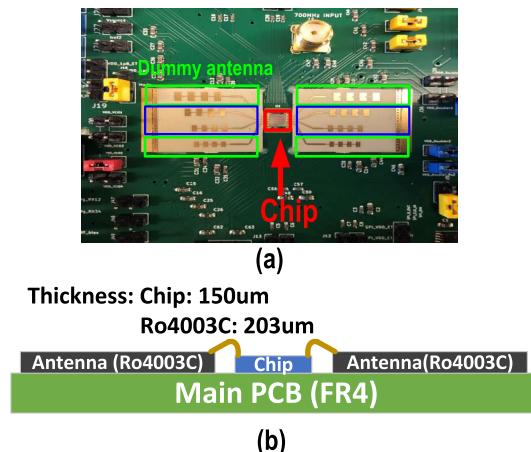

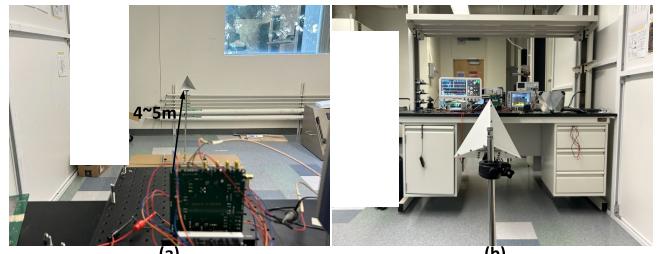

The complete circuit block diagram of the CMOS TRX excluding the antenna and interface is shown in Fig. 19. Shown in Fig. 20, the proposed radar TRX was fabricated in 22-nm fully depleted silicon on insulator (FD-SOI) CMOS, occupying  $4.5\text{ mm}^2$  of die area including pads. The TX and RX antenna arrays, shown in Fig. 21(a), were fabricated using Rogers 4003C. The two dummy antennas, positioned at the top and bottom, were added to mitigate process variations caused by the bending of the Rogers material [14]. Each linear-fed antenna array can achieve up to 8% radiation BW. As shown in Fig. 21(b), the antenna board and chip were glued on top of the platform FR-4 PCB, which also included the dc regulators and PLL input signal. To examine the operation of the proposed radar, three separate types of measurements were conducted: 1) stand-alone TX; 2) stand-alone RX; and 3) radar TRX measurements. In what follows, the specific measurements for each of these tests are provided and explained.

##### A. TX Measurements

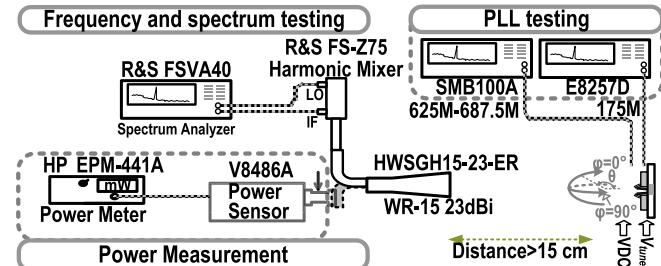

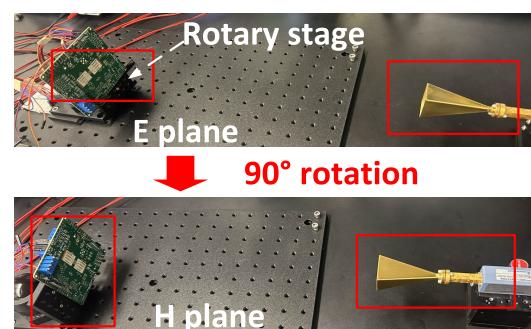

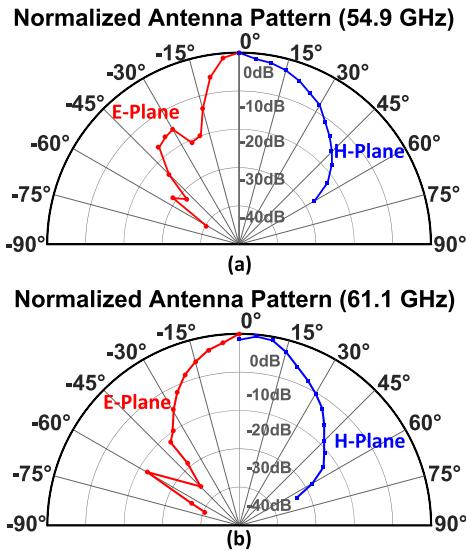

The TX/PLL measurement setup is shown in Fig. 22. To measure the radiation pattern of the TX antennas, the chip was mounted on a rotational optical stage and the diagonal horn antenna was kept still (see Fig. 23). Both *E*-plane and *H*-plane measurements of the radiation pattern were conducted for both frequency bands using this technique and the results are provided in Fig. 24. Both antenna arrays achieve more than 6.5 dBi of measured realized gain.

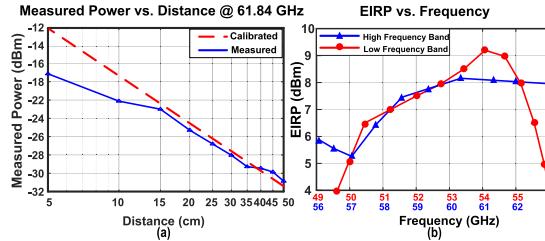

Wireless testing was performed at distances exceeding 15 cm, beyond the Fraunhofer distance, to evaluate frequency and spectrum performance. The received signal was collected using a diagonal horn antenna, and the effective isotropic radiated power (EIRP) was measured with a power sensor and power meter. For PN and spectral measurements, the received signal was fed to a spectrum analyzer, with measurements taken in both free-running and phase-locked modes. In phase-locked mode, a 175 MHz external reference was injected into the mixing PLL, while a ramp input signal between 625–687.5 MHz was applied to the reference PLL.

Fig. 19. Detailed TRX block diagram.

Fig. 20. Chip microphoto.

Fig. 21. Board design. (a) Top view and (b) cross section view.

The far-field EIRP measurements were repeated for various distances, and are shown in Fig. 25(a), where a close match between the received power with that estimated by the

Fig. 22. TX and PLL measurement setup.

Fig. 23. Antenna pattern measurement for both E-plane and H-plane.

Friis equation [18] are observed. The peak EIRP is above 9 dBm for the low-frequency band and above 8 dBm for the high-frequency band. The power variations across the two sub-bands are attributed to the frequency-band mismatch between the antenna and PA as well as 3-dB loss for deviated PA output load impedance due to process variations and shifts in operation frequency.

For spectral measurements, two separate sets of measurements were conducted for the free-running and phase-locked

Fig. 24. Measured normalized antenna pattern at (a) 54.9 GHz (low-frequency band) and (b) 61.1 GHz (high-frequency band).

Fig. 25. (a) Close match of power profile with Friis formula at 61.84 GHz. (b) Measured EIRP from 49 to 63 GHz.

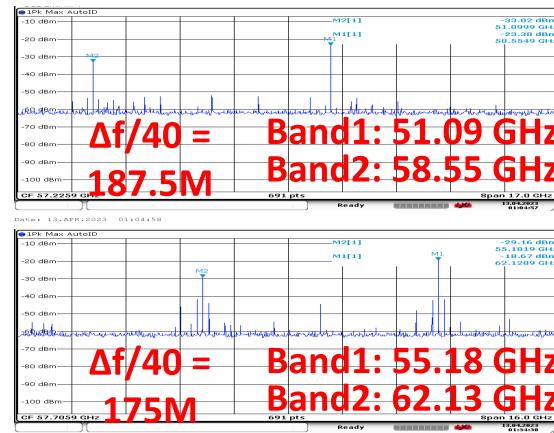

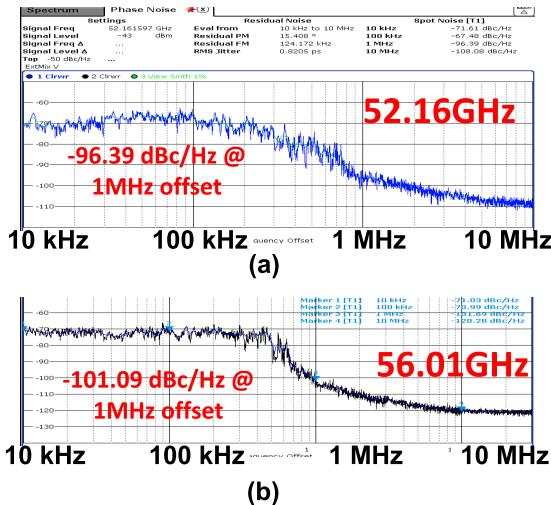

operations. On the TX side, the BW of free-running and phase-locked operation and the corresponding PN profiles were measured, as shown in Figs. 26–28, respectively. Each sub-band achieves close to 7 GHz of free-running BW in Fig. 26. However, the preferred mode of operation for this radar is the phase-locking mode, the frequency separation between the two sub-bands is precisely controlled. This is demonstrated in Fig. 27 where the external input to the mixing PLL sets  $\Delta f$  to 7.5 and 7 GHz for the respective scenarios shown in Fig. 27. The two pairs of spurs introduced by the input signals do not impair radar operation, since their spacing ( $\Delta f/40$ ) exceeds the 20-MHz IF BW of this radar, with all the spurs occurring at multiples of  $\Delta f/40$ . According to the measurement results, the TX can achieve a phase-locked radiation BW of 10 GHz. The smaller BW of phase-locked mode compared to the free-running scenario is attributed to the PLL loop BW, which limits the frequency tuning for stable loop operations. PN measurements at different spot frequencies under phase-locked operation are shown in Fig. 28. The PN at 1-MHz offset is  $-96.39$  and  $-101.7$  at 52.16 and 56.01 GHz, respectively. The locked loop BW varies between 200 and 500 kHz across all these samples.

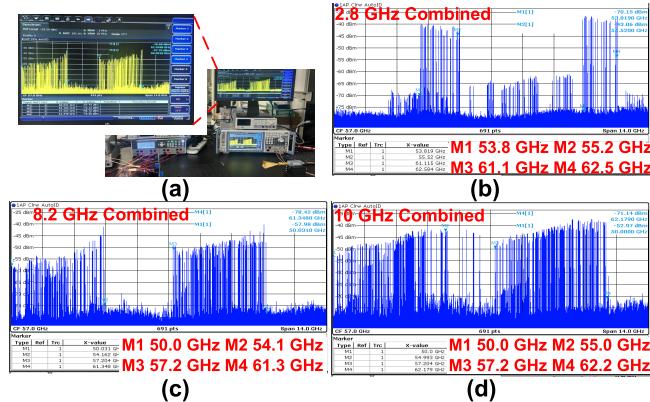

To demonstrate the simultaneous phase-locked operation of the radar for the two adjacent sub-bands, multiple dual-band measurements were conducted where the reference and mixing PLLs were enabled for variable BW associated with each sub-band. Three narrow-band operation scenarios (BW of each

Fig. 26. Free running operation at minimum and maximum frequencies.

Fig. 27. Phase-locked operation at two distinct PLL reference frequencies.

band below 1.4 GHz), medium resolution (combined BW of 8.2 GHz), and high-resolution (combined BW of 10 GHz) were captured, and the corresponding spectrums are shown in Fig. 29. An important feature of this radar is the similar output power profiles of the two sub-bands under various BWs, enabling adjustable range resolution to suit different applications.

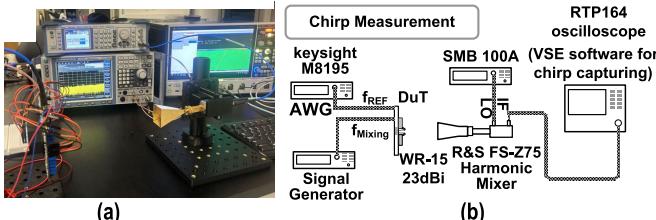

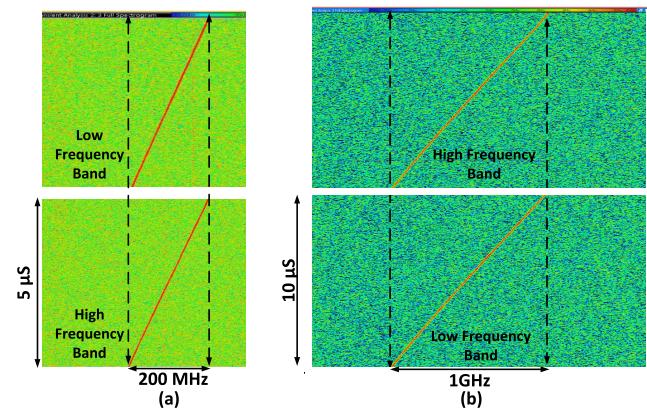

A chirp profile measurement was carried out using the measurement setup in Fig. 30(a), where the signal was down-converted using an R&S FS-Z75 and analyzed on an R&S RTP164B with VSA software. The setup block diagram is shown in Fig. 30(b). The measured dual-band chirp profiles under locking conditions are presented in Fig. 31(a) and (b) for modulation BWs of 200 MHz and 1 GHz per sub-band, respectively. The measured rms frequency errors for a 200 MHz modulation BW in the low and high-frequency sub-bands were 716 kHz and 1.844 MHz, respectively. At a 1-GHz modulation BW, the measured errors increased to 1.367 and 2.664 MHz in the low and high-frequency sub-bands, respectively.

Fig. 28. Measured phase-locked PN profile at 52.16 and 56.01 GHz.

Fig. 29. (a) Dual band operation measurement setup, (b) 2.8-GHz BW, (c) 8.2-GHz BW, and (d) 10-GHz BW.

Fig. 30. (a) Chirp measurement setup using an oscilloscope. (b) Block diagram of the measurement setup.

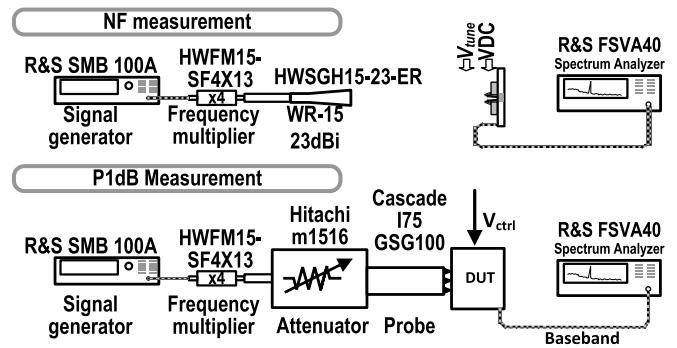

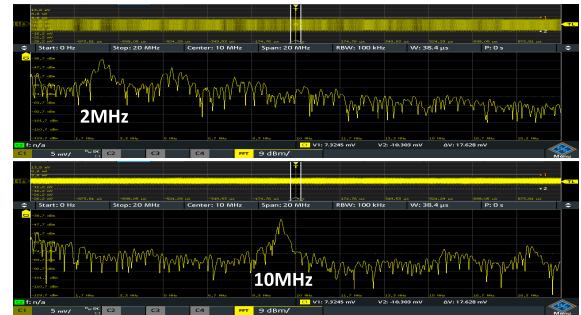

### B. RX Measurements

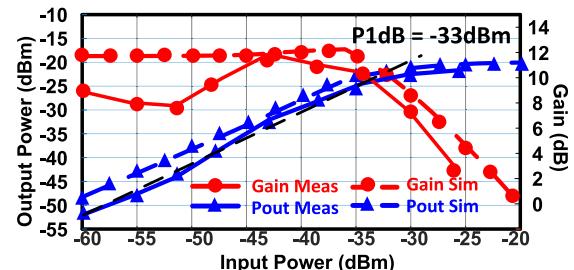

The RX measurement setup utilizing an external signal generator is shown in Fig. 32. The objective of this measurement is to evaluate the RX baseband signal by positioning the chip in the far-field of the diagonal horn antenna and receiving signals at different distances to induce shifts in the resultant IF signal. The IF spectrum associated with this measurement is shown in Fig. 33 where two peaks at 2 and 10 MHz were obtained by changing the distance between the horn antenna and chip. Both measurements indicate 30-dB SNR. The RX P1dB measurement was performed using a probe landing setup, with the input power adjusted through an attenuator, as illustrated in Fig. 32 (bottom). From the measured output

Fig. 31. Dual-band chirp operation for (a) 200-MHz BW and (b) 1-GHz BW per band.

Fig. 32. Measurement setup of RX NF (top) and P1dB (bottom).

Fig. 33. RX baseband fft spectrum with a peak at 2 and 10 MHz.

Fig. 34. Simulation and measurement results of RX Gain and  $P_{out}$  versus  $P_{in}$ .

power versus input power characteristics shown in Fig. 34, the RX 1-dB compression point (P1dB) is estimated to be approximately  $-33$  dBm.

TABLE I

PERFORMANCE SUMMARY AND COMPARISON WITH PREVIOUS ARTS

|                    | This work                          | [13]         | [56]           | [57]          | [58]            | [26]               | [32]            | [8]          |

|--------------------|------------------------------------|--------------|----------------|---------------|-----------------|--------------------|-----------------|--------------|

| Process            | 22nm<br>FD-SOI                     | 45nm<br>CMOS | 350nm<br>SiGe  | 130nm<br>SiGe | 28nm<br>CMOS    | 40nm<br>CMOS       | 22nm<br>FD-SOI  | 28nm<br>CMOS |

| Phase Locked       | Yes                                | Yes          | No             | No            | No              | Yes                | Yes             | Yes          |

| $N_{RX}/N_{TX}$    | 2/2                                | 4/3          | 4/2            | 1/1           | 3/2             | 2/2                | 2/2             | 1/1          |

| Frequency [GHz]    | 49-63                              | 57-64        | 57-64          | 58.3-63.9     | 57-64           | 54-69              | 57-66           | 57-66        |

| Architecture       | Coupled PLL                        | PLL          | VCO            | VCO           | VCO             | Cascaded-PLL       | ADPLL           | PLL          |

| PN [dBc/Hz]@1MHz   | -101.7                             | -93          | -105           | -             | -99.4           | -93.3              | -73             | -92.9        |

| Bandwidth          | 14 <sup>†</sup><br>10 <sup>†</sup> | 4            | -              | 5.6           | 9               | 7.2                | 9               | 7.2          |

| TX $P_{out}$ [dBm] | 6                                  | 12.1         | 4( $P_{sat}$ ) | 6.4           | 10( $P_{sat}$ ) | 12.8( $P_{sat}$ )  | 1               | 8.1          |

| Antenna gain [dB]  | 7 <sup>‡</sup>                     | -            | -              | -             | -               | -                  | -               | -            |

| RX NF [dB]         | 10                                 | 12.5         | 9.5            | -             | 12              | 10                 | 30              | 10.5         |

| RX Gain [dB]       | 20                                 | -            | 19             | -             | 77              | 20-87 <sup>^</sup> | 6               | 46           |

| RX P1dB [dBm]      | -33                                | -10/-14      | -8.5           | -8.1          | -12             | -11                | -               | -43 to -33   |

| $P_{dc}$ [mW]      | 400                                | 3500         | 990            | 520           | 920             | 695                | 68 <sup>◊</sup> | 62           |

| Area [ $mm^2$ ]    | 4.5                                | -            | 20.25          | 1.03*         | 7.45            | 9.9                | 1.25            | 4.13         |

<sup>†</sup> 14 GHz free running bandwidth and 10GHz phase locked bandwidth

<sup>‡</sup> Realized gain including matching structure

\* TX and RX share same antenna

<sup>^</sup> including baseband amplifier

<sup>◊</sup> not including baseband amplifier and digital loop filter

Fig. 35. Estimated NF measurement from radiation-based setup.

Fig. 36. Enhancement of range resolution by applying FFT on the combined IF signal of the two sub-bands. (a) Baseband time-domain signal from radar field measurement. (b) Enhanced range resolution achieved by applying FFT on the combined IF signal from the two subbands.

The key advantage of the phase-locked stepped chirp architecture lies in its ability to enhance resolution by integrating multiple sub-bands. To demonstrate this feature, a radar field measurement was performed at a distance of 50 cm, and the IF signals from both sub-bands were extracted separately. The time-domain IF signals were then combined, as shown in Fig. 36(a). The FFT of the combined signal, shown in Fig. 36(b), reveals a significant enhancement of range resolution where closely spaced peaks become clearly distinguishable. For this measurement, the range resolution of

Fig. 37. Radar field measurement with corner reflector object. (a) Radar field measurement taken from the chip side. (b) Radar field measurement taken from the object side.

Fig. 38. Radar field measurement at (a) 1.4, (b) 2.65, and (c) 4.8 m.

each sub-band was 28 mm, and for the combined signals, the range resolution was enhanced to the finer value of 14 mm.

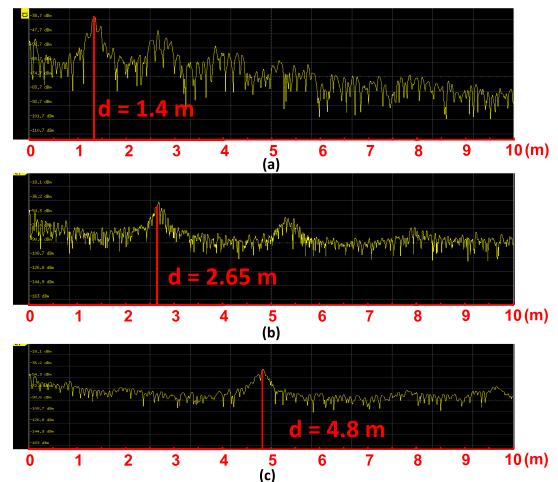

### C. Radar Field Measurements

Various field measurements of the radar are conducted at multiple distances between the radar TRX and a reflector

Fig. 39. Measured power consumption breakdown.

object. As shown in Fig. 37, a corner reflector object is placed at incremental distances ranging from 0.5 to 5 m.

The range measurements of the radar for these different range scenarios are shown in Fig. 38. It is observed that for all the measurements, the radar maintains an IF SNR above 16 dB translating to 10 dB of  $NF_{SSB}$  for the RX chain. These measurements were conducted at room temperature and with no aid from culminating Teflon lenses or silicon lenses to improve the EIRP of the TX.

Fig. 39 summarizes the measured power breakdown of the circuit blocks in the TX and RX. The total power consumption of this two-band phase-locked radar TRX is 400 mW, significantly lower compared to the prior art. Table I compares the measurement results with the prior art. This work outperforms the radars in the same frequency range in terms of PN, phase-locked BW, and power consumption. This design demonstrates the first phase-locked stepped chirp radar with more than 10-GHz synthetic BW, and a few meters detectable range.

## V. CONCLUSION

In this article, a fully integrated CMOS-based phase-locked stepped chirp radar TRX at 49–63 GHz was presented. The TX side employed a novel PLL scheme which reduced the power consumption and the necessary division ratio compared to conventional type-II PLLs. The RX side incorporated frequency-segmented narrow-band RXs which are combined in the IF domain to enhance the range resolution. The phase-locked BW of this radar was more than 10 GHz and achieved a peak EIRP of 9 dBm. Due to the selected frequency of operation and the total synthetic BW of operation, this radar achieved a meter-scale range of coverage and centimeter-scale (1.4 cm) range resolution simultaneously. This radar TRX with a low power consumption of 400 mW offers a potential candidate for future mm-wave radars for automotive, crack detection, and surface monitoring applications.

## ACKNOWLEDGMENT

The authors would like to express their gratitude to Global-Foundries (GF) for chip fabrication. They also sincerely thank Judy Pourazima and Adam Frisius from Rohde and Schwarz for their invaluable support with measurements, as well as Keysight for their assistance.

## REFERENCES

- C. Waldschmidt, J. Hasch, and W. Menzel, “Automotive radar—From first efforts to future systems,” *IEEE J. Microw.*, vol. 1, no. 1, pp. 135–148, Jan. 2021.

- J. Hasch, E. Topak, R. Schnabel, T. Zwick, R. Weigel, and C. Waldschmidt, “Millimeter-wave technology for automotive radar sensors in the 77 GHz frequency band,” *IEEE Trans. Microw. Theory Techn.*, vol. 60, no. 3, pp. 845–860, Mar. 2012.

- J. Weiß, R. Pérez, and E. Biebl, “Improved people counting algorithm for indoor environments using 60 GHz FMCW radar,” in *Proc. IEEE Radar Conf. (RadarConf)*, Sep. 2020, pp. 1–6.

- R. Jacobi and A. Aginsky, *Choosing 60-GHz mmWave Sensors Over 24-GHz to Enable Smarter Industrial Applications*. Dallas, TX, USA: Texas Instruments, Nov. 2018.

- M. Alesheikh, R. Feghhi, F. M. Sabzevari, A. Karimov, M. Hossain, and K. Rambabu, “Design of a high-power Gaussian pulse transmitter for sensing and imaging of buried objects,” *IEEE Sensors J.*, vol. 22, no. 1, pp. 279–287, Jan. 2022.

- X. Liu, M. H. Maktoomi, M. Alesheikh, P. Heydari, and H. Aghasi, “A 49–63 GHz phase-locked FMCW radar transceiver for high resolution applications,” in *Proc. IEEE 49th Eur. Solid State Circuits Conf. (ESSCIRC)*, Sep. 2023, pp. 509–512.

- T. Mitomo, N. Ono, H. Hoshino, Y. Yoshihara, O. Watanabe, and I. Seto, “A 77 GHz 90 nm CMOS transceiver for FMCW radar applications,” *IEEE J. Solid-State Circuits*, vol. 45, no. 4, pp. 928–937, Apr. 2010.

- S. Park et al., “A 62 mW 60 GHz FMCW radar in 28nm CMOS,” in *Proc. IEEE Radio Freq. Integr. Circuits Symp. (RFIC)*, Aug. 2020, pp. 31–34.

- H. Aghasi and P. Heydari, “Millimeter-wave radars-on-chip enabling next-generation cyberphysical infrastructures,” *IEEE Commun. Mag.*, vol. 58, no. 12, pp. 70–76, Dec. 2020.

- B. van Berlo, A. Elkelany, T. Ozcelebi, and N. Meratnia, “Millimeter wave sensing: A review of application pipelines and building blocks,” *IEEE Sensors J.*, vol. 21, no. 9, pp. 10332–10368, May 2021.

- S. Rao, “Introduction to mmWave sensing: FMCW radars,” in *Texas Instruments (TI) mmWave Training Series*, 2017, pp. 1–11.

- Y.-P. Su, C.-Y. Huang, and S.-J. Chen, “A 24-GHz fully integrated CMOS transceiver for FMCW radar applications,” *IEEE J. Solid-State Circuits*, vol. 56, no. 11, pp. 3307–3317, Nov. 2021.

- K. Dandu et al., “2.2 high-performance and small form-factor mm-wave CMOS radars for automotive and industrial sensing in 76-to-81 GHz and 57-to-64 GHz bands,” in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, vol. 64, Feb. 2021, pp. 39–41.

- B. P. Ginsburg et al., “A multimode 76-to-81 GHz automotive radar transceiver with autonomous monitoring,” in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2018, pp. 158–160.

- V. Jain, F. Tzeng, L. Zhou, and P. Heydari, “A single-chip dual-band 22–29-GHz/77–81-GHz BiCMOS transceiver for automotive radars,” *IEEE J. Solid-State Circuits*, vol. 44, no. 12, pp. 3469–3485, Dec. 2009.

- A. Arbabian, S. Callender, S. Kang, M. Rangwala, and A. M. Niknejad, “A 94 GHz mm-wave-to-baseband pulsed-radar transceiver with applications in imaging and gesture recognition,” *IEEE J. Solid-State Circuits*, vol. 48, no. 4, pp. 1055–1071, Apr. 2013.

- F. Norouzian, E. G. Hoare, E. Marchetti, M. Cherniakov, and M. Gashinova, “Next generation, low-THz automotive radar—The potential for frequencies above 100 GHz,” in *Proc. 20th Int. Radar Symp. (IRS)*, Jun. 2019, pp. 1–7.

- D. M. Pozar, *Microwave Engineering: Theory and Techniques*. Hoboken, NJ, USA: Wiley, 2021.

- M. I. Skolnik, *Introduction to Radar Systems*, vol. 3. New York, NY, USA: McGraw-Hill, 1980.

- H. S. Son, J. Y. Jang, D. M. Kang, H. J. Lee, and C. S. Park, “A 109 GHz CMOS power amplifier with 15.2 dBm PSAT and 20.3 dB gain in 65-nm CMOS technology,” *IEEE Microw. Wireless Compon. Lett.*, vol. 26, no. 7, pp. 510–512, Jul. 2016.

- A. E. Jarihani, S. Sarafi, M. Köberle, J. Sturm, and A. M. Tonello, “Characterization of on-chip interconnects: Case study in 28 nm CMOS technology,” in *Proc. Austrochip Workshop Microelectron. (Austrochip)*, Oct. 2019, pp. 93–99.

- M. H. Maktoomi, S. Saadat, O. Momeni, P. Heydari, and H. Aghasi, “Broadband antenna design for terahertz communication systems,” *IEEE Access*, vol. 11, pp. 20897–20911, 2023.

- S. Samala, “Signal processing and frequency generation in FMCW RADAR,” in *Proc. IEEE Custom Integr. Circuits Conf. (CICC)*, Apr. 2018, pp. 1–73.

- I. V. Komarov and S. M. Smolskiy, *Fundamentals Short-Range FM Radar*. Norwood, MA, USA: Artech House, 2003.

[25] A. Bourdoux et al., "A CMOS-based 140 GHz 4x4 MIMO radar prototype with 10 GHz bandwidth," in *Proc. 24th Int. Radar Symp. (IRS)*, May 2023, pp. 1–10.

[26] C. Xu et al., "A packaged 54-to-69-GHz wideband 2T2R FMCW radar transceiver employing cascaded-PLL topology and PTAT-enhanced temperature compensation in 40-nm CMOS," *IEEE J. Solid-State Circuits*, vol. 59, no. 10, pp. 3156–3171, Oct. 2024.

[27] H. Jia et al., "A 77 GHz frequency doubling two-path phased-array FMCW transceiver for automotive radar," *IEEE J. Solid-State Circuits*, vol. 51, no. 10, pp. 2299–2311, Oct. 2016.

[28] T. Ma et al., "A CMOS 76–81-GHz 2-TX 3-RX FMCW radar transceiver based on mixed-mode PLL chirp generator," *IEEE J. Solid-State Circuits*, vol. 55, no. 2, pp. 233–248, Feb. 2020.

[29] A. Townley et al., "A 94-GHz 4TX–4RX phased-array FMCW radar transceiver with antenna-in-package," *IEEE J. Solid-State Circuits*, vol. 52, no. 5, pp. 1245–1259, May 2017.

[30] A. Ahmed, L. Li, M. Jung, and G. M. Rebeiz, "A 140 GHz FMCW ultra wideband high dynamic range RADAR utilizing 8x8 phased arrays," in *IEEE MTT-S Int. Microw. Symp. Dig.*, Jun. 2024, pp. 489–492.

[31] X. Chen et al., "A 140-GHz FMCW TX/RX-antenna-sharing transceiver with low-inherent-loss duplexing and adaptive self-interference cancellation," *IEEE J. Solid-State Circuits*, vol. 57, no. 12, pp. 3631–3645, Dec. 2022.

[32] S. C. Rengifo, F. Chicco, E. L. Roux, and C. Enz, "An ultralow power short-range 60-GHz FMCW radar in 22-nm FDSOI CMOS," *IEEE Trans. Microw. Theory Techn.*, vol. 72, no. 4, pp. 2548–2559, Apr. 2024.

[33] A. Mostajeran et al., "A high-resolution 220-GHz ultra-wideband fully integrated ISAR imaging system," *IEEE Trans. Microw. Theory Techn.*, vol. 67, no. 1, pp. 429–442, Jan. 2019.

[34] V. Kafedziski and G. Josifovski, "USRP implementation of a high resolution FMCW radar using a stepped chirp waveform," in *Proc. 31st Int. Conf. Syst., Signals Image Process. (IWSSIP)*, Jul. 2024, pp. 1–5.

[35] L. Zhang, Z. Qiao, M. Xing, Y. Li, and Z. Bao, "High-resolution ISAR imaging with sparse stepped-frequency waveforms," *IEEE Trans. Geosci. Remote Sens.*, vol. 49, no. 11, pp. 4630–4651, Nov. 2011.

[36] B. Razavi and R. Behzad, *RF Microelectronics*, vol. 2. New York, NY, USA: Prentice-Hall, 2012.

[37] H. Afzal, R. Abedi, R. Kananizadeh, P. Heydari, and O. Momeni, "An mm-wave scalable PLL-coupled array for phased-array applications in 65-nm CMOS," *IEEE Trans. Microw. Theory Techn.*, vol. 69, no. 2, pp. 1439–1452, Feb. 2021.

[38] S.-L. Jang, W.-C. Lai, G.-Y. Lin, and C. Y. Huang, "Injection-locked frequency divider with a resistively distributed resonator for wide-locking-range performance," *IEEE Trans. Microw. Theory Techn.*, vol. 67, no. 2, pp. 505–517, Feb. 2019.

[39] F. Centurelli, G. Scotti, and G. Palumbo, "A very-low-voltage frequency divider in folded MOS current mode logic with complementary n- and p-type flip-flops," *IEEE Trans. Very Large Scale Integr. (VLSI) Syst.*, vol. 29, no. 5, pp. 998–1008, May 2021.

[40] K. Hadipour, A. Ghilioni, A. Mazzanti, M. Bassi, and F. Svelto, "A 40 GHz to 67 GHz bandwidth 23dB gain 5.8dB maximum NF mm-wave LNA in 28nm CMOS," in *Proc. IEEE Radio Freq. Integr. Circuits Symp. (RFIC)*, May 2015, pp. 327–330.

[41] B. Razavi, "Lower bounds on power consumption of clock generators for ADCs," in *Proc. IEEE Int. Symp. Circuits Syst. (ISCAS)*, Oct. 2020, pp. 1–5.

[42] X. Yi, C. Wang, X. Chen, J. Wang, J. Grajal, and R. Han, "A 220-to-320-GHz FMCW radar in 65-nm CMOS using a frequency-comb architecture," *IEEE J. Solid-State Circuits*, vol. 56, no. 2, pp. 327–339, Feb. 2021.

[43] B. Moradi, X. Liu, M. M. Green, and H. Aghasi, "A compact CMOS 76–82 GHz super-harmonic VCO with 189 dBc/Hz FoM operating based on harmonic-assisted ISF manipulation," in *Proc. IEEE Radio Freq. Integr. Circuits Symp. (RFIC)*, Jun. 2022, pp. 215–218.

[44] S. A.-R. Ahmadi-Mehr, M. Tohidian, and R. B. Staszewski, "Analysis and design of a multi-core oscillator for ultra-low phase noise," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 63, no. 4, pp. 529–539, Apr. 2016.

[45] L. Iotti, A. Mazzanti, and F. Svelto, "Insights into phase-noise scaling in switch-coupled multi-core LC VCOs for E-band adaptive modulation links," *IEEE J. Solid-State Circuits*, vol. 52, no. 7, pp. 1703–1718, Jul. 2017.

[46] W. L. Chan and J. R. Long, "A 58–65 GHz neutralized CMOS power amplifier with PAE above 10% at 1-V supply," *IEEE J. Solid-State Circuits*, vol. 45, no. 3, pp. 554–564, Mar. 2010.

[47] D. Pan et al., "A 77-GHz power amplifier with digital power control for multi-mode automotive radar in 28-nm bulk CMOS," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 70, no. 3, pp. 875–879, Mar. 2023.

[48] V.-S. Trinh and J.-D. Park, "Common-mode stability test and design guidelines for a transformer-based push-pull power amplifier," *IEEE Access*, vol. 8, pp. 42243–42250, 2020.

[49] Z. Wang and P. Heydari, "A study of operating condition and design methods to achieve the upper limit of power gain in amplifiers at near- $f_{max}$  frequencies," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 64, no. 2, pp. 261–271, Feb. 2017.

[50] M. Sayginer and G. M. Rebeiz, "A W-band LNA/phase shifter with 5-dB NF and 24-mW power consumption in 32-nm CMOS SOI," *IEEE Trans. Microw. Theory Techn.*, vol. 66, no. 4, pp. 1973–1982, Apr. 2018.

[51] L. Gao, E. Wagner, and G. M. Rebeiz, "Design of E- and W-band low-noise amplifiers in 22-nm CMOS FD-SOI," *IEEE Trans. Microw. Theory Techn.*, vol. 68, no. 1, pp. 132–143, Jan. 2020.

[52] T. Murakami, N. Hasegawa, Y. Utagawa, T. Arai, and S. Yamaura, "A 9 dB noise figure fully integrated 79 GHz automotive radar receiver in 40 nm CMOS technology," in *Proc. IEEE Radio Freq. Integr. Circuits Symp. (RFIC)*, Jun. 2019, pp. 307–310.

[53] H. Wang, H. Afzal, and O. Momeni, "A highly accurate and sensitive mmWave displacement-sensing Doppler radar with a quadrature-less edge-driven phase demodulator," *IEEE J. Solid-State Circuits*, vol. 58, no. 9, pp. 2451–2465, Sep. 2023.

[54] S. Zhou and M.-C.-F. Chang, "A CMOS passive mixer with low flicker noise for low-power direct-conversion receiver," *IEEE J. Solid-State Circuits*, vol. 40, no. 5, pp. 1084–1093, May 2005.

[55] M. Kalantari, W. Li, H. Shirinabadi, A. Fotowat-Ahmady, and C. P. Yue, "A W-band single-antenna FMCW radar transceiver with adaptive leakage cancellation," *IEEE J. Solid-State Circuits*, vol. 56, no. 6, pp. 1655–1667, Jun. 2021.

[56] I. Nasr et al., "A highly integrated 60 GHz 6-channel transceiver with antenna in package for smart sensing and short-range communications," *IEEE J. Solid-State Circuits*, vol. 51, no. 9, pp. 2066–2076, Sep. 2016.

[57] E. Öztürk et al., "A 60 GHz SiGe BiCMOS monostatic transceiver for radar applications," in *IEEE MTT-S Int. Microw. Symp. Dig.*, Jun. 2017, pp. 1408–1411.

[58] J. Rimmelspacher, R. Ciocoveanu, G. Steffan, M. Bassi, and V. Issakov, "Low power low phase noise 60 GHz multichannel transceiver in 28 nm CMOS for radar applications," in *Proc. IEEE Radio Freq. Integr. Circuits Symp. (RFIC)*, Los Angeles, CA, USA, Aug. 2020, pp. 19–22.

**Xuyang Liu** (Graduate Student Member, IEEE) received the B.S. degree in electronic information engineering from Jilin University, Changchun, China, in 2018, and the M.S. degree in electrical engineering from Columbia University, New York, NY, USA, in 2019. He is currently pursuing the Ph.D. degree in electrical engineering with the University of California at Irvine, Irvine, CA, USA.

In summer 2023, he interned at Marvell Technology, Santa Clara, CA, USA, where he characterized ring VCO and PLL. His research focuses on VCOs, frequency synthesizers, and FMCW radar front-end design.

Mr. Liu serves as a reviewer for IEEE JOURNAL OF SOLID-STATE CIRCUITS (JSSC) and IEEE TRANSACTIONS ON MICROWAVE THEORY AND TECHNIQUES (TMTT).

**Md. Hayyatullah Maktoomi** (Graduate Student Member, IEEE) received the B.Eng. degree in electronics and communication from Jamia Millia Islamia, New Delhi, India, in 2015, and the M.S. degree in electrical engineering from Washington State University, Vancouver, WA, USA in 2020. He is currently pursuing the Ph.D. degree with the University of California at Irvine, Irvine, CA, USA.

From 2016 to 2017, he was an Intern and a Research Assistant at IIT Delhi, New Delhi, where he was involved in research on passive RF/microwave circuits. In summer 2019, he joined the Research and Development Department, Wolfspeed Inc., Morgan Hill, CA, USA, as an RF Engineering Intern. In summer 2023, he interned at Qorvo Inc., Chelmsford, MA, USA, as an RF Design Intern. His current research is focused on RF/millimeter-wave integrated circuits.

Mr. Maktoomi was a recipient of the 2023 IEEE MTT-S Graduate fellowship. He was also a recipient of the 2022 IEEE Custom Integrated Circuits Conference (CICC) Education Award. He serves as a reviewer for *IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS—II: EXPRESS BRIEFS*, *IET Microwaves Antennas & Propagation*, *IET Electronics Letters*, and *Progress in Electromagnetics Research*.

**Mahdi Alesheikh** (Graduate Student Member, IEEE) received the B.Sc. degree in electrical engineering from the Sharif University of Technology, Tehran, Iran, and the M.S. degree in electrical and computer engineering from the University of Alberta, Edmonton, AB, Canada. He is currently pursuing the Ph.D. degree with the University of California at Irvine, Irvine, CA, USA.

In summer 2023, he joined Litrinium Inc., Mission Viejo, CA, USA, as an Analog Design Engineering Intern. In summer 2024, he joined the Research and Development Department at MFlex Inc., Irvine, as an RF Engineering Intern. His current research focuses on analog and mixed-signal integrated circuits, high-frequency and RF integrated circuit design, and wireless communication systems and circuits.

Mr. Alesheikh serves as a reviewer for more than ten different journals, including *IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS—I: REGULAR PAPERS*, *IEEE TRANSACTIONS ON TERAHERTZ SCIENCE AND TECHNOLOGY*, and *IEEE SENSORS JOURNAL*, among others.

**Payam Heydari** (Fellow, IEEE) received the B.S. and M.S. degrees in electrical engineering from the Sharif University of Technology, Tehran, Iran, in 1992 and 1995, respectively, and the Ph.D. degree from the University of Southern California, Los Angeles, CA, USA, in 2001.

He is currently the Henry Samueli Faculty Excellence Professor and the University Chancellor's Professor at the University of California at Irvine (UCI), Irvine, CA, USA. He is the Director of the Nanoscale Communication Integrated Circuits (NCIC) Laboratory. He is the (co)-author of two books, three book chapters, and more than 200 journal and conference papers. The primary focus of his research is on mixed-signal, analog, radio frequency, millimeter-wave, and terahertz integrated circuit design.

Dr. Heydari is a fellow of the National Academy of Inventors. He was the first-place co-winner for the IEEE Engineering in Medicine and Biology Conference (EMBC) 2024 Young Professional Paper Competition for their EMBC 2024 paper on brain-machine interfaces (BMI). He serves on the Technical Program Committee (TPC) of the IEEE International Microwave Symposium (IMS), and was a TPC Member for the International Solid-State Circuits Conference (ISSCC), the IEEE European Solid-State Circuits Conference (ESSCIRC), and CICC. From 2018 to 2020, he was the AdCom Member of the IEEE SSCS. He was a co-recipient of the 2024 IEEE Circuits and Systems Society Darlington Best Paper Award, and was a recipient of the 2023 IEEE MTT-S Distinguished Educator Award, the 2021 IEEE SSCS Innovative Education Award, and the Best Invited Paper Award at the 2021 IEEE Custom Integrated Circuits Conference (CICC). He was

selected as the inaugural Faculty Innovation Fellow by the UCI's Beall Applied Innovation. He was a recipient of the 2016–2017 UCI School of Engineering Mid-Career Excellence in Research, the 2014 Distinguished Engineering Educator Award from Orange County Engineering Council, the 2010 Faculty of the Year Award from UCI's Engineering Student Council (ESC), the 2009 Business Plan Competition First Place Prize Award and Best Concept Paper Award both from Paul Merage School of Business at UCI, the 2009 School of Engineering Fariborz Maseeh Best Faculty Research Award, the 2007 IEEE Circuits and Systems Society Guillemin-Cauer Award, the 2005 IEEE Circuits and Systems Society Darlington Best Paper Award, the 2005 National Science Foundation (NSF) CAREER Award, the 2005 Henry Samueli School of Engineering Teaching Excellence Award, the Best Paper Award at the 2000 IEEE Int'l Conference on Computer Design (ICCD), and the 2001 Technical Excellence Award from an Association of Professors and Scholars of Iranian Heritage (APSIH). His research on novel low-power multi-purpose multi-antenna RF front-ends received the Low-Power Design Contest Award at the 2008 IEEE Int'l Symposium on Low-Power Electronics and Design (ISLPED). He was an Associate Editor (AE) of *IEEE SOLID-STATE CIRCUITS LETTERS (SSC-L)* and *IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS—I: REGULAR PAPERS (TCAS-I)*. He is an AE of *IEEE JOURNAL OF SOLID-STATE CIRCUITS (JSSC)* and *IEEE OPEN JOURNAL OF THE SOLID-STATE CIRCUITS SOCIETY (OJ-SSCS)*. He served as a Distinguished Lecturer of both the IEEE Solid-State Circuits Society (SSCS) (2014–2016) and the IEEE Microwave Theory and Technology Society (MTT-S) (2019–2022).

**Hamidreza Aghasi** (Senior Member, IEEE) received the B.Sc. degree in electrical engineering from the Sharif University of Technology, Tehran, Iran, in 2011, and the M.S. and Ph.D. degrees in electrical engineering from Cornell University, Ithaca, NY, USA, in 2015 and 2017, respectively.

In summer 2014, he was an Intern at Samsung Research America's Display Laboratory, San Jose, CA, USA. From 2017 to 2018, he was a Post-Doctoral Research Fellow at the University of Michigan, Ann Arbor, MI, USA, and from 2018 to 2019, he was a mm-wave Research Scientist at Acacia Communications Inc., Holmdel, NJ, USA. He is currently an Assistant Professor with the Electrical Engineering and Computer Science Department, University of California at Irvine (UC Irvine), Irvine, CA, USA, where he is Director of the High-Speed Integrated Electronics (HIE) Laboratory. His research interests include RF, mm-wave, and terahertz circuit design for imaging, sensing, and communication applications.

Dr. Aghasi is a member of the Solid-State Circuits Society (SSCS) and the Microwave Theory and Techniques Society (MTT-S), a TPC Member of the IEEE Custom Integrated Circuit Conference (CICC) and the IEEE Radio Frequency Integrated Circuits Symposium (RFIC). He also serves as the IEEE MTT-S/EDS Chapter Chair for Orange County, CA. He has reviewed for *IEEE JOURNAL OF SOLID-STATE CIRCUITS*, *IEEE OPEN JOURNAL OF THE SOLID-STATE CIRCUITS*, *IEEE SOLID-STATE CIRCUITS LETTERS*, *IEEE TRANSACTIONS ON MICROWAVE THEORY AND TECHNIQUES*, *IEEE TRANSACTIONS ON VERY LARGE SCALE INTEGRATION (VLSI) SYSTEMS*, *IEEE ELECTRON DEVICE LETTERS*, *IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS—I: REGULAR PAPERS*, and *IEEE MICROWAVE AND WIRELESS COMPONENTS LETTERS*. He received the Cornell Graduate Fellowship in 2011, the Jacobs Fellowship in 2012, the Cornell ECE Innovation Award in 2013, the Cornell Scale-up and Prototyping Award in 2017, the NeurIPS ML4PS Reproducibility Award in 2024, and the NSF CAREER Award in 2025. He was the author of an “Article in Focus” in *IEEE Transactions on Nanotechnology* in 2016 and received the Best Invited Paper Award at the 2019 IEEE CICC. He is an Associate Editor of *IEEE TRANSACTIONS ON VERY LARGE SCALE INTEGRATION (TVLSI)*.