# Extension Doping with Low-Resistance Contacts for P-Type Monolayer WSe<sub>2</sub> Field-Effect Transistors

Sihan Chen,\* Yue Zhang, William P. King, Rashid Bashir,\* and Arend M. van der Zande\*

**Source/Drain extension doping is crucial for minimizing the series resistance of the ungated channel and reducing the contact resistance of field-effect transistors (FETs) in complementary metal–oxide–semiconductor (CMOS) technology. 2D semiconductors, such as MoS<sub>2</sub> and WSe<sub>2</sub>, are promising channel materials for beyond-silicon CMOS. A key challenge is to achieve extension doping for 2D monolayer FETs without damaging the atomically thin material. This work demonstrates extension doping with low-resistance contacts for monolayer WSe<sub>2</sub> p-FETs. Self-limiting oxidation transforms a bilayer WSe<sub>2</sub> into a hetero-bilayer of a high-work-function WO<sub>x</sub>Se<sub>y</sub> on a monolayer WSe<sub>2</sub>. Then, damage-free nanolithography defines an undoped nano-channel, preserving the high on-current of WO<sub>x</sub>Se<sub>y</sub>-doped FETs while significantly improving their on/off ratio. The insertion of an amorphous WO<sub>x</sub>Se<sub>y</sub> interlayer under the contacts achieves record-low contact resistances for monolayer WSe<sub>2</sub> over a hole density range of 10<sup>12</sup> to 10<sup>13</sup> cm<sup>-2</sup> (1.2 ± 0.3 kΩ μm at 10<sup>13</sup> cm<sup>-2</sup>). The WO<sub>x</sub>Se<sub>y</sub>-doped extension exhibits a sheet resistance as low as 10 ± 1 kΩ □<sup>-1</sup>. Monolayer WSe<sub>2</sub> p-FETs with sub-50 nm channel lengths reach a maximum drain current of 154 μA μm<sup>-1</sup> with an on/off ratio of 10<sup>7</sup>–10<sup>8</sup>. These results define strategies for nanometer-scale selective-area doping in 2D FETs and other 2D architectures.**

## 1. Introduction

Doping the source/drain extensions is essential for optimizing the performance of field-effect transistors (FETs)

in complementary metal–oxide–semiconductor (CMOS) technology. In CMOS, the top-gate underlaps the source/drain to minimize parasitic capacitance for fast operation. The source/drain extensions are ungated and must be heavily doped to minimize their series resistance.<sup>[1]</sup> Additionally, extension doping lowers the metal–semiconductor contact resistance<sup>[2,3]</sup> and adjusts the threshold voltage.<sup>[4,5]</sup> Monolayers of 2D semiconductors, including transition metal dichalcogenides (TMDs) such as MoS<sub>2</sub> and WSe<sub>2</sub>, represent the ultimate channels in transistor scaling, due to their atomically thin bodies and dangling-bond-free surfaces.<sup>[6]</sup> However, contact resistance remains one of the major technical hurdles to realizing 2D FETs in CMOS,<sup>[6]</sup> and more broadly across applications in electronic and optoelectronic devices from 2D materials and heterostructures.<sup>[7]</sup> While n-type contacts to TMD monolayers close to the quantum limit have been demonstrated,<sup>[8]</sup>

achieving low-resistance contacts to p-type monolayer 2D semiconductors remains challenging, especially when approaching nanometer-scale dimensions.<sup>[9]</sup> Developing new strategies to design nanometer-scale extension doping into monolayer 2D

S. Chen, W. P. King, R. Bashir, A. M. van der Zande

Holonyak Micro and Nanotechnology Laboratory

The Grainger College of Engineering

University of Illinois Urbana-Champaign

Urbana, IL 61801, USA

E-mail: schen141@illinois.edu; rbashir@illinois.edu; arendv@illinois.edu

Y. Zhang, W. P. King, R. Bashir, A. M. van der Zande

Department of Mechanical Science and Engineering

The Grainger College of Engineering

University of Illinois Urbana-Champaign

Urbana, IL 61801, USA

W. P. King, R. Bashir, A. M. van der Zande

Department of Materials Science and Engineering

The Grainger College of Engineering

University of Illinois Urbana-Champaign

Urbana, IL 61801, USA

W. P. King, R. Bashir, A. M. van der Zande

Materials Research Laboratory

The Grainger College of Engineering

University of Illinois Urbana-Champaign

Urbana, IL 61801, USA

R. Bashir

Department of Bioengineering

The Grainger College of Engineering

University of Illinois Urbana-Champaign

Urbana, IL 61801, USA

The ORCID identification number(s) for the author(s) of this article can be found under <https://doi.org/10.1002/aelm.202400843>

© 2024 The Author(s). Advanced Electronic Materials published by Wiley-VCH GmbH. This is an open access article under the terms of the Creative Commons Attribution License, which permits use, distribution and reproduction in any medium, provided the original work is properly cited.

DOI: 10.1002/aelm.202400843

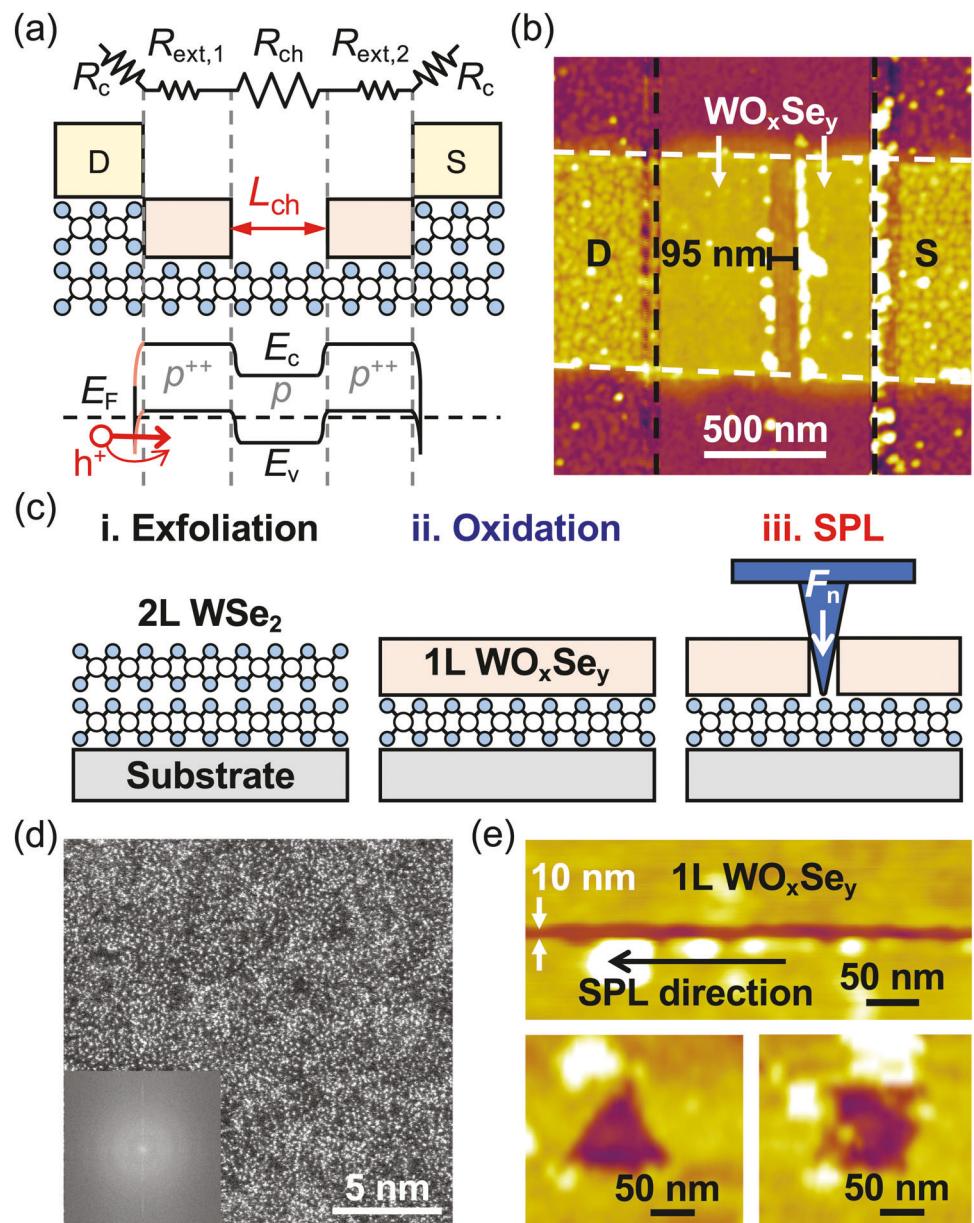

**Figure 1.** Concept of a monolayer  $WSe_2$  p-FET with doped extensions based on self-limiting oxidation and nanolithography. a) Equivalent circuit (top), schematic (middle), and band diagram (bottom) of a monolayer  $WSe_2$  p-FET with  $WO_xSe_y$ -doped extensions. The dashed black lines delineate the boundaries of the source (S) and drain (D), while the dashed white lines outline the edges of the  $WSe_2$ . c) Schematic showing the fabrication process of selectively  $WO_xSe_y$ -doped monolayer  $WSe_2$ . d) HAADF-STEM image of a freestanding monolayer  $WO_xSe_y$  film and the corresponding FFT pattern. e) Examples of nanopatterns of 1L  $WO_xSe_y$  on 1L  $WSe_2$  created by mechanical SPL.

semiconductors is a critical step in minimizing source/drain extension resistance and contact resistance, thereby realizing the potential of 2D semiconductors as channel materials in beyond-silicon CMOS.

Unfortunately, conventional doping techniques used in CMOS, such as ion implantation or substitutional doping, do not work well with 2D monolayer semiconductors, because of the creation of defects that damage the delicate atomic structure,<sup>[10–12]</sup> the difficulty of achieving selective doping,<sup>[13–16]</sup> or elevated processing temperatures that surpass the thermal

budget of silicon back-end-of-line integration (< 400 °C).<sup>[17–19]</sup> Surface charge transfer doping (SCTD), which relies on the charge transfer between the channel material and the surface dopant is a promising approach for extension doping in 2D FETs, due to its low processing temperature and effectiveness to dope surface materials without inducing defects.<sup>[20]</sup> Various chemical and physical deposition based SCTD methods have been explored for TMDs.<sup>[21–29]</sup> One particularly promising strategy is oxidizing the surface of TMDs like  $WSe_2$  with  $O_2$  plasma or UV/ozone to form a self-limiting oxide layer

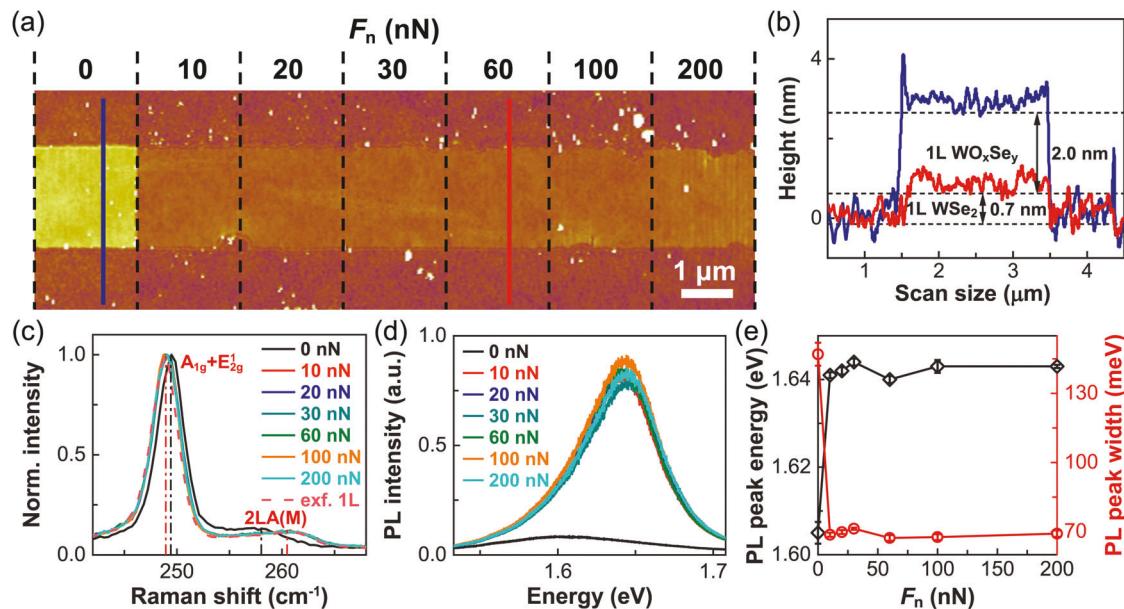

**Figure 2.** Exploring the optimal SPL force for AFM scratching of 1L  $\text{WO}_x\text{Se}_y$  on 1L  $\text{WSe}_2$ . a) AFM topography of 1L  $\text{WO}_x\text{Se}_y$  on 1L  $\text{WSe}_2$  after SPL with a normal force  $F_n$  of 0 to 200 nN. b) Line scans along the solid blue and red lines in (a). c) Normalized Raman spectra and d) PL spectra of 1L  $\text{WSe}_2$  from different regions in (a). The dashed pink line corresponds to the normalized Raman spectrum of pristine as-exfoliated (exf.) 1L  $\text{WSe}_2$ . e) PL peak energy and peak width extracted from the PL spectra in (d) versus  $F_n$ .

such as  $\text{WO}_x$  and  $\text{WO}_x\text{Se}_y$  on top of undamaged layers.<sup>[30–36]</sup> These high-work-function oxides generate strong hole doping in the underlying channel material,<sup>[30–33]</sup> yet are stable in air for months,<sup>[31–33]</sup> and are CMOS-compatible.<sup>[33,37,38]</sup> Key questions include how to realize oxidation-based selective-area doping for TMD monolayers, and how extension doping impacts the sheet and contact resistances and the overall FET performance in the technology-relevant short channel limit.

In this study, we demonstrate extension doping with low-resistance contacts for p-type monolayer  $\text{WSe}_2$  FETs by combining self-limiting oxidation with nanolithography. Using damage-free nanolithography, we create short-channel monolayer  $\text{WSe}_2$  p-FETs with doped extensions, preserving the high on-current of  $\text{WO}_x\text{Se}_y$ -doped FETs while significantly improving their on/off ratio. We systematically characterize the sheet resistance of doped extensions and contact resistance using the transfer length method. We find that inserting a monolayer of amorphous  $\text{WO}_x\text{Se}_y$  between evaporated metal contacts and monolayer  $\text{WSe}_2$  reduces the contact resistance by over an order of magnitude. One monolayer  $\text{WSe}_2$  p-FET reaches a record-high drain current of  $> 150 \mu\text{A} \mu\text{m}^{-1}$  under a 1 V drain-source bias at a hole density below  $10^{13} \text{ cm}^{-2}$ . These achievements the performance gap between p-type and n-type 2D monolayer transistors, demonstrating a promising route to realizing beyond-silicon electronics and optoelectronics with 2D monolayers and heterostructures.

## 2. Results and Discussion

### 2.1. Extension Doping

Figure 1 illustrates the concept of extension doping for monolayer  $\text{WSe}_2$  FETs by integrating self-limiting oxidation with

nanolithography. Figure 1a depicts a monolayer  $\text{WSe}_2$  p-FET with  $\text{WO}_x\text{Se}_y$ -doped extensions. The total resistance consists of the channel resistance ( $R_{\text{ch}}$ ), source/drain extension resistances ( $R_{\text{ext},1} + R_{\text{ext},2}$ ), and contact resistances ( $2R_c$ ) in series. The monolayer  $\text{WSe}_2$  channel exhibits light p-doping,<sup>[39]</sup> while the source/drain extensions are degenerately p-doped due to the high-work-function  $\text{WO}_x\text{Se}_y$  withdrawing electrons from the underlying monolayer  $\text{WSe}_2$ .<sup>[31,32]</sup> This results in energy bands bending near the metal-semiconductor junction, reducing the Schottky barrier width. Extension doping with  $\text{WO}_x\text{Se}_y$  serves to reduce both extension and contact resistances, enhancing the electrical performance of monolayer  $\text{WSe}_2$  p-FETs. Figure 1b shows the atomic force microscopy (AFM) topography of an example monolayer  $\text{WSe}_2$  p-FET with  $\text{WO}_x\text{Se}_y$ -doped extensions. The channel length  $L_{\text{ch}}$  is  $95 \pm 5 \text{ nm}$ , and the sum of the lengths of the source/drain extensions  $L_{\text{ext}}$  is  $740 \pm 20 \text{ nm}$ . The electrical characteristics of the FET are discussed in detail in Figure 3.

Figure 1c illustrates the fabrication process for selectively doping monolayer  $\text{WSe}_2$  with  $\text{WO}_x\text{Se}_y$ . All process details are in the Methods. First, bilayer (2L)  $\text{WSe}_2$  is exfoliated onto a substrate (i). The topmost layer of  $\text{WSe}_2$  is then oxidized using a controlled remote  $\text{O}_2$  plasma process, forming a monolayer (1L) p-dopant  $\text{WO}_x\text{Se}_y$  on top of 1L  $\text{WSe}_2$  (ii). Finally, mechanical scanning probe lithography (SPL) is used to selectively remove 1L  $\text{WO}_x\text{Se}_y$  from 1L  $\text{WSe}_2$  (iii). In mechanical SPL, an AFM probe scratches the surface material in contact mode with a normal force  $F_n$ .<sup>[40–42]</sup> As we will show in Figure 2, the significant difference in mechanical strength between  $\text{WO}_x\text{Se}_y$  and  $\text{WSe}_2$  allows for precise patterning by removing the top  $\text{WO}_x\text{Se}_y$  without damaging the underlying  $\text{WSe}_2$ . The removed  $\text{WO}_x\text{Se}_y$  accumulates along the boundaries of the scanned region. We choose mechanical SPL over additive lithography methods, such as optical and e-beam lithography, because the resist materials used in additive

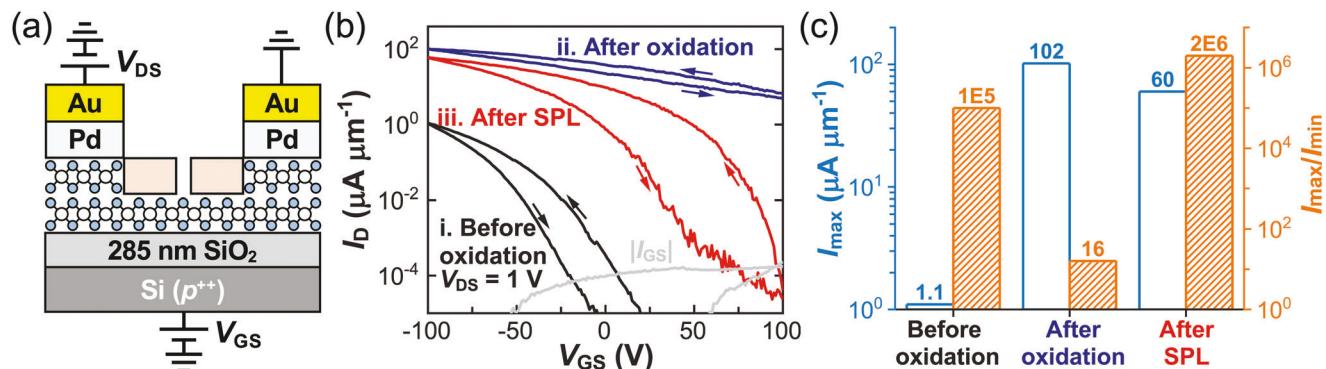

**Figure 3.** Example monolayer WSe<sub>2</sub> p-FET (Device A) with WO<sub>x</sub>Se<sub>y</sub>-doped extensions. a) Schematic of the electrical connections used to characterize the FET. b) Transfer curves of the FET before oxidation, after oxidation, and after SPL.  $V_{DS} = 1$  V. The gray line plots the gate leakage  $|I_{GS}|$  of the FET measured after SPL. c)  $I_{\max}$  and  $I_{\max}/I_{\min}$  at each stage of fabrication.

lithography are difficult to remove and degrade the p-doping effect of oxidized TMDs.<sup>[43,44]</sup>

Spectroscopy measurements in Figure S1 (Supporting Information) confirm the oxidation process is self-limiting to the top-most layer of WSe<sub>2</sub>. X-ray photoelectron spectroscopy (XPS) spectra in Figure S2 (Supporting Information) reveal the appearance of both W–O and Se–O bonds after oxidation, indicating the formation of WO<sub>x</sub>Se<sub>y</sub> rather than pure WO<sub>x</sub>. Figure 1d shows a high-angle annular dark-field scanning transmission electron microscopy (HAADF-STEM) image and the corresponding fast Fourier transform (FFT) pattern of monolayer WO<sub>x</sub>Se<sub>y</sub>, which appears amorphous and homogeneous. The amorphous monolayer WO<sub>x</sub>Se<sub>y</sub> is insulating.<sup>[45]</sup> Figure 1e shows AFM topography images of nanopatterns of 1L WO<sub>x</sub>Se<sub>y</sub> on 1L WSe<sub>2</sub> fabricated using mechanical SPL with an  $F_n$  of 130 nN, with the narrowest constriction being  $\approx 10$  nm. Figure S3 (Supporting Information) shows a scanning electron microscopy (SEM) image of a typical SPL probe with a tip radius of  $14 \pm 1$  nm.

A key fabrication challenge for achieving extension doping with mechanical SPL is to determine the applied force capable of removing WO<sub>x</sub>Se<sub>y</sub> without damaging the underlying monolayer WSe<sub>2</sub>. The mechanical properties of amorphous 2D monolayers remain largely unexplored.<sup>[46,47]</sup> In Figure 2, we combine AFM with Raman and photoluminescence (PL) spectroscopy to investigate the optimal force for SPL. Raman and PL spectra of TMD monolayers are sensitive to defects, doping, and strain,<sup>[48–54]</sup> making them reliable indicators of the material properties of the underlying monolayer WSe<sub>2</sub>.

Figure 2a shows an AFM topography image of a single WSe<sub>2</sub> (bottom)/WO<sub>x</sub>Se<sub>y</sub> (top) hetero-bilayer microribbon, patterned with rectangles of sequentially increasing  $F_n$  from 0 to 200 nN. This data shows that even a moderate  $F_n$  of 10 nN is sufficient to scratch amorphous WO<sub>x</sub>Se<sub>y</sub>. We note that multiple SPL scans are required for complete removal. Five scans were needed to entirely remove WO<sub>x</sub>Se<sub>y</sub> with an  $F_n$  of 10–20 nN, and only 1–2 scans with an  $F_n$  of 30 nN or larger. Figure 2b shows the height profile from regions corresponding to  $F_n = 0$  nN and  $F_n = 60$  nN and reveals a thickness of  $0.7 \pm 0.1$  nm for 1L WSe<sub>2</sub> and  $2.0 \pm 0.1$  nm for 1L WO<sub>x</sub>Se<sub>y</sub>.

Figure 2c shows the normalized Raman spectra of monolayer WSe<sub>2</sub> from different regions in Figure 2a. The presence of both A<sub>1g</sub>+E<sub>2g</sub><sup>1</sup> and 2LA(M) peaks suggests the preservation of the crys-

talline structure of the underlying 1L WSe<sub>2</sub> after SPL with an  $F_n$  of 10–200 nN. With the removal of WO<sub>x</sub>Se<sub>y</sub>, the A<sub>1g</sub>+E<sub>2g</sub><sup>1</sup> peak redshifted by  $0.5$  cm<sup>-1</sup> while the 2LA(M) peak blueshifted by  $2.5$  cm<sup>-1</sup>, indicating reduced p-doping in WSe<sub>2</sub>.<sup>[51,52]</sup> These Raman peaks of 1L WSe<sub>2</sub> obtained after the removal of WO<sub>x</sub>Se<sub>y</sub> exhibit no shift compared to those of pristine as-exfoliated 1L WSe<sub>2</sub>, confirming that the WSe<sub>2</sub> remains undamaged by the self-limiting oxidation and SPL processes. Raman peak positions exhibit no additional dependence on  $F_n$  after SPL within the 10–200 nN range, suggesting negligible variations in material quality, doping, and strain.<sup>[51–54]</sup>

Figure S4 (Supporting Information) shows a map of the PL peak intensity corresponding to Figure 2a. Figure 2d presents the averaged PL spectra from the center of each region, while Figure 2e plots the fitted PL peak energy (black) and PL peak width (red) as a function of  $F_n$ . Figure 2e reveals that the PL peak blueshifted by  $37 \pm 1$  meV and the peak width decreased by  $78 \pm 1$  meV after SPL, reconfirming reduced p-doping to 1L WSe<sub>2</sub> following the removal of WO<sub>x</sub>Se<sub>y</sub>.<sup>[32]</sup> PL peak intensity, position, and width also exhibit no discernible dependence on  $F_n$  between 10 and 200 nN.

In summary, a normal force as small as 10 nN could scratch amorphous monolayer WO<sub>x</sub>Se<sub>y</sub>, but effective removal of WO<sub>x</sub>Se<sub>y</sub> begins at  $\approx 30$  nN. There is no noticeable damage to the underlying monolayer WSe<sub>2</sub> up to 200 nN, suggesting a much weaker shear strength of amorphous TMD monolayers compared to crystalline TMD monolayers, as well as weak adhesion between crystalline TMDs and their surface oxide. Hereafter, we used  $F_n = 40$ –60 nN for SPL in the FET fabrication shown below.

In Figure 3, we demonstrate the enhanced electrical performance of a WSe<sub>2</sub> FET with extension doping by comparing its transport characteristics at key steps of the fabrication process: i) as a bilayer WSe<sub>2</sub> FET before oxidization, ii) as a WSe<sub>2</sub> (bottom)/WO<sub>x</sub>Se<sub>y</sub> (top) hetero-bilayer after oxidation, and iii) after SPL patterning of the undoped nanochannel and extensions. Figure 3a illustrates the electrical connections used to characterize the FET. This FET corresponds to the device shown in Figure 1b. Figure 3b presents the  $I_D$ – $V_{GS}$  sweeps of the FET at key steps through the fabrication process. Figure 3c highlights two key metrics of a field-effect transistor at each key step: the maximum drain current  $I_{\max}$ , and the maximum-to-minimum current ratio  $I_{\max}/I_{\min}$ . As expected, the FET could not be turned

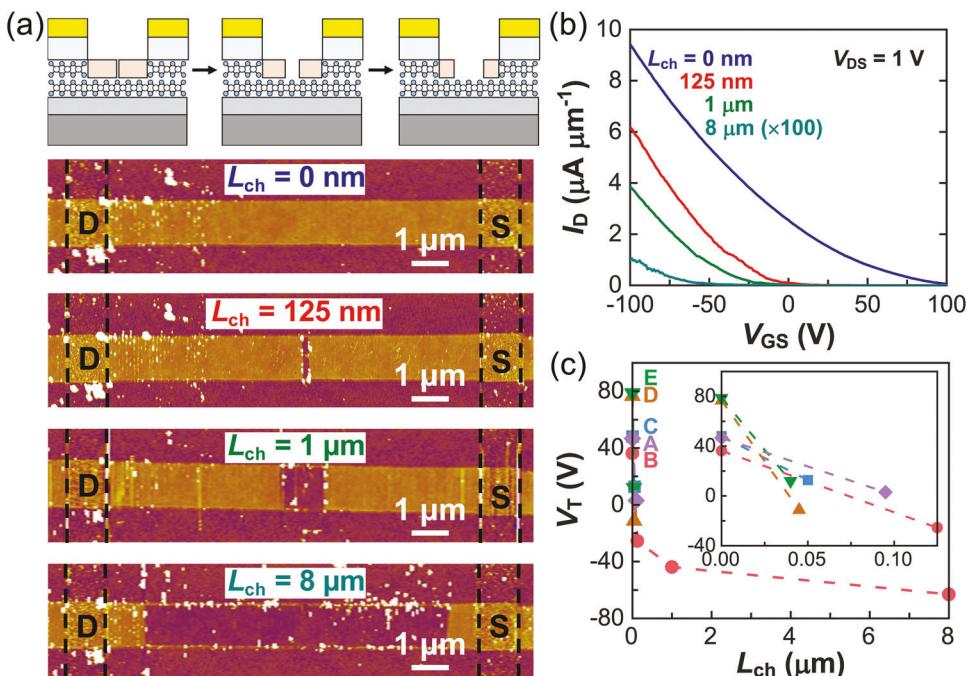

**Figure 4.** Tuning the threshold voltage. a) Schematic (top) and AFM topography (bottom) of a  $\text{WO}_x\text{Se}_y$ -doped monolayer  $\text{WSe}_2$  p-FET (Device B) with sequentially increased  $L_{ch}$  (from top to bottom). The dashed black lines delineate the edges of the source and drain. b) Transfer curves of the FET with different  $L_{ch}$ . c)  $V_T$  versus  $L_{ch}$ . The  $V_T$  versus  $L_{ch}$  data of other Devices reported in this work (Devices A, C-E) are also included in this plot for analysis.

off after oxidation, with  $I_{max}$  increasing by 100 times and the  $I_{max}/I_{min}$  ratio decreasing by  $10^4$ . SPL with an  $L_{ch}$  of  $95 \pm 5$  nm improved the  $I_{max}/I_{min}$  ratio by  $10^5$ , while slightly decreasing  $I_{max}$  by 40%. Overall, the monolayer  $\text{WSe}_2$  p-FET with  $\text{WO}_x\text{Se}_y$ -doped extensions exhibited an over one order of magnitude improvement in both  $I_{max}$  and  $I_{max}/I_{min}$  compared to the initial bilayer  $\text{WSe}_2$  FET. The hysteresis was 13.1 V before oxidation, 21.7 V after oxidation, and 38.9 V after SPL. The soft dipoles formed between  $\text{WO}_x\text{Se}_y$  and  $\text{WSe}_2$  may be affected by the backgate electric field, producing a large hysteresis loop during the backgate sweep.<sup>[23]</sup> In comparison, top-gated multilayer  $\text{WSe}_2$  FETs with  $\text{WO}_x\text{Se}_y$ -doped extensions have achieved negligible hysteresis, where the top-gate field was not applied to  $\text{WO}_x\text{Se}_y$  dopants.<sup>[33]</sup>

Achieving a threshold voltage  $V_T$  close to 0 V is crucial in CMOS. Many studies on 2D FETs have shown  $V_T$  values significantly deviating from 0 V, preventing the device from turning off at a gate voltage of 0 V.<sup>[55]</sup> Therefore, strategies to develop 2D n-FETs with a slightly positive threshold voltage and 2D p-FETs with a slightly negative threshold voltage are needed.<sup>[9]</sup> Figure 4 explores the proximity effects that tune the threshold voltage of a monolayer  $\text{WSe}_2$  p-FET by successively removing the surface dopant  $\text{WO}_x\text{Se}_y$  from the channel with SPL, which concurrently increases  $L_{ch}$  and decreases  $L_{ext}$ . Figure 4a presents the schematic and corresponding AFM images of the same FET, with  $L_{ch}$  increased from 0 nm to 8  $\mu$ m. Figure 4b compares the transfer characteristics of the same FET with different  $L_{ch}$ . Figure 4c shows the  $V_T$  versus  $L_{ch}$ . An  $L_{ch}$  near 50–100 nm achieved a  $V_T$  close to 0 V. The maximum  $\Delta V_T$  reached 99.4 V, demonstrating the potential to implement multiple  $V_T$  by adjusting  $L_{ch}$ .  $V_T$  decreased significantly when  $L_{ch}$  increased from 0 to 40–50 nm, suggesting that the effective lateral penetration depth of extension dop-

ing is much less than  $\approx 20$  nm. Figure S5 (Supporting Information) demonstrates that the  $\text{WO}_x\text{Se}_y$  doping was stable over several days in air, so the  $V_T$  drift during the experiment could be ignored.

## 2.2. Contact Engineering

Another crucial feature of extension doping is the contact resistance at the extension-electrode interface. Numerous studies have reported a significant reduction in contact resistance in TMD p-FETs following oxidation.<sup>[30–33,37,43,53,56]</sup> However, these studies typically involve the deposition of high-work-function metal contacts onto TMDs with high kinetic energy prior to oxidation, which inevitably causes defects at the metal/TMD interface and results in Fermi level pinning.<sup>[9,57]</sup> Introducing an ultrathin interlayer between evaporated metal contacts and the 2D semiconductors could mitigate metal-induced gap states, leading to Fermi level depinning.<sup>[58–62]</sup>

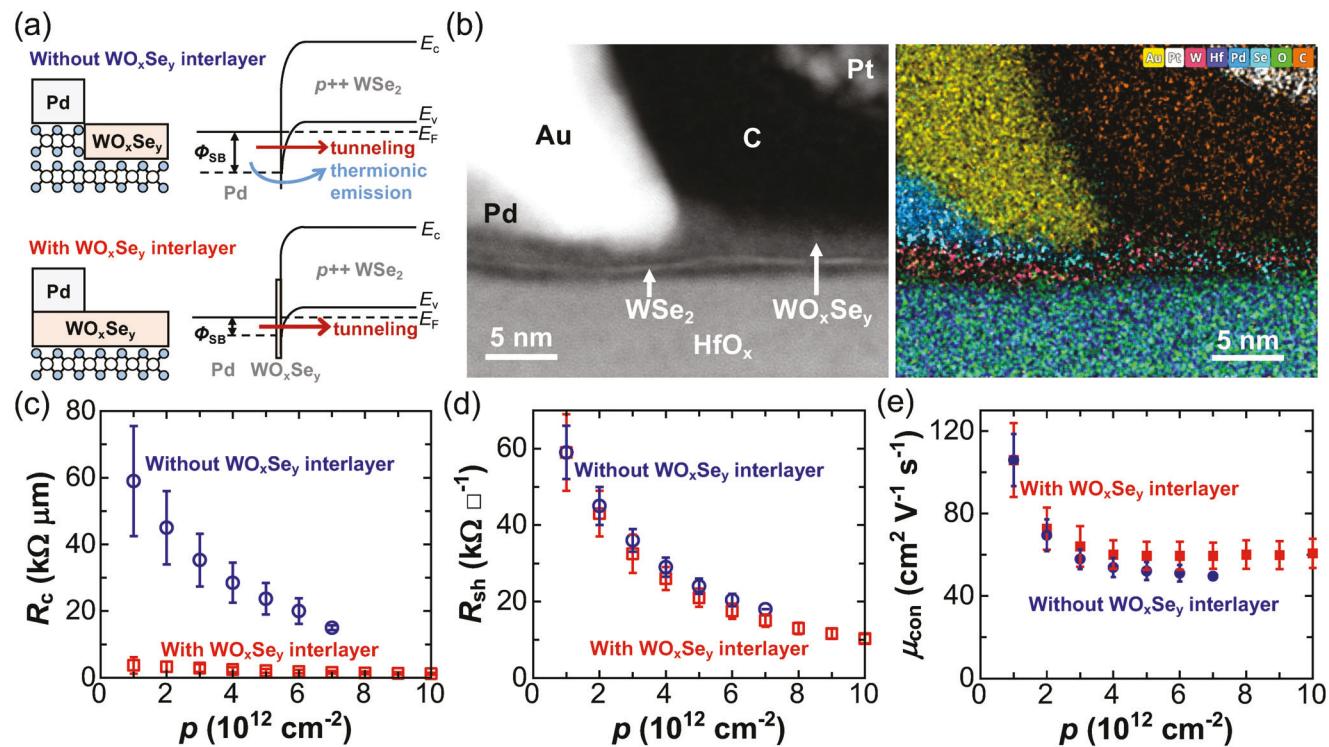

In Figure 5, we systematically compare different interface structures and processes to optimize the contacts. Figure 5a illustrates the out-of-plane structure and hypothesized band diagrams for two electrode contact configurations: one with a monolayer  $\text{WO}_x\text{Se}_y$  interlayer beneath the contacts and the other without. The former involves oxidizing  $\text{WSe}_2$  before metallization, while the latter is achieved by oxidation after metallization. Both configurations rely on doping the channel region near the contacts to reduce the Schottky barrier width, facilitating charge carrier tunneling and reducing contact resistance. Additionally, inserting a monolayer  $\text{WO}_x\text{Se}_y$  between  $\text{WSe}_2$  and the contacts diminishes metal-induced gap states, thereby lowering the

**Figure 5.** Contact resistance in  $\text{WO}_x\text{Se}_y$ -doped monolayer  $\text{WSe}_2$  FETs with and without a  $\text{WO}_x\text{Se}_y$  interlayer. a) Schematics and band diagrams of  $\text{WO}_x\text{Se}_y$ -doped monolayer  $\text{WSe}_2$  FETs without (top) and with (bottom) a  $\text{WO}_x\text{Se}_y$  interlayer between Pd and  $\text{WSe}_2$ . b) Cross-sectional HAADF-STEM image (left) of a  $\text{WO}_x\text{Se}_y$ -doped monolayer  $\text{WSe}_2$  FET with a  $\text{WO}_x\text{Se}_y$  interlayer, and the corresponding STEM EDS image (right). Pt and C are used for protection during focused ion beam (FIB) cutting. c) Contact resistance  $R_c$  versus  $p$ . d) Sheet resistance  $R_{sh}$  of monolayer  $\text{WSe}_2$  in source/drain extensions versus  $p$ . e) Conductivity mobility  $\mu_{con}$  versus  $p$ .

Schottky barrier height. Figure 5b shows the cross-sectional HAADF-STEM and energy dispersive spectroscopy (EDS) images of a  $\text{WO}_x\text{Se}_y$ -doped monolayer  $\text{WSe}_2$  FET with a  $\text{WO}_x\text{Se}_y$  interlayer. Interestingly, there is observable squeezing of the soft  $\text{WO}_x\text{Se}_y$  at the edge of the Pd/Au electrodes, suggesting that the amorphous  $\text{WO}_x\text{Se}_y$  interlayer also serves as a buffer that protects the underlying  $\text{WSe}_2$  from distortion caused by the evaporated metal contacts. Figure S6 (Supporting Information) shows additional cross-sectional STEM images of the same FET, confirming complete and self-limiting oxidation of the topmost  $\text{WSe}_2$  in both the channel and contact regions.

In comparison, a previous study found poor p-type performance in  $\text{WO}_x$ -doped  $\text{WSe}_2$  FETs with oxidation before metallization.<sup>[43]</sup> Shown in Figure S7 (Supporting Information), we also observed inferior electrical performance of  $\text{WO}_x\text{Se}_y$ -doped monolayer  $\text{WSe}_2$  FETs with oxidation before metallization, in agreement with that previous work. However, we leveraged the self-limiting nature of the oxidation process and re-oxidized these  $\text{WO}_x\text{Se}_y$ -covered monolayer  $\text{WSe}_2$  FETs after metallization. This addition of the re-oxidation process fully restored the p-doping effect of  $\text{WO}_x\text{Se}_y$  and improved the electrical performance of  $\text{WO}_x\text{Se}_y$ -doped monolayer  $\text{WSe}_2$  FETs with a  $\text{WO}_x\text{Se}_y$  interlayer beneath the contacts.

We used the transfer length method<sup>[63]</sup> (TLM) to extract and compare the electrode-extension contact resistances of  $\text{WO}_x\text{Se}_y$ -covered monolayer  $\text{WSe}_2$  FETs with and without a  $\text{WO}_x\text{Se}_y$  interlayer under the contacts. Figure S8 (Supporting Information)

shows the transfer curves, micrographs of the TLM structures, and the extraction of the contact resistance for each configuration. Figure 5c–e show the extracted electrode contact resistance  $R_c$ , extension sheet resistance  $R_{sh}$ , and conductivity mobility  $\mu_{con}$  versus carrier density  $p$ , respectively.

Figure 5c shows that the  $R_c$  with interlayer  $\text{WO}_x\text{Se}_y$  ranged from  $3.7 \pm 2.5 \text{ k}\Omega \mu\text{m}$  to  $1.2 \pm 0.3 \text{ k}\Omega \mu\text{m}$  over a hole density of  $10^{12}$ – $10^{13} \text{ cm}^{-2}$ , which is one order of magnitude lower than that without interlayer  $\text{WO}_x\text{Se}_y$ , ranging from  $59 \pm 17 \text{ k}\Omega \mu\text{m}$  to  $15 \pm 1 \text{ k}\Omega \mu\text{m}$  over  $(1\text{--}7) \times 10^{12} \text{ cm}^{-2}$ . A separate study found an  $R_c$  of  $40 \text{ k}\Omega \mu\text{m}$  for  $\text{WO}_x\text{Se}_y$ -doped monolayer  $\text{WSe}_2$  at  $p = 10^{13} \text{ cm}^{-2}$  without interlayer  $\text{WO}_x\text{Se}_y$ ,<sup>[32]</sup> aligning well with these results. Moreover, the  $R_c$  with interlayer  $\text{WO}_x\text{Se}_y$  shows a weaker dependence on carrier density compared to that without interlayer  $\text{WO}_x\text{Se}_y$ , indicating reduced Fermi-level pinning with a  $\text{WO}_x\text{Se}_y$  interlayer.<sup>[64]</sup>

In contrast, Figure 5d shows that  $R_{sh}$  of both configurations nearly overlap, with the same dependence on carrier density, despite the total resistances of these TLM structures differing by one order of magnitude (Figure S8, Supporting Information). This overlap indicates that i) the monolayer  $\text{WSe}_2$  channel is pristine and homogeneous, and ii) the oxidation process is indeed self-limiting and does not damage the underlying layer. As shown in Figure 5e, the monolayer  $\text{WSe}_2$  exhibited a high hole mobility of  $\approx 60 \text{ cm}^2 \text{V}^{-1} \text{s}^{-1}$  on a 3D oxide, suggesting minimal carrier scattering from  $\text{WO}_x\text{Se}_y$  doping and negligible damage to the underlying  $\text{WSe}_2$  during oxidation.

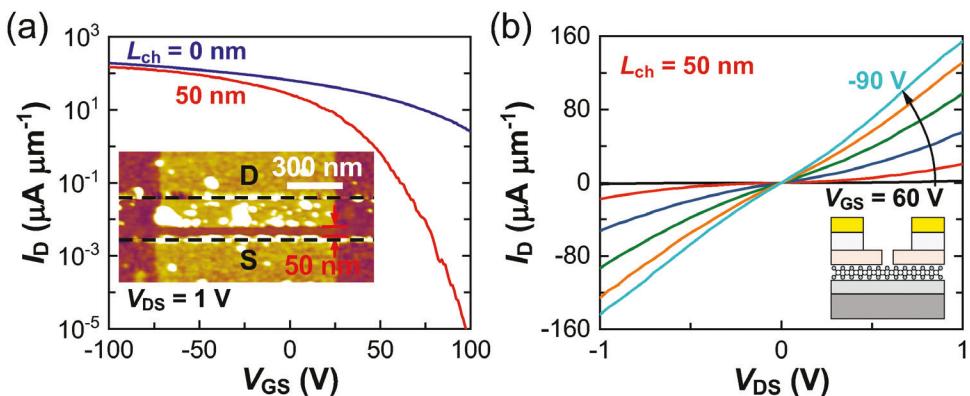

**Figure 6.** Electrical performance of a short-channel monolayer WSe<sub>2</sub> p-FET with WO<sub>x</sub>Se<sub>y</sub>-doped extensions (Device C). a) Transfer curves of the FET with  $L_{ch} = 0, 50$  nm.  $V_{DS} = 1$  V. Inset: AFM topography of the FET with  $L_{ch} = 50 \pm 5$  nm and  $L_{ext} = 150 \pm 5$  nm. The dashed black lines delineate the edges of the source and drain. b) Output curves of the FET with  $L_{ch} = 50$  nm. Inset: Schematic of the FET.

Compared to other contact interlayers such as hBN,<sup>[59]</sup> TMD,<sup>[61]</sup> and amorphous TiO<sub>2</sub>,<sup>[58]</sup> the WO<sub>x</sub>Se<sub>y</sub> interlayer is readily formed by CMOS-compatible self-limiting oxidation, with the potential to achieve wafer-scale uniformity. As shown in Figure S6 (Supporting Information), the WO<sub>x</sub>Se<sub>y</sub> contact interlayer was  $\approx 1$  nm thick,  $\approx 1$  nm thinner than the WO<sub>x</sub>Se<sub>y</sub> in the channel region. We hypothesize that the WO<sub>x</sub>Se<sub>y</sub> contact interlayer became thinner during the ebeam evaporation of Pd/Au contacts, as WO<sub>x</sub>Se<sub>y</sub> decomposes at elevated temperatures like 200 °C.<sup>[45,65]</sup> As with other ultrathin insulating contact interlayers,<sup>[58]</sup> the  $\approx 1$  nm WO<sub>x</sub>Se<sub>y</sub> contact interlayer still results in a Schottky barrier at the semiconductor-metal junction as a tunnel barrier. Further thinning of the WO<sub>x</sub>Se<sub>y</sub> contact interlayer is possible by in situ substrate heating or increasing the metal deposition power.

### 2.3. Short-Channel Monolayer WSe<sub>2</sub> p-FETs

Next, we combined extension doping with a WO<sub>x</sub>Se<sub>y</sub> interlayer under the contacts to fabricate high-performance short-channel monolayer WSe<sub>2</sub> p-FETs. Figure 6 shows the a) transfer and b) output characteristics of an example FET with an  $L_{ch}$  of  $50 \pm 5$  nm. Before SPL, the FET had an  $I_{max}$  of  $189 \mu\text{A} \mu\text{m}^{-1}$ , an  $I_{max}/I_{min}$  ratio of 74, and a  $V_T$  of 48.1 V at  $V_{DS} = 1$  V. After SPL,

these values changed to an  $I_{max}$  of  $154 \mu\text{A} \mu\text{m}^{-1}$ , an  $I_{max}/I_{min}$  ratio of  $4 \times 10^7$ , and a  $V_T$  of 12.8 V. As the channel length increased from 0 to 50 nm,  $I_{max}/I_{min}$  improved by 5 orders of magnitude, while  $I_{max}$  slightly decreased by 19%. Thus, the overall performance of the WO<sub>x</sub>Se<sub>y</sub> doped monolayer WSe<sub>2</sub> p-FET was optimized with sub-100 nm SPL. Figure 6b shows increased linearity of the  $I_D$ – $V_{DS}$  curves as  $V_{GS}$  decreased from 60 to  $-90$  V, suggesting a smaller Schottky hole barrier height with contact gating.

Figure S9 (Supporting Information) shows the transfer curves of two additional short-channel monolayer WSe<sub>2</sub> p-FETs with WO<sub>x</sub>Se<sub>y</sub>-doped extensions (Devices D and E), demonstrating similar performance.

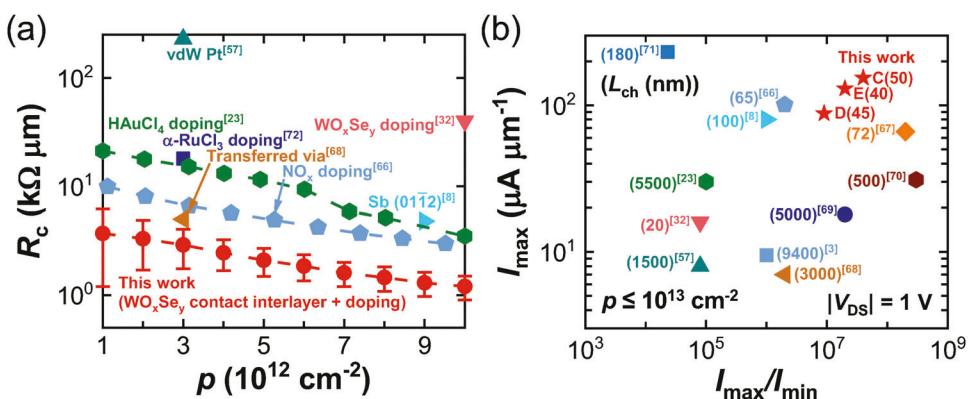

### 2.4. Benchmarking

Finally, Figure 7 benchmarks these short-channel FETs (Devices C–E) against the state-of-the-art monolayer WSe<sub>2</sub> p-FETs, as summarized in Table S1 (Supporting Information).<sup>[3,8,23,32,57,66–72]</sup> Figure 7a shows the benchmarking of  $R_c$  versus  $p$ . In this work, WO<sub>x</sub>Se<sub>y</sub> doping with a WO<sub>x</sub>Se<sub>y</sub> interlayer reached a contact resistance to monolayer WSe<sub>2</sub> of  $3.7 \pm 2.5$  to  $1.2 \pm 0.3$   $\text{k}\Omega \mu\text{m}$  at a hole density of  $10^{12}$ – $10^{13}$   $\text{cm}^{-2}$ . These values are about three times lower than the nearest comparisons, making them the lowest contact resistances at the same hole densities reported to date.

**Figure 7.** Benchmarking device performance of monolayer WSe<sub>2</sub> p-FETs. a) Benchmarking  $R_c$  versus  $p$ . b) Benchmarking  $I_{max}$  versus  $I_{max}/I_{min}$ .  $|V_{DS}| = 1$  V, and  $p \leq 10^{13} \text{ cm}^{-2}$ .  $L_{ch}$  is listed in parentheses for each data point.

Figure 7b benchmarks  $I_{\max}$  at  $|V_{DS}| = 1$  V versus  $I_{\max}/I_{\min}$ . To ensure a fair comparison, the upper limit of  $p$  was set to  $10^{13} \text{ cm}^{-2}$ . Devices C–E achieved performance comparable to the best monolayer WSe<sub>2</sub> p-FETs reported to date. To our knowledge, this study represents the first report of p-type extension doping for TMD monolayer FETs in the short-channel limit (Table S2, Supporting Information).

### 3. Conclusion

We demonstrated extension doping with low-resistance contacts for short-channel monolayer WSe<sub>2</sub> p-FETs by combining self-limiting-oxidation with damage-free nanolithography. WO<sub>x</sub>Se<sub>y</sub> doping, combined with an atomically thin amorphous WO<sub>x</sub>Se<sub>y</sub> contact interlayer, achieved record-low contact resistances for monolayer p-WSe<sub>2</sub> at a hole density ranged from  $10^{12}$  to  $10^{13} \text{ cm}^{-2}$ . Short-channel monolayer WSe<sub>2</sub> p-FETs with WO<sub>x</sub>Se<sub>y</sub>-doped extensions exhibited some of the best  $I_{\max}$  and  $I_{\max}/I_{\min}$  among TMD monolayer p-FETs.

To further enhance the performance of these short-channel monolayer WSe<sub>2</sub> p-FETs, several steps can be taken to potentially meet the technical targets for 2D transistors.<sup>[6]</sup> First, since  $R_c$  decreases with  $p$ , increasing  $p$  above  $10^{13} \text{ cm}^{-2}$  could reduce  $R_c$  below  $1 \text{ k}\Omega \mu\text{m}$ . Second, the FET did not reach current saturation at a  $V_{DS}$  of 1 V even with an  $L_{ch}$  of 50 nm and an  $L_{ext}$  of 150 nm, suggesting the potential for higher current density by further reducing  $L_{ch}$  and  $L_{ext}$ . Finally, residue-contaminated WO<sub>x</sub>Se<sub>y</sub> exhibited restored p-doping through self-limiting re-oxidation, indicating the potential to implement WO<sub>x</sub>Se<sub>y</sub>-based extension doping in CMOS via resist-based lithography, including deep or extreme ultraviolet lithography, along with wafer-scale bilayer WSe<sub>2</sub> grown using chemical vapor deposition.<sup>[32]</sup>

### 4. Experimental Section

**FET Fabrication:** First, a WSe<sub>2</sub> flake (HQ Graphene) was obtained and transferred by gold-assisted large-area exfoliation<sup>[73]</sup> onto a 285 nm SiO<sub>2</sub>/Si substrate. For all the FETs except the one shown in Figure 1c, SiO<sub>2</sub>/Si was passivated with 5 nm HfO<sub>x</sub> via atomic layer deposition before the transfer. HfO<sub>x</sub> serves as an etch stop for the following channel patterning step. The contribution of 5 nm HfO<sub>x</sub> to the gate capacitance is negligible (< 1%) compared to 285 nm SiO<sub>2</sub>. Subsequently, the bilayer region of the WSe<sub>2</sub> was patterned into a 1-μm-wide ribbon using e-beam lithography (EBL) and XeF<sub>2</sub> etch. For the FETs without WO<sub>x</sub>Se<sub>y</sub> underneath the contacts, the contact electrodes consisting of 5 nm Pd/50 nm Au was deposited onto the bilayer WSe<sub>2</sub> using EBL, e-beam evaporation, and liftoff. Then we used tip-based cleaning to remove polymer residues on WSe<sub>2</sub> for homogeneous oxidation.<sup>[40,41]</sup> Afterward, a controlled remote O<sub>2</sub> plasma process (Tergeo plasma cleaner, PIE scientific; 50 W, 1 min, 0.5 sccm O<sub>2</sub>; the same below) was used to convert the topmost layer of the WSe<sub>2</sub> channel into WO<sub>x</sub>Se<sub>y</sub>. For the FETs with WO<sub>x</sub>Se<sub>y</sub> underneath the contacts, the bilayer WSe<sub>2</sub> was oxidized before depositing the metal contacts. Finally, the FETs were re-oxidized after metallization to recover the p-doping of WO<sub>x</sub>Se<sub>y</sub>, using the same remote O<sub>2</sub> plasma recipe described above.

**STEM Sample Fabrication and Measurements:** Continuous and free-standing monolayer WO<sub>x</sub>Se<sub>y</sub> films were produced for STEM analysis by first transferring exfoliated monolayer WSe<sub>2</sub> onto holey TEM grids, and then oxidizing monolayer WSe<sub>2</sub> using remote O<sub>2</sub> plasma. Cross-sectional STEM samples were fabricated using standard FIB lift-out procedures with a FIB-SEM system (Helios 600i DualBeam, Thermo Fisher Scientific). The samples were imaged in an aberration corrected STEM (Themis Z, Thermo

Fisher Scientific). The STEM imaging was operated at 300 kV at a semi-convergence angle of 18 mrad with a beam current of 30 pA for monolayer WO<sub>x</sub>Se<sub>y</sub> and 50 pA for cross-sectional STEM. Elemental maps were collected with a Super-X EDS detection system with a beam current of 200 pA.

**XPS Measurements:** XPS measurements were performed using a Kratos Axis Supra<sup>+</sup> Photoelectron spectrometer with an Al K $\alpha$  X-ray source (1486.7 eV) and a concentric hemispherical analyzer. The analysis spot size was 55  $\mu\text{m}$  in diameter. The carbon C 1s peak at 284.8 eV was used for binding energy calibration.

**SPL and AFM Measurements:** All SPL and AFM measurements were performed using an Asylum MFP-3D AFM system. For all SPL experiments with transistors, a normal force of 40–60 nN, and a tip speed of  $\approx 10 \mu\text{m s}^{-1}$  was used. The SPL probes were single-crystal diamond probes (D80, Artech Carbon) with a tip radius of 10–30 nm and a spring constant of 3–4  $\text{nN nm}^{-1}$ . Single-crystalline diamond probes were used for SPL to minimize re-deposition of WO<sub>x</sub>Se<sub>y</sub>. The density of scan lines was  $\approx 1 \text{ nm per line}$ , much smaller than the tip radius to ensure that the pile-ups of WO<sub>x</sub>Se<sub>y</sub> were completely removed from the scanned surface of WSe<sub>2</sub>. After SPL, the SPL probe was replaced with a standard tapping-mode AFM probe (HQ:NSC15/AL\_BS, MikroMasch) for imaging.

**Raman and PL Measurements:** Raman and PL measurements on a confocal Raman microscope (Nanophoton Raman 11) using a 532 nm laser with a 100 $\times$  objective was performed. Raman spectra were obtained using a grating of  $2400 \text{ l mm}^{-1}$ . PL spectra were obtained using a grating of  $600 \text{ l mm}^{-1}$ .

**FET Transport Measurements and Data Processing:** We performed all FET transport measurements at room temperature in vacuum ( $10^{-4}$  Torr) using a semiconductor parameter analyzer (Agilent, 4155C). The threshold voltage  $V_T$  was extracted from the backward  $I_D-V_{GS}$  sweeps at  $V_{DS} = 1$  V by linear extrapolation.<sup>[74]</sup> Hysteresis was calculated as the difference between the threshold voltages of backward and forward  $I_D-V_{GS}$  sweeps. Both TLM structures in Figure S8a,d (Supporting Information) have at least four channels and at least one each of the contact and channel resistance-dominated devices, validating the employment of TLM to extract  $R_c$ .<sup>[63]</sup> The overlap of  $R_{sh}$  in Figure 5d also confirms the extraction of  $R_c$  using TLM is accurate.

### Supporting Information

Supporting Information is available from the Wiley Online Library or from the author.

### Acknowledgements

This work was partially funded by Taiwan Semiconductor Manufacturing Company (TSMC) under grant no. 089401, the National Institutes of Health (NIH) under grant no. R21HG010701, and funding from the University of Illinois Urbana-Champaign to RB. Y.Z. was funded by the Illinois Materials Research Science and Engineering Center (MRSEC) under grant no. DMR-2309037. This work was carried out in part in Holonyak Micro and Nanotechnology Laboratory and Materials Research Laboratory Central Facilities at University of Illinois Urbana-Champaign. The authors acknowledge the use of facilities and instrumentation supported by NSF through the Illinois MRSEC under grant no. DMR-2309037.

### Conflict of Interest

The authors declare no conflict of interest.

### Author Contributions

S.C. conceived the project. Under A.M.v.d.Z., R.B., and W.P.K.'s supervision, S.C. performed material characterization, device fabrication, measurements, and data analysis. Under A.M.v.d.Z.'s supervision, Y.Z. prepared bilayer WSe<sub>2</sub>. The manuscript was written through contributions

of all authors. All authors have given approval to the final version of the manuscript.

## Data Availability Statement

The data that support the findings of this study are available from the corresponding author upon reasonable request.

## Keywords

contact interlayer, contact resistance, scanning probe lithography, selective-area doping, short channel, tungsten oxselenide, WSe<sub>2</sub>

Received: November 5, 2024

Published online:

[1] J. Kedzierski, M. Ieong, E. Nowak, T. S. Kanarsky, Y. Zhang, R. Roy, D. Boyd, D. Fried, H. S. P. Wong, *IEEE Trans. Electron Devices* **2003**, *50*, 952.

[2] A. M. Cowley, S. M. Sze, *J. Appl. Phys.* **1965**, *36*, 3212.

[3] H. Fang, S. Chuang, T. C. Chang, K. Takei, T. Takahashi, A. Javey, *Nano Lett.* **2012**, *12*, 3788.

[4] Z. Zhang, M. Passlack, G. Pitner, S. Natani, S. K. Su, T. A. Chao, S. L. Liew, V. D. H. Hou, C. F. Hsu, W. E. Shipley, N. Safron, G. Doornbos, T. E. Lee, I. Radu, A. C. Kummel, P. Bandaru, H. S. P. Wong, *Nat. Electron.* **2023**, *6*, 999.

[5] S. Chouksey, J. G. Fossum, A. Behnam, S. Agrawal, L. Mathew, *IEEE Trans. Electron Devices* **2009**, *56*, 2348.

[6] Y. Liu, X. Duan, H. J. Shin, S. Park, Y. Huang, X. Duan, *Nature* **2021**, *591*, 43.

[7] P. V. Pham, S. C. Bodepudi, K. Shehzad, Y. Liu, Y. Xu, B. Yu, X. Duan, *Chem. Rev.* **2022**, *122*, 6514.

[8] W. Li, X. Gong, Z. Yu, L. Ma, W. Sun, S. Gao, Ç. Körögülu, W. Wang, L. Liu, T. Li, H. Ning, D. Fan, Y. Xu, X. Tu, T. Xu, L. Sun, W. Wang, J. Lu, Z. Ni, J. Li, X. Duan, P. Wang, Y. Nie, H. Qiu, Y. Shi, E. Pop, J. Wang, X. Wang, *Nature* **2023**, *613*, 274.

[9] Y. Wang, S. Sarkar, H. Yan, M. Chhowalla, *Nat. Electron.* **2024**, *7*, 638.

[10] K. Xu, Y. Zhao, Z. Lin, Y. Long, Y. Wang, M. Chan, Y. Chai, *Semicond. Sci. Technol.* **2017**, *32*, 124002.

[11] R. Murray, K. Haynes, X. Zhao, S. Perry, C. Haterm, K. Jones, *ECS J. Solid State Sci. Technol.* **2016**, *5*, Q3050.

[12] S. J. Yun, B. W. Cho, T. Dinesh, D. H. Yang, Y. I. Kim, J. W. Jin, S. H. Yang, T. D. Nguyen, Y. M. Kim, K. K. Kim, D. L. Duong, S. G. Kim, Y. H. Lee, *Adv. Mater.* **2022**, *34*, 2106551.

[13] L. Loh, Z. Zhang, M. Bosman, G. Eda, *Nano Res.* **2021**, *14*, 1668.

[14] A. Kozhakmetov, S. Stoltz, A. M. Z. Tan, R. Pendurthi, S. Bachu, F. Turker, N. Alem, J. Kachian, S. Das, R. G. Hennig, O. Gröning, B. Schuler, J. A. Robinson, *Adv. Funct. Mater.* **2021**, *31*, 2105252.

[15] F. Zhang, Y. Lu, D. S. Schulman, T. Zhang, K. Fujisawa, Z. Lin, Y. Lei, A. LauraElias, S. Das, S. B. Sinnott, M. Terrones, *Sci. Adv.* **2019**, *5*, 5003.

[16] A. Kozhakmetov, B. Schuler, A. Z. Marie Tan, K. A. Cochrane, J. R. Nasr, H. El-Sherif, A. Bansal, A. Vera, V. Bojan, J. M. Redwing, N. Bassim, S. Das, R. G. Hennig, A. Weber-Bargioni, J. A. Robinson, A. Kozhakmetov, A. Bansal, A. Vera, J. M. Redwing, S. Das, J. A. Robinson, B. Schuler, K. A. Cochrane, A. Weber-Bargioni, A. M. Z. Tan, R. G. Hennig, J. R. Nasr, H. El-Sherif, N. Bassim, V. Bojan, *Adv. Mater.* **2020**, *32*, 2005159.

[17] Y. Murai, S. Zhang, T. Hotta, Z. Liu, T. Endo, H. Shimizu, Y. Miyata, T. Irisawa, Y. Gao, M. Maruyama, S. Okada, H. Mogi, T. Sato, S. Yoshida, H. Shigekawa, T. Taniguchi, K. Watanabe, R. Canton-Vitoria, R. Kitaura, *ACS Nano* **2021**, *15*, 19225.

[18] J. Koike, M. Hosseini, H. T. Hai, D. Ando, Y. Sutou, in *2017 IEEE International Electron Devices Meeting (IEDM)*, **2018**, pp. 32.3.1–32.3.4.

[19] R. Torsi, K. T. Munson, R. Pendurthi, E. Marques, B. Van Troeye, L. Huberich, B. Schuler, M. Feidler, K. Wang, G. Pourtois, S. Das, J. B. Asbury, Y. C. Lin, J. A. Robinson, *ACS Nano* **2023**, *17*, 15629.

[20] R. Younas, G. Zhou, C. L. Hinkle, *Appl. Phys. Lett.* **2023**, *122*, 160504.

[21] S. Wang, W. Zhao, F. Giustiniano, G. Eda, *Phys. Chem. Chem. Phys.* **2016**, *18*, 4304.

[22] H. Cho, M. Sritharan, Y. Ju, P. Pujar, R. Dutta, W. S. Jang, Y. M. Kim, S. Hong, Y. Yoon, S. Kim, *ACS Nano* **2023**, *17*, 11279.

[23] P.-H. Ho, Y.-Y. Yang, S.-A. Chou, R.-H. Cheng, P.-H. Pao, C.-C. Cheng, I. Radu, C.-H. Chien, *Nano Lett.* **2023**, *23*, 10236.

[24] D. Lee, J. J. Lee, Y. S. Kim, Y. H. Kim, J. C. Kim, W. Huh, J. Lee, S. Park, H. Y. Jeong, Y. D. Kim, C. H. Lee, *Nat. Electron.* **2021**, *4*, 664.

[25] M. Si, C. Jiang, W. Chung, Y. Du, M. A. Alam, P. D. Ye, *Nano Lett.* **2018**, *18*, 3682.

[26] D. Sarkar, X. Xie, J. Kang, H. Zhang, W. Liu, J. Navarrete, M. Moskovits, K. Banerjee, *Nano Lett.* **2015**, *15*, 2852.

[27] A. Rai, A. Valsaraj, H. C. P. Movva, A. Roy, R. Ghosh, S. Sonde, S. Kang, J. Chang, T. Trivedi, R. Dey, S. Guchhait, S. Larentis, L. F. Register, E. Tutuc, S. K. Banerjee, *Nano Lett.* **2015**, *15*, 4329.

[28] C. J. McClellan, E. Yalon, K. K. H. Smithe, S. V. Suryavanshi, E. Pop, *ACS Nano* **2021**, *15*, 1587.

[29] K. Chen, D. Kiriya, M. Hettick, M. Tosun, T. J. Ha, S. R. Madhvapathy, S. Desai, A. Sachid, A. Javey, *APL Mater.* **2014**, *2*, 92504.

[30] S. Yang, G. Lee, J. Kim, *ACS Appl. Mater. Interfaces* **2021**, *13*, 955.

[31] A. Borah, A. Nipane, M. S. Choi, J. Hone, J. T. Teherani, *ACS Appl. Electron. Mater.* **2021**, *3*, 2941.

[32] A. Oberoi, Y. Han, S. P. Stepanoff, A. Pannone, Y. Sun, Y. C. Lin, C. Chen, J. R. Shallenberger, D. Zhou, M. Terrones, J. M. Redwing, J. A. Robinson, D. E. Wolfe, Y. Yang, S. Das, *ACS Nano* **2023**, *17*, 19709.

[33] T. D. Ngo, T. Huynh, I. Moon, T. Taniguchi, K. Watanabe, M. S. Choi, W. J. Yoo, *Nano Lett.* **2023**, *23*, 11345.

[34] D. Lee, J. Y. An, C. H. Lee, K. W. Bong, J. Kim, *ACS Appl. Nano Mater.* **2022**, *5*, 18462.

[35] S. Kang, Y. S. Kim, J. H. Jeong, J. Kwon, J. H. Kim, Y. Jung, J. C. Kim, B. Kim, S. H. Bae, P. Y. Huang, J. C. Hone, H. Y. Jeong, J. W. Park, C. H. Lee, G. H. Lee, *ACS Appl. Mater. Interfaces* **2021**, *13*, 1245.

[36] Y. C. Lin, B. M. Bersch, R. Addou, K. Xu, Q. Wang, C. M. Smyth, B. Jariwala, R. C. Walker, S. K. Fullerton-Shirey, M. J. Kim, R. M. Wallace, J. A. Robinson, *Adv. Mater. Interfaces* **2020**, *7*, 2000422.

[37] A. J. Arnold, D. S. Schulman, S. Das, *ACS Nano* **2020**, *14*, 13557.

[38] T. D. Ngo, M. S. Choi, M. Lee, F. Ali, Y. Hassan, N. Ali, S. Liu, C. Lee, J. Hone, W. J. Yoo, *Adv. Sci.* **2022**, *9*, 2202465.

[39] Y. Z. Zhang, G. J. Zhu, J. H. Yang, *Nanoscale* **2023**, *15*, 12116.

[40] J. Liang, K. Xu, B. Toncini, B. Bersch, B. Jariwala, Y. C. Lin, J. Robinson, S. K. Fullerton-Shirey, *Adv. Mater. Interfaces* **2019**, *6*, 1801321.

[41] S. Chen, J. Son, S. Huang, K. Watanabe, T. Taniguchi, R. Bashir, A. M. Van Der Zande, W. P. King, *ACS Omega* **2021**, *6*, 4013.

[42] Y. Kim, P. Herlinger, T. Taniguchi, K. Watanabe, J. H. Smet, *ACS Nano* **2019**, *13*, 14182.

[43] M. Yamamoto, S. Nakaharai, K. Ueno, K. Tsukagoshi, *Nano Lett.* **2016**, *16*, 2720.

[44] I. Irfan, A. James Turinske, Z. Bao, Y. Gao, *Appl. Phys. Lett.* **2012**, *101*, 093305.

[45] S. Chen, Y. Zhang, W. P. King, R. Bashir, A. M. Van Der Zande, *Adv. Mater.* **2024**, *36*, 2313694.

[46] Z. Yang, J. Hao, S. P. Lau, J. Appl. Phys. **2020**, *127*, 220901.

[47] H. Tian, Z. Yao, Z. Li, J. Guo, L. Liu, *ACS Nano* **2023**, *17*, 24468.

[48] M. R. Rosenberger, H. J. Chuang, K. M. McCreary, C. H. Li, B. T. Jonker, *ACS Nano* **2018**, *12*, 1793.

[49] H. G. Ji, P. Solís-Fernández, D. Yoshimura, M. Maruyama, T. Endo, Y. Miyata, S. Okada, H. Ago, *Adv. Mater.* **2019**, *31*, 1903613.

[50] O. B. Aslan, M. Deng, T. F. Heinz, *Phys. Rev. B* **2018**, *98*, 115308.

[51] D. H. Kang, J. Shim, S. K. Jang, J. Jeon, M. H. Jeon, G. Y. Yeom, W. S. Jung, Y. H. Jang, S. Lee, J. H. Park, *ACS Nano* **2015**, *9*, 1099.

[52] A. Nipane, M. S. Choi, P. J. Sebastian, K. Yao, A. Borah, P. Deshmukh, Y. Jung, B. Kim, A. Rajendran, K. W. C. Kwock, A. Zangiabadi, V. M. Menon, P. J. Schuck, W. J. Yoo, J. Hone, J. T. Teherani, *ACS Appl. Mater. Interfaces* **2021**, *13*, 1930.

[53] D. Lee, Y. Choi, J. Kim, J. Kim, *ACS Nano* **2022**, *16*, 8484.

[54] A. M. Dadgar, D. Scullion, K. Kang, D. Esposito, E. H. Yang, I. P. Herman, M. A. Pimenta, E. J. G. Santos, A. N. Pasupathy, *Chem. Mater.* **2018**, *30*, 5148.

[55] K. S. Kim, J. Kwon, H. Ryu, C. Kim, H. Kim, E. K. Lee, D. Lee, S. Seo, N. M. Han, J. M. Suh, J. Kim, M. K. Song, S. Lee, M. Seol, J. Kim, *Nat. Nanotechnol.* **2024**, *19*, 895.

[56] C. S. Pang, T. Y. T. Hung, A. Khosravi, R. Addou, Q. Wang, M. J. Kim, R. M. Wallace, Z. Chen, *Adv. Electron. Mater.* **2020**, *6*, 1901304.

[57] Y. Wang, J. C. Kim, Y. Li, K. Y. Ma, S. Hong, M. Kim, H. S. Shin, H. Y. Jeong, M. Chhowalla, *Nature* **2022**, *610*, 61.

[58] G. S. Kim, S. H. Kim, J. Park, K. H. Han, J. Kim, H. Y. Yu, *ACS Nano* **2018**, *12*, 6292.

[59] J. Wang, Q. Yao, C.-W. Huang, X. Zou, L. Liao, S. Chen, Z. Fan, K. Zhang, W. Wu, X. Xiao, C. Jiang, W.-W. Wu, *Adv. Mater.* **2016**, *28*, 8302.

[60] S. Lee, A. Tang, S. Aloni, H. S. Philip Wong, *Nano Lett.* **2016**, *16*, 276.

[61] K. Andrews, A. Bowman, U. Rijal, P. Y. Chen, Z. Zhou, *ACS Nano* **2020**, *14*, 6232.

[62] H. Cho, D. Kang, Y. Lee, H. Bae, S. Hong, Y. Cho, K. Kim, Y. Yi, J. H. Park, S. Im, *Nano Lett.* **2021**, *21*, 3503.

[63] Z. Cheng, C. S. Pang, P. Wang, S. T. Le, Y. Wu, D. Shahrjerdi, I. Radu, M. C. Lemme, L. M. Peng, X. Duan, Z. Chen, J. Appenzeller, S. J. Koester, E. Pop, A. D. Franklin, C. A. Richter, *Nat. Electron.* **2022**, *5*, 416.

[64] P. C. Shen, C. Su, Y. Lin, A. S. Chou, C. C. Cheng, J. H. Park, M. H. Chiu, A. Y. Lu, H. L. Tang, M. M. Tavakoli, G. Pitner, X. Ji, Z. Cai, N. Mao, J. Wang, V. Tung, J. Li, J. Bokor, A. Zettl, C. I. Wu, T. Palacios, L. J. Li, J. Kong, *Nature* **2021**, *593*, 211.

[65] M. G. Sales, A. Mazzoni, W. L. Sarney, A. C. Leff, J. Pearson, S. Najmaei, S. McDonnell, *Appl. Phys. Lett.* **2023**, *123*, 123502.

[66] C. C. Chiang, H. Y. Lan, C. S. Pang, J. Appenzeller, Z. Chen, *IEEE Electron Device Lett.* **2021**, *43*, 319.

[67] R. Wu, Q. Tao, J. Li, W. Li, Y. Chen, Z. Lu, Z. Shu, B. Zhao, H. Ma, Z. Zhang, X. Yang, B. Li, H. Duan, L. Liao, Y. Liu, X. Duan, X. Duan, *Nat. Electron.* **2022**, *5*, 497.

[68] Y. Liu, S. Liu, Z. Wang, B. Li, K. Watanabe, T. Taniguchi, W. J. Yoo, J. Hone, *Nat. Electron.* **2022**, *5*, 579.

[69] V. T. Vu, T. T. H. Vu, T. L. Phan, W. T. Kang, Y. R. Kim, M. D. Tran, H. T. T. Nguyen, Y. H. Lee, W. J. Yu, *ACS Nano* **2021**, *15*, 13031.

[70] J. Xie, Z. Zhang, H. Zhang, V. Nagarajan, W. Zhao, H. L. Kim, C. Sanborn, R. Qi, S. Chen, S. Kahn, K. Watanabe, T. Taniguchi, A. Zettl, M. F. Crommie, J. Analytis, F. Wang, *Nano Lett.* **2024**, *24*, 5937.

[71] H. Y. Lan, R. Tripathi, X. Liu, J. Appenzeller, Z. Chen, *In 2023 International Electron Devices Meeting (IEDM)*, **2023**, pp. 1–4.

[72] J. Pack, Y. Guo, Z. Liu, B. S. Jessen, L. Holtzman, S. Liu, M. Cothrine, K. Watanabe, T. Taniguchi, D. G. Mandrus, K. Barmak, J. Hone, C. R. Dean, *Nat. Nanotechnol.* **2024**, *19*, 948.

[73] S. B. Desai, S. R. Madhvapathy, M. Amani, D. Kiriya, M. Hettick, M. Tosun, Y. Zhou, M. Dubey, J. W. Ager, D. Chrzan, A. Javey, *Adv. Mater.* **2016**, *28*, 4053.

[74] D. K. Schröder, *Semiconductor Material and Device Characterization: Third Edition*, John Wiley & Sons, Hoboken, New Jersey, 2005.