# Breakdown Voltage and Leakage Current of the Non-uniformly Activated Lightly-doped p-GaN

Zineng Yang, Yunwei Ma, Matthew Porter, Hehe Gong, Zhonghao Du, Han Wang, Senior Member, IEEE, Yi Luo, Lai Wang, Member, IEEE and Yuhao Zhang, Senior Member, IEEE

Abstract— Many emerging GaN electronic and optoelectronic devices comprise p-GaN layers buried below n-type layers, which often show non-uniform (i.e., laterally-graded) acceptor concentration  $(N_A)$  after activation. In power devices, such buried p-GaN layer could be thick and lightly-doped, yet its voltage blocking characteristics remain unclear. This work fills this gap by studying the breakdown voltage ( $V_{BD}$ ) and leakage current of vertical GaN p-n<sup>+</sup> diodes with the uniform and non-uniform N<sub>A</sub> profiles in the 3.8 µm-thick, lightly-doped p-GaN drift region. The non-uniform N<sub>A</sub> is produced by burying the p-GaN under an n-GaN cap, followed by sidewall activation. The diodes show  $V_{\rm BD}$  up to over 400 V, which is the highest reported in vertical GaN devices with a p-type drift region. For the sidewall-activated diodes, their  $V_{\rm BD}$  is determined either by the peak electric field at the device edge (with the highest activation ratio) or the punch-through in the center (with the lowest activation ratio). An additional p<sup>++</sup>-GaN cap is essential to suppress the latter breakdown mechanism. For devices with either uniform or non-uniform  $N_A$ , their leakage current can be explained by variable range hopping, while in the sidewall-activated devices, the edge region instead of the total device area dominates the leakage current. These results provide key guidance for the design and processing of future high-voltage GaN devices with buried p-GaN, such as the GaN superjunction.

Index Terms—Power electronics, power semiconductor device, p-GaN, breakdown voltage, leakage current, p-n junctions

#### I. INTRODUCTION

P-TYPE Gallium Nitride (p-GaN) is an essential building block of many optoelectronic and electronic GaN devices including light-emitting diodes (LEDs) [1], power diodes [2], [3], high-electron-mobility transistors (HEMTs) [4]–[6], metal-oxide-semiconductor field-effect transistors (MOSFETs) [7], and junction-gate field effect transistors [8]. In industrial devices, p-GaN is usually grown by magnesium (Mg) doping in Metal-Organic Chemical Vapor Deposition (MOCVD). During the growth, atomic hydrogen (H) passivates the Mg dopants, leading to Mg-H complex [9], [10]. Post-growth annealing at a temperature range of 600-900 °C is usually required for acceptor activation in p-GaN by breaking the Mg-H bonds and diffusing H<sup>+</sup> out of the surface of p-GaN layer. Hence, in most aforementioned GaN devices, the p-GaN layer is positioned on top of the epitaxial structure.

The authors at Virginia Tech is funded in part by the Center for Power Electronics Systems (CPES) Industry Consortium and the National Science Foundation under the Contract ECCS-2045001.

Zineng Yang, Yunwei Ma, Matthew Porter, Hehe Gong and Yuhao Zhang are with the Center for Power Electronics Systems Virginia Polytechnic Institute and State University (Virginia Tech), Blacksburg, VA 24060 USA (email: yhzhang@vt.edu)

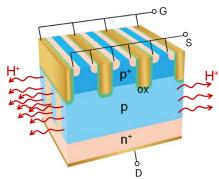

**Fig. 1.** 3D schematic of a vertical superjunction MOSFET with buried p-GaN, the activation of which is expected to rely on sidewall activation.

Recently, several advanced GaN devices such as tunnel junction LEDs [11], [12] and multidimensional power devices [13] demand the p-GaN layers situated beneath n-type nitride layers. Examples of such power devices include currentaperture vertical electron transistors (CAVETs) [14], trench MOSFETs [15], [16], and superjunction [17]. For instance, in a superjunction MOSFET (Fig. 1), the p-GaN drift layer is thick (at least a few micrometers) and lightly-doped, and they are usually buried below n<sup>+</sup>-GaN layers in the top channel region. These p-GaN pillars are used to achieve charge balance and block high voltage but not conduct current. Unfortunately, for the buried p-GaN, the through-surface activation is impractical due to a significant H diffusion barrier in n-GaN and the repassivation of p-GaN in the subsequent MOCVD epitaxy [18], [19]. Previous reports show that the lateral H diffusion along the etched sidewalls emerges as a prevalent solution [14]–[16]. However, this sidewall activation often produces a partially activated p-GaN with a non-uniform (i.e., laterally-graded) profile of acceptor concentration  $(N_A)$  [12], [20].

In the last few years, studies on the thick p-GaN epitaxy and the sidewall activation of buried p-GaN have gained increasing traction. Narita *et al.* achieved a wide range of p-GaN doping down to  $10^{16}$ - $10^{18}$  cm<sup>-3</sup> [21]–[23], which was deemed to be difficult previously. Meanwhile, Maeda *et al.* and Ji *et al.* demonstrated vertical GaN p-n<sup>+</sup> diodes [24]–[27] and employed them to extract the minority lifetime, breakdown field, and

Zhonghao Du is with the Ming Hsieh Department of Electrical and Computer Engineering, University of Southern California, Los Angeles, CA 90086 USA

Han Wang is with the Department of Electrical and Electronic Engineering, University of Hong Kong, Hong Kong, SAR, China

Yi Luo and Lai Wang are with Beijing National Research Center for Information Science and Technology (BNRist), Department of Electronic Engineering, Tsinghua University, Beijing 100084, China.

impact ionization coefficient in lightly-doped p-GaN. The highest breakdown voltage ( $V_{\rm BD}$ ) in these p-n<sup>+</sup> diodes is ~250 V, achieved in a ~3- $\mu$ m p-GaN drift region [26], [27].

On the other hand, a few groups studied the properties of the sidewall-activated, buried p-GaN [12], [20], [28]. For example, our recent work revealed the  $N_{\rm A}$  profile and  $V_{\rm BD}$  of the sidewall-activated p<sup>+</sup>-GaN [28]. However, the p-GaN layers used in these works are all highly doped with [Mg] >  $10^{19}$  cm<sup>-3</sup>, which cannot be used as a drift region of high-voltage devices. Overall, there still lacks studies into the  $V_{\rm BD}$  and leakage current of lightly-doped, thick, sidewall-activated p-GaN layer. This gap has been a critical roadblock for realizing the GaN superjunction devices. This is partly why the current GaN superjunction is built on alternative p-type oxide instead of p-GaN [17], [29].

This work fills this gap by delving into the  $N_{\rm A}$  profile,  $V_{\rm BD}$ , and leakage current of vertical GaN p-n<sup>+</sup> diodes with a lowly-doped ([Mg]~ $10^{18}$  cm<sup>-3</sup>), thick (3.8 µm) p-GaN drift region. Uniform and non-uniform (i.e., laterally-graded)  $N_{\rm A}$  profiles are produced by the surface- and sidewall-activation, respectively. A  $V_{\rm BD}$  over 400 V is achieved in the fully-activated p-n<sup>+</sup> diode, which is the highest reported in p-GaN based vertical devices. In addition to 10 times higher  $V_{\rm BD}$  compared to the p<sup>+</sup>-GaN in our prior work [28], we also find two competing breakdown mechanisms in the lightly-doped, non-uniform p-GaN, which was not present in the p<sup>+</sup>-GaN. Furthermore, the leakage current mechanism of the non-uniform p-GaN is found to differ from the one in the p<sup>+</sup>-GaN counterpart. The newly revealed breakdown and leakage current mechanisms provide critical reference for future multidimensional GaN power devices.

The remainder of this paper is organized as follows. Section III describes the epitaxy and device design. Section III describes the fabrication process for surface- and sidewall-activated diodes. Section IV and V discuss the breakdown and leakage current mechanisms, respectively. Section VI presents an extended discussion on device  $V_{\rm BD}$  based on the optimized epi design. Section VII concludes the paper.

## II. EPITAXIAL STRUCTURE AND DEVICE DESIGN

Fig. 2(a) illustrates the schematic of the as-grown epitaxial structure grown on an n-GaN substrate ([Si]: ~6×10<sup>18</sup> cm<sup>-3</sup>, dislocation density: ~106 cm<sup>-2</sup>) by MOCVD. The epilayer comprises a 200-nm n-GaN layer ([Si]: ~6×10<sup>18</sup> cm<sup>-3</sup>), a 3.8μm p-GaN drift layer ([Mg]: ~10<sup>18</sup> cm<sup>-3</sup>), and a heavily doped p<sup>++</sup>-GaN cap ([Mg]: ~10<sup>20</sup> cm<sup>-3</sup>). To explore the sidewall activation of Mg, a 300-nm n-GaN cap layer ([Si]: 5×10<sup>18</sup> cm<sup>-3</sup>), serving as a H diffusion barrier, was regrown atop the p<sup>++</sup>-GaN cap [see Fig. 2(b)]. The goal of using n-GaN regrowth is to mimic the device processing for future advanced power devices. For example, in superjunction devices, an n-GaN layer could be required to be deposited for the top channel region after the formation of superjunction drift region [30]. This regrowth also passivated the Mg dopants in the p-GaN region, as validated by the Secondary-Ion Mass Spectrometry (SIMS) result shown in Fig. 2(c). A [H]  $\sim 5 \times 10^{17}$  cm<sup>-3</sup> is present in the p-GaN layer after n-GaN regrowth. The [H] in n-GaN is much

**Fig. 2.** Cross-sectional view of (a) the as-grown epitaxial structure and (b) the one with the regrown n-GaN layer. (c) The SIMS profile of the n-p-n structure with the n-GaN cap layer.

lower, confirming the high diffusion barrier. The SIMS result also shows a relatively high [C]  $\sim 8 \times 10^{17}$  cm<sup>-3</sup> in the p-GaN, which is usual in the MOCVD growth of p-GaN without special adjustment (e.g., tuning the Mg source gas [21], [23]). Hence, the  $N_{\rm A}$  is expected to be smaller than [Mg] due to [C] compensation.

Table I summarizes the design of four vertical GaN p-n<sup>+</sup> diodes with different Mg activation schemes. All diodes were fabricated on the epi structure with a regrown n-GaN, followed by the etch of n-GaN and the anode formation on p-GaN. Diode A saw no Mg activation, while Mg dopants in diodes B1 and B2 were sidewall-activated with an activation time of 1 hour and 1.5 hours, respectively. The diode C underwent the Mg activation after the n-GaN etch-back, i.e., a combination of surface and sidewall activations. Due to the efficient [H] diffusion via the top p-GaN surface, the Mg acceptors in diode C were fully activated.

SUMMARY OF DEVICE DESIGNS WITH DIFFERENT MG ACTIVATION SCHEMES

| Diode type | Mg activation scheme                                    |

|------------|---------------------------------------------------------|

| A          | Non-activated                                           |

| B1         | 1-hour sidewall-activation                              |

| B2         | 1.5-hour sidewall-activation                            |

| C          | Surface- and sidewall-activation (i.e. full activation) |

## III. DEVICE FABRICATION

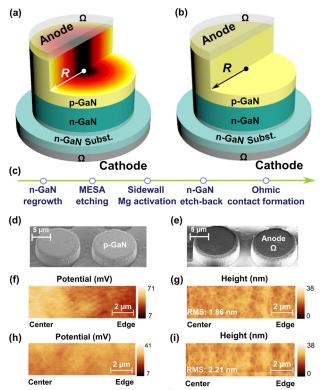

Fig. 3(a) depicts the 3D diagram of the circular GaN p-n<sup>+</sup> diode with a sidewall activated p-GaN. The color gradient shows the non-uniform Mg activation ratio along the diode radius (*R*). Fig. 3(b) shows the 3D diagram of the fully-activated diode (i.e., diode C). The fabrication process is similar to that described in our prior work [28], and is summarized in Fig. 3(c). For all characterized samples, after the n-GaN regrowth, device isolation was made by

Fig. 3. Schematics of vertical GaN p-n $^+$  diodes with (a) sidewall-activated and (b) fully-activated p-GaN layer. The symbol  $\Omega$  represents Ohmic contact. (c) The fabrication process of the GaN diode with sidewall-activated p-GaN. SEM images of (d) the epi after n-GaN etch-back and (e) the as-fabricated diodes. (f) Potential and (g) surface morphology of a sidewall-activated p-GaN measured by KPFM. (h) Potential and (i) surface morphology of a fully-activated p-GaN measured by KPFM.

# a 5-µm mesa dry-etch, followed by a TMAH treatment [31].

In samples B1 and B2, the Mg activation was then performed at 800 °C in N<sub>2</sub> atmosphere for 1 hour and 1.5 hours, respectively. Then the regrown n-GaN layer was etched, during which the 20-nm p<sup>++</sup>-GaN cap was inevitably removed. Fig. 3(d) shows the scanning electron microscopy (SEM) images of the sample after n-GaN etch-back. The Ohmic contact on p-GaN was formed by the e-beam evaporated Pd/Ni/Au annealed at 600 °C in N<sub>2</sub>, and the Ohmic cathode on the n-GaN substrate was made by Ti/Al/Ni/Au. The SEM image of the fabricated diode is depicted in Fig. 3(e).

In sample C, the Mg activation was performed after the n-GaN etch-back at 800  $^{\circ}\text{C}$  in  $N_2$  for 10 minutes. Other processes are the same as used for samples B1 and B2. Sample A underwent the same processes as used for samples B1, B2 and C, but without the Mg activation.

To qualitatively probe the activated  $N_A$  profile in the sidewall activated p-GaN layer, we employed the Kelvin probe force microscopy (KPFM), a technique widely used for discerning dopant profiles in GaN p-n junctions [32]–[34]. Fig. 3(f) and (g) show the surface potential and morphology of the p-GaN layer in diode B1, respectively. The surface potential gradually decreases from the center to the edge, while the surface morphology is uniform and smooth. This contrast supports a non-uniform  $N_A$  profile along the diode radius. Fig. 3(h) displays uniform surface potential of p-GaN layer in diode C, accompanied by the uniform and smooth surface morphology

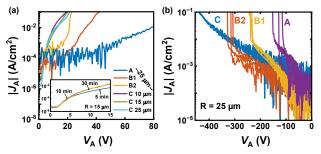

**Fig. 4.** (a) Forward *I-V* characteristics of diodes A-C, with the inset showing the forward *I-V* characteristics of diodes C with varying p-GaN annealing time. (b) Reverse *I-V* characteristics of diodes A-C, three devices shown for each type of diode.

shown in Fig. 3(i), which indicates the uniform  $N_A$  profile along the diode radius in diode C.

#### IV. Breakdown Characteristics and Mechanism

#### A. Forward I-V Characteristics

Fig. 4(a) depicts the forward I-V characteristics of diodes A, B1, B2, and C. Note that the current density ( $J_A$ ) is not critical for multidimensional devices as p-GaN is not used to conduct current. Instead, the comparison between diodes' forward characteristics can provide evidence for p-GaN activation. Diodes A, B1 and B2 have the same radius (R) of 25  $\mu$ m, whereas diode C has varying R between 10  $\mu$ m, 15  $\mu$ m and 25  $\mu$ m. Diodes B1, B2 and C demonstrate rectifying I-V behaviors, whereas diode A can hardly be turned on until the anode voltage ( $V_A$ ) > 50 V due to the non-activated p-GaN.

Diode C exhibits the lowest turn-on voltage of  $\sim$ 4 V at 0.1 mA/cm² and the highest  $J_{\rm A}$  compared to diodes B1 and B2, confirming the efficient Mg activation via surface. Also, the inset in Fig. 4(a) compares the forward I-V characteristics of the surface-activated diode annealed for 5, 10, and 30 minutes at 800 °C in N₂ atmosphere. Increasing annealing time from 5 to 10 minutes resulted in a notable rise in forward current, with no significant difference observed between diodes annealed for 10 and 30 minutes. This also suggests full activation of diode C after an activation annealing of over 10 minutes.

The  $J_{\rm A}$  of diode C is similar in magnitude as R varies from 10  $\mu$ m to 25  $\mu$ m, suggesting the current conduction via the bulk junction in the fully-activated diodes. For sidewall-activated diodes, B2 exhibits a larger forward current and a smaller turnon voltage compared to B1, suggesting an enhanced activation with an increasing activation time. Both diodes demonstrate significantly larger turn-on voltages than diode C, confirming the incomplete  $N_{\rm A}$  activation.

The relatively low forward current density and large forward voltage drop are mainly due to the poor Ohmic contact formed on the etched p-GaN surface. The etch-back process inevitably removes the p<sup>++</sup>-GaN cap layer, and the etching process can introduce nitrogen vacancies, which could form donor states. These two factors result in the high contact resistance and relatively large turn-on voltage.

#### B. Breakdown Characteristics and Mechanism

Fig. 4(b) shows the reverse *I-V* characteristics of the four types of diodes (data of three devices shown for each type) with

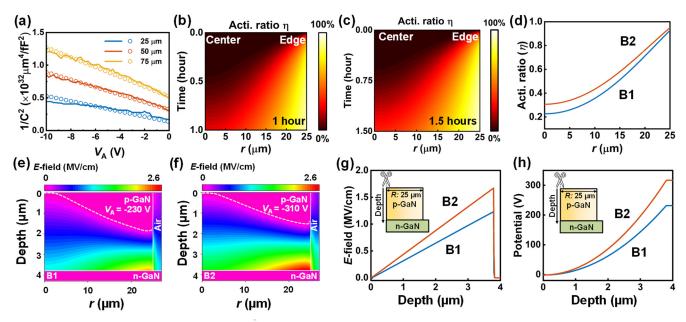

Fig. 5. (a) 1/C<sup>2</sup>-V plot of diodes B1 with R of 25 μm, 50 μm and 75 μm. The solid lines and symbols represent the experimental and modeled results, respectively. Spatial-temporal contour showing the Mg activation ratio ( $\eta$ ) of (b) the 1-hour and (c) the 1.5-hour sidewall-activated p-GaN with  $R=25 \mu m$ . (d) Extracted  $\eta$  profile along the radius after 1-hour and 1.5-hour activation. TCAD-simulated E-field distribution for (e) diode B1 at  $V_{\Lambda}$  of -230 V and (f) diode B2 at V<sub>A</sub> of -310 V. (g) Extracted longitudinal E-field profiles and (h) potential profiles for the diodes B1 and B2 at -230/-310 V in the center region. The insets in (g) and (h) represent the schematics of simulated half-diode cell, with extracted characteristics along the center cutline.

a current compliance of 0.1 A/cm<sup>2</sup> for  $V_{\rm BD}$  extraction. Diode A with non-activated p-GaN shows the lowest  $V_{\rm BD}$  of ~110 V. With the increased Mg sidewall activation time,  $V_{\rm BD}$  rises to ~230 V for diode B1 and ~310 V for diode B2. The fully activated diode C exhibits the highest  $V_{\rm BD}$  of ~420 V. While diode C shows a gradual increase in leakage current, diodes A-B2 exhibit a distinct sharp hump in leakage current at  $V_{\rm BD}$ .

To explore the breakdown mechanism, it is essential to quantify the activated NA profile in the fully-activated and sidewall-activated diodes. For this, we follow a similar method and model as developed in our prior work [28]. The C-V measurement of the fully-activated diode C gives an total ionizable  $N_A$  ( $N_A^0$ ) of ~7×10<sup>16</sup> cm<sup>-3</sup>, which is indeed smaller than the [Mg] measured via the SIMS due to the compensation by carbon deep donor states [22]. Furthermore, Mg impurities could exhibit double donor behavior when accommodated in an interstitial position, and nitrogen vacancies (V<sub>N</sub>) could also act as compensation donors, further decreasing the  $N_A^0$  value [35].

The  $N_A$  profile in the sidewall-activated p-GaN can be modeled by the [H] diffusion equation in the cylindrical coordinate [28]

$$D\frac{1}{r}\frac{\partial}{\partial r}\left(r\frac{\partial[H]}{\partial r}\right) = \frac{\partial[H]}{\partial t} \tag{1}$$

where D is the H diffusion constant, r is the radial distance of the diode, and t is the activation time.

Several boundary conditions can be derived: (a) the initial [H] bounded with the [Mg] that can ultimately form N<sub>A</sub> equals to  $N_{\rm A}^0$  (note that this [Mg] is much smaller than the total [Mg] as revealed in the SIMS as a large portion of [Mg] reacts with [C]); (b) [H] gradient in the center should be zero; (c) the surface barrier for [H] desorption at the sidewall is a constant (A). These conditions lead to the following equations

$$[H]|_{r=0} \approx N_A^{0} = 7 \times 10^{16} \text{ cm}^{-3}$$

(2)

$$\left. \frac{\partial [\mathbf{H}]}{\partial r} \right|_{r=0, t} = 0 \tag{3}$$

$$[H]\Big|_{r, t=0} \approx N_A^{\ 0} = 7 \times 10^{16} \text{ cm}^{-3}$$

$$\frac{\partial [H]}{\partial r}\Big|_{r=0, t} = 0$$

$$\frac{d}{dt} \left( \frac{[H]_{r=R, t=0}}{[H]_{r=R, t}} \right) = A$$

(2)

(3)

Note that this model under the cylindrical coordinate could be specifically applicable for 3D superjunction devices with a radial p-n junction [36]. For other superjunction form factors (e.g., stripes), a similar [H] diffusion model can be constructed from the same physics but different coordinates and modified boundary conditions.

Combining (1)-(4), the  $N_A$  profile along the radial direction  $(N_{A(r)})$  can be modeled. It has been shown in [28] that such  $N_{A(r)}$  can be calibrated by comparing the modeled and experimental C-V characteristics of the partially-activated diodes. For this, the modeled capacitance (C) is derived using the modeled  $N_{A(r)}$  and the integral of specific capacitance along r [28]

$$C = \int_{0}^{R} 2\pi r \sqrt{\frac{\epsilon q N_{{

m A}(r)} N_{{

m D}}}{2 (N_{{

m A}(r)} + N_{{

m D}}) (V_{{

m bi}} - V_{{

m A}})}} dr$$

(5)

where  $\epsilon$  is the permittivity of GaN, q is the electron charge,  $N_{\rm D}$ is the doping concentration of the n-GaN, and  $V_{\rm bi}$  is the built-in potential of the p-n junction.

Fig. 5(a) shows the agreement between the modeled and experimental  $1/C^2$ -V characteristics for the 1-hour sidewallactivated diodes with radii ranging from 25 µm to 75 µm. These agreements were attained using D of  $2.5 \times 10^{-10}$  cm<sup>2</sup>/s and A of 3.5×10<sup>-3</sup> s<sup>-1</sup>, which fall in the range reported elsewhere [12], [18], [20], [37]. For the diode with  $R = 25 \mu m$ , Fig. 5(b)-(d) plot the modeled activation ratio ( $\eta$ ) profiles of the p-GaN after 1hour and 1.5-hour sidewall activation. After 1-hour activation

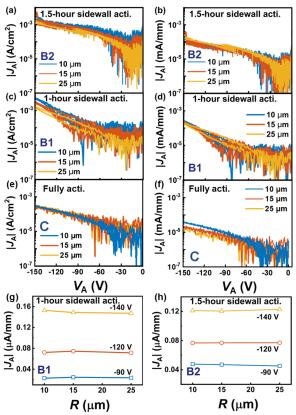

**Fig. 6.** Reverse *I-V* characteristics for diodes B2 normalized to (a) area and (b) perimeter; for diodes B1 normalized to (c) area and (d) perimeter; for diodes C normalized to (e) area and (f) perimeter. One or two *I-V* curves are provided for each diode with the same radius. Extracted  $|J_A|$  normalized to perimeter versus R at varying  $V_A$  for (g) diode B1 and (h) diode B2.

$\eta$  is ~93% at the diode edge ( $N_{A(r=R)} = 6.48 \times 10^{16}$  cm<sup>-3</sup>) and ~22% ( $N_{A(r=0)} = 1.58 \times 10^{16}$  cm<sup>-3</sup>) in the center. The 1.5-hour activation produces a higher  $\eta$  of 31% ( $N_{A(r=0)} = 2.15 \times 10^{16}$  cm<sup>-3</sup>) in the center. With the modeled  $N_{A(r)}$  profile, TCAD simulation in Silvaco was used to simulate the electric field (*E*-filed) distribution in the diode with R = 25 µm based on the models in [38], [39]. The simulated *E*-field distribution in diodes B1 and B2 at their respective  $V_{BD}$  are shown in Fig. 5(e) and (f), respectively. In diode B1, a peak *E*-field ( $E_{peak}$ ) of ~2.2 MV/cm is extracted near the edge of p-GaN at -230 V where most  $N_A$  is activated. Such an  $E_{peak}$  is much lower than the critical electric field ( $E_{crit}$ ) of GaN (>3 MV/cm) at  $N_{A(r=R)}$ . In diode B2, the  $E_{peak}$  is also located at the edge and smaller than  $E_{crit}$ . This indicates the breakdown is not induced by  $E_{peak}$ .

Fig. 5(g) and (h) show the simulated E-field and potential profiles along the vertical direction in the center of the p-GaN drift region, in diodes B1 and B2, respectively, at their respective  $V_{\rm BD}$ . Despite a lower E-field than the edge, the depletion region in the center reaches all the way through the p-GaN drift region to the anode Ohmic contact. This can be seen from the zero-field depletion fronts marked with white dashed lines in Fig. 5(e) and (f). This punch-through could lead to the sudden increase in leakage current and dominate the device breakdown, which has been proved in many power devices [40], [41].

**Fig. 7.** Reverse  $|J_A|$  versus  $E_{\text{peak}}$  of (a) diode B1 and (b) diode C at T of 293 K, 328 K, 353 K, 378 K and 403 K. Plots of the linear fits of  $\ln(|J_A|)$  versus  $T^{1.25}$  for (c) diode B1 and (d) diode C.

Assuming the measured  $V_{\rm BD}$  equals to the punch-through voltage ( $V_{\rm PT}$ ), we can calculate the  $N_{{\rm A}(r=0)}$  based on

$$V_{\rm PT} = \frac{qN_{\rm A(r=0)}t_{\rm GaN}^2}{2\epsilon} \tag{6}$$

where  $t_{GaN}$  is the thickness of the p-GaN layer (= 3.8  $\mu$ m).

With the measured  $V_{\rm PT}$  of 230/310 V in the diode B1/B2, the calculated  $N_{\rm A(r=0)}$  is  $1.57\times10^{16}/2.11\times10^{16}$  cm<sup>-3</sup>, which is in close agreement with the modeled  $N_{\rm A(r=0)}$ , thereby further validating the punch-through breakdown mechanism.

# V. LEAKAGE CURRENT MECHANISM

Fig. 6(a)-(d) present the reverse  $J_A$  normalized to area and perimeter for diodes B1 and B2 with radii of 10  $\mu$ m, 15  $\mu$ m and 25  $\mu$ m. At high reverse bias (e.g., 90-150 V),  $|J_A|$  normalized to the area differ in magnitudes with varying radii. Conversely,  $|J_A|$  normalized to the perimeter almost overlap, as evidenced by the similar extracted  $|J_A|$  values across radii at varying  $V_A$  (see Fig. 6(g)-(h)). This observation suggests that leakage current mainly flows near the edge in the sidewall-activated diodes, where the *E*-field is highest. For diode C with varying radii,  $|J_A|$  normalized to the area virtually overlap, whereas a noticeable difference in  $|J_A|$  normalized to the perimeter is visible (see Fig. 6(e)-(f)). This indicates that the leakage current predominantly flows through the bulk junction.

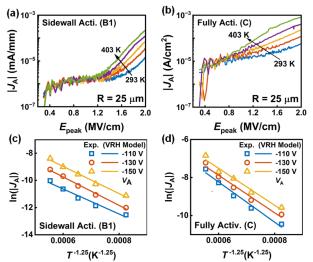

To investigate the leakage mechanism, temperature (T)-dependent reverse I-V characteristics were measured for the sidewall-activated diode B1 and the fully-activated diode C, plotted against  $E_{\text{peak}}$ .  $E_{\text{peak}}$  at the edge of p-n junction for diode B1 can be derived by

$$E_{\text{peak}} = \sqrt{\frac{2qN_{\text{D}}N_{\text{A}(r=\text{R})}}{\epsilon[N_{\text{D}} + N_{\text{A}(r=\text{R})}]}(V_{\text{bi}} - V_{\text{A}})}$$

(7)

where  $N_{A(r=R)}$  was extracted to be 6.48 ×10<sup>16</sup> cm<sup>-3</sup> using our model. (7) is also applicable to calculate the  $E_{peak}$  at the junction of diode C, utilizing the  $N_A{}^0$  extracted from the C-V data.

Fig. 7(a) and (b) present the  $|J_A|$  versus  $E_{\text{peak}}$  characteristics for diodes B1 and C across the T range of 293 K to 403 K, respectively. Both diodes yield a positive dependence of  $|J_A|$  on

E-field and T. In diode B1,  $|J_A|$  begins to rise beyond the measurement noise floor at an  $E_{\text{peak}}$  of 1.2 MV/cm and follows a linear trend from 1.2 MV/cm to 2.0 MV/cm in the semi-log plot. As shown in Fig. 7(b), this linear relationship between logarithmic  $|J_A|$  and  $E_{peak}$  is also observed in diode C for  $E_{peak}$ values between 0.8 MV/cm and 2.0 MV/cm. Fig. 7(c) and (d) display the extracted  $ln(|J_A|)$  plotted against  $T^{1.25}$  for diodes B1 and C, respectively, at varying  $V_A$  bias. The good linear fitting of  $ln(|J_A|)$  versus  $T^{-1.25}$  confirms variable range hopping (VRH) as the dominant leakage mechanism in both diodes, while one occurring near the edge region and the other across the entire junction region. VRH, involving carrier transport in the depletion region through dislocation/traps [42]-[44], is commonly observed in GaN vertical diodes at high bias [2], [8], [40], [42]. The mathematical model of VRH-dominated leakage current  $(J_{VRH})$  is [45]

$$J_{\text{VRH}} \propto \exp \left[ C \frac{qaE}{2k_{\text{B}}T} \left( \frac{T_0}{T} \right)^{\frac{1}{4}} \right]$$

(8)

where C is a constant, a is the localization radius of the electron wavefunction,  $k_{\rm B}$  is the Boltzmann constant, and  $T_0$  is a characteristic temperature.

Note that this leakage current mechanism is different from that revealed in sidewall-activated p<sup>+</sup>-GaN, where the tunneling prevails in the highly-doped junction [28]. This difference is because the thinner depletion region near the p<sup>+</sup>-n junction enables carrier tunneling at high electric field, whereas the wider depletion region in lightly doped p-GaN limits tunneling; instead, carriers hopping via dislocations/traps in the depleted region prevails.

### VI. FURTHER DISCUSSION ON BREAKDOWN VOLTAGE

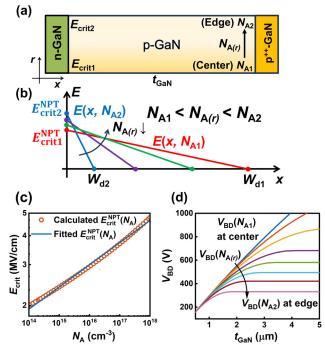

This section presents an analytical discussion on the  $V_{\rm BD}$  of the non-uniformly activated p-GaN if the center-region punch-through is resolved by inserting a p<sup>++</sup>-GaN atop. In this p<sup>++</sup>-p-n diode, as shown in Fig. 8(a) for a half cell,  $V_{\rm BD}$  hinges on the radial profile  $N_{\rm A(r)}$  and is determined by the minimum  $V_{\rm BD}$ :

$$V_{\text{BD}} = \min\{V_{\text{BD}}(N_{\text{A}1}), ... V_{\text{BD}}(N_{\text{A}(r)}), ... V_{\text{BD}}(N_{\text{A}2})\}$$

for  $N_{\text{A}(r)} \in [N_{\text{A}1}, N_{\text{A}2}]$  (9)

Here  $N_{A(r)}$  increases continuously from  $N_{A1}$  (center) to  $N_{A2}$  (edge). Under the condition of a sufficient  $t_{GaN}$  to enable the non-punch-through (NPT) design, the triangular *E*-field profiles in the p-GaN vary in relation to  $N_{A(r)}$  [see Fig. 8(b)].  $E_{crit}$  in case of NPT ( $E_{crit}^{NPT}$ ) as a function of  $N_{A}$  can be derived by solving the hole-initiated impact ionization integral [46].

$$\int_{0}^{x_{d}} \beta(x) \exp \left\{ \int_{0}^{x} [\alpha(x') - \beta(x')] dx' \right\} dx = 1 \quad (10)$$

where  $x_d$  is the depletion width in p-GaN,  $\alpha(x)$  and  $\beta(x)$  denote the electron and hole impact ionization rates, respectively.

The impact ionization rates of GaN have been measured by several groups, including Cao *et al* [47], [48], Maeda *et al* [26] and Ji *et al* [24]. The measured  $\alpha(x)$  and  $\beta(x)$  in [24] were employed for the numerical solution of (10), as shown in (11) and (12). Note that the choice of  $\alpha(x)$  and  $\beta(x)$  will result in variations in the absolute magnitudes of  $E_{\text{crit}}$  and  $V_{\text{BD}}$  along  $N_{A(r)}$ , whereas it will not impact the profile of  $V_{\text{BD}}$  along the

Fig. 8. (a) Schematics of the half unit cell of a GaN p<sup>++</sup>-p-n diode. (b) *E*-field profiles within the p-GaN drift region for at different radical  $N_{A(r)}$ .  $W_{d1}$  and  $W_{d2}$  are the depletion width in the p-GaN with  $N_{A1}$  and  $N_{A2}$ . (c) Computed NPT  $E_{crit}$  as a function of  $N_A$  and its power-law fitted curve. (d) Calculated  $V_{BD}$  as a function of both  $t_{GaN}$  and  $N_A$  considering the PT  $E_{crit}$ .

diode radius. The reason that the  $\alpha(x)$  and  $\beta(x)$  from [24] are used is due to the calculated  $V_{\rm BD}$  seems close to the measured  $V_{\rm BD}$  of diode C at the same  $N_{\rm A}$ .

$$\alpha(E) = 2.11 \times 10^9 \exp\left(-\frac{3.689 \times 10^7}{E(x)}\right) \text{ (cm}^{-1}) \text{ (11)}$$

$$\beta(E) = 4.39 \times 10^{6} \exp\left(-\frac{1.8 \times 10^{7}}{E(x)}\right) \text{ (cm}^{-1}) (12)$$

where  $E(x) = E_{\rm crit}^{\rm NPT} - q N_{\rm A} x/\epsilon$  is the *E*-field profile in p-GaN.

Fig. 8(c) shows the computed NPT critical electric field ( $E_{\text{crit}}^{\text{NPT}}$ ) can be approximated by a power law fit, which makes it easy to derive a closed form solution of  $V_{\text{BD}}$  [49].

$$E_{\text{crit}}^{\text{NPT}} = 8.8534 \times 10^4 N_A^{0.09557} \text{ (V/cm)}$$

(13)

The  $V_{\rm BD}$  of an NPT layer is given by

$$V_{\rm BD}^{\rm NPT} = \frac{\epsilon E_{\rm crit}^{\rm NPT^2}}{2qN_{\rm A}} \tag{14}$$

Substituting  $E_{

m crit}^{

m NPT}$  with the power-fitted expression  $E_{

m crit}^{

m NPT}=aN_A^{

m b}$  in (13) leads to

$$V_{\rm BD}^{\rm NPT} = \frac{\epsilon a^2 N_A^{2b-1}}{2q} \tag{15}$$

As 2b-1 < 0,  $V_{\mathrm{BD}}^{\mathrm{NPT}}$  will decrease monotonically with the increased  $N_{\mathrm{A}}$ , suggesting that the  $V_{\mathrm{BD}}$  of the NPT diode is determined by  $V_{\mathrm{BD}}^{\mathrm{NPT}}(N_{\mathrm{A}\,2})$  at the edge region.

Finally, we consider the PT situation in the p-GaN drift region, i.e., when  $t_{\text{GaN}}$  is smaller than the depletion width in the center ( $W_{\text{d1}}$ ). In this case, the *E*-field profiles along the diode

radius can either exhibit PT or NPT behaviors depending on  $N_A$ . The corresponding  $V_{BD}$  in the PT case is given by

$$V_{\rm BD}^{\rm PT} = E_{\rm crit}^{\rm PT} t_{\rm GaN} - \frac{qN_{\rm A}}{2\epsilon} t_{\rm GaN}^2$$

(16)

where  $E_{\mathrm{crit}}^{\mathrm{PT}}$  is PT critical electric field.

Note that (13) cannot be directly applied to calculate  $V_{\rm BD}^{\rm PT}$  since  $E_{\rm crit}^{\rm PT}$  will be (slightly) larger than  $E_{\rm crit}^{\rm NPT}$  at the same  $N_{\rm A}$  of the p-GaN drift layer. Such an increase is reasonable because a higher  $E_{\rm crit}$  is required to trigger avalanche breakdown in a PT case with shorter avalanche path, thereby  $E_{\rm crit}$  is dependent not only on  $N_{\rm A}$ , but on  $t_{\rm GaN}$  [26]. The numerical solution of (10) must be reevaluated to derive  $E_{\rm crit}^{\rm PT}$  by setting  $x_{\rm d}=t_{\rm GaN}$  and  $E(x)=E_{\rm crit}^{\rm PT}-qN_{\rm A}x/\epsilon$   $\Big|_{x~\in~t_{\rm GaN}}$  [50]. In this case, the entire  $V_{\rm BD}$  does not have a close-form solution.

Fig. 8(d) shows the numerically calculated  $V_{\rm BD}$  using (16) along the radial  $N_{\rm A(r)}$  from  $N_{\rm A1}$  (1×10<sup>16</sup> cm<sup>-3</sup>) to  $N_{\rm A2}$  (1×10<sup>17</sup> cm<sup>-3</sup>), while  $t_{\rm GaN}$  varies between 0.5 µm and 5 µm. It is evident that the minimum  $V_{\rm BD}$  consistently corresponds to  $V_{\rm BD}(N_{\rm A2})$ , suited at the edge region. Overall, the results in this section suggest that, when the center-region punch-through no longer leads to  $V_{\rm BD}$  due to the inserted p<sup>++</sup>-GaN, the  $V_{\rm BD}$  of the sidewall-activated diode is expected to be dominated by the edge region.

#### VII. CONCLUSION

This work investigates the  $V_{\rm BD}$  and leakage current of vertical GaN p-n<sup>+</sup> diodes with the uniform and non-uniform  $N_A$ profiles in a thick, lightly-doped p-GaN drift region. The nonuniform N<sub>A</sub> is produced by burying p-GaN under an n-GaN cap, followed by sidewall activation. The fully-activated diodes show  $V_{\rm BD}$  up to 420 V, which is the highest reported in vertical GaN devices with a p-type drift region. For the sidewallactivated diodes, their  $V_{\rm BD}$  is determined by the punch-through in the center region. For devices with uniform and non-uniform  $N_{\rm A}$ , their leakage currents are dominated by VRH in the entire junction region and the edge region, respectively. If an additional p<sup>++</sup>-GaN cap is inserted to suppress the punchthrough induced breakdown, the device  $V_{\rm BD}$  will be determined by the  $E_{\text{peak}}$  at the edge region. These learnings provide design guidelines for power devices involving the partially-activated, buried p-GaN layers, e.g., trench MOSFETs and superjunction.

# ACKNOWLEDGMENT

The authors would like to thank collaborations with Silvaco for device simulations.

## REFERENCES

- [1] G. Li, W. Wang, W. Yang, Y. Lin, H. Wang, Z. Lin, and S. Zhou, "GaN-based light-emitting diodes on various substrates: a critical review," Rep. Prog. Phys., vol. 79, no. 5, p. 056501, Apr. 2016, doi: 10.1088/0034-4885/79/5/056501.

- [2] Y. Zhang, A. Dadgar, and T. Palacios, "Gallium nitride vertical power devices on foreign substrates: a review and outlook," *J. Phys. Appl. Phys.*, vol. 51, no. 27, p. 273001, Jul. 2018, doi: 10.1088/1361-6463/aac8aa.

- [3] M. Xiao, Y. Ma, K. Liu, K. Cheng, and Y. Zhang, "10 kV, 39 mΩ·cm2 Multi-Channel AlGaN/GaN Schottky Barrier Diodes," *IEEE Electron Device Lett.*, vol. 42, no. 6, pp. 808–811, Jun. 2021, doi: 10.1109/LED.2021.3076802.

- [4] E. A. Jones, F. F. Wang, and D. Costinett, "Review of Commercial GaN Power Devices and GaN-Based Converter Design Challenges," *IEEE J. Emerg. Sel. Top. Power Electron.*, vol. 4, no. 3, pp. 707–719, Sep. 2016, doi: 10.1109/JESTPE.2016.2582685.

- [5] J. P. Kozak, R. Zhang, M. Porter, Q. Song, J. Liu, B. Wang, R. Wang, W. Saito, and Y. Zhang, "Stability, Reliability, and Robustness of GaN Power Devices: A Review," *IEEE Trans. Power Electron.*, vol. 38, no. 7, pp. 8442–8471, Jul. 2023, doi: 10.1109/TPEL.2023.3266365.

- [6] M. Xiao, Y. Ma, Z. Du, V. Pathirana, K. Cheng, A. Xie, E. Beam, Y. Cao, F. Udrea, H. Wang, and Y. Zhang, "Multi-Channel Monolithic-Cascode HEMT (MC2-HEMT): A New GaN Power Switch up to 10 kV," in 2021 IEEE International Electron Devices Meeting (IEDM), Dec. 2021, p. 5.5.1-5.5.4. doi: 10.1109/IEDM19574.2021.9720714.

- [7] T. Oka, "Recent development of vertical GaN power devices," Jpn. J. Appl. Phys., vol. 58, no. SB, p. SB0805, Apr. 2019, doi: 10.7567/1347-4065/ab02e7.

- [8] J. Liu, M. Xiao, R. Zhang, S. Pidaparthi, H. Cui, A. Edwards, M. Craven, L. Baubutr, C. Drowley, and Y. Zhang, "1.2-kV Vertical GaN Fin-JFETs: High-Temperature Characteristics and Avalanche Capability," *IEEE Trans. Electron Devices*, vol. 68, no. 4, pp. 2025–2032, Apr. 2021, doi: 10.1109/TED.2021.3059192.

- [9] W. Götz, N. M. Johnson, J. Walker, D. P. Bour, H. Amano, and I. Akasaki, "Hydrogen passivation of Mg acceptors in GaN grown by metalorganic chemical vapor deposition," *Appl. Phys. Lett.*, vol. 67, no. 18, pp. 2666–2668, Oct. 1995, doi: 10.1063/1.114330.

- [10] S. Nakamura, N. Iwasa, M. S. M. Senoh, and T. M. T. Mukai, "Hole Compensation Mechanism of P-Type GaN Films," *Jpn. J. Appl. Phys.*, vol. 31, no. 5R, p. 1258, May 1992, doi: 10.1143/JJAP.31.1258.

- [11] M. Malinverni, D. Martin, and N. Grandjean, "InGaN based micro light emitting diodes featuring a buried GaN tunnel junction," *Appl. Phys. Lett.*, vol. 107, no. 5, p. 051107, Aug. 2015, doi: 10.1063/1.4928037.

- [12] W. Li, K. Nomoto, K. Lee, S. M. Islam, Z. Hu, M. Zhu, X. Gao, J. Xie, M. Pilla, D. Jena, and H. G. Xing, "Activation of buried p-GaN in MOCVD-regrown vertical structures," *Appl. Phys. Lett.*, vol. 113, no. 6, p. 062105, Aug. 2018, doi: 10.1063/1.5041879.

- [13] Y. Zhang, F. Udrea, and H. Wang, "Multidimensional device architectures for efficient power electronics," *Nat. Electron.*, vol. 5, no. 11, Art. no. 11, Nov. 2022, doi: 10.1038/s41928-022-00860-5.

- [14] S. Chowdhury, B. L. Swenson, and U. K. Mishra, "Enhancement and Depletion Mode AlGaN/GaN CAVET With Mg-Ion-Implanted GaN as Current Blocking Layer," *IEEE Electron Device Lett.*, vol. 29, no. 6, pp. 543–545, Jun. 2008, doi: 10.1109/LED.2008.922982.

- [15] T. Oka, Y. Ueno, T. Ina, and K. Hasegawa, "Vertical GaN-based trench metal oxide semiconductor field-effect transistors on a free-standing GaN substrate with blocking voltage of 1.6 kV," *Appl. Phys. Express*, vol. 7, no. 2, p. 021002, Jan. 2014, doi: 10.7567/APEX.7.021002.

- [16] C. Gupta, C. Lund, S. H. Chan, A. Agarwal, J. Liu, Y. Enatsu, S. Keller, and U. K. Mishra, "In Situ Oxide, GaN Interlayer-Based Vertical Trench MOSFET (OG-FET) on Bulk GaN substrates," *IEEE Electron Device Lett.*, vol. 38, no. 3, pp. 353–355, Mar. 2017, doi: 10.1109/LED.2017.2649599.

- [17] M. Xiao, Y. Ma, Z. Du, Y. Qin, K. Liu, K. Cheng, F. Udrea, A. Xie, E. Beam, B. Wang, J. Spencer, M. Tadjer, T. Anderson, H. Wang, and Y. Zhang, "First Demonstration of Vertical Superjunction Diode in GaN," in 2022 International Electron Devices Meeting (IEDM), Dec. 2022, p. 35.6.1-35.6.4. doi: 10.1109/IEDM45625.2022.10019405.

- [18] S. M. Myers, A. F. Wright, G. A. Petersen, W. R. Wampler, C. H. Seager, M. H. Crawford, and J. Han, "Diffusion, release, and uptake of hydrogen in magnesium-doped gallium nitride: Theory and experiment," *J. Appl. Phys.*, vol. 89, no. 6, pp. 3195–3202, Mar. 2001, doi: 10.1063/1.1347410.

- [19] C. H. Seager, S. M. Myers, A. F. Wright, D. D. Koleske, and A. A. Allerman, "Drift, diffusion, and trapping of hydrogen in p-type GaN," J. Appl. Phys., vol. 92, no. 12, pp. 7246–7252, Dec. 2002, doi: 10.1063/1.1520719.

- [20] Y. Kuwano, M. Kaga, T. Morita, K. Yamashita, K. Yagi, M. Iwaya, T. Takeuchi, S. Kamiyama, and I. Akasaki, "Lateral Hydrogen Diffusion at p-GaN Layers in Nitride-Based Light Emitting Diodes with Tunnel Junctions," *Jpn. J. Appl. Phys.*, vol. 52, no. 8S, p. 08JK12, Aug. 2013, doi: 10.7567/JJAP.52.08JK12.

- [21] T. Narita, N. Ikarashi, K. Tomita, K. Kataoka, and T. Kachi, "Wide range doping control and defect characterization of GaN layers with various Mg concentrations," *J. Appl. Phys.*, vol. 124, no. 16, p. 165706, Oct. 2018, doi: 10.1063/1.5045257.

- [22] T. Narita, K. Tomita, Y. Tokuda, T. Kogiso, M. Horita, and T. Kachi, "The origin of carbon-related carrier compensation in p-type GaN layers grown by MOVPE," *J. Appl. Phys.*, vol. 124, no. 21, p. 215701, Dec. 2018, doi: 10.1063/1.5057373.

- [23] T. Narita, H. Yoshida, K. Tomita, K. Kataoka, H. Sakurai, M. Horita, M. Bockowski, N. Ikarashi, J. Suda, T. Kachi, and Y. Tokuda, "Progress on and challenges of p-type formation for GaN power devices," *J. Appl. Phys.*, vol. 128, no. 9, p. 090901, Sep. 2020, doi: 10.1063/5.0022198.

- [24] D. Ji, B. Ercan, and S. Chowdhury, "Experimental determination of impact ionization coefficients of electrons and holes in gallium nitride using homojunction structures," *Appl. Phys. Lett.*, vol. 115, no. 7, p. 073503, Aug. 2019, doi: 10.1063/1.5099245.

- [25] T. Maeda, T. Narita, H. Ueda, M. Kanechika, T. Uesugi, T. Kachi, T. Kimoto, M. Horita, and J. Suda, "Shockley–Read–Hall lifetime in homoepitaxial p-GaN extracted from recombination current in GaN p–n+ junction diodes," *Jpn. J. Appl. Phys.*, vol. 58, no. SC, p. SCCB14, May 2019, doi: 10.7567/1347-4065/ab07ad.

- [26] T. Maeda, T. Narita, S. Yamada, T. Kachi, T. Kimoto, M. Horita, and J. Suda, "Impact ionization coefficients and critical electric field in GaN," J. Appl. Phys., vol. 129, no. 18, p. 185702, May 2021, doi: 10.1063/5.0050793.

- [27] T. Maeda, T. Narita, S. Yamada, T. Kachi, T. Kimoto, M. Horita, and J. Suda, "Breakdown Electric Field of GaN p+-n and p-n+ Junction Diodes With Various Doping Concentrations," *IEEE Electron Device Lett.*, vol. 43, no. 1, pp. 96–99, Jan. 2022, doi: 10.1109/LED.2021.3125328.

- [28] Y. Ma, M. Xiao, Z. Du, L. Wang, E. Carlson, L. Guido, H. Wang, L. Wang, Y. Luo, and Y. Zhang, "Activating Thick Buried p-GaN for Device Applications," *IEEE Trans. Electron Devices*, vol. 69, no. 8, pp. 4224–4230, Aug. 2022, doi: 10.1109/TED.2022.3186652.

- [29] Y. Ma, M. Porter, Y. Qin, J. Spencer, Z. Du, M. Xiao, Y. Wang, I. Kravchenko, D. P. Briggs, D. K. Hensley, F. Udrea, M. Tadjer, H. Wang, and Y. Zhang, "1 kV Self-Aligned Vertical GaN Superjunction Diode," *IEEE Electron Device Lett.*, vol. 45, no. 1, pp. 12–15, Jan. 2024, doi: 10.1109/LED.2023.3332855.

- [30] M. Xiao, R. Zhang, D. Dong, H. Wang, and Y. Zhang, "Design and Simulation of GaN Superjunction Transistors With 2-DEG Channels and Fin Channels," *IEEE J. Emerg. Sel. Top. Power Electron.*, vol. 7, no. 3, pp. 1475–1484, Sep. 2019, doi: 10.1109/JESTPE.2019.2912978.

- [31] Y. Zhang, M. Sun, Z. Liu, D. Piedra, J. Hu, X. Gao, and T. Palacios, "Trench formation and corner rounding in vertical GaN power devices," *Appl. Phys. Lett.*, vol. 110, no. 19, p. 193506, May 2017, doi: 10.1063/1.4983558.

- [32] T. Nakamura, N. Ishida, K. Sagisaka, and Y. Koide, "Surface potential imaging and characterizations of a GaN p-n junction with Kelvin probe force microscopy," *AIP Adv.*, vol. 10, no. 8, p. 085010, Aug. 2020, doi: 10.1063/5.0007524.

- [33] T.-H. Kim, K. Fu, C. Yang, Y. Zhao, and E. T. Yu, "Electronic structure of epitaxially grown and regrown GaN pn junctions characterized by scanning Kelvin probe and capacitance microscopy," *J. Appl. Phys.*, vol. 131, no. 1, p. 015704, Jan. 2022, doi: 10.1063/5.0071422.

- [34] M. Xiao, X. Yan, J. Xie, E. Beam, Y. Cao, H. Wang, and Y. Zhang, "Origin of leakage current in vertical GaN devices with nonplanar regrown p-GaN," *Appl. Phys. Lett.*, vol. 117, no. 18, p. 183502, Nov. 2020, doi: 10.1063/5.0021374.

- [35] G. Miceli and A. Pasquarello, "Self-compensation due to point defects in Mg-doped GaN," Phys. Rev. B, vol. 93, no. 16, p. 165207, Apr. 2016, doi: 10.1103/PhysRevB.93.165207.

- [36] H. Kang and F. Udrea, "Theory of 3-D Superjunction MOSFET," *IEEE Trans. Electron Devices*, vol. 66, no. 12, pp. 5254–5259, Dec. 2019, doi: 10.1109/TED.2019.2947332.

- [37] T. Narita, K. Tomita, S. Yamada, and T. Kachi, "Quantitative investigation of the lateral diffusion of hydrogen in p-type GaN layers having NPN structures," *Appl. Phys. Express*, vol. 12, no. 1, p. 011006, Dec. 2018, doi: 10.7567/1882-0786/aaf418.

- [38] Y. Zhang, M. Sun, Z. Liu, D. Piedra, H.-S. Lee, F. Gao, T. Fujishima, and T. Palacios, "Electrothermal Simulation and Thermal Performance Study of GaN Vertical and Lateral Power Transistors," *IEEE Trans. Electron Devices*, vol. 60, no. 7, pp. 2224–2230, Jul. 2013, doi: 10.1109/TED.2013.2261072.

- [39] R. Zhang, J. P. Kozak, M. Xiao, J. Liu, and Y. Zhang, "Surge-Energy and Overvoltage Ruggedness of P-Gate GaN HEMTs," *IEEE Trans. Power Electron.*, vol. 35, no. 12, pp. 13409–13419, Dec. 2020, doi: 10.1109/TPEL.2020.2993982.

- [40] M. Xiao, X. Gao, T. Palacios, and Y. Zhang, "Leakage and breakdown mechanisms of GaN vertical power FinFETs," Appl. Phys. Lett., vol. 114, no. 16, p. 163503, Apr. 2019, doi: 10.1063/1.5092433.

- [41] Y. Ma, Y. Qin, M. Porter, J. Spencer, Z. Du, M. Xiao, B. Wang, Y. Wang, A. G. Jacobs, H. Wang, M. Tadjer, and Y. Zhang, "Wide-Bandgap Nickel Oxide with Tunable Acceptor Concentration for Multidimensional Power Devices," *Adv. Electron. Mater.*, vol. n/a, no. n/a, p. 2300662, doi: 10.1002/aelm.202300662.

- [42] Y. Zhang, H. Y. Wong, M. Sun, S. Joglekar, L. Yu, N. A. Braga, R. V. Mickevicius, and T. Palacios, "Design space and origin of off-state leakage in GaN vertical power diodes," in 2015 IEEE International Electron Devices Meeting (IEDM), Dec. 2015, p. 35.1.1-35.1.4. doi: 10.1109/IEDM.2015.7409830.

- [43] D. V. Kuksenkov, H. Temkin, A. Osinsky, R. Gaska, and M. A. Khan, "Origin of conductivity and low-frequency noise in reverse-biased GaN p-n junction," *Appl. Phys. Lett.*, vol. 72, no. 11, pp. 1365–1367, Mar. 1998, doi: 10.1063/1.121056.

- [44] D.-P. Han, C.-H. Oh, H. Kim, J.-I. Shim, K.-S. Kim, and D.-S. Shin, "Conduction Mechanisms of Leakage Currents in InGaN/GaN-Based Light-Emitting Diodes," *IEEE Trans. Electron Devices*, vol. 62, no. 2, pp. 587–592, Feb. 2015, doi: 10.1109/TED.2014.2381218.

- [45] B. Wang, M. Xiao, X. Yan, H. Y. Wong, J. Ma, K. Sasaki, H. Wang, and Y. Zhang, "High-voltage vertical Ga2O3 power rectifiers operational at high temperatures up to 600 K," *Appl. Phys. Lett.*, vol. 115, no. 26, p. 263503, Dec. 2019, doi: 10.1063/1.5132818.

- [46] J. A. Cooper and D. T. Morisette, "Performance Limits of Vertical Unipolar Power Devices in GaN and 4H-SiC," *IEEE Electron Device* Lett., vol. 41, no. 6, pp. 892–895, Jun. 2020, doi: 10.1109/LED.2020.2987282.

- [47] L. Cao, J. Wang, G. Harden, H. Ye, R. Stillwell, A. J. Hoffman, and P. Fay, "Experimental characterization of impact ionization coefficients for electrons and holes in GaN grown on bulk GaN substrates," *Appl. Phys. Lett.*, vol. 112, no. 26, p. 262103, Jun. 2018, doi: 10.1063/1.5031785.

- [48] L. Cao, Z. Zhu, G. Harden, H. Ye, J. Wang, A. Hoffman, and P. J. Fay, "Temperature Dependence of Electron and Hole Impact Ionization Coefficients in GaN," *IEEE Trans. Electron Devices*, vol. 68, no. 3, pp. 1228–1234, Mar. 2021, doi: 10.1109/TED.2021.3054355.

- [49] B. J. Baliga, "Breakdown Voltage," in Fundamentals of Power Semiconductor Devices, B. J. Baliga, Ed., Cham: Springer International Publishing, 2019, pp. 89–170. doi: 10.1007/978-3-319-93988-9\_3.

- [50] O. Slobodyan, J. Flicker, J. Dickerson, J. Shoemaker, A. Binder, T. Smith, S. Goodnick, R. Kaplar, and M. Hollis, "Analysis of the dependence of critical electric field on semiconductor bandgap," *J. Mater. Res.*, vol. 37, no. 4, pp. 849–865, Feb. 2022, doi: 10.1557/s43578-021-00465-2.