# Reducing the Barrier Height in Organic Transistors

Arash Ghobadi, Cherian J. Mathai, Jacob Cook, Guang Bian, Salahuddin Attar, Mohammed Al-Hashimi, Shubhra Gangopadhyay,\* and Suchismita Guha\*

**Reducing the Schottky barrier height and Fermi level de-pinning in metal-organic semiconductor contacts are crucial for enhancing the performance of organic transistors. The reduction of the Schottky barrier height in bottom-contact top-gate organic transistors is demonstrated by adding 1 nm thick atomic layer deposited  $\text{Al}_2\text{O}_3$  on the source and drain contacts. By using two different donor-acceptor copolymers, both *p*- and *n*-type transistors are investigated. Temperature-dependent current–voltage measurements from non-treated, self-assembled monolayer treated, and  $\text{Al}_2\text{O}_3$  treated Au source-drain contact field-effect transistors with varying channel lengths are carried out. The drain current versus drain voltage near zero gate voltage, which may be described by the thermionic emission model at temperatures above 150 K, allows the estimation of the Schottky barrier height ( $\varphi_B$ ). The  $\text{Al}_2\text{O}_3$  contact-treated transistors show more than 40% lower  $\varphi_B$  compared with the non-treated contacts in the *p*-type transistor. Similarly, an isoindigo-based transistor, with *n*-type transport, shows a reduction in  $\varphi_B$  with  $\text{Al}_2\text{O}_3$  treated contacts suggesting that such ultrathin oxide layers provide a universal method for reducing the barrier height.**

## 1. Introduction

The past 20 years have seen a revolution in flexible and wearable electronics owing to the extensive research and development in organic semiconductors and device engineering, enabling efficient charge injection and extraction, the two most important elements in organic light-emitting diodes (OLEDs) and organic solar cells. OLEDs are now an integral part of consumer electronics, offering a viable path for flexible displays.<sup>[1]</sup> Organic transistors, on the other hand, which were thought to be an alternative to inorganic transistors for large-area integrated circuits, have yet to achieve the same status as OLEDs in consumer electronics. Organic transistors still struggle to attain transit frequencies  $>10$  MHz, although there are a few reports of transit frequencies  $>20$  MHz.<sup>[2–4]</sup> Compared to inorganic semiconductors, where metal oxide semiconductor field-effect transistors (MOSFETs)

and gallium nitride high electron mobility transistors routinely achieve  $R_c$  (channel-width normalized contact resistance) as low as  $0.01 \Omega\text{cm}$ ,<sup>[5,6]</sup> organic transistors typically show  $R_c$  in the range of  $100 \text{ k}\Omega\text{cm}$ , and at best  $100 \Omega\text{cm}$ .<sup>[7]</sup> Thus far, the strategies for lowering  $R_c$  in organic transistors have mainly focused on controlling the thin-film morphology near the source-drain contacts by using self-assembled monolayers and/or exploiting solution processing conditions for polymeric semiconductors.<sup>[8–10]</sup> Combining contact modification and using extremely thin gate dielectrics have resulted in the value of  $R_c$  to be just under  $30 \Omega\text{cm}$ ,<sup>[11]</sup> and with a transfer metal contact technique,  $R_c$  of  $14 \Omega\text{cm}$  has been achieved in  $C_{10}$ -DNNT transistors.<sup>[12]</sup> Few efforts have been aimed at reducing the Schottky barrier height by de-pinning the Fermi level for improving the performance of organic field-effect transistors (FETs). This barrier refers to the energy mismatch between the Fermi level of the metal contact and the majority carrier band edge.

Most organic FETs operate in the accumulation region, where charge injection, and thus the contact work function of the metal ( $\varphi_m$ ), is a key parameter. Obtaining Ohmic contact at the metal-organic semiconductor interface is a challenge due to the formation of a Schottky barrier ( $\varphi_B$ ), an interface dipole barrier ( $\Delta$ ), an interfacial van der Waals gap ( $d_{vdW}$ ), and the width of the depletion region. Although there are several strategies for reducing  $\Delta$  and  $d_{vdW}$ , for example by adding self-assembled monolayers

A. Ghobadi, J. Cook

Department of Physics and Astronomy

University of Missouri

Columbia, MO 65211, USA

C. J. Mathai, S. Gangopadhyay

Department of Electrical Engineering and Computer Science

University of Missouri

Columbia, MO 65211, USA

E-mail: [gangopadhyays@missouri.edu](mailto:gangopadhyays@missouri.edu)

G. Bian, S. Guha

Department of Physics and Astronomy and MU Materials Science and

Engineering Institute

University of Missouri

Columbia, MO 65211, USA

E-mail: [guhas@missouri.edu](mailto:guhas@missouri.edu)

S. Attar, M. Al-Hashimi

Department of Chemical Engineering

Texas A&M University at Qatar

Doha 23874, Qatar

The ORCID identification number(s) for the author(s) of this article can be found under <https://doi.org/10.1002/aelm.202400503>

© 2024 The Author(s). Advanced Electronic Materials published by Wiley-VCH GmbH. This is an open access article under the terms of the [Creative Commons Attribution](#) License, which permits use, distribution and reproduction in any medium, provided the original work is properly cited.

DOI: [10.1002/aelm.202400503](https://doi.org/10.1002/aelm.202400503)

to the contacts,<sup>[13]</sup> such strategies do not necessarily alter the final barrier heights if the Fermi level gets “pinned.” Since  $R_c$  depends on  $\varphi_B$ , a reduction in the barrier height reduces the contact resistance as well. A recurring theme in inorganic semiconductors such as GaAs is the problem of Fermi level pinning due to the formation of interfacial mid-gap states.<sup>[14]</sup> The consequence of such states in organic semiconductors is that the Fermi level may be pinned with respect to the transport levels, implying that the changes in the contact work function are independent of the electron/hole barrier heights. Although the barrier height may only have a moderate influence on the FET channel current and the device geometry and processing conditions strongly impact the FET performance,<sup>[15]</sup> insights from 2D materials-metal interfaces highlight the role metal-induced mid-gap states, which may induce semiconductor to metal transitions.<sup>[16]</sup> Metal-induced gap states are intrinsic to organic FETs employing contact metals such as Au, which have a high density of states at the Fermi level. It is, therefore, important to reinvestigate the correlation between the barrier height, de-pinning the Fermi level by filling the mid-gap states, and FET performance including universal strategies for de-pinning the Fermi level in both *p*- and *n*-type transport.

There have been recent efforts in reducing the barrier height in organic FETs. Introducing oxygen between the metal and the organic semiconducting layer is seen to greatly reduce  $R_c$ , resulting in carrier mobilities as high as  $11 \text{ cm}^2 \text{ Vs}^{-1}$  in  $C_{10}\text{-DNTT}$ -based FETs.<sup>[17]</sup> However, this method is beneficial only for *p*-type FETs and not for *n*-type transport, suggesting that a more universal method should be sought after for reducing the barrier height in organic transistors. As such, doping the semiconductor is a means for reducing the barrier height and has been demonstrated to significantly enhance the performance of organic FETs.<sup>[18,19]</sup> However, contact doping can be challenging in organic FETs due to the diffusion of dopants within the bulk and the presence of counterions, which can deteriorate the transport characteristics. The use of an interlayer with a higher ionization energy compared with the organic semiconductor is seen to assist the formation of an Ohmic contact for hole injection in organic diodes by a realignment of the Fermi level.<sup>[20]</sup> A similar strategy by choosing an interlayer with a lower electron affinity compared with the organic semiconductor helps achieve Ohmic electron injection in diodes.<sup>[21]</sup> However, since some of these interlayers readily dissolve in solvents used for dissolving the organic semiconductor, bottom-contact FETs may suffer. Moreover, since Au contacts are ubiquitous for several classes of organic semiconductors for both *p*- and *n*-type transport in FETs, a robust route toward reducing  $\varphi_B$  is required.

In metal-inorganic semiconductor interfaces, the incorporation of a thin dielectric layer has been known to reduce  $\varphi_B$  by de-pinning the Fermi level.<sup>[22,23]</sup> In Ti/n-Si, for example, a 1 nm thick  $\text{TiO}_2$  interfacial layer reduces  $\varphi_B$  by 55% compared with the architecture that has no  $\text{TiO}_2$  layer.<sup>[24]</sup> The barrier layer, however, may effectively reduce the tunneling probability and injection efficiency. Hence, one must judiciously tune the thickness of the barrier layer to obtain the full benefit of de-pinning along with high carrier injection. A similar approach was used in top-contact bottom-gate (TCBG) pentacene FETs where a 1 nm thick metal-oxide layer in between a semiconducting pentacene layer and Au contacts was seen to reduce  $R_c$ , although this method was not shown to be universal for both *p*- and *n*-type transport.<sup>[25]</sup> More-

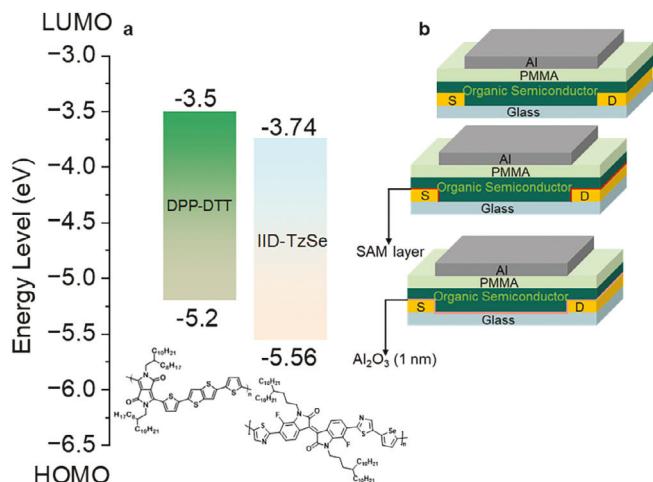

**Figure 1.** Energy levels and device architectures. a) Energy levels and chemical structures of the two copolymers: DPP-DTT and IID-TzSe. b) Device architectures with different treatments to the metal contacts.

over, the deposition of thin metal oxide layers on top of several classes of solution-processable polymeric semiconductors is not feasible. To modify metal-Si interfaces for achieving good Ohmic contacts, Zheng and co-workers used  $<1 \text{ nm}$   $\text{Al}_2\text{O}_3$  barrier layer embedded with sub-2 nm Pt nanoparticles.<sup>[26]</sup> This strategy not only resulted in a partial de-pinning of the Fermi level but also provided a mechanism for tuning  $\varphi_B$  by changing the size of the metal nanoparticles.

Taking a cue from metal-Si interfaces, in this work we add an ultrathin (1 nm) layer of atomic layer deposited (ALD)  $\text{Al}_2\text{O}_3$  on Au contacts in bottom contact top gate (BCTG) organic FET geometries. Two donor-acceptor copolymers were used as the active semiconducting layer and polymethylmethacrylate (PMMA) was used as the gate dielectric layer for fabricating the FETs. Diketopyrrolopyrrole (dithienylthieno[3,2-b]thiophene (DPP-DTT) predominantly served as *p*-type FETs and thiazole-selenophene linked fluorinated isoindigo (IID-TzSe) served as *n*-type FETs. Figure 1a,b shows the energy levels, chemical structures, and device architectures used in this work. We note that DPP-based copolymer may show ambipolarity and by tuning  $\varphi_m$  of the metal, both *p*- and *n*-type FETs have been demonstrated.<sup>[27,28]</sup> IID-TzSe also shows ambipolarity, although in BCTG architectures it exclusively shows *n*-type transport.<sup>[29]</sup> To further compare the effect of the ultrathin  $\text{Al}_2\text{O}_3$  layer on the contacts, DPP-DTT-based FETs with a self-assembled monolayer (SAM) layer treatment using pentafluorobenzenethiol (PFBT) were also employed. Detailed current-voltage measurements as a function of temperature reveal that the  $\text{Al}_2\text{O}_3$ -treated devices outperform the SAM layer-treated devices. By adopting the Schottky emission model at zero gate bias voltage, the temperature-dependent current-voltage measurements from the FETs allow an estimation of  $\varphi_B$ . The 1 nm  $\text{Al}_2\text{O}_3$  treated DPP-DTT FETs show a 40% reduction in  $\varphi_B$  compared with only 20% reduction in  $\varphi_B$  when PFBT is used. The reduction in  $\varphi_B$  is in comparison with the as-is (untreated) devices. Concomitantly, the *p*-type carrier mobility is also enhanced in  $\text{Al}_2\text{O}_3$ -treated DPP-DTT FETs. To demonstrate the universality of the  $\text{Al}_2\text{O}_3$  layer for reducing the barrier height, we developed IID-TzSe-based *n*-type

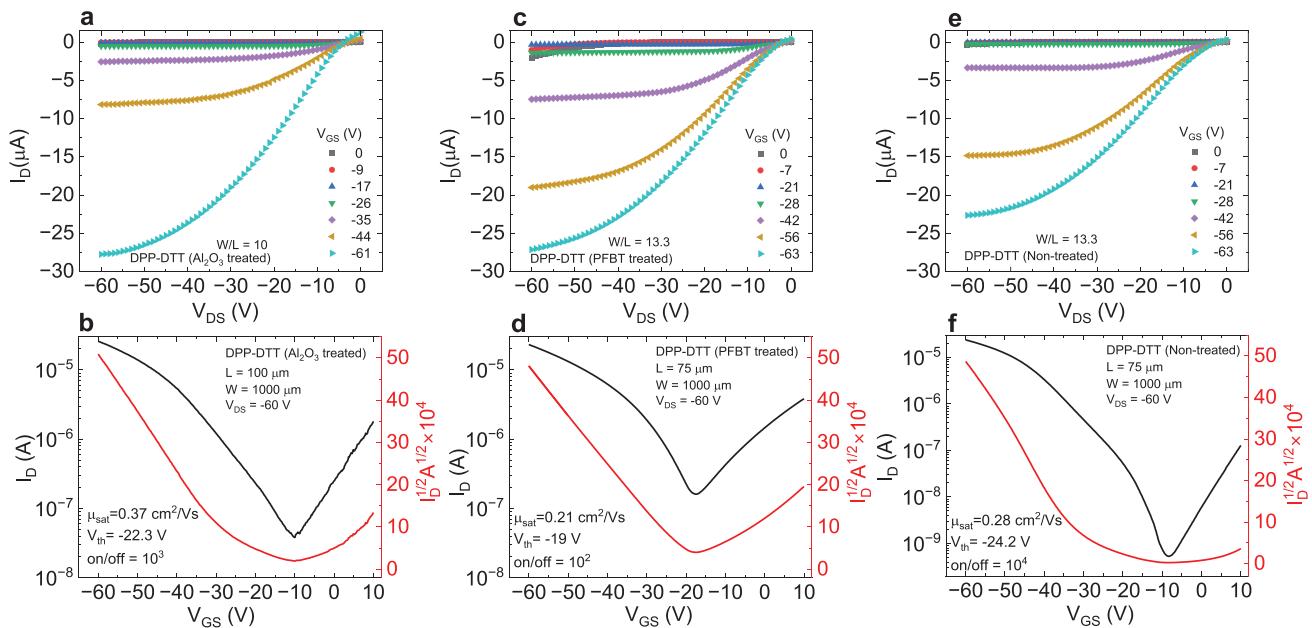

**Figure 2.** Output and transfer characteristics of DPP-DTT FETs. (a,b) represent an  $\text{Al}_2\text{O}_3$  treated FET with  $L = 100 \mu\text{m}$  and  $W = 1000 \mu\text{m}$ . c,d) represent a PFBT treated FET with  $L = 75 \mu\text{m}$  and  $W = 1000 \mu\text{m}$ . e,f) represent a non-treated FET with  $L = 75 \mu\text{m}$  and  $W = 1000 \mu\text{m}$ .

FETs. Again, the  $\text{Al}_2\text{O}_3$ -treated FETs show a lower  $\varphi_B$  compared with non-treated IID-TzSe FETs. Although the carrier mobilities are comparable, the threshold voltage, on/off ratio, and subthreshold swing are seen to significantly improve in the  $\text{Al}_2\text{O}_3$  barrier-modified IID-TzSe FETs compared with the non-treated devices. This work demonstrates that an ultrathin  $\text{Al}_2\text{O}_3$  layer in BCTG FET architectures enhances the injection of carriers from the metal to the semiconductor layer, irrespective of *p*- or *n*-type transport.

## 2. Results and Discussion

The growth of the 1 nm  $\text{Al}_2\text{O}_3$  layer on the Au contacts was accomplished using ALD as discussed in ref. [26]. Several optimization steps revealed that increasing the oxide layer to  $\geq 2$  nm deteriorates the transistor characteristics in DPP-DTT FETs most likely since a thicker layer impedes charge injection. Moreover, a thinner  $\text{Al}_2\text{O}_3$  layer of 0.5 nm resulted in no change in the FET characteristics of DPP-DTT FETs, suggesting that 1 nm thickness in within the optimized range. The FET carrier mobilities were determined in the saturation region from the transfer characteristics, where  $\mu_{sat} = \frac{2L}{W\tau_{ci}} \left( \frac{\partial \sqrt{I_D}}{\partial V_{GS}} \right)^2$ , by measuring the drain current ( $I_D$ ) as a function of the gate-source voltage ( $V_{GS}$ ) and by keeping the drain-source voltage ( $V_{DS}$ ) constant in the saturation region. Several FETs were tested with different channel length ( $L$ ) and width ( $W$ ). All the FETs reported here have  $W = 1000 \mu\text{m}$  with variable  $L$ . The on/off ratio and subthreshold swing (SS) demonstrate how distinct the “on” and “off” states are and how quickly the device switches between them, respectively. Temperature-dependent transfer and output characteristics were measured from FETs using both copolymers.

### 2.1. DPP-DTT Transistors

The highest occupied molecular orbital (HOMO) level of DPP-DTT is close to the  $\varphi_m$  of Au ( $\approx 5.0$  eV); hence with bare Au contacts, DPP-DTT FETs mainly display *p*-type transport. It should, however, be noted that substrates, inhomogeneities in surfaces, and deposition methods impact the  $\varphi_m$  of Au; a range of values from 4.6 to 5.6 eV has been reported in the literature.<sup>[30,31]</sup> Figure 2a-f shows the output and transfer characteristics at room temperature from three representative devices with  $\text{Al}_2\text{O}_3$  treated, PFBT treated, and non-treated Au contacts. The FET with 1 nm of  $\text{Al}_2\text{O}_3$  on Au contact shows the highest mobility of  $\mu_{sat} = 0.37 \text{ cm}^2 \text{ V}^{-1}\text{s}^{-1}$ . Several devices were measured and histograms of the carrier mobilities for  $\text{Al}_2\text{O}_3$ , PFBT, and non-treated FETs are presented in Figure S1 (Supporting Information). The PFBT-treated devices show slightly higher mean carrier mobility ( $0.28 \text{ cm}^2 \text{ V}^{-1}\text{s}^{-1}$ ) compared with the non-treated ones ( $0.22 \text{ cm}^2 \text{ V}^{-1}\text{s}^{-1}$ ) but the  $\text{Al}_2\text{O}_3$  treated FETs outperform with mean carrier mobility of  $0.41 \text{ cm}^2 \text{ V}^{-1}\text{s}^{-1}$ .

A shorter channel length ( $L = 50 \mu\text{m}$ ) of an  $\text{Al}_2\text{O}_3$  treated FET demonstrates  $\mu_{sat} = 0.81 \text{ cm}^2 \text{ V}^{-1}\text{s}^{-1}$  along with a more ambipolar transport, as seen in both the output and transfer characteristics (see Supporting Information). These values of  $\mu$  for DPP-DTT FETs (with  $\text{Al}_2\text{O}_3$  treatment) are similar to those obtained with contact-free nonlinear optical methods.<sup>[32]</sup> As proof of concept, we further show that a surface modification layer of polyethylenimine ethoxylated (PEIE) on the Au contacts in BCTG DPP-DTT based devices results in *n*-type transport, suggesting that it is easy to switch between *p*- and *n*-type transport in DPP-DTT. These results are shown in Figure S2 (Supporting Information). To further gain insights into the nature of transport and how the barrier height

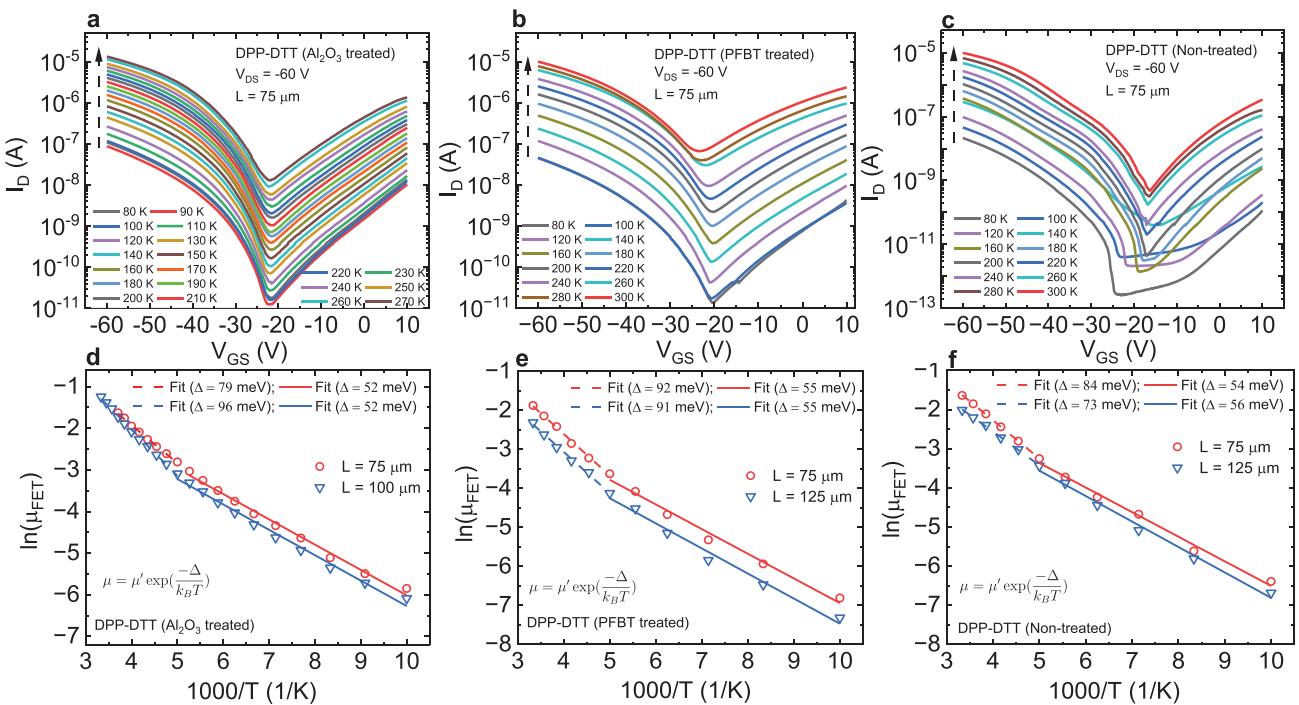

**Figure 3.** Temperature-dependent current–voltage measurements from DPP-DTT-based FETs. a–c) Temperature-dependent transfer characteristics of  $\text{Al}_2\text{O}_3$  treated, PFBT treated, and non-treated FETs. The dashed arrow denotes increasing temperature. d–f) Arrhenius plots of carrier mobilities from  $\text{Al}_2\text{O}_3$  treated, PFBT treated, and non-treated FETs for two different channel lengths ( $L$ ).

changes by adding a 1 nm thick  $\text{Al}_2\text{O}_3$  layer, temperature-dependent current–voltage measurements (80–300 K) were performed from representative DPP-DTT FETs with  $\text{Al}_2\text{O}_3$  treated, PFBT-treated, and non-treated Au contacts with different  $W/L$  ratios.

#### 2.1.1. Temperature-Dependent Current–Voltage Measurements

**Figure 3a–c** shows the transfer characteristics from three FETs as a function of temperature with contacts modified by  $\text{Al}_2\text{O}_3$ , PFBT, and a non-treated DPP-DTT FET. All three devices have the same channel  $L$  (75  $\mu\text{m}$ ) and  $W$  (1000  $\mu\text{m}$ ). Similar measurements were carried out for  $L = 50, 100$ , and 125  $\mu\text{m}$ . In each case, the current increases with increasing temperature.  $\mu_{\text{sat}}$  was determined at each temperature. **Figure 3d–f** shows the Arrhenius plots of  $\mu_{\text{sat}}$  for two different channel lengths for treated and non-treated FETs. All devices show a thermally activated transport, where the carrier mobility ( $\mu$ ) changes with temperature ( $T$ ), such that  $\mu = \mu' \exp\left(\frac{-\Delta}{k_B T}\right)$  with  $\mu'$  being the carrier mobility in the absence of traps,  $\Delta$  is the activation temperature and  $k_B$  is the Boltzmann constant. Two distinct regions are seen: 200–300 K and 100–200 K. The value of  $\Delta$  is smaller for all devices in the 100–200 K regions compared with the high-temperature range. The 200–300 K range shows slight variations but the overall trends across all three architectures at two different channel lengths are similar.

The  $I_D$ – $V_{DS}$  sweeps at  $V_{GS} = 0$  V can be described by the thermionic emission model, which is characterized by the

Richardson–Schottky equation, allowing the estimation of  $\varphi_B$ .<sup>[33]</sup> In this model, the current ( $I$ ) is given by:

$$I = AA^*T^2 \exp\left(\frac{-(\varphi_B - \sqrt{q^3V/4\pi\epsilon_0\epsilon_r d})}{k_B T}\right) \quad (1)$$

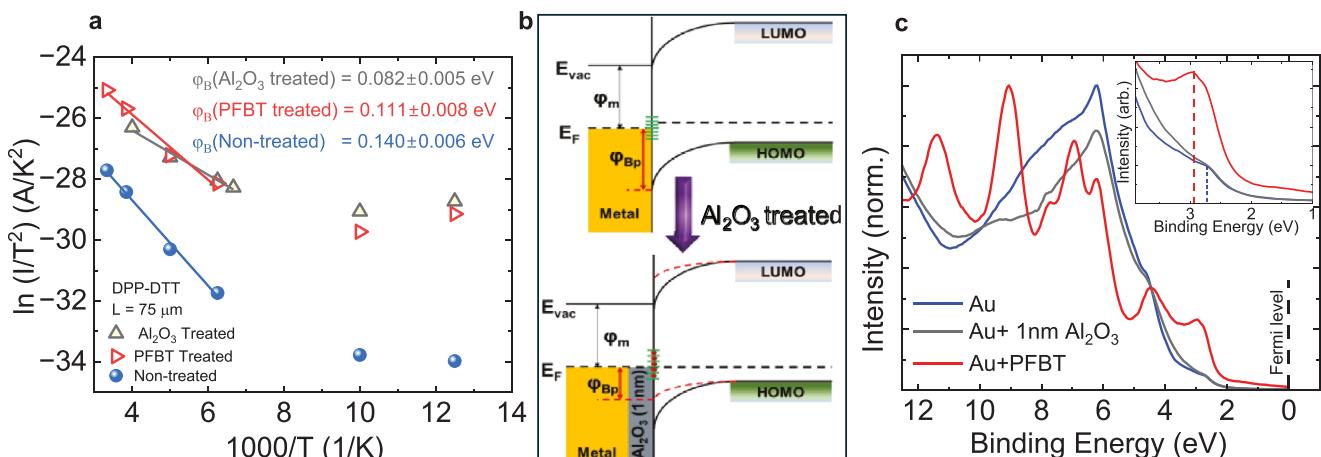

where  $A$  is the device area,  $A^*$  is the effective Richardson constant,  $\varphi_B$  is the Schottky barrier height,  $q$  is the element charge,  $V$  is the applied voltage between the S/D contacts,  $d$  translates to the channel length,  $\epsilon_0$  is the vacuum permittivity,  $\epsilon_r$  is the dielectric constant of the semiconductor, and  $k_B$  is the Boltzmann constant. **Figure 4a** plots  $\ln(I/T^2)$  versus  $1/T$  for the  $\text{Al}_2\text{O}_3$  treated, PFBT, and non-treated DPP-DTT FETs. Between 150 and 300 K, a linear region is seen, depicting the range for thermionic emission. The low-temperature region (<140 K) is representative of tunneling of carriers.<sup>[34]</sup> By assuming  $\epsilon_r$  to be 3 for DPP-DTT and from the slope, we estimate  $\varphi_B$  for the three devices. The  $\text{Al}_2\text{O}_3$  treated FET shows the lowest  $\varphi_B$  value of  $82 \pm 5$  meV compared with  $140 \pm 6$  meV for the non-treated device. The PFBT-treated FET yields a value of  $\varphi_B$  to be  $111 \pm 8$  meV.

Our results show that the PFBT SAM layer helps in reducing the barrier but is not effective as the 1 nm layer of  $\text{Al}_2\text{O}_3$ , suggesting that the Fermi level may still be pinned. **Figure 4b** shows a schematic of the energy levels with and without the  $\text{Al}_2\text{O}_3$  layer. ALD-grown  $\text{Al}_2\text{O}_3$  uses trimethylaluminum and deionized water (DI) as precursors, where the DI water promotes the formation of the OH bonds on the surface of the oxide film. It is likely that the OH groups on the  $\text{Al}_2\text{O}_3$  layer help in filling the trap states, thus de-pinning the Fermi level and reducing  $\varphi_B$ . The SAM layer

**Figure 4.** a) Comparison of  $I/T^2$  vs  $1/T$  characteristics of DPP-DTT FETs with  $\text{Al}_2\text{O}_3$  treated, PFBT treated, and non-treated contacts. The bold lines are fits to Equation (1). b) Schematic energy band diagrams for *p*-type transport where the Fermi level is pinned due to interface states (top) and with the application of a 1 nm  $\text{Al}_2\text{O}_3$  layer (bottom), which helps in de-pinning the Fermi level.  $\varphi_{Bp}$  denotes the Schottky barrier for the holes and  $\varphi_m$  represents the work function of the metal. c) UPS spectra for bare Au, Au + 1 nm  $\text{Al}_2\text{O}_3$ , and Au+PFBT. The inset shows a zoomed-in region with scaled intensities. The red and blue dashed lines depict the topmost peak position of Au 5d orbitals.

treatment, on the other hand, reduces  $\varphi_m$  without filling the traps; thus, the Fermi level remains partially pinned. This argument is further deduced from the estimation of the contact resistance. Using the transmission line method (TLM), the contact resistance ( $R_C$ ) normalized with  $W$  is related to the total resistance ( $R$ ) in the channel and is given by:

$$RW = R_C W + \frac{L}{\mu_{\text{eff}} C_i (V_{GS} - V_{Th})} \quad (2)$$

where  $\mu_{\text{eff}}$  is the effective mobility free from the contact resistance and  $V_{Th}$  is the threshold voltage. From three or four different devices with different  $W/L$  ratios,  $R_C W$  was estimated as 143 k $\Omega$  cm for the non-treated FET, 19.5 k $\Omega$  cm for the PFBT-treated FET, and 7 k $\Omega$  cm for the  $\text{Al}_2\text{O}_3$ -treated FET. See Figure S4 (Supporting Information) for the plots. These results show a similar order of magnitude for  $R_C W$  after treating with PFBT and with the thin  $\text{Al}_2\text{O}_3$  layer, suggesting that the further reduction of  $\varphi_B$  with  $\text{Al}_2\text{O}_3$ -treated FETs arises from a de-pinning of the Fermi level.

As a further check, we have measured the ultraviolet photoelectron spectra (UPS) from bare Au, Au treated with 1 nm  $\text{Al}_2\text{O}_3$ , and Au treated with PFBT. The filled valence states (0–12 eV binding energy) of the three samples are shown in Figure 4c. The intensities are normalized, and the Fermi edge is shown by the dashed line. We denote the occupied states below the Fermi edge as positive energies. The photon energy is 21.2 eV and the work function of photoelectron detector is 4.5 eV. The Au sample is grounded with the photoelectron detector; hence, direct determination of the work function of the metal (Au) is not feasible.<sup>[35]</sup> However, the data allows us to see the trends and to infer how the surface of Au behaves differently when treated with PFBT versus with  $\text{Al}_2\text{O}_3$ . The features in the UPS spectra from 2 to 6 eV mainly arise from the 5d band of Au. The sharp peaks from 6 to 8 eV in the PFBT+Au sample are from the pentafluorophenol ring.<sup>[36]</sup> A sample fit for the PFBT+Au interface is included in Supporting Information along with the peak positions (Figure S6, Support-

ing Information). The inset of Figure 4c shows a zoomed-in region  $\approx$  (2–3 eV). A clear peak shift is seen in PFBT+Au compared with bare Au and  $\text{Al}_2\text{O}_3$  on Au. The topmost peak from the Au 5d orbitals is marked by the red and blue dashed lines in the inset of Figure 4c. A shift in energy of the 5d electrons in PFBT+Au implies a change (of 0.2 eV) in the work function compared with bare Au due to the electron transfer from Au to PFBT. The UPS spectra of  $\text{Al}_2\text{O}_3$  on Au and bare Au, on the other hand, are almost identical, suggesting that the role of the thin  $\text{Al}_2\text{O}_3$  layer is mainly in depinning the Fermi level without altering the work function when interfaced with the organic semiconductor in FET architectures. To test the universality of such a thin oxide layer for reducing the barrier height in organic FETs, we investigated an *n*-type FET, the results of which are provided in the next section.

## 2.2. IID-TzSe Transistors

Another class of donor-acceptor copolymers based on electron-deficient Isoindigo (IID) units have attracted considerable attention in organic solar cells<sup>[37,38]</sup> and transistors.<sup>[39–41]</sup> Selenium substituted fluorinated IID (IID-TzSe), with chemical structure shown in Figure 1a, has been known to show *n*-type FET transport and combined with other *p*-type FETs has promising applications in complementary inverter circuits.<sup>[29,42]</sup> Using a similar ALD-grown 1 nm  $\text{Al}_2\text{O}_3$  on Au contacts as in the DPP-DTT devices, BCTG FETs were fabricated using IID-TzSe as the active semiconducting layer.

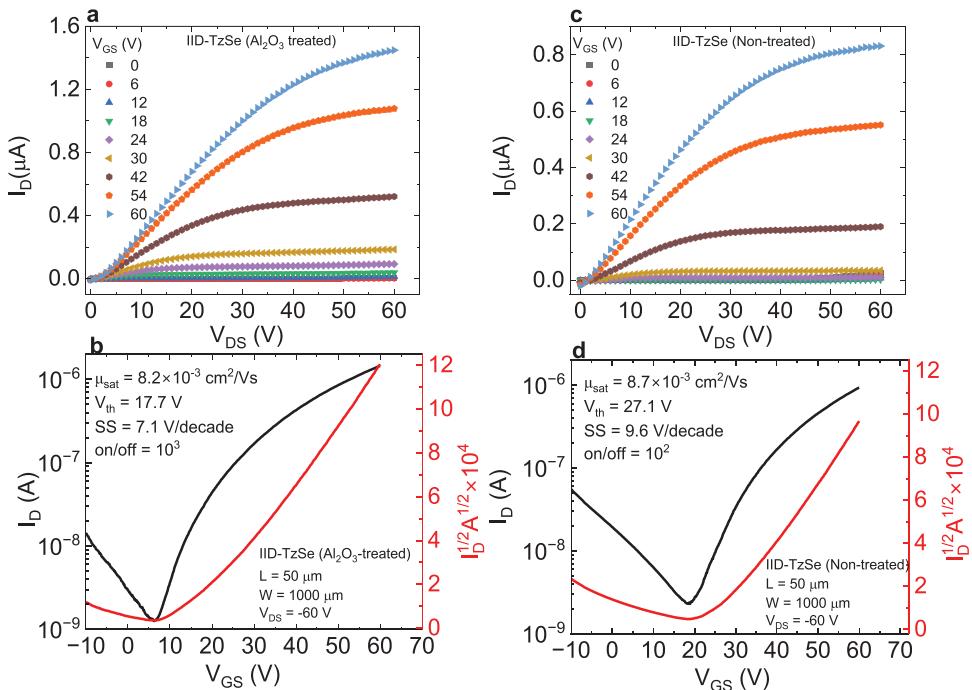

Figure 5a–d plots the output and transfer characteristics for two similar IID-TzSe FETs (with  $L = 50 \mu\text{m}$ ), one with  $\text{Al}_2\text{O}_3$  Au contacts and the other non-treated. Both FETs show *n*-type transport. Although the carrier mobilities are similar, the on/off ratio, SS, and  $V_{th}$  all seem to improve in the  $\text{Al}_2\text{O}_3$ -treated device.  $V_{th}$  decreases from 27 V in the non-treated to device to 17.7 V in the  $\text{Al}_2\text{O}_3$ -treated device. We note that the molecular weight of IID-TzSe in this work is different from ref. [29],

**Figure 5.** a,b) Output and transfer characteristics of an IID-TzSe FET with  $\text{Al}_2\text{O}_3$  treated contacts. c,d) Output and transfer characteristics of an IID-TzSe FET with non-treated contacts.

resulting in slightly lower carrier mobilities here. To determine  $\varphi_B$ , temperature-dependent current–voltage measurements were performed. The transfer characteristics further allow us to estimate  $\mu_{sat}$ ,  $V_{th}$ , and  $SS$  as a function of temperature.

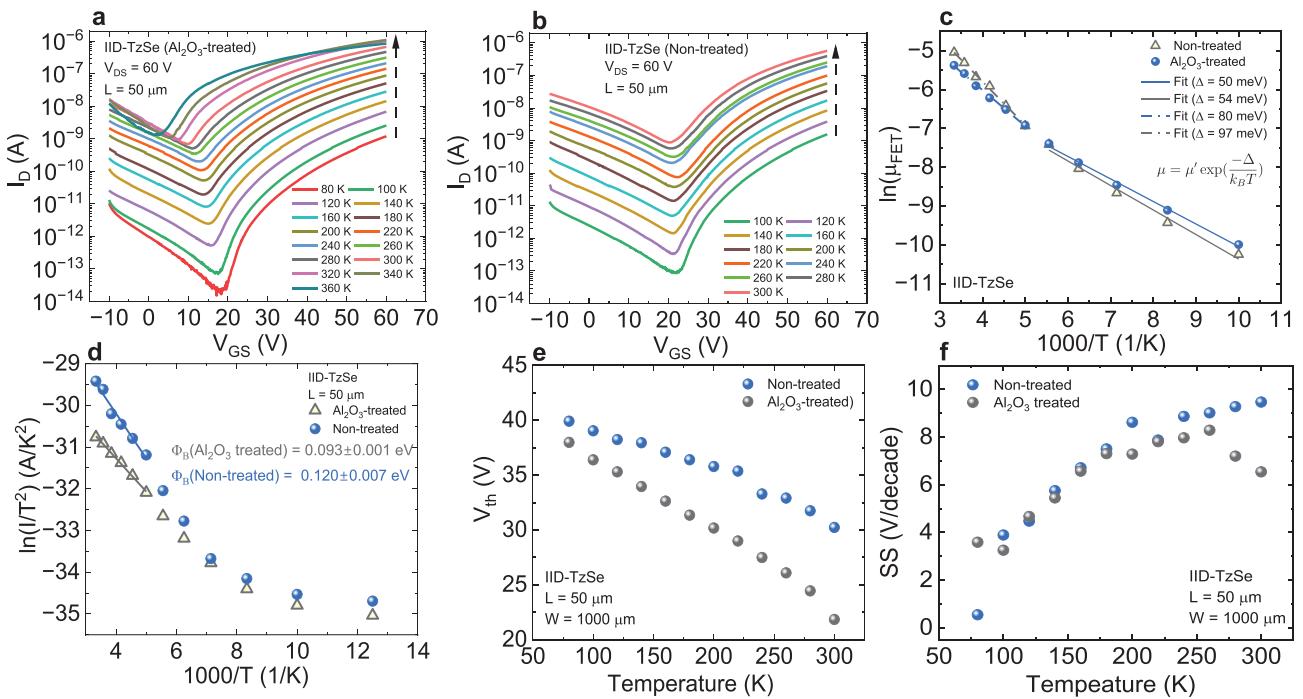

Figure 6a,b displays the transfer curves from IID-TzSe FETs with and without  $\text{Al}_2\text{O}_3$  treated contacts as a function of temperature. The  $\text{Al}_2\text{O}_3$  treated device was measured up to 360 K; beyond 340 K there is some degradation due to which all analysis has been carried out only till 300 K. The *n*-type carrier mobilities, extracted at each temperature, are plotted as natural log versus  $1/T$  in Figure 6c. Similar to the DPP-DTT FETs, an activated transport is seen with two temperature regimes. The high-temperature region (200–300 K) shows a similar activation barrier ( $\Delta \approx 90$  meV) for both treated and non-treated FETs. From the  $I_D$ - $V_{DS}$  sweeps at  $V_{GS} = 0$  V at different temperatures,  $I/T^2$  is obtained and plotted as a function of  $1/T$  in Figure 6d. Using Equation (1),  $\varphi_B$  is obtained as  $120 \pm 7$  meV for the non-treated device and  $93 \pm 1$  meV for the  $\text{Al}_2\text{O}_3$ -treated device. Thus, even for *n*-type transport in IID-TzSe, we observe more than 20% reduction in the Schottky barrier height. Although this reduction in  $\varphi_B$  does not strongly impact the carrier mobility, there is a reduction in  $V_{th}$  for  $\text{Al}_2\text{O}_3$ -treated IID-TzSe FETs at all temperatures compared with the non-treated device (Figure 6e). Similarly, at higher temperatures beyond 200 K, the  $SS$  values in the  $\text{Al}_2\text{O}_3$ -treated FET is lower compared with the non-treated FET.

An ultrathin 1 nm ALD-grown  $\text{Al}_2\text{O}_3$  on Au contacts universally reduces the barrier height for charge injection in both *p*- and *n*-type organic FETs. This contrasts other methods such as oxygen adsorption at the metal-semiconductor interface which mainly benefits *p*-type transport but not *n*-type transport in organic FETs.<sup>[17]</sup> The lowering of  $\varphi_B$  in both DPP-DTT and IID-

TzSe FETs with an ultrathin layer of  $\text{Al}_2\text{O}_3$  suggests that unlike SAM layers, which mainly alter the work function of the metal to better match the HOMO or the LUMO level of the semiconductor, the oxide layer helps in de-pinning the Fermi level by filling the interface mid-gap states (Figure 4b).

To gauge whether a combination of  $\text{Al}_2\text{O}_3$  and SAM layer may further improve the FET performance, we treated  $\text{Al}_2\text{O}_3$ -Au contacts with PFBT for fabrication of DPP-DTT FETs. Since the  $\text{Al}_2\text{O}_3$  layer is deposited at high temperatures, it is not possible to add the oxide layer on PFBT-treated contacts. These devices were fabricated with a different batch of the DPP-DTT copolymer; hence, the carrier mobilities are slightly lower than the ones shown in Figure 1. The FET current–voltage characteristics of  $\text{Al}_2\text{O}_3$ -treated and  $\text{Al}_2\text{O}_3$ +PFBT-treated devices are shown in Figure S7 (Supporting Information). Although the on/off ratios are similar, the carrier mobility is lower for the  $\text{Al}_2\text{O}_3$ +PFBT treated transistor, suggesting that a SAM layer can disrupt the effectiveness of the ultrathin oxide layer on the Au contact.

Solution-processed organic semiconductors pose a problem with top polymeric gate architectures due to solvent incompatibility. Since PMMA dissolved in DMSO does not affect the DPP-DTT or the IID-TzSe layers, we used PMMA as the dielectric layer. It should, however, be noted that the dielectric constant ( $\kappa$ ) of PMMA  $\leq 3.5$ , implies limitations in achieving low-operating voltage FETs. As seen for both DPP-DTT and IID-TzSe FETs, the saturation voltages here are close to 60 V. Such high voltages with polymer dielectrics can lead to substantial gate currents, reducing the overall performance of the transistors. Polymer ferroelectrics such as polyvinylidene (PVDF) with  $\kappa > 8$  are a good choice and can dramatically lower the operating voltages<sup>[43,44]</sup> but are difficult to integrate into top-gate architectures. It is conceivable that

**Figure 6.** a,b) Transfer characteristics of IID-TzSe FETs as a function of temperature with  $\text{Al}_2\text{O}_3$  treated contacts and non-treated contacts, respectively. The channel length and width are identical for both devices. The dashed arrow represents increasing temperature. c) Arrhenius plots of carrier mobilities for  $\text{Al}_2\text{O}_3$  treated and non-treated FETs. d-f) Comparison of  $I/T^2$ ,  $V_{th}$ , and SS as a function of temperature for  $\text{Al}_2\text{O}_3$  treated (grey circles) and non-treated (blue circles) FETs, respectively.

with a better choice of a dielectric layer such as a combination of a thin fluoropolymer and high  $\kappa$  oxide dielectric, the operating voltages of DPP-DTT and IID-TzSe FETs are reduced with further enhancement in carrier mobilities. Additional modifications to the  $\text{Al}_2\text{O}_3$  layer by embedding sub-2 nm metal nanoparticles, as realized in metal/Si interfaces,<sup>[26]</sup> may further aid in de-pinning the Fermi level and lowering  $\varphi_B$ . This work is a proof-of-concept that an ultrathin oxide layer improves charge injection for both *p*- and *n*-type transport. Reduction in the channel length would further benefit the performance of the devices. The processing conditions and molecular weight of the copolymers play a significant role in the chain conformation, and thus, in dictating the values of carrier mobilities, especially in DPP-based systems.<sup>[27,45]</sup> Future directions involving varying the processing conditions of the copolymers along with modifications of the ultrathin oxide layer with metal nanoparticles may further enhance the performance of organic FETs.

### 3. Conclusion

In summary, we report an effective strategy for modifying the contacts with an ultrathin oxide layer, which lowers the Schottky barrier height in both *p*- and *n*-type organic transistors. Unlike SAM layers that mainly alter the work function of the metal, the ultrathin  $\text{Al}_2\text{O}_3$  layer helps in filling up the trap states at the metal-semiconductor interface, thus de-pinning the Fermi level and reducing the overall barrier height. In DPP-DTT FETs, which demonstrate *p*-type transport,  $\varphi_B$  reduces from 140 meV to 82 meV when the Au contacts are treated with a 1 nm ALD-grown

$\text{Al}_2\text{O}_3$ . Similarly, for IID-TzSe FETs demonstrating *n*-type transport,  $\varphi_B$  reduces from 120 to 93 meV upon treating the contacts with  $\text{Al}_2\text{O}_3$ . This work reveals the importance of a relatively simple treatment of the metal contacts by an ultrathin oxide layer which has advantages to both *p*- and *n*-type transport in organic transistors for improving charge injection.

### 4. Experimental Section

**Materials:** The copolymer of DPP (DPP-DTT) was purchased from 1-Material Inc. (Dorval, Quebec, Canada). IID-TzSe was synthesized based on a protocol reported earlier.<sup>[29]</sup> All solvents were procured from Sigma-Aldrich. Pentafluorothiophenol (PFBT), polymethylmethacrylate (PMMA), and polyethylenimine ethoxylated (PEIE) were also purchased from Sigma-Aldrich.

**Device Fabrication:** 1" x 1" glass microscope slides were organically cleaned by rinsing and sonication in an acetone bath for 20 min, rinsing and sonication in an isopropanol bath for 20 min, and finally rinsing and sonication in a DI-water bath for 20 min. The substrates were then baked at 125 °C in an oven for 30 min to remove all moisture. 50 nm of Au contact was thermally evaporated onto the surface of the glass with a patterned mask for the source/drain contacts. Each substrate has four devices with the same channel width of 1000  $\mu\text{m}$  and varying channel lengths of 50, 75, 100, and 125  $\mu\text{m}$ . The substrates with the Au contacts were plasma cleaned for 10 min in a Harrick Plasma PDC-32G plasma cleaner at a chamber pressure between 300 and 500 mTorr of  $\text{O}_2$  gas. In one case, 10 mM concentration solution of PFBT was made by mixing 40  $\mu\text{L}$  of the PFBT solution in 30 mL of isopropanol. After mixing for 1 min, the cleaned substrates with the Au contacts were immersed in the mixture for 30 min to allow the monolayer to form. The substrates were then rinsed with isopropanol, submerged in an isopropanol bath, and then finally dried with either

compressed air or nitrogen gas. For the other substrates, 1 nm of  $\text{Al}_2\text{O}_3$  was deposited using atomic layer deposition (ALD), details of which are given below. To form the semiconducting film, DPP-DTT precursor solution was made by dissolving it in 1,2-dichlorobenzene (DCB) with a concentration of 5 mg  $\text{mL}^{-1}$ . A magnetic stirrer was added, and the solution was heated sequentially at 100 °C for 1 h, 130 °C for 1 h, and finally maintained at 145 °C for over 12 h while stirring at 200 RPM. The solution was then allowed to stir overnight at room temperature. The solution was filtered through a 0.45  $\mu\text{m}$  PTFE filter and then returned to the hotplate for  $\approx$ 30 min prior to spin-coating. 75  $\mu\text{L}$  of the DPP-DTT solution was dynamically spin-coated on the Au contacts at 900 RPM for 60 s under nitrogen atmosphere. The DPP-DTT film was restricted to a small channel during spin-coating by applying Teflon tape. After removing the Teflon tape, the film was annealed at 120 °C for an hour under nitrogen atmosphere. PMMA, used as the top gate dielectric, was dissolved in dimethyl sulfoxide (DMSO) at a concentration of 60 mg  $\text{mL}^{-1}$ , which was then heated at 80 °C and magnetically stirred for  $\approx$ 2 h. The PMMA thin film was formed by spin-coating at a spin speed of 5000 RPM for 60 s with 100  $\mu\text{L}$  being cast statically on the substrate. The PMMA film was then annealed at 100 °C for 20 min, resulting in a thickness of 170–200 nm. Finally, 50 nm of Al gate electrode was thermally evaporated on top of the PMMA layer.

The IID-TzSe precursor solution was prepared by dissolving IID-TzSe in 1,2-dichlorobenzene (DCB) at a concentration of 5 mg/mL. The solution was stirred ( $\approx$ 200 rpm) and heated at 100 °C (1 h), 135 °C (1 h), and finally at 145 °C ( $>$ 12 h). Subsequently, the solution was allowed to be stirred at room temperature overnight. The solution was filtered via 0.45  $\mu\text{m}$  PTFE filter and then returned to the hotplate ( $\approx$ 30 mins) prior to spin-coating. To deposit the IID-TzSe onto the Au contacts, 75  $\mu\text{L}$  of the solution was dynamically spin-coated at 900 RPM for 40 s under nitrogen atmosphere. Prior to the spin-coating process, Teflon tape was applied as a mask to pattern the IID-TzSe film onto a specific region. Following the removal of the tape, the film was annealed at 180 °C for 10 min under nitrogen atmosphere.

**ALD Deposition:** 1 nm of  $\text{Al}_2\text{O}_3$  was precisely deposited by Atomic Layer Deposition (ALD) employing the S200 system sourced from Cambridge NanoTech. This process involved introducing deionized water (DI-water) and trimethylaluminum (TMA) obtained from Sigma-Aldrich into the system. Both the chamber and the lid O-ring heater were set to 300 °C. Following sample loading, a continuous flow of 5 sccm  $\text{N}_2$  was introduced into the chamber, and then it was increased to 20 sccm. Deposition proceeded through 11 cycles, each consisting of 0.01 s pulse of DI-water, 8 s of  $\text{N}_2$  purge, 0.015 s pulse of TMA vapor, followed by another 8 s of  $\text{N}_2$  purge. The entire process lasted  $\approx$ 4 min. Upon completion of deposition, the  $\text{N}_2$  flow rate was reduced to 5 sccm, and the samples were ready for removal.

**Characterization:** Current–voltage (I–V) measurements under low temperature were performed using a Keithley 4200A-SCS parameter analyzer and a Janis cryogenic (liquid nitrogen flow) probe station. Room temperature I–V measurements were done both under ambient conditions as well under vacuum (33–55 mTorr). Low temperature I–V measurements were carried out from 80 K and upward. The UPS measurements were performed using a SPECS PHOIBOS 150 hemisphere analyzer with a SPECS UVS 300 helium discharge lamp ( $\text{He I-}E_{\text{ph}} = 21.2 \text{ eV}$ ).

## Supporting Information

Supporting Information is available from the Wiley Online Library or from the author.

## Acknowledgements

The authors acknowledge support of this work through the U.S. National Science Foundation (NSF) under Grant No. ECCS-2324839. G.B. was supported by the U.S. Department of Energy, Office of Science, Office of Basic Energy Sciences, Division of Materials Science and Engineering, under Grant No. DE-SC0024294.

## Conflict of Interest

The authors declare no conflict of interest.

## Author Contributions

A.G. fabricated the devices, conducted the electrical measurements, and analyzed the data. S.G. and S.G. conceived the work. C.M. optimized and performed the ALD and helped in the setup of low-temperature electrical measurements. S.A. and M.A.H. carried out the synthesis and characterization of the IID copolymer. J.C. and G.B. conducted the UPS measurements. S.G. and S.G. helped with the analysis of the data. The manuscript was written by S.G. and A.G. with contributions from all authors. All authors have approved the final version of the manuscript.

## Data Availability Statement

The data that support the findings of this study are available from the corresponding author upon reasonable request.

## Keywords

atomic layer deposition,  $\text{Al}_2\text{O}_3$ , donor-acceptor polymers, organic transistors, Schottky barrier

Received: July 8, 2024

Revised: September 4, 2024

Published online: October 4, 2024

- [1] A. Salehi, X. Fu, D.-H. Shin, F. So, *Adv. Funct. Mater.* **2019**, 29, 1808803.

- [2] J. W. Borchert, U. Zschieschang, F. Letzkus, M. Giorgio, R. T. Weitz, M. Cironi, J. N. Burghartz, S. Ludwigs, H. Klauk, *Sci. Adv.* **2020**, 6, eaaz5156.

- [3] T. Losi, Ł. Witczak, M. Łysieć, P. Rossi, P. Moretti, C. Bertarelli, V. Mattoli, M. Cironi, *Adv. Funct. Mater.* **2023**, 33, 2302656.

- [4] A. Yamamura, S. Watanabe, M. Uno, M. Mitani, C. Mitsui, J. Tsurumi, N. Isahaya, Y. Kanaoka, T. Okamoto, J. Takeya, *Sci. Adv.* **2018**, 4, eaao5758.

- [5] S. Datta, F. Assad, M. S. Lundstrom, *Superlattices Microstruct.* **1998**, 23, 771.

- [6] J. W. Chung, W. E. Hoke, E. M. Chumbes, T. Palacios, *IEEE Electron Device Lett.* **2010**, 31, 195.

- [7] M. Waldrip, O. D. Jurchescu, D. J. Gundlach, E. G. Bittle, *Adv. Funct. Mater.* **2020**, 30, 1904576.

- [8] C.-H. Kim, H. Hlaing, J.-A. Hong, J.-H. Kim, Y. Park, M. M. Payne, J. E. Anthony, Y. Bonnassieux, G. Horowitz, I. Kymmissis, *Adv. Mater. Interf.* **2015**, 2, 1400384.

- [9] S. Choi, C. Fuentes-Hernandez, C.-Y. Wang, T. M. Khan, F. A. Larrain, Y. Zhang, S. Barlow, S. R. Marder, B. Kippelen, *ACS Appl. Mater. Interfaces* **2016**, 8, 24744.

- [10] J. Roh, T. Lee, C. Kang, J. Kwak, P. Lang, G. Horowitz, H. Kim, C. Lee, *S. Rep. Sci. Rep.* **2017**, 7, 46365.

- [11] J. W. Borchert, B. Peng, F. Letzkus, J. N. Burghartz, P. K. L. Chan, K. Zojer, S. Ludwigs, H. Klauk, *Nat. Commun.* **2019**, 10, 1119.

- [12] J. Zeng, D. He, J. Qiao, Y. Li, L. Sun, W. Li, J. Xie, S. Gao, L. Pan, P. Wang, Y. Xu, Y. Li, H. Qiu, Y. Shi, J.-B. Xu, W. Ji, X. Wang, *Nat. Commun.* **2023**, 14, 324.

- [13] J. W. Borchert, R. T. Weitz, S. Ludwigs, H. Klauk, *Adv. Mater.* **2022**, 34, 2104075.

[14] R. T. Tung, *Phys. Rev. B* **2001**, *64*, 205310.

[15] D. J. Gundlach, L. Zhou, J. A. Nichols, T. N. Jackson, P. V. Necliuodov, M. S. Shur, *J. Appl. Phys.* **2006**, *100*, 024509.

[16] M. Dendzik, A. Bruix, M. Michiardi, A. S. Ngankeu, M. Bianchi, J. A. Miwa, B. Hammer, P. Hofmann, C. E. Sanders, *Phys. Rev. B* **2017**, *96*, 235440.

[17] Y. Fu, J. Zhu, Y. Sun, S. Sun, K. Tie, J. Qi, Y. Wang, Z. Wang, Y. Hu, S. Ding, R. Huang, Z. Gong, Y. Huang, X. Chen, L. Li, W. Hu, *ACS Nano* **2023**, *17*, 15044.

[18] B. Lüssem, C.-M. Keum, D. Kasemann, B. Naab, Z. Bao, K. Leo, *Chem. Rev.* **2016**, *116*, 13714.

[19] Y. Xu, H. Sun, A. Liu, H.-H. Zhu, W. Li, Y.-F. Lin, Y.-Y. Noh, *Adv. Mater.* **2018**, *30*, 1801830.

[20] N. B. Kotadiya, H. Lu, A. Mondal, Y. Ie, D. Andrienko, P. W. M. Blom, G.-J. A. H. Wetzelaer, *Nat. Mat.* **2018**, *17*, 329.

[21] D. Trieb, P. W. M. Blom, G.-J. A. H. Wetzelaer, *Adv. Mater. Interf.* **2023**, *10*, 2202424.

[22] D. Connelly, C. Faulkner, P. A. Clifton, D. E. Grupp, *Appl. Phys. Lett.* **2006**, *88*, 012105.

[23] D. R. Gajula, P. Baine, M. Modreanu, P. K. Hurley, B. M. Armstrong, D. W. McNeill, *Appl. Phys. Lett.* **2014**, *104*, 012102.

[24] A. Agrawal, J. Lin, M. Barth, R. White, B. Zheng, S. Chopra, S. Gupta, K. Wang, J. Gelatos, S. E. Mohney, S. Datta, *Appl. Phys. Lett.* **2014**, *104*, 112101.

[25] P. Darmawan, T. Minari, A. Kumataki, Y. Li, C. Liu, K. Tsukagoshi, *Appl. Phys. Lett.* **2012**, *100*, 013303.

[26] H. Zheng, B. K. Mahajan, S. C. Su, S. Mukherjee, K. Gangopadhyay, S. Gangopadhyay, *Sci. Rep.* **2016**, *6*, 25234.

[27] Y. Li, P. Sonar, L. Murphy, W. Hong, *Energy Environ. Sci.* **2013**, *6*, 1684.

[28] Y. Lei, P. Deng, J. Li, M. Lin, F. Zhu, T.-W. Ng, C.-S. Lee, B. S. Ong, *Sci. Rep.* **2016**, *6*, 24476.

[29] J. Barron, S. Attar, P. Bhattacharya, P. Yu, M. Al-Hashimi, S. Guha, *J. Mater. Chem. C* **2022**, *10*, 14653.

[30] J. W. Kim, A. Kim, H. U. Hwang, J. H. Kim, S. Choi, N. Koch, D. Shin, Z. Zhao, F. Liu, M. Choi, K. M. Lee, Y. Park, *J. Vac. Sci. Technol. A* **2023**, *41*, 053211.

[31] P. Borghetti, A. El-Sayed, E. Goiri, C. Rogero, J. Lobo-Checa, L. Floreano, J. E. Ortega, D. G. de Oteyza, *ACS Nano* **2014**, *8*, 12786.

[32] P. Bhattacharya, P. Yu, S. Guha, *Phys. Rev. Appl.* **2023**, *19*, 044059.

[33] S. M. Sze, K. K. Ng, *Physics of Semiconductor Devices*, John Wiley & Sons, Hoboken, NJ **2006**.

[34] H. S. Kang, J. W. Lee, M. K. Kim, J. Joo, J. M. Ko, J. Y. Lee, *J. Appl. Phys.* **2006**, *100*, 064508.

[35] H. Lee, Y. Zhang, L. Zhang, T. Mirabito, E. K. Burnett, S. Trahan, A. R. Mohebbi, S. C. B. Mannsfeld, F. Wudl, A. L. Briseno, *J. Mater. Chem. C* **2014**, *2*, 3361.

[36] F. von Wrochem, D. Gao, F. Scholz, H.-G. Nothofer, G. Nelles, J. M. Wessels, *Nat. Nanotechnol.* **2010**, *5*, 618.

[37] E. Wang, Z. Ma, Z. Zhang, K. Vandewal, P. Henriksson, O. Inganäs, F. Zhang, M. R. Andersson, *J. Am. Chem. Soc.* **2011**, *133*, 14244.

[38] Z. Ma, E. Wang, M. E. Jarvid, P. Henriksson, O. Inganäs, F. Zhang, M. R. Andersson, *J. Mater. Chem.* **2012**, *22*, 2306.

[39] T. Lei, J.-H. Dou, Z.-J. Ma, C.-H. Yao, C.-J. Liu, J.-Y. Wang, J. Pei, *J. Am. Chem. Soc.* **2012**, *134*, 20025.

[40] E.-S. Shin, Y. H. Ha, E. Gann, Y.-J. Lee, S.-K. Kwon, C. R. McNeill, Y.-Y. Noh, Y.-H. Kim, *ACS Appl. Mater. Interfaces* **2018**, *10*, 13774.

[41] J. Yang, Z. Zhao, H. Geng, C. Cheng, J. Chen, Y. Sun, L. Shi, Y. Yi, Z. Shuai, Y. Guo, S. Wang, Y. Liu, *Adv. Mater.* **2017**, *29*, 1702115.

[42] J. Barron, S. Attar, A. Ghobadi, S. Gangopadhyay, D. Sredojevic, M. Al-Hashimi, S. Guha, A. C. S. Appl. *Electron. Mater.* **2024**, *6*, 1464.

[43] A. Laudari, J. Barron, A. Pickett, S. Guha, *ACS Appl. Mater. Interfaces* **2020**, *12*, 26757.

[44] A. Laudari, A. Pickett, F. Shahedipour-Sandvik, K. Hogan, J. E. Anthony, X. He, S. Guha, *Adv. Mater. Interf.* **2019**, *6*, 1801787.

[45] Y. Zheng, R. Venkatesh, C. P. Callaway, C. Viersen, K. H. Fagbohungbe, A. L. Liu, C. Risko, E. Reichmanis, C. Silva-Acuña, *Chem. Mat.* **2023**, *35*, 10258.